Welcome to the latest Renesas Electronics' PCI Express® Timing Blog entry. The PCIe Express Gen6 Base Specification has been released, and supply chains are vastly different than when I wrote the last entry. So now is a good time to revisit "future-proof." When system designers talk about future-proofing, we refer to the attempt to reuse designs for multiple product generations. Sometimes that means anticipating certain technology developments so that one’s project is not made obsolete too soon. That said, some things cannot be anticipated. For Renesas, future proofing in the current supply chain environment includes choosing process nodes with sufficient upside capacity for new devices.

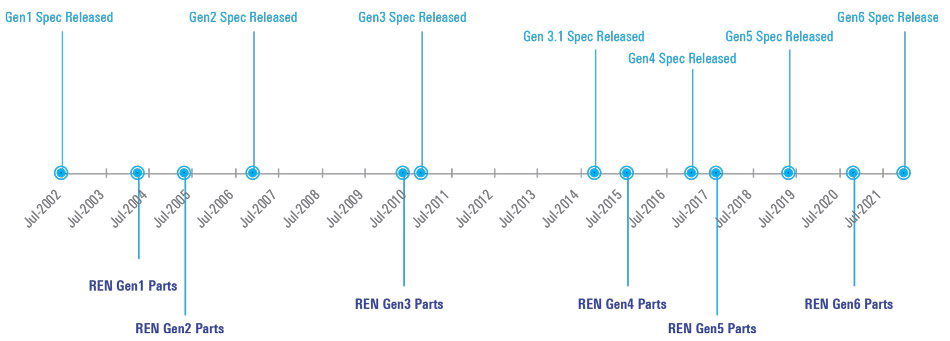

In a prior blog post, Comparing and Contrasting PCIe and Ethernet Clock Jitter Specifications, I mentioned that the PCI SIG was moving to release new specifications at a faster pace. The 7-year gap between the release of the Gen3 and Gen4 specifications was unacceptably long. The Gen5 specification was released less than 2 years after Gen4, and the Gen6 specification was released in January 2022, less than 3 years after the Gen5 specification release.

How does this faster pace impact future proofing? A timing device used in PCIe Gen2 systems could be used for almost a decade before PCIe Gen3 systems came to market. A decade of reuse is very cost-effective. The faster-paced release of new PCIe specifications implies a faster-paced release of systems supporting the new specifications. This means that it is likely designs will be reusable for shorter amounts of time. When Renesas designs PCIe clock chips, we always attempt to aim ahead of the proposed performance specifications. Several of our clocks designed for PCIe Gen3 (9FGL02/04/06/08) support PCIe Gen4 and Gen5. Many of our PCIe Gen4 clocks support PCIe Gen5 and PCIe Gen6 (9FGV1002/9FGV1006). Our new 9SQ440 server main clock, designed to support PCIe Gen5, also supports PCIe Gen6 with margin (40fs RMS against the 100fs RMS spec limit). Since newer PCIe generations are always backward compatible with older generations, these newer devices can also be used to support older designs. Both Renesas and our customers share in the following benefits:

- Customers get improved performance margin for today’s systems and can continue using the parts for next-generation designs. This reduces procurement costs, qualification efforts, and design time.

- Renesas can increase lifetime volumes on the clock chips, improving reliability and bringing about additional supply-chain benefits, which also accrue to our customers.

Figure 1 shows a timeline of PCI Express development since its beginning. The top half of the timeline lists the release dates for each PCIe specification. The bottom half shows the availability dates of Renesas' PCIe-compliant clocks for each generation. In general, clocks were available before the specifications were released. The exception to date has been PCIe Gen1 when the whole industry was bringing an entirely new technology ecosystem to market.

Figure 1. Timeline of PCI Express development

The time between the release of a PCI Express specification and deployment of compliant systems can be significant, years in some cases. Looking at Figure 1, Renesas had PCIe Gen4-compliant parts in late 2015, the PCIe Gen4 specification was released in late 2017, and PCIe Gen4 systems began shipping in mid-2019. When we have devices that are compliant with an unreleased specification, we note that they are ready for the upcoming generation. The devices we introduced in late 2015 were described as Gen4-ready. In 2017, we released Gen5-ready devices, and in 2020 we had Gen6-ready parts. Today, we have Gen6 compliant devices available and are looking at Gen7!

There is more to a clock chip than jitter performance. To illustrate this point, I’d like to use a sports car analogy. There is more to a sports car than horsepower. Braking ability, steering and traction all influence how fast a car is around a racetrack. There is a road course in Germany called the Nurburgring. Performance automobile manufacturers develop cars at this track. Running a quick time requires power, braking, steering, traction, and predictable behavior. A 2015 model from a particular manufacturer completed the course in 7 minutes, 20 seconds (7:20). The engine in this car produced 368kW (493hp). The 2018 model of the same car has an engine that produces 383kW (513hp), along with numerous improvements in braking, handling, and traction. It ran the same course in 6:56.4! This is a 6% reduction in lap time with only a 4% increase in power.

The analogy holds for Renesas timing. There is more to a clock chip that jitter performance. Features providing predictable behavior in unusual conditions, reduced propagation delays, tight output-to-output skews and great jitter performance all contribute to a future-proof clock design. Check out the new RC19024/20/16/13/08/04 family of clock buffers and RC19216/08/04/02 family of clock muxes for some outstanding examples.

Visit renesas.com/pcietiming to see the complete PCIe timing portfolio and select the clock generator or buffer that best fits your next design.