# Analog Decoder for Single Wire Multi-Key Detection

Author: Howard Sung Date: May 15, 2016

### Introduction

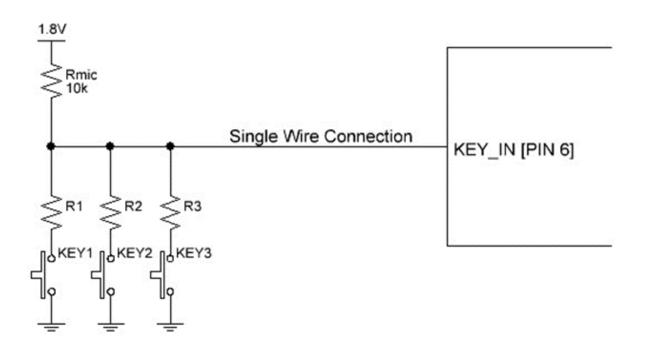

This application note will explain how to build a multi-level comparator for single wire, multi-key detection using three components in GreenPAK4: the ADC block, the digital comparator (DCMP) and the analog comparator (ACMP). This concept is useful when trying to decode an analog input voltage that varies with external circumstances. For this application note, this analog voltage will be varied using three input buttons as shown in Figure 1.

### **Key Detection Schematic**

Figure 1 shows the button pressing schematic for this design. By pressing KEY1 (or KEY2/KEY3), R1 (or R2/R3) forms a resistive divider with R<sub>mic</sub> and produces an analog voltage at KEY IN. This single wire design reduces the number of hardware connections between the KEYs and KEY IN. In order to resistor values, needs choose one determine the desired KEY\_IN voltages for each button press. In this particular design,  $R_{mic}$  has been set to 10 k $\Omega$ . Table 1 shows the desired voltages for single key button presses.

**Figure 1. Key Detection Schematic**

# **Analog Decoder for Single Wire Multi-Key Detection**

|           | KEY_IN Voltage<br>[mV] |

|-----------|------------------------|

| VKEY1_DEC | 950                    |

| VKEY2_DEC | 770                    |

| VKEY1_DEC | 630                    |

**Table 1. Single Key Press Voltages**

Using the equation below, the resistance values in Table 2 can be calculated.

$$R_{\#} = R_{mic} * \frac{V_{KEY\#\_DEC}}{1.8V - V_{KEY\#\_DEC}}$$

|    | Resistance [ $k\Omega$ ] |

|----|--------------------------|

| R1 | 11.18                    |

| R2 | 7.48                     |

| R3 | 5.38                     |

**Table 2. Calculated Resistor Values**

## **Factory Mode Detection**

By pressing two keys at the same time, additional KEY\_IN voltages can be generated. When two buttons are pressed simultaneously, the effective resistive divider ratios change and generate the KEY\_IN voltages shown in Table . These values were calculated using the equations below.

$$V_{KEY\_IN} = \frac{R12}{R12 + R_{mic}} * 1.8; where R12 = \frac{R1 * R2}{R1 + R2}$$

$$V_{KEY\_IN} = \frac{R23}{R23 + R_{mic}} * 1.8; where R23 = \frac{R2 * R3}{R2 + R3}$$

$$V_{KEY\_IN} = \frac{R13}{R13 + R_{mic}} * 1.8; where R13 = \frac{R1 * R3}{R1 + R3}$$

|            | Equivalent<br>Resistance ( $k\Omega$ ) | KEY_IN<br>Voltage<br>[mV] |

|------------|----------------------------------------|---------------------------|

| VKEY12_DEC | 4.48                                   | 560                       |

| VKEY13_DEC | 3.63                                   | 480                       |

| VKEY23_DEC | 3.13                                   | 430                       |

**Table 3. Double Key Press Voltages**

## Functionality Diagram of Key detection

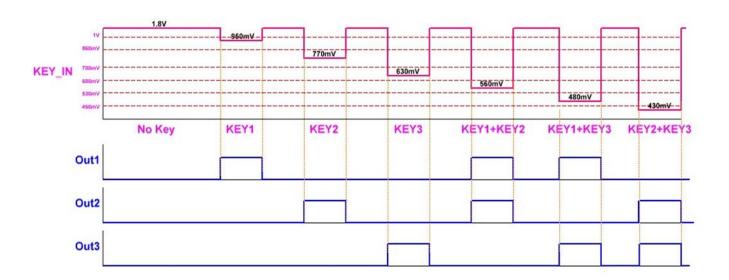

Figure 2 shows a functionality diagram for the desired key press combinations and the resulting three digital output pins.

## **GreenPAK Logic Block Set-up**

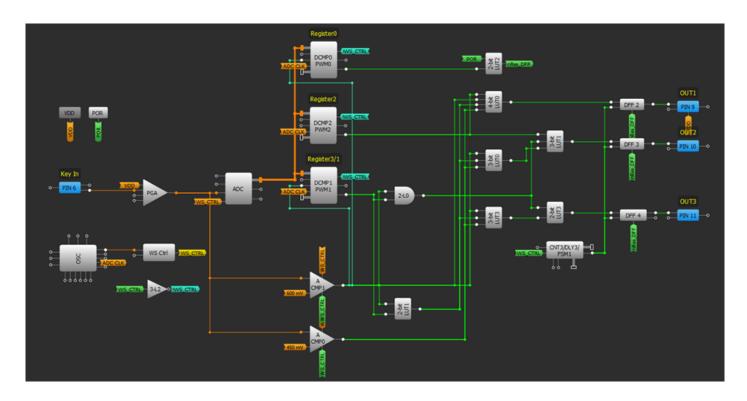

Figure 3 shows the GreenPAK configuration for decoding theses input button presses. In order to generate this multi-level comparator design, both the ACMPs and DCMPs need to be used to create the comparator window voltages shown in Figure 2 and Table 4.

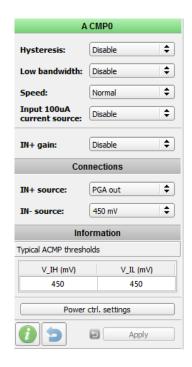

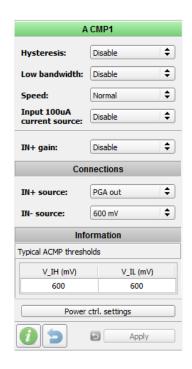

The 450 mV and 600 mV voltage levels in Table 4 are obtained using ACMP0 and ACMP1. The specific block settings are shown in Figure 4 and Figure 5 respectively. To avoid increased response time, these analog comparators should have hysteresis disabled.

**Figure 2. Key Press Functionality Diagram**

Figure 3. Key detection GreenPAK Configuration

|        | 1                  |                       |                       |

|--------|--------------------|-----------------------|-----------------------|

| Window | KEY<br>Combination | Lower Voltage<br>(mV) | Upper Voltage<br>(mV) |

| 1      | KEY2+KEY3          | 0                     | 450                   |

| 2      | KEY1+KEY3          | 450                   | 530                   |

| 3      | KEY1+KEY2          | 530                   | 600                   |

| 4      | KEY3               | 600                   | 700                   |

| 5      | KEY2               | 700                   | 860                   |

| 6      | KEY1               | 860                   | 1000                  |

| 7      | No KEY             | 1000                  |                       |

**Table 4. Comparator Windows**

Figure 4. ACMP0 setting

Figure 5. ACMP1 setting

## **Analog Decoder for Single Wire Multi-Key Detection**

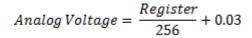

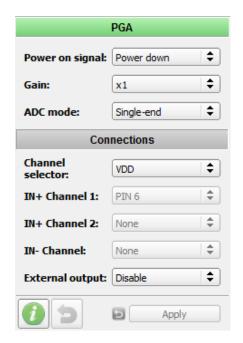

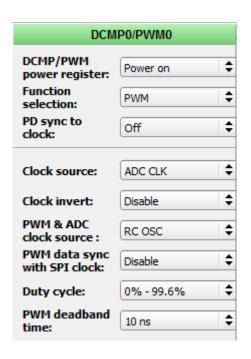

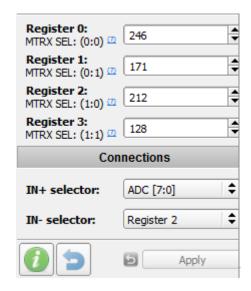

For the remaining voltage levels, the DCMPs need to be used. These blocks compare two digital bytes of information on the IN+ and IN- inputs of the logic block. To pass an input signal to the DCMPs, the input signal has to the programmable pass through amplifier (PGA) to get to the ADC. The ADC changes the analog input voltage into a digital byte and passes these values into the DCMPs. Figure 6 shows the PGA settings. Figure 7 shows the DCMP settings. When this byte of data is passed into the DCMP's IN+ terminal, it can be compared to the registers shown in Figure 8. The equation below can translate these register values into analog voltages.

Figure 6. PGA Settings

Figure 7. DCMP setting

**Figure 8. DCMP Register Settings**

## **Analog Decoder for Single Wire Multi-Key Detection**

# Minimizing Current Consumption

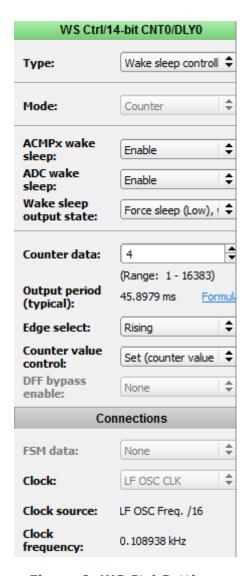

In order to minimize current consumption, the ADC, DCMP's, and ACMP's can be power cycled by using Wake/Sleep mode. Without using this feature, the current consumption is approximately 170 uA with KEY\_IN pulled high to the 1.8 V supply. In the example, supply current is lowered to 34 uA by applying the settings as shown in Figure 9, which sets the total cycle period to 45 ms. Lower current consumption can be achieved with longer cycles at the expense of sample rate. Note the wake time is determined by the clock source, and it is important to wake up the analog blocks for a sufficient amount of time. In this example, we set the clock source to LF Osc / 16 in order to ensure sufficient wake to time across full 1.7 to 5.5V voltage range and -40 to 85C temperature. For more information, please see the Wake / Sleep Timing Generator application note on Dialog's website (AN-1076).

# **Example Application: Bluetooth Headsets**

An example Bluetooth (BT) headset has 3 keys (Play, FF, and RFF) on the left side and 3 keys (Talk, Volume Up, and Volume Down) on the right side of the headset. Without this design, three wires would have to run from each side of the headset to a central node where all six buttons would be decoded. This design reduces the number of wires to two: one single wire connection from Figure 1 on each side of the headset.

BT headsets often have а common manufacturing issue centered around mechanical button wiring done by hand. The single wire decoding methods described in this application note help decrease the production failure rate by minimizing the number of wire connections between the left and right sides of the BT headset.

Figure 9. WS Ctrl Settings

# Analog Decoder for Single Wire Multi-Key Detection

### Conclusion

By using the DCMP and ACMP blocks in the GreenPAK4, we were able to create a 7 window multi-level comparator for single

wire, multi-key detection. In addition to the button pressing application described in this application note, this design can be altered to decode any analog input voltages provided to the Dialog's GreenPAK4.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.