Renesas Synergy<sup>™</sup> Platform

# Power Profiles v2 (PPV2) Framework for DK-S3A7

R20AN0498EU0100 Rev.1.00 Mar 7, 2018

## Introduction

This application project enables you to effectively use the Power Profiles v2 (PPv2) Framework module in your own design, and reduces your effort in using the power control modes and low power modes (LPM) provided in Synergy MCUs. In this document you are first introduced to basic knowledge about Synergy MCU power control modes and LPMs, which are abstracted into power profile configurations and APIs in the PPv2. Then the document describes the PPv2 framework operational flow, and a basic implementation when using the PPv2 in applications. And lastly, this document provides an example of the PPv2 framework that uses the power control mode and LPM mode transitions.

The PPv2 Framework improves control for users to set a power control mode and the LPM mode in the Synergy MCU. The PPv2 Framework supports all the features of the Power Profiles v1 available in the current release of the SSP framework using the LPM v1 driver. However, Power Profiles v1 and PPv2 Framework are not compatible. Power Profiles v1 and PPv2 Framework are not compatible. Power Profiles v1 and PPv2 Framework cannot be used in the same project. For all new projects, it is recommended that applications use PPv2 Framework.

This document guides you as you add the described module to your own design, configure it correctly for the target application, and write code using the included application example code as a reference and efficient starting point. References to API descriptions that better illustrate advanced uses of the module are available in the SSP User Manual version 1.3.0 or later, which is a valuable resource for creating increasingly complex designs.

## **Required Resources**

To perform the procedures in this application notes, you need:

- Renesas DK-S3A7(v2.0) kit

- Micro USB cables

- e<sup>2</sup> studio ISDE 5.4.0.023 or later (Renesas Electronics America Inc.)

- IAR Embedded Workbench<sup>®</sup> for Renesas Synergy<sup>™</sup> 7.71.3 or later (IAR Systems)

- Synergy Software Package (SSP) v1.3.0 (Renesas Electronics America Inc) or later.

- Synergy Standalone Configurator (SSC) v5.4.0.023 or later.

You can download the required Renesas software from the Renesas Synergy Gallery (https://synergygallery.renesas.com).

## Prerequisites

As the user of this application note, it is assumed that you have some experience with the Renesas  $e^2$  studio ISDE and SSP. For example, before you perform the procedure in this application note, you should follow the procedure in the *SSP User's Manual* to build and run the Blinky project. By doing so, you will become familiar with  $e^2$  studio and the SSP. This also ensures that the debug connection to your board is functioning properly.

The intended audience are users who want to develop applications using PPv2 Framework with S1/S3/S5/S7 Synergy MCU series.

## Contents

| 1. Synergy Power Profiles Overview                                   | 4  |

|----------------------------------------------------------------------|----|

| 1.1 Power Profile v2 Framework Overview                              | 4  |

| 1.1.1 PPv2 Framework Features                                        | 4  |

| 1.2 Synergy MCU Power Profile Overview                               | 4  |

| 1.2.1 Synergy MCU Power Control Modes                                | 4  |

| 1.2.2 Synergy MCU Low Power Modes                                    | 6  |

| 2. Power Profile v2 Framework Operational Overview                   | ß  |

| 2.1 Power Profile v2 Framework Operational Overview                  |    |

| 2.1.1 PPv2 Framework Run Profile                                     |    |

| 2.1.2 PPv2 Framework Low Power Profile                               |    |

| 2.2 PPv2 Low Power Modes Operational Notes                           |    |

| 2.3 PPv2 Module Limitations                                          |    |

|                                                                      |    |

| 3. Power Profile v2 Module APIs Overview                             | 11 |

| 3.1 PPv2 Framework API Functions                                     | 11 |

| 4. Including the PPv2 Framework in an Application                    | 13 |

| 4.1 Including PPv2 Framework using ThreadX                           | 13 |

| 4.1.1 Adding PPv2 Run Profile Module into a Thread                   | 14 |

| 4.1.2 Adding the PPv2 Low Power Profile Module into a Thread         | 16 |

| 4.2 Including PPv2 Framework without using ThreadX                   | 16 |

| 4.2.1 Adding PPv2 Run Profile Module into the HAL/Common Stacks      | 16 |

| 4.2.2 AddingPPv2 Low Power Profile Module into the HAL/Common Stacks | 17 |

| 5. Configuring PPv2 Framework Modules                                | 17 |

| 5.1 Configuration of PPv2 Framework Run Profile                      |    |

| 5.1.1 I/O Configuration of PPv2 Framework Run Profile                |    |

| 5.1.2 CGC Configuration of PPv2 Framework Run Profile                |    |

| 5.2 Configuration of PPv2 Framework Low Power Profile                |    |

| 5.2.1 Configuration of the LPM Sleep Mode                            |    |

| 5.2.2 Configuration of the LPM Standby Mode                          | 22 |

| 5.2.3 Configuration of the LPM Snooze mode                           | 23 |

| 5.2.4 Configuration of the LPM Deep Software Standby Mode            | 23 |

| 5.3 Configuration of PPv2 Framework Common Modules                   | 26 |

| 6. PPv2 Framework Application Example                                | 27 |

| 6.1 Project Overview                                                 |    |

| 6.2 Project Software Architecture                                    |    |

| 6.3 Project Configuration                                            |    |

| 6.3.1 Configuration of the Power_Ctl_Mode_Thread                     |    |

| 6.3.2 Configuration of the LPM_Mode_Thread                           |    |

|                                                                      |    |

| 7.  | Running the PPv2 Framework Module Application Example          | .33 |

|-----|----------------------------------------------------------------|-----|

| 7.1 | Powering up the Board                                          | 33  |

| 7.2 | Verifying the Demo                                             | 34  |

| 8.  | Customizing the PPv2 Framework Module for a Target Application | 34  |

| 9.  | References                                                     | 35  |

## 1. Synergy Power Profiles Overview

## 1.1 Power Profile v2 Framework Overview

The Power Profiles v2 (PPv2) Framework is a component of the Synergy Software Package (SSP), and is intended to help SSP users in configuring and utilizing sophisticated power saving features of the Synergy MCU Groups. The PPv2 modules can be instantiated into ThreadX RTOS aware multithreads, and configured with the SSP configurator to the expected power control modes and LPM modes, and then inserted into application. However, users are required to understand those power saving features of the Synergy MCU Groups to properly set up the PPv2 modules.

#### 1.1.1 PPv2 Framework Features

Some of the supported features of the PPv2 are:

- Configurable options to set different MCU power control modes with customizable clock domains

- Configurable options to set different MCU low power modes with different IO port or pin configurations

- Supports both threaded and non-threaded operations

## 1.2 Synergy MCU Power Profile Overview

Synergy MCU Groups utilize two sets of control registers, Power Control Modes and Low Power Modes (LPMs), to support different power or performance requirements. This section describes basic concepts and usage of these modes. For more details, refer to the specific *Synergy Microcontroller Group User's Manual* for the configuration of the control register, and the *Synergy SSP User's Manual* for APIs.

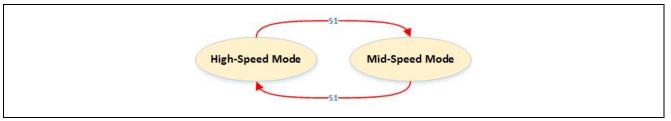

#### 1.2.1 Synergy MCU Power Control Modes

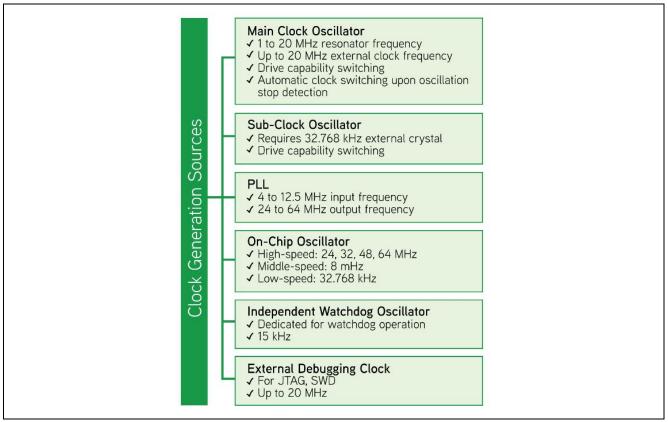

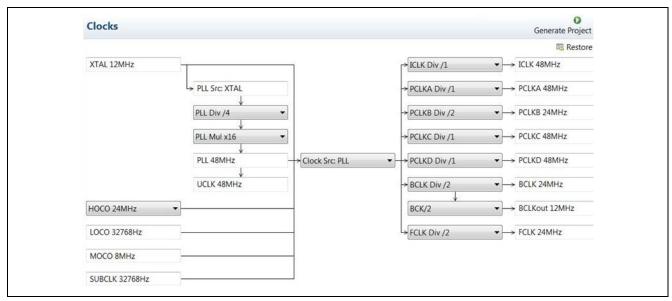

Power consumption can be reduced in Normal or running mode by selecting an appropriate operating power control mode with different clock sources and the operating frequencies. This capability enables flexible operation and optimization of the devices across several power and performance points. The system clock can be provided externally (from a single-ended clock source) or it can be generated internally using different on-chip oscillators such as the main clock oscillator, or sub-clock oscillator. Moreover, you can adjust the System Clock (ICLK), Peripheral Module Clocks (PCLKB, PCLKD), External Bus Clock (BCLK), etc. by setting different division ratios in Clock Generation Circuit (CGC) registers. A block diagram of the clock sources for the Synergy MCU S3 series is illustrated below.

Figure 1 Clock generation source for Synergy MCU S3 Series

The Synergy MCU Groups define some power control modes, such as High-speed mode, Middle-speed mode, Lowvoltage mode, Low-speed mode, and Subosc-speed mode with different clock generation sources and frequency ranges. The corresponding power consumption levels are decreased gradually. However, selecting a power control mode is a design tradeoff, where factors such as the processing time, (static and dynamic) power consumption, leakage current, and reliability should be considered.

The power control modes currently associated with the Synergy MCU Groups are listed in the following table.

|                      | Power Control Modes |                      |                     |                   |                      |  |

|----------------------|---------------------|----------------------|---------------------|-------------------|----------------------|--|

| Synergy MCU<br>Group | High-speed<br>mode  | Middle-speed<br>mode | Low-voltage<br>mode | Low-speed<br>mode | Subosc-speed<br>mode |  |

| S124                 | х                   | х                    | х                   | x                 | Х                    |  |

| S128                 | х                   | х                    | х                   | x                 | Х                    |  |

| S3A3                 | х                   | х                    | х                   | x                 | Х                    |  |

| S3A6                 | х                   | x                    | х                   | x                 | х                    |  |

| S3A7                 | х                   | x                    | х                   | x                 | х                    |  |

| S5D5                 | х                   |                      |                     | x                 | х                    |  |

| S5D9                 | х                   |                      |                     | x                 | х                    |  |

| S7G2                 | х                   |                      |                     | x                 | Х                    |  |

Note: Each Synergy MCU may have different power control modes definitions. The operating frequency and voltage of each power control mode is specified in the specific *Synergy Microcontroller Group User's Manual*. For example, the S3A7 MCU has 5 predefined power control modes as described in the *Synergy S3A7 Microcontroller Group User's Manual*, and the power consumption levels are shown in the following graphic.

|              | Oscillator |                                     |                                       |                                    |                          |                         |                                             | Deves Commention  |

|--------------|------------|-------------------------------------|---------------------------------------|------------------------------------|--------------------------|-------------------------|---------------------------------------------|-------------------|

| Mode         | PLL*1      | High-speed<br>on-chip<br>oscillator | Middle-speed<br>on-chip<br>oscillator | Low-speed<br>on-chip<br>oscillator | Main clock<br>oscillator | Sub-clock<br>oscillator | IWDT-<br>dedicated<br>on-chip<br>oscillator | Power Consumption |

| High-speed   | Available  | Available                           | Available                             | Available                          | Available                | Available               | Available                                   | . <u>Ц</u>        |

| Middle-speed | Available  | Available                           | Available                             | Available                          | Available                | Available               | Available                                   | V                 |

| Low-voltage  | N/A        | Available                           | Available                             | Available                          | Available                | Available               | Available                                   | ¥.                |

| Low-speed    | N/A        | Available                           | Available                             | Available                          | Available                | Available               | Available                                   | low               |

| Subosc-speed | N/A        | N/A                                 | N/A                                   | Available                          | N/A                      | Available               | Available                                   |                   |

#### Figure 2 Power control modes and their power consumption of the S3A7 MCU

The power control modes are defined in the Synergy MCU user's manuals.

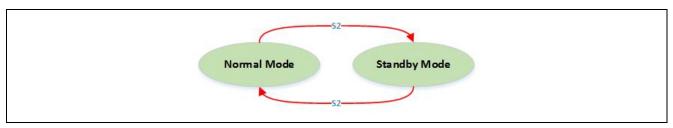

#### 1.2.2 Synergy MCU Low Power Modes

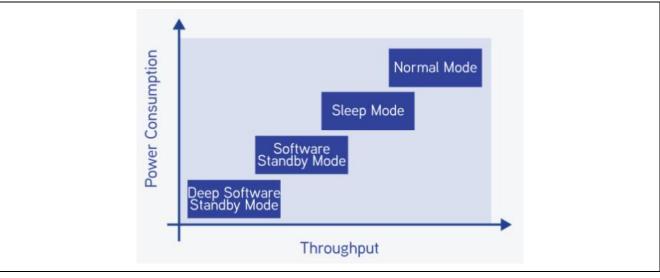

To further reduce the power consumption, the Synergy MCUs provide users Low Power Modes (LPM) by allowing operation of a peripheral while keeping the CPU and other peripherals clock gated or powered down. There are 4 possible different LPM modes: Sleep mode, Software Standby mode, Deep Software Standby mode, and Snooze mode. As an example, the core is clock gated and peripheral are available in sleep mode. The core and most peripherals are clock gated but data retained in Software Standby mode. In addition, Renessa Synergy<sup>™</sup> S7 Series and S5 Series MCUs have Deep Software Standby mode, where the core and most peripherals are powered off. Their effects on the Synergy MCUs power consumption and throughput are illustrated as below

Figure 3 Power consumption and throughput of the LPM modes

|                   |            | Low F                 | Power Modes                |             |

|-------------------|------------|-----------------------|----------------------------|-------------|

| Synergy MCU Group | Sleep Mode | Software Standby Mode | Deep Software Standby Mode | Snooze Mode |

| S124              | X          | x                     |                            | x           |

| S128              | х          | Х                     |                            | х           |

| S3A3              | х          | Х                     |                            | х           |

| S3A6              | х          | Х                     |                            | х           |

| S3A7              | х          | Х                     |                            | х           |

| S5D5              | х          | Х                     | х                          | х           |

| S5D9              | х          | Х                     | x                          | х           |

| S7G2              | х          | Х                     | x                          | х           |

#### Table 2 Low power modes supported in the Synergy MCU Groups

#### 1.2.2.1 Sleep Mode

In Sleep mode, the CPU stops operating but the contents of its internal registers are retained. Other peripheral functions do not stop. The CPU can be woken up by any interrupt, RES pin reset, a power-on reset, a voltage monitor reset, an SRAM parity error reset, or a reset caused by an IWDT or a WDT underflow.

#### 1.2.2.2 Software Standby Mode (SBY)

In SBY the CPU and most of the on-chip peripheral functions and oscillators are clock gated. However, the contents of the CPU internal registers and SRAM data, the states of on-chip peripheral functions, and the I/O ports are retained. Software Standby mode allows a significant reduction in power consumption because most of the oscillators stop in this mode. Only those interrupts specified by the Wake-UP Interrupt Enable Register (WUPEN) can cancel the Software Standby mode.

#### 1.2.2.3 Deep-Software Standby Mode (DSBY)

In DSBY more power consumption reduction compared to SBY is achieved by stopping more components such as oscillators, SRAM and flash. In this mode the contents of CPU internal registers and SRAM data, the states of on-chip peripheral functions and the I/O ports can be retained.

#### 1.2.2.4 Snooze (SNZ)

Snooze feature provides operational flexibility to dramatically reduce current consumptions. Snooze is an extension of the Software Standby mode where some peripheral modules can operate without waking up the CPU. The Snooze mode can be entered through the Software Standby mode via some interrupt sources and woken up by those available interrupts in the Software Standby Mode.

A general description of those LPM modes can be summarized in the following table, but their detailed configurations are defined in the corresponding *Synergy Microcontroller Group User's Manual*.

| Mode of<br>Operation        | Core           | Flash            | SRAM                     | RTC, AGT,<br>Vbatt, LVD | Other<br>Peripherals | IO Pins           | Snooze    |

|-----------------------------|----------------|------------------|--------------------------|-------------------------|----------------------|-------------------|-----------|

| Normal                      | Operating      | Selectable       | Selectable               | Selectable              | Selectable           | Selectable        | N/A       |

| Sleep                       | Clock<br>Gated | Selectable       | Selectable               | Selectable              | Selectable           | Selectable        | N/A       |

| Software<br>Standby         | Clock<br>Gated | Data<br>Retained | Data<br>Retained         | Selectable              | Clock Gated          | State<br>Retained | Available |

| Deep<br>Software<br>Standby | Powered<br>Off | Powered<br>Off   | Partially<br>Powered Off | Selectable              | Powered Off          | State<br>Retained | N/A       |

Table 3

LPM modes and their basic configurations

Note: Selectable means that operating or disable can be selected by control registers. Some modules are also controlled by module-stop bit.

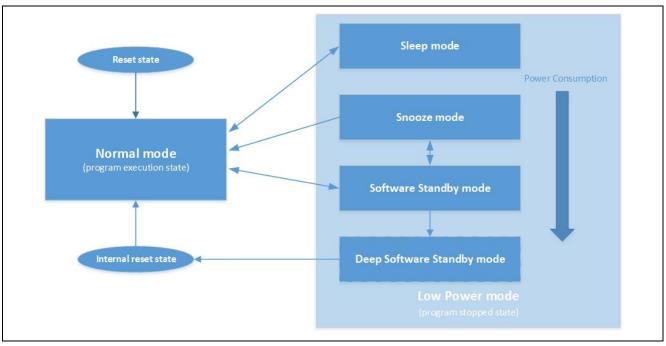

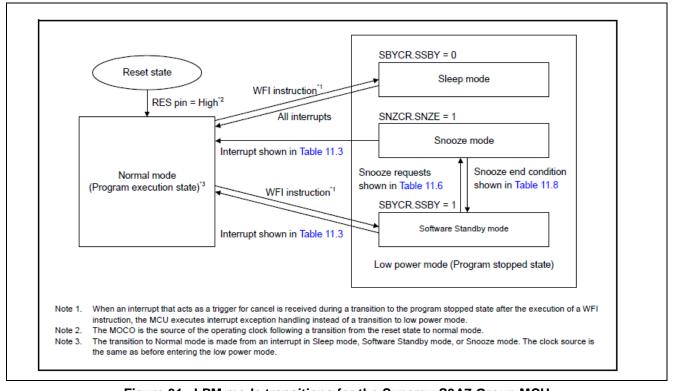

#### **1.2.2.5** Transitions between the Low Power Modes

The transitions between the Normal mode and the LPM modes can be abstracted as shown in the following figure.

Figure 4 Transitions between the Normal mode and 4 LPM modes

Note: This graph only shows possible LPM modes but does not include the transition conditions of each mode, since different Synergy MCU Groups have different number of the LPM modes, and different transition conditions. In addition, their actual power consumption is also dependent on the LPM mode configurations. The users should refer to the specific *Synergy Microcontroller Group User's Manual*.

## 2. Power Profile v2 Framework Operational Overview

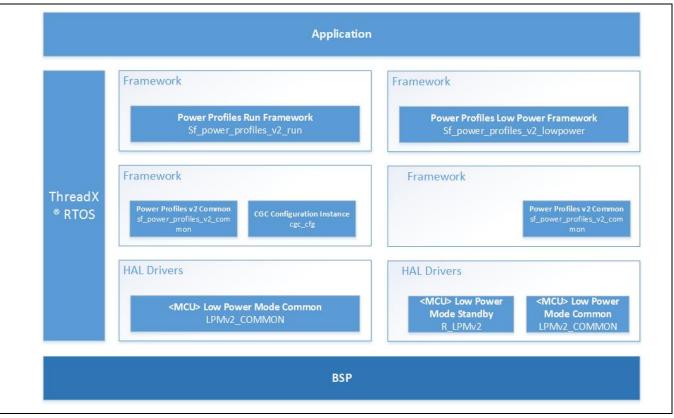

The PPv2 Framework provides a generic API for supporting low level power profiles in the Synergy MCU, when used with the LPM v2 Driver, CGC Driver, and IO Port Driver. It can be considered as an advanced control interface over the power consumption of the MCU, and can be used both in an application with or without ThreadX RTOS. Internally, it relies on the LPM v2, IOPORT, and CGC Drivers of the SSP, and provides an easy-to-use software interface to control the power modes of the MCU.

## 2.1 Power Profile v2 Framework

The PPv2 Framework provides two main profiles to control the MCU power consumption, the **Run Profile** and **Low Power Profile**. The module structure can be illustrated in the following diagram.

Figure 5 PPv2 Framework Stack

## 2.1.1 PPv2 Framework Run Profile

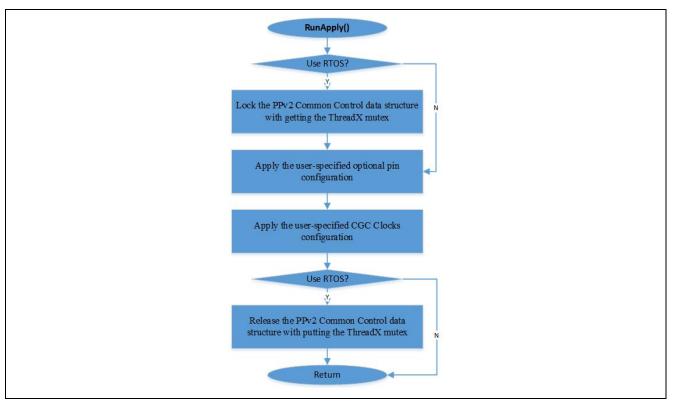

The **Run Profile** uses a CGC Clocks configuration and an IO Port pin configuration to set the system clocks and IO Port pins of the MCU in the normal running modes. Its function is implemented in the **RunApply()** API to perform the following tasks in the specified order.

Figure 6 PPv2 RunApply() process

#### 2.1.2 PPv2 Framework Low Power Profile

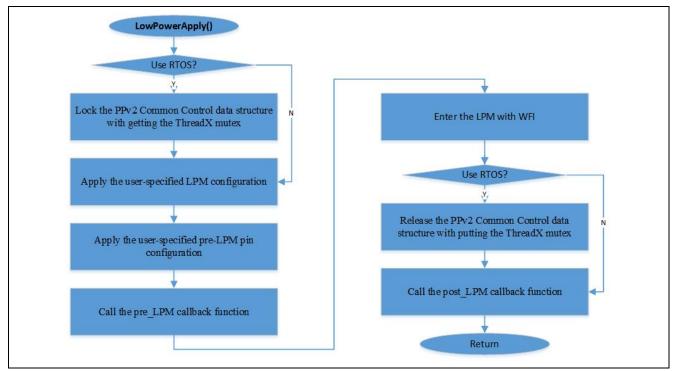

The **Low Power Profile** uses an LPM v2 configuration and both a pre-LPM and a post-LPM IO port configuration to set the low power mode and IO port pins before entering the configured low power mode and after waking up from the low power mode. See the SSP User's Manual and the particular *Synergy Microcontroller Group User's Manual* for details on the available low power modes.

The internal function LowPowerApply() API performs the following tasks in order.

Figure 7 The PPv2 LowPowerApply() process

## 2.2 PPv2 Low Power Modes Operational Notes

The following operational notes are based on observations of the current release of the PPv2 framework and driver, and will be updated as more user feedback is received, and new versions of the power profiles package are released.

#### • Power Profile v1 and PPv2

The Power Profiles v1 and PPv2 Framework are not compatible, so do not use PPv1 and PPv2 Framework in the same project. For all new projects, it is recommended that applications use PPv2 Framework.

#### • An LPM v2 driver instance is added to PPv2 applications by default

This MCU specific LPM v2 driver defines configurations and APIs for configuring, enabling and disabling LPM operations in structures of lpmv2\_mcu\_cfg\_t and lpmv2\_api\_t, then will be instantiated in the automatically generated file common\_data.c. So, PPv2 Framework instance is based on an LPM v2 Driver instance.

#### • Additional CGC driver instance for using PPv2 runApply() function

A default CGC driver is included in all Synergy projects, and instantiated in the file common\_data.c, which will not increase the code size of a project. Another instance of the CGC Driver is required for a CGC Clocks configuration of a PPv2 runApply() function.

#### • I/O port driver instance for different pin configurations

Different pin configuration tables can be defined in the PPv2 power profiles, but only one I/O port driver instance ioport\_instance\_t is instantiated in the automatically generated file common\_data.c.

#### • Operation with ThreadX

As shown in the above RunApply() and LowPowerApply() processes, the PPv2 Framework APIs uses a ThreadX intrinsic objects like a mutex for multithread applications when used with ThreadX.

#### • Special Consideration on Multithreads Applications

In following LPM modes: Software Standby, Deep Software Standby, or Snooze modes; the source clock for Systick may be configured to be disabled. So special consideration is needed when implementing a multithread RTOS project with the PPv2 LPM modes.

#### • Debugger Usage in LPM Modes

The MCU may not enter or stay in Software Standby and Deep Software Standby modes with the debugger attached, since the MCU may be woken up from Software Standby and Deep Software Standby modes by the debugger.

#### 2.3 PPv2 Module Limitations

- The Power Profiles V2 Framework open function will not be called automatically prior to the main if the project does not use ThreadX. The initialization must be done explicitly by calling g\_common\_init() or by explicitly calling the API function open(). This is not a PPv2 limitation but a result of any Framework module that supports being used without an RTOS.

- The PPv2 Framework does not handle starting or stopping MCU peripherals, since no property view is available to select which peripherals to be stopped in a LPM mode, so users must stop them manually.

- Current version of PPv2 Framework only support following Synergy MCUs: S124, S128, S3A7, S5D9, and S7G2.

- Current version of PPv2 Framework doesn't support the transition from the Snooze to the Normal in a LPM Standby mode .

#### 3. Power Profile v2 Module APIs Overview

PPv2 API functions at the framework layer and this section provides an operational overview of their usage.

## 3.1 PPv2 Framework API Functions

Assume that one of the PPv2 profiles is already added from the framework pulldown menu, and its configuration data structures corresponding to your instance are declared in the sf\_power\_profile\_v2\_api.h. This has three parts, p\_ctrl, p\_cfg, and p\_api.

```

/* This structure encompasses everything that is needed to use an instance of this interface. */

typedef struct st_sf_power_profiles_v2_instance

{

sf_power_profiles_v2_ctrl_t * p_ctrl; ///< Pointer to the control structure for this

instance

sf_power_profiles_v2_cfg_t const * p_cfg; ///< Pointer to the configuration structure for

this instance

sf_power_profiles_v2_api_t const * p_api; ///< Pointer to the API structure for this

instance

} sf_power_profiles_v2_instance_t;</pre>

```

The control structure sf\_power\_profiles\_v2\_ctrl\_t is defined as below.

```

typedef struct st_sf_power_profiles_v2_ctrl

{

uint32_t open; ///< Used by driver to check if pointer to control block is

valid

#if (1 == BSP_CFG_RTOS)

TX_MUTEX mutex; ///< Mutex used to protect access to lower level driver

hardware registers

#endif /* (1 == BSP_CFG_RTOS) */

} sf_power_profiles_v2_ctrl_t;</pre>

```

The configuration structure sf\_power\_profiles\_v2\_cfg\_t is defined as below.

The **Run Profile** configuration has a structure:

```

typedef struct st_sf_power_profiles_v2_run_cfg

{

/** Pointer to IOPORT settings */

ioport_cfg_t const * p_ioport_pin_tbl;

/** Pointer to a CGC configuration */

cgc_clocks_cfg_t const * p_clock_cfg;

/** Pointer to additional settings */

void const * p_extend;

} sf_power_profiles_v2_run_cfg_t;

```

The Low Power Profiles configuration has a structure: typedef struct st\_sf\_power\_profiles\_v2\_low\_power\_cfg { /\*\* Pointer to IOPORT settings to apply after exiting the low power mode \*/ ioport\_cfg\_t const \* p\_ioport\_pin\_tbl\_exit; /\*\* Pointer to IOPORT settings to apply before entering low power mode \*/ const \* p\_ioport\_pin\_tbl\_enter; ioport\_cfg\_t /\*\* Pointer to an LPMv2 instance \*/ lpmv2\_instance\_t const \* p\_lower\_lvl\_lpm; /\*\* Callback function \*/ void (\* p\_callback)(sf\_power\_profiles\_v2\_callback\_args\_t \* p\_args); /\*\* Placeholder for user data \*/ void \* p\_context; /\*\* Pointer to additional settings \*/ void const \* p\_extend; } sf\_power\_profiles\_v2\_low\_power\_cfg\_t;

The PPv2 framework APIs (sf\_power\_profiles\_v2\_api\_t) are summarized as follows.

#### Table 4 PPv2 framework API summary

| Function Name | Example API Call and Description                                                                                                                        |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| .open         | g_sf_power_profiles_v2_common.p_api->                                                                                                                   |

|               | <pre>open(g_sf_power_profiles_v2_common.p_ctrl,</pre>                                                                                                   |

|               | g_sf_power_profiles_v2_common.p_cfg);                                                                                                                   |

|               | Initialized the PPv2 framework.                                                                                                                         |

|               | [in,out] p_ctrl Pointer to a structure allocated by user. Elements initialized                                                                          |

|               | here.(See definition of sf_power_profiles_v2_ctrl_t)                                                                                                    |

|               | [in] p_cfg Pointer to configuration structure. Elements of the structure                                                                                |

|               | <pre>must be set by user. (See definition of sf_power_profiles_v2_cfg_t)</pre>                                                                          |

| .runApply     | g_sf_power_profiles_v2_common.p_api->                                                                                                                   |

|               | <pre>runApply(g_sf_power_profiles_v2_common.p_ctrl, &amp;p_cfg);</pre>                                                                                  |

|               | Apply a <b>Run profile</b> .                                                                                                                            |

|               | <pre>[in] p_ctrl Pointer to control block set in the open() API above.<br/>[in] p_cfg Pointer to the run configuration structure. Elements of the</pre> |

|               | <pre>structure must be set by user. (See definition of<br/>sf_power_profiles_v2_run_cfg_t)</pre>                                                        |

RENESAS

| .lowPowerApply | g_sf_power_profiles_v2_common.p_api->                                                                                                                                                                                                                         |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.5           | <b>lowPowerApply</b> (g_sf_power_profiles_v2_common.p_ctrl,&p_cfg);                                                                                                                                                                                           |

|                |                                                                                                                                                                                                                                                               |

|                | Apply a Low Power profile.                                                                                                                                                                                                                                    |

|                | <pre>[in] p_ctrl Pointer to control block set in the open() API above.<br/>[in] p_cfg Pointer to the low power configuration structure. Elements of the<br/>structure must be set by user. (See definition of<br/>sf_power_profiles_v2_low_power_cfg_t)</pre> |

| .versionGet    | <pre>g_sf_power_profiles_v2_common.p_api-&gt;versionGet(&amp;version);</pre>                                                                                                                                                                                  |

|                | Get the version and place it at the pointer version, p_version.                                                                                                                                                                                               |

|                | [out] p_version Code and API version used.                                                                                                                                                                                                                    |

| . close        | <pre>g_sf_power_profiles_v2_common.p_api-&gt; close(g_sf_power_profiles_v2_common.p_ctrl);</pre>                                                                                                                                                              |

|                | Close the framework.                                                                                                                                                                                                                                          |

|                | [in] p_ctrl Pointer to control block set in the <b>open()</b> API above.                                                                                                                                                                                      |

Note: For more detailed descriptions of operation and definitions for the function data structures, typedefs, defines, API data, API structures, and function variables, review the SSP User's Manual API References for the associated module.

The return values of the PPv2 framework APIs are defined as below.

| Name                         | Description                                  |

|------------------------------|----------------------------------------------|

| SSP_SUCCESS                  | Function successful.                         |

| SSP_ERR_ASSERTION            | Assertion error.                             |

| SSP_ERR_IN_USE               | The framework has already been initialized.  |

| SSP_ERR_INVALID_HW_CONDITION | Incompatible system clock configuration.     |

| SSP_ERR_NOT_OPEN             | Device not open.                             |

| SSP_ERR_UNSUPPORTED          | The function is not supported by the module. |

| SSP_ERR_INTERNAL             | Internal error.                              |

Note: Lower level drivers may return Common Error Codes. See the SSP *User's Manual* API References for the associated module for a definition of all relevant status return values.

## 4. Including the PPv2 Framework in an Application

There are two possible ways to include the PPv2 Framework modules into an application:

- With using ThreadX

- Without using ThreadX

## 4.1 Including PPv2 Framework using ThreadX

The typical steps in using the PPv2 Framework in an application are:

- Step 1: Add the PPv2 Run Profile modules into a thread.

- **Step 2**: Configure power control modes, and set the pin configurations (Run Profile).

- Step 3: Add the PPv2 Low Power Profile modules into a thread.

- **Step 4**: Configure the LPM modes to set the transition conditions, and the pin configurations (Low Power Profile) for pre- and post- LPM modes.

This section focuses on Step 2 & 3, to add PPv2 Framework profile modules into a thread. The profile configurations for Steps 2 & 4 are covered in the section 5.

#### 4.1.1 Adding PPv2 Run Profile Module into a Thread

Assume that a Synergy C project is already created for a selected MCU device by following the e<sup>2</sup> studio ISDE User Guide, and a new thread is also created by clicking a **New Thread** in the **Thread** tab, then click on the **Name** and **Symbol** entries in the property view, and enter a distinctive name and symbol for the new thread.

| Thread                        | S                                    |                         | Generate Pro      | ject Content |

|-------------------------------|--------------------------------------|-------------------------|-------------------|--------------|

| Threads                       | <b>a</b>                             | New Thread Stacks       |                   | <b>a</b>     |

| g_el<br>g_io<br>g_fn<br>♥ New | 4                                    |                         |                   |              |

| New The                       | read Objects 🛛 🗟 🔊                   |                         |                   |              |

|                               |                                      |                         |                   |              |

|                               |                                      |                         |                   |              |

|                               |                                      |                         |                   |              |

|                               |                                      |                         |                   |              |

|                               | BSP Clocks Pins Threads M            | essaging ICU Components |                   |              |

| *Proper                       | ties 🏼 💦 Problems                    |                         |                   |              |

| New Th                        | read                                 |                         | Enter the         | name of your |

| Settings                      | Property                             | Valu                    | -                 | re. Example: |

|                               |                                      |                         |                   |              |

| Sectings                      | ▲ Thread                             |                         |                   | ly Thread    |

| Sectings                      | Thread<br>Symbol                     | new_                    | thread0           | ly Thread    |

| Sectings                      |                                      |                         | $\sim$            | 1y Thread    |

| Sectings                      | Symbol                               |                         | thread0<br>Thread | Iy Thread    |

| Settings                      | Symbol<br>Name                       | New                     | thread0<br>Thread | Iy Thread    |

| Settings                      | Symbol<br>Name<br>Stack size (bytes) | New<br>1024             | thread0<br>Thread | Iv Thread    |

Figure 8 Adding a new thread on the Thread tab

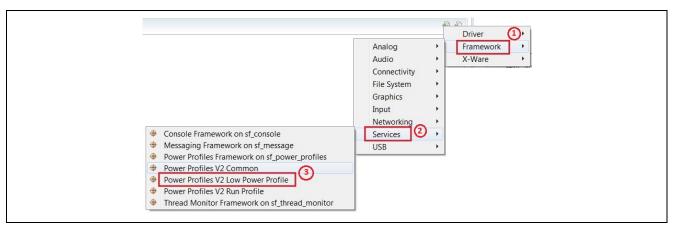

The On the selected thread, click on New to select the Run profile module from the pull-down menu.

|                                                                                                                                                                                                                                                                                                                                    | Analog Driver Driver<br>Audio Karameter Kar<br>Karameter Karameter Ka |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Console Framework on sf_console</li> <li>Messaging Framework on sf_message</li> <li>Power Profiles Framework on sf_power_profiles</li> <li>Power Profiles V2 Common</li> <li>Power Profiles V2 Low Power Profile</li> <li>Power Profiles V2 Run Profile</li> <li>Thread Monitor Framework on sf_thread_monitor</li> </ul> | Services 2 +<br>USB +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Figure 9 Adding a PPv2 Run Profile module

Then change the name of this Run Profile module to a meaningful name, such as g\_sf\_power\_profiles\_v2\_run\_high\_speed\_mode.

Note: You should give each instance of the PPv2 module a unique name in your project.

| Property                                                                        | Value                                      |

|---------------------------------------------------------------------------------|--------------------------------------------|

| Module g_sf_power_profiles_v2_run_high_speed_mode Power Profiles V2 Run Profile |                                            |

| Name                                                                            | g sf power profiles v2 run high speed mode |

| Pin configuration table                                                         | NULL                                       |

Figure 10 Naming the Run profile module

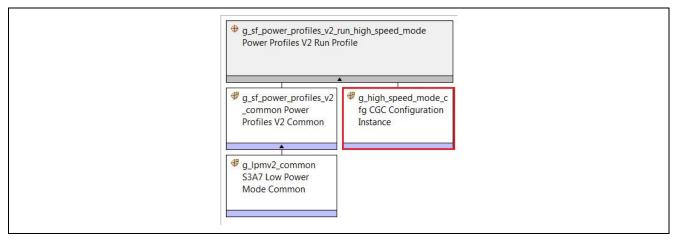

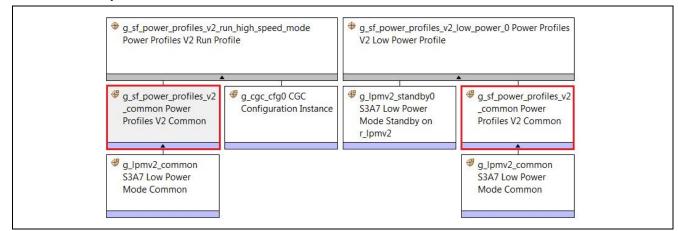

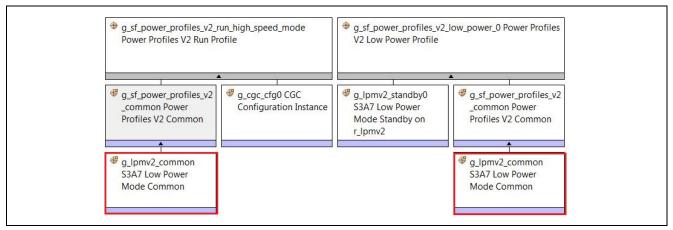

Figure 11 shows the created power control modes in the SSP configurator. Define its operating frequencies by switching clocks on and off, changing clock dividers, and selecting the system clocks in the Properties view of **the CGC Configuration Instance** module, which is covered in section 5.1.2.

| New Thread Stacks         Image: g_sf_power_profiles_v2_run_high_speed_mode         Power Profiles V2 Run Profile         Image: g_sf_power_profiles_v2_common Power         Profiles V2 Common         Image: g_dd LPM V2 Common         Image |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Figure 11 A power control mode defined in the PPv2 Run profile

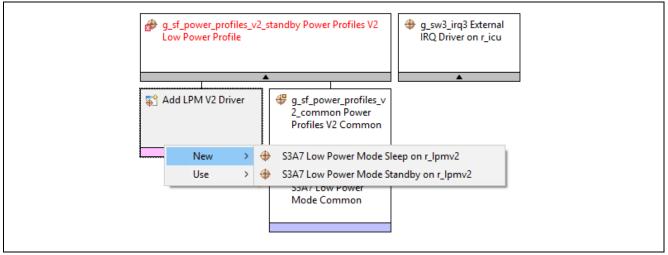

Figure 12 shows selecting a LPM common module from the **New** pull-down menu, which contains specific PPv2 framework settings for a selected Synergy MCU Group, such as S3A7.

| Wew Thread Stacks                                                                             |                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| g_sf_power_profiles_v2<br>_common Power<br>Profiles V2 Common     Add LPM V2 Common<br>Module | ▲ g_cgc_cfg0 CGC<br>Configuration Instance                                                                                                                                                                                         |

| New                                                                                           | <ul> <li>S124 Low Power Mode Common</li> <li>S128 Low Power Mode Common</li> <li>S3A3 Low Power Mode Common</li> <li>S3A7 Low Power Mode Common</li> <li>S5D9 Low Power Mode Common</li> <li>S7G2 Low Power Mode Common</li> </ul> |

Figure 12 Adding the LPM v2 common module

#### 4.1.2 Adding the PPv2 Low Power Profile Module into a Thread

On the selected thread, click **New** to select the Low Power profile module from the pull-down menu.

Figure 13 Adding a PPv2 Low Power profile module

A LPM Low Power profile module is generated in the SSP configurator. Available LPM modes for selected the MCU will be enabled.

Figure 14 PPv2 Low Power Profile Module

In their applications users can add a PPv2 framework module to represent Sleep, Standby, or Deep Standby mode.

## 4.2 Including PPv2 Framework without using ThreadX

Similar to the steps of including PPv2 into a ThreadX based application, the PPv2 Framework profile modules can also be added into a non-thread project:

- Step 1: Add the PPv2 Run Profile modules into the HAL/Common Stacks.

- Step 2: Configure power control modes, and set the pin configurations (Run Profile).

- **Step 3**: Add the PPv2 Low Power Profile modules into the HAL/Common Stacks.

- **Step 4**: Configure the LPM modes to set the transition conditions, and the pin configurations (Low Power Profile) for pre- and post- LPM modes.

Step 2 & 4 profile configurations are covered in the section 5.

#### 4.2.1 Adding PPv2 Run Profile Module into the HAL/Common Stacks

Assume that a Synergy C project is already created for a selected MCU device by following the e<sup>2</sup> studio ISDE User Guide, then click the **Add** button to add the following PPv2 Framework Run profile module.

| Threads                                                                                                        |                   |                              |                             | Generate Project Content                                     |

|----------------------------------------------------------------------------------------------------------------|-------------------|------------------------------|-----------------------------|--------------------------------------------------------------|

| Threads<br>R HAL/Common<br>g_cgc CGC Driver on r_cgc<br>g_elc ELC Driver on r_elc<br>g_fmi FMI Driver on r_fmi | HAL/Common Stacks | g_fmi FMI Driver on<br>r_fmi | g joport I/C Port     Drive | Networking      Framework     Services      Z      Yest List |

#### Figure 15 Adding a PPv2 Run Profile module into a HAL/Common stack

Assign a unique name for this Run Profile module in the property view, such as

**g\_sf\_power\_profiles\_v2\_run\_high\_speed\_mode**. Now, click **New** on the LPM common module to select a PPv2 framework configuration for a Synergy MCU Group, like Figure 9 to Figure 13 show.

#### 4.2.2 AddingPPv2 Low Power Profile Module into the HAL/Common Stacks

Similar to the operations adding PPv2 Low Power profile modules into a thread in the section 4.1.2, there are different PPv2 LPM profile modules that can be added by clicking the **Add** button, and then selecting the Low Power profile module from the pull-down menu.

## 5. Configuring PPv2 Framework Modules

Up to now sections described different ways to include the PPv2 Framework modules into applications, the next step is to show how to configure the PPv2 Framework profile modules, provide detailed configuration parameters, and give recommended values so that the user can apply them as applicable in their project applications.

Before discussing configurations of PPv2 Framework Profile modules, the property of a new thread is explained, the thread could be used with PPv2 Framework profiles shown in the Figure 8 (Section 4.2.2).

| ISDE Property                 | Value                | Description                                                          |

|-------------------------------|----------------------|----------------------------------------------------------------------|

| Symbol                        | New_thread0(default) | User can specify different name                                      |

| Name                          | New Thread (default) | User can specify different name                                      |

| Stack size (bytes)            | 1024 (default)       | Application dependent                                                |

| Priority                      | 1 (default)          | User can adjust this priority based on specific application          |

| Auto start                    | Enabled (default)    | User can adjust this setting based on the application implementation |

| Time slicing interval (ticks) | 1 (default)          | User can adjust this interval based on specific application          |

#### Table 5 Configurations for a new thread

## 5.1 Configuration of PPv2 Framework Run Profile

Assumed that a PPv2 Framework Run profile module has been included into a project by performing operations in the Section 4, with module configurations discussed in the following section.

#### 5.1.1 I/O Configuration of PPv2 Framework Run Profile

Figure 16 shows a Run profile, such as the following high-speed mode, and its configuration settings

| g_sf_power_profiles_v2_r<br>Power Profiles V2 Run Pr                                                                                                                                                              |                                                         |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|

| <ul> <li> <sup>#</sup> g_sf_power_profiles_v2<br/>_common Power<br/>Profiles V2 Common         <sup>★</sup><br/><sup>#</sup><br/><sup>g</sup>_lpmv2_common<br/>S3A7 Low Power<br/>Mode Common         </li> </ul> | g_high_speed_mode_c<br>fg CGC Configuration<br>Instance |  |

#### Figure 16 PPv2 Run Profile module

#### Table 6 Configuration settings on a Run profile module

| ISDE Property           | Value                                          | Description               |

|-------------------------|------------------------------------------------|---------------------------|

| Name                    | g_sf_power_profiles_v2_run_high_sp<br>eed_mode | Module name               |

| Pin configuration table | NULL (default)                                 | A pin configuration table |

A pin configuration table can be created for a power mode, and linked into the Run profile property. Otherwise, the power mode uses the default pin assignment given by g\_bsp\_pin\_cfg.

Basic steps to create a custom pin configuration table are given as follows:

- Copy a given board pin configuration file, such as S3A7-DK.pincfg, by right-clicking the file with the mouse button, selecting **Copy** from the menu, and then **Paste** to copy it into the same project.

- Rename this new pin configuration file, e.g., S3A7-DK2\_RUN.pincfg.

#### Figure 17 Create a new pin configuration file with Copy and Pates

• Figure 18 shows selecting the new pin configuration from the pull-down menu on the Pins tab of SSP Configurator, then specifying a pin configuration name to be generated.

| Select pin configuration              | on o      |                         |      |

|---------------------------------------|-----------|-------------------------|------|

| S3A7-DK2_RUN.pincfg                   | ▼ Gener   | ate data: g_run_pin_cfg | ] () |

| R7FS3A77C3A01CFB.pi<br>S3A7-DK.pincfg | incfg     |                         | ୍    |

| S3A7-DK2_RUN.pincfg                   | <b></b> 0 | Pin Configuration       |      |

| type filter text                      |           |                         |      |

| ▷ ✓ Ports                             |           |                         |      |

| Peripherals                           |           |                         |      |

| Other Pins                            |           |                         |      |

Figure 18 Select a new pin configuration file to be assigned

• Configure I/O functions on each pin, and then generate a new pin configuration by pressing the **Generate Project Content** button on the SSP Configurator as specified in the *Synergy SSP User's Manual*.

#### 5.1.2 CGC Configuration of PPv2 Framework Run Profile

A power control mode of this Run Profile can be defined using the property view of a CGC Configuration Instance.

#### Figure 19 CGC Configuration Instance in the Run Profile module

Table 7 lists parameters of the CGC configuration property view.

| ISDE Property           | Value                                           | Description                         |

|-------------------------|-------------------------------------------------|-------------------------------------|

| Name                    | g_cgc_cfg                                       | Module name                         |

| System Clock            | HOCO (default), MOCO, LOCO, Main                | Set the system clock source         |

|                         | Oscillator, Sub-Clock, PLL                      |                                     |

| LOCO State Change       | None (default), Stop, Start                     | LOCO state change selection         |

| MOCO State Change       | None (default), Stop, Start                     | MOCO state change selection         |

| HOCO State Change       | None (default), Stop, Start                     | HOCO state change selection         |

| Sub-Clock State Change  | None (default), Stop, Start                     | Sub-clock state change selection    |

| Main Clock State Change | None (default), Stop, Start                     | Main clock state change selection   |

| PLL State Change        | None (default), Stop, Start                     | PLL source clock selection          |

| PLL Source Clock        | HOCO (default), MOCO, LOCO, Main                | Set the PLL source                  |

|                         | Oscillator, Sub-Clock, PLL                      |                                     |

| PLL Divisor             | 1 (default), 2, 3, 4                            | PLL Output Frequency Division       |

| PLL Multiplier          | 10.0(default), 10.5, 11.0, 11.5, 12.0, 12.5,    | PLL Output Frequency Multiplication |

|                         | 13.0, 13.5, 14.0, 14.5, 15.0, 15.5, 16.0, 16.5, |                                     |

|                         | 17.0, 17.5, 18.0, 18.5, 19.0, 19.5, 20.0, 20.5, |                                     |

|                         | 21.0, 21.5, 22.0, 22.5, 23.0, 23.5, 24.0, 24.5, |                                     |

|                         | 25.0, 25.5, 26.0, 26.5, 27.0, 27.5, 28.0, 28.5, |                                     |

|                         | 29.0, 29.5, 30.0, 31.0                          |                                     |

| PCLKA Divisor           | 1(default), 2, 4, 8, 16, 64                     | Peripheral Clock A Division         |

| PCLKB Divisor           | 1(default), 2, 4, 8, 16, 64                     | Peripheral Clock B Division         |

| PCLKC Divisor           | 1(default), 2, 4, 8, 16, 64                     | Peripheral Clock C Division         |

| PCLKD Divisor           | 1(default), 2, 4, 8, 16, 64                     | Peripheral Clock D Division         |

| BCLK Divisor            | 1(default), 2, 4, 8, 16, 64                     | External Bus Clock Division         |

| FCLK Divisor            | 1(default), 2, 4, 8, 16, 64                     | Flash Clock Division                |

| ICLK Divisor            | 1(default), 2, 4, 8, 16, 64                     | System Clock Division               |

Note: Assignments on these CGC parameters must be satisfied given the oscillator availability for each power control mode, and the expected frequencies of each operating clock. Specific relationships are shown in a CGC block diagram in the applicable Synergy MCU User's Manual.

The maximum operating frequency range for these clocks should not be outside the given ranges in the MCU User's Manual. Figure 20 shows a table from the *S3A7 Microcontroller Group User's Manual* listing clock specifications.

| ltem                                 | Clock source                     | Clock supply                                                                   | Specification                                                                       |

|--------------------------------------|----------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| System clock (ICLK)                  | MOSC/SOSC/HOCO/MOCO/<br>LOCO/PLL | CPU, DTC, DMAC, Flash,<br>SRAM                                                 | Up to 48 MHz<br>Division ratio:<br>1/2/4/8/16/32/64                                 |

| Peripheral module clock A<br>(PCLKA) | MOSC/SOSC/HOCO/MOCO/<br>LOCO/PLL | Peripheral module (QSPI,<br>SPI, SCI, SCE5, SDHI, CRC,<br>IrDA, GPT bus-clock) | Up to 48 MHz<br>Division ratio:<br>1/2/4/8/16/32/64                                 |

| Peripheral module clock B<br>(PCLKB) | MOSC/SOSC/HOCO/MOCO/<br>LOCO/PLL | Peripheral module (DAC12,<br>IIC, SSI, DOC, CAC, CAN,<br>AGT, POEG, CTSU)      | Up to 32 MHz<br>Division ratio:<br>1/2/4/8/16/32/64                                 |

| Peripheral module clock C<br>(PCLKC) | MOSC/SOSC/HOCO/MOCO/<br>LOCO/PLL | Peripheral module<br>(ADC14 conversion clock)                                  | Up to 64 MHz<br>Division ratio:<br>1/2/4/8/16/32/64                                 |

| Peripheral module clock D<br>(PCLKD) | MOSC/SOSC/HOCO/MOCO/<br>LOCO/PLL | Peripheral module<br>(GPT count clock)                                         | Up to 64 MHz<br>Division ratio:<br>1/2/4/8/16/32/64                                 |

| FlashIF clock (FCLK)                 | MOSC/SOSC/HOCO/MOCO/<br>LOCO/PLL | FlashIF                                                                        | 1 MHz to 32 MHz (P/E)<br>Up to 32 MHz (Read)<br>Division ratio:<br>1/2/4/8/16/32/64 |

| External bus clock (BCLK)            | Mpsc/sosc/hoco/moco/<br>Loco/PLL | External bus                                                                   | Up to 24 MHz<br>Division ratio:<br>1/2/4/8/16/32/64                                 |

| EBCLK pin output (EBCLK)             | BCLK or 1/2 BCLK                 | EBCLK pin                                                                      | Up to 12 MHz<br>Division ratio:<br>1 or 2                                           |

| USB clock (UCLK)                     | PLL                              | USBFS                                                                          | 48 MHz                                                                              |

#### Figure 20 Maximum operating frequency range for Synergy S3A7 MCU Group internal clocks

Since the current property view does not validate assignments automatically, use the CGC panel of the SSP Configurator to check your assignments first. Figure 21 shows the CGC configuration screen with a high-speed mode example.

Figure 21 Checking the clock setting for a power control mode

Similarly, you can define the CGC configuration for other power control modes.

## 5.2 Configuration of PPv2 Framework Low Power Profile

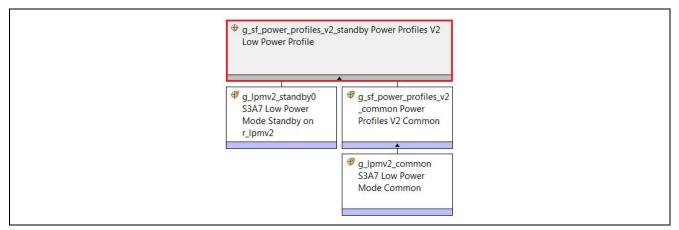

Depending on the selected Synergy MCU Group, you may have three LPM modes available in the pull-down menu of the Low Power Profile module: Sleep, Software Standby, and Deep Software Standby.

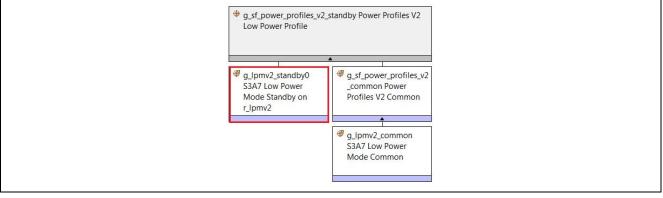

Figure 22 PPv2 Low Power Profile Standby module

Assume that a Low Power Profile module is already added into a thread, it will have the following configurations:

| Table 8 Configuration settings on the PPv2 Low Power Profile mo |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

| ISDE Property                                                        | Value                                  | Description                                                                           |

|----------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------|

| Name                                                                 | g_sf_power_profiles_v2_<br>low_power_0 | Module name                                                                           |

| Callback (Low Power Exit Event N/A when using Deep Software Standby) | NULL (default)                         | Callback function to handle the pre-entering LPM event and the post-exiting LPM event |

| Low power entry pin configuration table                              | NULL (default)                         | Pin configuration table for pre-entering LPM                                          |

| Low power exit pin configuration table                               | NULL (default)                         | Pin configuration table for post-exiting LPM                                          |

The callback function can be used for handling the following events:

- SF\_POWER\_PROFILES\_V2\_EVENT\_PRE\_LOW\_POWER

- SF\_POWER\_PROFILES\_V2\_EVENT\_POST\_LOW\_POWER

You can change the IO port functionality with the following two pin configuration tables:

- Low power entry pin configuration table

- Low power exit pin configuration table

These tables are used internally in the PPv2 API function LowPowerApply().

#### 5.2.1 Configuration of the LPM Sleep Mode

The configuration of the LPM Sleep mode is simple, since any interrupt wakes the MCU from the Sleep mode. So only the module name can be renamed.

| g_sf_power_profiles_v2_low_power_0 Power Profiles<br>V2 Low Power Profile                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Image: g_lpmv2_sleep0 S3A7         Low Power Mode         Sleep on r_lpmv2             Image: g_sf_power_profiles_v2         _common Power         Profiles V2 Common |

| g_lpmv2_common<br>S3A7 Low Power<br>Mode Common                                                                                                                       |

#### Figure 23 PPv2 Low Power Profile Sleep driver r\_lpmv2

#### Table 9 Configuration Settings on the PPv2 Profile Sleep module

| ISDE Property      | Value                            | Description                                |

|--------------------|----------------------------------|--------------------------------------------|

| Parameter Checking | BSP (default), Enabled, Disabled | Enables or disables the parameter checking |

| Name               | g_lpmv2_sleep0                   | Module name                                |

#### 5.2.2 Configuration of the LPM Standby Mode

The Standby mode configuration sets up the exit triggers, and some transition conditions between the Standby and the Snooze mode, which are treated as a special case of the Standby mode in the current release of the PPv2. See the next section for more about the Snooze configuration.

Figure 24 shows an example of a S3A7 MCU Standby module.

Figure 24 PPv2 Low Power Profile Standby driver r\_lpmv2

#### Table 10 Configuration settings on the PPv2 Profile Standby module r\_1pmv2

| ISDE Property                    | Value                           | Description                                |

|----------------------------------|---------------------------------|--------------------------------------------|

| Parameter Checking               | BSP (default), Enabled,         | Enables or disables the parameter checking |

|                                  | Disabled                        |                                            |

| Name                             | g_lpmv2_standby0                | Module name                                |

| Choose the low power mode        | Standby (default), Standby with | Low power mode selection                   |

|                                  | Snooze enabled                  |                                            |

| Output port state in standby and | No Change (default), High       | Output port state selection                |

| Deep Software Standby, applies   | Impedance state                 |                                            |

| to address output, data output,  |                                 |                                            |

| and other bus control pins       |                                 |                                            |

| Select Standby Exit Sources      |                                 | Select Fields below                        |

| IRQ[0:15]                        | Enabled, Disabled (default)     | Select an external IRQ0 to IRQ15           |

| IWDT                             | Enabled, Disabled (default)     | IWDT selection                             |

| ISDE Property                  | Value                          | Description                            |

|--------------------------------|--------------------------------|----------------------------------------|

| Key Interrupt                  | Enabled, Disabled (default)    | Key Interrupt selection                |

| LVD1 Interrupt                 | Enabled, Disabled (default)    | LVD1 selection                         |

|                                | (Default: Disabled)            |                                        |

| LVD2 Interrupt                 | Enabled, Disabled (default)    | LVD2 selection                         |

| Analog Comparator High-speed 0 | Enabled, Disabled (default)    | Analog Comparator selection            |

| Interrupt                      |                                |                                        |

| RTC Period                     | Enabled, Disabled (default)    | RTC Period selection                   |

| RTC Alarm                      | Enabled, Disabled (default)    | RTC Alarm selection                    |

| USBFS                          | Enabled, Disabled (default)    | USBFS selection                        |

| AGT1 underflow                 | Enabled, Disabled (default)    | AGT1 underflow selection               |

| AGT1 Compare Match A           | Enabled, Disabled (default)    | AGT1 CMA selection                     |

| AGT1 Compare Match B           | Enabled, Disabled (default)    | AGT1 CMB selection                     |

| I2C 0                          | Enabled, Disabled (default)    | I2C 0 selection                        |

| Snooze Mode Settings           |                                |                                        |

| Snooze Entry Source            | RXD0 falling edge (default),   | Source of entering the Snooze mode     |

|                                | IRQ0:15, KINT (Key Interrupt), |                                        |

|                                | ACMPLP (Low-speed Analog       |                                        |

|                                | Comparator), RTC Alarm, RTC    |                                        |

|                                | Period, AGT1 Underflow, AGT1   |                                        |

|                                | Compare Match A, AGT1          |                                        |

|                                | Compare Match B                |                                        |

| Snooze Exit Sources            |                                | Select fields below                    |

| AGT1 Underflow                 | Enabled, Disabled (default)    | AGT1 Underflow selection               |

| DTC Transfer Completion        | Enabled, Disabled (default)    | DTC Transfer Completion selection      |

| DTC Transfer Completion        | Enabled, Disabled (default)    | DTC Transfer Completion Negated signal |

| Negated signal                 |                                | selection                              |

| ADC0 Compare Match             | Enabled, Disabled (default)    | ADC0 Compare Match selection           |

| ADC0 Compare Mismatch          | Enabled, Disabled (default)    | ADC0 Compare Mismatch selection        |

| SCI0 Address Match             | Enabled, Disabled (default)    | SCI0 Address Match selection           |

| DTC state in Snooze Mode       | Enabled, Disabled (default)    | DTC state in Snooze Mode selection     |

## 5.2.3 Configuration of the LPM Snooze mode

Currently, as seen in Figure 25, the Snooze mode is enabled in the property view of the PPv2 Software Standby mode by selecting "**Standby with Snooze Enabled**" in the field of the "**Choose the low power mode**."

| g_lpmv2_st  | andby0 S3A7 Low Power Mode Star       | ndby on r_lpmv2             |

|-------------|---------------------------------------|-----------------------------|

| Settings    | Property                              | Value                       |

| Information | ▲ Common                              |                             |

| Information | Parameter Checking                    | Default (BSP)               |

|             | Module g_lpmv2_standby0 S3A7 Low Pc   | ower Mo                     |

|             | Name                                  | g_lpmv2_standby0            |

|             | Choose the low power mode             | Standby with Snooze Enabled |

|             | Output port state in standby, applies | to addre Standby            |

|             | Select Standby Exit Sources           | Standby with Snooze Enabled |

|             | IRQ0                                  | Disabled                    |

|             | IRQ1                                  | Disabled                    |

|             | IRQ2                                  | Disabled                    |

|             | IRQ3                                  | Disabled                    |

Figure 25 Create a Snooze mode in the Software Standby mode

#### 5.2.4 Configuration of the LPM Deep Software Standby Mode

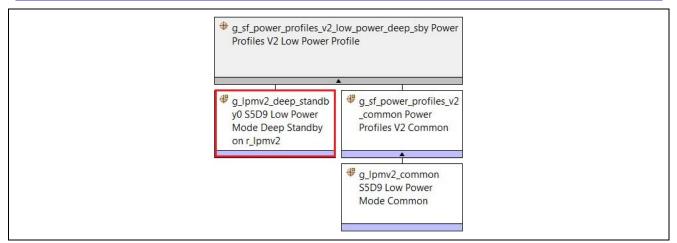

The configuration on the Deep Software Standby mode is to set the exit triggers of the Deep Software Standby mode, and the internal power supply options. Use the PPv2 Framework on the S5D9 as an example to show the possible configurations as follows:

Figure 26 PPv2 Low Power Profile Deep Software Standby driver r\_lpmv2

#### Table 11 Configuration settings on the PPv2 Profile Deep Software Standby module

| ISDE Property                                                                                                                                       | Value                                                                                                                                                                                                                                                                                          | Description                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Parameter Checking                                                                                                                                  | BSP (default), Enabled, Disabled                                                                                                                                                                                                                                                               | Enables or disables the parameter                                      |

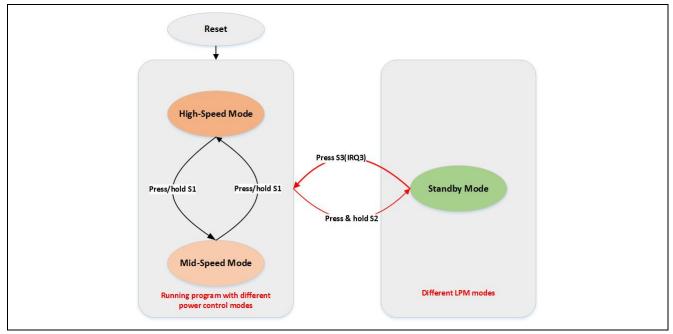

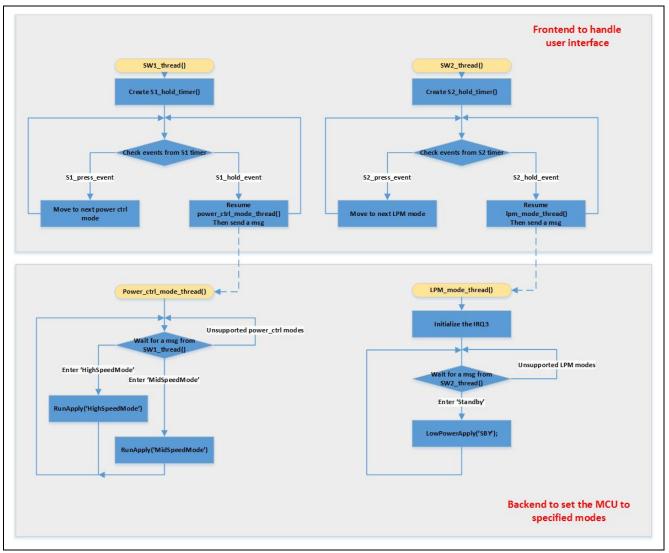

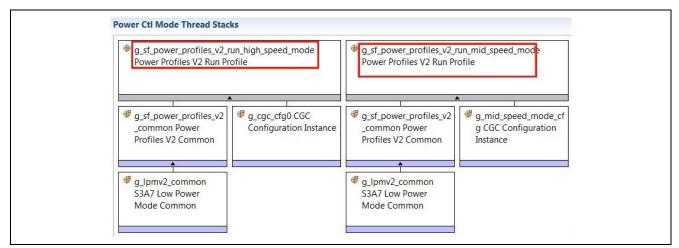

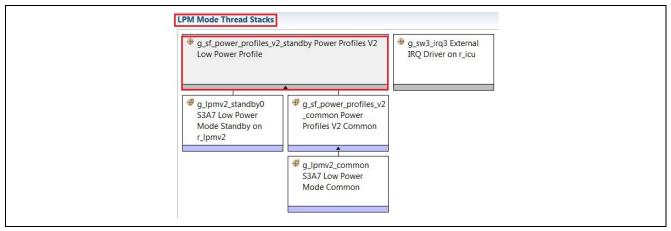

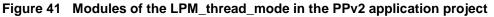

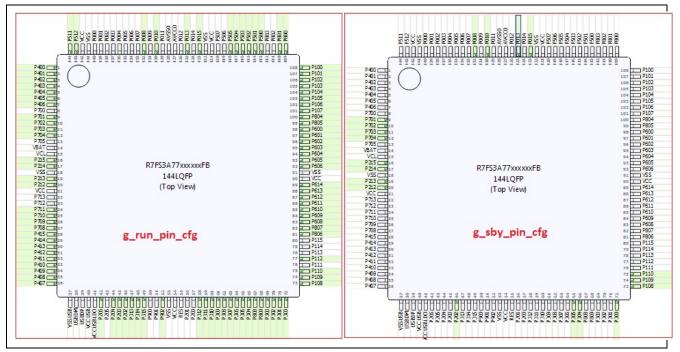

|                                                                                                                                                     |                                                                                                                                                                                                                                                                                                | checking                                                               |