Author: Bogdan Holod Date: December 22, 2014

### Introduction

This application note demonstrates how to design a simple LED brightness control using a GreenPAK chip. To control the brightness of an LED you can vary the average power which is sent to the LED. PWM from the GreenPAK can provide the varying levels of power by varying the duty cycle. For example, if we turn the LED on for 50% and off for 50% of the time, the LED will appear half as bright. The pulse width is the important factor here. By varying the pulse width we can effectively control the average light power from the LED. The minimum LED oscillating frequency should be at least 50Hz so the switching is not obvious to the human eye. In this application, we will use 50Hz. When using PWM, duty-cycle refers to the percentage of time a pulse is 'on' over the duration of the cycle. At the 50Hz frequency the resulting period is 20ms. During that time we have to turn the LED either on or off depending on the required duty-cycle. For example, a 75% duty-cycle requires the pulse to be HIGH for 15ms (LED will be off) and then LOW for 5ms (LED will be on due to open drain pulldown circuit used for this application).

# LED Brightness Control Circuit Design

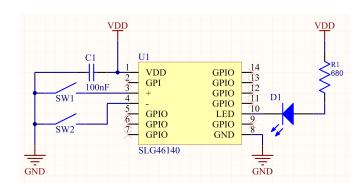

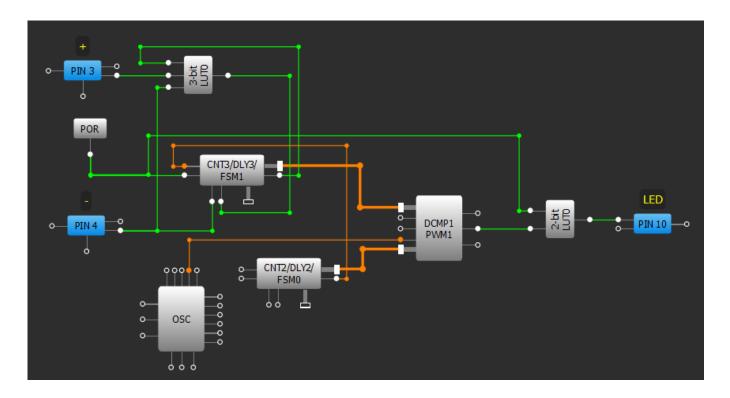

The screen capture of FSM that controls the PWM can be seen in Figure 5. The 3-bit LUT0 is connected to PIN3, PIN4, which are configured as Digital in with Schmitt trigger with pull up resistor 1MegΩ. Output of 3-bit LUT0 is connected to KEEP FSM1. When KEEP is HIGH, Q will stay at its current value. The 2-bit LUT0 is configured as NAND. Output LED is configured to be 1x Open Drain NMOS. PWM period is defined by the period of FSM0.

FSM0 period is 20ms. IN+ for the PWM is an 8-bit data string that is sourced from FSM1. IN- for the PWM is an 8-bit data string that sourced from FSM0. PWM output duty cycle ranges from 0% to 99.61% and is determined by: Output Duty Cycle = IN+/256 (IN+=0: output duty cycle = 0/256=0%; IN+=255: output duty cycle = 255/256=99.61%).

Note: PWM block has a possibility to configure duty cycle range with two options: 0% to 99.61% and 0.39% to 100%. This application note utilizes the first option.

Finite State Machine, which has features for UP/DOWN control. When UP/DOWN is HIGH, FSM is in up-counting mode, the Q value will count from 0 to 255 (256 steps total). When Q is equal to 255, OUT generates a single clock cycle pulse. When UP/DOWN is LOW, FSM is in down-counting mode. When Q is equal to 0, OUT generates a single clock cycle pulse.

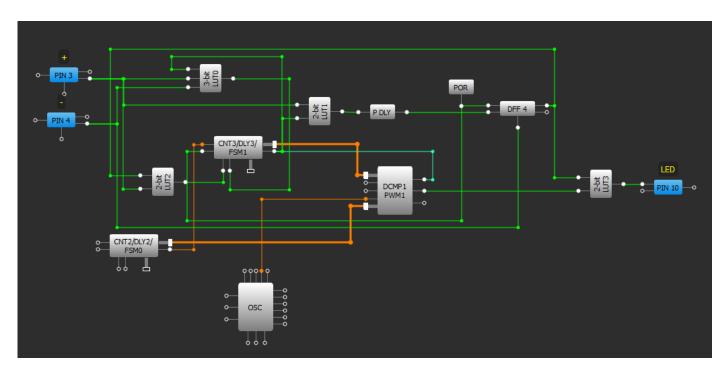

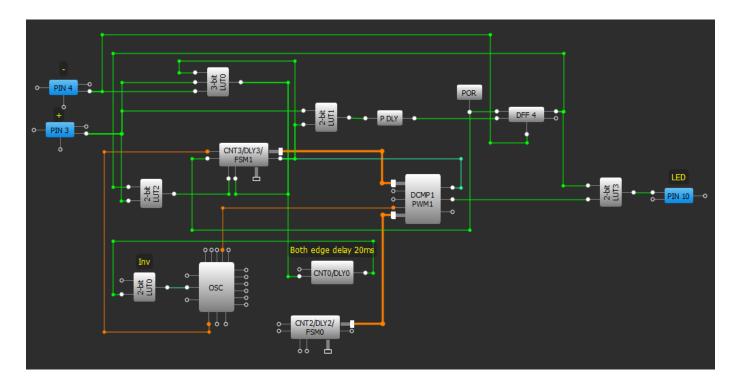

As can be seen in Figures 7 and 8, output of FSM1 is connected to the PWM SHARED PD and IN0 of 2-bit LUT1. The 2-bit LUT1, P DLY and DFF4 are used to obtain 0% duty cycle. The 2-bit LUT3 is connected to DFF4 and PWM. The 2-bit LUT3 is configured as NOR. The 2-bit LUT2 is connected to DFF4 and PIN3. Output of 2-bit LUT2 is connected to UP/DOWN of FSM1. FSM1 is in down-counting mode when the output of DFF4 is LOW and button "+" is not pressed. P DLY is configured as "both edge delay".

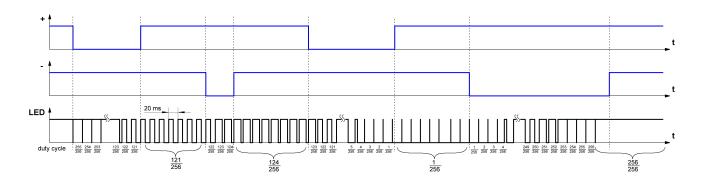

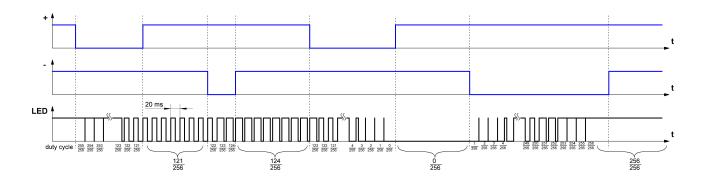

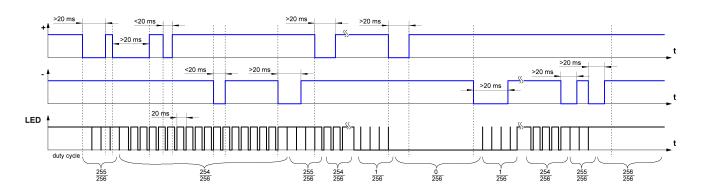

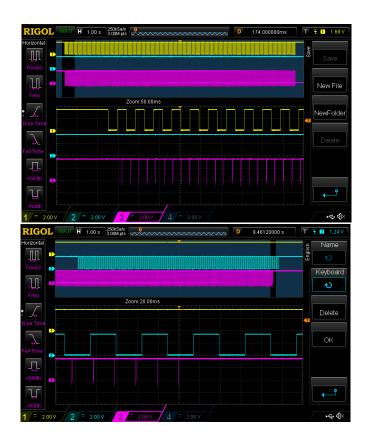

Figures 2, 3 and 4 show the timing diagrams of the circuits' functionality shown in Figures 5, 6 and 7.

Figure 1 shows the application circuit with buttons connected to the GND and LED connected to PIN 10.

Figure 1. LED Brightness Control Typical Application Circuit

Figure 2. LED Brightness Control\_1 Timing Diagram

Figure 3. LED Brightness Control\_2 Timing Diagram

Figure 4. LED Brightness Control\_3 Timing Diagram

Figure 5. LED Brightness Control\_1 Block Diagram

Figure 6. LED Brightness Control\_2 Block Diagram

Figure 7. LED Brightness Control\_3 Block Diagram

# LED Brightness Control Circuit Analysis

Figure 8 shows the operation of the design LED Brightness Control\_1. If button "+" is pressed, "LED" output will generate PWM signal with changing duty cycle from 256/256 to 1/256 (the LED brightness will go up). When button "-" is pressed, "LED" output will generate PWM with changing duty cycle from 1/256 to 256/256 (the LED brightness will go down).

LED Control\_2 design advantages are decreased quiescent current and PWM duty cycle range to 0/256.

Figure 10 shows the operation of the design LED Brightness Control \_3. If button "+" is pressed, output PWM duty cycle will decrease by 1/256. When button "-" is pressed, output PWM duty cycle will increase by 1/256.

Figure 8. LED Brightness Control \_1 waveforms. Top line is button "+" input, 2nd line is button "-" input, 3rd line – LED output

Figure 9 shows the operation of the design LED Brightness Control \_2. If button "+" is pressed, "LED" output will generate PWM with changing duty cycle from 256/256 to 0/256. When button "-" is pressed, "LED" output will generate PWM with changing duty cycle from 0/256 to 256/256.

Figure 9. LED Brightness Control \_2 waveforms. Top line is button "+" input, 2nd line is button "-" input, 3rd line – LED output

### **Related Files**

Programming code for GreenPAK Designer.

Figure 10. LED Brightness Control \_3 waveforms. Top line is button "+" input, 2nd line is button "-" input, 3rd line – LED output

## Conclusion

The PWM block is a standard block used in many devices and systems. The ease of use and configurability of this block in GreenPAK4 devices makes it a perfect candidate to replace bigger and more expensive microcontrollers.

## **About the Author**

Name: Bogdan Holod

Background: Bogdan Holod graduated from Lviv Polytechnic National University in 2011 and

received a Master's Degree in Radio engineering devices, systems and complexes. Since 2012 he has been working as a design engineer on low power analog systems,

and developing design guidelines of digital and analog electronic circuits.

## **Document History**

Document Title: GreenPAK Macro Circuit Design LED Brightness Control

Document Number: AN-1052

| Revision | Orig. of Change | Submission Date | Description of Change |

|----------|-----------------|-----------------|-----------------------|

| Α        | Bogdan Holod    | 12/22/2014      | New application note  |

### **Worldwide Sales and Design Support**

Silego Technology maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at **Silego Locations**.

#### **About Silego Technology**

Silego Technology, Inc. is a fabless semiconductor company headquartered in Santa Clara, California, with operations in Taiwan, and additional design/technology centers in China, Korea and Ukraine.

Silego Technology Inc. 1515 Wyatt Drive Santa Clara, CA 95054

Phone Fax : 408-327-8800 : 408-988-3800

Website

: ww.silego.com

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.