## AN-1062 GreenPAK Macro Cell Example: Constructing additional DFF types

Author: Serhiy Prykhodko Date: February 02, 2015

### Introduction

D-type flip flops are used in many GreenPAK designs. Sometimes a user may need more of them than the available pre-configured DFF blocks in the GreenPAK IC.

Reference books can give a variety of solutions on how to construct DFF's. However, some are not efficient designs. The following is a collection of solutions with working examples using GreenPAK. Emphasis is on simplicity, and minimizing circuit resource usage.

### From concept to simple examples

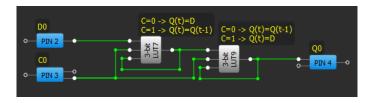

Using LUT's in the latch configuration. The first LATCH passes the logic level from the D input to the first LUT output if the C input is LOW. If the C input is HIGH, then the state of the first output doesn't change. (This corresponds to the LATCH cell function in a GPAK chip). The second LATCH operates just as the first LATCH does, but its C input is inverted. The first LATCH output is connected to the input of the second LATCH and their C inputs are connected to the same clock signal source (See Fig.1).

Figure 1. DFF based on LUT cells (DFF0)

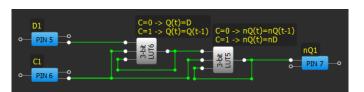

This circuit does not use an edge detector or oneshot, which avoids those potential issues. Using only two 3-bit LUTs, this DFF is also simpler than what is typically offered in reference books. A variant of this simple DFF with the inverted output is shown in Fig.2.

Figure 2. DFF with inverted output (DFF1)

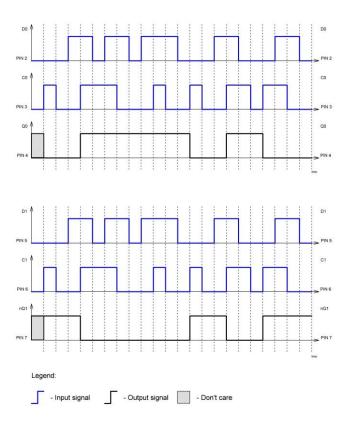

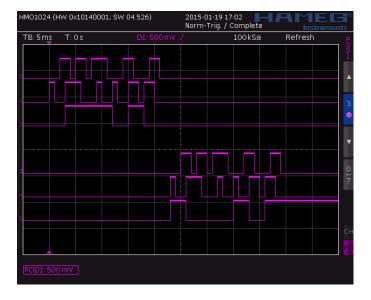

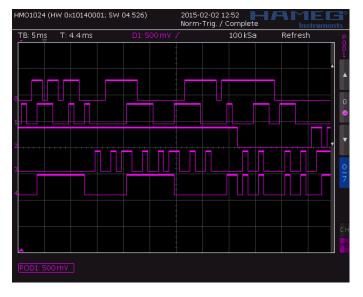

The timing diagrams and functional waveforms for these DFF's are shown in Fig.3, 4.

Fig. 4. Waveform definition:

D0 – PIN#2 (D0) D1 – PIN#3 (C0) D2 – PIN#4 (Q0) D3 – PIN#5 (D1) D4 – PIN#6 (C1) D5 – PIN#7 (nQ1)

DFF0 and DFF1 macro cells configuration can be found in Appendix 1.

## GreenPAK Macro Cell Example: Constructing additional DFF types

Figure 4. DFF0 and DFF1 functional waveforms

# DFF with nRESET or nSET input. MODE input in the DFF.

DFFs with nRESET or nSET are the type most commonly used in designs. We will look at how to construct them using LUT cells.

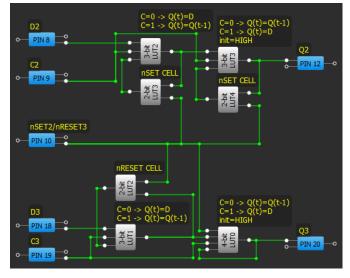

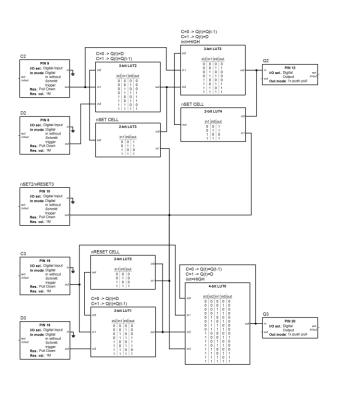

The schematic of the flip flop with nSET input (DFF2), and also with the nRESET input (DFF3) is shown In Fig. 5. There are small differences from the previous DFF0,1 versions. 2-bit LUTs are added to the feedback circuits of the first LATCH and the second LATCH.

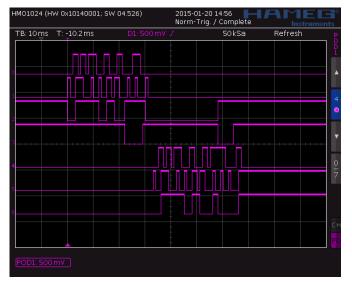

DFF3 also utilizes a 4-bit LUT in making the second latch. Operation of these DFF's is as follows. A LOW level on the nSET input will set output of each LATCH HIGH and then the DFF2 output will be set HIGH. Similarly, a LOW on the nRESET input will set output of each LATCH LOW that will reset the DFF3 output. Timing diagrams for DFFs with nSET and nRESET inputs can be found in Fig. 6. Waveforms for these flip flops operation are shown in Fig. 7.

Figure 5. DFFs with nSET and nRESET input

Figure 6. DFF2 and DFF3 timing diagram

Fig. 7. Waveform definition:

D0 – PIN#8 (D2) D1 – PIN#9 (C2) D2 – PIN#12 (Q2) D3 – PIN#10 (nSET2/nRESET3) D4 – PIN#18 (D3) D5 – PIN#19 (C3) D6 – PIN#20 (Q3)

# RENESAS

Figure 7. DFF2 and DFF3 functionality waveform

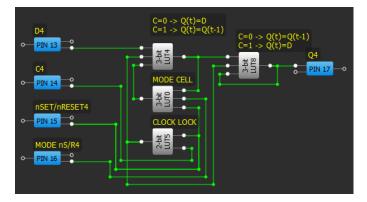

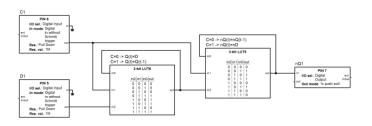

The previously described DFF0,1,2,3 examples are functional equivalents of preconfigured GreenPAK DFF cells. The following example will extend DFF functionality within GreenPAK (See Fig. 8). In this macro cell one additional input is added, a MODE input. MODE makes it possible to select whether DFF4 will be nSET or nRESET type input.

The nSET/nRESET input functions as nSET if the MODE input is HIGH, and nRESET if MODE input is LOW. Assignment of the nSET/nRESET PIN can be changed dynamically.

Also, the initial state of DFF4 depends on MODE input. The initial state will be HIGH if the MODE input is HIGH, and vice versa.

DFF4 functions a little differently, therefore we will review it in more detail. While the two latches (3-bit LUT4 and 3-bit LUT8) are familiar, the distinctions are in the feedback loop. MODE CELL (3-bit LUT0) controls the feedback.

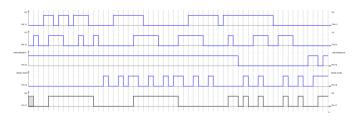

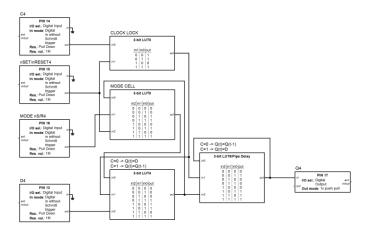

When the nSET/nRESET PIN is HIGH, this cell shorts the feedback of the 3-bit LUT4 cell, and DFF4 functions in normal mode. If nSET/nRESET input is LOW, then the output of MODE CELL is set the same as the logic level on MODE nS/R4 input. Respective with MODE nS/R4 PIN, this action sets or resets the first latch. For the second latch this function is realized differently. When nSET/nRESET input is LOW, the signal from C4 input isn't passed to a CLOCK LOCK cell output, and a HIGH level is set on this output. As a result, on the output of the second latch the same logical level will be set, which is present on the output of the first latch. Such implementation option requires the minimum quantity of circuit resources. The timing diagram (Fig. 9) helps to understand the functionality of DFF4. Functional waveforms for DFF4 are shown in Fig. 10.

DFF2, DFF3 and DFF4 macro cells configuration can be found in Appendix 1.

Figure 8. DFF4 with nSET/nRESET and MODE inputs

Figure 9. DFF4 timing diagram

Figure 10. DFF4 functionality waveforms

# Conclusion

The DFFs presented can be used in designs where additional flip flop cells are required. Flexibility and simplicity of the proposed circuits allow efficient adaptation to specific designs. Also, introduction of a dynamic nRESET/nSET mode circuit provides additional flexibility when using GreenPAK.

Fig. 10. Waveform definition:

- D0 PIN#13 (D4)

- D1 PIN#14 (C4)

- D2 PIN#15 (nSET/nRESET4)

- D3 PIN#16 (MODE nS/R4)

- D4 PIN#17 (Q4)

# GreenPAK Macro Cell Example: Constructing additional DFF types

# **Appendix 1**

Figure 1.1. Block Diagram for Design

### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.