# I/O INTERFACE STANDARDS

## INTRODUCTION:

The vast growth experienced by the communication and semiconductor industry in the past decade was matched with an equal increase in the number interface standards. In the past, there was generally one or maybe two standard interfaces within a system. In today's systems, it is common to see three or more standard interfaces. This trend is driven by several factors: legacy/backwards compatible designs, complexity and size of newer systems, and different requirements for different sections of the system. This application note will provide a summary of the most common interface standards in use today and provide examples of how to correctly implement them.<sup>(1)</sup>

## SINGLE-ENDED INTERFACE STANDARDS

Single-ended interfaces are very common for signaling at less than 300MHz. Their familiarity, ease of design, and ease of use make them highly attractive. Moreover, at lower frequencies, the advantages of a differential interface standard, such as common-mode noise rejection and faster rise/fall time, do not offset the cost of having two pins and two traces per signal.

Single-ended interfaces in use today include:

- LVTTL and LVCMOS (JESD8-5, JESD8-B)

- SSTL (JESD8-8, JESD8-9B, JESD8-15)

- HSTL (JESD8-6)

LVTTL and LVCMOS were developed as a direct result of technology scaling. With each reduction in device geometry, the associated voltage supply has also been reduced in order to maintain the same basic operational characteristics of the transistors. Since the 1980s, this industry has seen a rapid reduction of supply voltage from 1980's  $3.5\mu$  5V technology to today's  $0.13\mu$  1.2V technology. LVTTL and LVCMOS offer manufacturers a migration path as their designs evolve with the technology trend.

LVTTL and LVCMOS buffers are generally simple push-pull designs. One possible implementation is a simple CMOS inverter. The only parameters to meet are VIL/VIH, VOL/VOH and the current drive strengths, which makes this interface standard relatively easy to implement. The input and output specifications are in the following tables. Note that there are several different VDD ranges and different specifications associated with each VDD range. The specifications must be met over the entire range of VDD values for which the parameters apply.

#### NOTE:

1. Refer to the official specification from the appropriate standards bodies for the complete specification.

## INPUT SPECIFICATIONS FOR LVTTL AND LVCMOS

#### For VDD = 3V to 3.6V

| Symbol | Parameter                | Min  | Max       | Unit |

|--------|--------------------------|------|-----------|------|

| Vih    | High Level Input Voltage | 2    | Vdd + 0.3 | V    |

| Vil    | Low Level Input Voltage  | -0.3 | 0.8       | V    |

| lin    | Input Current            |      | ±5        | mA   |

#### For VDD = 2.3V to 2.7V

| Symbol | Parameter                | Min  | Max       | Unit |

|--------|--------------------------|------|-----------|------|

| Vih    | High Level Input Voltage | 1.7  | Vdd + 0.3 | V    |

| Vil    | Low Level Input Voltage  | -0.3 | 0.7       | V    |

| lin    | Input Current            |      | ±15       | mA   |

#### For VDD = 1.8V to 2.7V

| Symbol | Parameter                | Min    | Max       | Unit |

|--------|--------------------------|--------|-----------|------|

| Vih    | High Level Input Voltage | 0.7Vdd | Vdd + 0.3 | V    |

| Vil    | Low Level Input Voltage  | -0.3   | 0.2Vdd    | V    |

| lin    | Input Current            |        | ±15       | mA   |

# OUTPUT SPECIFICATIONS FOR LVTTL AND LVCMOS

#### LVTTL : VDD = 3V to 3.6V

| Symbol | Parameter                 | Test Condition | Min | Max | Unit |

|--------|---------------------------|----------------|-----|-----|------|

| Vон    | High Level Output Voltage | Іон = -2mA     | 2.4 |     | V    |

| Vol    | Low Level Output Voltage  | Iон = 2mA      |     | 0.4 | V    |

#### LVCMOS : $V_{DD} = 3.0V$ to 3.6V

| Symbol | Parameter                 | Test Condition | Min       | Max | Unit |

|--------|---------------------------|----------------|-----------|-----|------|

| Vон    | High Level Output Voltage | Іон = -100μА   | Vdd - 0.2 |     | V    |

| Vol    | Low Level Output Voltage  | Іон = 100μА    |           | 0.2 | V    |

#### LVTTL / LVCMOS : VDD = 2.3V to 2.7V

| Symbol | Parameter                 | Test Condition | Min | Max | Unit |

|--------|---------------------------|----------------|-----|-----|------|

|        |                           | Іон = -100μА   | 2.1 |     |      |

| Vон    | High Level Output Voltage | Iон = -1mA     | 2   |     | V    |

|        |                           | Іон = -2mA     | 1.7 |     |      |

|        |                           | Іон = 100μА    |     | 0.2 |      |

| Vol    | Low Level Output Voltage  | Iон = 1mA      |     | 0.4 | V    |

|        |                           | Iон = 2mA      |     | 0.7 |      |

#### LVTTL / LVCMOS : VDD = 1.8V to 2.7V

| Symbol | Parameter                 | <b>Test Condition</b> | Min       | Max | Unit |

|--------|---------------------------|-----------------------|-----------|-----|------|

| Vон    | High Level Output Voltage | Іон = -100μА          | Vdd - 0.2 |     | V    |

| Vol    | Low Level Output Voltage  | Іон = 100μА           |           | 0.2 | V    |

Stub Series Terminated Logic (SSTL) comes in three different flavors: SSTL\_18, SSTL\_2, and SSTL\_3. The three flavors were created to address the process technology trends. The SSTL family differs from the LVTTL and LVCMOS family in one very important aspect. SSTL assumes that transmission line termination is required. As such, SSTL has specifications for output impedance and different methods of termination. This difference is important for high-speed signaling because a properly terminated transmission line reduces reflections, reduces EMI emissions, improves settling time, and improves timing margins. LVTTL and LVCMOS signaling can also be terminated. However, because this assumption is not explicit in the specification, the user needs to be careful of the impact the termination resistors have on signal swing.

The design of the SSTL driver is not so much different than that of the LVTTL driver. A very typical implementation is a CMOS inverter. However, the design of the input buffer is vastly different.

The LVTTL input buffer is generally a CMOS inverter. This is an excellent implementation because of its simplicity and near zero-DC power consumption. However, it suffers from poor matching between the NMOS and PMOS transistors over voltage, temperature, and process. Because of this uncertainty in its threshold voltage and its poor voltage gain, this type of buffers requires a higher voltage swing to ensure reliable switching.

The SSTL input buffer is generally a differential pair. The differential pair offers better voltage gain and bandwidth and smaller variations in the threshold voltage. This makes reliable performance possible with small voltage swings. Figure 1 shows a general implementation of a LVTTL I/O versus an SSTL I/O.

The SSTL standard is rather involved and sophisticated. It would be cumbersome to try to replicate the specification in this short application note. The SSTL tables on the following page show the supply and input specifications. Note that SSTL has different output specifications for different classes of drivers. SSTL\_3 and SSTL\_2 define two classes of drivers that are targeted at different termination schemes. SSTL\_18 does not have explicit definitions of classes. However, depending on the termination environment, the driver must be able to produce the appropriate voltage swing at the input buffer. The user is advised to consult the JEDEC publication for a complete discussion of this standard.

The AC parameters refer to the threshold voltage at which the receiver must change state when the signal crosses that voltage. The receiver will maintain the new logic state as long as the voltage stays beyond the DC parameters. The motivation for this distinction is to accommodate ringing in the system and still maintain predictable performance. This problem is common in memory subsystems.

High-Speed Transceiver Logic (HSTL) is yet another standard that was developed to address the process technology trend. HSTL is meant to be voltage scalable and technology independent. Like SSTL, HSTL uses differential amplifiers for the input. Similar to SSTL, HSTL calls out a specification for the output supply voltage and the device supply voltage and allowing those two voltages to be different. (Chronologically, HSTL proceeds SSTL by about a year.) A summary of the supply voltage and input specifications are in the following tables.

OUT

OUT

VREE

LVTTL STTL VDDQ = 3.3VVDDQ = 2.5VOUT Vssq Vsso **OUTPUT BUFFER** OUTPUT BUFFER VDD = 3.3V VDD = 2.5V OUT IN Vss Vss INPUT RECIEVER INPUT RECIEVER

Figure 1 : I/O Implementation Examples

# SSTL SUPPLY VOLTAGE LEVELS

#### SSTL\_3

| Symbol        | Parameter                          | Min         | Тур               | Max        | Unit      |

|---------------|------------------------------------|-------------|-------------------|------------|-----------|

| Vdd           | Device Supply Voltage              | Vddq        |                   | N/A        | V         |

| Vddq          | Output Supply Voltage              | 3           | 3.3               | 3.6        | V         |

| Vref          | Input Reference Voltage            | 1.3         | 1.5               | 1.7        | V         |

| Vtt           | Termination Voltage                | Vref-0.05   | Vref              | Vref+0.05  | V         |

| SSTL_2        |                                    |             |                   |            |           |

|               |                                    |             |                   |            |           |

| Symbol        | Parameter                          | Min         | Тур               | Max        | Unit      |

| Symbol<br>Vdd | Parameter<br>Device Supply Voltage | Min<br>Vddq | Тур               | Max<br>N/A | Unit<br>V |

| <u> </u>      |                                    |             | <b>Тур</b><br>2.5 |            |           |

| Vdd           | Device Supply Voltage              | VDDQ        |                   | N/A        | V         |

#### SSTL\_18

| Symbol | Parameter               | Min     | Тур  | Max     | Unit |

|--------|-------------------------|---------|------|---------|------|

| Vddq   | Output Supply Voltage   | 1.7     | 1.8  | 1.9     | V    |

| VREF   | Input Reference Voltage | 833     | 900  | 969     | mV   |

| Vtt    | Termination Voltage     | Vref-40 | Vref | Vref+40 | mV   |

# SSTL INPUT SPECIFICATION

#### SSTL\_3

| Symbol  | Parameter     | Min         | Max         | Unit |

|---------|---------------|-------------|-------------|------|

| Vıн(dc) | DC Input HIGH | Vref + 0.2  | VDDQ + 0.3  | V    |

| Vı∟(dc) | DC Input LOW  | -0.3        | Vref - 0.2  | V    |

| Vin(ac) | AC Input HIGH | Vref + 0.4  |             | V    |

| V⊫(ac)  | AC Input LOW  |             | Vref – 0.4  | V    |

| SSTL_2  |               |             |             |      |

| Symbol  | Parameter     | Min         | Max         | Unit |

| Vıн(dc) | DC Input HIGH | Vref + 0.15 | VDDQ + 0.3  | V    |

| V⊩(dc)  | DC Input LOW  | -0.3        | Vref - 0.15 | V    |

| Vin(ac) | AC Input HIGH | Vref + 0.31 |             | V    |

| V⊫(ac)  | AC Input LOW  |             | Vref – 0.31 | V    |

### SSTL\_18

| Symbol  | Parameter     | Min        | Max        | Unit |

|---------|---------------|------------|------------|------|

| Vін(dc) | DC Input HIGH | Vref + 125 | VDDQ + 300 | mV   |

| Vı∟(dc) | DC Input LOW  | -300       | Vref - 125 | mV   |

| Vin(ac) | AC Input HIGH | Vref + 250 |            | mV   |

| V⊫(ac)  | AC Input LOW  |            | Vref – 250 | mV   |

## HSTL SUPPLY VOLTAGE LEVELS

| Symbol | Parameter               | Min  | Тур  | Мах | Unit |

|--------|-------------------------|------|------|-----|------|

| Vdd    | Device Supply Voltage   | N/A  |      | N/A | V    |

| Vddq   | Output Supply Voltage   | 1.4  | 1.5  | 1.6 | V    |

| Vref   | Input Reference Voltage | 0.68 | 0.75 | 0.9 | V    |

# HSTL SINGLE-ENDED INPUT SPECIFICATION

| Symbol  | Parameter     | Min        | Max        | Unit |

|---------|---------------|------------|------------|------|

| ViH(dc) | DC Input HIGH | Vref + 0.1 | VDDQ + 0.3 | V    |

| Vı∟(dc) | DC Input LOW  | -0.3       | Vref - 0.1 | V    |

| Vin(ac) | AC Input HIGH | Vref + 0.2 |            | V    |

| V⊫(ac)  | AC Input LOW  |            | Vref – 0.2 | V    |

### DIFFERENTIAL SIGNALING INTERFACE STANDARDS

Several of the advantages to differential amplifiers have already been mentioned. The differential amplifier offers better voltage gain and bandwidth and smaller variations in the threshold voltage. This makes reliable performance possible with small voltage swings. The low voltage swing enables higher signaling rates. In addition, differential amplifiers only operate on the difference between the true and complement signals. Any signal that is common to the true and complement signals, such as noise, is rejected; this is called common-mode rejection. Thus, differential signaling offers better noise immunity. This is in contrast to single-ended signals that operate on absolute voltage levels. There are additional system level benefits to differential signaling, such as zero return current and minimal self-induced supply noise.

The two major disadvantages of differential signaling are the increase in pin and trace count and the need to match the true and complement traces on the PCB. It is interesting to note that the increase in pin and trace count is not 2 to 1 versus high-performance single-ended signaling because single-ended signaling requires a signal return for every 2-4 signal lines. The ratio is closer to 1.3 to 1.8. Differential signaling "standards" in use today include current-mode logic (CML), positive-emitter coupled logic (PECL), low-voltage PECL (LVPECL), and low-voltage differential signaling (LVDS). Of these, only LVDS is a true standard – TIA/EIA-644. CML is a generic term used to refer to signaling that is based on a simple differential amplifier. PECL was developed by Motorola as a modification of their ECL (emitter-coupled logic) products. Efforts to standardize PECL were not fruitful. LVPECL was developed as a direct result of process technology and voltage scaling. It's important to note that because there is no formal standard for these three interfaces, interoperability should not be expected to be automatic. The user must ensure that the relevant parameters of the I/O buffers meet the requirements for interoperability.

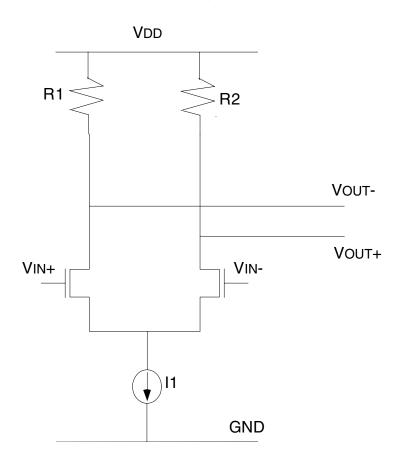

CML input and output buffers are based on the differential amplifier (see figure 2). In the case of an output buffer, the goal is to steer the flow of current, I1, through either the R1 or R2. Suppose the voltage at VIN+ is higher than the voltage at VIN- such that all the current, I1, is steered to flow through R1. The voltage at VOUT- is then VDD- (I1 \* R1). The voltage at VOUT+ is VDD, since no current flows through R2. If the voltage at VIN- is higher than the voltage at VIN+, then all the current flows through R2, resulting in VOUT+ = VDD- (I1 \* R2) and VOUT- = VDD.

Generally, R1 is the same value as R2. To match the characteristic impedance of a  $50\Omega$  transmission line, R1 and R2 are generally set at  $50\Omega$ . The peak-to-peak differential voltage swing is then | Vout+ - Vout-|=11 \* R1.

Different vendors will use a different value for 11, and thus the voltage swing may vary from one vendor to another. Though the resistors can also differ between vendors, it's unlikely in high-performance and high-speed devices. Another factor is the common-mode voltage. This is important if DC-coupling is the desired method of connecting to a receiver; DC-coupling reduces component count and cost. In this case, the user must ensure that the common-mode voltage at the output matches the common-mode voltage expected by the receiver. Common-mode voltage is not a problem if AC-coupling is used.

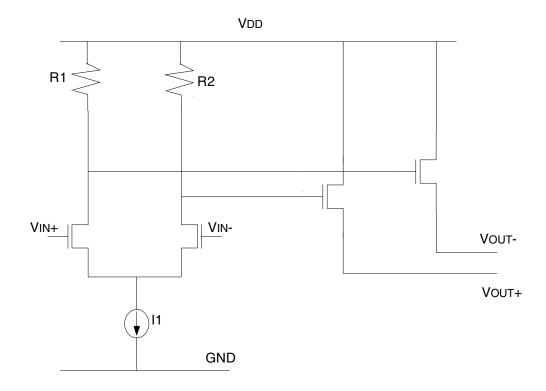

PECL input buffers are generally simple differential amplifiers as is the case with CML input buffers. PECL output buffers are differential amplifiers followed by a common-source amplifier. The output is open-source, as shown in figure 3. The user needs to add external resistors to ground to complete the circuit. Just like CML, the output voltage swing of PECL and LVPECL drivers vary from vendor to vendor. It depends not only on the value of the external resistors, but also on the gate voltages of the common-source amplifiers. And like CML, PECL and LVPECL need the same consideration regarding the common-mode voltage, voltage swing, and interoperability. The difference between CML and PECL (and LVPECL) drivers, namely the addition of the common-source amplifiers in PECL drivers, gives PECL a slight advantage in certain applications. Common-source amplifiers are excellent drivers because they have low output impedance; this allows them to drive heavier loads. The use of the external resistor, which may or may not be advantageous, gives the user a certain amount of control over output swing, power consumption, and termination scheme.

Figure 3 : PECL Output Buffer

#### I/OINTERFACESTANDARDS

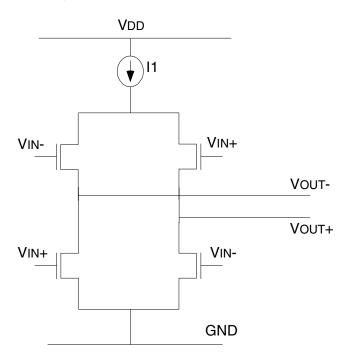

LVDS input buffers are generally simple differential amplifiers. The output buffer is an H-bridge design vastly different than CML or PECL (see figure 4). Current is steered through one of the transistors on the top into the load and back through the transistor on the bottom. The load is generally a 100 $\Omega$  termination resistor placed across VouT+ and VouT-; note that the load is an essential part of this circuit. A voltage is developed across the load and this is sensed by the input buffer.

Figure 4 : LVDS Output Buffer

LVDS is an official standard and as such, there are strict specifications on the various parameters that are important for interoperability. The next LVDS table gives a brief summary of the critical parameters. Note that LVDS outputs can be DC-coupled to LVDS inputs because of the tight control over commonmode voltage. The elimination of the external AC-coupling capacitor will become more and more critical as the number of I/Os continue to increase, the pitch of package pins continue to decrease, and PCB real estate becomes even more of a premium.

## SUMMARY OF LVDS PARAMETERS

| Symbol        | Parameter                     | Min   | Max   | Unit |

|---------------|-------------------------------|-------|-------|------|

| Vod           | Differential Output Voltage   | 247   | 454   | mV   |

| Vos           | Offset or Common-Mode Voltage | 1.125 | 1.375 | V    |

| $\Delta V$ od | Change of Vob                 |       | 50    | mV   |

| ΔVos          | Change of Vos                 |       | 50    | mV   |

| Vтн           | Threshold Voltage             |       | ±100  | mV   |

| Vin           | Input Voltage Range           | 0     | 2.4   | V    |

# EXAMPLES OF INTERFACING DIFFERENT STANDARDS

With system complexity growing, having two, three, or even four interface standards on a single board is not uncommon. This section will show some examples of how to connect output buffers of one standard to input buffers of another standard.

A common question is interoperability between standards from the same family. For example, can a SSTL\_2 driver be connected to a SSTL\_18 receiver? What about a SSTL\_3 driver driving a SSTL\_18 receiver? The AC voltage swings are obviously not a problem when moving from the 3.3V or 2.5V SSTL family to the 1.8V family, assuming the VREF and VTT levels are adjusted accordingly. The potential problem is with the DC voltage, in particular, the maximum VIH.

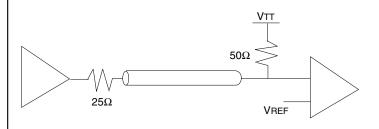

Figure 5 : Typical SSTL Class I Environment

Figure 5 shows a typical SSTL Class I environment. The maximum VIH for all three families is VDDQ + 300mV. For SSTL\_18, the worst case value is VDDQ(min) + 300mV = 2V. SSTL receivers are high-impedance, so all of the current will go to and come from VTT. For SSTL\_18, the VTT(max) = 969mV + 40mV = 1.009V. If there is 1V across the 50 $\Omega$  resistor, then the VIH specification will be violated. This would require the driver to source 20mA, which is a definite possibility. Typical SSTL drivers will deliver 8-10mA, which would suggest that SSTL\_2 and SSTL\_3 drivers can drive SSTL\_18 receivers.

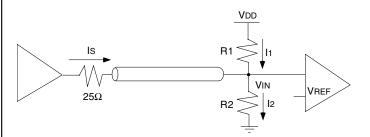

What if the driver is able to source and sink more than 20mA? In this case, the termination scheme must be changed (see figure 6). The values of R1 and R2 must be found such that V<sub>IN</sub> never exceeds 2V (for SSTL\_18). A quick application of Kirchoff's current will yield the correct results. This is for a logic high. In general, the user should always double check the conditions for a logic low and ensure that those are within specification for the given resistor values.

Figure 6 : Alternative Termination for SSTL

The problem with this method of choosing the resistor values is that the signal might not swing symmetrically around VREF. For example, if Is = 25mA, VDD = 3.3V, and VIN is limited to a maximum of 2V, then R1 and R2 are  $217\Omega$  and  $65\Omega$ , respectively. The relevant equations are:

$$\frac{V_{DD} - V_{IN}(MAX)}{R1} + I_{S} = \frac{V_{IN}(MAX)}{R2}$$

R1 || R2 =  $50\Omega$

The signal at VIN would swing from 0V to 2V. Noise margin is sacrificed if VREF is set to 0.9V (for SSTL\_18). Moreover, duty-cycle distortion might also be induced because of the offset in VREF from symmetry. The user must make these considerations and make the appropriate calculations based on the exact termination scheme and the capabilities of the driver and receiver in order to ensure bulletproof interoperability.

The above discussion can more generally be applied to interfacing singleended drivers to receivers that are based on differential amplifiers. One side of the receiver should be tied to some VREF and the other side should be connected to the single-ended driver. Some examples are:

- LVTTL  $\rightarrow$  SSTL/HSTL

- LVTTL → LVPECL/CML

- LVTTL  $\rightarrow$  LVDS

- SSTL/HSTL → LVPECL/CML

- SSTL/HSTL  $\rightarrow$  LVDS

The critical factors to keep in mind are:

- 1. Set the VREF level to maximize system margins.

- Double-check that the selected VREF is a valid common-mode level for the receiver.

- Double-check that the maximum voltage specifications of the receiver are not violated if interfacing between I/Os with different power supply voltages.

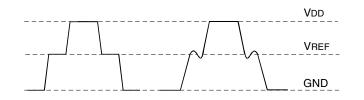

Interfacing singled-ended drivers to differential receivers should be done with care. Differential receivers are extremely sensitive. They might take as little as ±100mV or less to distinguish between a logic high and a logic low. The singled-ended signals, ideally, should be strictly monotonic within several hundred milli-volts of the selected VREF. Waveforms such as those in figure 7 would cause unreliable performance whereas they would be no problem for single-ended receivers.

Figure 7 : Waveform Examples

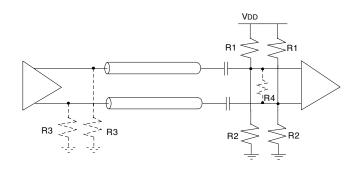

The most common way to interface between the differential signaling standards is AC-coupling. The issue of common-mode voltage is eliminated, but the issue of the maximum voltage remains. The maximum voltage specification is potentially an issue when interfacing between I/Os with different power supply voltages. This is a moot issue if both I/Os use the same power supply voltage; this is also true with singled-ended signaling. AC-coupling also offers the advantage that ground drops will not cause system margins to be lost. Figure 8 shows a typical example. The common-mode voltage can be set at any arbitrary value that's appropriate for the receiver. The resistors can be chosen to correctly terminate the transmission line. If the receiver is internally biased, then it's not necessary to have the resistors R1 and R2. Correct termination is still required and can be provided by R4. In the case of PECL and LVPECL, the DC path to ground is provided by resistors R3.

Figure 8 : Example of AC-Coupling

#### I/OINTERFACESTANDARDS

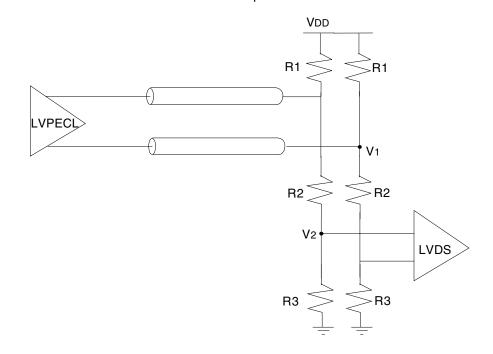

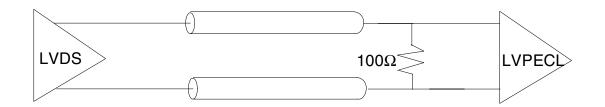

Just as with single-ended signaling, DC-coupling is also possible with differential signaling. Figure 9 shows one example of connecting an LVPECL driver to an LVDS receiver. R1, R2, and R3 must be chosen to satisfy the following conditions:

- 1. R1 || (R2 + R3) must match the characteristic impedance of the transmission line.

- 2. The voltage at V1 should be VDD 2V. This is generally the termination voltage for LVPECL.

- 3. The voltage at V2 should be 1.2V or some other acceptable commonmode voltage for the LVDS receiver.

Incidentally, DC-coupling LVDS to LVPECL is a straight forward procedure (see figure 10). The common-mode voltage of LVDS is 1.2V. LVPECL receivers generally have a relatively wide common-mode range and can accept the 1.2V without problems; the user should nevertheless check the specifications.

Figure 9 : LVPECL DC-Coupled to LVDS

Figure 10 : LVDS DC-Coupled to LVPECL

## ADDENDUM

There are some instances where it's necessary to perform true signal translation rather than merely trying to use external passive components to perform level shifting. Examples include:

- To perform single-ended to differential conversion for better noise immunity and better performance driving long traces such as on the backplane.

- To perform differential to single-ended conversion to drive single-ended receivers.

- To increase voltage swing to drive receivers that require a larger swing. (For example, 1.8V LVTTL cannot drive 2.5V LVTTL without a conversion.)

- To interface to receivers where a solution with external passive components is not feasible or desirable.

In many cases, this signal translation can be performed at the same time as some other useful functions. IDT offers a full portfolio of devices that are capable of signal translation. The following table shows a short list of some of these parts.

| Part Number         | Description         | Input Interface                        | Output Interface |

|---------------------|---------------------|----------------------------------------|------------------|

| 5T915, 5T905, 5T907 | Fanout Buffer       | 2.5V/1.8V LVTTL,                       | 1.8V/2.5V LVTTL, |

|                     |                     | 1.5V/1.8V HSTL,                        | 1.8V/1.5V HSTL   |

|                     |                     | 2.5V PECL                              |                  |

| 5T93xx              | Fanout Buffer       | 1.8V/1.5V HSTL,                        | LVDS             |

|                     |                     | 2.5V/3.3V LVPECL,                      |                  |

|                     |                     | CML, LVDS                              |                  |

| 85304               | Fanout Buffer       | LVPECL, LVDS, LVTTL,                   | LVPECL           |

|                     |                     | LVHSTL, SSTL, HCSL, CML                |                  |

| 5T2110, 5T2010      | Zero-Delay Buffer   | Differential                           | 1.8V/1.5V HSTL,  |

|                     |                     | 1.8V/1.5V HSTL, 1.8/2.5 LVTTL,         | 1.8V/2.5V LVTTL  |

|                     |                     | LVPECL or single-ended 1.8V/2.5V LVTTL |                  |

| 5T94x               | Precision Generator | 1.8V/1.5V HSTL,                        | LVPEC, LVDS      |

|                     |                     | SSTL, LVTTL, LVPECL, LVDS              |                  |

| 5T9010              | Programmable Skew   | Differential                           | 1.8V/1.5V HSTL,  |

|                     |                     | 1.8V/1.5V HSTL, 1.8/2.5 LVTTL,         | 1.8V/2.5VLVTTL   |

|                     |                     | LVPECL or single-ended 1.8V/2.5V LVTTL |                  |

|                     |                     |                                        |                  |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.