# IDT's PCIe® Gen2 Switch Family Non-Transparent Operations

# Application Note AN-707

#### **Notes**

#### **Overview**

The IDT family of Gen2 PCI Express® switches are designed for high-performance applications, supporting multiple simultaneous peer-to-peer traffic flows. Target applications include multi-host or intelligent I/O based systems where inter-domain communication is required, such as servers, storage, communications, and embedded systems.

This application note discusses the non-transparent bridging (NTB) feature of these switches.

# **Switch Partitioning**

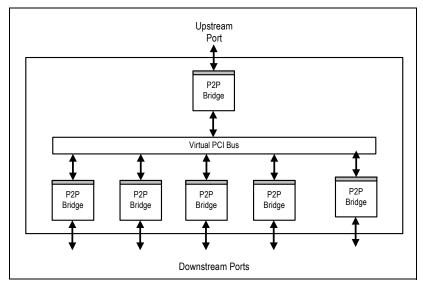

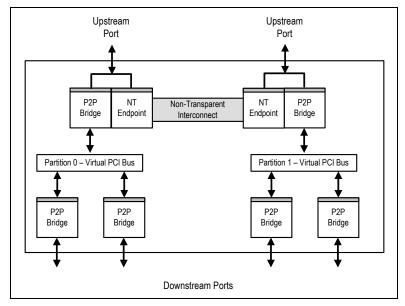

The logical view of a PCI Express switch is shown in Figure 1. A PCI Express switch contains one upstream port and one or more downstream ports. Each port is associated with a PCI-to-PCI (P2P) bridge. All PCI-to-PCI bridges associated with a PCI Express switch are interconnected by a virtual PCI bus.

The primary side of the upstream port's PCI-to-PCI bridge is associated with the external link, while the secondary side connects to the virtual PCI bus. The primary side of a downstream port's PCI-to-PCI bridge is connected to the virtual PCI bus, while the secondary side is associated with the external link.

Figure 1 Transparent PCI Express Switch

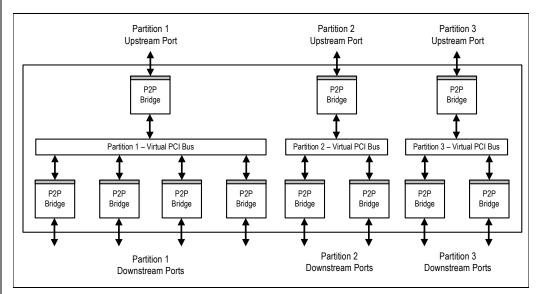

The switch is a *partitionable* PCI Express switch. This means that in addition to operating as a standard PCI Express switch, the switch ports may be partitioned into groups that logically operate as completely independent PCI Express switches. Figure 2 illustrates a three partition configuration.

Figure 2 Example of Switch Partitioning

Each partition operates logically as a completely independent PCI Express switch that implements the behavior and capabilities outlined in the PCI Express Base specification required of a switch.

The switch supports boot-time (i.e., Fundamental Reset) and runtime configuration of ports into partitions. Boot time configuration may be performed via serial EEPROM, external SMBus master, or software executing on a root port (e.g., BIOS, OS, driver or hypervisor). Runtime reconfiguration allows the number of active partitions in the device and assignment of ports to partitions to be modified while the system is active. Runtime reconfiguration does not affect partitions whose configuration is not modified.

The PCI Express architectural model is one in which a root, typically the main CPU, is responsible for configuring a tree of endpoints (i.e., a hierarchy of virtual PCI buses). Once configured, any endpoint or root may initiate transactions. The root and endpoints share a common address space with routing configured in PCI-PCI bridges.

A limitation of the PCI Express architectural model is that it allows only a single root and that the root and all of the endpoints must share a common address space. This limitation may be overcome through the use of a *non-transparent bridge (NTB)*. A non-transparent bridge allows two roots or PCI Express trees (i.e., hierarchies) to be interconnected with one or more shared address windows between them.

The switch supports eight non-transparent functions (a.k.a., NT functions or NT endpoints). Each NT function appears as a PCI Express endpoint in the PCI Express hierarchy. The NT function is located in a partition's upstream port. In each partition, the operating mode of the switch's upstream port determines if this port contains an NT function. A port configured to operate in one of the following modes contains an NT function:

- NT function

- NT with DMA function

- Upstream switch port with NT function

- Upstream switch port with NT and DMA functions

# **Non-Transparent Operation**

The PCI architecture defines a hierarchy of buses interconnected by PCI-to-PCI bridges. This hierarchy forms a tree and is referred to as a PCI domain.

- A PCI domain consists of a single memory address space, I/O address space, and ID address space.

- The PCI ID consists of a bus, device and function number that uniquely defines an element in the domain.

Although PCI Express switches support direct transfers between ports, the logical view seen by software remains that of a hierarchy of buses as defined by the PCI architecture and illustrated in Figure 1. The portion of a PCI domain emanating from a PCI Express root port is referred to as the PCI Express domain.

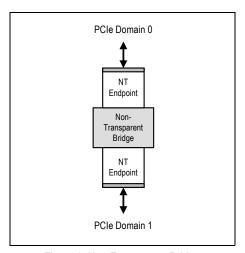

In many applications a need exists to interconnect two independent PCI domains. A Non-Transparent Bridge (NTB) enables this inter-domain communications. The architecture of an NTB is illustrated in Figure 3.

Figure 3 Non-Transparent Bridge

An NTB consists of two PCI functions each defined by a Type 0 PCI header that are interconnected by a bridging function. The two Type 0 PCI functions are referred two as Non-Transparent (NT) endpoints. Each function advertises one or more memory windows using PCI Base Address Registers (BARs). Software executing on each hierarchy allocates PCI memory space to the BAR.

Memory operations that target a memory window defined by an NT endpoint are routed within the domain to that endpoint. When the non-transparent bridge receives a memory operation that targets a BAR used for mapping through the bridge, it translates the address of the transaction to a new address in the opposite domain and forwards the transaction to the other domain. Completions are handled in a similar manner.

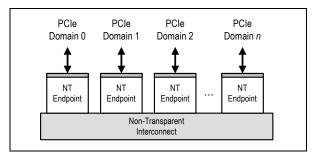

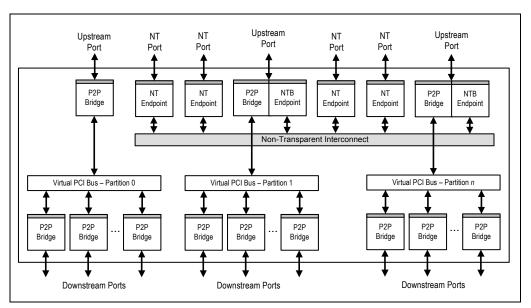

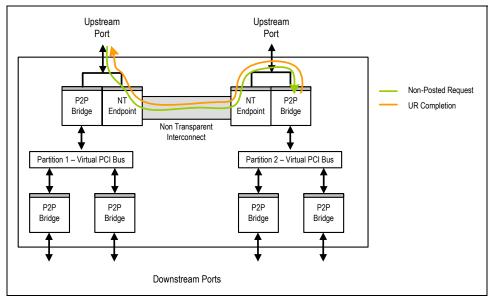

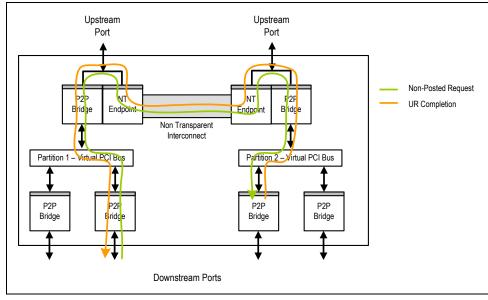

As shown in Figure 4, the switch allows two or more non-transparent endpoints to directly communicate over a *non-transparent interconnect*. This extension of non-transparent bridging from two-ports to multiple ports parallels the evolution of two-port PCI bridges to multi-port PCI Express switches.

Figure 4 Generalized Multi-Port Non-Transparent Interconnect

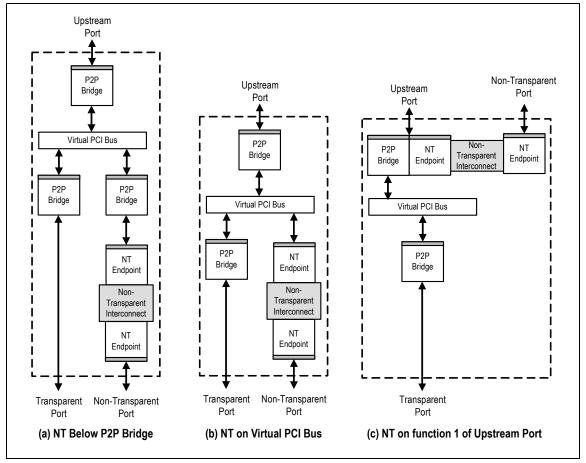

There are numerous approaches for integrating a non-transparent bridge into a PCI Express switch. Figure 5 illustrates three approaches.

#### **IDT** Application Note AN-707

Figure 5(a) shows an architecture in which a non-transparent bridge is integrated below the PCI-to-PCI bridge associated with a downstream port. This architecture is used in IDT Gen 1 switches. A disadvantage of this approach is that it leads to complex implementations when extended to direct non-transparent switching.

Figure 5(b) illustrates an architecture in which a non-transparent bridge is integrated directly onto the virtual PCI bus. The advantage of this approach is that it is simple to implement since the PCI-to-PCI bridge associated with a downstream port may be replaced (or reconfigured) with a non-transparent bridge. The issue with this approach is that it violates the fundamental requirement outlined in the PCI Express base specification that endpoints (represented by type 0h headers) must not appear to configuration software on a switch's internal bus as peers of the virtual PCI-to-PCI bridges representing the switch downstream ports.

Figure 5(c) exhibits the architecture used in the switch. In this architecture, the upstream port is transformed into a multi-function device with function 0 representing the PCI-to-PCI bridge associated with the upstream port, and function 1 representing the NT endpoint.

Figure 5 Architectural Approaches for Integrating Non-Transparency into a PCI Express Switch

A switch port may be configured to operate in one of seven major modes.

- Upstream switch port (i.e., upstream PCI-to-PCI bridge)

- Downstream switch port (i.e., downstream PCI-to-PCI bridge)

- Upstream switch port with DMA function

- Upstream switch port with NT function

- Upstream switch port with NT and DMA functions

- NT function

- NT with DMA function

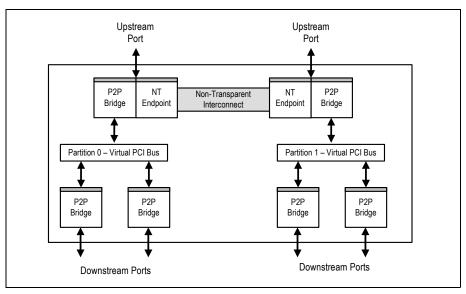

Figure 6 illustrates a basic non-transparent switch configuration. In this configuration, the ports are split into two partitions. Each partition represents a three-port transparent PCI Express switch. The upstream port of each partition is configured to operate as an *upstream switch port with NT endpoint*.

This configuration allows direct partition to partition communications without consuming external switch ports or links.

The NT endpoints in Figure 6 communicate using the non-transparent interconnect. This allows PCI Express functions in either domain to communicate using the address windows presented by the NT endpoint BARs.

Functions may be connected to the upstream port (e.g., the root) or to a downstream switch port. Upstream port TLPs flow directly to the corresponding NT endpoint. Downstream switch port TLPs flow through the corresponding three-port transparent switch and then back to the NT endpoint via the upstream port.

TLPs flowing from the secondary side of an upstream port's PCI-to-PCI bridge, through the bridge, to the NT endpoint stay entirely within the switch and are not transmitted on the upstream port's link.

Figure 6 Non-Transparent Switch with Non-Transparency Between Partitions

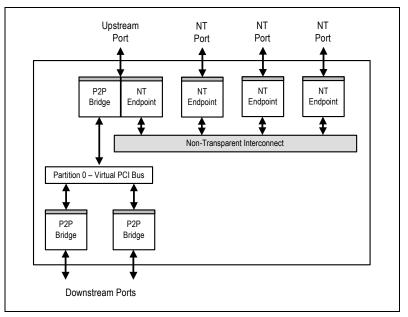

Figure 7 illustrates a basic non-transparent configuration with NT ports for the switch. In this configuration, the ports are split into four partitions. The first partition, partition 0, represents a three-port transparent PCI Express switch. The remaining three partitions consist of the three NT endpoints 1. Requesters in any of the NT domains may communicate using the address windows presented by the NT endpoint BARs.

5 of 44

<sup>1.</sup> A port configured as an NT port logically consists of only an NT endpoint and represents a switch partition.

Figure 7 Non-Transparent Switch with Non-Transparent Ports Example # 1

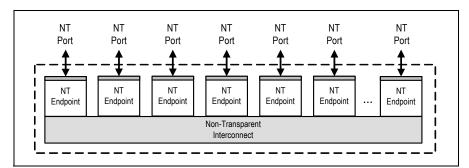

Figure 8 illustrates the configuration in which all ports are configured as NT endpoints. Such a configuration may be useful in bladed systems.

Figure 8 Non-Transparent Switch with Non-Transparent Ports Example # 2

This section outlined several possible switch NTB configurations. The ability to configure ports to operate in a variety of modes together with support for up to 16 partitions provides the switch with the flexibility required for a wide variety of system applications. Figure 9 illustrates a configuration with three transparent switch partitions and four NT port partitions. Non-transparent communication is supported between all partitions except partition zero.

Figure 9 Non-Transparent Switch with Non-Transparent Ports Example # 3

# **Base Address Registers (BARs)**

Each NT-endpoint implements six Base Address Registers (BARs) labeled BAR 0 through BAR 5. Table 1 summarizes supported BAR configurations. All BARs may be configured to create 32-bit memory 1 windows between the PCI Express domain and the non-transparent interconnect.

- All BARs support direct address translation

- BAR 2 (or BAR 2/3 in 64-bit mode) supports direct address translation or lookup address translation

- BAR 4 (or BAR 4/5 in 64-bit mode) supports direct address translation or lookup address translation

Even and odd BARs may be paired to form 64-bit prefetchable memory space. The 4 KB configuration space associated with the NT endpoint may be mapped into 32-bit memory using BAR 0. BAR 0 and BAR 1 may be paired to map the 4 KB configuration space associated with the NT endpoint into 64-bit memory.

| BAR   | Description                                                                                                                                                                                                                                   |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BAR 0 | 32-bit BAR that maps 4 KB NT-endpoint configuration registers Lower half of 64-bit BAR that maps 4 KB NT-endpoint configuration registers 32-bit BAR with direct address translation Lower half of 64-bit BAR with direct address translation |  |  |  |  |  |

| BAR 1 | Upper half of 64-bit BAR that maps 4 KB NT-endpoint configuration registers 32-bit BAR with direct address translation Upper half of 64-bit BAR with direct address translation                                                               |  |  |  |  |  |

| BAR 2 | 32-bit BAR with direct or lookup table address translation Lower half of 64-bit BAR with direct or lookup address translation                                                                                                                 |  |  |  |  |  |

Table 1 NT Endpoint BARs (Page 1 of 2)

<sup>1.</sup> The NT function's BARs do not support I/O space.

| BAR   | Description                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| BAR 3 | 32-bit BAR with direct address translation Upper half of 64-bit BAR with direct or lookup table address translation                 |

| BAR 4 | 32-bit BAR with direct or lookup table address translation Lower half of 64-bit BAR with direct or lookup table address translation |

| BAR 5 | 32-bit BAR with direct address translation Upper half of 64-bit BAR with direct or lookup table address translation                 |

Table 1 NT Endpoint BARs (Page 2 of 2)

Each BAR has a corresponding setup register. For example, BAR 0 (BAR0) has an associated BAR Setup 0 (BARSETUP0) register. BAR setup registers allow a BAR to be enabled or disabled, control the operating mode of the BAR as well as advertised capabilities (e.g., size of the BAR window), and if applicable, control the address translation mechanism.

When an even BAR is configured for 64-bit operation, the odd BAR takes on the function of the upper 32-bits of the BADDR field of the even BAR. When an even and odd BAR are merged for 64-bit operation, the fields of the odd BAR Setup register remain read-write but have no functional effect on the operation of the device.

#### **BAR Limit**

Base Address Registers are used by a function to specify the amount of memory space required by the function. Software configures read-write BAR register bits with the base address of the allocated memory range.

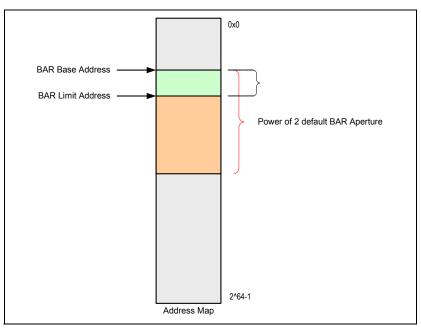

Since BARs specify the size of an aperture with read-only bits in the BADDR field, the PCI architecture only allows apertures to be requested that are a power of two in size. In many applications, it is desirable to allocate smaller apertures.

Associated with each BAR is a BAR Limit Address (BARLIMITx) register. The limit address specified by this register allows arbitrary control of the aperture size associated with a BAR. Using this capability, the *effective aperture size* may be set arbitrarily to any value, in 1 KB multiples, up to the power of two aperture size requested by the BAR.

- The lower 10-bits of the BARLIMITx register are reserved and <u>assumed to be all ones by the hard-ware</u>. Thus, the BAR limit address may be anywhere in the range from 0x3FF (i.e., 1KB) to the highest possible memory address.

- Setting the address limit of a BAR to a value less than the BAR base address effectively disables the BAR. The effective aperture size in this case is zero.

- Setting the address limit of a BAR to a value between the BAR base address and the BAR base address plus the power of two aperture size requested by the BAR sets the effective aperture to be from the BAR base address up to and including the BAR limit address.

- Setting the address limit of a BAR to a value greater than the BAR base address plus the power

of two aperture size requested by the BAR disables the limit capability. The aperture and effective

aperture in this case are both equal to the power of two size requested by the BAR.

- The default value of the BARLIMITx register causes the BAR limit address to point to the highest possible address, in effect disabling the effect of the BARLIMIT register.

- The BARLIMIT0 register is ignored when BAR 0 is mapped to the NT endpoint's configuration space.

When an even BAR is configured for 64-bit operation, the odd BAR takes on the function of the upper 32-bits of the BADDR field of the even BAR. In this mode, the odd BARLIMITx register acts as the upper 32-bits of the LADDR field associated with the even BAR. Figure 10 graphically illustrates the operation of the BAR limit address.

Figure 10 BAR Limit Operation

A received TLP whose address does not fall within the effective BAR aperture of a BAR is not processed by the BAR. A received TLP whose address falls within a BAR aperture, but outside the *effective BAR aperture*, is treated as an unsupported request by the NT function. The behavior for TLPs whose address falls within the effective address of multiple BARs is undefined.

#### **Mapping NT Configuration Space to BAR 0**

As mentioned above, the 4 KB configuration space associated with the NT endpoint may be mapped into 32-bit memory using BAR 0. BAR 0 and BAR 1 may be paired to map the 4 KB configuration space associated with the NT endpoint into 64-bit memory.

- Mapping NT configuration space to BAR 0 allows these configuration space registers to be accessed via memory read or writes.

- Mapping NT configuration space to BAR 0 requires that the MODE field be set appropriately in the BARSETUP0 register. When NT configuration space is mapped to BAR 0, the size of the BAR aperture is automatically set to 4 KB and the BARLIMIT0 register is ignored.

When the NT function's configuration space is mapped to BAR 0, it is recommended that this configuration space be placed in non-prefetchable memory space, as some registers may generate side-effect actions when accessed. In addition, memory read or write requests to BAR 0 must specify a length of 1 DWord. Violating this last requirement produces undefined results.

#### **TLP Translation**

#### **Direct Address Translation**

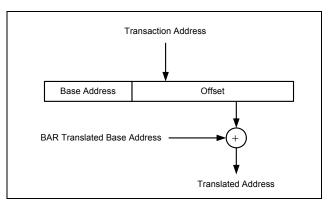

All BARs may be configured to support direct address translation. Figure 11 illustrates the address translation process for a BAR configured as a memory address window with direct address translation.

Figure 11 Direct Address Translation

The address of a TLP that falls within the effective BAR aperture of a BAR may be partitioned into a base address and an offset.

- The base address is equal to the value programmed in BAR BADDR field bits that are read/write.

- The offset address corresponds to address bits that are not part of the base address.

Associated with each BAR is a translated base address.

- The translated base address is a 64-bit quantity. The upper 32-bits are set to zero when the translated base address is less than or equal to 0xFFFF\_FFFF (i.e., lower 4 GB).

- The translated base address is always DWord aligned. Therefore, the bottom two bits are always zero.

The translated address for the TLP is equal to the sum of the TLP offset address with the corresponding translated base address field.

- Following formation of the translated address, the TLP header size is adjusted accordingly.

- If the upper 32-bits of the 64-bit address are all zero, then a 3 DWord header is used.

- If the upper 32-bits of the 64-bit address are non-zero, then a 4 DWord header is used.

The partition of the translated TLP is specified by the Translated Partition (TPART) field in the corresponding BARSETUPx register.

If the partition associated with the translated TLP is invalid (e.g., there is no NT endpoint associated with the destination partition, the destination partition is not in the active state, or the destination partition is the same as the original partition), then the TLP is treated as an unsupported request by the NT endpoint that received the request.

The behavior of a TLP whose translated address falls within the BAR aperture(s) of the NT function in the destination (i.e., translated) partition is undefined.

### **Lookup Table Address Translation**

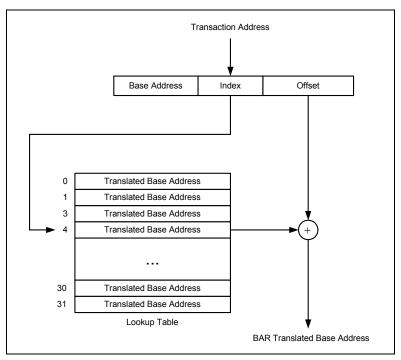

BARs two and four may be configured to support lookup table address translation.

- BAR two may be configured to support either a 16-entry or 32-entry lookup table.

- BAR four only supports 16-entry lookup table address translation. Configuring BAR four for 32-entry lookup table address translation produces undefined results.

- If both BARs two and four are configured for lookup table address translation, then BAR two only supports a 16-entry lookup table. Configuring BAR two for 32-entry lookup table address translation while BAR four is configured for 16-entry lookup table address translation produces undefined results.

Figure 12 illustrates the address translation process for a BAR configured as a memory address window with lookup table address translation.

Figure 12 Lookup Table Translation

The address of a TLP that falls within the effective BAR aperture of a BAR may be partitioned into a base address, index, and offset.

- The base address is equal to the value programmed in the BAR BADDR field bits that are read/ write.

- If the BAR is configured for a 16-entry lookup table, then the index corresponds to the next 4-bits

of the address. If the BAR is configured for a 32-entry lookup table, then the index corresponds to

the next 5-address bits.

- The offset address corresponds to address bits that are not part of the base address or index.

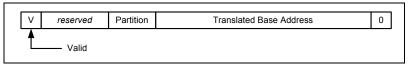

When the BAR is configured to operate as an address window with lookup table address translation, valid values for the SIZE field in the corresponding BARSETUPx register are 14 through 37 (values greater than 32 require a 64-bit BAR). Setting the SIZE field outside this range produces undefined results. Associated with a BAR configured to use lookup table address translation is a 16 or 32-entry lookup table. The format of a table entry is shown in Figure 13.

- The translated base address field plays the same role as the translated base address in direct address translation.

- The partition field specifies the destination partition associated with the translated TLP.

- The valid field indicates if the table entry is valid.

Figure 13 Lookup Table Entry Format

When a TLP is processed by a BAR that is configured for lookup table address translation, the index portion of the TLP address is used as an index into the lookup table. If the table entry pointed to by the index is not valid, then the TLP is treated as an unsupported request. If the table entry pointed to by the index is valid, then the translated address for the TLP is formed by adding the offset field of the TLP address to the translated base address associated with the table entry.

- The translated base address is a 64-bit quantity allowing the translated window to be located anywhere within the address space of the destination PCI Express domain.

- The size of a PCI Express TLP header varies depending on the size of the address. A 32-bit address has a three DWord header while a 64-bit address has a four DWord header. Following formation of the translated address, the TLP header size is adjusted accordingly.

The destination partition associated with the translated TLP is specified by the partition field in the lookup table entry. If the partition associated with the translated TLP is invalid (e.g., there is no NT endpoint associated with the destination partition, the destination partition is not in the active state, or the destination partition is the same as the original partition), then the TLP is treated as an unsupported request by the NT endpoint that received the request. The behavior of a TLP whose translated address falls within the BAR aperture(s) of the NT function in the destination partition is undefined.

Table 2 and Table 4 summarize the parameters associated with a 16-entry and 32-entry lookup table. Page size refers to the size of the address space translated by each table entry.

| BARSETU<br>Px SIZE<br>Field | Aperture<br>Size | Page<br>Size | Base<br>Address<br>(bits) <sup>1</sup> | Index<br>(bits) | Offset<br>(bits) |

|-----------------------------|------------------|--------------|----------------------------------------|-----------------|------------------|

| 14                          | 16 KB            | 1 KB         | [63:14]                                | [13:10]         | [9:0]            |

| 15                          | 32 KB            | 2 KB         | [63:15]                                | [14:11]         | [10:0]           |

| 16                          | 64 KB            | 4 KB         | [63:16]                                | [15:12]         | [11:0]           |

| 17                          | 128 KB           | 8 KB         | [63:17]                                | [16:13]         | [12:0]           |

| 18                          | 256 KB           | 16 KB        | [63:18]                                | [17:14]         | [13:0]           |

| 19                          | 512 KB           | 32 KB        | [63:19]                                | [18:15]         | [14:0]           |

| 20                          | 1 MB             | 64 KB        | [63:20]                                | [19:16]         | [15:0]           |

| 21                          | 2 MB             | 128 KB       | [63:21]                                | [20:17]         | [16:0]           |

| 22                          | 4 MB             | 256 KB       | [63:22]                                | [21:18]         | [17:0]           |

| 23                          | 8 MB             | 512 KB       | [63:23]                                | [22:19]         | [18:0]           |

| 24                          | 16 MB            | 1 MB         | [63:24]                                | [23:20]         | [19:0]           |

| 25                          | 32 MB            | 2 MB         | [63:25]                                | [24:21]         | [20:0]           |

| 26                          | 64 MB            | 4 MB         | [63:26]                                | [25:22]         | [21:0]           |

| 27                          | 128 MB           | 8 MB         | [63:27]                                | [26:23]         | [22:0]           |

| 28                          | 256 MB           | 16 MB        | [63:28]                                | [27:24]         | [23:0]           |

| 29                          | 512 MB           | 32 MB        | [63:29]                                | [28:25]         | [24:0]           |

| 30                          | 1 GB             | 64 MB        | [63:30]                                | [29:26]         | [25:0]           |

| 31                          | 2 GB             | 128 MB       | [63:31]                                | [30:27]         | [26:0]           |

| 32                          | 4 GB             | 256 MB       | [63:32]                                | [31:28]         | [27:0]           |

| 33                          | 8 GB             | 512 MB       | [63:33]                                | [32:29]         | [28:0]           |

| 34                          | 16 GB            | 1 GB         | [63:34]                                | [33:30]         | [29:0]           |

Table 2 16-Entry Lookup Table Parameters (Page 1 of 2)

| BARSETU<br>Px SIZE<br>Field | Aperture<br>Size | Page<br>Size | Base<br>Address<br>(bits) <sup>1</sup> | Index<br>(bits) | Offset<br>(bits) |

|-----------------------------|------------------|--------------|----------------------------------------|-----------------|------------------|

| 35                          | 32 GB            | 2 GB         | [63:35]                                | [34:31]         | [30:0]           |

| 36                          | 64 GB            | 4 GB         | [63:36]                                | [35:32]         | [31:0]           |

| 37                          | 128 GB           | 8 GB         | [63:37]                                | [36:33]         | [32:0]           |

Table 2 16-Entry Lookup Table Parameters (Page 2 of 2)

<sup>&</sup>lt;sup>1.</sup> Assumes 64-bit TLP address. If only 32-bits are used then bits [31:x] are used.

| BARSETU<br>Px SIZE<br>Field | Aperture<br>Size | Page<br>Size | Base<br>Address<br>(bits) <sup>1</sup> | Index<br>(bits) | Offset<br>(bits) |

|-----------------------------|------------------|--------------|----------------------------------------|-----------------|------------------|

| 14                          | 16 KB            | 512 B        | [63:14]                                | [13:9]          | [8:0]            |

| 15                          | 32 KB            | 1 KB         | [63:15]                                | [14:10]         | [9:0]            |

| 16                          | 64 KB            | 2 KB         | [63:16]                                | [15:11]         | [10:0]           |

| 17                          | 128 KB           | 4 KB         | [63:17]                                | [16:12]         | [11:0]           |

| 18                          | 256 KB           | 8 KB         | [63:18]                                | [17:13]         | [12:0]           |

| 19                          | 512 KB           | 16 KB        | [63:19]                                | [18:14]         | [13:0]           |

| 20                          | 1 MB             | 32 KB        | [63:20]                                | [19:15]         | [14:0]           |

| 21                          | 2 MB             | 64 KB        | [63:21]                                | [20:16]         | [15:0]           |

| 22                          | 4 MB             | 128 KB       | [63:22]                                | [21:17]         | [16:0]           |

| 23                          | 8 MB             | 256 KB       | [63:23]                                | [22:18]         | [17:0]           |

| 24                          | 16 MB            | 512 KB       | [63:24]                                | [23:19]         | [18:0]           |

| 25                          | 32 MB            | 1 MB         | [63:25]                                | [24:20]         | [19:0]           |

| 26                          | 64 MB            | 2 MB         | [63:26]                                | [25:21]         | [20:0]           |

| 27                          | 128 MB           | 4 MB         | [63:27]                                | [26:22]         | [21:0]           |

| 28                          | 256 MB           | 8 MB         | [63:28]                                | [27:23]         | [22:0]           |

| 29                          | 512 MB           | 16 MB        | [63:29]                                | [28:24]         | [23:0]           |

| 30                          | 1 GB             | 32 MB        | [63:30]                                | [29:25]         | [24:0]           |

| 31                          | 2 GB             | 64 MB        | [63:31]                                | [30:26]         | [25:0]           |

| 32                          | 4 GB             | 128 MB       | [63:32]                                | [31:27]         | [26:0]           |

| 33                          | 8 GB             | 256 MB       | [63:33]                                | [32:28]         | [27:0]           |

| 34                          | 16 GB            | 512 MB       | [63:34]                                | [33:29]         | [28:0]           |

| 35                          | 32 GB            | 1 GB         | [63:35]                                | [34:30]         | [29:0]           |

| 36                          | 64 GB            | 2 GB         | [63:36]                                | [35:31]         | [30:0]           |

| 37                          | 128 GB           | 4 GB         | [63:37]                                | [36:32]         | [31:0]           |

#### Table 3 32-Entry Lookup Table Parameters

The lookup table for both BARs is configured using the Lookup Table Offset (LUTOFFSET), Lookup Table Lower Data (LUTLDATA), Lookup Table Middle Data (LUTMDATA), Lookup Table Upper Data (LUTUDATA) registers.

$<sup>^{1.}</sup>$  Assumes 64-bit TLP address. If only 32-bits are used then bits [31:x] are used.

Fields associated with lookup entries are modified by accessing the LUTLDATA, LUTLMDATA and LUTUDATA registers. A read from one of these registers returns the field values of the lookup table entry pointed to by the LUTOFFSET register. Similarly, a write updates the fields of the lookup entry pointed to by the LUTOFFSET register.

The BAR field in the LUTOFFSET register selects the lookup table associated with the corresponding BAR while the INDEX field in the LUTOFFSET field selects the lookup table entry. The state of the lookup table is preserved across all resets except a switch fundamental reset. Following a switch fundamental reset, the state of all lookup table fields except the Valid (V) field is undefined. Following a switch fundamental reset, the Valid field is cleared in all entries.

#### **ID Translation**

PCI Express TLPs may be categorized into request TLPs and completion TLPs.

- A request TLP is a packet used to initiate a transaction.

- A completion TLP is a packet used to terminate, or partially terminate a transaction sequence.

Request TLPs contain a requester ID field that defines the unique PCI Express identifier associated with the requester that generated the request TLP. Completion TLPs contain both a requester ID field and a completer ID field. The completer ID field defines the unique PCI Express identifier associated with the completer that generated the completion TLP.

A PCI Express identifier consists of a 16-bit quantity that is unique for each function in a PCI Express hierarchy. The 16-bit quantity may be interpreted as an 8-bit bus number, 5 bit device number, and 3 bit function number. The Alternate Routing-ID Interpretation ECN specifies a secondary interpretation.

#### **NT Mapping Table**

Associated with the switch is a 64-entry Non-Transparent (NT) mapping table. The NT mapping table is used to perform ID translation and ID based protection. The NT mapping table is a global table shared by all ports configured for NT operation. The format of the NT mapping table is shown in Figure 14 and the fields are described in Table 4.

| Mapping Table |     |     |     |          |      |     |     |      |   |

|---------------|-----|-----|-----|----------|------|-----|-----|------|---|

| <u>Entry</u>  |     |     |     |          |      |     |     | T    |   |

| 0             | RNS | ATP | ATP | Reserved | PART | BUS | DEV | FUNC | ٧ |

| 1             | RNS | ATP | ATP | Reserved | PART | BUS | DEV | FUNC | ٧ |

| 2             | RNS | ATP | ATP | Reserved | PART | BUS | DEV | FUNC | ٧ |

| 3             | RNS | ATP | ATP | Reserved | PART | BUS | DEV | FUNC | ٧ |

| 4             | RNS | ATP | ATP | Reserved | PART | BUS | DEV | FUNC | ٧ |

| 5             | RNS | ATP | ATP | Reserved | PART | BUS | DEV | FUNC | ٧ |

|               |     |     |     |          |      |     |     |      |   |

| ŧ             |     |     |     |          |      |     |     |      |   |

| 63            | RNS | ATP | ATP | Reserved | PART | BUS | DEV | FUNC | ٧ |

Figure 14 NT Mapping Table

| Bit<br>Field | Field<br>Name | Description                                                                                                                     |  |  |  |

|--------------|---------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0            | V             | Valid. This bit is set if the mapping table is valid.                                                                           |  |  |  |

| 3:1          | FUNC          | Function. This field contains the mapping table entry PCI Express function number.                                              |  |  |  |

| 8:4          | DEV           | Device. This field contains the mapping table entry PCI Express device number.                                                  |  |  |  |

| 16:9         | BUS           | Bus. This field contains the mapping table entry PCI Express bus number.                                                        |  |  |  |

| 19:17        | PART          | Partition. This field contains the mapping table entry partition number.                                                        |  |  |  |

| 29           | ATP           | Address Type Processing. This field specifies the processing of the address type (AT) field on request TLPs. Refer to Section . |  |  |  |

| 30           | CNS           | Completion No Snoop Processing. This field specifies the no snoop processing on completion TLPs. Refer to Section .             |  |  |  |

| 31           | RNS           | Request No Snoop Processing. This field specifies the no snoop processing on request TLPs. Refer to Section .                   |  |  |  |

Table 4 NT Mapping Table Field Description

The state of the NT mapping table is preserved across all resets except a switch fundamental reset. Following a switch fundamental reset, the state of all NT mapping table fields except the Valid (V) field is undefined. Following a switch fundamental reset, the Valid field is cleared in all entries. The mapping tables may be initialized by using the NT Mapping Table Address (NTMTBLADDR) and NT Mapping Table Data (NTMTBLDATA) registers.

To access a mapping table entry, the NT Mapping Table Address (ADDR) field in the port's NTMT-BLADDR register is initialized with the partition NT mapping table entry to be accessed. Reading from the NT Mapping Table Data (NTMTBLDATA) register returns the value of the fields of the corresponding partition NT mapping table entry pointed to by the ADDR field in the NTMTBLADDR register. Writing to the NTMTBLDATA register causes the fields in the corresponding partition NT mapping table entry pointed to by the ADDR field in the NTMTBLADDR register to be updated with the value written. The NTMTBLDATA register must be accessed using DWORD operations. The behavior for all other access sizes is undefined.

Causing an NT mapping table protection violation results in the NT Mapping Table Access Error (ERR) bit to be set in the NT Mapping Table Status (NTMTBLSTS) register. Since the NT mapping table is global and shared by all partitions, the switch supports NT mapping table protection and virtualization.

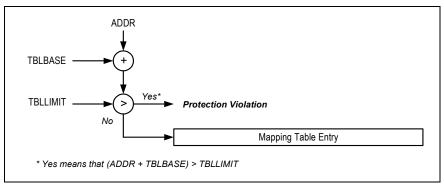

Located in the Switch Control and Status register space is an NT Mapping Table Protection (NTMTBL-PROTx) register for each partition. NT Mapping Table Base (TBLBASE) and NT Mapping Table Limit (TBLLIMIT) fields in the NTMTBLPROTx register control how partition NT mapping table accesses are translated into physical NT mapping table accesses. The translation process is shown in Figure 15.

Figure 15 NT Table Partitioning

The physical NT mapping table entry accessed is equal to the sum of the partition NT mapping table entry, specified by the ADDR field in the NTMTBLADDR register, with the TBLBASE field in the NTMTBL-PROT register associated with the partition. If the resulting physical NT mapping table entry address is less than or equal to the value in the TBLLIMIT field in the NTMTBLPROT field associated with the partition, then the read or write access is performed on the physical NT mapping table entry. If the value of the resulting NT mapping table entry address is greater than the NTBLLIMIT field, then a protection violation is signaled.

Located in each NTMTBLPROT register is a Partition Blocking Vector (PARTBLOCK). Associated with each partition in the device is a corresponding bit in the PARTBLOCK vector. When a write to the NTMT-BLDATA register is performed with a PART field value whose corresponding bit is set in the PARTBLOCK vector, then a protection violation is signaled.

A protection violation during an NTMTBLDATA read operation results in a value of zero being returned in all fields and setting of the NT Mapping Table Access Error (ERR) bit in the NT Mapping Table Status (NTMTBLSTS) register. A protection violation during an NTMTBLDATA write operation causes the write operation to be ignored (i.e., no table entry or register field is actually updated) and setting of the NT Mapping Table Access Error (ERR) bit in the NT Mapping Table Status (NTMTBLSTS) register.

Following a switch fundamental reset, NT mapping table protection and virtualization is disabled.

- All partitions may access all 64 physical NT mapping table entries.

- The virtual NT mapping table address of all partitions is equal to the physical NT mapping table address.

- A partition may update any NT mapping table entry with any PART field value.

#### **Request ID Translation**

Request TLPs contain a requester ID field that defines the unique PCI Express identifier associated with the requester that generated the request TLP. When a request TLP is received by an NT endpoint that is to be routed on the NT interconnect (i.e., the TLP hits an NT endpoint BAR aperture and has a valid translation), a requester ID lookup and translation are performed.

The lookup is performed by matching the 16-bit requester ID in the request TLP along with the partition associated with the NT endpoint to entries in the NT mapping table. If a lookup match is not found, then the TLP is treated as an unsupported request. Otherwise, the TLP is processed normally as described below:

- 16-bit requester ID is compared to the 16-bit value in each NT mapping table consisting of the BUS, DEV, and FUNC fields regardless of the requester ID interpretation. A requester ID match occurs when the 16-bit value in the requester ID field of the TLP matches an NT mapping table entry.

- The partition associated with a request TLP is the partition ID associated with the NT endpoint which received the request TLP. A partition match occurs when the partition associated with a request TLP matches the PART field of an NT mapping table entry.

- A lookup match occurs for a request TLP when a NT mapping table entry exists that is valid (i.e., the V bit is set) and has both a requester ID match as well as a partition match.

- The behavior of a request TLP with multiple lookup matches is undefined. Multiple lookup matches are the result of an invalid configuration.

PCI Express allows a function to expand the number of supported outstanding requests requiring completions beyond 256 through the use of phantom function numbers. When phantom function numbers are enabled, the Tag field in the TLP header may be logically expanded by using unimplemented function numbers. These unimplemented function numbers are referred to as phantom function numbers. A requester that uses phantom function numbers when communicating with the NT endpoint requires a unique NT mapping table entry for each phantom function number.

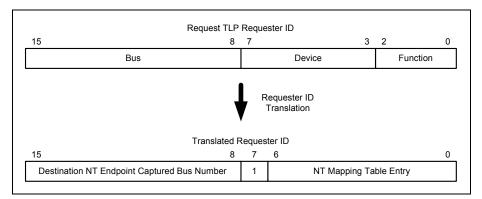

The requester ID field associated with a request TLP that has a lookup match is translated as shown in Figure 16.

- The bus field is replaced by the captured bus number of the NT endpoint associated with the partition of the translated TLP.

- Bit 4 of the device field is set to one.

- The lower four bits of the device field and the function field are replaced with the lookup table match entry.

Figure 16 Request TLP Requester ID Translation

One function of request TLP ID translation process is that it allows a corresponding reverse translation to occur for completions. This reverse translation is described in section Completion ID Translation on page 18. Posted requests (e.g., memory writes) have no corresponding completions. Therefore, the primary role of the NT mapping table lookup for these TLPs is to provide a form of protection (i.e., only authorized requesters are allowed to issue TLPs that map onto the NT interconnect). When the ID Protection Check Disable (IDPROTDIS) bit in the Endpoint Control (NTCTL) register is set, the NT table lookup for posted requests is skipped and all posted requests are allowed to map onto the NT interconnect regardless of requester ID.

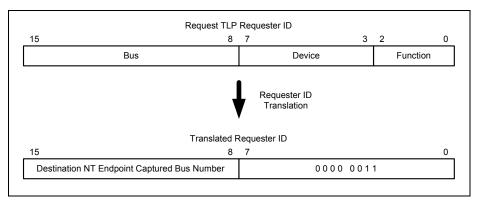

The requester ID field associated with a posted request TLP is translated as shown in Figure 17 when the IDPROTDIS bit is set in the NTCTL register.

- The bus field is replaced by the captured bus number of the NT endpoint associated with the partition of the translated TLP.

- The device and function fields are replaced by the value 0x3. This corresponds to device 0, function 3.

Figure 17 Request TLP Requester ID Translation with ID Protection Check Disabled

If the Bus Master Enable (BME) bit is cleared in the PCI Command (PCICMD) register of the NT endpoint associated with the translated TLP (i.e., in the destination partition), then the request is treated as an unsupported request by the NT endpoint that received the request (i.e., in the source partition).

## **Completion ID Translation**

Completion TLPs contain both a requester ID field and a completer ID field. The completer ID field defines the unique PCI Express identifier associated with the completer that generated the completion TLP.

When a completion TLP is received and claimed by an NT endpoint the following processing is performed:

- If the TLP's requester ID function field matches that of the NT endpoint (i.e., either zero or one depending on the port operating mode), and a punch-through configuration is in progress, the TLP is accepted by the NT endpoint and processed as described in section Punch-Through Configuration Requests on page 22.

- If the TLP's requester ID function field matches that of the NT endpoint and a punch-through configuration is not in progress, then the TLP is handled as an unexpected completion by the NT function.

- Refer to section Error Detection and Handling by the NT Function on page 27.

- Otherwise, the 8-bit value consisting of the device and function fields are extracted from the requester ID field to form the NT lookup table entry index, and the processing described below is performed.

The NT mapping table entry index extracted from the TLP is used as an index into the NT lookup table. The requester ID of the translated completion TLP is formed as follows:

- The requester ID bus field is replaced by the NT mapping table bus field.

- The requester ID device field is replaced by the NT mapping table device field.

- The requester ID function field is replaced by the NT mapping table function field.

The completer ID of the translated completion TLP is equal to the bus, device, and function of the NT endpoint associated with the partition of the translated completion TLP (i.e., the NT function that emits the TLP).

Note that the setting of the Bus Master Enable (BME) bit in the PCICMD register of the NT endpoint in the destination partition has no effect on translation of completion TLPs.

# TLP Attribute Processing

### **No Snoop Processing**

The No Snoop attribute in the header of request TLPs indicates whether hardware enforced cache coherence is expected. Some platforms lack the ability to control the no snoop attribute for generated requests. Therefore, the switch provides the ability to modify the No Snoop attribute for TLPs flowing through the NT interconnect.

When an NT table lookup is performed for request TLPs (described in Section), the Request No Snoop Processing (RNS) field in the matching NT mapping table entry is examined. If the RNS bit is set, then the No Snoop attribute in the translated TLP is inverted. If the RNS bit is cleared, then the No Snoop attribute in the translated TLP is equal to that of the received request TLP (i.e., the No Snoop attribute is not modified).

If the Completion No Snoop Processing (CNS) field in the NT mapping entry corresponding to the extracted NT mapping table index (see Section ) is set, then the No Snoop attribute in the translated TLP is inverted. If the CNS bit is cleared, then the No Snoop attribute in the translated TLP is equal to that of the received completion TLP (i.e., the No Snoop attribute is not modified).

#### **Address Type Processing**

As described in the Address Translation Services specification [2] and the PCI Express specification [1], the Address Type (AT) field in the header of a memory read or memory write TLP indicates the type of address in the TLP (i.e., untranslated, translation request, translated).

<sup>&</sup>lt;sup>1.</sup> A completion TLP is claimed by the NT endpoint when the TLP's requester ID matches the NT function's bus/device/function assignment within the PCI Express hierarchy or matches a <u>valid</u> entry in the NT function's mapping table.

The NT endpoint does not support Address Translation Services (ATS) as defined by the PCI-SIG, but it has the ability to modify the AT field for TLPs that cross the NTB. This allows the NTB to receive TLPs with translated addresses (i.e., AT field set to 'translated') in a source partition and emit them as TLPs with translated or untranslated addresses in the destination partition, or vice-versa.

Address type processing is only applied to memory read or write TLPs whose AT field is set to 'translated' or 'untranslated'. Address type processing is not applied to TLPs whose AT field is set to 'translation request'.

When an NT table lookup is performed for a request TLP (described in section Request ID Translation on page 16), the Address Type Processing (ATP) field in the matching NT mapping table entry is examined. If the ATP field is set to 0x1, then the AT field is set to 'translated' in the TLP emitted by the NT endpoint in the destination partition. Otherwise, the AT field is set to 'untranslated' in the TLP emitted by the NT endpoint in the destination partition.

Note that completion TLPs always have the AT attribute set to zero and are not subject to address type field modification.

#### **NT Multicast**

The NT function supports non-transparent (NT) multicast, which allows a TLP received by the NT function to be transmitted by zero or more ports of the switch, across partitions. A discussion of this function is beyond the scope of this application note. Contact IDT at ssdhelp@idt.com for additional information.

#### **Inter-Domain Communications**

The NT inter-domain communications capability structure provides facilities for supporting communications between processors in different PCI Express domains. The NT inter-domain communications capability provides the following facilities:

- Doorbell registers

- Message registers

#### **Doorbell Registers**

Doorbells facilitate event signalling between partitions. Associated with each NT endpoint are 32 outbound and inbound doorbell registers.

An outbound doorbell request from an NT endpoint is initiated by writing a one to the corresponding bit in the Outbound Doorbell Set (OUTDBELLSET) register.

- An outbound doorbell request from an NT endpoint is terminated by writing a one to the corresponding bit in the Outbound Doorbell Clear (OUTDBELLCLR) register.

- Writing a zero to a bit position in either the OUTDBELLSET or OUTSBELLDBELLCLR register has

no effect on the register contents or corresponding doorbell request.

An inbound doorbell request to the NT endpoint results in the setting of the corresponding bit in the Inbound Doorbell Status (INDBELLSTS) register.

- The setting of a bit in the INDBELLSTS register may be used to generate an NT endpoint interrupt.

- Individual bits in the INDBELLSTS register may be masked from generating an interrupt by setting the corresponding bit in the Inbound Doorbell Mask (INDBELLMSK) register.

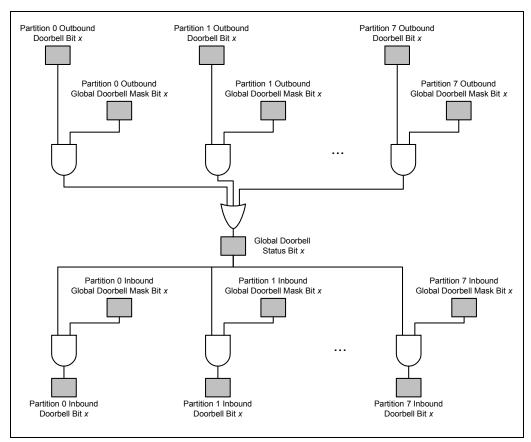

The logical operation of doorbells is illustrated in Figure 18.

- For each of the 32 outbound doorbell request, the requests from all partitions are logically OR-ed together to form a global doorbell request. This global doorbell request is then used to initiate inbound doorbell requests to each of the partitions.

- The global doorbell request status may be determined by reading the Global Doorbell Status (GDBELLSTS) register.

- A bit in the GDBSELLSTS register is set if there exists an unmasked outbound doorbell request in any partition that corresponds to the bit.

- An outbound doorbell may initiate inbound doorbell requests in one or more partitions. All inbound doorbell requests share the same index. In other words, writing a one to bit position 8 in the OUTDBELLSET register may initiate an inbound doorbell request in multiple partitions, but each inbound doorbell request will be associated with the same bit position (i.e., position 8) as that of the outbound request.

- Associated with each outbound doorbell is a Global Outbound Doorbell Mask (GODBELLMSK[31:0]) register that contains a bit corresponding to each partition. When a bit in this register is set, outbound doorbell requests from the corresponding partition are masked. For example, setting bit 7 in the GOBDBELLMSK4 register masks doorbell 4 requests from partition 7.

- When a doorbell request from a partition is masked, the state of the doorbell in the corresponding partition plays no role in determining the state of the global doorbell status.

- A global doorbell request results in the initiation of corresponding inbound doorbell requests to all unmasked partitions.

- A global doorbell request may be masked to a partition by setting the corresponding partition bit in the Global Inbound Doorbell Mask (GIDBELLMSK[31:0]) register.

- When an inbound doorbell request is masked to a partition, the state of the global doorbell status

plays no role in determining the state of the corresponding inbound doorbell request in that partition.

Figure 18 Logical Representation of Doorbell Operation

Doorbells are "level sensitive." This means that a global doorbell request remains set as long as there exists an unmasked outbound request from any partition. Bits in the Inbound Doorbell Status (INDBELLSTS) register may be used to generate NT endpoint interrupts. A bit in the INDBELLSTS register may be masked from generating an interrupt by setting the corresponding bit in the Inbound Doorbell Mask (INDBELLMSK) register.

#### **Message Registers**

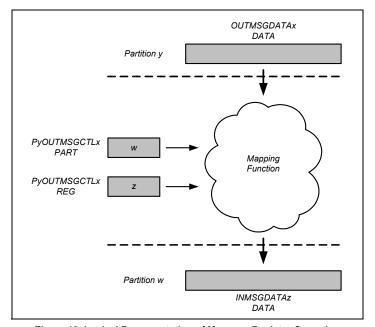

Message registers enable 32-bit values to be passed between partitions with interrupt notification. Each NT endpoint supports four Inbound Message (INMSG[3:0]) registers and four Outbound Message (OUTMSG[3:0]) registers. The logical operation of doorbells is illustrated in Figure 19.

- Associated with each outbound message register in a partition is a Switch Partition Message Control (SWPxMSGCTL[3:0]) register.

- The register SWPxMSGCTLy corresponds to outbound message register y in switch partition x.

- When an outbound message register is written, the value written to the register is transferred to the inbound message register specified by the Register Select (REG) field of the SWPxMSGCTLy register in the partition specified by the Partition (PART) field of the SWPxMSGCTLy register. Thus, fields in the SWPxMSGCTLy register specify the routing of an outbound message register in one partition to an inbound message register in typically a different partition.

Figure 19 Logical Representation of Message Register Operation

Since the mapping of outbound message registers to inbound message registers need not be one-toone, it is possible to map multiple outbound message registers, from typically different partitions, to a single inbound message register. In such a configuration, it is necessary to deal with possible contention to the inbound message register.

- When an outbound message register is written, the written value is transferred to the inbound message register specified by the corresponding SWPxMSGCTLy register. The transferred value may be accepted or rejected by the inbound message register.

- A transferred value is accepted if the message register is empty. When a transferred value is accepted, the Inbound Message (INMSG) field in the corresponding Inbound Message (INMSGx) register is updated with the transferred value, the Inbound Message Source Partition (SRC) field in the Inbound Message Source (INMSGSRC) register is updated with the partition number from which the message arrived, and the corresponding Inbound Message Status (INMSGSTSx) bit is set in the Message Status (MSGSTS) register. Once a transferred value is accepted, the inbound message register becomes full and remains full until the corresponding INTMSGSTSx bit is cleared.

- A transferred value is rejected if the message register is full. When a transfer value is rejected, the

Outbound Message Status (OUTMSGSTSx) bit is set in the Message Status (MSGSTS) register

that corresponds to the outbound message register that was written. This bit may be used to determine a transfer failed and needs to be retried.

Bits in the Message Status (MSGSTS) register may be used to generate NT interrupts. A bit in the MSGSTS register may be masked from generating an interrupt by setting the corresponding bit in the Message Status Mask (MSGSTSMSK) register.

# **Punch-Through Configuration Requests**

The NT endpoint has the capability to generate PCI Express configuration transactions on the upstream link. This mechanism, referred to as *punch-through*, is provided to facilitate configuration of systems in which a root complex is not present in the PCI Express hierarchy associated with the NT endpoint. In essence, the NT endpoint may be crosslinked to another endpoint or to a switch device, and issue configuration requests to configure these devices.

Punch-through requests are always emitted on the NT function's link. In port operating modes with multiple functions (e.g., upstream switch port with NT function), it is not allowed for punch through requests issued by the NT function to hit the primary/secondary/subordinate window of the PCI-to-PCI bridge function or the bus/device/function ID associated with other functions in the port. Breaking this rule produces undefined results.

To generate a punch-through configuration transaction on the NT endpoint's link, the following sequence should be executed. Note that the registers that control punch-through requests are located in the configuration space of the NT function. These registers may be programmed via another port (i.e., using the global address space indirection registers) or via the SMBus interface.

- Check if the punch-through configuration interface is busy by examining the Busy (BUSY) bit in the Punch-Through Configuration Status (PTCSTS) register (located in the configuration space of the NT function) and wait until the interface is not busy.

- Configure the operation (e.g., read or write) in the Punch-Through Configuration Control (PTCCTL) register.

- 3. Write to the Punch-Through Configuration Data (PTCDATA) register to initiate the configuration read or write operation as selected by the OP field in the PTCCTL register.

- This step causes the NT endpoint to emit a PCI Express configuration request TLP. The requester ID in the configuration request TLP is as follows.

- The bus field is replaced by the captured bus number of the NT endpoint associated in the target partition.

- The device and function fields are replaced by the value 0x4. This corresponds to device 0, function 4.

- The tag field is set to 0x0.

- In addition, the BUSY bit in the PTCSTS register is set to indicate a punch-through configuration transaction is in progress.

- Wait for the operation to complete by polling the status of the Done (DONE) bit in the PTCSTS register.

- The Done bit is set when the NT function receives a completion<sup>1</sup> whose destination ID matches

the NT function's requester ID (see the requester ID description above).

- Check the transaction completion status in the Status (STATUS) field of the PTCSTS register. If the initiated transaction was a read and it successfully completed, then the read result may be read from the PTCDATA register.

- The STATUS field in the PTCSTS register reflects the status of the received completion (e.g., successful completion, unsupported request, completer abort, etc.)

It is possible for a completion to not be received in response to a punch-through configuration transaction. A punch-through operation may be aborted by writing a one to the DONE bit in the PTCSTS register. This will cause subsequent completions to be discarded until a new punch-through configuration transaction is generated. This mechanism should only be used when it is certain that a completion is lost and will never arrive. It is up to the user to make this determination.

<sup>&</sup>lt;sup>1.</sup> The NT function assumes that the received completion is a completion with data (CpID) TLP and does not check for any violations in the format of the TLP.

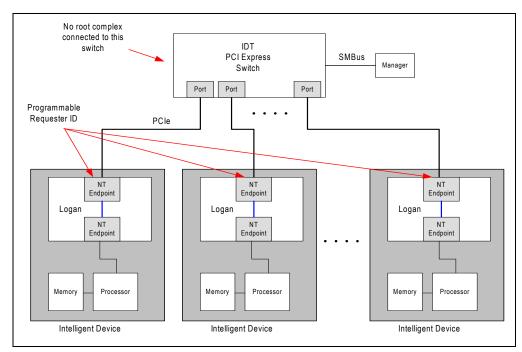

# Re-programming the Bus Number of the NT Function

In some systems, it may be desirable to use a PCI Express switch to interconnect several intelligent devices without the presence of a PCI Express root (i.e., the switch can be configured via SMBus or EEPROM). One of the challenges in building this type of system is the assignment of PCI Express requester IDs (i.e., bus, device, function) to each of the intelligent devices. Such assignment is a pre-requisite in order for ID-routed TLPs (i.e., completions) to be correctly routed by the PCI Express switch.

Normally, devices with a PCI Express port capture the bus number associated with the port on reception of type 0 configuration write requests that target the port. In system scenarios where there is no root complex in the PCI Express hierarchy, the devices will not receive type 0 configuration write requests. As a result, the default bus number (i.e., bus number 0) will be used by the devices, and ID-routing across the hierarchy won't be possible.

The switch contains a feature that allows software to explicitly configure the bus number associated with a switch port that has an NT function. The programming is done by writing to the Bus (BUS) field in the TLCNTCFG register located in the port's configuration space. Programming of the port's bus number is only allowed when the port operates in NT function mode or NT with DMA function mode.

Figure 20 shows a system scenario where a PCI Express switch is used to connect several intelligent devices. This system does not have a root complex, and communication among the intelligent devices is desired. Each intelligent device uses a switch NT port to connect to the PCI Express switch. Prior to initiating communication, the CPU located in the intelligent device programs the switch NT port that faces the rootless PCI Express hierarchy with an appropriate requester ID (i.e., by writing to the BUS field in the NT port's TLCNTCFG register; this register can be accessed by the processor on the intelligent device using the switch's global address space access registers).

Once the requester IDs for each intelligent device are programmed with unique values, traffic across the rootless PCI Express switch routes normally.

Figure 20 Example of a rootless PCI Express hierarchy with Bus Number Reprogramming

# **Interrupts**

The NT endpoint has six sources of interrupts.

- Message status

- Doorbell status

- Switch signals to the partition with which the NT endpoint is associated

- Switch events

- Failover change initiated by the failover capability associated with the partition

- Failover change completed by the failover capability associated with the partition

- A temperature sensor alarm

The interrupt sources each have a corresponding status bin in the NT Endpoint Interrupt Status (NTINTSTS) register.

- When an interrupt source requests service, the corresponding bit in the NTINTSTS register is set.

- An interrupt source may be masked from generating an interrupt by setting the corresponding mask bit in the NT Endpoint Interrupt Mask (NTINTMSK) register. By default, all interrupt sources are masked.

When an unmasked interrupt condition occurs, an MSI or interrupt message is generated by the NT endpoint as described in Table 5. The removal of the interrupt condition occurs when unmasked status bits causing the interrupt are masked or cleared.

When an NT endpoint is configured to generate INTx messages, the INTx used (i.e., INTA, INTB, etc.) depends on the programming of the Interrupt Pin (INTRPIN) register.

An MSI may be transmitted to a device (i.e., link partner) associated with any switch port of the partition, except for the cases below.

An MSI must not target the NT or DMA functions (if present) in a switch partition. An MSI generated with an address that maps to the NT or DMA function within the switch partition produces undefined results.

| Unmasked<br>Interrupt | EN bit in<br>MSICAP<br>Register | INTXD bit<br>in PCICMD<br>Register | Action                                  |

|-----------------------|---------------------------------|------------------------------------|-----------------------------------------|

| Asserted              | 1                               | Х                                  | MSI message generated                   |

|                       | 0                               | 0                                  | Assert_INTx message request generated   |

|                       | 0                               | 1                                  | None                                    |

| Negated               | 1                               | Х                                  | None                                    |

|                       | 0                               | 0                                  | Deassert_INTx message request generated |

|                       | 0                               | 1                                  | None                                    |

Table 5 NT Endpoint Interrupts

# **Virtual Channel Support**

The NT function contains a VC Capability Structure that provides architected port arbitration and TC/VC mapping for VC0. For port operating modes in which the NT function is function 0 of the port, the VC Capability Structure in this function provides architected port arbitration and TC/VC mapping for all functions of the port. For port operating modes in which the NT function is not function 0 of the port, the registers in the NT function's VC Capability Structure are 'reserved' and must not be programmed. In these modes, the VC Capability Structure in function 0 of the port provides architected port arbitration and TC/VC mapping for all functions of the port, including the NT function.

<sup>1.</sup> Reading from a reserved address returns and undefined value. Writes to a reserved address complete successfully but produce undefined behavior on the register.

# **Maximum Payload Size**

The switch requires that the Maximum Payload Size (MPS) field in the PCI Express Device Control (PCIEDCTL) register be set identically in all functions (i.e., PCI-to-PCI bridge, NT, and DMA) of a partition. In addition, when inter-partition transfers are possible between two or more partitions (i.e., across the NT interconnect), all switch functions in these partitions must have the same MPS setting. Violating this rule produces undefined results.

Note that a port with a maximum link width of x1 supports a Maximum Payload Size (MPS) of up to 1 KB. Ports with a maximum link width of x2, x4, or x8 support an MPS of up to 2 KB. The MPAYLOAD field in the PCI Express Device Capabilities (PCIEDCAP) register is automatically set by the hardware based on the port's maximum link width to reflect this.

# **Bus Locking**

The NT function does not support bus locking. Memory read request-locked TLPs received by an NT function are treated as unsupported requests and an unsupported request completion with no data (CplLk) is returned. The operation of a switch partition is undefined when bus locking is performed in a partition that contains an NT function in its upstream port.

# **ECRC Support**

End-to-End CRC (ECRC) is supported for transactions that are forwarded through the NT interconnect. Since the TLP contents (i.e., header) are modified for TLPs flowing between NT endpoints, a new ECRC must be computed. When a TLP is forwarded on to the NT interconnect by an NT endpoint, the NT endpoint computes the ECRC for the new translated TLP in parallel with checking the ECRC, if it exists, of the received TLP. The existence of an ECRC in the received TLP is indicated by the TD bit in the TLP header.

The NT function only checks and logs ECRC errors when the ECRC Check Enable (ECRCCE) bit is set in the function's AER Control (AERCTL) register, and the TLP with ECRC is received from the upstream port's link.

- ECRC error checking and logging is not performed by the NT function when it does not receive the TLP from the link.

- In this case, the ECRC error checking and logging is done by the port that received the TLP from the link (e.g., downstream port).

If ECRC checking applicable as described above and an ECRC error is detected, then an ECRC error is reported by the NT endpoint that received the TLP. See Section, *Error Detection and Handling by the NT Function* for details.

If ECRC checking is enabled in an NT endpoint, then ECRC is checked in all TLPs received by the NT endpoint that contain an ECRC. The reception of a TLP without ECRC is not considered an error (i.e., the TLP is processed normally).

ECRC generation is enabled in the NT endpoint when the ECRC Generation Enable (ECRCGE) bit is set in the function's AER Control (AERCTL) register.

If ECRC generation is enabled in the NT endpoint associated with the destination partition of the translated TLP, then the translated TLP contains an ECRC and the TD bit in the translated TLP header is set.

- If ECRC checking is not enabled in the NT endpoint that received the TLP, or if the received TLP does not contain an ECRC, or if ECRC checking is enabled and the ECRC computed by the NT endpoint is correct, then the ECRC associated with the translated TLP is that computed by the NT endpoint.

- If ECRC checking is enabled in the NT endpoint and the received TLP contains an ECRC error, then the ECRC associated with the translated TLP is equal to the ECRC computed by the NT endpoint with even bits inverted.

If ECRC generation is enabled in an NT endpoint, then all TLPs originated by that endpoint contain an ECRC.

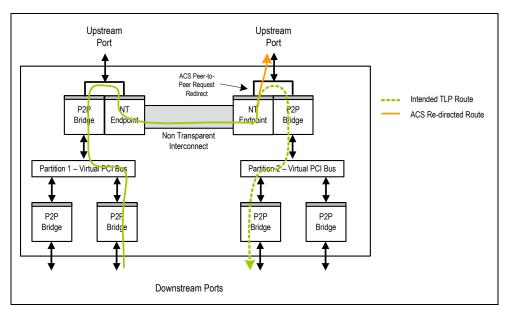

# **Access Control Services (ACS)**

The NT function supports the following ACS checks<sup>1</sup>:

- ACS Peer-to-Peer<sup>2</sup> Request Redirect

- ACS Peer-to-Peer Completion Redirect

- ACS Direct Translated Peer-to-Peer

ACS is programmed via the ACS Capability Structure in the NT function's configuration space.

- The NT function supports ACS checks when the port operates in the following port operating modes:

- · Upstream switch port with NT function

- · Upstream switch port with NT and DMA function

- In these modes, the ACS Capability Structure is linked into the NT function's configuration space.

- The NT function does not support ACS checks when the port operates in any other mode.

The NT function applies the above ACS checks for TLPs it emits (i.e., TLPs received on another partition that have undergone NT address translation).

ACS checks are not applied to punch-through configuration requests issued by the NT function.

Table 6 lists ACS checking and handling performed by the NT function. Note that there are none of the ACS checks results in an ACS violation error.

| ACS Check                                     | PCI Express<br>Specification <sup>1</sup><br>Section | Error<br>Reporting<br>Condition    | Action Taken                                                      |

|-----------------------------------------------|------------------------------------------------------|------------------------------------|-------------------------------------------------------------------|

| ACS Peer-to-Peer<br>(P2P) Request<br>Redirect | 6.12.1.1                                             | N/A<br>(not an ACS viola-<br>tion) | Offending request is redirected upstream towards root complex.    |

| ACS P2P Completion Redirect                   |                                                      |                                    | Offending completion is redirected upstream towards root complex. |

| ACS Direct Trans-<br>lated P2P                |                                                      |                                    | Offending TLP is subject to ACS P2P Request Redirect rules.       |

Table 6 ACS Checks Performed by the NT Function in a Port Operating in Multi-function Mode  $^{1}$ . Refer to [1]

When an ACS check causes a TLP to be re-directed, the re-direction is implemented such that TLPs emitted by the NT function that are ACS re-directed follow the ordering rules. Note that ACS Direct Translated Peer-to-Peer requires that the NT function perform a check on the Address Type (AT) field in request TLPs it emits. Prior to performing this ACS check, the AT field in the emitted TLPs is subject to the processing described in section Address Type Processing on page 18.

If the NT function clears the AT field in a TLP it emits (i.e., the TLP is marked as untranslated), the ACS Direct Translated P2P check is reduced to an ACS P2P Request Redirect check.

ACS checks are only applicable to certain TLP types. Table 7 list the ACS checks supported by the NT function and the TLP types on which they are applied.

<sup>&</sup>lt;sup>1.</sup> The switch does not support ACS Peer-to-Peer Egress Control among the functions of a multi-function upstream port.

<sup>&</sup>lt;sup>2.</sup> In a multi-function upstream port, 'peer-to-peer' implies traffic exchanged among the port functions (e.g., from the port's NT function to the port's PCI-to-PCI bridge function).

| ACS Check                               | Applicable to the following TLP Type(s) |

|-----------------------------------------|-----------------------------------------|

| ACS Peer-to-Peer (P2P) Request Redirect | Peer-to-Peer Request TLPs               |

| ACS P2P Completion Re-direct            | Peer-to-Peer Completion TLPs            |

| ACS Direct Translated P2P               | Peer-to-Peer Memory Request TLPs        |

Table 7 TLP Types Affected by ACS Checks

As an example of an ACS check performed by the NT function, consider the case where software enables ACS Peer-to-Peer Request Redirect in the NT function. This commands the NT function to redirect upstream (i.e., transmit on the upstream link) all requests that it issues which would have otherwise been logically routed via the upstream port's PCI-to-PCI bridge function. Figure Figure 21 shows an example of a ACS Peer-to-Peer Request Redirect. The green lines mark the requests intended route, and the orange lines the request's re-directed route due to ACS.

Figure 21 Example of ACS Peer-to-Peer Request Redirect Applied by the NT Function

When multiple ACS checks are enabled, they are prioritized. Refer to [1] for further information on ACS.

# **Error Detection and Handling by the NT Function**

This section describes error conditions associated with non-transparent switch operation. This includes physical, data-link, and transaction layer errors detected by the switch ports, as well as application layer errors associated with the non-transparent-bridge (NTB) functionality.

Internal switch errors (i.e., parity errors, switch time-out, and internal memory errors) are associated with the switch core and not with a specific port function.

The errors described here apply to ports that operate in a mode that includes the NT function (e.g., NT endpoint mode, upstream switch port with NT endpoint mode, etc.) This section focuses specifically on errors related to the NT function. Errors that affect all functions of the port (i.e., non function-specific errors) are noted where appropriate.

Error detection and handling in the switch follows the requirements in the PCI Express specification [1].

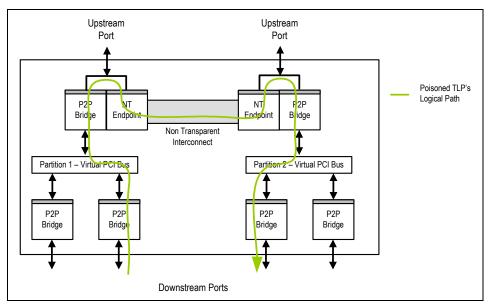

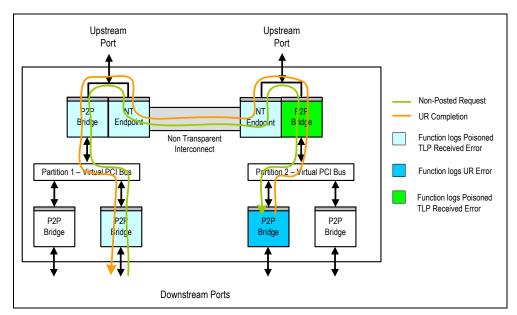

The error checking and handling described here is performed by each switch NT function. In cases where the error condition propagates among multiple NT functions (e.g., a poisoned TLP received by an NT function, passed across the NT interconnect, and emitted by the NT function in another partition), each NT function performs error checking and handling independently. Refer to section NTB Inter-Partition Error Propagation on page 36 for further details and examples on this.

The errors described below are associated with specific actions to log and report the error. The terms 'uncorrectable error processing' and 'correctable error processing' refer to the processing described in Section 6.2.5 of [1].

Errors which are not function-specific are logged in the corresponding status & logging registers of <u>all functions in the port</u>. Errors that are function-specific are logged in the status & logging register of the affected function only. Signaling of non function-specific errors follows the rules in Section 6.2.4 of [1].

Some of the errors described below are marked as function-specific when the "function claims the TLP". A function claims a TLP in the following cases:

- NT Endpoint function:

- Address Routed TLPs: The TLP address falls within the address space range(s) programmed in the function's base address registers (BARs).

- ID Routed TLPs: The TLP destination ID matches a <u>valid</u> entry in the NT function's mapping table or the NT function's bus/device/function assignment within the PCI Express hierarchy.

- Implicit Route TLPs: Always.

- PCI-to-PCI Bridge function

- DMA function

For a port in Upstream Switch Port with NT Endpoint mode, the TLP is claimed when either one of its two functions claims the TLP.

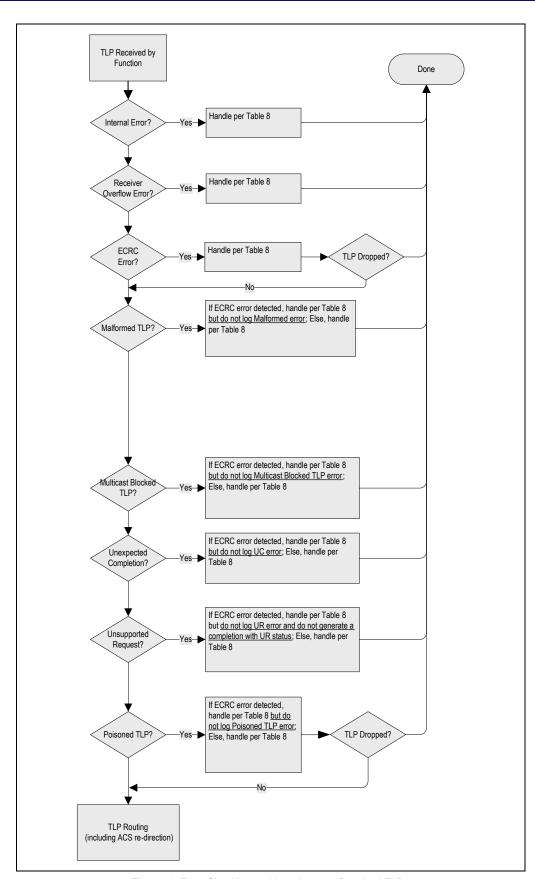

#### **Physical Layer Errors**