A Spice-2 Subcircuit Representation For Power MOSFETs Using Empirical Methods

AN9209 Rev.2.00 October 1, 1999

## Abstract

An accurate power-MOSFET model is not widely available for CAD circuit simulation. This work provides a subcircuit model which is compatible with SPICE-2 software and MOSFET terminal measurements. SPICE-2 is the circuit simulation package of choice for this work because of its universal availability, despite its inherent limitations. These limitations are circumvented through circuit means.

This effort models power-MOSFET terminal behavior consistent with SPICE-2 limitations; hence it will differ from the physical model as suggested by Wheatley, et al<sup>1</sup>, Ronan et al<sup>2</sup> and others. We feel we have advanced prior efforts<sup>3</sup> particularly in areas of third-quadrant operations, avalanche-mode simulation, switching waveforms and diode recovery waveforms.

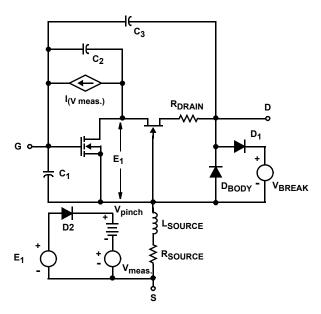

# FIGURE 1. SPICE-2 SUBCIRCUIT FOR POWER MOSFET SIMULATION

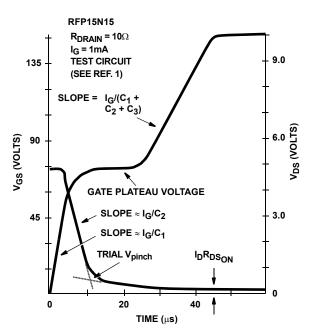

NOTE: If the JFET source voltage, E<sub>1</sub>, is very low relative to its V<sub>PINCH</sub> voltage, the JFET is in a highly conductive state, tightly coupling C<sub>2</sub> to the JFET drain. However, as the voltage E<sub>1</sub> approaches V<sub>PINCH</sub>, the JFET operates in a constant-current mode, thereby permitting a much faster drain slew rate, which is determined primarily by C<sub>3</sub>.

### Discussion

The subcircuit shown in Figure 1 is described in Table 1. All passive circuit elements are constants. The very-high-gain JFET is used to simulate the dual-slope drain voltage vs time switching curve common to the power MOSFET.<sup>1,2</sup>

If E<sub>1</sub> exceeds V<sub>PINCH</sub>, errors will exist in the turn-on waveforms. The C<sub>2</sub> discharge current-controlled current source remedies this situation in conjunction with the subcircuit containing D<sub>2</sub>. The D<sub>2</sub> ideality factor was set at 0.03 to assure that E<sub>1</sub> minus V<sub>PINCH</sub> does not exceed several millivolts.

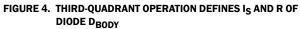

The body diode cannot be properly modeled by the JFET gatedrain diode, hence  $D_{BODY}$ . Conditions of Table 1 assure that most third-quadrant current flow is via  $D_{BODY}$ . Avalanche breakdown is more accurately modeled by the clamp circuit containing  $D_1$ .

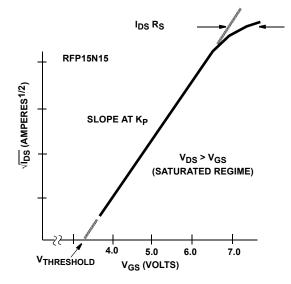

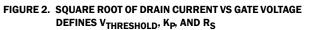

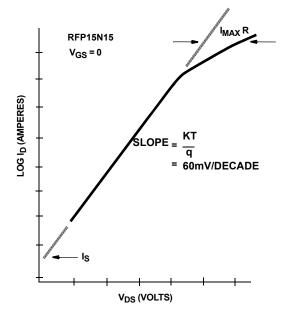

Table 1 in combination with Figures 2, 3, 4 and 5 provides the required empirical inputs. Table 2 lists the preferred algorithm for parameter extraction.

| MOSFET             | Enhancement mode; W = L = 1 $\mu$ m; K <sub>P</sub> (Figure 2); V <sub>TO</sub> (Figure 2); C's = 0; I <sub>DSO</sub> = IE -12                                                                                              |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JFET               | Depletion mode; areas factor = 1; B = $100K_P$<br>(Figure 2); V <sub>TO</sub> = V <sub>PINCH</sub> (Figure 5); C's = diode<br>lifetime = R <sub>SERIES</sub> = 0; diode ideality factor =<br>1.0, I <sub>DSO</sub> = IE -20 |

| BODY DIODE         | $ \begin{array}{l} I_S \mbox{ from Figure 4; Ideality Factor = 1.0; R from } \\ Figure 4 (must be very much greater than R_D); C (from C_{OSS}); lifetime = best fit to T_{RR} \end{array} $                                |

| D <sub>1</sub>     | I <sub>S</sub> = arbitrary; C = lifetime = 0; ideality factor = best low-current fit; R = best high-current fit                                                                                                             |

| D <sub>2</sub>     | I <sub>S</sub> = 1E -8; C = lifetime = R = 0; ideality factor = 0.03                                                                                                                                                        |

| R <sub>S</sub>     | Figure 2.                                                                                                                                                                                                                   |

| R <sub>DRAIN</sub> | Figure 3                                                                                                                                                                                                                    |

| L <sub>S</sub>     | Approximately (5L) In (4 L/d) nH; L and d are source wire inches.                                                                                                                                                           |

| V <sub>PINCH</sub> | V <sub>TO</sub> of JFET.                                                                                                                                                                                                    |

| V <sub>BRK</sub>   | Avalanche voltage.                                                                                                                                                                                                          |

| C1                 | From Figure 5.                                                                                                                                                                                                              |

| C <sub>2</sub>     | Maximum from Figure 5.                                                                                                                                                                                                      |

| C <sub>3</sub>     | Minimum from Figure 5.                                                                                                                                                                                                      |

TABLE 1. EMPIRICAL INPUTS

#### TABLE 2. PREFERRED ALGORITHM FOR PARAMETER EXTRACTION

- 1. Determine K<sub>P</sub> of lateral MOS

- 2. Determine V<sub>TH</sub> of lateral MOS

- 3. Determine C1

- 4. Determine  $C_1 + C_2 + C_3$

- 5. Determine R<sub>DS</sub>

- 6. Assign B of JFET = 100 x K<sub>P</sub> of lateral MOS

- 7. Use trial V<sub>PINCH</sub>

- 8. Use  $C_2$  (Maximum),  $C_3$  (Minimum) are curve-fit C's

- 9. Adjust V<sub>PINCH</sub> to fix gate voltage plateau

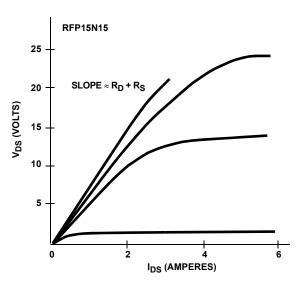

FIGURE 3. DRAIN CURRENT VS DRAIN VOLTAGE WITH CONSTANT GATE VOLTAGE DEFINES "ON" RESISTANCE

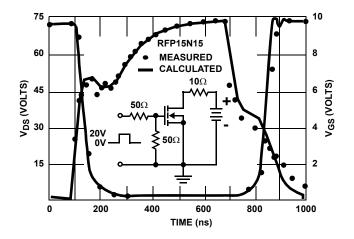

FIGURE 5. DRAIN AND GATE VOLTAGE VS TIME DETERMINE C1, C2, C3 AND VPINCH.

## **Results**

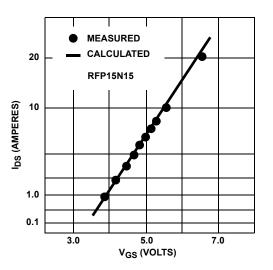

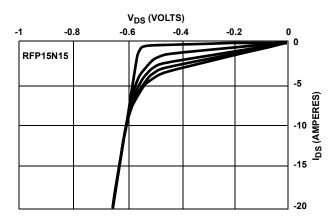

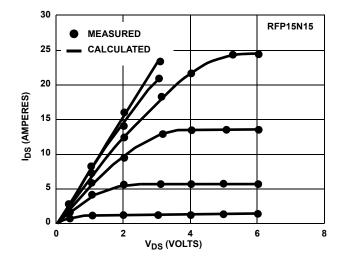

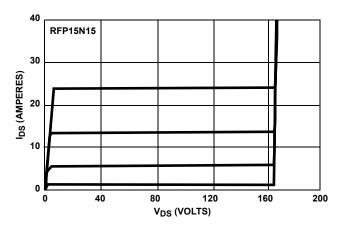

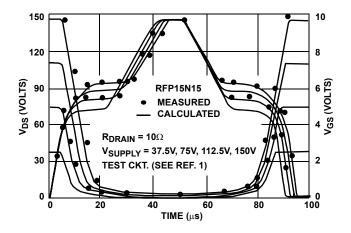

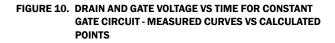

Figure 6 and Figure 7 compare measured static data to calculated transfer curves and output curves. Calculated staticoutput curves are shown in Figure 8 and Figure 9 for thirdquadrant range, including avalanche. Calculated switching data is compared to measured switching curves<sup>1,2</sup> in Figure 10 and Figure 11. Calculated body-diode recovery curves are shown in Figure 12.

FIGURE 6. DRAIN CURRENT VS GATE VOLTAGE (NOTE SQUARE ROOT SCALE) - MEASURED CURVE VS CALCULATED POINTS

FIGURE 8. THIRD-QUADRANT DRAIN CURRENT VS DRAIN VOLTAGE WITH CONSTANT POSITIVE GATE VOLTAGE (CALCULATED)

FIGURE 7. DRAIN CURRENT VS DRAIN VOLTAGE FOR CONSTANT VALUES OF GATE VOLTAGE - MEASURED CURVES VS CALCULATED POINTS

FIGURE 9. FIRST-QUADRANT DRAIN CURRENT VS DRAIN VOLTAGE,  $V_{GS}$  = CONSTANT. NOTE AVALANCHE BREAKDOWN (CALCULATED)

FIGURE 11. DRAIN AND GATE VOLTAGE VS TIME FOR STANDARD SWITCHING CIRCUIT - MEASURED CURVES VS CALCULATED POINTS

#### Conclusion

An equivalent-circuit model for power-MOSFETs, that is suitable for use with the SPICE CAD program, has been demonstrated. The model is compatible with all versions of SPICE presently available without modification to the program's internal code. The model addresses static and dynamic behavior of first and third-quadrant operation, including avalanche breakdown, and is empirical in nature. All necessary input parameters may be inferred from data sheets or simple terminal measurements.

Excellent agreement has been obtained between measured and simulated results.

### References

- Wheatley Jr., C. F. and Ronan Jr., H. R., "Switching Waveforms of the L<sup>2</sup>FET: A 5-Volt Gate-Drive Power MOSFET," Power Electronic Specialists Conference Record, June 1984, p. 238

- [2] Ronan Jr., H. R. and Wheatley Jr., C. F., "Power MOSFET Switching Waveforms: A New Insight," Proceedings of Powercon II, April 1984, p. C-3

- [3] Nienhaus, H. A., Bowers, J. C., and Herren Jr., P. C., "A High Power MOSFET Computer Model," Power Conversion International, January 1982, p 65

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard" Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances; machine tools; personal electronic equipment: industrial robots: etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics oroducts outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Plea e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### **Renesas Electronics Corporation**

http://www.renesas.com

SALES OFFICES Refer to "http://www.renesas.com/" for the latest and detailed information Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Miliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tei: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tei: +822-558-3737, Fax: +822-558-5338