# Application Note DA9313-DA9063: Example Ultrabook/Notebook Power Architecture

**AN-PM-079**

# Abstract

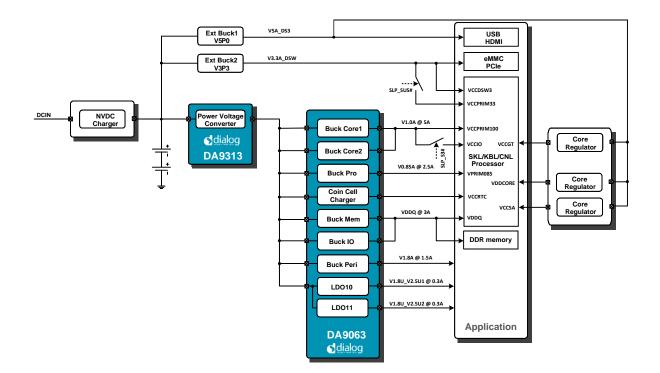

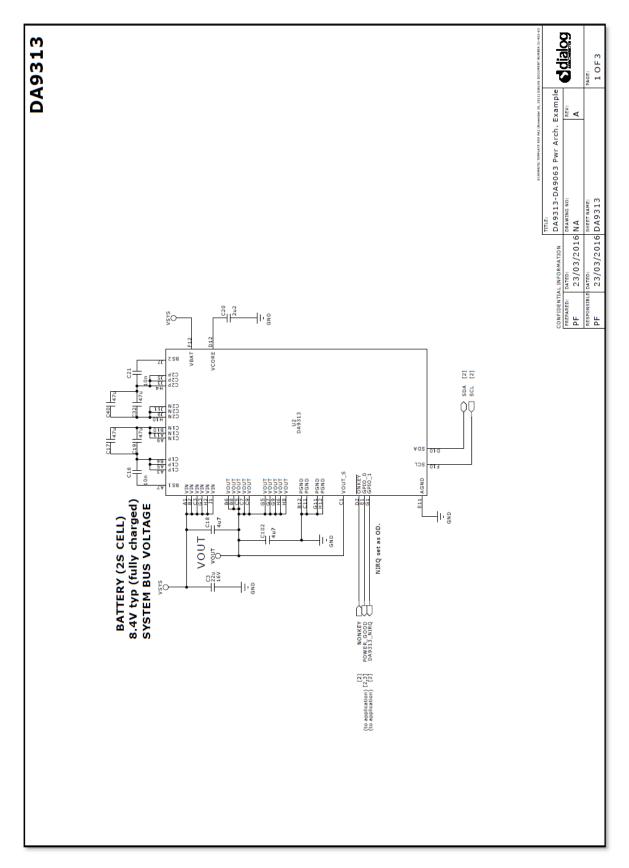

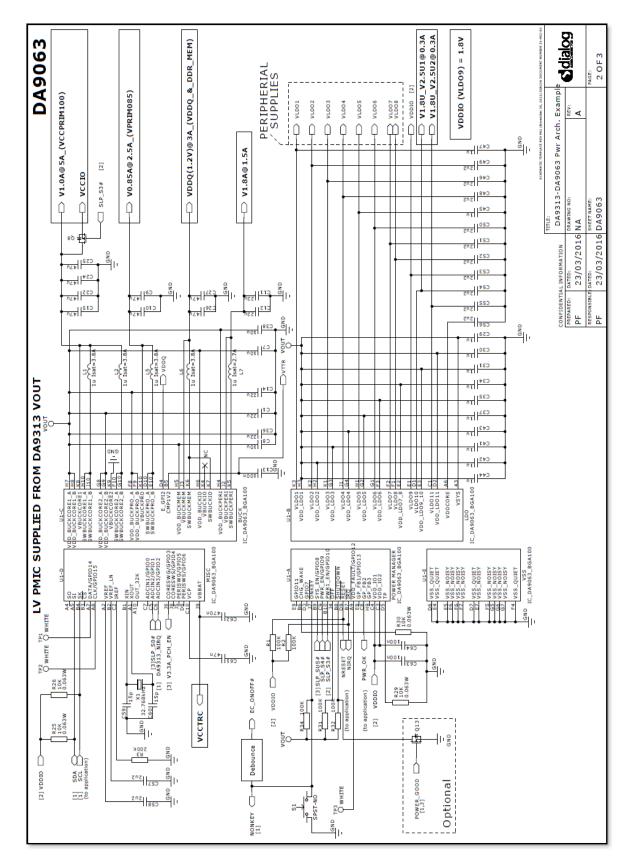

This applications note presents an example of a power architecture design for Ultrabook/Notebook applications operated from a dual cell (2S) stacked Li-ion or Li-polymer battery pack using Dialog Semiconductor's DA9313 converter and DA9063 power management IC.

# DA9313-DA9063: Example Ultrabook/Notebook Power Architecture

# Contents

| Ab  | stract  |                                                      |             |                                                           | 1  |  |  |

|-----|---------|------------------------------------------------------|-------------|-----------------------------------------------------------|----|--|--|

| Co  | ontents |                                                      |             |                                                           | 2  |  |  |

| Fig | gures   |                                                      |             |                                                           | 3  |  |  |

| Та  | bles    |                                                      |             |                                                           | 3  |  |  |

| 1   | Term    | s and De                                             | finitions   |                                                           | 4  |  |  |

| 2   |         |                                                      |             |                                                           |    |  |  |

| 3   |         |                                                      |             |                                                           |    |  |  |

| 4   |         |                                                      |             |                                                           |    |  |  |

| 4   | 4.1     | ROP Support           4.1         Power Distribution |             |                                                           |    |  |  |

|     | 4.2     |                                                      |             |                                                           | -  |  |  |

|     | 1.2     | 4.2.1                                                |             | Controller Supply                                         |    |  |  |

|     |         | 4.2.2                                                |             | ver States                                                |    |  |  |

|     |         | 4.2.3                                                |             | State                                                     |    |  |  |

|     | 4.3     | Low Pow                                              | ver Mode    |                                                           | 9  |  |  |

|     | 4.4     | I <sup>2</sup> C Interf                              | face        |                                                           | 10 |  |  |

|     | 4.5     | nIRQ                                                 |             |                                                           | 10 |  |  |

|     | 4.6     | Power B                                              | utton       |                                                           | 10 |  |  |

|     |         | 4.6.1                                                | Short Pres  | 3S                                                        | 11 |  |  |

|     |         |                                                      | 4.6.1.1     | Short Press Operation Signal Description                  | 11 |  |  |

|     |         | 4.6.2                                                | Long Pres   | s (Cold Off)                                              |    |  |  |

|     |         |                                                      | 4.6.2.1     | Long Press (Cold Off) Operation Signal Sequence           |    |  |  |

|     |         | 4.6.3                                                | 0           | s (Emergency Reset)                                       |    |  |  |

|     |         |                                                      | 4.6.3.1     | Long Press (Emergency Reset) Operation Signal Description |    |  |  |

|     | 4.7     |                                                      |             | <b>•</b>                                                  |    |  |  |

|     |         | 4.7.1                                                |             | Shutdown                                                  |    |  |  |

|     |         | 4.7.2                                                | •           | Shutdown                                                  |    |  |  |

|     |         | 4.7.3                                                |             | Reset Source                                              |    |  |  |

|     |         | 4.7.4                                                | 4.7.4.1     | ld Off<br>Critical Temperature                            |    |  |  |

|     |         |                                                      |             | Other Reset Sources                                       |    |  |  |

|     | 4.8     | Rail Con                                             |             | Other Reset Gources                                       |    |  |  |

|     | 4.9     |                                                      |             | S                                                         |    |  |  |

|     |         | 4.9.1                                                | 0           | ower Good                                                 |    |  |  |

|     |         | 4.9.2                                                | •           | PWRGD Generation                                          |    |  |  |

|     |         | 4.9.3                                                |             |                                                           |    |  |  |

|     |         |                                                      | Generation  | n                                                         | 17 |  |  |

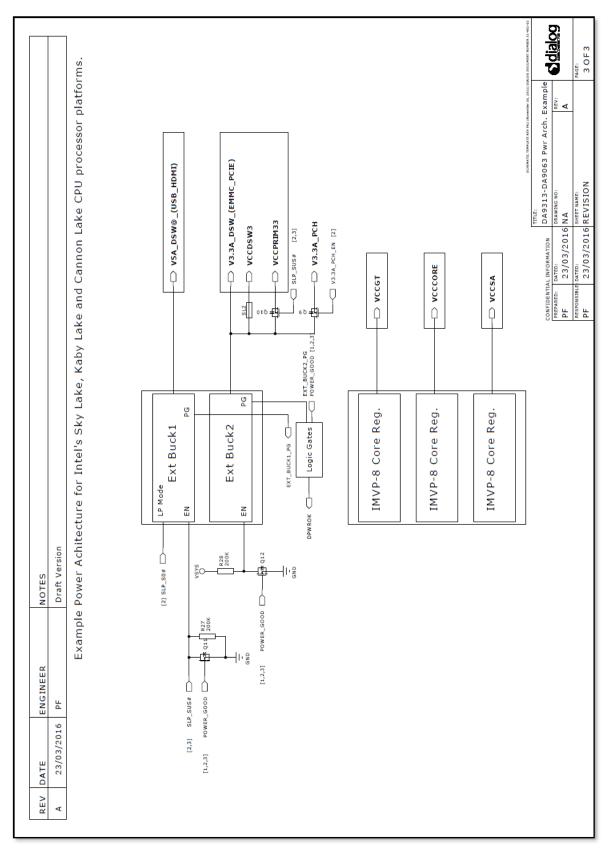

| 5   | Exam    | ple Powe                                             | er Architec | ture Schematic                                            | 19 |  |  |

| 6   | Exam    | ple Powe                                             | er Architec | ture BOM                                                  | 23 |  |  |

| 7   | Platfo  | orm Flow                                             | Diagrams    |                                                           | 25 |  |  |

| Re  |         |                                                      | -           |                                                           |    |  |  |

| -   |         | · · · ·                                              |             |                                                           | -  |  |  |

# **Figures**

| Figure 1: Power Architecture Block Diagram                | . 5 |

|-----------------------------------------------------------|-----|

| Figure 2: Main Signals Between DA9313, DA9063, PCH and EC | . 6 |

| Figure 3: DA9063 Sequencer                                | . 8 |

| Figure 4: Short Press Timing                              | 11  |

| Figure 5: Long Press (Cold Off) Timing                    | 12  |

| Figure 6: Long Press (Emergency Reset) Timing             | 13  |

| Figure 7: Power-Up from Cold Boot to S0                   | 15  |

| Figure 8: RSMRST#_PWRGD Signal Generation                 | 17  |

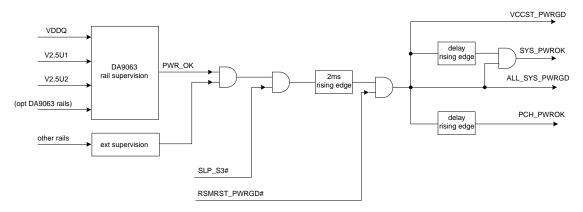

| Figure 9: Power Good Signals Generation                   | 17  |

| Figure 10: Example Power Architecture Schematic           |     |

| Figure 11: SKL U/Y (Volume Segment) Flow Diagram          | 25  |

| Figure 12: SKL U/Y (Premium Segment) Flow Diagram         |     |

| Figure 13: KBL U/Y (Volume Segment) Flow Diagram          | 27  |

| Figure 14: KBL (Premium Segment) Flow Diagram             | 28  |

# **Tables**

| Table 1: RESET (0x99)                                      | 9  |

|------------------------------------------------------------|----|

| Table 2: BMEM_CONF (0xA1)                                  | 10 |

| Table 3: VBMEM_B (0xB7)                                    | 10 |

| Table 4: Power Up from Cold Boot to S0 Signal Descriptions | 16 |

| Table 5: ADC Channel Assignment                            | 17 |

| Table 6: DA9313 BOM                                        | 23 |

| Table 7: DA9063 BOM                                        | 24 |

# DA9313-DA9063: Example Ultrabook/Notebook Power Architecture

# **1** Terms and Definitions

| BOM<br>DPWROK<br>EC<br>HV<br>IC<br>LV<br>NVDC<br>MCP<br>PCB<br>PCH<br>PCH<br>PFM<br>PG<br>PMIC | Bill of Materials<br>Delayed Power OK<br>Embedded Controller<br>High Voltage<br>Integrated Circuit<br>Low Voltage<br>Narrow Voltage DC/DC<br>Media Communication Processor<br>Printed Circuit Board<br>Platform Controller Hub<br>Pulse Frequency Modulation<br>Power Good |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                |                                                                                                                                                                                                                                                                            |

| PMIC<br>PVC<br>ROP                                                                             | Power Management IC<br>Power Voltage Converter<br>Rest of Platform                                                                                                                                                                                                         |

# 2 References

- [1] DA9313-Datasheet, Dialog Semiconductor

- [2] DA9063-Datasheet, Dialog Semiconductor

# 3 Introduction

The purpose of this application note is to provide an example power architecture design for Ultrabook/Notebook (using Intel<sup>®</sup>'s Core<sup>™</sup> and Xeon<sup>®</sup> (formerly Skylake (SKL)), Kaby Lake (KNL) or Cannonlake (CNL) processors) applications.

Dialog Semiconductor's DA9313 converter can be used to provide the system bus voltage from a dual cell (2S) stacked Li-ion or Li-polymer battery pack (5.4 V to 8.7 V). Additionally, Dialog Semiconductor's DA9063 LV PMIC can be used to power up the power rails of the rest of platform (ROP), see Figure 1.

#### NOTE

This example power architecture includes a narrow voltage DC/DC (NVDC) charger, two external buck regulators (Ext Buck1 and Ext Buck2) and some IMVP8<sup>™</sup> core regulators available from third parties. Their operation is not described in this document.

| An      | plic | atio | on N | lote |

|---------|------|------|------|------|

| · · · · | P 4  |      |      |      |

# 4 **ROP Support**

This section describes how to combine and connect Dialog's DA9313 converter and DA9063 PMIC to support the Intel requirements for the ROP in a typical application.

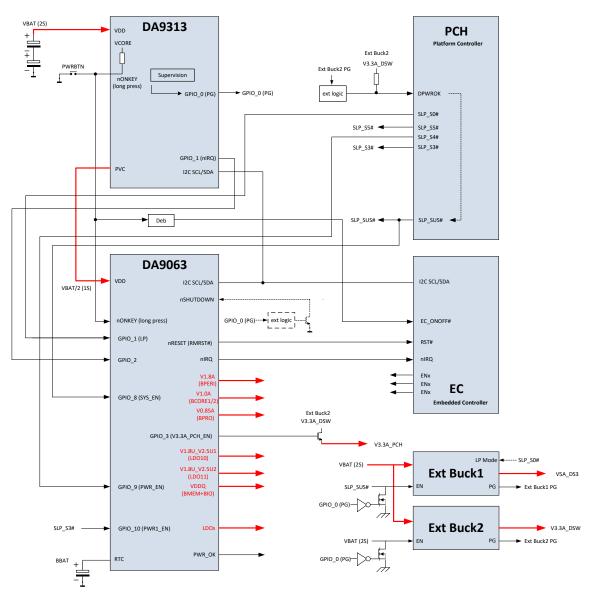

Figure 2 shows how to connect some of the most relevant signals on the platform. The red arrows indicate power rails.

# 4.1 **Power Distribution**

A dual stacked Li-ion battery or an NVDC charger can fully power the system. Alternatively, the system can be powered using a combination of both. Therefore the actual input voltage of the system can vary between 6 V and 8.4 V.

To comply with the maximum supply voltage for the DA9063 (5.5 V), the system input voltage is halved by the DA9313 power voltage converter (PVC). The PVC rail is enabled in DA9313 by configuring  $PVC_EN = 1$  and AUTOBOOT = 1. The PVC rail will remain enabled providing the input

| pplication Note | Revision 1.2 | 23-Feb-2022 |

|-----------------|--------------|-------------|

voltage is higher than the configurable under-voltage lockout (UVLO) threshold ( $V_{BAT_UV_CRIT}$  setting) of DA9313. To reduce the power dissipation, the automatic frequency mode of the DA9313 PVC should be configured by setting PVC\_MODE = 1.

The DA9063 has AUTOBOOT = 1, therefore the DA9063 will initiate a power-up sequence as soon as the DA9313 PVC rail is up.

# 4.2 Rail Control

# 4.2.1 Platform Controller Supply

The platform controller hub (PCH) is supplied by the (always on) V3.3\_DSW rail, except when fault conditions occur and a power cycle is needed. V3.3\_DSW is enabled when the battery is present and disabled when the DA9313 power good (PG) is de-asserted. This rail is supported by an external buck regulator called Ext Buck2.

The output voltage is monitored and combined with the necessary signals, including the PG of the DA9313, to output the delayed power good signal (DPWROK) to the PCH.

# 4.2.2 S4/S5 Power States

After the assertion of SLP\_SUS# from the PCH, the S4 (Suspend to Disk) or S5 (Soft Off) state is entered.

SLP\_SUS# is connected to the enable pin of Ext Buck1, which is configured as V5A\_DS3. The main purpose of Ext Buck1 is to supply the IMVP8 core regulators.As a result, V5A\_DS3 is turned on as soon as the SLP\_SUS# is asserted.

#### NOTE

Ext Buck1 can be disabled when the DA9313 PG is de-asserted.

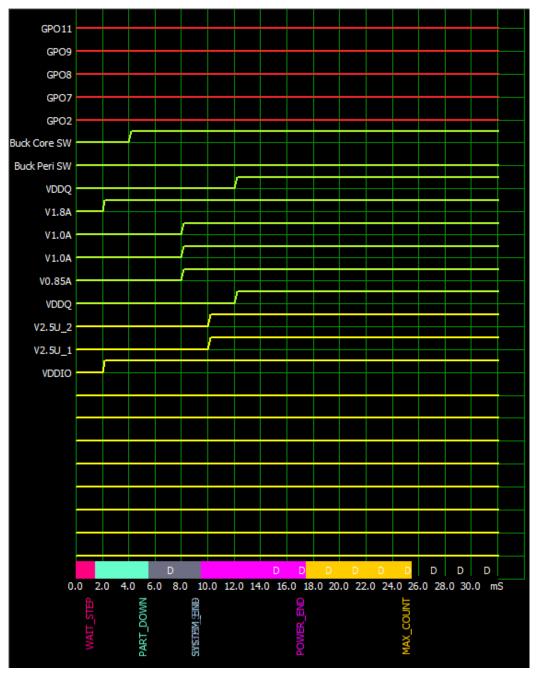

The SLP\_SUS# port is also connected to GPIO\_8 (SYS\_EN) on DA9063. This starts a power-up sequence which ends on completion of domain SYSTEM (SYSTEM\_END slot) in DA9063. Rails can be individually assigned to a dedicated slot of the sequencer, as shown in Figure 3.

**Application Note**

Figure 3: DA9063 Sequencer

To fulfil the start-up requirements for ROP, the V1.8A rail is assigned to slot 1, the V3.3A\_PCH\_EN is assigned to slot 2 (shown as Buck Core SW in Figure 3), a delay slot is assigned to slot 3 and the V1.0A rail is assigned to slot 4 (possibly together with V0.85V when the rail is present).

GPIO\_3 of DA9063 is used as a sequence controlled output port (called CORE\_SWG), to enable an external FET for the generation of the V3.3A\_PCH rail. This is easily implemented via the rail switch implementation of DA9063.

At the end of the domain SYSTEM the nRESET port of DA9063 is released as needed for RSMRST#.

| Application Note | Revision 1.2 |

|------------------|--------------|

| Application Note |              |

### Table 1: RESET (0x99)

| Bit | Туре | Label       | Default | Description                                                                                                                                                                                                                                                                                                                   |

|-----|------|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | R/W  | RESET_EVENT | 01      | RESET timer started by<br>00: EXT_WAKEUP<br>01: SYS_UP<br>10: PWR_UP<br>11: leaving PMIC RESET state (do not use in<br>combination with nRES_MODE = 1)                                                                                                                                                                        |

| 5:0 | R/W  | RESET_TIMER | 000101  | 000000: 0.000 ms<br>000001: 1.024 ms<br>000010: 2.048 ms<br>000010: 2.048 ms<br>000100: 4.096 ms<br>000100: 4.096 ms<br>000101: 5.120 ms<br><br>011110: 30.720 ms<br>011111: 31.744 ms<br>100000: 32.768 ms<br>100001: 65.536 ms<br>100001: 98.304 ms<br><br>111101: 983.040 ms<br>111110: 1015.808 ms<br>111111: 1048.576 ms |

### 4.2.3 S0 Power State

The transition from S4/S5 to S0 (Working) state is driven by the PCH through SLP\_S3#, SLP\_S4# and SLP\_S5#.

SLP\_S4# is connected to GPIO\_9 (PWR\_EN) on DA9063. This continues the power-up sequencing up to POWER\_END, as shown in Figure 3. V1.8U\_V2.5U1 and V1.8U\_V2.5U2 are assigned to slot 5; VDDQ is assigned to slot 6.

SLP\_S3# is connected to GPIO\_10 (PWR1\_EN) on DA9063. This can be used to enable other LDOs on DA9063 after having assigned them to a sequencer slot.

SLP\_S5# is generally used to shut power off to all non-critical systems when in the S5 (Soft Off) states. Though in this example power architecture, SLP\_S5# is not used by the DA9313 or the DA9063.

### 4.3 Low Power Mode

SLP\_S0# is a platform level low power mode indicator that is set low to send the system into connected standby mode.

To save power, connect SLP\_S0# to Ext Buck1 (V5A) LP mode. This sets Ext Buck1 into pulse frequency modulation (PFM) mode. If this connection is not possible the operating mode should be configured by  $l^2C$ .

DA9063 GPIO\_1 is also connected to SLP\_S0# and controls the operation of V1.0A and VDDQ. The B-registers are selected depending on the GPIO\_1 level (active high for normal operation and active low for standby).

# DA9313-DA9063: Example Ultrabook/Notebook Power Architecture

The LP voltage of the regulators can be configured in VBCORE1\_B and VBMEM\_B, whilst the operation is set to PFM mode if BCORE1\_SL\_B = 1, BMEM\_SL\_B = 1 and BCORE1\_MODE = 00, BMEM\_MODE\_ 00.

#### Table 2: BMEM\_CONF (0xA1)

| Bit | Туре | Label      | Default | Description                                                                                                                                                                                                                                         |  |

|-----|------|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:6 | R/W  | BMEM_ MODE | 00      | <ul> <li>00: Sleep/Synchronous mode controlled via voltage A and B registers</li> <li>01: BUCKMEM always operates in Sleep Mode</li> <li>10: BUCKMEM always operates in Synchronous Mode</li> <li>11: BUCKMEM operates in Automatic Mode</li> </ul> |  |

#### Table 3: VBMEM\_B (0xB7)

| Bit | Туре | Label     | Default | Description                                                                                                                                                  |  |

|-----|------|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | R/W  | BMEM_SL_B | 1       | 0: Configures BUCKMEM to Synchronous mode, when<br>selecting B voltage settings<br>1: Configures BUCKMEM to Sleep mode, when selecting B<br>voltage settings |  |

### 4.4 I<sup>2</sup>C Interface

The embedded controller (EC) can communicate via I<sup>2</sup>C with DA9313 and DA9063. The lines are pulled up to the 3.3 V rail generated from the always on V3.3A\_DSW.

# 4.5 nIRQ

DA9313 GPIO\_1 is configured as nIRQ and is connected to DA9063 GPIO\_2, (configured as input). Therefore, any DA9313 interrupt is directly passed to the EC via the DA9063 nIRQ pin.

### 4.6 **Power Button**

The power button (PWRBTN) connects to DA9313 and DA9063 and has an internal pull-up to VCORE.

For both devices only the long press functionality for emergency reset is used. This is enabled when the press time is longer than KEY\_DELAY + SHUT\_DELAY. The system is power cycled and both devices are reset.

After a long nONKEY press, DA9313 and DA9063 will initially only assert control bit E\_KEY\_RESET in the fault register and signal a non-maskable interrupt allowing the host to clear the armed reset sequence within 1 s. If the host does not clear E\_KEY\_RESET a power cycle is initiated.

The short press detection is managed by the EC and the PCH. A debounced version of the signal is needed. This function must be implemented externally using an additional circuit.

#### NOTE

In SHELF mode (that is DA9313 POWER-DOWN state), the whole supply chain is unpowered therefore no nONKEY can be captured by the DA9063. In this case, a special feature is available in the DA9313 that automatically pulls down the nONKEY briefly to allow the DA9063 to wake up. The nONKEY is de-asserted after a small delay.

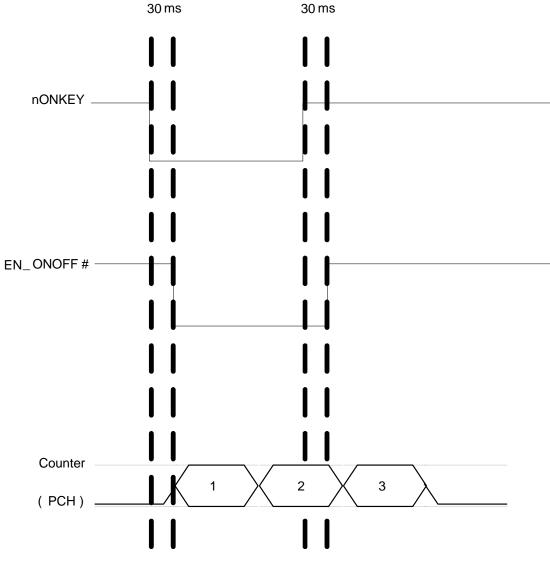

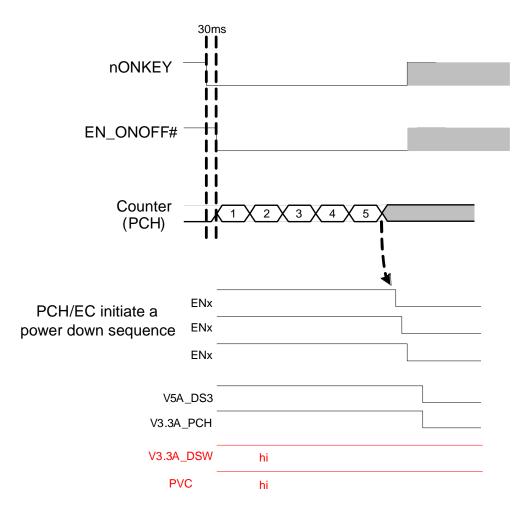

# 4.6.1 Short Press

### Figure 4: Short Press Timing

### 4.6.1.1 Short Press Operation Signal Description

- The nONKEY press is debounced by an external circuitry.

- The EC communicates to the PCH which initiates a counter.

- If the counter elapses before 5 s, the PCH knows it is a short press.

| -  |       | _    |      |

|----|-------|------|------|

| Δn | nlica | tion | Note |

| ΠP | piica |      | NOLE |

# 4.6.2 Long Press (Cold Off)

#### Figure 5: Long Press (Cold Off) Timing

#### 4.6.2.1 Long Press (Cold Off) Operation Signal Sequence

- The nONKEY press is debounced by an external device.

- The EC communicates to the PCH which initiates a counter.

- The counter reaches 5 s so the PCH knows it is a long press.

- The PCH initiates a cold off sequence.

- All rails are shut down, except the V3.3A\_DSW from Ext Buck2 and the PVC.

- The PVC must be kept on in order to supply the LV PMIC:

- Allows the nONKEY detection to wake up.

- $\circ$  Allows supplying the RTC from the main V<sub>BAT</sub> instead of from the backup battery.

|    |           |       | -   |      |

|----|-----------|-------|-----|------|

| Λ. | nn        | licat | ion | Note |

|    | <b>JP</b> | πυαι  |     | NULE |

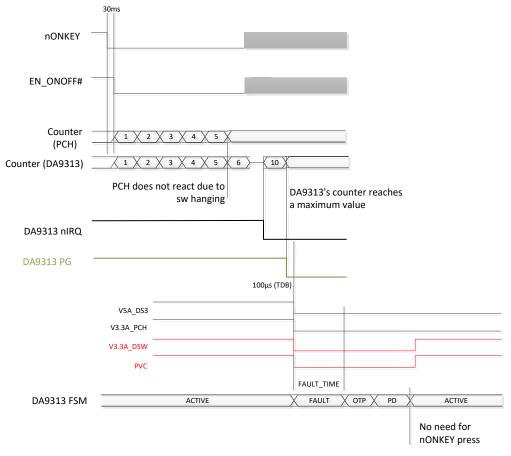

### 4.6.3 Long Press (Emergency Reset)

#### Figure 6: Long Press (Emergency Reset) Timing

#### 4.6.3.1 Long Press (Emergency Reset) Operation Signal Description

- The nONKEY press is debounced by an external device.

- The EC communicates to the PCH which initiates a counter.

- The counter reaches 5 s but the PCH does not react, due to for example hanging software.

- DA9313 and DA9063 have an internal counter (long press). When reaching the long press time they generate an IRQ and wait 1 s for the host processor to clear the KEY\_RESET event.

- If the event is not cleared, DA9313 de-asserts PG (power cycle indicator function) to signal the host, the DA9063 and Ext Buck1 / Ext Buck2 that it is shutting down 10 µs (configurable) after PG is de-asserted.

- DA9313 and DA9063 will wait a FAULT\_TIME before powering up again, so that the external capacitors of the PVC / buck / LDO rails can be discharged in a clean way.

# 4.7 Shutdown Source

### 4.7.1 Firmware Shutdown

When a force shutdown is initiated by the processor, this is done via an I<sup>2</sup>C write on DA9313 SOFTRESET bit. DA9313 is power cycled and consequently all devices connected to the PVC are power cycled as well.

The DA9313 PG signal is de-asserted at the beginning of the power cycle causing Ext Buck1 and Ext Buck2 to switch off and the system to shut down.

#### 4.7.2 Surprise Shutdown

A surprise shutdown could be caused by an unexpected power loss, an over-temperature or a VR fault.

If an input under-voltage or a critical over-temperature condition happens to DA9313, it is power cycled and consequently all devices connected to the PVC are power cycled as well. DA9313 PG signal is de-asserted and after 10 µs (configurable) it begins a power cycle.

If the failure happens at DA9063, it initiates a power-down sequence. In this case the DPWROK signal is released during the power-down sequence.

### 4.7.3 Store the Reset Source

When the system recovers and powers up after a failure, both devices will have logged the reason for the failure. This is supported in the DA9313 even in the case of the main battery being removed because the information should be mirrored in a domain supplied by the backup battery. So an event will be generated after recovery and even after battery re-insertion.

#### NOTE

On DA9063 the backup battery does not supply the FAULT\_LOG register, which contains information on the reason of the specific failure. So the main battery is needed to store this information.

### 4.7.4 Forced Cold Off

A forced cold off (FCO) can be actioned via the power button. In this case DA9313 must initiate the power-down sequence slightly ahead of DA9063. Before the DA9313 initiates a power-down sequence, it de-asserts the PG 1 s before bringing down the PVC rail so that the host can be warned of an imminent power-down event and act upon it.

The cause of the power-down event is stored in DA9313's FAULT\_LOG register. The long press duration of the power button can be programmed on both DA9313 and DA9063.

#### 4.7.4.1 Critical Temperature

The critical temperature (CRITTEMP) bit in the FAULT\_LOG of both DA9313 and DA9063, indicates which device has generated a shutdown due to over-temperature.

#### 4.7.4.2 Other Reset Sources

There are additional failure sources supported by DA9313 and DA9063; for example an undervoltage condition at  $V_{BAT}$  or a permanent short circuit at the PVC output. For these conditions, the DA9313 initiates a shutdown of the PVC rail. The related fault cause is stored in the FAULT\_LOG register.

# 4.8 Rail Control

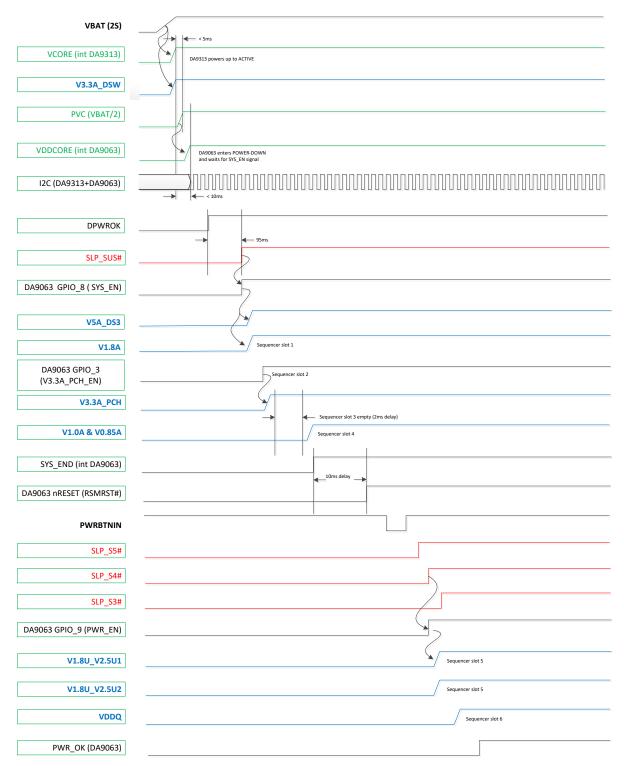

Figure 7 shows the power-up of the platform to S0. The green signals are internal rails; the blue signals are platform rails. Signals coming from the EC and PCH are red.

### Figure 7: Power-Up from Cold Boot to S0

| Application Note | Revision 1.2 | 23-Feb-2022                |

|------------------|--------------|----------------------------|

| CFR0014          | 15 of 31     | © 2022 Renesas Electronics |

| Signal                         | Description                                                                                                                                                                              |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DPWROK                         | A delayed V3.3A_DSW_PG signal from the Ext Buck2.                                                                                                                                        |  |

| SLP_SUS#                       | PCH sleep control signal output that allows for entering S4 or S5 state.                                                                                                                 |  |

| V5AEN/SYS_EN                   | An input signal from the host processor to the DA9063 that enables the regulators in domain SYSTEM. The feature is enabled using GPIO8.                                                  |  |

| V3.3V_PCH_EN                   | Enables the 3.3 V line switch, via DA9063 GPIO_3, that connects the Ext Buck2 output to the PCH.                                                                                         |  |

| SYS_END<br>(SYSTEM_END)        | Internal to DA9063, indicates that the last supply of domain SYSTEM has been reached.                                                                                                    |  |

| RSMRST#                        | Connected to DA9063's nRESET pin to tell the host to enter the reset state.                                                                                                              |  |

| PWRBTNIN                       | Power button input signal.                                                                                                                                                               |  |

| SLP_S3#,<br>SLP_S4#<br>SLP_S5# | Used by the PCH to enable some voltage regulators to enter the S0 state.                                                                                                                 |  |

| PWR_EN                         | An input signal from the host processor to the DA9063. It is used to trigger a wake-up event from POWER-DOWN mode to continue the power-up sequence. The feature is enabled using GPI09. |  |

| PWR_OK                         | A regulator status indicator from DA9063. It is asserted if none of the selected DA9063 regulators are out-of-range. The feature is outputted on GP_FB2.                                 |  |

#### Table 4: Power Up from Cold Boot to S0 Signal Descriptions

# 4.9 Power Good Signals

The DA9313 and DA9063 with an external circuit fully meet the requirements for the PG generation.

### 4.9.1 Delayed Power Good

The delayed power good signal (DPWROK) of the Ext Buck2 regulator (that is V3.3V\_DSW power domain) that can be generated using a few logic gates externally. DPWORK must be asserted no earlier than 10 ms after the V3.3A\_DSW rail is valid, and it must immediately de-assert without any delay if  $V_{BAT} \leq 5.4$  V.

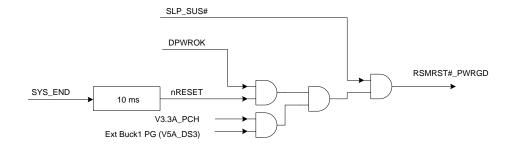

#### 4.9.2 **RSMRST#\_PWRGD** Generation

This is supported by the nRESET signal of DA9063. The actual voltages are not actively monitored, but at the end of the power-up sequence the nRESET signal is released. It relies on sequencing information rather than on actual voltage power good. If active monitoring is needed, an external supervision and logic should be added.

A few logic gates are externally required, see Figure 8.

#### Figure 8: RSMRST#\_PWRGD Signal Generation

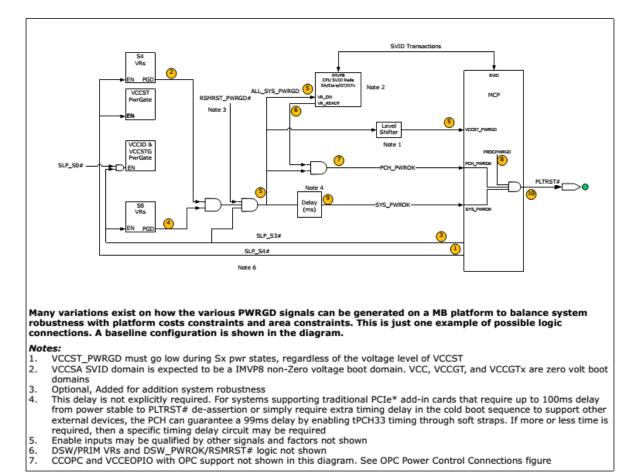

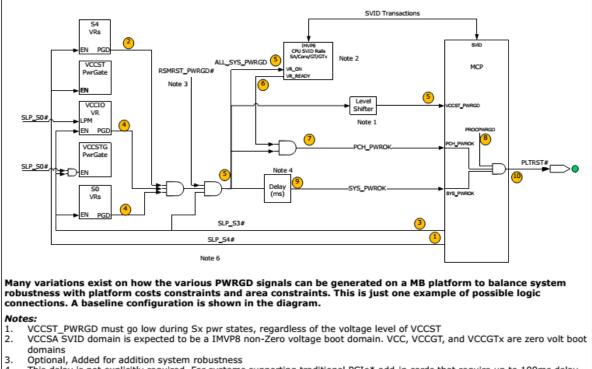

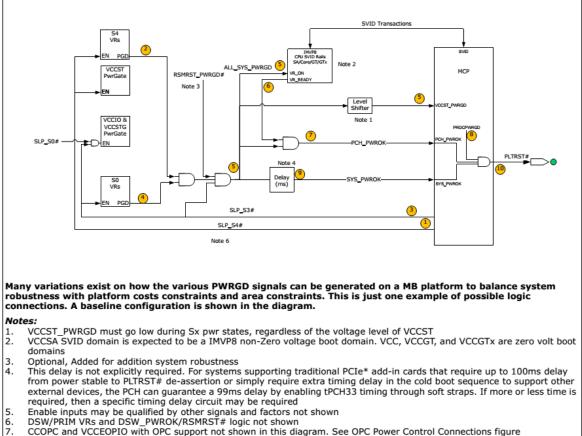

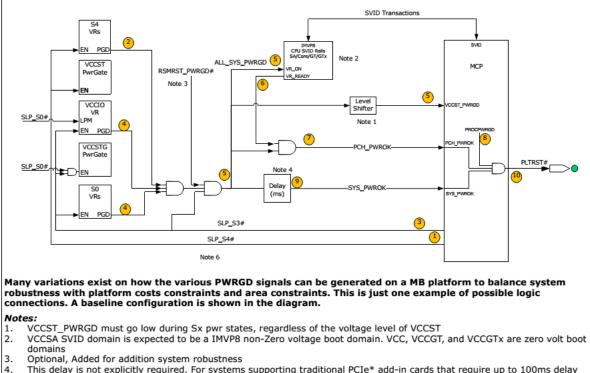

### 4.9.3 VCCST\_PWRGD, SYS\_PWROK, ALL\_SYS\_PWRGD, PCH\_PWROK Generation

The PWR\_OK configurable output port on the DA9063 generates a subset of the signals. An additional external supervision is necessary along with a few external logic blocks, see Figure 9.

#### **Figure 9: Power Good Signals Generation**

An embedded ADC in the DA9063 monitors the VDDQ, V1.8U\_V2.5U1 and V1.8U\_V2.5U2 rails (and optionally DA9063 generated rails such as V1.8A and V1.00A) by using channels 8, 9, and 10 of the ADC scheduler. The monitoring can be enabled individually on each regulator resulting in the output signal PWR\_OK, providing all rails are powered.

| Table 5: | ADC | Channel | Assignment |

|----------|-----|---------|------------|

|----------|-----|---------|------------|

| ADC Channel      | Regulator                                                  | Enable                                                                                      |

|------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| A8               | BUCKCORE1<br>BUCKCORE2<br>BUCKPRO<br>LDO3<br>LDO4<br>LDO11 | BCORE1_MON_EN<br>BCORE2_MON_EN<br>BPRO_MON_EN<br>LDO3_MON_EN<br>LDO4_MON_EN<br>LDO11_MON_EN |

| A9               | BUCKIO<br>BUCKMEM<br>BUCKPERI<br>LDO1<br>LDO2<br>LDO5      | BIO_MON_EN<br>BMEM_MON_EN<br>BPERI_MON_EN<br>LDO1_MON_EN<br>LDO2_MON_EN<br>LDO5_MON_EN      |

| A10              | LDO6<br>LDO7                                               | LDO6_MON_EN<br>LDO7_MON_EN                                                                  |

| Application Note | Povicion 1.2                                               | 22 Ech 2022                                                                                 |

**Application Note**

**Revision 1.2**

| LDO8  | LDO8_MON_EN  |

|-------|--------------|

| LDO9  | LDO9_MON_EN  |

| LDO10 | LDO10_MON_EN |

5 Example Power Architecture Schematic

# DA9313-DA9063: Example Ultrabook/Notebook Power Architecture

# DA9313-DA9063: Example Ultrabook/Notebook Power Architecture

# Figure 10: Example Power Architecture Schematic

| Application No | te |

|----------------|----|

# DA9313-DA9063: Example Ultrabook/Notebook Power Architecture

# 6 Example Power Architecture BOM

# Table 6: DA9313 BOM

| Ref Des            | Value  | Description             | Mfr    | Part Number        | Qty |

|--------------------|--------|-------------------------|--------|--------------------|-----|

| U2                 | DA9313 |                         | Dialog | DA9313             | 1   |

| C3                 | 22 µF  | 0805 16V JB capacitor   | TDK    | C2012JB1C226M085AC | 1   |

| C18, C102          | 4.7 µF | 0402 10V X5R capacitor  | Murata | GRM155R61A475MEAA  | 2   |

| C20                | 2.2 µF | 0402 16V X5R capacitor  | Murata | GRM155R61C225KE11  | 1   |

| C16, C21           | 10 nF  | 0201 10V X7R capacitor  | Murata | GRM033R71A103KA01D | 2   |

| C17, C19, C32, C40 | 47 µF  | 0603 6.3V X5R capacitor | Murata | GRM188R60J476ME15  | 4   |

# DA9313-DA9063: Example Ultrabook/Notebook Power Architecture

# Table 7: DA9063 BOM

| Ref Des                                                             | Value      | Description                       | Mfr              | Part Number                      | Qty |

|---------------------------------------------------------------------|------------|-----------------------------------|------------------|----------------------------------|-----|

| U1                                                                  | DA9063     |                                   | Dialog           | DA9063                           | 1   |

| L1, L2, L5, L6                                                      | 1 µH       | DFE252012 series<br>SMD inductor  | Murata-Toko      | 1239AS-H-1R0M                    | 4   |

| L7                                                                  | 1 µH       | DFE201610 series<br>SMD inductor  | Murata-Toko      | 1285AS-H-1R0N                    | 1   |

| C9, C10, C15, C22,<br>C24, C25, C26,<br>C27                         | 47 μF      | 0805 6.3V X5R<br>capacitor        | Murata           | GRM21BR60J476M#                  | 8   |

| C11, C12                                                            | 22 µF      | 0603 6.3V X5R<br>capacitor        | ТДК              | C1608X5R0J226M080AC#             | 2   |

| C1, C14, C36                                                        | 22 µF      | 0805 10V X5R<br>capacitor         | Taiyo Yuden      | LMK212BJ226MG-T#                 | 3   |

| C7, C8, C38                                                         | 10 µF      | 0805 10V X7R<br>capacitor         | Murata           | GRM21BR71A106KE51L#              | 3   |

| C13, C63, C64                                                       | 100 nF     | 0402 10V X5R<br>capacitor         | Murata           | GRM155R61A104KA01D#              | 3   |

| R25, R26, R29,<br>R30                                               | 10 kΩ      | 0402 resistor                     | Yageo            | RC0402FR-0710KL                  | 4   |

| C57, C58, C46,<br>C48, C49, C50,<br>C51, C52, C53,<br>C54, C55, C56 | 2.2 µF     | 0402 6.3V X5R<br>capacitor        | Kemet            | C0402C225M9PACTU#                | 12  |

| R3                                                                  | 200 kΩ     | 0402 resistor                     | Yageo            | RC0402FR-07200KL#                | 1   |

| C59, C60                                                            | 15 pF      | 0402 COG capacitor                | Murata           | GRM1555C1H150JZ01D#              | 2   |

| X1                                                                  | 32.768 kHz | XTAL 32.768kHz<br>9.0pF SM FC-135 | EPSON<br>TOYOCOM | FC-135 32.768KHZ<br>20PPM,9.0PF# | 1   |

| C61                                                                 | 47 nF      | 0402 10V X5R<br>capacitor         | Murata           | GRM155R61A473KA01D#              | 1   |

| C62                                                                 | 470 nF     | 0402 10V X5R<br>capacitor         | Murata           | GRM155R61A474KE15D#              | 1   |

| R1, R2, R31, R32,<br>R34                                            | 100 kΩ     | 0404 resistor                     | Yageo            | RC0402FR-07100KL#                | 5   |

| C29, C30, C31,<br>C34, C35, C37,<br>C41, C43, C42,<br>C44, C45, C47 | 1 μF       | 0402 10V X5R<br>capacitor         | Murata           | GRM155R61A105KE15D#              | 12  |

# 7 Platform Flow Diagrams

Figure 11: SKL U/Y (Volume Segment) Flow Diagram

**Application Note**

This delay is not explicitly required. For systems supporting traditional PCIe\* add-in cards that require up to 100ms delay from power stable to PLTRST# de-assertion or simply require extra timing delay in the cold boot sequence to support other external devices, the PCH can guarantee a 99ms delay by enabling tPCH33 timing through soft straps. If more or less time is 4. required, then a specific timing delay circuit may be required

- 5.

- 6. 7.

- Enable inputs may be qualified by other signals and factors not shown DSW/PRIM VRs and DSW\_PWROK/RSMRST# logic not shown CCOPC and VCCEOPIO with OPC support not shown in this diagram. See OPC Power Control Connections figure

Figure 12: SKL U/Y (Premium Segment) Flow Diagram

CCOPC and VCCEOPIO with OPC support not shown in this diagram. See OPC Power Control Connections figure

**Application Note**

This delay is not explicitly required. For systems supporting traditional PCIe\* add-in cards that require up to 100ms delay from power stable to PLTRST# de-assertion or simply require extra timing delay in the cold boot sequence to support other external devices, the PCH can guarantee a 99ms delay by enabling tPCH33 timing through soft straps. If more or less time is required, then a specific timing delay circuit may be required Enable inputs may be qualified by other signals and factors not shown DSW/PRIM VRs and DSW\_PWROK/RSMRST# logic not shown CCOPC and VCCEOPIO with OPC support not shown in this diagram. See OPC Power Control Connections figure

- 5.

- 6. 7.

#### Figure 14: KBL (Premium Segment) Flow Diagram

# **Revision History**

| Revision | Date        | Description                    |

|----------|-------------|--------------------------------|

| 1.0      | 06-Apr-2016 | Initial release                |

| 1.1      | 21-Feb-2107 | Minor changes                  |

| 1.2      | 23-Feb-2022 | Document rebranded to Renesas. |

### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### **Important Notice and Disclaimer**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

© 2022 Renesas Electronics Corporation. All rights reserved.

(Rev.1.0 Mar 2020)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu

Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

https://www.renesas.com/contact/

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Application Note**

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.