# RENESAS

UART to 7-Segment Display SLG47910

This application shows how to design a UART to Seven-Segment Display. We are using a PmodSSD for the 2digit seven segment display connected to the Evaluation Board. The working of the UART Terminal is also discussed in this AN. Simulation waveforms generated by GTKWave software can be used to verify the functionality of the design.

This application note comes complete with design files which can be found in the Reference section.

### Contents

| Ter | ns an | nd Definitions                    | 1  |

|-----|-------|-----------------------------------|----|

| Ref | erenc | es                                | 2  |

| 1.  | UAR   | Т                                 | 2  |

| 2.  | Seve  | en Segment Display                | 3  |

|     | 2.1   | Seven-Segment Display Truth Table | 4  |

| 3.  | Ingro | edients                           | 5  |

| 4.  | Veril | og Code                           | 5  |

| 5.  |       | rplan: CLB Utilization            |    |

| 6.  | Desi  | gn Steps                          | 9  |

| 7.  | GTK   | Wave Simulation Waveform          | 13 |

|     | 7.1   | UART to 7-Segment (main_tb)       | 13 |

|     | 7.2   | Baud Rate Generator               | 13 |

|     | 7.3   | UART_Receiver_rx                  | 13 |

|     | 7.4   | UART Receiver                     | 14 |

|     | 7.5   | Seven_Segment Display             | 14 |

| 8.  |       | clusion                           |    |

| 9.  | Revi  | sion History                      | 15 |

### **Terms and Definitions**

| FPGA               | Field Programmable Gate Array                             |

|--------------------|-----------------------------------------------------------|

| UART               | Universal Asynchronous Receiver Transmitter               |

| FPGA Core          | Circuit Block that contains the digital array macro cells |

| ForgeFPGA Workshop | Top level FPGA display and control window                 |

| FPGA Editor        | Main FPGA design and simulation window                    |

| CLB                | Configuration Logic Block                                 |

| EVB                | Evaluation Board                                          |

| Pmod               | Peripheral Module Interface                               |

RENESAS

### References

For related documents and software, please visit:

ForgeFPGA Low-density FPGAs | Renesas

Download our free ForgeFPGA<sup>™</sup> Designer software [1] to open the .ffpga design files [2] and view the proposed circuit design.

[1] Go Configure Software Hub, Software Download and User Guide

[2] AN-FG-012 UART to 7-segment Display.ffpga, ForgeFPGA Design File

[3] SLG47910, Preliminary Datasheet, Renesas Semiconductor

### 1. UART

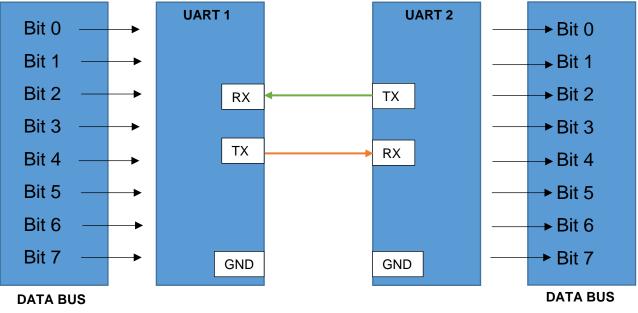

UART or Universal Asynchronous Receiver-Transmitter is a commonly utilized communication protocol between devices. It provides a direct way to communicate with an FPGA, allowing for the exchange of commands between a device which have a UART interface and the FPGA. With proper configuration, UART is compatible with various serial protocols that require the transmission and reception of serial data. In serial communication, data is transmitted bit by bit using a single line or wire, and in bi-directional communication, two wires are employed to enable successful serial data transfer.

The two signals of each UART device are named:

- Transmitter (Tx)

- Receiver (Rx)

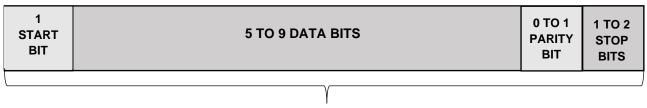

The main purpose of a transmitter and receiver line for each device is to transmit and receive serial data intended for serial communication (see Figure 1). For a UART, the baud rate needs to be set the same on both the transmitting and the receiving device. UART devices have a few important parameters used for setting different configurations (see Figure 2):

1. **Baud Rate**: It is the rate at which information is transferred between communication channels. It can also be defined as the maximum number of bits per seconds to be transferred. Some common Baud Rates for an UART device is 9600,19200 and 115200.

RENESAS

- 2. **Number of Data Bits**: Data bits are contained inside a Data Frame. It can be 5 bits up to 8 bits long if parity bit is used. If no parity bit is used, then the Data Frame can be 9 bits long. The parity bit can be appended after the data is sent.

- 3. **Stop Bit**: To signal the end of the data packet, the sending UART drives the data transmission line from a low voltage to a high voltage. The Stop Bit is most preferably set to 1. Stop Bits are 1, 1.5 and 2 bits.

PACKET Figure 2: Data Frame for Receiver

4. Parity Bit: Parity is used by the receiving UART to detect any changes that may have occurred during transmission. Once the data frame is received, the receiving UART counts the number of bits with a value of 1 and checks if the total is odd or even based on the value of the parity bit. In case of even parity (parity bit set to 0), the total number of 1 bit in the data frame should be even, whereas in case of odd parity (parity bit set to 1), the total number of 1 bit in the data frame should be odd. The UART considers the transmission error-free when the parity bit matches the data. However, if the total is odd when the parity bit is set to 0 or even when the parity bit is set to 1, the UART detects that the data frame has been modified.

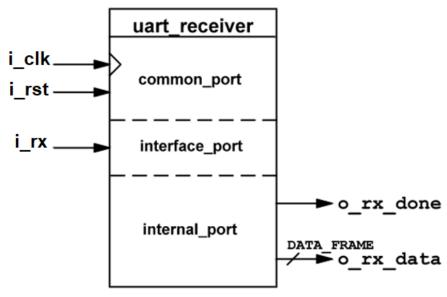

Figure 3: UART Receiver Block

### 2. Seven Segment Display

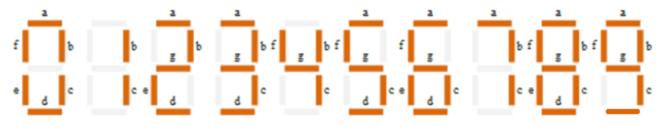

The seven-segment display is made up of seven LEDs that are arranged in a rectangular shape. Each LED is referred to as "segment" because it forms part of a numerical digit when illuminated. In some cases, an extra 8<sup>th</sup> LED may be included in the same package to indicate a decimal point (DP). When multiple seven-segment displays are connected to display numbers the DP LED can be used to differentiate between whole numbers and decimals. The displays common pin is generally used to identify which type of seven-segment display it is. As

each LED has two connecting pins, one called the "Anode" and the other called the "Cathode", there are therefore two types of LED seven-segment display called: **Common Cathode** (CC) and **Common Anode** (CA).

In the common cathode display, all the cathode connections of the LED segments are joined together to logic "0" or ground. The individual segments are illuminated by application of a "HIGH", or logic "1" signal via a current limiting resistor to forward bias the individual Anode terminals (a-g). In the common anode display, all the anode connections of the LED segments are joined together to logic "1". The individual segments are illuminated by applying a ground, logic "0" or "LOW" signal via a suitable current limiting resistor to the Cathode of the segment (a-g). See Figure 4

Figure 4: Digital Segments for all numbers

### 2.1 Seven-Segment Display Truth Table

| Decimal | Individual Segments Illuminated |   |   |   |   |   |   |  |  |  |  |  |  |

|---------|---------------------------------|---|---|---|---|---|---|--|--|--|--|--|--|

| Digit   | а                               | b | с | d | е | f | g |  |  |  |  |  |  |

| 0       | Н                               | Н | Н | Н | Н | Н | L |  |  |  |  |  |  |

| 1       | L                               | Н | Н | L | L | L | L |  |  |  |  |  |  |

| 2       | Н                               | Н | L | Н | Н | L | Н |  |  |  |  |  |  |

| 3       | Н                               | Н | Н | Н | L | L | Н |  |  |  |  |  |  |

| 4       | L                               | Н | Н | L | L | Н | Н |  |  |  |  |  |  |

| 5       | L                               | Н | Н | Н | L | Н | Н |  |  |  |  |  |  |

| 6       | Н                               | L | Н | Н | Н | Н | Н |  |  |  |  |  |  |

| 7       | Н                               | Н | Н | L | L | L | L |  |  |  |  |  |  |

| 8       | Н                               | Н | Н | Н | Н | Н | Н |  |  |  |  |  |  |

| 9       | Н                               | Н | Н | L | L | Н | Н |  |  |  |  |  |  |

### 3. Ingredients

- SLG47910 Device

- Latest Revision of the ForgeFPGA Workshop software

- ForgeFPGA Evaluation Board and cables

- PmodSSD Device (2-Digits)

- Jump Wire

### 4. Verilog Code

The UART to seven-Segment design is available for download (AN-FG-012 UART to 7seg.ffpga). It contains one top module which has instances of two IP Modules: UART Receiver and the seven-Segment display. These two modules are connected, and the necessary parameters are specified. The UART Receiver IP module has two more sub-modules inside which is used to define the baud rate and to define the working of the receiver.

Shown below is the (\*top\*) module named uart\_to\_7seg. The Verilog code for UART to seven-segment can be found in the complete design example. It is available for download (AN-FG-012 UART to 7seg.ffpga)

Multiple always block in the Verilog code allows the user to configure the counter and the UART FSM structure to ensure communication between blocks and data flow. The signals in the UART Receiver IP Module can be seen in Figure 3.

```

(* top *) module uart to 7seg #(

parameter IN_CLK_HZ = 46_000_000,

parameter DATA FRAME

// number of data bits

= 8,

// transmitting speed

parameter BAUD RATE

= 115200,

// bit offset or overlap

parameter OVERSAMPLING MODE = 16,

= 1,

parameter STOP_BIT

// length of stop bit

= 1,

// determine serial data transfer 1=

parameter LSB

MSB to LSB

parameter SEL CA

= 1

// common cathode

) (

// Main inputs

(* iopad external pin, clkbuf inhibit *) input i clk,

(* iopad external pin *) input i por,

// OSC config outputs

(* iopad_external_pin *) output osc_ctrl_en,

// Custom IO

(* iopad external pin *) input i rx,

(* iopad external pin *) output rx oe,

(* iopad external pin *) output o cat, // determines which active digit

(* iopad external pin *) output o out a,

(* iopad external pin *) output o out b,

(* iopad external pin *) output o out c,

(* iopad external pin *) output o out d,

(* iopad external pin *) output o out e,

(* iopad external pin *) output o out f,

(* iopad external pin *) output o out g,

(* iopad external pin *) output o cat oe,

(* iopad external pin *) output o out a oe,

(* iopad external pin *) output o out b oe,

(* iopad external pin *) output o out c oe,

(* iopad external pin *) output o out d oe,

```

```

(* iopad external pin *) output o out e oe,

(* iopad external pin *) output o out f oe,

(* iopad external pin *) output o out g oe

);

wire

w rx done;

wire [7:0] w_rx_data, w_segment;

wire [1:0] w_active_digit;

reg [11:0] r_counter;

reg [1:0] r_rx;

reg

r tick;

assign osc_ctrl en = 1'b1;

//oe

assign rx oe = 0;

assign o cat oe = 1;

assign o_out_a_oe = 1;

assign o_out_b_oe = 1;

assign o_out_c_oe = 1;

assign o_out_d_oe = 1;

assign o_out_e_oe = 1;

assign o_out_f_oe = 1;

assign o_out_g_oe = 1;

// reset buffer

wire w rst;

input reset buf impl input reset buf (

.i clk

(i clk),

.i por

(i por),

.o_rst

(w rst)

);

//Synchronized rx to avoid metastability

always @(posedge i clk) begin

if(w rst) begin

r rx <= 2'b11;

end else begin

r_rx <= {r_rx[0], i_rx};</pre>

end

end

assign o cat = w active digit[1];

always @(posedge i clk) begin

if (w rst) begin

r counter <= 'h00;</pre>

r tick <= 1'b0;

end else begin

if(r counter <= 2499) begin</pre>

r_counter <= r_counter + 1;</pre>

r tick <= 1 b0;

end else begin

r_counter <= 'h00;</pre>

r tick <= 1'b1;

end

end

end

// instantiate the UART Receiver

uart receiver #(

```

```

.IN CLK HZ

(IN CLK HZ

),

.DATA FRAME

(DATA FRAME

),

(BAUD RATE

.BAUD RATE

),

.OVERSAMPLING MODE (OVERSAMPLING MODE),

.STOP_BIT

(STOP_BIT

),

.LSB

(LSB

)

) impl_uart_rx (

.i_clk

(i clk

),

.i_rst

(w rst

),

(r_rx[1] ),

.i_rx

.o_rx_data

(w_rx_data),

.o_rx done

(w_rx_done)

);

// instantiate the 7-segment Module

seven_seg_disp_ctrl_2d #(

.SEL CA (SEL CA)

) impl_seven_seg_disp_ctrl_2d (

.i_clk

(i_clk

),

.i_load

(w rx done

),

.i_en

(1'b1

),

.i_rst

(w rst

),

.i_refresh_clock (r_tick

),

.i_data ({2'b00,w_rx_data}),

.o active digit (w active digit ),

.o segment (w segment

)

);

assign o out a = w segment[7];

assign o out b = w segment[6];

assign o_out_c = w_segment[5];

assign o_out_d = w_segment[4];

assign o out e = w segment[3];

assign o out f = w segment[2];

assign o out g = w segment[1];

```

endmodule

### 5. Floorplan: CLB Utilization

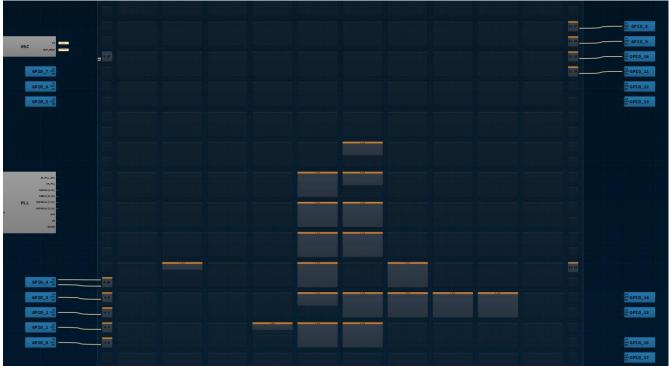

Figure 5: Floorplan

From Figure 5, we can see a part of the floorplan for this application note.

From the Verilog code, the user can observe which GPIOs are being used for this Application Note. This can also be observed under the floorplan tab in the software. The connection between each CLB in the floorplan can be observed by clicking on the CLB of interest and observing the yellow(input) and blue(output) wires connecting the CLBs internally.

### 6. Design Steps

1. Launch the latest version of the Go Configure Software Hub. Select the SLG47910V device and the ForgeFPGA Workshop software will load.

2. From the ForgeFPGA tool bar, select the FPGA Editor tab.

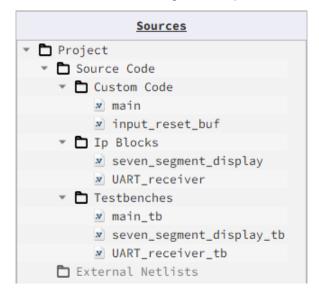

3. Enter the Verilog code into the HDL editor and save the code using the save button on the top left corner of the FPGA Editor. Make sure that there are five tabs containing different parts of the code. (See Figure 6)

#### Figure 6: Source files for this project

4. Open the IO planner tab on the FPGA editor. Assign the IOs that are in the Verilog code to GPIO pins on the device and save. (See Figure 7)

5. Next select the Synthesize button on the lower left side of the FPGA editor.

6. Select the Generate Bitstream button on the lower left side of the FPGA editor. Check the Logger and Issues tabs to make sure that the Bitstream was generated correctly. Now click on the Floorplan tab and see the CLB utilization. Press the Ctrl and the mouse wheel to zoom-in. (Figure 5). Confirm that the IOs selected in the IO Planner (Figure 7) are shown in the floorplan.

| FUNCTION           |             |

|--------------------|-------------|

| OSC_CLK            | i_clk       |

| FPGA_CORE_READY    | i_por       |

| [PIN 17] GPIO4_IN  | i_rx        |

| [PIN 16] GPIO3_OUT | o_cat       |

| [PIN 16] GPIO3_OE  | o_cat_oe    |

| [PIN 23] GPIO8_OUT | o_out_a     |

| [PIN 23] GPIO8_OE  | o_out_a_oe  |

| [PIN 24] GPIO9_OUT | o_out_b     |

| [PIN 24] GPIO9_OE  | o_out_b_oe  |

| [PIN 1] GPI010_OUT | o_out_c     |

| [PIN 1] GPIO10_OE  | o_out_c_oe  |

| [PIN 2] GPI011_OUT | o_out_d     |

| [PIN 2] GPI011_OE  | o_out_d_oe  |

| [PIN 13] GPIO0_OUT | o_out_e     |

| [PIN 13] GPIO0_OE  | o_out_e_oe  |

| [PIN 14] GPIO1_OUT | o_out_f     |

| [PIN 14] GPIO1_OE  | o_out_f_oe  |

| [PIN 15] GPIO2_OUT | o_out_g     |

| [PIN 15] GPIO2_OE  | o_out_g_oe  |

| OSC_EN             | osc_ctrl_en |

| [PIN 17] GPIO4_OE  | rx_oe       |

#### Figure 7: IO Planner

7. This design file also comes with a testbench to verify the working of UART and the Seven-Segment display. The simulation waveforms can be verified by using the inbuilt GTKWave software. Uart\_receiver\_tb is the testbench for UART side of the design file and the seven\_segment\_tb is the other testbench used to verify the working of the seven\_segment display. The user can launch the GTKWave software by clicking on the Simulate Testbench icon on the toolbar. This will automatically launch the GTKWave software provided there are no errors in your testbench. The errors/issues can be observed from the console at the bottom of window.

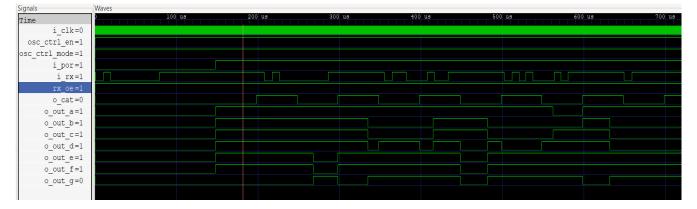

8. In the GTKWave software, the user can insert the desired signal in the window from the list of all the signals in the code and observe the waveform. Through the generated waveform the user can verify the functionality of UART and the seven-segment display without going through the hassle of connecting the development board. (See Section 7)

9. Once the user is satisfied with the waveform, the user can Debug the design file. Close the FPGA Editor and go to the ForgeFPGA widow. Selecting the Debug tab will enable the debug controls. Double click on the VDD pin and set VDD = 1.2V. Then double click on VDDIO pin and set VDDIO = 1.8V.

10. In the ForgeFPGA Workshop window, select Change platform on the Debugging Controls tab. Choose the ForgeFPGA Development Platform then select Emulation. The Emulation button will toggle the design on and off.

11.To observe the outputs of this application note, connect the Evaluation Board along with the PmodSSD connected to its GPIO. User the upper slots of the GPIO in the EVB to connect to the PmodSSD.

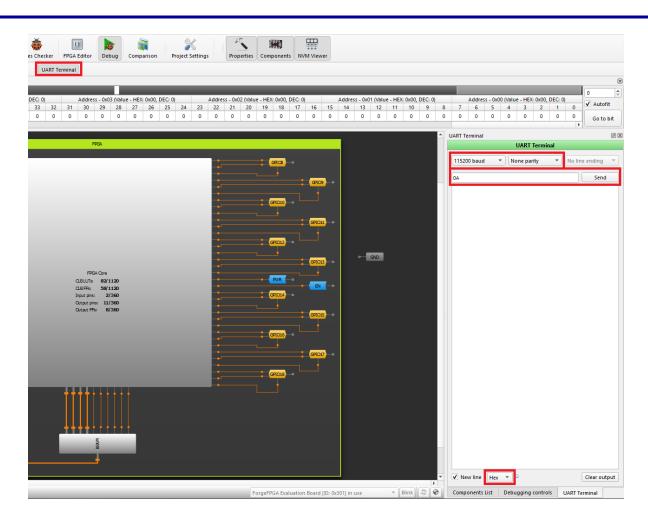

12. To send the data from the UART to the Pmod, we need to use the inbuilt UART Terminal. The EVB has a connection for the UART. The user needs to connect the TX within the UART on the board to GPIO4 for the UART Terminal to work. (See Figure 8)

Figure 8: UART Connection on EVB

Figure 9: UART Terminal

13. The user can then send the desired data from the UART Terminal to the PmodSSD in Hexadecimal form. The user needs to set the Baud Rate as 115200 and set the Parity Bit to "None Parity". The user can type the desired data (HEX) they want to send to the Pmod in the UART Terminal (See Figure 9) and then click Send to see it appear on the PmodSSD. (See Figure 10)

Figure 10: PmodSSD Results

### 7. GTKWave Simulation Waveform

The design file has three sets of testbenches which can be used to verify the functionality of the design. There are three testbench files, uart\_receiver\_tb, seven\_segment\_display\_tb and main\_tb. Inside the uart\_receiver\_tb, we have two sub modules, baud\_rate\_generator and uart\_receiver\_rx. We can observe the waveform for each submodule in GTKWave to verify. The main\_tb is used to verify the total functionality of the seven-segment receiving data from the UART.

### 7.1 UART to 7-Segment (main\_tb)

### 7.2 Baud Rate Generator

| Signals      | Waves |   |   |    |       |      |    |    |    |      |        |     |   |    |    |      |       |    |    |    |      |       |   |   |    |

|--------------|-------|---|---|----|-------|------|----|----|----|------|--------|-----|---|----|----|------|-------|----|----|----|------|-------|---|---|----|

| Time         | us    |   |   |    | 18010 | 0 ns |    |    |    | 180  | 200 ns |     |   |    |    | 1803 | 00 ns |    |    |    | 1804 | 00 ns |   |   |    |

| clk          |       |   |   |    |       |      |    |    | ÌΓ |      |        | 1 r |   |    |    |      |       |    |    |    |      |       |   |   | ίĒ |

| nreset       |       |   |   |    |       |      |    |    |    |      |        |     |   |    |    |      |       |    |    |    |      |       |   |   |    |

| r count[4:0] | 6 7   | 8 | 9 | 10 | 11    | 12   | 13 | 14 | 1  | 5 16 | 17     | )1  | 8 | 19 | 20 | 21   | 22    | 23 | 24 | 25 | 26   | 0     | 1 | 2 | 3  |

| tick         |       |   |   |    |       |      |    |    |    |      |        |     |   |    |    |      |       |    |    |    |      |       |   |   |    |

|              |       |   |   |    |       |      |    |    |    |      |        |     |   |    |    |      |       |    |    |    |      |       |   |   |    |

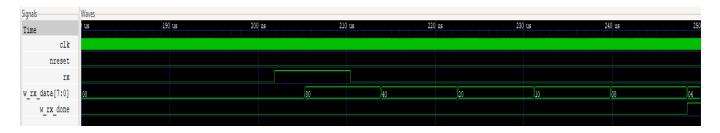

### 7.3 UART\_Receiver\_rx

| Signals        | Waves              |                    |                     |                    |             |

|----------------|--------------------|--------------------|---------------------|--------------------|-------------|

| Time           | us 190             | us 200             | us 210              | us 220             | us          |

| clk            |                    |                    |                     |                    |             |

| nreset         |                    |                    |                     |                    |             |

| rx             |                    |                    |                     |                    |             |

| r_cnt[3:0]     | DCBA9876543210FEDC | BA9876543210FEDCBA | 9876543210FEDCBA987 | 6543210FEDCBA98765 | 1/3/2/1/0/F |

| r_cnt_en       |                    |                    |                     |                    |             |

| r_index[2:0]   | 000 001            | X010               | )011                | (100               | )1          |

| r_index_cnt_en |                    |                    |                     |                    |             |

| r_read_data    |                    |                    |                     |                    |             |

| state[3:0]     | 4                  |                    |                     |                    |             |

| next[3:0]      | 4                  |                    |                     |                    |             |

| tick           |                    |                    |                     |                    |             |

| w_cnt_en       |                    |                    |                     |                    |             |

| w_index_cnt_en |                    |                    |                     |                    |             |

| w_read_data    |                    |                    |                     |                    |             |

| w_rx_done      |                    |                    |                     |                    |             |

| o_rx_done      |                    |                    |                     |                    |             |

| o_rx_data[7:0] | 00                 |                    | 80                  | 40                 | 2           |

|                |                    |                    |                     |                    |             |

### 7.4 UART Receiver

### 7.5 Seven\_Segment Display

| Signals           | Waves-          |                |                |       |       |          |       |       |        |      |                |                |            |

|-------------------|-----------------|----------------|----------------|-------|-------|----------|-------|-------|--------|------|----------------|----------------|------------|

| Time              | us              | 31100 ns       | 3120           | 00 ns | 3130  | 0 ns     | 3140  | 0 ns  | 3150   | 0 ns | 31600          | ) ns 3         | 1700       |

| clk               |                 | muunniunnu     |                | mumuu | muumu | IMMIIMII |       | uumuu | muumuu | muum |                |                | nuum       |

| refresh_clock     |                 |                |                |       |       |          |       |       |        |      |                |                |            |

| nreset            |                 |                |                |       |       |          |       |       |        |      |                |                |            |

| en                |                 |                |                |       |       |          |       |       |        |      |                |                |            |

| i                 | 0               |                |                |       |       |          |       |       |        |      |                |                | /1         |

| j                 | 4 5             | )(e            | (7             | 8     | 9     | /10      | X     | 11    | 12     | 13   | 14             | 15             | <u>)</u> 0 |

| data[9:0]         | 4 5             | Xe             | (7             | 8     | 9     | /10      | X     | 11    | 12     | 13   | 14             | 15             | )2         |

| active_digit[1:0] | ) <u>10 )01</u> | <u>/10 /01</u> | <u>\10 \01</u> | 10 0  | 1 10  | )(01 )(1 | .0 01 | 10    | 01 10  | 01   | <u>)10 )01</u> | <u>\10 \01</u> | (10        |

| load              |                 |                |                | Л     |       |          |       |       | Π      | Л    | $-\Pi$         |                | $\Box$     |

| out_a             |                 |                |                |       |       |          |       |       |        |      |                |                |            |

| out_b             |                 |                |                |       |       |          |       |       |        |      |                |                |            |

| out_c             |                 |                |                |       |       |          |       |       |        |      |                |                |            |

| out_d             |                 |                |                |       |       |          |       |       |        |      |                |                |            |

| out_dp            |                 |                |                |       |       |          |       |       |        |      |                |                |            |

| out_e             |                 |                |                |       |       |          |       |       |        |      |                |                |            |

| out_f             |                 |                |                |       |       |          |       |       |        |      |                |                |            |

| out_g             |                 |                |                |       |       |          |       |       |        |      |                |                |            |

|                   |                 |                |                |       |       |          |       |       |        |      |                |                |            |

### 8. Conclusion

In this application, we integrated two IP Modules together and created a design which allows the data to flow from a UART to a seven-segment display. The two digits can be observed on a PmodSSD which is connected to the ForgeFPGA's Evaluation Board. Through this Application Note we also understood the working of the UART Terminal.

If interested, please contact the ForgeFPGA Business Support Team.

## 9. Revision History

| Revision | Date           | Description                |

|----------|----------------|----------------------------|

| 1.00     | March 18, 2023 | Initial release.           |

| 2.0      | Feb 23, 2024   | Updated as per BB Revision |