# R2A20114BFP

## APPLICATION NOTE

Application Note

R03AN0011EJ0200 Rev.2.00 July 25, 2017

## Introduction

R2A20114BFP is a boost converter control IC with PFC (Power Factor Correction).

Employing continuous conduction mode (CCM), it has interleaving control which produces 180 degrees phase shift between the output signals (GD1,2) driving the boost converters. Interleaving control of the boost converters enables the system to perform high conversion efficiency and low switching noises and, at the same time, to reduces ripple currents in input and output current and then this allows use of smaller components such as boost inductors, input filters and output capacitors, which is best suitable for high power applications.

Based on the R2A20114AFP, R2A20114BFP features improved usability such as built-in PFC boost voltage control, current detection amplifier with differential inputs, independent and high-functional error output pin, timer reset of OFF latch, and partial switch for PFC.

The two mode over voltage protection, over current protection are built in to enable construct a reliable power supply system with few external parts.

#### **Target Device**

R2A20114BFP

#### Contents <contents header>

| 1.  | Outli | ne                                                              | 3  |

|-----|-------|-----------------------------------------------------------------|----|

| 2.  | Bloc  | k Diagram                                                       | 4  |

| 3.  | R2A2  | 20114BFP Block Descriptions                                     | 5  |

| 3.1 | Pro   | tection                                                         | 5  |

| 3   | 8.1.1 | Over-voltage protection <ovp></ovp>                             | 5  |

| 3   | 8.1.2 | Over-voltage protection 2 <ovp2></ovp2>                         | 5  |

| 3   | 8.1.3 | Feedback loop open detect                                       | 5  |

| 3   | 8.1.4 | Over-current protection <ocp></ocp>                             | 6  |

| 3.2 | 2 Dri | ve Stage                                                        | 6  |

| 3.3 | S So  | ft Start                                                        | 7  |

| 3.4 | Pha   | ase Drop                                                        |    |

| 3.5 | 5 Err | or Function                                                     | 9  |

| 3   | 8.5.1 | E_OVP pin movement by overvoltage protection detection 2 (OVP2) |    |

| 3   | 8.5.2 | E_PHASE pin movement by phase error detection 2                 |    |

| 3   | 8.5.3 | E_OCP pin movement by overcurrent detection                     | 11 |

| 3.6 | 6 OF  | F Function                                                      |    |

| 3.7 | ′ Syı | nchronous Function                                              |    |

| 3.8 | S Syı | nchronous Output Function                                       |    |

| 3.9 | PW    | /M_IN Function                                                  |    |

| 4.  | Desi         | gn Guide                                                           | 15    |

|-----|--------------|--------------------------------------------------------------------|-------|

| 4.1 | l Bo         | oost inductor                                                      | . 155 |

| 4.2 | 2 Oi         | Itput capacitor                                                    | . 155 |

| 4.3 | B Po         | ower MOSFET(IGBT), and boost diode                                 | . 155 |

| 4.4 | 4 Op         | perating Frequency                                                 | . 166 |

| 4   | 4.4.1        | Operating Frequency Setting                                        | 16    |

| 4   | 4.4.2        | A method to limit Max. Duty of GD                                  | 17    |

| 4.5 | 5 Inj        | out AC voltage sensing                                             | . 188 |

| 4.6 | 6 Re         | esistor of current sensing                                         | . 188 |

| 4.7 | 7 Ph         | ase Compensation Circuit of Current Amplifier                      | . 199 |

| 4   | 4.7.1        | RS pin                                                             | . 199 |

| 4   | 4.7.2        | CSO pin                                                            | . 199 |

| 4.8 | B Re         | esistor of IRAMP pin                                               | 20    |

| 4.9 | ) Ca         | pacitor of Soft-start                                              | 21    |

| 4.1 | l0 Pr        | otection Functions                                                 | . 221 |

| 4   | 4.10.1       | OVP2 voltage setting                                               | . 221 |

| 4   | 4.10.2       | E-DELAY setting                                                    | . 222 |

| 4.1 | <b>Ι1 Οι</b> | Itput Voltage Setting and Frequency Characteristics of Voltage Amp | . 222 |

| 4   | 4.11.1       | Output voltage setting                                             | . 222 |

| 4   | 4.11.2       | COMP parameter setting                                             | . 222 |

| 4   | 4.11.3       | PFC boost voltage setting                                          | 24    |

| 4.1 | 12 Tr        | eatment of Each Pin                                                | 25    |

| 4.1 | I3 Ur        | nused Pins                                                         | 29    |

| 4.1 | 14 No        | otice for PCB Layout                                               | 30    |

### 1. Outline

R2A20114BFP is a boost converter control IC with PFC (Power Factor Correction).

Employing continuous conduction mode (CCM), it has interleaving control which produces 180 degrees phase shift between the output signals (GD1,2) driving the boost converters. Interleaving control of the boost converters enables the system to perform high conversion efficiency and low switching noises and, at the same time, to reduces ripple currents in input and output current and then this allows use of smaller components such as boost inductors, input filters and output capacitors, which is best suitable for high power applications.

Also, R2A20114BFP uses resistors to detect current of switching elements, enabling small space and low cost current sense best suitable for air-conditioner application.

The two mode over voltage protection, over current protection are built in to enable construct a reliable power supply system with few external parts.

Compared to the conventional R2A20114AFP, harmonic current characteristics in smaller input/output voltage difference is improved in R2A20114BFP. And functions for stable operation are improved. Table 1 shows the difference from R2A20114AFP.

| Function              | R2A20114BFP                                                                                                        | R2A20114AFP (conventional)    |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Boost voltage control | Built-in                                                                                                           | External circuits required    |

| Current amplifier     | Differential amplifier                                                                                             | Single end                    |

| Error detecting pins  | Independent OCP, OVP, Phase error output pin                                                                       | Sharing 1 pin                 |

|                       | Error can be distinguished even if<br>error pins are put together, by<br>changing output duration for the<br>error | Errors can't be distinguished |

|                       | Low at error                                                                                                       | High at error                 |

| OFF latch reset       | Timer automatically reset                                                                                          | Need to power off to reset    |

| Partial SW            | Built-in                                                                                                           | Not applicable                |

| Semi bridge-less PFC  | Negative voltage of CS pin                                                                                         | Not applicable                |

| 4 phases operation    | SYNC-O signal is inverter output<br>of RT/SYNC wave                                                                | External circuits required.   |

Table1 Difference between R2A20114AFP and R2A20114BPF

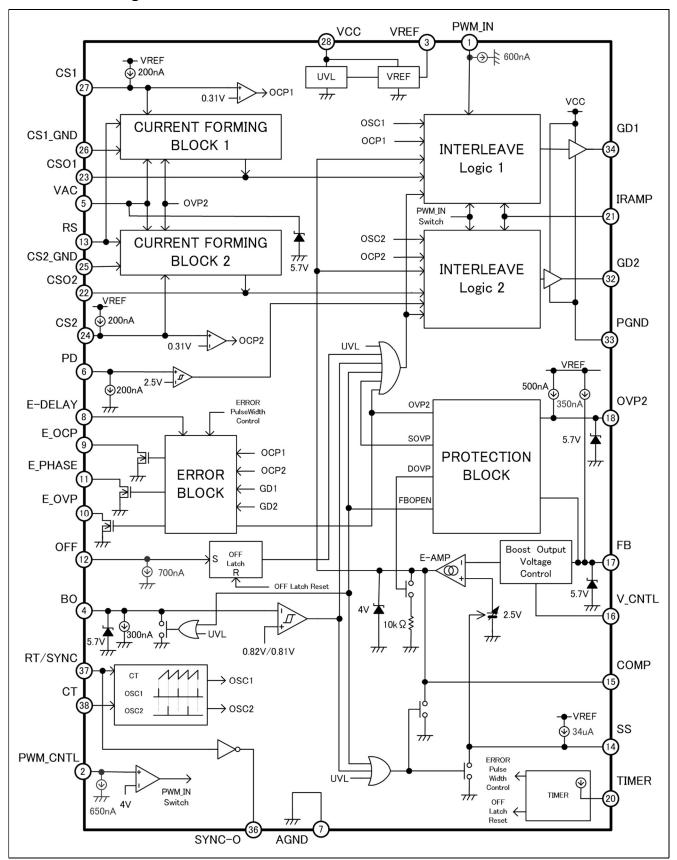

#### 2. Block Diagram

#### 3. R2A20114BFP Block Descriptions

#### 3.1 Protection

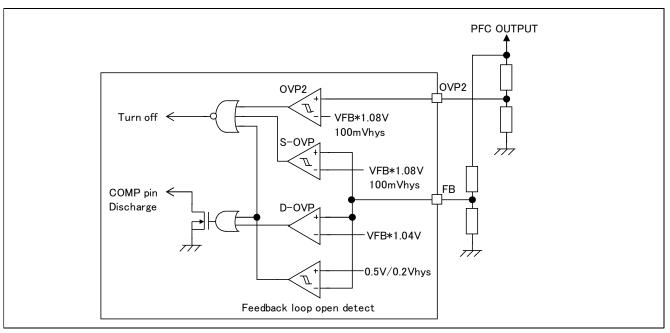

R2A20114BFP provides 4 types of protecting functions, over-voltage protection, over-voltage protection 2, overcurrent protection and feedback loop open detect.

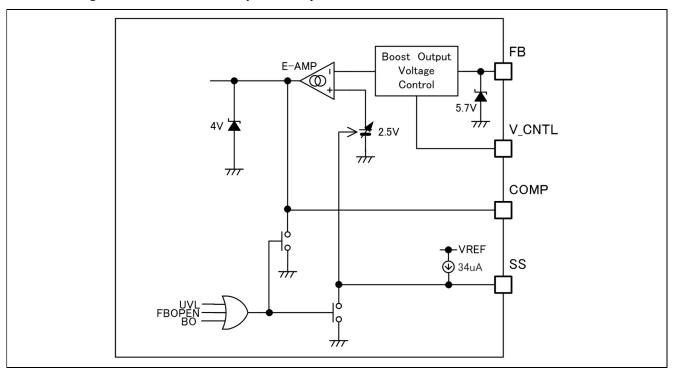

#### Figure 1 Protection

#### 3.1.1 Over-voltage protection <OVP>

The over voltage protection has two step protections. Dynamic over voltage protection (D-OVP) discharges COMP pin voltage when FB pin voltage reaches 1.04 \*VFB (2.5Vtyp). The Power MOSFET on time is limited gradually, therefore the audio noise is avoided because an inductor current does not stop suddenly. Static over voltage protection (S-OVP) stops IC output when FB pin voltage reaches 1.08 \*VFB (2.5Vtyp). A Power MOSFET turns off quickly and S-OVP keeps stopping until FB pin voltage reaches 1.08 \*VFB (2.5Vtyp) – 100mV.

#### 3.1.2 Over-voltage protection 2 <OVP2>

In over-voltage protection 2 (OVP2), PFC output voltage is monitored by a special pin independent from FB pin which has D-OVP and S-OVP functions. When OVP2 pin becomes 1.08\*VFB(2.5Vtyp), it stops switching and keeps re-start when OVP2 pin voltage reaches 1.08\*VFB(2.5Vtyp) - 100mV. If over-voltage protection 2 is detected, E\_OVP pin operates. For details, refer to item 3.5.

#### 3.1.3 Feedback loop open detect

The feedback open-loop protection discharges COMP pin voltage to stop IC output during FB pin voltage is under 0.5V There is 0.2V hysteresis in detection voltage.

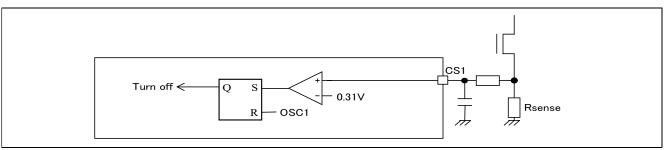

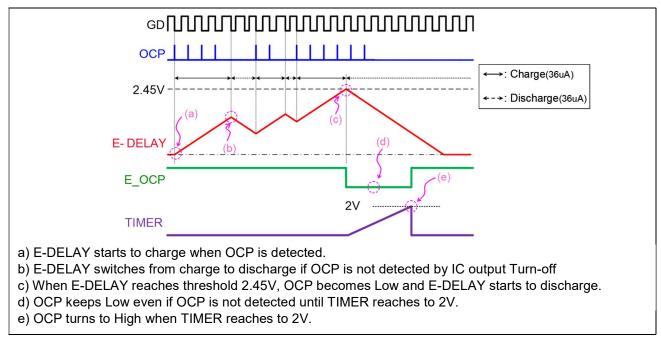

#### 3.1.4 Over-current protection <OCP>

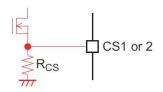

R2A20114BFP stops output of GD1 or GD2 when CS1 or CS2 pin reaches 0.31V. OCP is reset every cycle by pulse by pulse protection.

When over current is detected, E-DELAY pin charges, and turn into discharge status when over current status is cancelled. If over-current status continues up to E-DELAY pin being 2.45V, open drain element at E-OCP pin turns ON. For details, refer to item 3.5.

Figure 2 Over-current protection

#### 3.2 Drive Stage

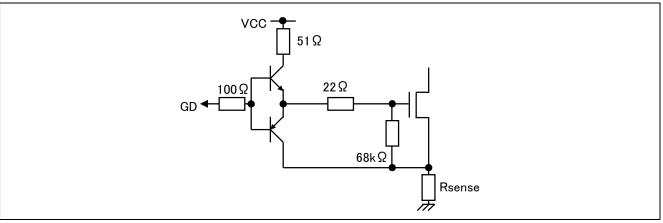

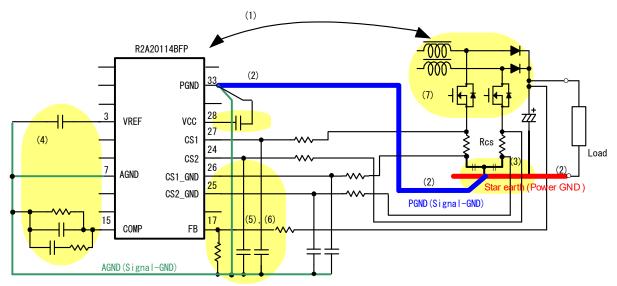

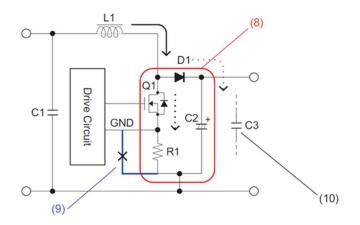

R2A20114BFP contains two totem-pole output for phase 1 and phase 2. The maximum rating of drivability is 0.2A peak. Use the drive circuit to adjust the drivability for switching elements characteristics used. The following shows a drive circuit example. By connecting GND of drive circuit to emitter (or source), it can avoid the influence of long wiring for stable characteristics

Figure 3 Drive circuit example

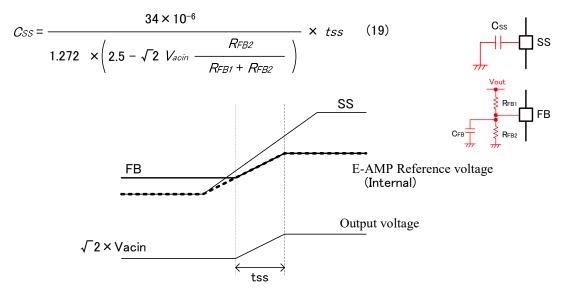

#### 3.3 Soft Start

ON time increase gradually by connecting capacitor between SS pin and GND. SS pin charge current is 34uA constant current, and SS time is adjustable by changing external capacitor value. SS pin discharge the capacitor when VCC is under UVLO threshold voltage or FB voltage is under 0.3Vtyp. or BO voltage is under 0.81V.

The error signal  $E_OVP$  may be output during the soft start period at startup. When the gate pulse is stopped by using  $E_OVP$ , it is recommended to mask the error signal, or count the number of error signal occurrence and stop the system when detecting a certain number of times by microcomputer or the like.

Figure 4 Soft Start

#### 3.4 Phase Drop

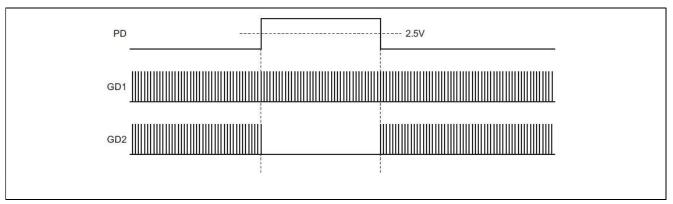

When the PD signal becomes 2.5V or more, GD2 stops in order to reduce switching loss at light load

Figure 5 Phase Drop

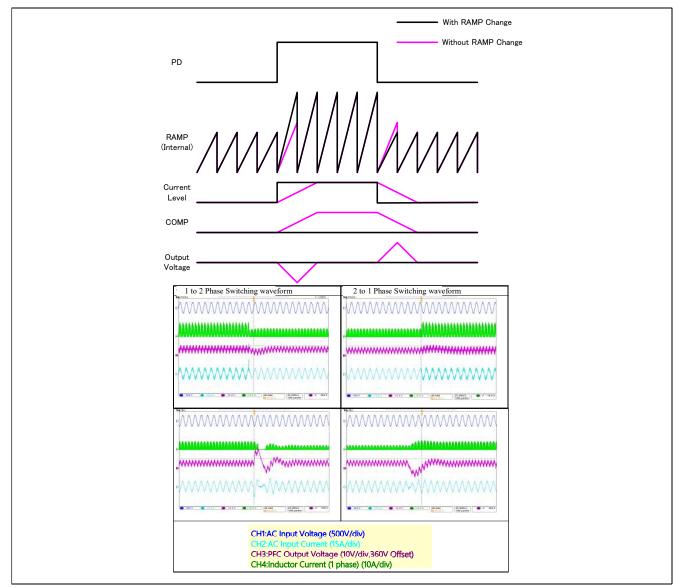

Phase drop switching is equal to increase to twice/reduce by half momentarily. It prevents output voltage variation at phase drop switching by controlling slope of internal RAMP signal to increase/decrease momentary current supply.

Figure 6 Operation at Phase Drop Switching

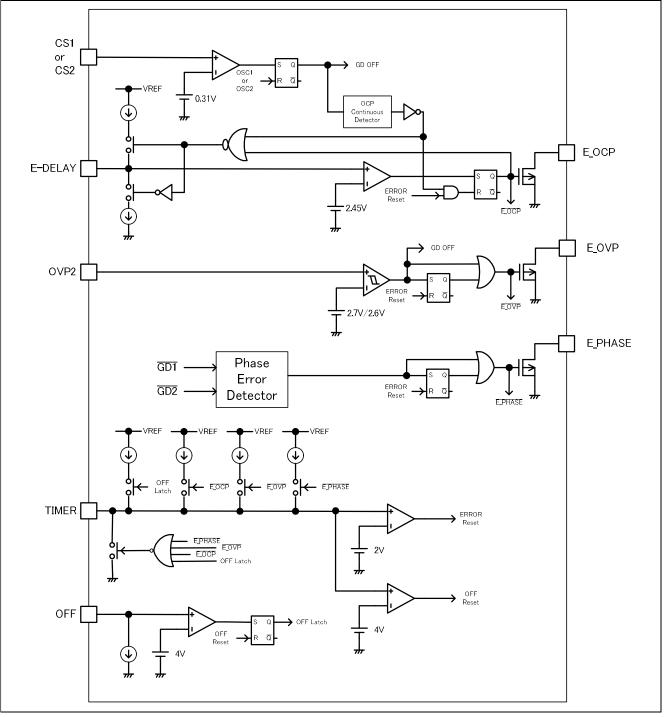

#### 3.5 Error Function

When over-voltage protection 2 (OVP2), over-current protection (OCP) or phase error is detected, the corresponding error pin (E\_OVP pin, E\_OCP pin, E\_PHASE pin respectively) operates in R2A20114BFP. Each error pins are open drain output and the open drain element turns ON at error detection. During the error continues, the open drain element keeps ON. If any error is detected, TIMER pin charges. If the TIMER pin does not reach 2Vtyp when the error is cancelled, the open drain element keeps ON until it reaches 2V typ., then turns OFF. If TIMER pin voltage is over 2Vtyp., the open drain element turns OFF immediately. When open drain element becomes OFF, the TIMER pin current switches into rapid discharge mode.

The charge current varies depending on the error. Since the period of error pin being ON is different in case of transient short-time error, MCU can distinguish the error type.

Figure 7 Error Function

#### 3.5.1 E\_OVP pin movement by overvoltage protection detection 2 (OVP2)

When an OVP2 pin voltage exceeds 1.08\*VFB[2.5Vtyp.], it becomes OVP2 error and E\_OVP pin operates. When an OVP2 pin voltage becomes less than 1.08\*VFB[2.5Vtyp.]-100mV, the over-voltage error is cancelled.

The error signal  $E_OVP$  may be output during the soft start period at startup. When the gate pulse is stopped by using  $E_OVP$ , it is recommended to mask the error signal, or count the number of error signal occurrence and stop the system when detecting a certain number of times by microcomputer or the like.

Also in case the switching of 2 phase and 4 phase is done by ON/OFF of slave IC in 4 phase application, it is done by pulling up OVP2 pin of slave IC, so that Please be aware that an error signal is output from the E\_OVP pin of the slave IC.

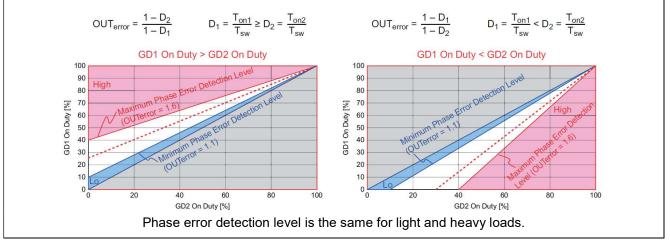

#### 3.5.2 E\_PHASE pin movement by phase error detection 2

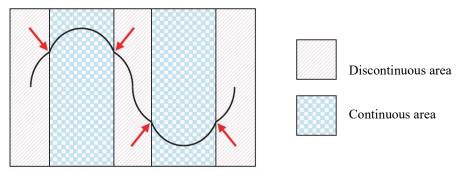

When the duty ratio of GD1, 2 becomes large by abnormal movement such as the open/short destruction of the power element, it's judged to be phase error and E\_PHASE pin operates. When the duty ratio of GD1,2 becomes small close to 1, the phase error is cancelled. The followings show the area judged to be phase error with considering variations of devices.

Figure 8 Phase Error Area

When the duty of GD1 and GD2 is within the deep blue area, E\_PHASE pin is OFF. If it's in red area, E\_PHASE pin turns ON. The white area is dispersion area of phase error detection circuits, where phase error may be detected.

In normal operation, the duty is balanced by feedback control and the phase error does not occur. However, the duty balance may be temporarily lost in transient duration such as sudden change of load or input voltage at power on, to make E\_PHASE pin ON

#### 3.5.3 E\_OCP pin movement by overcurrent detection

When the over-current protection operates, E-DELAY pin start charging. If the over-current is cancelled, E-DELAY discharges. When over-current status continue up to E-DELAY pin voltage being the threshold 2.45V, it's in OCP error. If the overcurrent condition continues, the OCP error condition will also continue.

Connecting a capacitor between E-DELAY pin and GND can adjust the time from the OCP detection to error signal output. The followings outlines OCP timer latch operation.

Figure 9 Over-current Error Operation

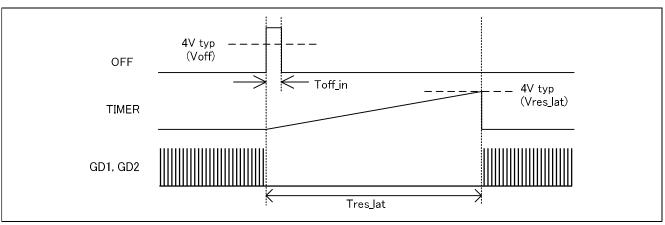

#### 3.6 **OFF** Function

When a pulse signal which amplitude is over than the threshold voltage Voff is added to OFF pin, GD pulse stops and TIMER pin is in charge mode. The OFF function is cancelled when TIMER pin is charged up to 4V(typ.) and the gate pulse is reset and the TIMER pin is discharged rapidly.

The pulse width Toff\_in input to the OFF pin must be shorter than the TIMER pin charging time Tres\_lat.

When stopping with the OFF function by error signal ,since there is a possibility that each error signal is output during transient period such as startup, brownout, rapid load change, it is recommended to mask the error signal during the transient period, or count the number of error signal occurrence and stop the system when detecting a certain number of times by connecting to the OFF pin via a microcomputer or the like. When an error signal is received outside the masking period, follow the regulation of the above pulse for pulses input from the microcomputer to the OFF pin. This latch mode is also cancelled by reducing Vcc pin voltage below UVLO Turn-off Threshold voltage to reset the IC. OFF pin may respond to signals as short as 10ns. To avoid malfunction, it's necessary to construct filters if OFF function is used.

Figure 3.6 OFF Function Operation

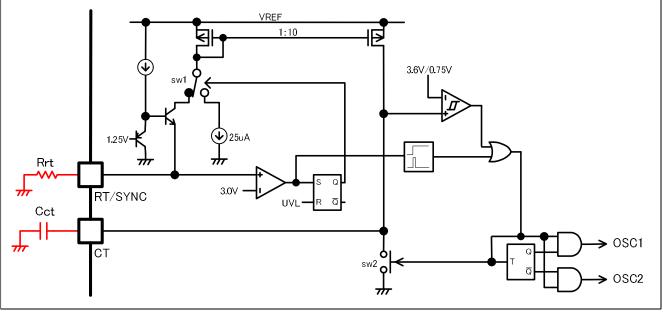

#### 3.7 Synchronous Function

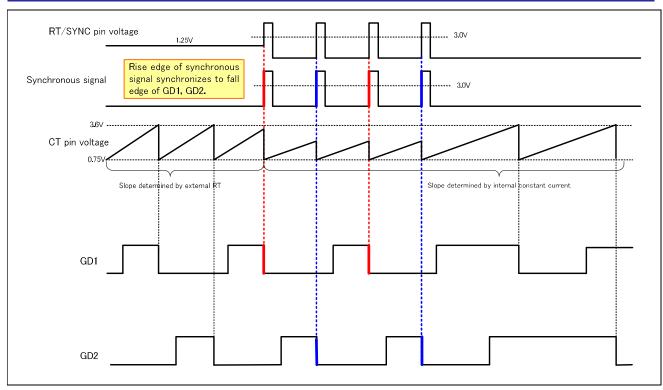

R2A20114BFP switched synchronous mode by inputting synchronous signal into RT/SYNC pin. The followings shows the detail of synchronous operation.

The following figure is outline of built-in oscillator.

Figure 10 Outline of Synchronous Circuits

Synchronous signal is rise edge (3Vtyp. threshold) trigger operation. As shown in the synchronous timing chart, the fall timing of GD1 and GD2 are alternatively determined by rise edge of synchronous signal.

R2A20114BFP switches into synchronous operation mode once RT/SYNC pin voltage exceeds 3Vtyp. In synchronous operation mode, internal switch sw1 turns and the CT charge current is switched to constant current of 250uAtyp.  $\pm$  30%, which is determined in IC internally and does not depend on resistance at RT/SYNC pin. Therefore, the IC operates in this charge current and the frequency by CT pin capacitance unless synchronous input is not provided. Cct should be determined so as to make this frequency slower than the frequency of synchronous signal.

Once 3Vtyp. or more voltage is applied to TR/RYNC pin, sw1 does not turn to RT/SYNC pin side unless supply voltage Vcc is lower than UVL voltage. To release the synchronous operation, IC should be reset by decreasing Vcc.

#### Figure 11 Synchronous Operation

To use synchronous function, please pay attention to the following items.

- 1) Synchronous signal should not be input when IC stops (Vcc is Low)

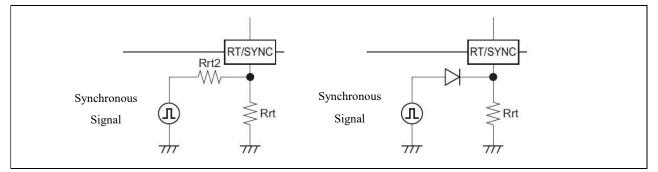

- 2) In case that synchronous circuits are directly connected to RT/SYNC pin, current over the maximum ratings of RT/SYNC pin, 200uA may be applied at startup or switching from normal mode to synchronous mode if the output impedance of synchronous signal circuits is low. (In synchronous mode, the RT/SYNC pin is in high-impedance and, therefore the possibility of current flowing is only at switching into synchronous mode.) In those case, increase of current should be prevented by e.g. inserting a limit resistor or diode as shown below.

Figure 12 Synchronous Signal Input

- 3) In synchronous mode, RT/SYNC pin is in high-impedance and may be influenced by noise or negative voltage. For the case, removing noise by RC filter or clamping negative voltage by SBD is required.

- 4) There is an internal delay between the RT / SYNC pin and the SYNC O pin, and the phase difference does not become 90 ° if the On Duty of the synchronous signal is 50%. Please adjust the phase difference on the slave side with the On Duty of the synchronization signal.

#### 3.8 Synchronous Output Function

SYNC-O pin provides inverted signal of synchronous signal input to RT/SYNC pin.

#### 3.9 **PWM\_IN** Function

This function is to provide PWM\_IN pin at GD1 pin. It enables to use as driver IC with built-in various protection functions for partial switches. This function is available by pulling up PWM\_CNTL pin to VREF pin.

Over-current and over-voltage function operate, therefore additional protection circuits are not required.

If the PWM\_CNTL and VREF pins are shorted, an error signal continues to be output from the E\_OCP pin. If the E\_OCP pin is not used, there is no problem with short circuit, but when using it, pull up the PWM\_CNTL pin to the VREF pin after 500  $\mu$ s after VCC is applied.

#### 4. Design Guide

#### 4.1 Boost inductor

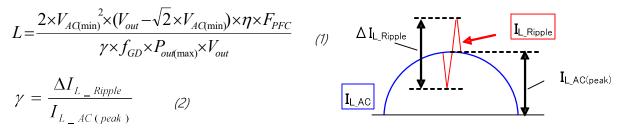

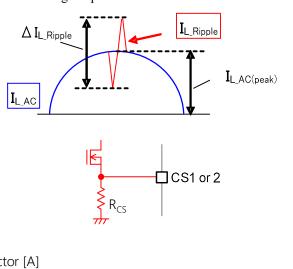

The boost inductor value is determined by an output power and a fixed switching frequency.

A switching frequency must become over 20kHz which is audio frequency to avoid audio noise of an inductor or a input capacitor. Generally it is around 30kHz.

The boost inductor value is obtained by Equation 1 . A conduction loss  $\eta$  input around 0.9.

Vac(min) : Effective value of minimum input voltage [V(rms)]

Vout : Output voltage[V]

Pout : Maximum output power [W]

η : Efficiency

F<sub>PFC</sub> : Power Factor

f<sub>GD</sub> : fixed switching frequency[Hz]

ΔIL\_Ripple : Maximum ripple current of Boost inductor.

IL\_AC(peak) : Peak current of Boost inductor

#### 4.2 Output capacitor

The necessary capacitor value to guarantee voluntary hold-up time is expressed in the next equation.

$$C \text{ out } [F] \geq \frac{2 \times F_{out} \times t \text{ hold}}{V_{out}^2 - V_{out} (\min)}$$

(3)

thold[s] : Hold-up time Vomin[V] : Minimum output voltage

## 4.3 Power MOSFET(IGBT), and boost diode

A peak current flowing on a Power MOSFET(IGBT) or a boost diode  $% 10^{-1}$  is expressed in the next equation. A conduction loss  $\eta$  input around 0.9.

$$I_{in} = \frac{P_{OUT}}{V_{AC(\min)} \times \eta \times F_{PFC}}$$

(4)

$$I_{L(peak)} = (1 + \gamma/2) \times I_{in}/\sqrt{2} \quad (5)$$

I<sub>in</sub>: Effective value of Maximum input current.

I, (peak) : Peak current of Boost inductor

#### 4.4 **Operating Frequency**

#### 4.4.1 Operating Frequency Setting

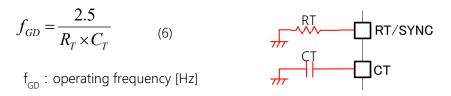

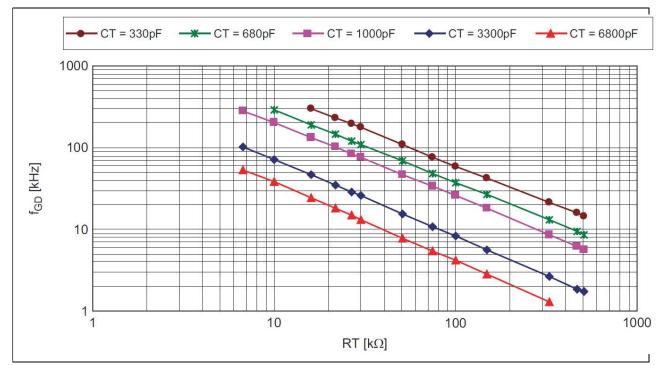

The R2A20114BFP operating frequency fGD is determined by adjusting the timing resistor RT (the RT pin) and the timing capacitance CT (the CT pin).

The operating frequency is approximated by the following expression (6). The expression (6) is the formula that was similar so that an error of the whole range of each capacity value and the resistance value of fig.13 is small. Therefore, the calculation result of the expression (6) does not completely accord with the real frequency. Ct and Rt from the expression (6) is used as an initial setting values. More correct value is calculated from the graph in figure 13 or by Excel Calculation Sheet.

It is necessary to select a 7 k $\Omega$  or more resistance connected to the RT pin, to limit maximum RT current less than 200uA. Also, use a 100 pF or more capacitor connected to CT pin, to reduce effects from parasitic capacitance and noise.

As a reference, the operating frequency fGD when the timing resistor RT and the timing capacitance CT are changed is shown in the figure 13.

Figure 13 Operating Frequency Characteristics

#### 4.4.2 A method to limit Max. Duty of GD

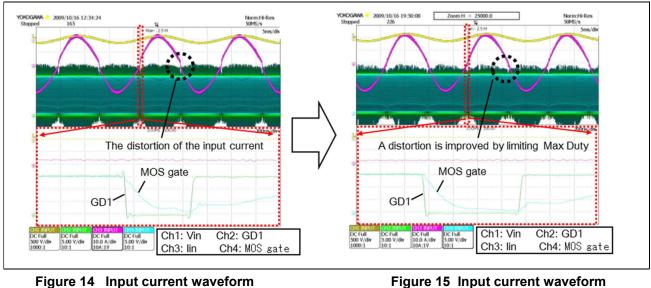

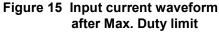

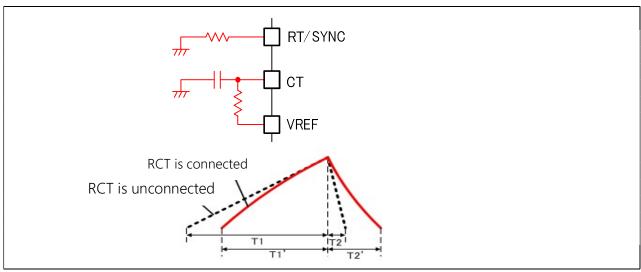

By the setting of the drive circuit, On Duty becomes a little less than 100% value in zero cross of input voltage for the delay of the MOS gate. As a result, there is the case that the input current of zero cross is not normal like figure 14. When such a waveform occurred, Max Duty is limited by connecting resistance between Vref and CT as figure 16, and an input current waveform is improved.

with the distortion at zero cross

Figure 16 Max. Duty limit circuit

Only adding resistor, however, causes oscillation frequency change. Rt and Ct must be adjusted together.

When the fixed number is decided, please decide them with the Excel sheet prepared for.

#### 4.5 Input AC voltage sensing

To turn ON/OFF PFC operation according to input AC voltage, the full-bridge rectification wave is divided by resistors and smoothed by capacitors as expression (12), to apply to BO pin. When PFC ON/OFF is controlled by MCU and is not needed to follow AC voltage, the circuits to apply full-bridge rectifier wave into BO pin are unnecessary. Circuits from full-bridge rectifier wave to VAC pin should be connected.

$$V_{BO} = \frac{2\sqrt{2} \times R_{BO-2} \times V_{ac}}{\pi \times (R_{BO-1} + R_{BO-2})}$$

(12)

$$C_{BO} = \frac{1}{2\pi \times f_c \cdot \left(\frac{R_{BO-1} \times R_{BO-2}}{R_{BO-1} + R_{BO-2}}\right)}$$

(13)

$$Vac : \text{Effective value of minimum input voltage [V(rms)]}$$

$$R_{VAC1}$$

$$R_{VAC2}$$

t<sub>c</sub> : Cutott trequency [Hz]

Be sure to apply signal which is full-bridge rectifier wave divided by resistors to VAC pin. First decide OVP2 pin resistors by expression (20) in 4.10.1 and then decide to meet expression (14)

$$\frac{R_{VAC1}}{R_{VAC2}} = \frac{R_{OVP2\_1}}{R_{OVP2\_2}}$$

(14)

#### 4.6 Resistor of current sensing

Current sensing resistance is determined within expression (15). Small resistance can reduce the loss by resistors, but the over-current value increase together. Need to pay attention to ratings of power elements.

$$R_{CS} \le \frac{0.6\sqrt{2} \times V_{ac} \times \eta \times F_{PFC}}{Pout \times (2+\gamma)}$$

(15)

Vac : Effective value of input voltage [V]

Pout : Maximum output power [W]

η: Efficiency

$F_{PEC}$  : Power Factor

$\gamma$ : Ripple of boost inductor current

ΔIL\_Ripple : Maximum ripple current of Boost inductor [A]

IL\_AC(peak) : Peak current of Boost inductor [A]

### 4.7 Phase Compensation Circuit of Current Amplifier

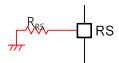

4.7.1 RS pin

$$R_{RS} \left[ \Omega \right] = \frac{L \times 10^9}{2.5 \times R_{CS}} \times \frac{R_{ovp \, 2_2}}{R_{ovp \, 2_1} + R_{ovp \, 2_2}} \quad (16)$$

L : Boost inductor [H]

Rcs : Resistor of Current sense  $[\Omega]$

Vout : Output voltage[V]

As expression (16), RS pin resistance is in proportion to boost inductance and it's necessary to pay attention for the case where current superposition characteristics of inductance is large as dust type inductance. The expression (16) is usually calculated by inductance value at maximum current.

RS pin resistance influences AC input current waveform. Generally, in small RS pin resistance the peak point of AC input current wave tends to expand to be triangular wave as a whole, and in large RS pin resistance the peak point becomes flat to be trapezoidal wave. Please use it as a guide to adjust.

If load regulation deteriorate significantly at maximum load, ON duty may be limited (COMP pin voltage is over 3.8V). Then, adjust by reducing RS pin resistance.

In PFC control, the inductor current becomes discontinuous near zero cross point of AC voltage. This discontinuous area is expanded for smaller boost inductance. This case, at the border line of discontinuous area and continuous area, the following step may be found in AC current. This step damages a fifth harmonic wave.

For the case, reducing RS pin resistance restricts the current rising and improves the step. However too small resistance rises the peak point resulting to a third harmonic wave deterioration. The expression (16) is based on continuous operation and the calculation result will mis-match under long discontinuous area. The resistance may be as small as 1/10 of calculation results in expression (16). Please adjust to be the best harmonic current confirming the input AC current waveform in the actual devices.

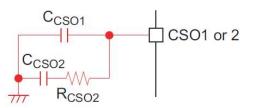

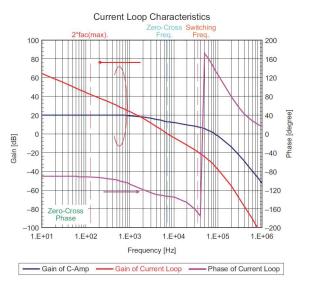

#### 4.7.2 CSO pin

CSO1 pin and CSO2 pin determine the current loop characteristics in PFC control. The current loop is important to shape the AC input current to the sine wave similar to the AC input voltage. Please adjust the following characteristics by Excel fixed values calculation sheet prepared for.

Current loop frequency characteristics should have set below conditions.

• It has enough gain at twice of AC input frequency.

#### R2A20114BFP

- It has enough lower gain at switching frequency.

- It has enough phase margin

As a recommendation,

- Over 40 dB at twice of AC input frequency

- Set zero cross frequency of current loop around 1/10 of switching frequency.

- Around -30 dB at switching frequency

- 60 degrees or more phase margin

Although it's difficult to meet all conditions, please adjust as possible as it's satisfied.

Parts at CSO pin influence the waveform and stability of AC input current. For unstable AC input current, larger Ccso2 usually makes inductor current stable but increases distortion of AC input current waveform.

The same values of external parts should be used for CSO1 and CSO2 pins.

#### 4.8 Resistor of IRAMP pin

The Riramp must be adjusted to be able to output max power with the minimum input voltage. The Riramp is approximated by the expression (17) on the condition that it is operated with CCM in the minimum input voltage and the max power. The calculation by the expression is just approximation. For more accurate values, please use Excel fixed value calculation sheet prepared for. Larger Riramp deteriorates load regulation and smaller value causes current waveform distortion.

Please adjust it, confirming the output voltage and input current waveform.

$$R_{IRAMP}[\Omega] = 4 \times 10^{9} \times \left(\frac{\sqrt{2} \times V_{AC(\min)}}{V_{OUT} \times f_{GD}} - 2 \times 10^{-6}\right) \times \frac{1}{V_{CSO(delta)}}$$

(17)

$$V_{CSO(delta)} : \text{Peak voltage of the CSO pin [V]}$$

(17)

The Vcso(delta) is the voltage which smooths the voltage waveform similar to inductance current which is addition of MOS current detected at CS pin and diode current calculated internally in the IC. It's expressed as (18)

$$V_{CSO(delta)} [V] = \frac{4.5 \sqrt{2} \times P_{out} \times R_{cs}}{V_{AC} \times \eta}$$

(18)

#### 4.9 Capacitor of Soft-start

If PFC circuits does not operate at AC voltage Vacin input, the output voltage of PFC circuits is  $\sqrt{2} \times \text{Vacin}$ . To set the time from PFC starting operation from the voltage to SS pin reaching the defined output voltage, the capacitance Css required to SS pin is calculated in expression (19).

Startup time varies depending on load or input/output conditions, adjust Css under the actual operation after determining the reference value by the calculation.

#### 4.10 **Protection Functions**

#### 4.10.1 OVP2 voltage setting

FB pin has OVP function but may continue normal control operation even if the voltage dividing resistors at FB pin are halfway destroyed to be abnormal resistance values. This case, the FB pin is doing normal control operation and the OVP function at FB pin can't detect the abnormality. OVP2 pin monitors output voltage via another resistors than FB pin and can detect such an abnormality.

$$V_{OVP2} [V] = \frac{R_{ovp2_1} + R_{ovp2_2}}{R_{ovp2_2}} \times 2.5 \times 1.08 \quad (20)$$

After setting the divided resistance at OVP2 pin, set the resistance at VAC pin from the expression (14).

$$\frac{R_{VAC1}}{R_{VAC2}} = \frac{R_{OVP2\_1}}{R_{OVP2\_2}}$$

(14)

OVP2 pin voltage is used as a control signal internally in the IC, voltage corresponding to the output voltage should be applied. If OVP2 function is not used, short-circuit the FB pin and OVP2 pin.

#### 4.10.2 E-DELAY setting

The time between entering OCP status to E\_OCP signal output, tdelay is set.

If E\_OCP signal output is not required when OCP continues, short-circuit E-DELAY pin to GND.

$$C_{delay}[F] = \frac{36 \times 10^{-6}}{2.45} \times t_{delay} \quad (21)$$

#### 4.11 Output Voltage Setting and Frequency Characteristics of Voltage Amp.

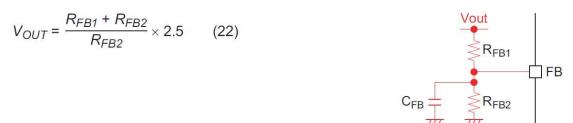

#### 4.11.1 Output voltage setting

R2A20114BFP is feedback controlled so that FB pin is around 2.5V at all times and the output voltage is controlled to be a constant value. The output voltage is determined by voltage dividing resistors at FB in.

#### 4.11.2 COMP parameter setting

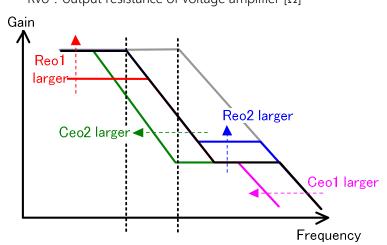

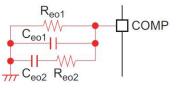

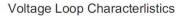

Voltage and current amplifier are transconductance (gm) amplifier. It does not need to feedback for input side. Therefore, it is possible to minimize influence on input circuit by feedback circuit. Gain of gm amplifier is calculated by product of transconductance and output impedance in (23). Gm-v is transconductance of voltage amplifier. Rvo is output resistor of voltage amplifier itself.

As CSO pin, please use Excel fixed value calculation sheet for COMP pin also.

$$G_{V} = G_{m-v} \cdot \frac{1}{\frac{1}{R_{vo}} + \frac{1}{R_{eol}} + j\omega C_{eol} + \frac{1}{R_{eo2}} + \frac{1}{j\omega C_{eo2}}}$$

(23)

Gm-v : transconductance of voltage amplifier [S] Rvo : output resistance of voltage amplifier [ $\Omega$ ]

#### R2A20114BFP

Comp pin determines voltage loop characteristics in PFC control. The voltage loop characteristics is relating to output voltage control and influences on ripple characteristics of output voltage, load regulation, response characteristics and stability.

Voltage loop frequency characteristics should be

- It has enough lower gain at twice of AC input frequency.

- · Zero-cross frequency is lower than AC input frequency

- It has enough phase margin.

As a recommendation,

- Over -30 dB at twice of AC input frequency

- 60 degrees or more phase margin.

Some characteristics conflict and it's difficult to meet all conditions. Please adjust as possible as they're satisfied.

These parameters influence the following characteristics.

Reo1 determines load regulation of output voltage. Smaller resistance increases output voltage change.

In Ceo1, the gain of the frequency twice of AC frequency influences output voltage ripple. Lower gain reduces ripple. Larger Ceo1 reduces the gain, but the response characteristics of the output voltage becomes worse.

Reo2 and Ceo2 make zero to keep phase margin.

These recommendations are just for reference. Operation should be checked in actual power supply devices. Adjust for the required performance by confirming the operation in an actual devices.

#### 4.11.3 **PFC** boost voltage setting

Output voltage can be changed for V\_CNTL pin voltage. The output voltage is calculated by the expression (24) by V\_CNTL pin voltage.

$$V_{OUT} = \frac{R_{FB1} + R_{FB2}}{R_{FB2}} \times \left( 2.5 - \frac{V_{V\_CNTL}}{4} \right)$$

(24)

#### 4.12 Treatment of Each Pin

Input pins of the IC is usually in high-impedance and may be influenced by noise or overshoot/undershoot of input signals. Some output pins require decoupling capacitors for stable operation. The followings describes example setting and point to be attended of each pin. These are for just reference, and it's necessary to confirm by actual devices.

| Pin no. | in no. Pin Name Example setting |                             | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------|---------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | PWM_IN                          | Noise<br>R3 Vo<br>MCU<br>C1 | Long wiring of PWM_IN signal may cause<br>damage by overshoot, undershoot and noise.<br>Remove unnecessary components by RC filter<br>or SBD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 2       | PWM_CNTL                        | PWM_IN used                 | When PWM_IN function is not used, pull-<br>down to GND.<br>When PWM_IN function is used, pull-up to<br>VREF.<br>Please also refer to P.14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 3       | VREF                            | Other circuits              | Since VREF pin is the source of reference<br>voltage in the IC, 0.1uF or more decoupling<br>capacitor should be connected. The<br>decoupling capacitor is connected to AGND<br>pin as close as possible. It's possible to use as<br>voltage source to surrounding circuits but the<br>load should not exceed 10mA.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 4       | во                              | ON/OFF by AC voltage        | BO pin turns ON/OFF gate pulse and the<br>malfunction by noise causes omissions in the<br>gate pulse.<br>In case of ON/OFF corresponding to AC<br>voltage, set the cut off frequency of detecting<br>circuits R1, R2 and C0 to be about 1/10 of AC<br>frequency to reject ripple in AC frequency. If<br>the detecting circuit can't be placed near the<br>IC, add RC filter R3 and C1 whose cut off<br>frequency is about 1/10 of switching<br>frequency to the pin directly to avoid<br>switching noise onto the long wiring.<br>In case of using only ON/OFF functions from<br>MCU signals, also add RC filter R3 and C1<br>whose cut off frequency is about 1/10 of<br>switching frequency to the pin directly to<br>avoid switching noise. |  |

| Pin no.       | Pin Name                  | Example setting                                 | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------------|---------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5             | VAC                       | Noise<br>R1<br>R3<br>Vo<br>C0<br>R2<br>C1<br>TT | Set the detecting circuit R1, R2, C0 between<br>full-bridge rectifier wave and VAC pin to<br>have cutoff frequency which is 20 times of<br>AC frequency to minimize distortion and<br>phase shift.<br>Normally, this detecting circuit filters<br>switching noise but RC filter R3 and C1<br>whose cut off frequency is about 1/10 of<br>switching frequency may be added to the pin<br>directly if necessary in such a case of long<br>wiring from the detecting circuit.<br>Set the ratio of R1/R2 to be the same as<br>resistance ratio in detecting circuit at OVP2<br>pin. |  |

| 6             | PD                        | Noise<br>R3 Vo<br>MCU<br>C1<br>777              | If necessary, RC filter R3 and C1 whose cut<br>off frequency is about 1/10 of switching<br>frequency may be added to the pin directly<br>when PD function is used by MCU control<br>signal.                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 8             | E-DELAY                   |                                                 | Connect a capacitor to the pin as close as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 9<br>10<br>11 | E_OCP<br>E_OVP<br>E_PHASE | R1<br>R3 Vo<br>C0<br>C1<br>777                  | E_OCP, E_OVP, E_PHASE pins are open<br>drain and require pull-up resistor R1 if used.<br>Adding capacitor C0 can decrease the<br>sensitivity of E_OCP, E_OVP, E_PHASE<br>signals.<br>In receiving signal by MCU, they have<br>influence of switching noise caused by long<br>wiring. If necessary, RC filter R3 and C1<br>whose cut off frequency is about 1/10 of<br>switching frequency may be added directly to<br>the MCU.                                                                                                                                                  |  |

| 12            | OFF                       | Noise<br>R3 Vo<br>MCU<br>C1                     | If necessary, RC filter R3 and C1 whose cut<br>off frequency is about 1/10 of switching<br>frequency may be added to the pin directly<br>when OFF function is used by MCU control<br>signal.                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Pin no. | Pin Name | Example setting                                               | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|----------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13      | RS       |                                                               | RS pin provides voltage which is 1/5 of the<br>difference between OVP2 pin voltage and<br>VAC pin voltage. Since the output voltage<br>waveform is like upside down of full-bridge<br>rectifier waveform, set the cut off frequency to<br>be about 20 times of AC frequency to<br>minimize distortion and phase shift.                                                                                                                                                                                                |

| 14      | SS       |                                                               | Adjust the capacitance according to the required startup time of the PFC circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15      | СОМР     |                                                               | Refer to 4.11.2 for the setting.<br>The ripple voltage and the phase at COMP pin<br>influences the harmonic current. This COMP<br>pin circuits determines the frequency<br>characteristics of FB pin and the frequency<br>characteristics of voltage amp, and also<br>determines the ripple voltage and the phase of<br>COMP pin. Smaller ripple voltage and<br>smaller phase shift to AC cycle improve the<br>harmonic current.                                                                                      |

| 16      | V_CNTL   | Noise<br>MCU<br>C1<br>777                                     | If necessary, RC filter R3 and C1 whose cut<br>off frequency is about 1/10 of switching<br>frequency may be added to the pin directly<br>when V_CMTL function is used by DC signal<br>from MCU.<br>When V_CNTL function is used by PWM<br>signal from MCU, DC voltage is input to<br>V_CNTL pin. Then, add RC filter R3 and C1<br>to the pin directly to smooth PWM signal<br>from MCU.                                                                                                                               |

| 17      | FB       | Noise<br>R3<br>Vout<br>R3<br>Vo<br>C0<br>R2<br>C1<br>R2<br>C1 | Ratio of R1 and R2 determines the output<br>voltage.<br>Adjust the cut off frequency of detecting<br>circuit R1, R2, C0 between output voltage to<br>FB pin so that the phase of ripple voltage of<br>COMP pin matches the phase of AC cycle.<br>Normally, this detecting circuit filters<br>switching noise but RC filter R3 and C1<br>whose cut off frequency is about 1/10 of<br>switching frequency may be added to the pin<br>directly if necessary in such a case of long<br>wiring from the detecting circuit. |

| Pin no.              | Pin Name                         | Example setting                                                                      | Cautions                                                                                                                                                                                                                                                                                                              |  |

|----------------------|----------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 18                   | OVP2                             | Noise<br>R1<br>R3<br>Vo<br>C0<br>R2<br>C1<br>TT<br>TT                                | The frequency characteristics of detecting<br>circuit between output voltage and OVP2 pin<br>is made to equivalent to those of FB pin.<br>The ratio of R1/R2 is set according to the over<br>voltage level to be detected. The resistance<br>ratio of VAC pin is adjusted to be the same as<br>this resistance ratio. |  |

| 20                   | TIMER                            |                                                                                      | Connect a capacitor to the pin as close as possible.                                                                                                                                                                                                                                                                  |  |

| 21                   | IRAMP                            |                                                                                      | Voltage which is about 1/5 of COMP pin<br>voltage is output at IRAMP pin. Set the cut<br>off frequency nearly equal to the switching<br>frequency.                                                                                                                                                                    |  |

| 22<br>23             | CSO2<br>CSO1                     |                                                                                      | Refer to 4.7.2 for the setting.                                                                                                                                                                                                                                                                                       |  |

| 24<br>25<br>26<br>27 | CS2<br>CS2_GND<br>CS1_GND<br>CS1 | Noise<br>Current sense<br>resistor<br>C1<br>777                                      | Between current detection resistor and CS pin,<br>add RC filter whose cut off frequency is about<br>1/10 to 1/3 of the switching frequency to the<br>pin directly.<br>CS* pins and CS*_GND pins are connected to<br>the resistors of current detection in a separate<br>wiring.                                       |  |

| 28                   | VCC                              | Noise<br>From auxiliary<br>power                                                     | Noise from auxiliary power may cause<br>unstable operation. In such a case, adding RC<br>filter to the pin directly may have effect to<br>reject the noise for stable operation.                                                                                                                                      |  |

| 32<br>34             | GD2<br>GD1                       | GD<br>W<br>GD<br>W<br>GD<br>W<br>GD<br>W<br>GD<br>W<br>GD<br>W<br>GD<br>W<br>GD<br>W | When driver circuit is added, place near the switching elements.                                                                                                                                                                                                                                                      |  |

| Pin no. | Pin Name | Example setting              | Cautions                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|---------|----------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 36      | SYNC-O   | R3 Vo<br>PWM IC<br>C1<br>777 | Switching noise may be applied by wiring<br>when a PWM-IC in the next stage or MCU<br>receives the signal. If necessary, RC filter R3<br>and C1 whose cut off frequency is about 1/10<br>of noise frequency may be added directly to<br>the PWM-IC or MCU.                                                                                                                |  |  |

| 37      | RT/SYNC  | Self-oscillating operation   | In normal operation, 1.25V voltage is output<br>at RT/SYNC. If necessary construct RC filter<br>whose cut off frequency is 1/10 of switching<br>frequency.<br>In synchronous operation, RT/SYNC pin is in<br>high impedance, influenced by overshoot,<br>undershoot and noise due to synchronous<br>signals wiring. Remove unnecessary<br>components by RC filter or SBD. |  |  |

| 38      | СТ       |                              | Connect a capacitor to the pin as close as possible.                                                                                                                                                                                                                                                                                                                      |  |  |

#### 4.13 Unused Pins

Unused pins in R2A20114BFP is connected as follows. All pins except the table below are used.

| Pin No. | Pin Name            | Connection when unused                                    |

|---------|---------------------|-----------------------------------------------------------|

| 1       | PWM_IN              | GND                                                       |

| 2       | PWM_CNTL            | GND                                                       |

| 4       | BO                  | VREF                                                      |

| 6       | PD                  | GND                                                       |

| 8       | E-DELAY             | Open: when E_OCP is used.<br>GND: when E_OCP is not used. |

| 9,10,11 | E_OCP,E_OVP,E_PHASE | Open                                                      |

| 12      | OFF                 | GND                                                       |

| 14      | SS                  | Open                                                      |

| 36      | SYNC-O              | Open                                                      |

| -       | N.C.                | Open                                                      |

#### 4.14 Notice for PCB Layout

The followings are notices for PCB layout.

- 1. Please make sure PFC IC be located as apart from power stage (MOSFET, DIODE, Boost L) as possible. Specially be careful to MOSFET drain line layout to avoid radiation noise.

- 2. Please separate Power-GND and Signal-GND pattern surely and connect possibly near to the IC. The pattern for Power-GND is widely from output CAP to PGND. And place the capacitor between Vcc and AGND.

- 3. The pattern for resistance RCS of current detection is made an even phase as short as possible, and connect it under the output CAP.

- 4. COMP/VREF external parts are placed as close to the IC pins as possible.

- 5. The filters for CS1, CS2 are placed as close to the IC as possible to avoid radiation noise. CS1, C1\_GND, CS2, CS2 GND lines are connected directly to resistance RCS of current detection in separate wiring.

- 6. The FB resistor is placed as close to the IC as possible to avoid radiation noise.

- 7. The pattern for power stage (MOSFET, DIODE, Boost L) parts is shortened as much as possible.

- 8. For discontinuous current flowing lines, wide and short pattern restricts overshoot of power MOS drain voltage.

- 9. GND of drive circuit is connected to the source of power MOS (Q1). GND current is separated into large current for power circuit and small current for drive circuit.

- 10. When switching ripple voltage of output is too large, film capacitor C3 is added near the diode (D1). Select a film capacitor of good high frequency characteristics.

## Website and Support <website and support,ws>

Renesas Electronics Website <u>http://www.renesas.com/</u>

#### Inquiries

http://www.renesas.com/contact/

All trademarks and registered trademarks are the property of their respective owners.

## Revision History <revision history,rh>

|      |              | Description |                          |

|------|--------------|-------------|--------------------------|

| Rev. | Date         | Page        | Summary                  |

| 1.00 | Nov.07,2016  | -           | New                      |

| 2.00 | July.25.2017 | P.11 etc.   | Writing error correction |

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for

the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use

of these circuits, software, or information.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics

assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade. as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

Refer to "http://www.renesas.com/" for the latest and detailed information.

# RENESAS

#### SALES OFFICES

**Renesas Electronics Corporation**

http://www.renesas.com

Renesas Electronics America Inc. 2801 Scott Boulevard Santa Clara, CA 95050-2549, U.S.A. Tel: +1-408-588-6000, Fax: +1-408-588-6130 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 9251 Yonge Street, St Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-585-100, Fax: +44-1628-585-900 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germany Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100191, P.R.China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, P. R. China 200333 Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tei: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco ... orp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HALII Stage, Indiranagar, Bangalore, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 12F., 234 Teheran-ro, Gangnam-Gu, Seoul, 135-080, Korea Tel: +82-2-558-3737, Fax: +82-2-558-5141