# **RL78 Family**

# Board Support Package Module Using Software Integration System

### Summary

The Renesas board support package SIS module (r\_bsp) forms the foundation of any project that uses Software Integration System (SIS) modules. The r\_bsp is easily configurable and provides all the code needed to get the MCU and the board from reset to the main() function. This document describes r\_bsp conventions and explains how to use it, configure it, and create a BSP for your own board.

### **Device on Which Operation Confirmed**

RL78/F23, F24 Group

RL78/G15 Group

RL78/G16 Group

RL78/G22 Group

RL78/G23 Group

RL78/G24 Group

When using this application note with other Renesas MCUs, careful evaluation is recommended after making modifications to comply with the alternate MCU.

### **Supported Compilers**

- Renesas Electronics C/C++ Compiler Package for RL78 Family

- IAR C/C++ Compiler for Renesas RL78

- LLVM C/C++ Compiler for Renesas RL78

For details of the confirmed operation of each compiler, refer to 7.1, Confirmed Operating Environment.

Limitations apply to some functions. Refer to 4.4, Limitations.

# Contents

| 1.    | Overview                                  | 4  |

|-------|-------------------------------------------|----|

| 1.1   | Terminology                               | 4  |

| 1.2   | File Structure                            | 5  |

| 2.    | Functionality                             | 7  |

| 2.1   | MCU Information                           |    |

| 2.2   | Initial Settings                          |    |

| 2.3   | Global Interrupts                         |    |

| 2.4   | Clock Settings                            |    |

| 2.5   | Stack Area                                | 10 |

| 2.6   | ID Code                                   | 10 |

| 2.7   | Option Bytes                              | 10 |

| 2.8   | RAM/SFR Guard Functionality               | 10 |

| 2.9   | CPU Functionality                         | 11 |

| 2.10  | Disabling Startup                         | 11 |

| 2.10  | 1 Settings to Disable Startup             | 11 |

| 3.    | Configuration                             | 12 |

| 3.1   | Choosing a Platform                       |    |

| 3.2   | Platform Configuration                    |    |

| 3.2.1 | с.<br>С                                   |    |

| 3.2.2 |                                           |    |

| 3.2.3 |                                           |    |

| 3.2.4 |                                           |    |

| 3.2.5 |                                           |    |

| 3.2.6 | RTOS(r_bsp_config.h)                      | 15 |

| 3.2.7 | RTOS(r_bsp_config.inc)                    | 15 |

| 3.2.8 | Clock Settings                            | 16 |

| 3.2.9 | Option Bytes                              | 21 |

| 3.2.1 | 0 Security ID Codes for On-Chip Debugging | 21 |

| 3.2.1 | 1 Startup Disable                         | 22 |

| 3.2.1 | 2 Smart Configurator                      | 22 |

| 3.2.1 | 3 API Functions disable Usage             | 23 |

| 3.2.1 | 4 Parameter check Usage                   | 23 |

| 3.2.1 | 5 Callback Function at Warm Start         | 24 |

| 3.2.1 | 6 Watchdog timer refresh                  | 24 |

| 4.    | API Information                           | 25 |

| 4.1   | Hardware Requirements                     |    |

| 4.2   | Hardware Resource Requirements            |    |

| 4.3   | Software Requirements                     | 25 |

# RL78 Family

# Board Support Package Module Using Software Integration System

| 4.4    | Limitations                                                                          | . 25 |

|--------|--------------------------------------------------------------------------------------|------|

| 4.4.1  | IAR Compiler Limitations                                                             | . 25 |

| 4.4.2  | Watchdog Timer Refresh Limitations                                                   | . 25 |

| 4.5    | Supported Toolchains                                                                 | . 25 |

| 4.6    | Interrupt Vectors Used                                                               | . 25 |

| 4.7    | Header Files                                                                         | . 25 |

| 4.8    | Integer Types                                                                        | . 25 |

| 4.9    | API Typedef                                                                          | . 26 |

| 4.9.1  | Clock Resource                                                                       | . 26 |

| 4.9.2  | Unit of Software Delay                                                               | . 26 |

| 4.10   | Return Values                                                                        | . 26 |

| 4.10.1 | 1 Error Codes                                                                        | . 26 |

| 4.11   | Code Size                                                                            | . 27 |

| 4.12   | "for," "while," and "do while" Statements                                            | . 29 |

| 5. /   | API Functions                                                                        | 30   |

| 5.1    | Overview                                                                             |      |

| 5.2    | R_BSP_StartClock()                                                                   |      |

| 5.2    | R_BSP_StopClock()                                                                    |      |

| 5.4    | R_BSP_SetClockSource()                                                               |      |

| 5.5    | R_BSP_GetFclkFreqHz()                                                                |      |

| 5.6    | R_BSP_ChangeClockSetting()                                                           |      |

| 5.7    | R_BSP_SoftwareDelay()                                                                |      |

| 0.7    |                                                                                      | . 40 |

| 6. I   | Project Setup                                                                        | . 42 |

| 6.1    | Adding the SIS Module                                                                | . 42 |

| 6.2    | Adding the SIS Module to a Project in e <sup>2</sup> studio                          | . 43 |

| 6.2.1  | Adding the SIS Module Using Smart Configurator in e <sup>2</sup> studio              | . 43 |

| 7. /   | Appendix                                                                             | .47  |

| 7.1    | Confirmed Operating Environment                                                      |      |

| 7.2    | Notes on API functions when updating from Rev1.30 to Rev1.40                         |      |

| 7.3    | Notes on the R_BSP_ChangeClockSetting function when updating from Rev1.30 to Rev1.40 |      |

| 7.4    | Notes on the R_BSP_ChangeClockSetting function when updating from Rev1.60 to Rev1.61 |      |

| 1.1    |                                                                                      |      |

| Revis  | sion History                                                                         | . 52 |

### 1. Overview

Before running a user application there are a series of operations that must be performed to get the MCU set up properly. These operations, and their number, will vary depending on the MCU being used. Common examples include: setting up stack(s), initializing memory, configuring the CPU and peripheral hardware clock, and setting up port pins. The steps described in this document must to be followed in order to configure the above items. The r\_bsp is provided in order to make configuration easier.

The r\_bsp provides all the elements needed to get the MCU from reset to the start of the user application's main() function. The r\_bsp also provides common functionality that is needed by many applications. Examples of this include functions to start and stop the clocks and to get the frequency of the CPU and peripheral hardware clock.

The necessary steps after a reset are the same for every application, but this does not mean that the settings will be the same. For example, stack sizes and the clocks used will vary depending on the application. The r\_bsp configuration options are contained in the config header file for easy access.

### 1.1 Terminology

| Term     | Description                                                      |  |

|----------|------------------------------------------------------------------|--|

| Platform | The user's development board. Used interchangeably with "board." |  |

| BSP      | Abbreviation of "board support package."                         |  |

### 1.2 File Structure

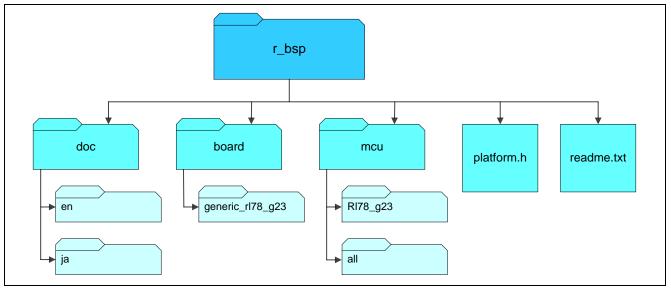

The r\_bsp file structure is shown below in Figure 1.1. The *r\_bsp* folder contains three folders and two files.

The *doc* folder contains r\_bsp documentation.

The board folder contains the generic folders.

There is a generic folder for each supported MCU.

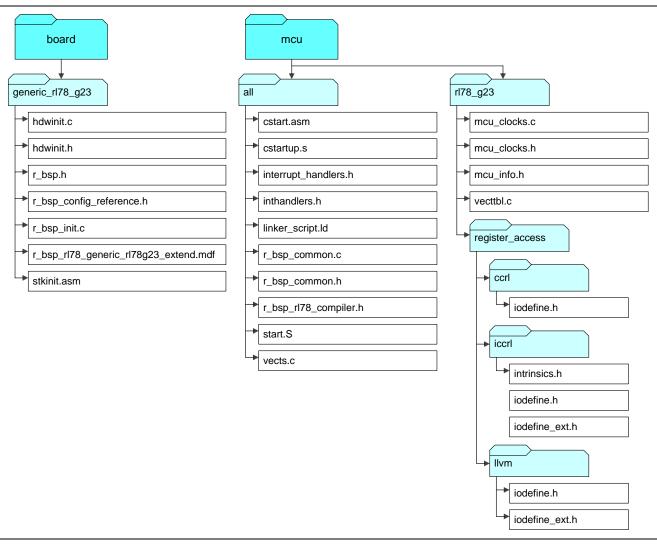

Figure 1.2 shows the contents of the generic folder.

The *mcu* folder contains one folder for each supported MCU. The *mcu* folder also contains the *all* folder, which contains source code common to all MCUs supported by the r\_bsp.

The *platform.h* file allows you to choose your current development platform. It is used to select all the header files from the *board* and *mcu* folders required for your project. This is discussed in more detail in later sections.

The *readme.txt* file provides a summary of information about the r\_bsp.

Figure 1.1 r\_bsp File Structure

### **RL78** Family

### Board Support Package Module Using Software Integration System

Figure 1.2 Structure of Generic Folder

### 2. Functionality

This section describes in detail the functionality provided by the r\_bsp.

### 2.1 MCU Information

One of the main benefits of the r\_bsp is that it lets you define the global system settings only once, in a single place in the project, and those settings are then shared throughout. This information is defined in the r\_bsp and can then be used by the SIS modules and user code. SIS modules use this information to automatically configure their code to match your system configuration. If the r\_bsp did not provide this information, you would have to specify system information to each SIS module separately.

Configuring the r\_bsp is discussed in Section 3. The r\_bsp uses this configuration information to set macro definitions in *mcu\_info.h*. An example of an MCU-specific macro in *mcu\_info.h* is shown below.

| Definition                                | Description                                                                                                                                                                                                                                                                 |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSP_MCU_FAMILY_ <mcu_family></mcu_family> | Which MCU Family this MCU belongs to. Example:<br>BSP_MCU_FAMILY_RL78 would be defined if the MCU was<br>an RL78/G23.                                                                                                                                                       |

| BSP_MCU_SERIES_ <mcu_series></mcu_series> | Which MCU Series this MCU belongs to. Example:<br>BSP_CMU_SERIES_RL78G2X would be defined if the MCU<br>was RL78/G23.                                                                                                                                                       |

| BSP_MCU_GROUP_ <mcu_group></mcu_group>    | Which MCU group this MCU belongs to. Example:<br>BSP_MCU_GROUP_RL78G23 would be defined if the MCU<br>was RL78/G23.                                                                                                                                                         |

| BSP_ <clock>_HZ</clock>                   | Each of these macros corresponds to one of the MCU's clocks.<br>Each macro defines the corresponding clock's frequency in<br>hertz (Hz). For example, BSP_LOCO_HZ defines the LOCO<br>frequency in Hz, and BSP_SUB_CLOCK_HZ defines the<br>subsystem clock frequency in Hz. |

### 2.2 Initial Settings

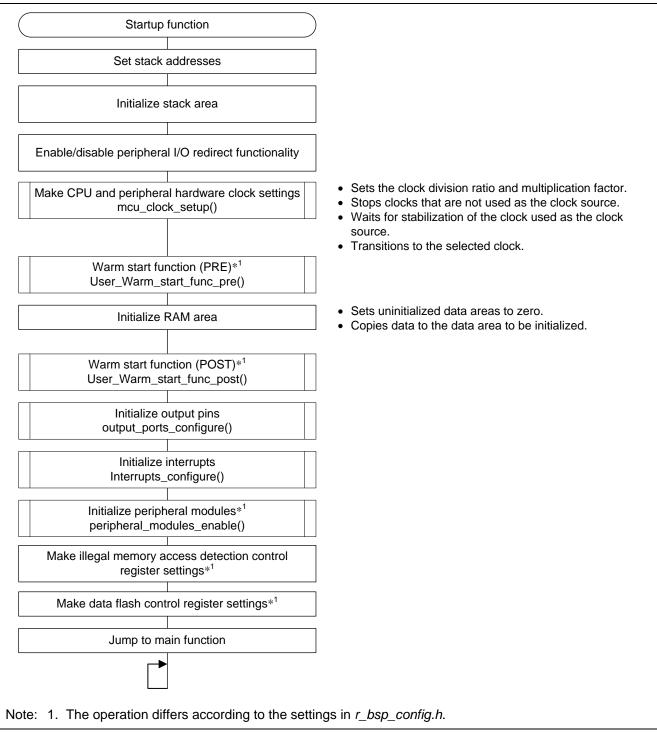

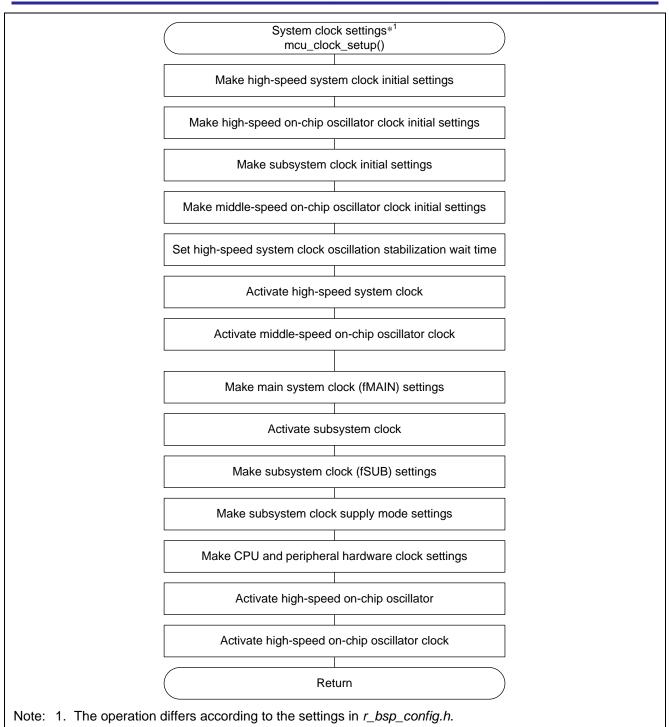

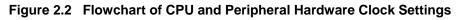

The \_start function is set as the reset vector for the MCU when using the Renesas compiler, and the PowerON\_Reset function is set as the reset vector when using the LLVM compiler. The \_\_iar\_program\_start function is set as the reset vector for the MCU when using the IAR compiler. The \_start function, PowerON\_Reset\_PC function, or function \_\_iar\_program\_start function (the startup function) performs various types of initialization processing to get the MCU ready to use the user application. The flowcharts below show startup function operations and CPU and peripheral hardware clock settings.

Figure 2.1 Flowchart of Startup Function

### 2.3 Global Interrupts

Interrupts are disabled after a reset. Enable interrupts as needed. Use the BSP\_ENABLE\_INTERRUPT function to enable interrupts and the BSP\_DISABLE\_INTERRUPT function to disable them. For details, refer to 5.1, Overview.

RL78 devices have a fixed vector table. The fixed vector table is located at a static location at the top of the memory map.

The fixed vector table is defined in *iodefine.h.*

### 2.4 Clock Settings

CPU and peripheral hardware clock settings are made during r\_bsp initialization. Clocks are configured based upon the user's settings in the *r\_bsp\_config.h* file (see 3.2.5). Clock settings are applied before the C runtime environment is initialized. When a clock is selected, the code in the r\_bsp implements the required delays to allow the selected clock to stabilize.

### 2.5 Stack Area

The stacks are configured and initialized by the startup function after a reset. When using the IAR compiler it is possible to specify the stack size using a GUI.

### 2.6 ID Code

RL78 MCUs have a ID code stored in ROM that protects the MCU's memory from being read through a debugger, or in serial boot mode, in an attempt to extract the firmware from the device. ID code resides in the on-chip debug security ID setting memory. The value of the security ID is specified in the compile options of the Renesas compiler environment. In the IAR or LLVM environment it is specified in *r\_bsp\_config.h.* For details of ID code options, refer to the Option Bytes and On-Chip Debug Function chapters in your MCU's hardware manual.

### 2.7 Option Bytes

The option bytes are located in the flash memory of RL78 MCUs. The option bytes are referenced automatically after power-on or a reset, and the specified function settings are applied. Option bytes can be used to specify settings for the watchdog timer or voltage detection circuit, for example. Option byte setting values are specified in the compile options of the Renesas compiler or LLVM environment. In the IAR environment they are specified in *r\_bsp\_config.h* (see 3.2.6).

### 2.8 RAM/SFR Guard Functionality

RL78 MCUs are provided with an illegal memory access detection control register that protects the data in the specified RAM space as well as the data in the control registers of the port, interrupt, clock control, voltage detection circuit, and RAM parity error detection functions. The setting values can be specified in *r\_bsp\_config.h*.

### 2.9 CPU Functionality

API functions are provided for making settings related to CPU functionality such as enabling and disabling interrupts. Refer to Section 5 for details.

### 2.10 Disabling Startup

To disable startup, manually delete the startup assembler code. The names of the files containing the startup assembler code for each environment are as follows:

- Renesas compiler: cstart.asm

- LLVM compiler: start.S

- IAR compiler: cstartup.s

Additionally, you will need to add your own startup code.

#### 2.10.1 Settings to Disable Startup

Make settings as described below to disable BSP startup processing.

#### (1) Configuration File Settings

Specify your own startup processing in  $r\_bsp\_config.h$ . Some BSP API functions and peripheral SIS modules reference the contents of  $r\_bsp\_config.h$ . Note that some SIS modules may not function correctly if there are discrepancies between the details of the startup processing you created and the contents of  $r\_bsp\_config.h$ .

The BSP information referenced by the peripheral SIS modules is generated based on  $r\_bsp\_config.h$ , so it is necessary to ensure that the details of the startup processing you created and the contents of  $r\_bsp\_config.h$  match.

Figure 2.3 illustrates configuration file settings.

Figure 2.3 Configuration File Settings

### 3. Configuration

Two header files are used to configure the r\_bsp. One is used to choose the platform, and the other to configure the chosen platform.

### 3.1 Choosing a Platform

The r\_bsp provides board support packages for a variety of MCUs. Choosing the platform to be used is accomplished by modifying the *platform.h* file located in the *r\_bsp* folder.

### 3.2 Platform Configuration

After selecting a platform, you must configure it. The file *r\_bsp\_config.h* contains the platform settings. Each platform has a configuration file called *r\_bsp\_config\_reference.h*, which is located in the platform's *board* folder.

The contents of each *r\_bsp\_config.h* file differs according to the MCU associated with it, but many of the options are the same. The following sections provide details on these configuration options. Note that each macro starts with the common prefix "BSP\_CFG\_," which makes them easy to search for and identify.

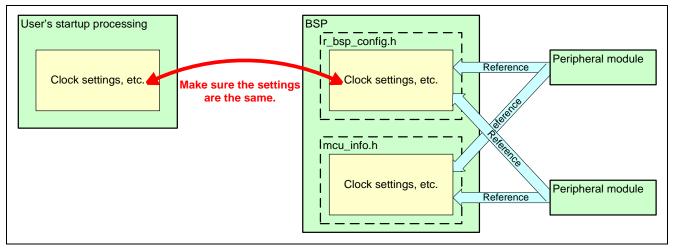

When using Smart Configurator, the configuration options can be set on the software component configuration screen. Setting values are automatically reflected in *r\_bsp\_config.h* when adding modules to a user project.

### 3.2.1 MCU Product Part Number Information

The MCU's product part number information makes it possible to provide a variety of information about the MCU along with the r\_bsp. Information related to the MCU's product part number is defined at the beginning of the configuration file. All of these macros start with "BSP\_CFG\_MCU\_PART." Some MCUs have more product part number–related information than others, but the standard definitions are listed below.

| Table 3.1 | <b>Product Part Number Definitions</b> |

|-----------|----------------------------------------|

|-----------|----------------------------------------|

| Definition                          | Value                                                 | Description                                                  |

|-------------------------------------|-------------------------------------------------------|--------------------------------------------------------------|

| BSP_CFG_MCU_PART_ROM_SI<br>ZE       | See comments above #define in <i>r_bsp_config.h</i> . | Defines the ROM size.                                        |

| BSP_CFG_MCU_PART_PIN_NU<br>M        |                                                       | Defines the pin count.                                       |

| BSP_CFG_MCU_PART_HAS_DA<br>TA_FLASH |                                                       | Defines whether or not the device incorporates flash memory. |

| BSP_CFG_MCU_PART_ROM_T<br>YPE       |                                                       | Defines the device type.                                     |

### RL78 Family

### 3.2.2 Peripheral I/O Redirection Register

RL78 MCUs provide functionality to switch the ports assigned to alternate functions. After a reset the r\_bsp makes MCU pin assignment settings using the pin assignment configuration macros in *r\_bsp\_config.h*.

### Table 3.2 Peripheral I/O Redirection Register Definitions

| Definition                   | Corresponding Device                                         | Value                                                       | Description                                                                                                                                                                             |

|------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSP_CFG_PIORx<br>(x=0-5)     | RL78/G22,<br>RL78/G23                                        | See comments above<br>#define in<br><i>r_bsp_config.h</i> . | Defines ports to which<br>alternate functions are<br>assigned.<br>The value of x varies<br>from device to device.<br>Refer to r_bsp_config.h<br>for the details of each<br>definition.  |

| BSP_CFG_PIORyy<br>(yy=00-99) | RL78/F23,<br>RL78/F24,<br>RL78/G15,<br>RL78/G16,<br>RL78/G24 | See comments above<br>#define in<br><i>r_bsp_config.h.</i>  | Defines ports to which<br>alternate functions are<br>assigned.<br>The value of yy varies<br>from device to device.<br>Refer to r_bsp_config.h<br>for the details of each<br>definition. |

### RL78 Family Board Support Package Module Using Software Integration System

### 3.2.3 RAM/SFR Guard Functionality

RL78 MCUs are provided with functionality to protect the data in the specified RAM space as well as the data in the control registers of the port, interrupt, clock control, voltage detection circuit, and RAM parity error detection functions. After a reset the r\_bsp makes MCU guard area settings using the guard functionality configuration macros in *r\_bsp\_config.h*.

| Table 3.3 | RAM/SFR | Guard | Functionality | / Definitions |

|-----------|---------|-------|---------------|---------------|

|-----------|---------|-------|---------------|---------------|

| Definition                                         | Value                                                 | Description                                                                                                                                                 |

|----------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSP_CFG_INVALID_MEMORY_<br>ACCESS_DETECTION_ENABLE | See comments above #define in <i>r_bsp_config.h</i> . | Defines whether or not illegal memory access detection is performed.                                                                                        |

| BSP_CFG_RAM_GUARD_FUNC                             |                                                       | Defines the size of the RAM guard space.                                                                                                                    |

| BSP_CFG_PORT_FUNCTION_G<br>UARD                    |                                                       | Defines whether or not guarding is applied to port function control registers.                                                                              |

| BSP_CFG_INT_FUNCTION_GUA<br>RD                     |                                                       | Defines whether or not guarding is applied to interrupt function registers.                                                                                 |

| BSP_CFG_CHIP_STATE_CTRL_<br>GUARD                  |                                                       | Defines whether or not guarding is<br>applied to clock control, voltage<br>detection circuit, and RAM parity error<br>detection function control registers. |

#### 3.2.4 RAM start address

RL78 MCUs has a function that can change the start address of RAM.

After reset, r\_bsp sets the RAM start address using the RAMSAR address definition and RAM start address definition in r\_bsp\_config.inc.

#### Table 3.4 RAM start address setting register Definitions

| Definition                              | Value                    | Description                                                                                           |

|-----------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------|

| BSP_CFG_ASM_RAMSAR_ADD<br>RESS          | Set in r_bsp_config.inc. | Defines the address of the RAMSAR<br>register.<br>No setting is required in the CC-RL<br>environment. |

| BSP_CFG_ASM_RAM_GUARD_<br>START_ADDRESS |                          | Defines the RAM start address.<br>Do not define for devices that do not<br>have a RAMSAR register.    |

### 3.2.5 Data Flash Access Restriction

RL78 MCUs are provided with functionality to enable or disable access to the data flash. After a reset the r\_bsp makes data flash access settings using the data flash access restriction functionality configuration macros in *r\_bsp\_config.h*.

| Table 3.5 | Data Flash Access Restriction Definitions |

|-----------|-------------------------------------------|

|-----------|-------------------------------------------|

| Definition              | Value                      | Description                        |

|-------------------------|----------------------------|------------------------------------|

| BSP_CFG_DATA_FLASH_ACCE | See comments above         | Defines whether access to the data |

| SS_ENABLE               | #define in r_bsp_config.h. | flash is enabled or disabled.      |

### RL78 Family Board Support Package Module Using Software Integration System

### 3.2.6 RTOS(r\_bsp\_config.h)

Defines if a RTOS is being used in the current application. After a reset the r\_bsp makes RTOS settings using the RTOS functionality configuration macros in r\_bsp\_config.h.

| Table 3.6 | RTOS(r_ | _bsp_ | _config.h) | Definitions |

|-----------|---------|-------|------------|-------------|

|-----------|---------|-------|------------|-------------|

| Definition        | Value                    | Description                        |

|-------------------|--------------------------|------------------------------------|

| BSP_CFG_RTOS_USED | 0=RTOS is not used.      | Defines whether access to the data |

|                   | 1=Reserved.              | flash is enabled or disabled.      |

|                   | 2=Reserved.              | Set the same value as              |

|                   | 3=Reserved.              | BSP_CFG_ASM_RTOS_USED in           |

|                   | 4=Renesas ITRON is used. | r_bsp_config.inc.                  |

### 3.2.7 RTOS(r\_bsp\_config.inc)

Defines if a RTOS is being used in the current application. After a reset the r\_bsp makes RTOS settings using the RTOS functionality configuration macros in r\_bsp\_config.inc.

#### Table 3.7 RTOS(r\_bsp\_config.inc) Definitions

| Definition            | Value                    | Description                        |

|-----------------------|--------------------------|------------------------------------|

| BSP_CFG_ASM_RTOS_USED | 0=RTOS is not used.      | Defines whether access to the data |

|                       | 1=Reserved.              | flash is enabled or disabled.      |

|                       | 2=Reserved.              | Set the same value as              |

|                       | 3=Reserved.              | BSP_CFG_RTOS_USED in               |

|                       | 4=Renesas ITRON is used. | r_bsp_config.h.                    |

### 3.2.8 Clock Settings

The available clocks vary among RL78 MCUs, but the same basic concepts apply to all. After a reset the r\_bsp initializes the MCU clocks using the clock configuration macros in *r\_bsp\_config.h*.

| Definition               | Value                                            | Description                             |

|--------------------------|--------------------------------------------------|-----------------------------------------|

| BSP_CFG_HISYSCLK_SOURCE  | 0 = Port                                         | Defines the oscillation source of the   |

|                          | 1 = Connected                                    | high-speed system clock.                |

|                          | crystal/ceramic oscillator                       |                                         |

|                          | 2 = External clock input                         |                                         |

| BSP_CFG_HISYSCLK_OPERATI | (X1 oscillation mode)                            | Defines high-speed system clock         |

| ON                       | 0 = X1 oscillator operating                      | operation control.                      |

|                          | 1 = X1 oscillator stopped                        |                                         |

|                          | (External clock input mode)                      |                                         |

|                          | 0 = External clock from                          |                                         |

|                          | EXCLK pin is valid                               |                                         |

|                          | 1 = External clock from                          |                                         |

|                          | EXCLK pin is invalid                             |                                         |

|                          | (Port mode)                                      |                                         |

|                          | 0 = I/O  port                                    |                                         |

|                          | 1 = I/O port                                     |                                         |

| BSP_CFG_SUBCLK_SOURCE    | 0 = Input port                                   | Defines the oscillation source of the   |

|                          | 1 = Connected crystal                            | subsystem clock.                        |

|                          | oscillator                                       |                                         |

|                          | 2 = External clock input                         |                                         |

| BSP_CFG_SUBCLK_OPERATIO  | (XT1 oscillation mode)                           | Defines subsystem clock operation       |

| Ν                        | 0 = XT1 oscillator operating                     | control.                                |

|                          | 1 = XT1 oscillator stopped                       |                                         |

|                          | (External clock input mode)                      |                                         |

|                          | 0 = External clock from                          |                                         |

|                          | EXCLKS pin is valid                              |                                         |

|                          | 1 = External clock from<br>EXCLKS pin is invalid |                                         |

|                          | (Port mode)                                      |                                         |

|                          | 0 = Input port                                   |                                         |

|                          | 1 = Input port                                   |                                         |

| BSP_CFG_MOCO_SOURCE      | 0 = Middle-speed on-chip                         | Defines whether the middle-speed        |

| BSP CFG MOCO OPERATION   | oscillator stopped                               | on-chip oscillator clock operates or is |

| BSF_CIG_MOCO_OFERATION   | 1 = Middle-speed on-chip                         | stopped.                                |

|                          | oscillator operating                             |                                         |

| BSP_CFG_OCOCLK_SOURCE    | 0 = High-speed on-chip                           | Defines the clock source used as the    |

|                          | oscillator clock                                 | main on-chip oscillator clock (foco).   |

|                          | 1 = Middle-speed on-chip                         |                                         |

|                          | oscillator clock                                 |                                         |

| BSP_CFG_MAINCLK_SOURCE   | 0 = Main on-chip oscillator                      | Defines the clock source used as the    |

|                          | clock (f <sub>OCO</sub> )                        | main system clock (f <sub>MAIN</sub> ). |

|                          | 1 = High-speed system clock                      |                                         |

|                          | (f <sub>MX</sub> )                               |                                         |

| BSP_CFG_SUBSYSCLK_SOUR   | 0 = Subclock                                     | Defines the clock source used as the    |

| CE                       | 1 = Low-speed on-chip                            | subsystem clock.                        |

|                          | oscillator clock                                 |                                         |

| Definition                        | Value                                                   | Description                                                               |

|-----------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------|

| BSP_CFG_FCLK_SOURCE               | 0 = Main system clock (f <sub>MAIN</sub> )              | Defines the clock source used as the                                      |

|                                   | $1 = $ Subsystem clock ( $f_{SUB}$ )                    | CPU and peripheral hardware clock                                         |

|                                   |                                                         | (f <sub>CLK</sub> ).                                                      |

| BSP_CFG_XT1_OSCMODE               | 0 = Low-power oscillation 1                             | Defines the oscillation mode of the                                       |

|                                   | (default)                                               | XT1 oscillator circuit.                                                   |

|                                   | 1 = Normal oscillation                                  |                                                                           |

|                                   | 2 = Low-power oscillation 2                             |                                                                           |

|                                   | 3 = Low-power oscillation 3                             |                                                                           |

| BSP_CFG_FMX_HZ                    | High-speed system clock                                 | Defines the frequency of the high-                                        |

|                                   | frequency (unit: Hz)                                    | speed system clock.                                                       |

| BSP_CFG_X1_WAIT_TIME_SEL          | $0 = 2^8 / f_X$                                         | Defines the oscillation stabilization                                     |

|                                   | $1 = 2^{9}/f_{X}$                                       | time of the X1 clock.                                                     |

|                                   | $2 = 2^{10}/f_X$                                        |                                                                           |

|                                   | $3 = 2^{11}/f_X$                                        |                                                                           |

|                                   | $4 = 2^{13}/f_X$<br>5 = 2 <sup>15</sup> /f <sub>X</sub> |                                                                           |

|                                   | $5 = 2^{17}/f_X$<br>6 = 2 <sup>17</sup> /f <sub>X</sub> |                                                                           |

|                                   | $6 = 2^{17}/f_X$<br>7 = 2 <sup>18</sup> /f <sub>X</sub> |                                                                           |

| BSP_CFG_ALLOW_FSUB_IN_S           | 0 = Supply of subsystem                                 | Defines supply of the subsystem                                           |

| TOPHALT                           | clock to peripheral functions                           | clock in STOP mode and in HALT                                            |

|                                   | enabled                                                 | mode when the CPU is operating on                                         |

|                                   | 1 = Supply of subsystem                                 | the subsystem clock.                                                      |

|                                   | clock to peripheral functions                           |                                                                           |

|                                   | other than realtime clock                               |                                                                           |

|                                   | stopped                                                 |                                                                           |

| BSP_CFG_ALLOW_FSL_IN_STO<br>PHALT | 0 = Enables supply of                                   | Defines setting in STOP mode or                                           |

| PHALT                             | subsystem/low-speed on-chip oscillator select clock to  | HALT mode while subsystem/low-<br>speed on-chip oscillator select clock   |

|                                   | peripheral functions.                                   | is selected as CPU clock.                                                 |

|                                   | 1 = Stops supply of                                     |                                                                           |

|                                   | subsystem/low-speed on-chip                             |                                                                           |

|                                   | oscillator select clock to                              |                                                                           |

|                                   | peripheral functions.                                   |                                                                           |

| BSP_CFG_FIL_OPERATION             | 0 = Low-speed on-chip                                   | Defines selection of CPU/peripheral                                       |

|                                   | oscillator stopped.                                     | hardware clock(fCLK).                                                     |

|                                   | 1 = Low-speed on-chip                                   |                                                                           |

|                                   | oscillator operating.                                   | Defines the energing cleak of the                                         |

| BSP_CFG_RTC_OUT_CLK_SOU<br>RCE    | 0 = Subsystem clock                                     | Defines the operating clock of the realtime clock, 32-bit interval timer, |

|                                   | 1 = Low-speed on-chip<br>oscillator clock               | UARTO and UART1 serial interfaces,                                        |

|                                   |                                                         | remote control signal reception                                           |

|                                   |                                                         | function, and clock output/buzzer                                         |

|                                   |                                                         | output control circuit.                                                   |

| BSP_CFG_HOCO_DIVIDE               | See comments above                                      | Defines the frequency of the high-                                        |

|                                   | #define in <i>r_bsp_config.h</i> .                      | speed on-chip oscillator.                                                 |

|                                   |                                                         | Use an option byte (000C2H) to                                            |

|                                   |                                                         | specify the setting of FRQSEL3. See                                       |

| RSD CEC WAKELID MODE              | 0 = Normal activation                                   | 2.7 for the setting procedure.                                            |

| BSP_CFG_WAKEUP_MODE               | 0 = Normal activation<br>1 = Fast activation            | Defines the high-speed on-chip<br>oscillator activation setting when      |

|                                   |                                                         | STOP mode is canceled and when                                            |

|                                   |                                                         | transitioning to SNOOZE mode.                                             |

| BSP_CFG_FIH_SEL                   | See comments above                                      | Defines the frequency of the high-                                        |

|                                   | #define in r_bsp_config.h.                              | speed on-chip oscillator.                                                 |

|                                   |                                                         |                                                                           |

| Definition               | Value                                                        | Description                                              |

|--------------------------|--------------------------------------------------------------|----------------------------------------------------------|

| BSP_CFG_PFB_ENABLE       | 0 = Disables the prefetch                                    | Defines control of the prefetch buffer.                  |

|                          | buffer.                                                      |                                                          |

|                          | 1 = Enables the prefetch                                     |                                                          |

|                          | buffer.                                                      |                                                          |

| BSP_CFG_FLASH_MODE       | 0 = LP (low-power main)<br>mode                              | Defines selection of flash operation mode.               |

|                          | 1 = LS (low-speed main)                                      | mode.                                                    |

|                          | mode                                                         |                                                          |

|                          | 2 = HS (high-speed main)                                     |                                                          |

|                          | mode                                                         |                                                          |

| BSP_CFG_MOSC_DIVIDE      | $0 = f_{MX}$                                                 | Defines the frequency dividing ratio of                  |

|                          | $1 = f_{MX}/2$                                               | the high-speed system clock.                             |

|                          | $2 = f_{MX}/4$<br>$3 = f_{MX}/8$                             |                                                          |

|                          | $3 = I_{MX}/8$<br>4 = f <sub>MX</sub> /16                    |                                                          |

| BSP CFG MOCO DIVIDE      | 0 = 4  MHz                                                   | Defines the frequency of the middle-                     |

|                          | 1 = 2  MHz                                                   | speed on-chip oscillator.                                |

|                          | 2 = 1 MHz                                                    |                                                          |

| BSP_CFG_FMP_DIVIDE       | See comments above                                           | Defines fMP clock division control.                      |

|                          | #define in r_bsp_config.h.                                   |                                                          |

| BSP_CFG_PLL_DIVIDE       | See comments above                                           | Defines control of PLL frequency                         |

| BSP_CFG_PLL_OPERATION    | #define in <i>r_bsp_config.h.</i><br>0 = Stops PLL operation | division selection.<br>Defines control of PLL operation. |

| BSP_CFG_PLLCLK_OPERATION | 1 = Starts PLL operation                                     | Dennes control of PEL operation.                         |

| N                        |                                                              |                                                          |

| BSP_CFG_PLLCLK_SOURCE    | 0 = Stops supply of the on-                                  | Defines control of the PLL operating                     |

|                          | chip oscillator                                              | clock supply.                                            |

|                          | clock(fOCO)/high-speed<br>system clock(fMX).                 |                                                          |

|                          | 1 = Enables supply of the on-                                |                                                          |

|                          | chip oscillator                                              |                                                          |

|                          | clock(fOCO)/high-speed                                       |                                                          |

|                          | system clock(fMX).                                           |                                                          |

| BSP_CFG_FMAIN_DIVIDE     | 0 = No division                                              | Defines control of PLL input clock                       |

|                          | 1 = Divided by 2 (fMAIN = 16<br>MHz input only)              | (fPLLI) division selection.                              |

|                          | 2 = Divided by 4 (fMAIN = 20)                                |                                                          |

|                          | MHz input only)                                              |                                                          |

| BSP_CFG_PLL_MULTI        | See comments above                                           | Defines control of PLL multiplication                    |

|                          | #define in r_bsp_config.h.                                   | selection.                                               |

| BSP_CFG_PLL_MODE         | 0 = Clock through mode                                       | Defines control of clock mode                            |

|                          | (fMAIN)<br>1 = PLL-clock-selected mode                       | selection.                                               |

|                          | (fPLL)                                                       |                                                          |

| BSP_CFG_FPLL_HZ          | PLL clock frequency                                          | Defines the frequency of the PLL                         |

|                          | (unit: Hz)                                                   | clock.                                                   |

| BSP_CFG_LOCKUP_WAIT_COU  | 0 = Selects 128/fMAIN                                        | Defines control of setting lock-up wait                  |

| NT_SEL                   | 1 = Selects 256/fMAIN                                        | counter.                                                 |

|                          | 2 = Selects 512/fMAIN                                        |                                                          |

|                          | 3 = Selects 1024/fMAIN                                       |                                                          |

| Definition         Value         Description           BSP_CFG_CAN_CLOCK_OPER         0 = Stops CAN X1 clock (X)<br>supply.         Stops CAN X1 clock<br>(X) supply.           BSP_CFG_LIN1_CLOCK_SOUR         0 = Stelets the fLX clock         Defines control of selecting LIN1<br>communication clock source<br>supply         Defines control of supplying or<br>stopping LIN1 communication clock source.           BSP_CFG_LIN0_CLOCK_OPER         0 = Stops LIN1<br>communication clock source<br>supply         Defines control of selecting LIN0<br>communication clock source           BSP_CFG_LIN0_CLOCK_SOUR         0 = Selects the fICLK clock<br>1 = Selects the fMX clock         Defines control of supplying or<br>stopping LIN1 communication clock<br>source.           BSP_CFG_TRD_CLOCK_SOUR         0 = Selects the fICLK clock<br>1 = Selects Stel<br>LIN0<br>communication clock source<br>supply         Defines control of supplying or<br>stopping LIN0 communication clock<br>source.           BSP_CFG_TRD_CLOCK_SOUR         0 = Selects Stel<br>Loop count<br>(unit: number of times)         Defines the subsystem clock.           BSP_CFG_FIHWAITTIME         Loop count<br>(unit: number of times)         Defines the high-speed on-chip<br>oscillator clock sollation stabilization<br>wait time.           BSP_CFG_FIHWAITTIME         Loop count<br>(unit: number of times)         Defines the indele-speed on-chip<br>oscillator clock sollation stabilization<br>wait time.           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times) </th <th></th> <th>1</th> <th></th>                                                                                                                                                                                                                                                                                                                         |                          | 1                         |                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------|---------------------------------------|

| ATION       supply.       stopping CAN X1 clock (KX).         BSP_CFG_LIN1_CLOCK_SOUR       0 = Selects the fCLK clock       Defines control of selecting LIN1         CE       1 = Selects the fKX clock       Defines control of selecting LIN1         BSP_CFG_LIN1_CLOCK_OPER       0 = Stops LIN1       Defines control of selecting LIN1         ATION       1 = Enables LIN1       Defines control of selecting LIN0         CE       1 = Selects the fKX clock       Defines control of selecting LIN0         CE       1 = Selects the fKX clock       Defines control of selecting LIN0         CE       1 = Selects the fKX clock       Defines control of supplying or stopping LIN1 communication clock source.         BSP_CFG_LIN0_CLOCK_SOUR       0 = Stops LIN0       Defines control of supplying or stopping LIN0 communication clock source.         Stopping LIN0       0 = Stops LIN0       Defines control of TRDe clock source.         Supply       1 = Enables LIN0       Defines control of TRDe clock source.         Supply       1 = Selects TSL       Defines control of TRDe clock source.         BSP_CFG_SUBWAITTIME       Loop count       Defines to busystem clock oscillation stabilization wait time.         BSP_CFG_FIHWAITTIME       Loop count       Defines the high-speed on-chip oscillator clock scillation stabilization wait time.         BSP_CFG_FILWAITTIME       Loop count       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |                           | -                                     |

| I = Enables CAN X1 clock<br>(X) supply.         Interpretation           BSP_CFG_LIN1_CLOCK_SOUR<br>CE         0 = Selects the fCLK clock<br>1 = Selects the fLX clock<br>0 = Stops LIN1<br>communication clock source<br>supply         Defines control of supplying or<br>stopping LIN1 communication clock source<br>supply           BSP_CFG_LIN0_CLOCK_OPER<br>ATION         0 = Selects the fCLK clock<br>1 = Selects the fLK clock         Defines control of supplying or<br>stopping LIN1 communication clock source<br>supply           BSP_CFG_LIN0_CLOCK_OPER<br>ATION         0 = Stelects the fMX clock         Defines control of supplying or<br>stopping LIN1 communication clock source.           BSP_CFG_LIN0_CLOCK_OPER<br>ATION         0 = Stelects the fIX clock         Defines control of supplying or<br>stopping LIN2 communication clock source<br>supply           BSP_CFG_TRD_CLOCK_SOUR<br>CE         0 = Stelects fLN0<br>communication clock source<br>supply         Defines control of TRDe clock<br>selection.           BSP_CFG_TRD_CLOCK_SOUR<br>CE         0 = Selects fLK or fMP<br>selects fSL         Defines the subsystem clock<br>source.           BSP_CFG_SUBWAITTIME         Loop count<br>(unit: number of times)         Defines the subsystem clock<br>wait time.           BSP_CFG_FIHWAITTIME         Loop count<br>(unit: number of times)         Defines the lin2/speed on-chip<br>oscillator clock scillation stabilization<br>wait time.           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the loop count using the<br>main system clock.*1           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         D                                                                                                                                                                                                                                                                                                                                                          |                          |                           |                                       |

| (X) supply.         Defines control of selecting LIN1           BSP_CFG_LIN1_CLOCK_OPER         0 = Stops LIN1         Communication clock source.           BSP_CFG_LIN1_CLOCK_OPER         0 = Stops LIN1         Defines control of supplying or stopping LIN1 communication clock source.           BSP_CFG_LIN0_CLOCK_OPER         0 = Stops LIN1         Defines control of supplying or stopping LIN1 communication clock source.           BSP_CFG_LIN0_CLOCK_SOUR         0 = Stops LIN0         Defines control of supplying or stopping LIN0 communication clock source.           BSP_CFG_LIN0_CLOCK_SOUR         0 = Stops LIN0         Defines control of supplying or stopping LIN0 communication clock source.           ATION         0 = Stops LIN0         Defines control of supplying or stopping LIN0 communication clock source.           BSP_CFG_TRD_CLOCK_SOUR         0 = Stops LIN0         Defines control of supplying or stopping LIN0 communication clock source.           BSP_CFG_SUBWAITTIME         Loop count         Defines the subsystem clock source.           BSP_CFG_FIRD_CLOCK_SOUR         0 = Selects fCLK or fMP         Defines the subsystem clock.           BSP_CFG_SIBWAITTIME         Loop count         Defines the subsystem clock.           BSP_CFG_FIHWAITTIME         Loop count         Defines the high-speed on-chip oscillator clock soillator stabilization wait time.           BSP_CFG_FILWAITTIME         Loop count         Defines the sublex stin using the main system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ATION                    |                           | stopping CAN X1 clock (fX).           |

| BSP_CFG_LIN1_CLOCK_SOUR         0 = Selects the fCLK clock<br>1 = Selects the fMX clock         Defines control of selecting LIN1<br>communication clock source.           BSP_CFG_LIN1_CLOCK_OPER<br>ATION         0 = Stops LIN1<br>communication clock source<br>supply         Defines control of supplying or<br>stopping LIN1 communication clock<br>source.           BSP_CFG_LIN0_CLOCK_SOUR         0 = Selects the fCLK clock         Defines control of supplying or<br>stopping LIN1 communication clock source<br>supply           BSP_CFG_LIN0_CLOCK_OPER<br>ATION         0 = Stops LIN0<br>communication clock source<br>supply         Defines control of supplying or<br>stopping LIN0 communication clock<br>source.           BSP_CFG_TRD_CLOCK_OPER<br>ATION         0 = Stops LIN0<br>communication clock source<br>supply         Defines control of TRDe clock<br>source.           BSP_CFG_TRD_CLOCK_SOUR<br>CE         0 = Selects fCLK or fMP<br>selects fL         Defines tontrol of TRDe clock<br>selection.           BSP_CFG_SUBWAITTIME         Loop count<br>(unit: number of times)         Defines tontrol of TRDe clock<br>selection.           BSP_CFG_FIHWAITTIME         Loop count<br>(unit: number of times)         Defines the subsystem clock oscillation<br>scillator clock socillation stabilization<br>wait time.           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the high-speed on-chip<br>oscillator clock socillation stabilization<br>wait time.           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the loop count using the<br>main system clock.*1           BSP_CFG_FILWAITTIME <td< td=""><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                        |                          |                           |                                       |

| CE         1 = Selects the fMX clock         communication clock source.           BSP_CFG_LIN1_CLOCK_OPER         0 = Stops LIN1         Defines control of supplying or stopping LIN1 communication clock source.           ATION         1 = Enables LIN1         Defines control of supplying or stopping LIN1 communication clock source.           BSP_CFG_LIN0_CLOCK_SOUR         0 = Selects the fCLK clock         Defines control of supplying or stopping LIN1 communication clock source.           BSP_CFG_LIN0_CLOCK_OPER         0 = Selects the fMX clock         Defines control of supplying or stopping LIN0 communication clock source.           BSP_CFG_TRD_CLOCK_SOUR         0 = Selects fLN0 communication clock source supply         Defines control of TRDe clock source.           BSP_CFG_TRD_CLOCK_SOUR         0 = Selects fLX or fMP         Defines control of TRDe clock source.           BSP_CFG_SUBWAITTIME         Loop count (unit: number of times)         Defines the subsystem clock oscillation stabilization wait time.           BSP_CFG_FIHWAITTIME         Loop count (unit: number of times)         Defines the inde-speed on-chip oscillator of clock oscillation stabilization wait time.           BSP_CFG_FILWAITTIME         Loop count (unit: number of times)         Defines the inde-speed on-chip oscillation stabilization wait time.           BSP_CFG_FILWAITTIME         Loop count (unit: number of times)         Defines the loop count using the main system clock.* <sup>1</sup> BSP_CFG_FILWAITTIME         Loop co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |                           |                                       |

| BSP_CFG_LIN1_CLOCK_OPER         0 = Stops LIN1<br>communication clock source<br>supply         Defines control of supplying or<br>stopping LIN1 communication clock<br>source.           BSP_CFG_LIN0_CLOCK_SOUR         0 = Selects the fCLK clock         Defines control of selecting LIN0<br>communication clock source.           BSP_CFG_LIN0_CLOCK_OPER<br>ATION         0 = Stepts LIN0<br>communication clock source<br>supply         Defines control of supplying or<br>stopping LIN0 communication clock<br>source.           BSP_CFG_TRD_CLOCK_OPER<br>ATION         0 = Stepts LIN0<br>communication clock source<br>supply         Defines control of TRDe clock<br>source.           BSP_CFG_TRD_CLOCK_SOUR         0 = Selects fiel KN2 clock         Defines control of TRDe clock<br>source.           BSP_CFG_TRD_CLOCK_SOUR         0 = Selects fiel KN2         Defines control of TRDe clock<br>source.           BSP_CFG_TRD_CLOCK_SOUR         0 = Selects fiel KS         Defines the subsystem clock.           BSP_CFG_SUBWAITTIME         Loop count<br>(unit: number of times)         Defines the subsystem clock.           BSP_CFG_FIHWAITTIME         Loop count<br>(unit: number of times)         Defines the loop count using the<br>main system clock.           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the loop count using the<br>main system clock.           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the table variatime for the<br>PLL multiplication setting.           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number o                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |                           |                                       |

| ATION       communication clock source<br>supply       stopping LIN1 communication clock<br>source.       stopping LIN1 communication clock<br>source.         BSP_CFG_LIN0_CLOCK_SOUR       0 = Selects the fCLK clock<br>1 = Selects the fMX clock<br>CE       Defines control of selecting LIN0<br>communication clock source<br>supply         BSP_CFG_LIN0_CLOCK_OPER       0 = Selects the fMX clock<br>communication clock source<br>supply       Defines control of supplying or<br>stopping LIN0 communication clock<br>source.         BSP_CFG_TRD_CLOCK_SOUR       0 = Selects fCLK or fMP<br>1 = Enables LIN0<br>communication clock source<br>supply       Defines control of TRDe clock<br>selection.         BSP_CFG_SUBWAITTIME       Loop count<br>(unit: number of times)       Defines the subsystem clock<br>oscillation stabilization wait time.<br>Defined as the loop count using the<br>main system clock.*1         BSP_CFG_FIHWAITTIME       Loop count<br>(unit: number of times)       Defines the high-speed on-chip<br>oscillator clock oscillation stabilization<br>wait time.<br>Defined as the loop count using the<br>main system clock.*1         BSP_CFG_FILWAITTIME       Loop count<br>(unit: number of times)       Defines the inide-speed on-chip<br>oscillator clock oscillation stabilization<br>wait time.<br>Defined as the loop count using the<br>main system clock.*1         BSP_CFG_FILWAITTIME       Loop count<br>(unit: number of times)       Defines the low-speed on-chip<br>oscillator clock oscillation stabilization<br>wait time.<br>Defined as the loop count using the<br>main system clock.*1         BSP_CFG_FILWAITTIME       Loop count<br>(unit: number of times)       Defines the look-count using the<br>main system clock.*1 <td></td> <td>1 = Selects the fMX clock</td> <td>communication clock source.</td>                                                                                                                                                                                                           |                          | 1 = Selects the fMX clock | communication clock source.           |

| supply<br>1 = Enables LIN1<br>communication clock source<br>supply         source.           BSP_CFG_LIN0_CLOCK_SOUR         0 = Selects the fCLK clock         Defines control of supplying or<br>communication clock source<br>supply           BSP_CFG_LIN0_CLOCK_OPER<br>ATION         0 = Stops LIN0<br>communication clock source<br>supply         Defines control of supplying or<br>stopping LIN0 communication clock<br>source.           BSP_CFG_TRD_CLOCK_OPER<br>CE         0 = Stops LIN0<br>communication clock source<br>supply         Defines control of TRDe clock<br>selection.           BSP_CFG_TRD_CLOCK_SOUR         0 = Selects fSL         Defines the subsystem clock<br>selection.           BSP_CFG_SUBWAITTIME         Loop count<br>(unit: number of times)         Defines the subsystem clock<br>selection.           BSP_CFG_FIHWAITTIME         Loop count<br>(unit: number of times)         Defines the subsystem clock.*1           BSP_CFG_FIHWAITTIME         Loop count<br>(unit: number of times)         Defines the india-speed on-chip<br>oscillator clock oscillation stabilization<br>wait time.           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the loop count using the<br>main system clock.*1           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the toop count using the<br>main system clock.*1           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defined as the loop count using the<br>main system clock.*1           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |                           |                                       |

| 1 = Enables LIN1<br>communication clock source<br>supply         Defines control of selecting LIN0           BSP_CFG_LIN0_CLOCK_OPER<br>ATION         0 = Stops LIN0<br>communication clock source<br>supply         Defines control of supplying or<br>stopping LIN0 communication clock<br>source.           BSP_CFG_TRD_CLOCK_OPER<br>ATION         0 = Stops LIN0<br>communication clock source<br>supply         Defines control of supplying or<br>stopping LIN0 communication clock<br>source.           BSP_CFG_TRD_CLOCK_SOUR<br>CE         0 = Selects fCLK or fMP<br>1 = Selects fSL         Defines the subsystem clock<br>selection.           BSP_CFG_SUBWAITTIME         Loop count<br>(unit: number of times)         Defines the subsystem clock.*1           BSP_CFG_FIHWAITTIME         Loop count<br>(unit: number of times)         Defines the subsystem clock.*1           BSP_CFG_FIHWAITTIME         Loop count<br>(unit: number of times)         Defines the nigh-speed on-chip<br>oscillator clock socillation stabilization<br>wait time.           BSP_CFG_FIHWAITTIME         Loop count<br>(unit: number of times)         Defines the idp-speed on-chip<br>oscillator clock socillation stabilization<br>wait time.           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the loop count using the<br>main system clock.*1           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the loop count using the<br>main system clock.*1           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the stable wait time for the<br>PLL multiplication setalij.<br>Defined as the loop co                                                                                                                                                                                                                                                                                                                                                                | ATION                    |                           |                                       |

| communication clock source<br>supply         communication clock source<br>supply           BSP_CFG_LIN0_CLOCK_SOUR         0 = Selects the fCLK clock         Defines control of selecting LIN0<br>communication clock source.           BSP_CFG_LIN0_CLOCK_OPER         0 = Stops LIN0<br>communication clock source<br>supply         Defines control of supplying or<br>stopping LIN0 communication clock<br>source.           BSP_CFG_TRD_CLOCK_SOUR         0 = Stops LIN0<br>communication clock source<br>supply         Defines control of TRDe clock<br>source.           BSP_CFG_TRD_CLOCK_SOUR         0 = Selects fCLK or fMP         Defines control of TRDe clock<br>selection.           BSP_CFG_SUBWAITTIME         Loop count<br>(unit: number of times)         Defines the subsystem clock<br>oscillation stabilization wait time.<br>Defined as the loop count using the<br>main system clock.*1           BSP_CFG_FIHWAITTIME         Loop count<br>(unit: number of times)         Defines the subsystem clock.*1           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the indid-speed on-chip<br>oscillator clock oscillation stabilization<br>wait time.<br>Defined as the loop count using the<br>main system clock.*1           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the indid-speed on-chip<br>oscillator clock scillation stabilization<br>wait time.<br>Defined as the loop count using the<br>main system clock.*1           BSP_CFG_FILWAITTIME         Loop count<br>(unit: number of times)         Defines the stable wait time for the<br>PLL multiplication setting.<br>Defines the stable wait time for the<br>main system clock.*1                                                                                                                                                                                                                                                                                                                                   |                          |                           | source.                               |

| supply         selects the fLLK clock           BSP_CFG_LIN0_CLOCK_OPER         1 = Selects the fMX clock         communication clock source.           BSP_CFG_LIN0_CLOCK_OPER         0 = Stops LIN0         communication clock source.           ATION         Defines control of supplying or stopping LIN0 communication clock source.         befines control of supplying or stopping LIN0 communication clock source.           BSP_CFG_TRD_CLOCK_OPER         0 = Stops LIN0 communication clock source.         befines control of TRDe clock source.           BSP_CFG_TRD_CLOCK_SOUR         0 = Selects fLK or fMP         befines control of TRDe clock selection.           BSP_CFG_SUBWAITTIME         Loop count (unit: number of times)         Defines the subsystem clock.*1           BSP_CFG_FIHWAITTIME         Loop count (unit: number of times)         Defines the high-speed on-chip oscillator clock socillation stabilization wait time.           BSP_CFG_FIHWAITTIME         Loop count (unit: number of times)         Defines the high-speed on-chip oscillator clock.*1           BSP_CFG_FILWAITTIME         Loop count (unit: number of times)         Defines the loop count using the main system clock.*1           BSP_CFG_FILWAITTIME         Loop count (unit: number of times)         Defines the loop count using the main system clock.*1           BSP_CFG_FILWAITTIME         Loop count (unit: number of times)         Defines the loop count using the main system clock.*1           BSP_CFG_FILWAITTIME </td <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |                           |                                       |