# RL78/G14

## R01AN1231EJ0110 Rev. 1.10 June 1, 2013

# Setting the D/A Converter's Normal Mode

# **Abstract**

This document describes a method to output analog voltage using the D/A converter in the RL78/G14 Group MCU.

# **Products**

RL78/G14

When using this application note with other Renesas MCUs, careful evaluation is recommended after making modifications to comply with the alternate MCU.

# **Contents**

| 1. | Spe | ecific | ations                                  | 3    |

|----|-----|--------|-----------------------------------------|------|

| 2. | Ор  | eratio | on Confirmation Conditions              | 4    |

| 3. |     |        | re                                      |      |

|    | 3.1 |        | dware Configuration                     |      |

|    | 3.2 | Pin    | Used                                    | 5    |

| 4. | Sof | ftwar  | e                                       | 6    |

|    | 4.1 | Оре    | eration Overview                        | 6    |

|    | 4.2 | Opt    | ion-Setting Memory                      | 8    |

|    | 4.3 | Var    | iables                                  | 8    |

|    | 4.4 | Fun    | ctions                                  | 8    |

|    | 4.5 | Fun    | ction Specifications                    | 9    |

|    | 4.6 | Flov   | vcharts                                 | . 11 |

|    | 4.6 | 6.1    | Overall Flowchart                       | . 11 |

|    | 4.6 | 6.2    | Initial Setting                         | . 11 |

|    | 4.6 | 6.3    | Initial Setting of Peripheral Functions | . 12 |

|    | 4.6 | 6.4    | Initial Setting of the CPU Clock        | . 12 |

|    | 4.6 | 6.5    | Initial Setting of TAU0                 | . 13 |

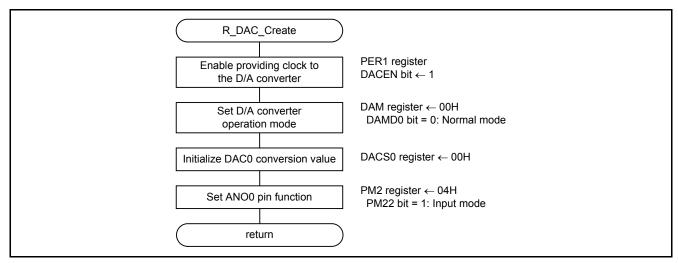

|    | 4.6 | 6.6    | Initial Setting of the D/A Converter    | . 21 |

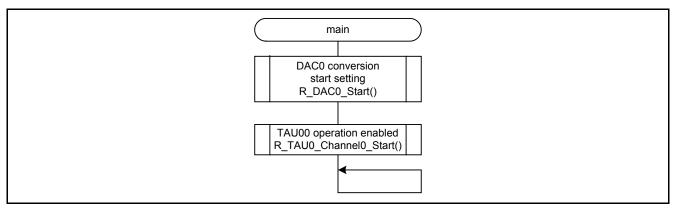

|    | 4.6 | 6.7    | Main Processing                         | . 23 |

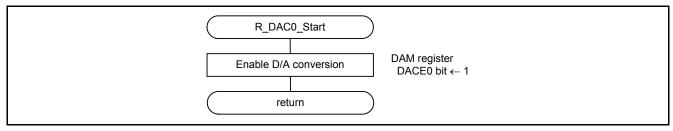

|    | 4.6 | 6.8    | DAC0 Conversion Start Setting           | . 24 |

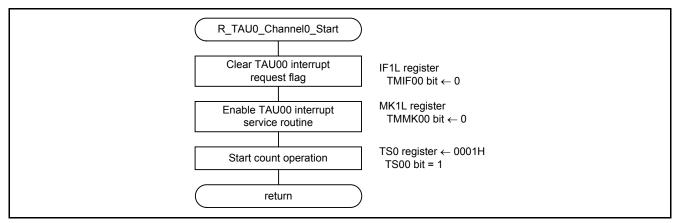

|    | 4.6 | 6.9    | TAU00 Operation Enable Setting          | . 25 |

|    | 4.6 | 6.10   | TAU00 Interrupt                         | . 27 |

|    | 4.6 | 6.11   | D/A Conversion Value Switch Processing  | . 27 |

|    | 4.6 | 6.12   | DAC0 Conversion Value Setting           | . 28 |

| 5. | Sar | mple   | Code                                    | . 29 |

| 6  | Do. | foron  | nco Documents                           | 20   |

# 1. Specifications

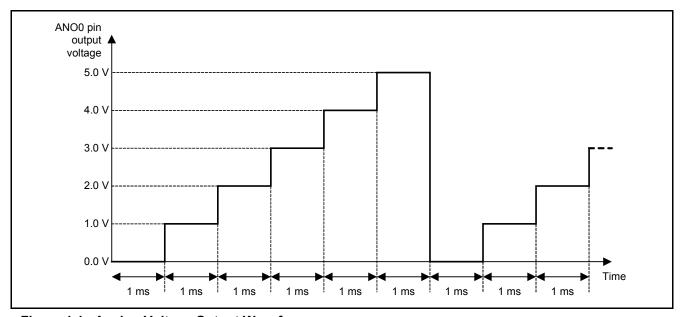

Output analog voltage from the ANO0 pin using the D/A converter. Output for the analog voltage starts at 0.0~V and the output level changes every millisecond in the following order:

$$0.0~V \rightarrow 1.0~V \rightarrow \cdots~4.0~V \rightarrow 5.0~V \rightarrow 0.0~V \rightarrow 1.0~V~\cdots$$

Table 1.1 lists the Peripheral Functions and Their Applications. Figure 1.1 shows the Analog Voltage Output Waveform.

**Table 1.1 Peripheral Functions and Their Applications**

| Peripheral Function                                  | Application                                    |

|------------------------------------------------------|------------------------------------------------|

| D/A converter 0 (hereinafter referred to as DAC0)    | Output the analog voltage                      |

| Timer array unit 0 (hereinafter referred to as TAU0) | Generate a period to change the analog voltage |

Figure 1.1 Analog Voltage Output Waveform

# 2. Operation Confirmation Conditions

The sample code accompanying this application note has been run and confirmed under the conditions below.

**Table 2.1 Operation Confirmation Conditions**

| Item                   | Contents                                                                |  |  |  |  |  |  |  |

|------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|--|

| MCU used               | RL78/G14 (R5F104PJA)                                                    |  |  |  |  |  |  |  |

| Operating frequencies  | • Internal high-speed oscillator clock (fносо): 16 MHz (typical)        |  |  |  |  |  |  |  |

| Operating frequencies  | ◆ CPU/peripheral hardware clock (fclk): 16 MHz                          |  |  |  |  |  |  |  |

| Operating voltage      | 5.0 V (2.9 to 5.5 V)                                                    |  |  |  |  |  |  |  |

| Operating voltage      | LVD operation (VLVH): Reset mode rising edge 2.81 V/falling edge 2.75 V |  |  |  |  |  |  |  |

| Integrated development | Renesas Electronics Corporation                                         |  |  |  |  |  |  |  |

| environment            | CubeSuite+ V1.02.00                                                     |  |  |  |  |  |  |  |

| C compiler             | Renesas Electronics Corporation                                         |  |  |  |  |  |  |  |

| C compiler             | CA78K0R V1.40                                                           |  |  |  |  |  |  |  |

| RL78/G14 code library  | Renesas Electronics Corporation                                         |  |  |  |  |  |  |  |

| RE70/014 Code library  | CodeGenerator for RL78/G14 V1.01.01                                     |  |  |  |  |  |  |  |

## 3. Hardware

# 3.1 Hardware Configuration

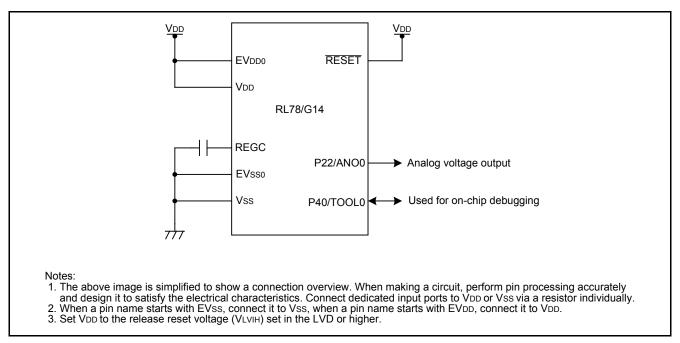

Figure 3.1 shows the Hardware Configuration used in this document.

Figure 3.1 Hardware Configuration

# 3.2 Pin Used

Table 3.1 lists the Pin Used and Its Function.

Table 3.1 Pin Used and Its Function

| Pin Name | I/O    | Function                  |

|----------|--------|---------------------------|

| P22/ANO0 | Output | Output the analog voltage |

#### 4. Software

# 4.1 Operation Overview

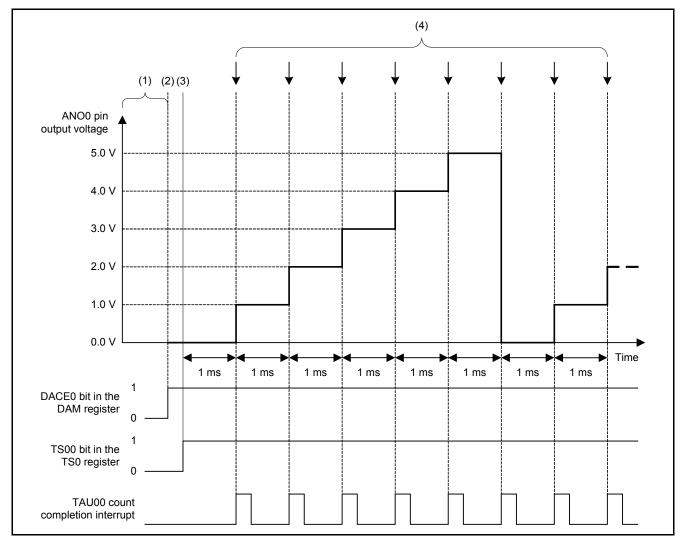

Output the analog voltage from the ANO0 pin using DAC0. The analog output voltage immediately after DAC0 conversion operation is enabled is 0.0 V.

Use TAU0 channel 0 (hereinafter referred to as TAU00) in interval timer mode and generate interrupts every millisecond. Rewrite the DACS0 register value in the count completion interrupt service routine of TAU00 to change the analog output voltage. Use the value stored in the D/A conversion value table for the DACS0 register and output the analog output voltage repeatedly in the following order:

$$0.0~V \rightarrow 1.0~V \rightarrow \cdots~4.0~V \rightarrow 5.0~V \rightarrow 0.0~V \rightarrow 1.0~V \cdots$$

The D/A conversion value table lists D/A conversion values to output 0.0 V, 1.0 V, 2.0 V, 3.0 V, 4.0 V, and 5.0 V as the analog output voltage when VDD is 5.0 V. Use the value calculated based on the following calculating formula for the D/A conversion value.

Analog output voltage of the D/A converter (VANO0) = reference voltage for the D/A converter (VDD)  $\times$  (DACS0)  $\div$  256

Settings of DAC0 and TAU00 are shown below.

#### DAC0 settings:

- Use normal mode for the operation mode.

- Use the ANO0 pin.

#### TAU00 settings:

- Use interval timer mode for the operation mode.

- Set 1 ms for the interrupt period.

- Use the TAU00 count completion interrupt.

- Use fclk (16 MHz) for the count source.

- (1) Initial settings

- Perform initial settings of DAC0 and TAU00. Set the D/A conversion value to the DACS0 register to output 0.0 V from the ANO0 pin.

- (2) Enable the D/A conversion operation.

The analog voltage which was D/A converted for the DACS0 register value is output from the ANO0 pin.

- (3) Start the TAU00 count. Start counting 1 ms.

- (4) TAU00 count completion interrupt Set the D/A conversion value to the DACS0 register.

Figure 4.1 shows the Timing Diagram.

Figure 4.1 Timing Diagram

#### 4.2 **Option-Setting Memory**

Table 4.1 lists the Option-Setting Memory Configured in the Sample Code. When necessary, set a value suited to the user system.

Table 4.1 Option-Setting Memory Configured in the Sample Code

| Address       | Setting Value | Contents                                                                 |

|---------------|---------------|--------------------------------------------------------------------------|

| 000C0H/010C0H | 11101111B     | Watchdog timer operation is stopped (count is stopped after reset)       |

| 000C1H/010C1H | 01111111B     | LVD reset mode Detection voltage: Rising edge 2.81 V/falling edge 2.75 V |

| 000C2H/010C2H | 11101001B     | Internal high-speed oscillation HS mode: 16 MHz                          |

| 000C3H/010C3H | 10000100B     | On-chip debugging enabled                                                |

#### 4.3 **Variables**

Table 4.2 lists the Global Variables.

Table 4.2 Global Variables

| Type    | Variable Name | Contents                     | Functions Used |

|---------|---------------|------------------------------|----------------|

| uint8_t | da_data[]     | D/A conversion value table   | da_out_change  |

| uint8_t | da_cnt        | D/A conversion value counter | da_out_change  |

#### 4.4 **Functions**

Table 4.3 lists the Functions.

Table 4.3 Functions

| Function Name              | Outline                                 |

|----------------------------|-----------------------------------------|

| hdwinit                    | Initial setting                         |

| R_Systeminit               | Initial setting of peripheral functions |

| R_CGC_Create               | Initial setting of the CPU clock        |

| R_TAU0_Create              | Initial setting of TAU0                 |

| R_DAC_Create               | Initial setting of the D/A converter    |

| main                       | Main processing                         |

| R_DAC0_Start               | DAC0 conversion start setting           |

| R_TAU0_Channel0_Start      | TAU00 operation enable setting          |

| r_tau0_channel0_interrupt  | TAU00 interrupt                         |

| da_out_change              | D/A conversion value switch processing  |

| R_DAC0_Set_ConversionValue | DAC0 conversion value setting           |

#### 4.5 **Function Specifications**

The following tables list the sample code function specifications.

hdwinit

**Outline** Initial setting

Header None

**Declaration** void hdwinit(void)

**Description** Perform the initial setting of peripheral functions.

**Argument** None **Return Value** None

R Systeminit

**Outline** Initial setting of peripheral functions

Header None

void R\_Systeminit(void) **Declaration**

Perform the initial setting of peripheral functions used in this document. **Description**

**Argument Return Value** None

R\_CGC\_Create

Outline Initial setting of the CPU clock

Header r\_cg\_cgc.h

**Declaration** void R\_CGC\_Create(void)

Perform the initial setting of the CPU clock. Description

**Argument** None **Return Value** None

R\_TAU0\_Create

Outline Initial setting of TAU0

Header r\_cg\_timer.h

void R\_TAU0\_Create(void) **Declaration**

Perform the initial setting to use TAU00 as an interval timer. **Description**

**Argument** None **Return Value** None

R DAC Create

**Outline** Initial setting of the D/A converter

Header r\_cg\_dac.h

**Declaration** void R\_DAC\_Create(void)

Perform the initial setting to use DAC0 in normal mode. **Description**

**Argument** None **Return Value** None main

Outline Main processing

**Header** None

**Declaration** void main(void)

**Description** Perform main processing.

Argument None Return Value None

## R\_DAC0\_Start

Outline DAC0 conversion start setting

**Header** r\_cg\_dac.h

Declarationvoid R\_DAC0\_Start(void)DescriptionStart D/A conversion.

Argument None Return Value None

## R\_TAU0\_Channel0\_Start

Outline TAU00 operation enable setting

**Header** r\_cg\_timer.h

**Declaration** void R\_TAU0\_Channel0\_Start(void)

**Description** Start TAU00 count.

Argument None Return Value None

## r\_tau0\_channel0\_interrupt

Outline TAU00 interrupt

**Header** None

Declarationvoid r\_tau0\_channel0\_interrupt(void)DescriptionPerform TAU00 interrupt service routine.

Argument None Return Value None

## da\_out\_change

Outline D/A conversion value switch processing

**Header** r\_cg\_userdefine.h

**Declaration** void da\_out\_change(void)

**Description** Change the output analog voltage value.

Argument None Return Value None

# R\_DAC0\_Set\_ConversionValue

Outline DAC0 conversion value setting

**Header** r\_cg\_dac.h

Declarationvoid R\_DAC0\_Set\_ConversionValue(uint8\_t reg\_value)DescriptionSet the D/A conversion value to the DACS0 register.ArgumentD/A conversion value

Return Value None

## 4.6 Flowcharts

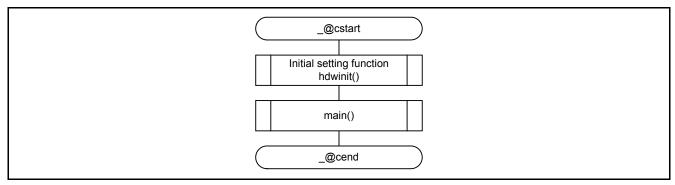

#### 4.6.1 Overall Flowchart

Figure 4.2 shows the Overall Flowchart.

Figure 4.2 Overall Flowchart

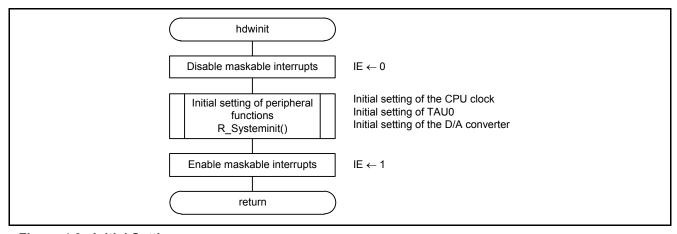

## 4.6.2 Initial Setting

Figure 4.3 shows the Initial Setting.

Figure 4.3 Initial Setting

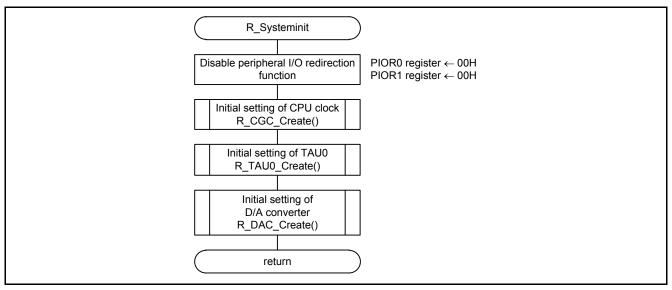

## 4.6.3 Initial Setting of Peripheral Functions

Figure 4.4 shows the Initial Setting of Peripheral Functions.

Figure 4.4 Initial Setting of Peripheral Functions

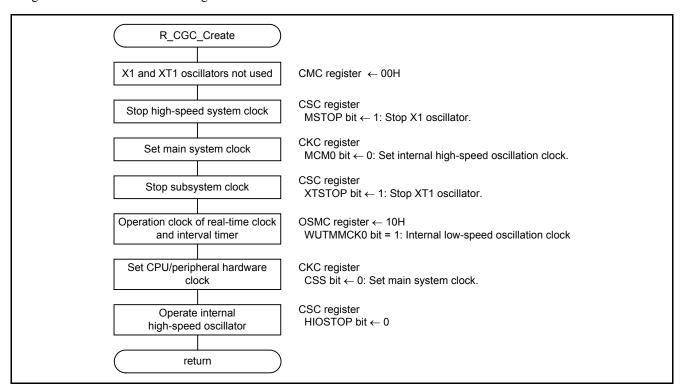

# 4.6.4 Initial Setting of the CPU Clock

Figure 4.5 shows the Initial Setting of the CPU Clock.

Figure 4.5 Initial Setting of the CPU Clock

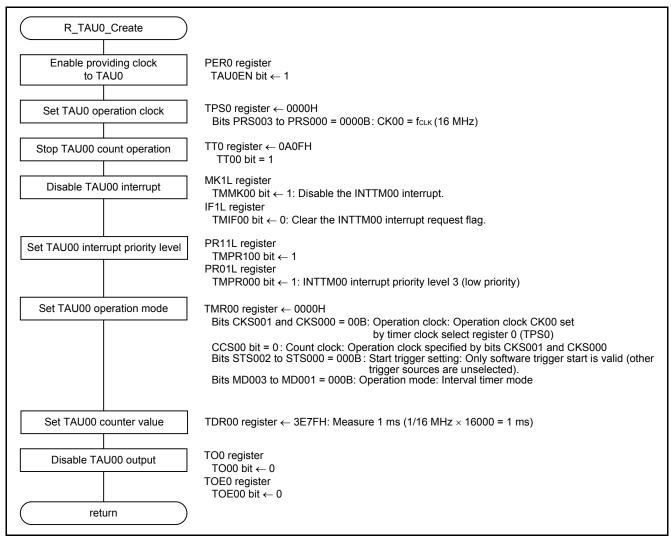

## 4.6.5 Initial Setting of TAU0

Figure 4.6 shows the Initial Setting of TAU0.

Figure 4.6 Initial Setting of TAU0

# Enable providing a clock to TAU0.

• Peripheral Enable Register 0 (PER0)

| Symbol        | 7     | 6       | 5     | 4       | 3      | 2      | 1      | 0      |

|---------------|-------|---------|-------|---------|--------|--------|--------|--------|

| PER0          | RTCEN | IICA1EN | ADCEN | IICA0EN | SAU1EN | SAU0EN | TAU1EN | TAU0EN |

| Setting Value | Х     | Х       | Х     | Х       | Х      | Х      | Х      | 1      |

#### Bit 0

| TAU0EN | Control of timer array unit 0 input clock supply                                                                         |

|--------|--------------------------------------------------------------------------------------------------------------------------|

| 0      | Stops input clock supply.  SFR used by timer array unit 0 cannot be written.  Timer array unit 0 is in the reset status. |

| 1      | <ul><li>Enables input clock supply.</li><li>SFR used by timer array unit 0 can be read and written.</li></ul>            |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

Set an operation clock of TAU0.

• Timer Clock Select Register 0 (TPS0)

Set 16 MHz for the operation clock.

Symbol TPS0

Setting Value

| 15 | 14 | 13  | 12  | 11 | 10 | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----|----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|    |    | PRS | PRS |    |    | PRS |

| 0  | 0  | 031 | 030 | 0  | 0  | 021 | 020 | 013 | 012 | 011 | 010 | 003 | 002 | 001 | 000 |

| _  | _  | ×   | ×   | _  | _  | ×   | ×   | ×   | ×   | ×   | ×   | 0   | 0   | 0   | 0   |

Bits 3 to 0

| PRS | PRS | PRS | PRS |                      |           | Selection of op | eration clock (Cl | <b>(00)</b> |           |

|-----|-----|-----|-----|----------------------|-----------|-----------------|-------------------|-------------|-----------|

| 003 | 002 | 001 | 000 |                      | fclk=     | fclk =          | fclk=             | fclk =      | fclk=     |

|     |     |     |     |                      | 2 MHz     | 5 MHz           | 10 MHz            | 20 MHz      | 32 MHz    |

| 0   | 0   | 0   | 0   | fcLK                 | 2 MHz     | 5 MHz           | 10 MHz            | 20 MHz      | 32 MHz    |

| 0   | 0   | 0   | 1   | fclk/2               | 1 MHz     | 2.5 MHz         | 5 MHz             | 10 MHz      | 16 MHz    |

| 0   | 0   | 1   | 0   | fclk/2 <sup>2</sup>  | 500 kHz   | 1.25 MHz        | 2.5 MHz           | 5 MHz       | 8 MHz     |

| 0   | 0   | 1   | 1   | fclk/2 <sup>3</sup>  | 250 kHz   | 625 kHz         | 1.25 MHz          | 2.5 MHz     | 4 MHz     |

| 0   | 1   | 0   | 0   | fclk/2 <sup>4</sup>  | 125 kHz   | 312.5 kHz       | 625 kHz           | 1.25 MHz    | 2 MHz     |

| 0   | 1   | 0   | 1   | fськ/2 <sup>5</sup>  | 62.5 kHz  | 156.2 kHz       | 312.5 kHz         | 625 kHz     | 1 MHz     |

| 0   | 1   | 1   | 0   | fcьк/2 <sup>6</sup>  | 31.25 kHz | 78.1 kHz        | 156.2 kHz         | 312.5 kHz   | 500 kHz   |

| 0   | 1   | 1   | 1   | fcьк/2 <sup>7</sup>  | 15.62 kHz | 39.1 kHz        | 78.1 kHz          | 156.2 kHz   | 250 kHz   |

| 1   | 0   | 0   | 0   | fclk/2 <sup>8</sup>  | 7.81 kHz  | 19.5 kHz        | 39.1 kHz          | 78.1 kHz    | 125 kHz   |

| 1   | 0   | 0   | 1   | fcьк/2 <sup>9</sup>  | 3.91 kHz  | 9.76 kHz        | 19.5 kHz          | 39.1 kHz    | 62.5 kHz  |

| 1   | 0   | 1   | 0   | fclk/2 <sup>10</sup> | 1.95 kHz  | 4.88 kHz        | 9.76 kHz          | 19.5 kHz    | 31.25 kHz |

| 1   | 0   | 1   | 1   | fcьк/2 <sup>11</sup> | 976 Hz    | 2.44 kHz        | 4.88 kHz          | 9.76 kHz    | 15.63 kHz |

| 1   | 1   | 0   | 0   | fclк/2 <sup>12</sup> | 488 Hz    | 1.22 kHz        | 2.44 kHz          | 4.88 kHz    | 7.81 kHz  |

| 1   | 1   | 0   | 1   | fclк/2 <sup>13</sup> | 244 Hz    | 610 Hz          | 1.22 kHz          | 2.44 kHz    | 3.91 kHz  |

| 1   | 1   | 1   | 0   | fclk/2 <sup>14</sup> | 122 Hz    | 305 Hz          | 610 Hz            | 1.22 kHz    | 1.95 kHz  |

| 1   | 1   | 1   | 1   | fclк/2 <sup>15</sup> | 61 Hz     | 153 Hz          | 305 Hz            | 610 Hz      | 976 Hz    |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

# Stop the TAU00 count operation.

• Timer Channel Stop Register 0 (TT0)

Set 16 MHz for the operation clock.

| Symbol           | 15 | 14 | 13 | 12 | 11        | 10 | 9         | 8 | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|------------------|----|----|----|----|-----------|----|-----------|---|---|---|---|---|------|------|------|------|

| TT0              | 0  | 0  | 0  | 0  | TTH<br>03 | 0  | TTH<br>01 | 0 | 0 | 0 | 0 | 0 | TT03 | TT02 | TT01 | TT00 |

| Setting<br>Value | _  | _  | _  | _  | ×         | _  | ×         | _ | _ | _ | _ | _ | ×    | ×    | ×    | 1    |

Bit 0

| TT00 | Operation stop trigger of channel 0                                                                                                                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | No trigger operation                                                                                                                                                                   |

| 1    | Operation is stopped (stop trigger is generated). This bit is the trigger to stop operation of the lower 8-bit timer for TT01 and TT03 when channel 1 or 3 is in the 8-bit timer mode. |

# Disable the TAU00 interrupt.

• Interrupt Mask Flag Register (MK1L)

| Symbol        | 7      | 6      | 5      | 4      | 3       | 2                 | 1                           | 0                           |  |  |

|---------------|--------|--------|--------|--------|---------|-------------------|-----------------------------|-----------------------------|--|--|

| MK1L          | TMMK03 | TMMK02 | TMMK01 | тммкоо | IICAMK0 | SREMK1<br>TMMK03H | SRMK1<br>CSIMK11<br>IICMK11 | STMK1<br>CSIMK10<br>IICMK10 |  |  |

| Setting Value | Х      | Х      | Х      | 1      | Х       | Х                 | Х                           | Х                           |  |  |

Bit 4

| TMMK00 | Interrupt servicing control  |

|--------|------------------------------|

| 0      | Interrupt servicing enabled  |

| 1      | Interrupt servicing disabled |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

• Interrupt Request Flag Register (IF1L)

| Symbol        | 7      | 6      | 5      | 4      | 3       | 2                 | 1                           | 0                           |

|---------------|--------|--------|--------|--------|---------|-------------------|-----------------------------|-----------------------------|

| IF1L          | TMIF03 | TMIF02 | TMIF01 | TMIF00 | IICAIF0 | SREIF1<br>TMIF03H | SRIF1<br>CSIIF11<br>IICIF11 | STIF1<br>CSIIF10<br>IICIF10 |

| Setting Value | Х      | Х      | Х      | 0      | Х       | Х                 | Х                           | Х                           |

Bit 4

| TMIF00 | Interrupt request flag                                   |

|--------|----------------------------------------------------------|

| 0      | No interrupt request signal is generated                 |

| 1      | Interrupt request is generated, interrupt request status |

Set the TAU00 interrupt priority level.

• Priority Specification Flag Register (PR11L, PR01L)

| Symbol        | 7       | 6       | 5       | 4       | 3        | 2                   | 1                              | 0                              |

|---------------|---------|---------|---------|---------|----------|---------------------|--------------------------------|--------------------------------|

| PR11L         | TMPR103 | TMPR102 | TMPR101 | TMPR100 | IICAPR10 | SREPR11<br>TMPR103H | SRPR11<br>CSIPR111<br>IICPR111 | STPR11<br>CSIPR110<br>IICPR110 |

| Setting Value | Х       | Х       | Х       | 1       | Х        | Х                   | Х                              | Х                              |

| Symbol        | 7       | 6       | 5       | 4       | 3        | 2                   | 1                              | 0                              |

| PR01L         | TMPR003 | TMPR002 | TMPR001 | TMPR000 | IICAPR00 | SREPR01<br>TMPR003H | SRPR01<br>CSIPR011<br>IICPR011 | STPR01<br>CSIPR010<br>IICPR010 |

| Setting Value | Х       | Х       | Х       | 1       | Х        | Х                   | Х                              | Х                              |

Bit 4

| TMPR100 | TMPR000 | Priority level selection              |

|---------|---------|---------------------------------------|

| 0       | 0       | Specify level 0 (high priority level) |

| 0       | 1       | Specify level 1                       |

| 1       | 0       | Specify level 2                       |

| 1       | 1       | Specify level 3 (low priority level)  |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

## Set TAU00 operation mode.

• Timer Mode Register (TMR00) Operation clock (fMCK): CK00 Count clock (fTCLK): fMCK

Start trigger: Only software trigger start is valid.

Operation mode: Interval timer mode (A timer interrupt is not generated when counting is started.)

| Symbol           | 15  | 14  | 13 | 12  | 11 | 10  | 9   | 8   | 7   | 6   | 5 | 4 | 3   | 2   | 1   | 0   |

|------------------|-----|-----|----|-----|----|-----|-----|-----|-----|-----|---|---|-----|-----|-----|-----|

| TMR00            | CKS | CKS | 0  | ccs | 0  | STS | STS | STS | CIS | CIS | 0 | 0 | MD  | MD  | MD  | MD  |

| TIVINOU          | 001 | 000 | 0  | 00  |    | 002 | 001 | 000 | 001 | 000 |   | 0 | 003 | 002 | 001 | 000 |

| Setting<br>Value | 0   | 0   | ı  | 0   | ı  | 0   | 0   | 0   | ×   | ×   | ı | ı | 0   | 0   | 0   | 0   |

#### Bits 15 and 14

| CKS<br>001 | CKS<br>000 | Selection of operation clock (fмск) of channel 0                 |  |  |  |  |  |

|------------|------------|------------------------------------------------------------------|--|--|--|--|--|

| 0          | 0          | Operation clock CK00 set by timer clock select register 0 (TPS0) |  |  |  |  |  |

| 0          | 1          | Operation clock CK02 set by timer clock select register 0 (TPS0) |  |  |  |  |  |

| 1          | 0          | Operation clock CK01 set by timer clock select register 0 (TPS0) |  |  |  |  |  |

| 1          | 1          | Operation clock CK03 set by timer clock select register 0 (TPS0) |  |  |  |  |  |

Operation clock (fMCK) is used by the edge detector. A count clock (fTCLK) and a sampling clock are generated depending on the setting of the CCS00 bit. The operation clocks CK02 and CK03 can only be selected for channels 1 and 3.

#### Bit 12

| CCS<br>00 | Selection of count clock (fτclκ) of channel 0                                                   |  |  |  |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 0         | Operation clock (fмск) specified by the CKS000 and CKS001 bits                                  |  |  |  |  |  |  |  |

| 1         | Valid edge of input signal input from the TI00 pin                                              |  |  |  |  |  |  |  |

| Count clo | Count clock (ftclk) is used for the timer/counter, output controller, and interrupt controller. |  |  |  |  |  |  |  |

#### Bits 10 to 8

| STS<br>002       | STS<br>001 | STS<br>000 | Setting of start trigger or capture trigger of channel 0                                                                                       |  |  |  |  |  |

|------------------|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0                | 0          | 0          | nly software trigger start is valid (other trigger sources are unselected).                                                                    |  |  |  |  |  |

| 0                | 0          | 1          | Valid edge of the TI00 pin input is used as both the start trigger and capture trigger.                                                        |  |  |  |  |  |

| 0                | 1          | 0          | Both the edges of the TI00 pin input are used as a start trigger and a capture trigger.                                                        |  |  |  |  |  |

| 1                | 1 0 0      |            | Interrupt signal of the master channel is used (when the channel is used as a slave channel with the simultaneous channel operation function). |  |  |  |  |  |

| Other than above |            |            | Setting prohibited                                                                                                                             |  |  |  |  |  |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

#### Bits 3 to 1

| MD<br>003 | MD<br>002                                                                                 | MD<br>001 | MD<br>000 | Operation mode of channel 0 | Corresponding function                                                             | Count operation of TCR |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------|-----------|-----------|-----------------------------|------------------------------------------------------------------------------------|------------------------|--|--|--|--|

| 0         | 0                                                                                         | 0         | 1/0       | Interval timer mode         | Interval timer / Square wave<br>output / Divider function / PWM output<br>(master) | Counting down          |  |  |  |  |

| 0         | 1                                                                                         | 1         | 1/0       | Capture mode                | Input pulse interval measurement                                                   | Counting up            |  |  |  |  |

| 0         | 1                                                                                         | 1         | 0         | Event counter mode          | External event counter                                                             | Counting down          |  |  |  |  |

| 1         | 0                                                                                         | 0         | 1/0       | One-count mode              | Delay counter / One-shot pulse output / PWM output (slave)                         | Counting down          |  |  |  |  |

| 1         | 1                                                                                         | 0         | 0         | Capture & one-count mode    | Delay counter / One-shot pulse output / PWM output (slave)                         | Counting up            |  |  |  |  |

|           | Other tha                                                                                 | an above  |           | Setting prohibited          |                                                                                    |                        |  |  |  |  |

| The ope   | The operation of the MD000 bit varies depending on each operation mode (see table below). |           |           |                             |                                                                                    |                        |  |  |  |  |

#### Rit 0

| Operation mode (Value set by the MD003 to MD001 bits (see table above)) | MD<br>000 | Setting of starting counting and interrupt                                                                                                                                                               |

|-------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • Interval timer mode (0, 0, 0)                                         | 0         | Timer interrupt is not generated when counting is started (timer output does not change, either).                                                                                                        |

| • Capture mode (0, 1, 0)                                                | 1         | Timer interrupt is generated when counting is started (timer output also changes).                                                                                                                       |

| • Event counter mode (0, 1, 1)                                          | 0         | Timer interrupt is not generated when counting is started (timer output does not change, either).                                                                                                        |

| One-count mode                                                          | 0         | Start trigger is invalid during counting operation. At that time, interrupt is not generated, either.                                                                                                    |

| (1, 0, 0)                                                               | 1         | Start trigger is valid during counting operation. At that time, interrupt is also generated.                                                                                                             |

| • Capture & one-count mode (1, 1, 0)                                    | 0         | Timer interrupt is not generated when counting is started (timer output does not change, either).  Start trigger is invalid during counting operation.  At that time interrupt is not generated, either. |

| Other than above                                                        | •         | Setting prohibited                                                                                                                                                                                       |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

Set the TAU00 count value.

• Timer Data Register (TDR00)

Set 3E7FH to the counter and measure 1 ms.

|       | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| TDR00 | 0  | 0  | 1  | 1  | 1  | 1  | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Disable the TAU00 output.

• Timer Output Register (TO0)

| Symbol  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|---------|----|----|----|----|----|----|---|---|---|---|---|---|------|------|------|------|

| TO0     | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | TO03 | TO02 | TO01 | TO00 |

| Setting |    |    |    |    |    |    |   |   |   |   |   |   |      | ,    | ~    | 0    |

| Value   |    |    |    |    |    |    |   |   |   |   |   |   | ×    | ×    | ×    | 0    |

Bit 0

| TO00 | Timer output of channel 0  |

|------|----------------------------|

| 0    | Timer output value is "0". |

| 1    | Timer output value is "1". |

• Timer Output Enable Register (TOE0)

| Symbol  | 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|---------|--------|----|----|----|----|----|---|---|---|---|---|---|-----|-----|-----|-----|

| T050    | 0      | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | TOE | TOE | TOE | TOE |

| TOEU    | TOE0 0 | 0  | 0  | 0  | 0  |    | 0 | 0 |   |   | 0 | 0 | 03  | 02  | 01  | 00  |

| Setting |        |    | _  |    |    |    | _ |   |   |   |   |   | ×   | ×   | ×   | 0   |

| Value   |        |    |    |    |    |    |   |   |   |   |   |   |     |     |     |     |

Bit 0

| TOE00 | Timer output enable/disable of channel 0                                                                                                     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Timer output is disabled.  Timer operation is not applied to the TO00 bit and the output is fixed.  Writing to the TO00 bit is enabled.      |

| 1     | Timer output is enabled. Timer operation is applied to the TO00 bit and an output waveform is generated. Writing to the TO00 bit is ignored. |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

# 4.6.6 Initial Setting of the D/A Converter

Figure 4.7 shows the Initial Setting of the D/A Converter.

Figure 4.7 Initial Setting of the D/A Converter

Enable providing a clock to the D/A converter.

• Peripheral Enable Register 1 (PER1)

| Symbol        | 7     | 6     | 5     | 4      | 3     | 2 | 1 | 0      |

|---------------|-------|-------|-------|--------|-------|---|---|--------|

| PER1          | DACEN | TRGEN | CMPEN | TRD0EN | DTCEN | 0 | 0 | TRJ0EN |

| Setting Value | 1     | Х     | Х     | Х      | Х     | _ | _ | Х      |

#### Bit 7

| DACEN | Control of D/A converter input clock                                                                                   |

|-------|------------------------------------------------------------------------------------------------------------------------|

| 0     | Stops input clock supply.  SFR used by the D/A converter cannot be written.  The D/A converter is in the reset status. |

| 1     | Supplies input clock.  • SFR used by the D/A converter can be read/written.                                            |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

Set the D/A converter to normal mode.

• D/A Converter Mode Register (DAM)

| Symbol        | 7 | 6 | 5     | 4     | 3 | 2 | 1     | 0     |

|---------------|---|---|-------|-------|---|---|-------|-------|

| DAM           | _ |   | DACE1 | DACE0 |   |   | DAMD1 | DAMD0 |

| Setting Value | _ | _ | Х     |       | _ | _ | Х     | 0     |

Bit 0

| DAMD0 | D/A converter operation mode selection |

|-------|----------------------------------------|

| 0     | Normal mode                            |

| 1     | Real-time output mode                  |

Initialize the DAC0 conversion value.

• D/A Conversion Value Setting Register 0 (DACS0) Set 000H to the D/A conversion value.

Symbol 5 3 2 0 7 1 DACS07 DACS0 DACS06 DACS05 DACS04 DACS03 DACS02 DACS01 DACS00 Setting Value 0 0 0 0 0 0 0 0

| _              | Function                                                                                                                                                                |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits<br>7 to 0 | The relation between the resolution and analog output voltage (VANO0) of the D/A converter are as follows.  VANO0 = Reference voltage for D/A converter × (DACS0) / 256 |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

Set the ANO0 pin function.

• Port Mode Register 2 (PM2)

| Symbol        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------------|------|------|------|------|------|------|------|------|

| PM2           | PM27 | PM26 | PM25 | PM24 | PM23 | PM22 | PM21 | PM20 |

| Setting Value | Х    | Х    | Х    | Х    | Х    | 1    | Х    | Х    |

Bit 2

| PM22 | P22 pin I/O mode selection     |  |  |  |  |  |

|------|--------------------------------|--|--|--|--|--|

| 0    | Output mode (output buffer on) |  |  |  |  |  |

| 1    | Input mode (output buffer off) |  |  |  |  |  |

#### 4.6.7 **Main Processing**

Figure 4.8 shows the Main Processing.

Figure 4.8 Main Processing

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

# 4.6.8 DAC0 Conversion Start Setting

Figure 4.9 shows the DAC0 Conversion Start Setting.

Figure 4.9 DAC0 Conversion Start Setting

Enable D/A conversion.

• D/A Converter Mode Register (DAM)

| Symbol        | 7 | 6 | 5     | 4     | 3 | 2 | 1     | 0     |

|---------------|---|---|-------|-------|---|---|-------|-------|

| DAM           | _ | _ | DACE1 | DACE0 | _ | _ | DAMD1 | DAMD0 |

| Setting Value | _ | _ | Х     | 1     | _ | _ | Х     |       |

#### Bit 4

| DACE0 | D/A conversion operation control |  |  |  |  |  |

|-------|----------------------------------|--|--|--|--|--|

| 0     | tops D/A conversion operation    |  |  |  |  |  |

| 1     | Enables D/A conversion operation |  |  |  |  |  |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

# 4.6.9 TAU00 Operation Enable Setting

Figure 4.10 shows the TAU00 Operation Enable Setting.

Figure 4.10 TAU00 Operation Enable Setting

Clear the TAU00 interrupt request flag.

• Interrupt Request Flag Register (IF1L)

| Symbol        | 7      | 6      | 5      | 4      | 3       | 2                 | 1                           | 0                           |

|---------------|--------|--------|--------|--------|---------|-------------------|-----------------------------|-----------------------------|

| IF1L          | TMIF03 | TMIF02 | TMIF01 | TMIF00 | IICAIF0 | SREIF1<br>TMIF03H | SRIF1<br>CSIIF11<br>IICIF11 | STIF1<br>CSIIF10<br>IICIF10 |

| Setting Value | Х      | Х      | Х      | 0      | Х       | Х                 | Х                           | Х                           |

#### Bit 4

| TMIF00 | Interrupt request flag                                   |  |  |  |  |  |

|--------|----------------------------------------------------------|--|--|--|--|--|

| 0      | No interrupt request signal is generated                 |  |  |  |  |  |

| 1      | Interrupt request is generated, interrupt request status |  |  |  |  |  |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

Enable the TAU00 interrupt service routine.

• Interrupt Mask Flag Register (MK1L)

| Symbol        | 7      | 6      | 5      | 4      | 3       | 2                 | 1                           | 0                           |

|---------------|--------|--------|--------|--------|---------|-------------------|-----------------------------|-----------------------------|

| MK1L          | TMMK03 | TMMK02 | TMMK01 | тммкоо | IICAMK0 | SREMK1<br>TMMK03H | SRMK1<br>CSIMK11<br>IICMK11 | STMK1<br>CSIMK10<br>IICMK10 |

| Setting Value | Х      | Х      | Х      | 0      | Х       | Х                 | Х                           | Х                           |

Bit 4

| TMMK00 | Interrupt servicing control  |  |  |  |  |  |

|--------|------------------------------|--|--|--|--|--|

| 0      | Interrupt servicing enabled  |  |  |  |  |  |

| 1      | Interrupt servicing disabled |  |  |  |  |  |

## Start count operation.

• Timer Channel Start Register (TS0)

| Symbol           | 15 | 14 | 13 | 12 | 11        | 10 | 9         | 8 | 7 | 6 | 5 | 4 | 3        | 2        | 1        | 0        |

|------------------|----|----|----|----|-----------|----|-----------|---|---|---|---|---|----------|----------|----------|----------|

| TS0              | 0  | 0  | 0  | 0  | TSH<br>03 | 0  | TSH<br>01 | 0 | 0 | 0 | 0 | 0 | TS<br>03 | TS<br>02 | TS<br>01 | TS<br>00 |

| Setting<br>Value | 1  | 1  | 1  | _  | ×         | _  | ×         | 1 | 1 | 1 | 1 | 1 | ×        | ×        | ×        | 1        |

Bit 0

| TS00 | Operation enable (start) trigger of channel 0                                                                                                                                            |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | No trigger operation                                                                                                                                                                     |

| 1    | The TE00 bit is set to 1 and the count operation becomes enabled.  The TCR00 register count operation start in the count operation enabled state varies depending on each operation mode |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

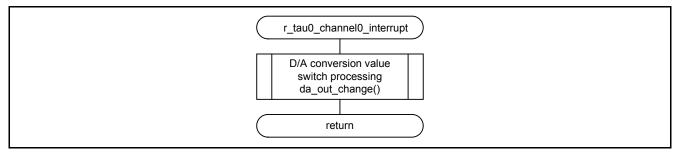

# 4.6.10 TAU00 Interrupt

Figure 4.11 shows the TAU00 Interrupt.

Figure 4.11 TAU00 Interrupt

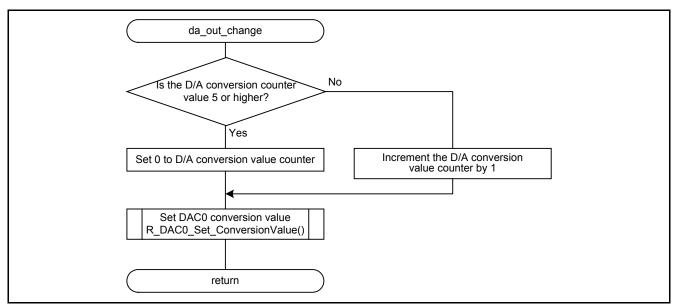

# 4.6.11 D/A Conversion Value Switch Processing

Figure 4.12 shows the D/A Conversion Value Switch Processing.

Figure 4.12 D/A Conversion Value Switch Processing

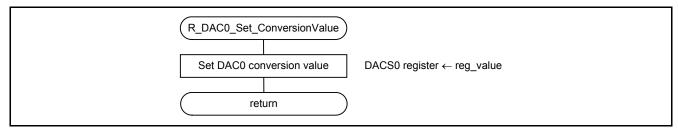

# 4.6.12 DAC0 Conversion Value Setting

Figure 4.13 shows the DAC0 Conversion Value Setting.

Figure 4.13 DAC0 Conversion Value Setting

Set the DAC0 conversion value.

• D/A Conversion Value Setting Register (DACS0) Set an analog output value output to the ANO0 pin.

| Symbol        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| DACS0         | DACS07 | DACS06 | DACS05 | DACS04 | DACS03 | DACS02 | DACS01 | DACS00 |

| Setting Value | 0/1    | 0/1    | 0/1    | 0/1    | 0/1    | 0/1    | 0/1    | 0/1    |

Refer to the RL78/G14 user's manual (hardware) for details on individual registers. Initial values of individual bits

# 5. Sample Code

Sample code can be downloaded from the Renesas Electronics website.

## 6. Reference Documents

User's Manual: Hardware

RL78/G14 Group User's Manual: Hardware Rev.1.00 RL78 Family User's Manual: Software Rev.1.00

The latest versions can be downloaded from the Renesas Electronics website.

Technical Update/Technical News

The latest information can be downloaded from the Renesas Electronics website.

# **Website and Support**

Renesas Electronics website http://www.renesas.com

Inquiries

http://www.renesas.com/contact/

| DEVICION LUCTORY | RL78/G14                                |

|------------------|-----------------------------------------|

| REVISION HISTORY | Setting the D/A Converter's Normal Mode |

| Boy       | Dete          |      | Description              |

|-----------|---------------|------|--------------------------|

| Rev. Date |               | Page | Summary                  |

| 1.00      | Aug. 31, 2012 | _    | First edition issued     |

| 1.10      | June 1, 2013  | 4    | Fixed typo in Table 2.1  |

|           |               | 5    | Fixed typo in Figure 3.1 |

All trademarks and registered trademarks are the property of their respective owners.

## **General Precautions in the Handling of MPU/MCU Products**

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

## 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

#### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

- 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access

these addresses; the correct operation of LSI is not guaranteed if they are accessed.

#### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

#### 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or

- You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics

#### SALES OFFICES

#### Renesas Electronics Corporation

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information

Renesas Electronics America Inc. 2880 Scott Boulevard Santa Clara, CA 95050-2554, U.S.A. Tel: +1-408-588-6000, Fax: +1-408-588-6130

Renesas Electronics Canada Limited 1101 Nicholson Road, Newmarket, Ontario L3Y 9C3, Canada Tel: +1-905-898-5441, Fax: +1-905-898-3220

Renesas Electronics Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-651-700, Fax: +44-1628-651-804

Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germany Tel: +49-211-65030, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd.

7th Floor, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100083, P.R.China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679

Renesas Electronics (Shanghai) Co., Ltd. Unit 204, 205, AZIA Center, No.1233 Lujiazui Ring Rd., Pudong District, Shanghai 200120, China Tel: +86-Z1-5877-1818, Fax: +86-Z1-6887-7858 / -7898

Renesas Electronics Hong Kong Limited

Unit 1601-1613, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

Tel: +852-2886-9318, Fax: +852 2886-9022/9044

Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670

Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #d6-02 Hyflux Innovation Centre Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300

Renesas Electronics Malaysia Sdn.Bhd.

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: +60-3-7955-9390, Fax: +60-3-7955-9510

Renesas Electronics Korea Co., Ltd. 11F., Samik Lavied' or Bldg., 720-2 Yeoksam-Dong, Kangnam-Ku, Seoul 135-080, Korea Tel: +82-2-558-3737, Fax: +82-2-558-5141