# **RZ/A Series**

# Hardware Design Guide

# Introduction

This application note is a summary of the items serving as design points as reference materials for use when designing hardware which incorporates RZ/A Series LSIs.

# **Target LSIs**

The following RZ/A Series groups

RZ/A1H group<sup>\*1\*2</sup>, RZ/A1M group<sup>\*1\*2</sup>

RZ/A1L group\*1\*3, RZ/A1LU group\*1\*3, RZ/A1LC group\*1\*3

RZ/A2M group

Notes: In the rest of this document, unless clearly specifying a particular group, this will be contracted to simply "group",

- \*1. In this document, when indicating these groups collectively, it will be noted as "RZ/A1".

- \*2. In this document, when indicating these groups collectively, it will be noted as "RZ/A1HM".

- \*3. In this document, when indicating these groups collectively, it will be noted as "RZ/A1L".

# **Reference Application Note**

For additional information associated with this document, refer to the following application note.

- RZ/A2M Group Guidelines for High-Speed USB2.0 Board Design (R01AN4964EJ)

- RZ/A1 Guidelines for High-Speed USB2.0 Board Design (R01AN5119EJ)

- RZ/A2M Group Guidelines for LVDS and MIPI Board Design (R01AN5280EJ)

# Trademarks

CoreSight<sup>™</sup> is a trademark of Arm Ltd.

HyperBus™/HyperFlash™/HyperRAM™/HyperMCP™ are trademarks of Cypress Semiconductor Corporation.

OctaFlash<sup>™</sup>/OctaRAM<sup>™</sup>/OctaMCP<sup>™</sup> are trademarks of Macronix International Co., Ltd. Xccela<sup>™</sup> flash memory is a trademark of Micron Technology, Inc.

# List of Abbreviations and Acronyms

| Abbreviation | Full Form                                     |

|--------------|-----------------------------------------------|

| ACIA         | Asynchronous Communications Interface Adapter |

| bps          | bits per second                               |

| CRC          | Cyclic Redundancy Check                       |

| DMA          | Direct Memory Access                          |

| DMAC         | Direct Memory Access Controller               |

| GSM          | Global System for Mobile Communications       |

| Hi-Z         | High Impedance                                |

| IEBus        | Inter Equipment Bus                           |

| I/O          | Input/Output                                  |

| IrDA         | Infrared Data Association                     |

| LSB          | Least Significant Bit                         |

| MSB          | Most Significant Bit                          |

| NC           | Non-Connect                                   |

| PLL          | Phase Locked Loop                             |

| PWM          | Pulse Width Modulation                        |

| SFR          | Special Function Register                     |

| SIM          | Subscriber Identity Module                    |

| UART         | Universal Asynchronous Receiver/Transmitter   |

| VCO          | Voltage Controlled Oscillator                 |

| Abbreviation | Full Form                                            |  |

|--------------|------------------------------------------------------|--|

| CPHAR        | Clock Phase Reception (Input latch timing)           |  |

| CPHAT        | Clock Phase Transmission (Output shift timing)       |  |

| CPOL         | Clock Polarity                                       |  |

| EMI          | Electromagnetic Interference                         |  |

| EMS          | Electromagnetic Susceptibility                       |  |

| ESD          | Electrostatic Discharge                              |  |

| RSPI         | Renesas Serial Peripheral Interface                  |  |

| SPIBSC       | Serial Peripheral Interface Multi I/O Bus Controller |  |

# Contents

| 1.    | Power Supply                                                               | 5  |

|-------|----------------------------------------------------------------------------|----|

| 1.1   | Power Supply                                                               | 5  |

| 1.2   | Absolute Maximum Ratings                                                   | 7  |

| 1.2.1 | Points of caution when voltage is applied while system power supply is OFF | 9  |

| 1.3   | Bypass Capacitor                                                           |    |

| 2.    | Reset                                                                      | 19 |

| 2.1   | Power ON and Power OFF Sequences                                           |    |

| 2.2   | Oscillation Settling Time                                                  | 21 |

| 3.    | Oscillator Circuit                                                         | 22 |

| 3.1   | Clock Pins                                                                 |    |

| 3.2   | Example of External Clock Connection                                       |    |

| 3.3   | Example of Crystal Resonator Connection                                    |    |

| 4.    | Operating Mode                                                             | 24 |

| 4.1   | Boot Mode                                                                  |    |

| 4.1.1 |                                                                            |    |

| 4.1.2 |                                                                            |    |

| 4.1.3 |                                                                            |    |

| 4.1.4 |                                                                            |    |

| 4.1.5 | eMMC Boot                                                                  |    |

| 4.1.6 | Serial Flash Boot (3.3-V products)                                         |    |

| 4.1.7 | Octal-SPI Flash Boot (1.8-V products)                                      |    |

| 4.1.8 | HyperFlash Boot 1 (1.8-V products)                                         |    |

| 4.1.9 | OctaFlash Boot (1.8-V products)                                            |    |

| 4.1.1 | 0 HyperFlash Boot 2 (1.8-V products)                                       |    |

| 4.1.1 | 1 Points of caution when selecting flash memory for use as boot memory     |    |

| 4.2   | Clock Mode                                                                 |    |

| 4.2.1 | Clock Mode Setting Pin                                                     |    |

| 5.    | External Memory                                                            |    |

| 5.1   | Connectable Memory                                                         |    |

| 5.2   | Parallel NOR Flash Memory                                                  |    |

| 5.3   | SDRAM                                                                      |    |

| 5.4   | EEPROM                                                                     |    |

| 5.5   | Serial Flash Memory                                                        |    |

| 5.6   | Xccela Flash Memory                                                        |    |

| 5.7   | HyperBus Memory                                                            |    |

| 5.7.1 | HyperFlash                                                                 |    |

| 5.7.2 | HyperRAM                                                                   |    |

| 5.7.3 | 3 HyperMCP                           | 45 |

|-------|--------------------------------------|----|

| 5.8   | Octa Memory                          | 46 |

| 5.8.1 | OctaFlash                            | 46 |

| 5.8.2 | 2 OctaRAM                            | 47 |

| 5.8.3 | 3 OctaMCP                            | 47 |

| 5.9   | NAND Flash Memory                    | 48 |

| 5.10  | SD Card                              | 49 |

| 5.11  | eMMC                                 | 51 |

| 6.    | Debugger Interface                   | 52 |

| 6.1   | Characteristics                      |    |

| 6.2   | Treatment of TRST# Pin               |    |

| 6.3   | Example of Emulator Connection       |    |

| 6.3.1 |                                      |    |

| 6.3.2 |                                      |    |

| 6.3.3 | 3 TRACE Interface                    | 53 |

| 6.3.4 | Connection to CoreSight 20 Connector | 54 |

| 6.3.5 | Connection to CoreSight 10 Connector | 56 |

| 7     | Treatment of Dine                    | 57 |

| 7.    | Treatment of Pins                    |    |

| 7.1   | Analog Pin Protection Circuit        |    |

| 7.2   | Treatment of Unused Pins             | 58 |

| 8.    | Layout Guide                         | 60 |

| 8.1   | Layout and Wiring                    | 60 |

| 8.2   | Differential Signal                  | 61 |

| 8.2.7 | Impedance Control                    | 61 |

| 8.2.2 | 2 Cautions for Wiring                | 61 |

| 9.    | Noise Countermeasures                | 62 |

| 9.1   | EMI Countermeasures                  |    |

| 9.2   | EMS Countermeasures                  |    |

|       |                                      |    |

| 10.   | Checklist                            | 64 |

| 11.   | Reference Documents                  | 68 |

| 12.   | Design Support                       | 68 |

| Rev   | ision History                        | 69 |

# 1. Power Supply

## 1.1 Power Supply

LSI of this series have the power supplies shown in Table 1.1 and Table 1.2. When designing a board, separate the digital power supply and the analog power supply as much as possible to prevent switching noise from the digital power supply.

In addition, the PLL power supply is sensitive to noise and the like, with the result that interference from other power supplies may cause erroneous operation or malfunctions in the overall system. To prevent such malfunction, the PLL power supply and other power supplies should not supply the same resources on the board if at all possible. Wiring length from the board power supply pins must be as short as possible and pattern width must be as wide as possible to reduce inductive interferences.

| Symbol     | Type <sup>*1</sup> | Name                                                  | Voltage Range    |

|------------|--------------------|-------------------------------------------------------|------------------|

| PVcc       | D                  | Power supply for I/O circuits                         | 3.0 V to 3.6 V   |

| Vcc        | D                  | Power supply                                          | 1.10 V to 1.26 V |

| Vss        | D                  | Ground                                                | 0 V              |

| USBDPVcc   | D                  | Power supply for transceiver digital pins             | 3.0 V to 3.6 V   |

| USBDPVss   | D                  | Ground for transceiver digital pins                   | 0 V              |

| USBDVcc    | D                  | Power supply for transceiver digital core             | 1.10 V to 1.26 V |

| USBDVss    | D                  | Ground for transceiver digital core                   | 0 V              |

| USBUVcc    | D                  | 480-MHz power supply for USB 2.0 host/function module | 1.10 V to 1.26 V |

| USBUVss    | D                  | 480-MHz ground for USB 2.0 host/function module       | 0 V              |

| PLLVcc     | D                  | Power supply for PLL                                  | 1.10 V to 1.26 V |

| LVDSPLLVcc | D                  | LVDS PLL power supply                                 | 1.10 V to 1.26 V |

| USBAPVcc   | А                  | Power supply for transceiver analog pins              | 3.0 V to 3.6 V   |

| USBAPVss   | А                  | Ground for transceiver analog pins                    | 0 V              |

| USBAVcc    | А                  | Power supply for transceiver analog core              | 1.10 V to 1.26 V |

| USBAVss    | А                  | Ground for transceiver analog core                    | 0 V              |

| VDAVcc     | А                  | Analog power supply                                   | 3.0 V to 3.6 V   |

| VDAVss     | А                  | Analog ground                                         | 0 V              |

| LVDSAPVcc  | А                  | LVDS analog power supply                              | 3.0 V to 3.6 V   |

| LVDSAPVss  | А                  | LVDS analog ground                                    | 0 V              |

| AVcc       | А                  | Analog power supply                                   | 3.0 V to 3.6 V*2 |

| AVss       | А                  | Analog ground                                         | 0 V              |

| AVref      | А                  | Analog reference voltage                              | 3.0 V to 3.6 V*3 |

Table 1.1 Power supply (RZ/A1)

Notes: Connect all power supply and ground pins. LSI operation is not guaranteed if there are open pins. Some pins may not exist depending on the packages.

\*1. Digital systems power supply is shown as "D" and analog systems power supply is shown as "A"

\*2. Set within the range of PVcc -  $0.3 V \le AVcc \le PVcc$

\*3. Set within the range of 3.0 V  $\leq$  AVref  $\leq$  AVcc

## Table 1.2Power supply (RZ/A2M)

| Symbol                  | Type <sup>*1</sup> | Name                                                 | Voltage Range    |

|-------------------------|--------------------|------------------------------------------------------|------------------|

| PVcc                    | D                  | Power supply for I/O circuits                        | 3.0 V to 3.6 V   |

| Vcc                     | D                  | Power supply                                         | 1.14 V to 1.26 V |

| Vss                     | D                  | Ground                                               | 0V               |

| USBDPVcc1,<br>USBDPVcc0 | D                  | Power supply for transceiver digital pins            | 3.0 V to 3.6 V   |

| PVcc_SPI,               | D                  | 1.8-V/3.3-V switchable power supply for I/O circuits | 1.7 V to 1.9 V   |

| PVcc_SD1,<br>PVcc_SD0   |                    |                                                      | 3.0 V to 3.6 V   |

| PVcc_HO                 | D                  | Power supply for I/O circuits                        | 1.7 V to 1.9 V   |

| AVcc                    | А                  | Analog power supply and reference voltage            | 3.0 V to 3.6 V   |

| AVss                    | А                  | Analog ground                                        | 0 V              |

| USBAPVcc1,<br>USBAPVcc0 | A                  | Power supply for transceiver analog pins             | 3.0 V to 3.6 V   |

| LVDSAPVcc               | А                  | LVDS analog power supply                             | 3.0 V to 3.6 V   |

| MIPIAVcc18              | А                  | MIPI analog power supply                             | 1.7 V to 1.9 V   |

| PLLVcc                  | А                  | Power supply for PLL                                 | 1.14 V to 1.26 V |

| LVDSPLLVcc              | А                  | LVDS PLL power supply                                | 1.14 V to 1.26 V |

| USBVss                  | <b>_</b> *2        | Ground for transceiver pins                          | 0 V              |

Notes: Connect all power supply and ground pins. LSI operation is not guaranteed if there are open pins. Some pins may not exist depending on the packages.

\*1. Digital systems power supply is shown as "D" and analog systems power supply is shown as "A" \*2. Ground for USB.

# **1.2 Absolute Maximum Ratings**

Design the board so that the absolute maximum ratings for LSI of this series, as shown in Table 1.3 and Table 1.4 are satisfied. Permanent damage to the LSI may result if absolute maximum ratings are exceeded.

| Symbol                | Name                                      | Rating Value                         |

|-----------------------|-------------------------------------------|--------------------------------------|

| PVcc                  | Power supply for I/O circuits             | -0.3 V to 4.2 V                      |

| Vcc                   | Power supply                              | -0.3 V to 1.6 V                      |

| PLLVcc                | Power supply for PLL                      | -0.3 V to 1.6 V                      |

| AVcc                  | Analog power supply voltage               | -0.3 V to 4.2 V                      |

| AVref                 | Analog reference voltage                  | -0.3 V to AVcc*1 + 0.3 V             |

| USBAPVcc              | Power supply for transceiver analog pins  | -0.3 V to 4.2 V                      |

| USBDPVcc*2            | Power supply for transceiver digital pins | -0.3 V to 4.2 V                      |

| USBAVcc               | Power supply for transceiver analog core  | -0.3 V to 1.6 V                      |

| USBDVcc               | Power supply for transceiver digital core | -0.3 V to 1.6 V                      |

| USBUVcc               | 480-MHz power supply                      | -0.3 V to 1.6 V                      |

|                       | for USB 2.0 host/function module          |                                      |

| VDAVcc                | Analog power supply                       | -0.3 V to 4.2 V                      |

| LVDSAPVcc             | LVDS analog power supply                  | -0.3 V to 4.2 V                      |

| LVDSPLLVcc            | LVDS analog ground                        | -0.3 V to 1.6 V                      |

| VBUS1, VBUS0          | VBUS input                                | -0.3 V to 5.5 V                      |

| REFRIN                | Reference input                           | -0.3 V to USBAPVcc*1 + 0.3 V         |

| DP1, DM1, DP0, DM0    | USB 2.0 host/function module D+/D- data   | -0.3 V to USBDPVcc*1*2 + 0.3 V       |

| VIN2A, VIN1A, VIN2B,  | Composite video signal (CVBS) input       | -0.3 V to VDAVcc*1 + 0.3 V           |

| VIN1B, VRP, VRM, REXT |                                           |                                      |

| LVDSREFRIN            | Reference input                           | -0.3 V to LVDSAPVcc*1 + 0.3 V        |

| AN7 to AN0            | Analog input pins                         | -0.3 V to AVcc*1 + 0.3 V*3           |

| Other input pins      | -                                         | -0.3 V to PVcc <sup>*1</sup> + 0.3 V |

| Table 1.3 | Absolute | maximum | ratings | (RZ/A1) |

|-----------|----------|---------|---------|---------|

|-----------|----------|---------|---------|---------|

Notes: Some pins may not exist depending on the packages.

\*1. Rated value changes in accordance with the power supply voltage applied.

For example, when 0 V is applied to AVcc, the AVref rated value will be -0.3 V to 0.3 V.

\*2. In case of BGA package, this is PVcc.

\*3. This is the rated value when the GPIO ports are set to analog input pins.

#### Table 1.4 Absolute maximum ratings (RZ/A2M)

| Symbol                              | Name                                      | Rating Value                            |

|-------------------------------------|-------------------------------------------|-----------------------------------------|

| PVcc                                | Power supply for I/O circuits             | -0.3 V to 4.2 V                         |

| PVcc_SPI,                           | 1.8-V/3.3-V switchable power supply       | -0.3 V to 4.2 V                         |

| PVcc_SD1,                           | for I/O circuits                          |                                         |

| PVcc_SD0                            |                                           |                                         |

| PVcc_HO                             | Power supply for I/O circuits             | -0.3 V to 4.2 V                         |

| Vcc                                 | Power supply                              | -0.3 V to 1.6 V                         |

| PLLVcc                              | Power supply for PLL                      | -0.3 V to 1.6 V                         |

| AVcc                                | Analog power supply and reference voltage | -0.3 V to 4.2 V                         |

| USBAPVcc1,                          | Power supply for transceiver analog pins  | -0.3 V to 4.2 V                         |

| USBAPVcc0                           |                                           |                                         |

| USBDPVcc1,                          | Power supply for transceiver digital pins | -0.3 V to 4.2 V                         |

| USBDPVcc0                           |                                           |                                         |

| LVDSAPVcc                           | LVDS analog power supply                  | -0.3 V to 4.2 V                         |

| LVDSPLLVcc                          | LVDS PLL power supply                     | -0.3 V to 1.6 V                         |

| MIPIAVcc18                          | MIPI analog power supply                  | -0.3 V to 2.6 V                         |

| HM_RWDS/OM_DQS,                     | HyperBus Controller and                   | -0.3 V to PVcc_HO <sup>*1</sup> + 0.3 V |

| HM_DQ7/OM_SIO7 to                   | Octa Memory Controller input pins         |                                         |

| HM_DQ0/OM_SIO0                      |                                           |                                         |

| CSI_DATA1P, CSI_DATA1N,             | MIPI CSI-2 Interface input pins           | -0.3 V to MIPIAVcc18*1 + 0.3 V          |

| CSI_DATA0P, CSI_DATA0N,             |                                           |                                         |

| CSI_CLKP, CSI_CLKN                  |                                           |                                         |

| QSPI1_SSL,                          | SPI Multi I/O Bus Controller input pins   | -0.3 V to PVcc_SPI*1 + 0.3 V            |

| QSPI1_IO3 to QSPI1_IO0,             |                                           |                                         |

| QSPI0_IO3 to QSPI0_IO0,<br>RPC_INT# |                                           |                                         |

| SD0 DAT7 to SD0 DAT0,               | SD/MMC Host Interface                     | -0.3 V to PVcc SD0*1 + 0.3 V            |

| SD0_DAT7 to SD0_DAT0,               | Channel 0 input pins                      | -0.3 V 10 F VCC_3D0 V + 0.3 V           |

| SD1 DAT3 to SD1 DAT0,               | SD/MMC Host Interface                     | -0.3 V to PVcc SD1*1 + 0.3 V            |

| SD1_CMD                             | Channel 1 input pins                      | 0.0 1 10 1 100_001 1 0.0 1              |

| RREF0                               | Reference input                           | -0.3 V to USBAPVcc0*1 + 0.3 V           |

| RREF1                               | Reference input                           | -0.3 V to USBAPVcc1*1 + 0.3 V           |

| DP0, DM0                            | D+/D- data for USB 2.0 host/function      | -0.3 V to USBDPVcc0*1 + 0.3 V           |

| .,                                  | module channel 0                          |                                         |

| DP1, DM1                            | D+/D- data for USB 2.0 host/function      | -0.3 V to USBDPVcc1*1 + 0.3 V           |

| · ·                                 | module channel 1                          |                                         |

| AN007 to AN000                      | Analog input pins                         | -0.3 V to AVcc*1 + 0.3 V*2              |

| Other input pins                    | -                                         | -0.3 V to PVcc*1 + 0.3 V                |

| <u> </u>                            |                                           | ۱                                       |

Notes: Some pins may not exist depending on the packages.

In RZ/A2M, there is no input pin which uses LVDSAPVcc.

In the RZ/A2M Hardware Manual Table 56.1 Absolute Maximum Rating "Other input pin" item, power supply pins that apply 3.3 V are listed without differentiation, so LVDSAPVcc is included in the RZ/A2M Hardware Manual Table 56.1.

\*1. Rated value changes in accordance with the power supply voltage applied.

For example, when 0 V is applied to AVcc, the AN000 rated value will be -0.3 V to 0.3 V.

\*2. This is the rated value when the GPIO ports are set to analog input pins.

#### 1.2.1 Points of caution when voltage is applied while system power supply is OFF

Design the board so that the absolute maximum ratings for LSI of this series, as shown in Table 1.3 and Table 1.4 are observed, even when the power supply is OFF.

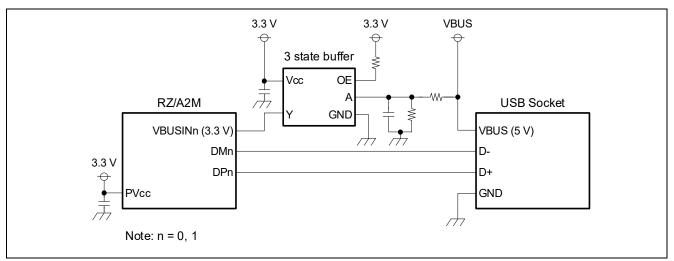

For example, in the case that the RZ/A2M is used as a USB function module, when the RZ/A2M power supply is OFF and the USB host module is connected, if voltage that exceeds the absolute maximum rating (-0.3 V to 0.3 V) <sup>\*1</sup> is applied to the RZ/A2M VBUSIN input pin<sup>\*1</sup>, it may permanently damage the LSI. In order to avoid this, refer to the protection circuit shown in Figure 1.1 and ensure that LSI of this series is protected.

Note: \*1. The RZ/A2M VBUSIN input pin is multiplexed to the GPIO port, therefore the pin's absolute maximum rating is -0.3 V to PVcc + 0.3 V. For details, refer to "Other input pins" as shown in Table 1.4.

Figure 1.1 Example of LSI protection circuit

# 1.3 Bypass Capacitor

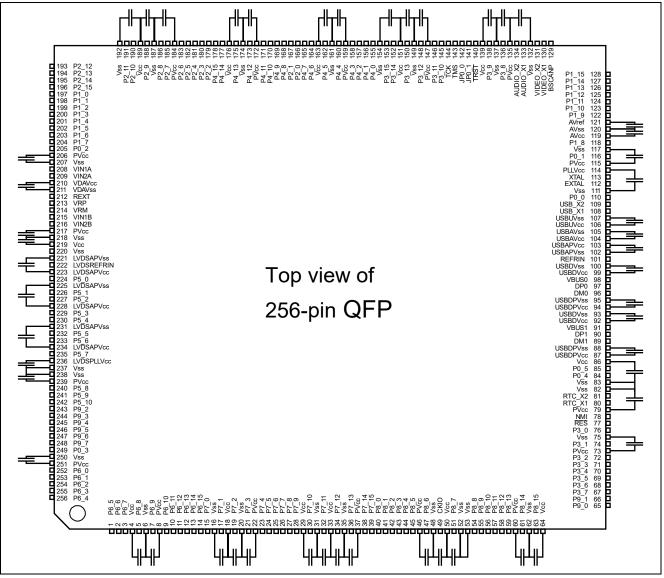

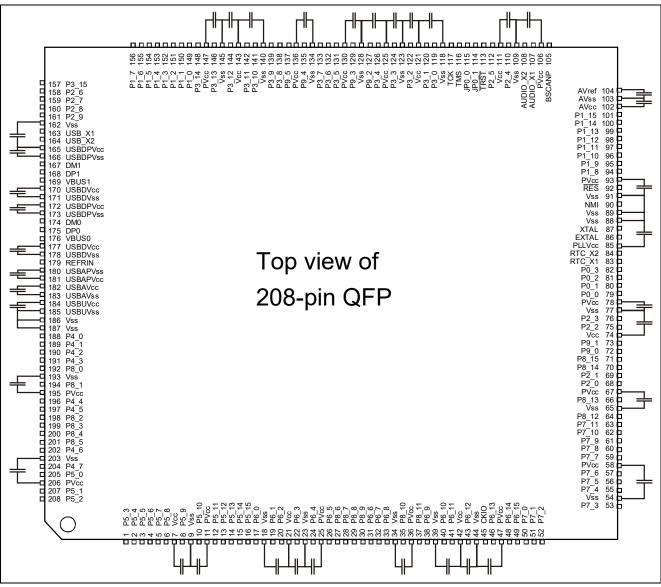

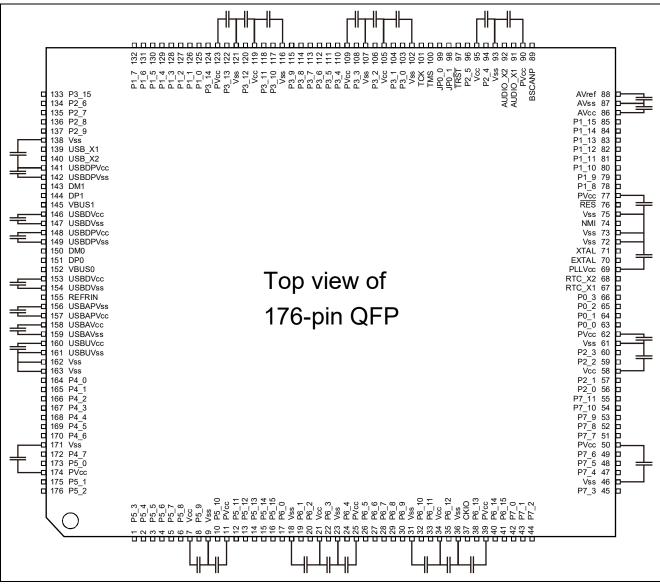

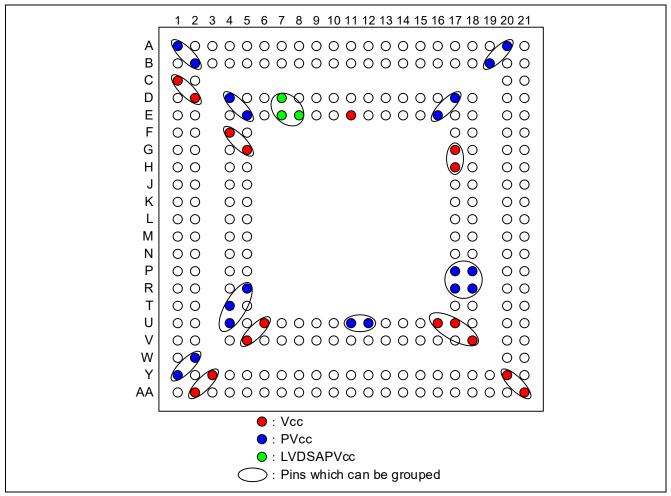

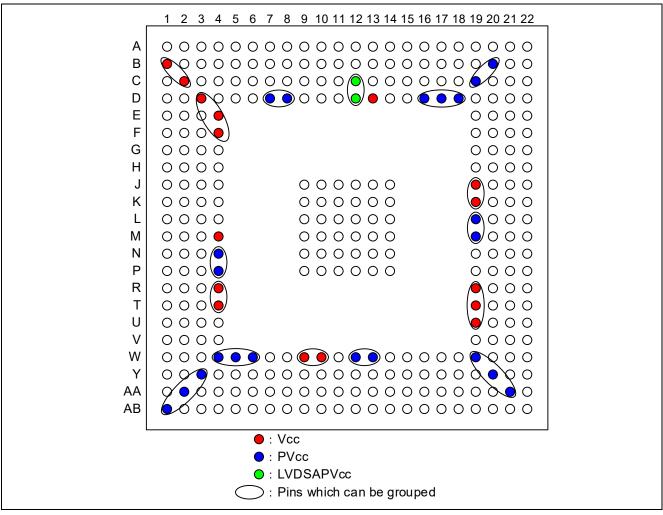

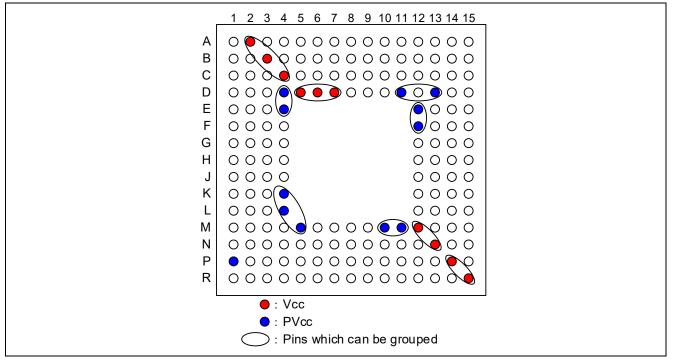

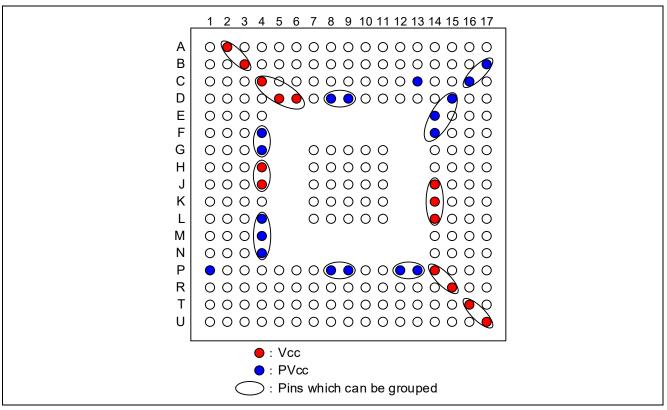

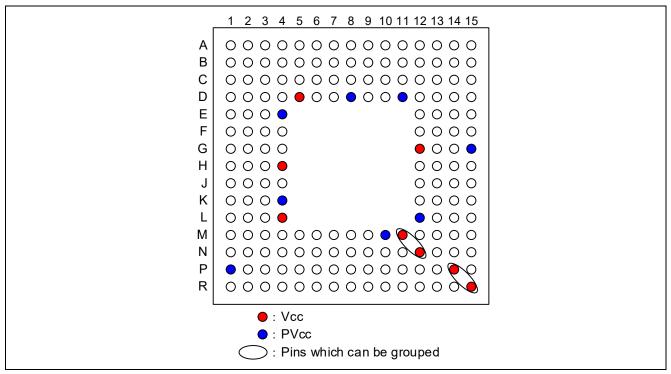

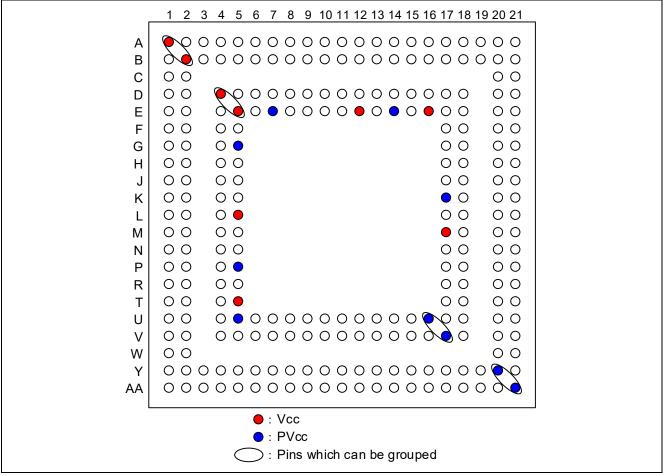

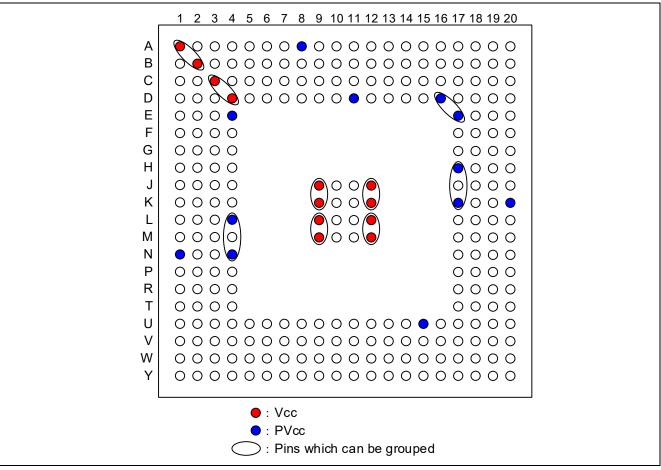

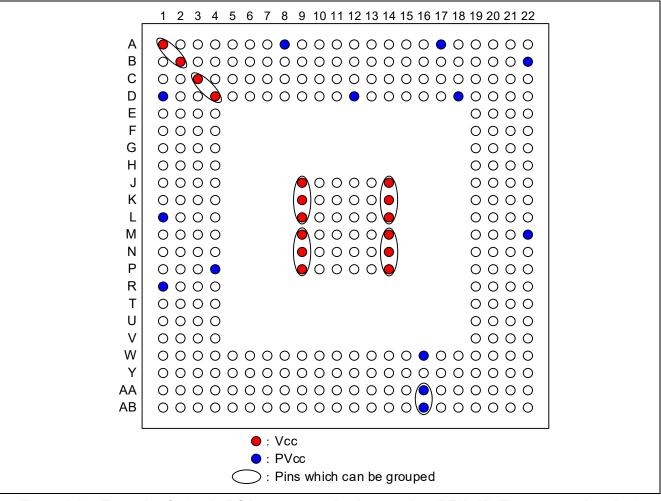

On the QFP, connect a laminated ceramic capacitor to each power supply pin pair as a bypass capacitor. Examples of QFP bypass capacitor configurations are shown in Figure 1.2 for 256-pin QFP, Figure 1.3 for 208-pin QFP, and Figure 1.4 for 176-pin QFP.

For the BGA package, if it is difficult to connect a bypass capacitor to all power supply pins, it is possible to collectively connect to multiple power supply pins. Figure 1.5 to Figure 1.12 shows the pins which can be grouped.

Locate the capacitor as close as possible to the LSI power supply pin, and use a capacity value from 0.1  $\mu F$  to 0.33  $\mu F$  (recommended value) per pin.

Figure 1.2 Example of 256-pin QFP capacitor configuration (RZ/A1HM)

Figure 1.3 Example of 208-pin QFP capacitor configuration (RZ/A1L)

Figure 1.4 Example of 176-pin QFP capacitor configuration (RZ/A1L)

Figure 1.5 Example of 256-pin BGA power supply pin grouping (RZ/A1HM) (Top perspective view)

Figure 1.6 Example of 324-pin BGA power supply pin grouping (RZ/A1HM) (Top perspective view)

Figure 1.7 Example of 176-pin BGA power supply pin grouping (RZ/A1L) (Top perspective view)

Figure 1.8 Example of 233-pin BGA power supply pin grouping (RZ/A1L) (Top perspective view)

Figure 1.10 Example of 256-pin BGA power supply pin grouping (RZ/A2M) (Top perspective view)

Figure 1.11 Example of 272-pin BGA power supply pin grouping (RZ/A2M) (Top perspective view)

Figure 1.12 Example of 324-pin BGA power supply pin grouping (RZ/A2M) (Top perspective view)

## 2. Reset

#### 2.1 Power ON and Power OFF Sequences

There is no particular order required for turning the 1.2-V power supply<sup>\*1</sup>, 1.8-V power supply<sup>\*1\*2</sup>, 1.8-V/3.3-V switchable power supply<sup>\*1\*2</sup> and 3.3-V power supply<sup>\*1</sup> on or off.

When turning power on, ensure that TRST# pin and RES# pin are set to low level \*3. If this is not observed, the output from the output pin or the I/O pin will become undefined, which may cause erroneous operation or malfunctions in the overall system.

When turning power off, if there is the possibility of the problem described above, ensure that TRST# pin and RES# pin are set to low level.

In addition, ensure that the power on timing requirement shown in Table 2.1 are satisfied.

Notes: \*1. For breakdowns of each power supply, refer to Table 1.1 and Table 1.2.

- \*2. This power supply is not present in RZ/A1.

- \*3. For details, refer to Table 2.2 and Figure 2.5.

Table 2.1

Timing requirements

| Item                               | Symbol | Min. | Max. | Unit | Reference<br>Figure |

|------------------------------------|--------|------|------|------|---------------------|

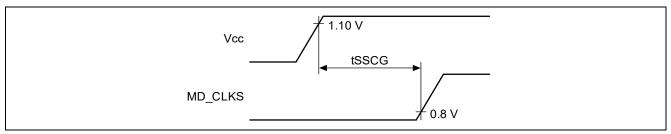

| SSCG stabilizing time *1*2         | tSSCG  | 1    | -    | μs   | Figure 2.1          |

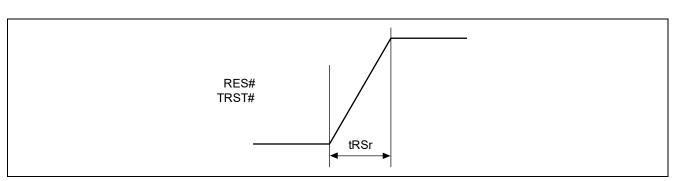

| RES# input rise time <sup>*3</sup> | tRSr   | -    | 500  | μs   | Figure 2.2          |

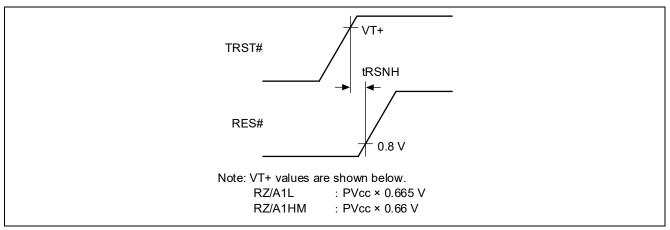

| RES# negating hold time*1*4        | tRSNH  | 0    | -    | ns   | Figure 2.3          |

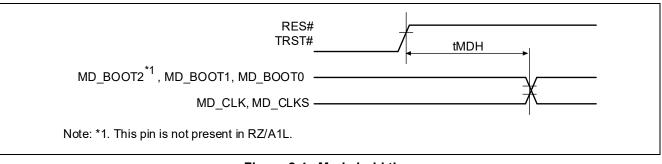

| Mode hold time                     | tMDH   | 200  | -    | ns   | Figure 2.4          |

Notes: \*1. This stipulation is not present in RZ/A2M.

- \*2. Ensure that this requirement is satisfied if the SSCG function is used.

- \*3. For RZ/A1, ensure that this item is satisfied if the TRST# pin and RES# pin are controlled using the same signal.

- \*4. Ensure that this item is satisfied if the TRST# pin and RES# pin are controlled using different signals separately.

Figure 2.1 SSCG stabilizing time

Figure 2.2 RES# input rise time

Figure 2.4 Mode hold time

## 2.2 Oscillation Settling Time

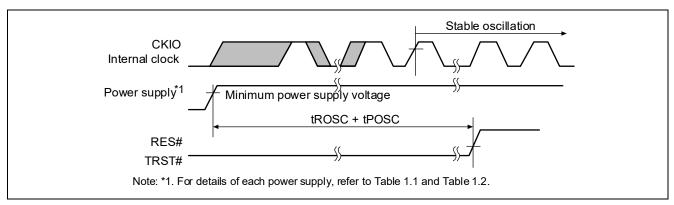

If the RES# pin is set to low level, LSI of this series will change to the power on reset state. In order to definitively reset LSI of this series, ensure that the RES# pin and TRST# pin are maintained at low level for the power on oscillation settling time (tROSC + tPOSC) while power supply is switched on.

The power on oscillation settling time is stipulated as the time from when the power supply voltage rises above the minimum value until the RES# pin has exceeded the VIL Max. Table 2.2 shows the timing requirements of power on oscillation settling time and Figure 2.5 shows the power on oscillation settling time.

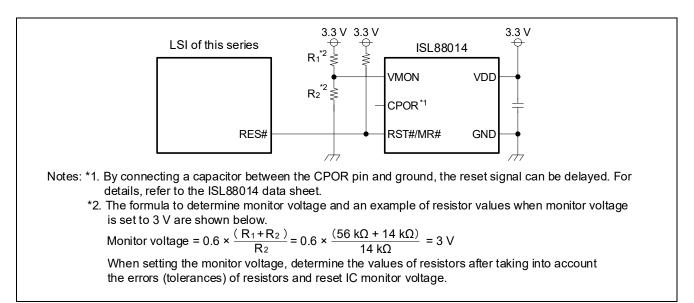

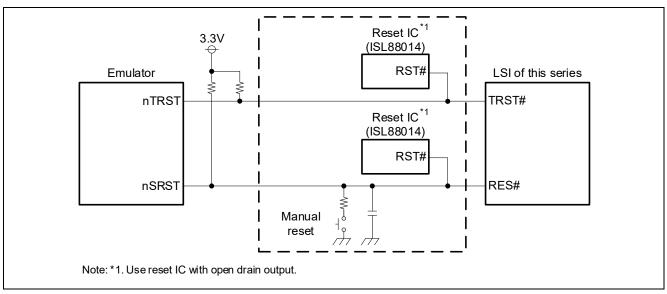

Power on reset control is possible by using the reset IC such as Renesas Electronics ISL88014. Figure 2.6 shows a connection example for the reset IC.

#### Table 2.2 Timing requirements of power on oscillation settling time

| Item                                                                | Symbol | Min. | Max.            | Unit |

|---------------------------------------------------------------------|--------|------|-----------------|------|

| On-chip PLL circuit oscillation settling time                       | tPOSC  | 1    | -               | ms   |

| On-chip oscillation circuit oscillation settling time <sup>*1</sup> | tROSC  | -    | 4 <sup>*2</sup> | ms   |

Note: \*1. When use external clock, this time is unnecessary.

<sup>\*2.</sup> Settings for values smaller than the above specifications may be possible, as long as the values are confirmed through evaluation by the manufacturer of the oscillator.

Figure 2.5 Power on oscillation settling time

#### Figure 2.6 Example of reset IC connection

# 3. Oscillator Circuit

## 3.1 Clock Pins

Table 3.1 shows pins to which a crystal resonator can connect or a clock can be input, and their frequencies.

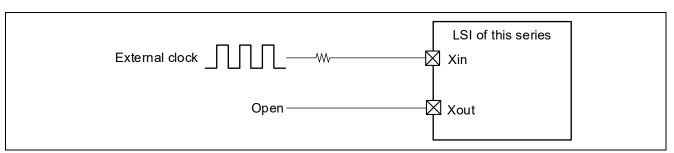

If the clock pin is not used, fix the Xin pin (pull-up, pull-down, or ground connection), and set the Xout pin to open-circuit.

#### Table 3.1 Clock pins

| Xin Pin <sup>*1</sup> | Xout Pin <sup>*1</sup> | Comments                                                                                          |                                                                   | Applicable LSIs |

|-----------------------|------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|

| EXTAL                 | XTAL                   | EXTAL clock input frequency<br>(When providing clock to<br>USB2.0 host/function module)           | 12 MHz ± 100ppm<br>12 MHz ± 100ppm<br>24 MHz ± 100ppm<br>*2       | RZ/A1<br>RZ/A2M |

|                       |                        | EXTAL clock input frequency<br>(When not providing clock to<br>USB2.0 host/function module)       | 10 MHz to 13.33 MHz<br>10 MHz to 12 MHz<br>20 MHz to 24 MHz<br>*2 | RZ/A1<br>RZ/A2M |

| USB_X1                | USB_X2                 | During high speed operation<br>During non-high speed<br>operation and during host<br>operation    | 48 MHz ± 100ppm<br>48 MHz ± 500ppm                                | RZ/A1           |

|                       |                        | During non-high speed<br>operation and during function<br>operation                               | 48 MHz ± 2500ppm                                                  |                 |

|                       |                        | USB_X1 clock input frequency<br>(When providing 48MHz clock<br>to USB2.0 host/function<br>module) | 48 MHz ± 100ppm                                                   | RZ/A2M          |

| AUDIO_X1              | AUDIO_X2               | When a crystal resonator is connected                                                             | 10 MHz to 50 MHz                                                  | RZ/A Series     |

|                       |                        | When external clock is input                                                                      | 1 MHz to 50 MHz                                                   |                 |

| RTC_X1                | RTC_X2                 | 32.768 kHz                                                                                        |                                                                   | RZ/A Series     |

| RTC_X3                | RTC_X4                 | 4 MHz                                                                                             |                                                                   | RZ/A1HM         |

| VIDEO_X1              | VIDEO_X2               | 27 MHz ± 50ppm <sup>*3</sup>                                                                      |                                                                   | RZ/A1HM         |

Notes: \*1. When using an external clock, input to Xin pin, when using a crystal resonator, connect between Xin pin and Xout pin.

\*2. Input frequency range changes according to MD\_CLK pin. For details, refer to "Table 4.14 Clock mode setting pin and clock I/O relationship".

\*3. Reference value. The accuracy of the clock signal affects the quality of images output by the digital video decoder. Input clock signals that are as accurate as is possible.

## 3.2 Example of External Clock Connection

Figure 3.1 shows an example of an external clock connection. If the Xout pin is set to an open state, the parasitic capacitance must be 10 pF or less.

Figure 3.1 Example of external clock connection

## 3.3 Example of Crystal Resonator Connection

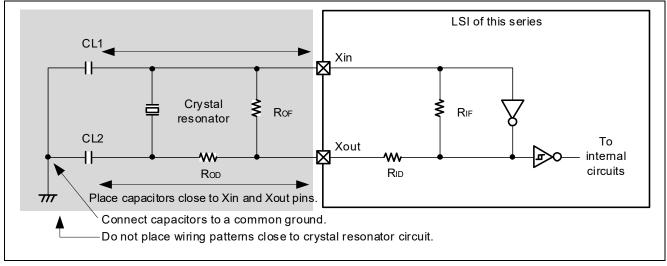

Figure 3.2 shows an example of a crystal resonator connection.

The crystal resonator and capacitors CL1 and CL2 should be placed as close as possible to the Xin pin and the Xout pin. In addition, to avoid inductance and to ensure proper oscillation, make the grounding point common for the resonator and the added capacitors, and ensure that the wiring patterns are not placed close to these parts.

Because the resonator's circuit constants will vary depending on the crystal resonator itself, the floating capacity of the implemented circuit, etc., determine the parameters (resistance and capacity value) after consulting with the resonator manufacturer<sup>\*1</sup> and performing sufficient evaluations. Although LSI of this series has an on-chip feedback resistor, an external feedback resistor may be required depending on the resonator's properties.

Note: \*1. Examples of resonator and circuit matching suitable for the products for LSI of this series are shown on the resonator manufacturer website below. If the optimized resonator circuit constant for your system is necessary, ask the manufacturer of the resonator. <a href="http://prdct-search.kyocera.co.jp/crystal-ic/?p=en\_search/">http://prdct-search.kyocera.co.jp/crystal-ic/?p=en\_search/</a>

Figure 3.2 Example of crystal resonator connection

# 4. Operating Mode

## 4.1 Boot Mode

LSI of this series have the boot modes shown in Table 4.1, and the boot mode is determined using the boot mode setting pins (MD\_BOOT2<sup>\*1</sup> to MD\_BOOT0).

Note: \*1. MD\_BOOT2 pin is not present on RZ/A1L.

## 4.1.1 Boot Mode Setting Pin (MD\_BOOT2 to MD\_BOOT0)

For LSI of this series, the boot mode is determined using the boot mode setting pins when the RES# pin is set to low level. The relationship between the boot mode setting pins and the boot modes is shown in Table 4.1. In addition, Figure 5.1 to Figure 5.26 show connection examples for various boot modes.

Ensure that the mode hold time (tMDH) is satisfied on reset cancellation. For details, refer to "2.1 Power ON and Power OFF Sequences".

| Table 4 1 | Relationshi  | n between boot m | odes and boot r | node setting nins | (MD | BOOT2 to MD_BO | OT0) |

|-----------|--------------|------------------|-----------------|-------------------|-----|----------------|------|

|           | Relationship |                  |                 | noue setting pins |     |                | 010) |

| Boot Mode                             | RZ/A1HM<br>MD_BOOT |   | RZ/A1L<br>MD_BOOT |   | RZ/A2M<br>MD_BOOT |   |   | Connection |                               |

|---------------------------------------|--------------------|---|-------------------|---|-------------------|---|---|------------|-------------------------------|

|                                       |                    |   |                   |   |                   |   |   | Diagram    |                               |

|                                       | 2                  | 1 | 0                 | 1 | 0                 | 2 | 1 | 0          | -                             |

| CS0 Space 16-bit Boot                 | N/A*1              | 0 | 0                 | 0 | 0                 | 0 | 0 | 0          | Figure 5.1                    |

| CS0 Space 32-bit Boot                 | N/A*1              | 1 | 0                 | - | -                 | - | - | -          | Figure 5.2<br>Figure 5.3      |

| eSD Boot                              | 0                  | 1 | 1                 | 0 | 1                 | 0 | 0 | 1          | -                             |

| eMMC Boot                             | 1                  | 1 | 1                 | 1 | 1                 | 0 | 1 | 0          | Figure 5.26                   |

| Serial Flash Boot (3.3-V products)    | 1                  | 0 | 1                 | 1 | 0                 | 0 | 1 | 1          | Figure 5.10 to<br>Figure 5.13 |

| Octal-SPI Flash Boot (1.8-V products) | -                  | - | -                 | - | -                 | 1 | 0 | 0          | Figure 5.14<br>Figure 5.19    |

| HyperFlash Boot 1 (1.8-V products)    | -                  | - | -                 | - | -                 | 1 | 0 | 1          | Figure 5.15                   |

| OctaFlash Boot (1.8-V products)       | -                  | - | -                 | - | -                 | 1 | 1 | 0          | Figure 5.20                   |

| HyperFlash Boot 2 (1.8-V products)    | -                  | - | -                 | - | -                 | 1 | 1 | 1          | Figure 5.16                   |

Note: \*1. N/A (Not Applicable) indicates that the pin state can be either 0 or 1.

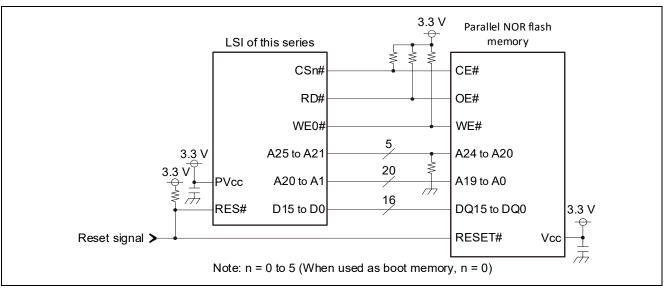

### 4.1.2 CS0 Space 16-bit Boot

Boot from memory (16-bit bus width) connected to CS0 space.

Table 4.2 shows the pins for which the boot program sets functions in this boot mode.

The initial state for pins from A25 to A21 is as general purpose ports<sup>\*1</sup>, and therefore if the output is indefinite, access to the intended addresses may not be possible. Therefore, if using pins from A25 to A21, use an external pull-down.

An example of connection supported by this boot mode is shown in Figure 5.1.

Note: \*1. For RZ/A1, these become the general purpose input port, and for RZ/A2M, these become the general purpose I/O ports in Hi-Z state.

| Pin Name  | Port                            |                                |                                                |  |  |  |

|-----------|---------------------------------|--------------------------------|------------------------------------------------|--|--|--|

|           | RZ/A1HM                         | RZ/A1L                         | RZ/A2M <sup>*1</sup>                           |  |  |  |

| A20 to A1 | P8_12 to P8_0,<br>P7_15 to P7_9 | P4_3 to P4_0,<br>P3_15 to P3_0 | PA_4 to PA_0,<br>P9_7 to P9_0,<br>P8_7 to P8_1 |  |  |  |

| D15 to D0 | P6_15 to P6_0                   | P5_15 to P5_0                  | P2_3 to P2_0,<br>P1_4 to P1_0,<br>P0_6 to P0_0 |  |  |  |

| CS0#      | P7_0                            | P2_7                           | PB_3                                           |  |  |  |

| RD#       | P7_8                            | P2_8                           | P7_7                                           |  |  |  |

| CKIO      | CKIO                            | CKIO                           | CKIO                                           |  |  |  |

Table 4.2

Pins used in CS0 space 16-bit boot mode

Note: \*1. Only for 324-pin BGA package.

#### 4.1.3 CS0 Space 32-bit Boot

Boot from memory (32-bit bus width) connected to CS0 space.

Table 4.3 shows the pins for which the boot program sets functions in this boot mode.

The initial state for pins from A25 to A21 is as general purpose ports, and therefore if the output is indefinite, access to the intended addresses may not be possible. Therefore, if using pins from A25 to A21, use an external pull-down.

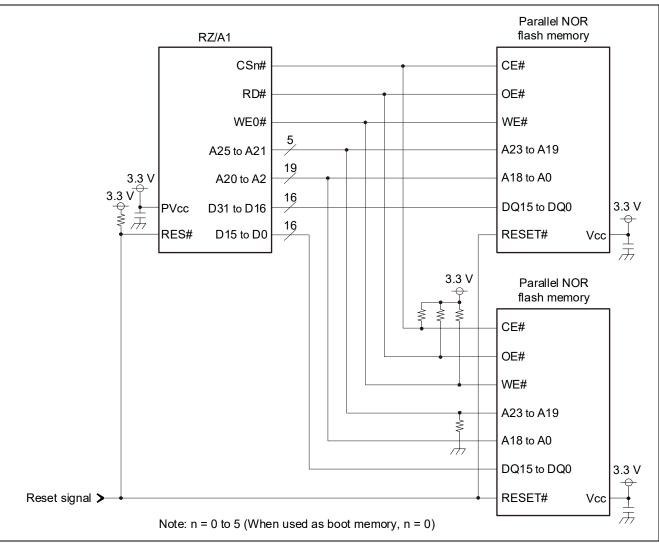

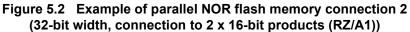

Examples of connection supported by this boot mode are shown in Figure 5.2 and Figure 5.3.

| Table 4.3 | Pins used in CS0 space 32-bit boot mode |

|-----------|-----------------------------------------|

|-----------|-----------------------------------------|

| Pin Name  | Port                             | Port   |        |  |  |  |  |

|-----------|----------------------------------|--------|--------|--|--|--|--|

|           | RZ/A1HM                          | RZ/A1L | RZ/A2M |  |  |  |  |

| A20 to A2 | P8_12 to P8_0,<br>P7_15 to P7_10 | -      | -      |  |  |  |  |

| D31 to D0 | P2_15 to P2_0,<br>P6_15 to P6_0  | -      | -      |  |  |  |  |

| CS0#      | P7_0                             | -      | -      |  |  |  |  |

| RD#       | P7_8                             | -      | -      |  |  |  |  |

| CKIO      | CKIO                             | -      | -      |  |  |  |  |

## 4.1.4 eSD Boot

Boots from the on-chip NAND flash memory<sup>\*1</sup> for the SD controller connected to Channel 0 on the SD Host Interface<sup>\*2</sup>.

Table 4.4 shows the pins for which the boot program sets functions in this boot mode.

For RZ/A2M, fix the unused pins from SD0\_DAT7 to SD0\_DAT4 (pull-up/pull-down). For details, refer to "7.2 Treatment of Unused Pins".

In this boot mode, the write protect pin<sup>\*3</sup> and card detection pin<sup>\*4</sup> are not used. Treat pins in accordance with software specifications.

Notes: For development of SD host related products, conclusion of an SD Host/Ancillary Product License Agreement (SD HALA) is necessary.

- \*1. It is possible to boot the LSI from the embedded SD (eSD) defined by the SD specification part 1 eSD addendum version 2.10 standard.

- \*2. For RZ/A2M, this is an SD/MMC Host Interface.

- \*2. Pin names are SD\_WP\_0 in RZ/A1 and SD0\_WP in RZ/A2M.

- \*3. Pin names are SD\_CD\_0 in RZ/A1 and SD0\_CD in RZ/A2M.

Table 4.4 Pins used in eSD boot

| Pin Name             | Port          |             |                      |  |  |

|----------------------|---------------|-------------|----------------------|--|--|

|                      | RZ/A1HM       | RZ/A1L      | RZ/A2M               |  |  |

| SD_CLK_0             | P4_12         | P3_3        | -                    |  |  |

| SD_CMD_0             | P4_13         | P3_2        | -                    |  |  |

| SD_D3_0 to SD_D0_0   | P4_14, P4_15, | P3_1, P3_0, | -                    |  |  |

|                      | P4_10, P4_11  | P3_5, P3_4  |                      |  |  |

| SD0_CLK              | -             | -           | SD0_CLK              |  |  |

| SD0_CMD              | -             | -           | SD0_CMD              |  |  |

| SD0_DAT3 to SD0_DAT0 | -             | -           | SD0_DAT3 to SD0_DAT0 |  |  |

## 4.1.5 eMMC Boot

Boots from the on-chip NAND flash memory<sup>\*1</sup> for the MMC controller connected to Channel 0 on the MMC Host Interface<sup>\*2</sup> (4-bit width for RZ/A1 and 8-bit width for RZ/A2M).

Table 4.5 shows the pins for which the boot program sets functions in this boot mode.

Examples of the connection supported by this boot mode are shown in Figure 5.26 and Figure 5.27.

# Note: \*1. Boot is possible only from eMMC devices which comply with the JEDEC STANDARD JESD84 A44 (MMCA 4.4). (Cannot boot from MMC card.)

\*2. For RZ/A2M, this is an SD/MMC Host Interface.

| Pin Name             | Port          |             |                      |  |  |

|----------------------|---------------|-------------|----------------------|--|--|

|                      | RZ/A1HM       | RZ/A1L      | RZ/A2M               |  |  |

| MMC_CLK              | P3_12         | P7_4        | -                    |  |  |

| MMC_CMD              | P3_13         | P7_5        | -                    |  |  |

| MMC_D3 to MMC_D0     | P3_14, P3_15, | P7_6, P7_7, | -                    |  |  |

|                      | P3_10, P3_11  | P7_2, P7_3  |                      |  |  |

| SD0_CLK              | -             | -           | SD0_CLK              |  |  |

| SD0_CMD              | -             | -           | SD0_CMD              |  |  |

| SD0_DAT7 to SD0_DAT0 | -             | -           | SD0_DAT7 to SD0_DAT0 |  |  |

| SD0_RST#             | -             | -           | SD0_RST#             |  |  |

#### Table 4.5 Pins used in eMMC boot

## 4.1.6 Serial Flash Boot (3.3-V products)

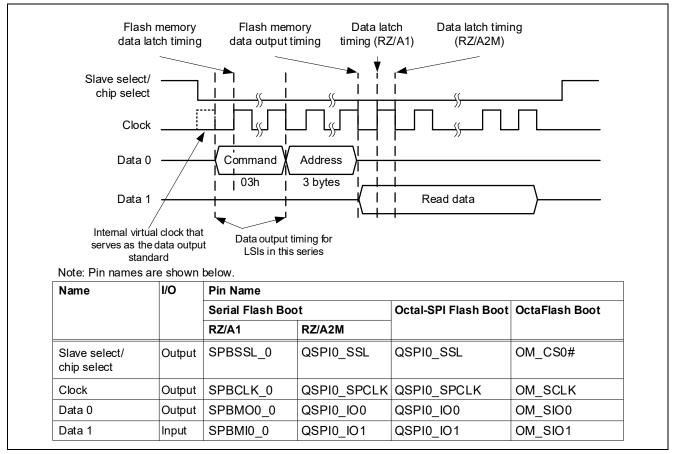

Boot from serial flash memory (3.3-V products) connected to SPI multi-I/O bus space.

Table 4.6 shows the pins for which the boot program sets functions in this boot mode.

In this boot mode, after released from the reset state, because read is performed from the serial flash memory setting as shown in Table 4.7, ensure that products which satisfy these are used.

Examples of connection supported by this boot mode are shown in Figure 5.10 to Figure 5.13.

| Table 4.6 | Pins used | in serial | flash boot |

|-----------|-----------|-----------|------------|

|-----------|-----------|-----------|------------|

| Pin Name    | Port    | Port   |             |  |  |  |

|-------------|---------|--------|-------------|--|--|--|

|             | RZ/A1HM | RZ/A1L | RZ/A2M      |  |  |  |

| SPBCLK_0    | P9_2    | P4_4   | -           |  |  |  |

| SPBSSL_0    | P9_3    | P4_5   | -           |  |  |  |

| SPBMO0_0    | P9_4    | P4_6   | -           |  |  |  |

| SPBMI0_0    | P9_5    | P4_7   | -           |  |  |  |

| QSPI0_SPCLK | -       | -      | QSPI0_SPCLK |  |  |  |

| QSPI0_SSL   | -       | -      | QSPI0_SSL   |  |  |  |

| QSPI0_IO0   | -       | -      | QSPI0_IO0   |  |  |  |

| QSPI0_IO1   | -       | -      | QSPI0_IO1   |  |  |  |

Table 4.7 Serial flash boot settings

| Item                   | Description                               |  |

|------------------------|-------------------------------------------|--|

| Bit rate <sup>*1</sup> | 12.5 MHz to 16.67 MHz (RZ/A1)             |  |

|                        | 13.75 MHz to 16.5 MHz (RZ/A2M)            |  |

| Opcode                 | READ (03h)                                |  |

| Address cycle          | 3 bytes                                   |  |

| Dummy cycle            | None                                      |  |

| Bus width              | 1-bit                                     |  |

| CPOL                   | Positive polarity                         |  |

| CPHAR                  | Receive data on odd number edge (RZ/A1)   |  |

|                        | Receive data on even number edge (RZ/A2M) |  |

| CPHAT                  | Transmit data on even number edge         |  |

| Note: *1. RZ/A1        | SPBCLK 0                                  |  |

RZ/A2M : QSPI0\_SPCLK Bit rate is dependent on input freque

Bit rate is dependent on input frequency.

#### 4.1.7 Octal-SPI Flash Boot (1.8-V products)

Boot from Octal-SPI flash memory connected to SPI multi-I/O bus space (1.8-V products).

Table 4.8 shows the pins for which the boot program sets functions in this boot mode.

In this boot mode, RZ/A2M operates the same as serial flash boot.

Examples of connection supported by this boot mode are shown in Figure 5.14 and Figure 5.19.

#### Table 4.8 Pins used in Octal-SPI flash boot

| Pin Name    | Port    | Port   |             |  |  |  |

|-------------|---------|--------|-------------|--|--|--|

|             | RZ/A1HM | RZ/A1L | RZ/A2M      |  |  |  |

| QSPI0_SPCLK | -       | -      | QSPI0_SPCLK |  |  |  |

| QSPI0_SSL   | -       | -      | QSPI0_SSL   |  |  |  |

| QSPI0_IO0   | -       | -      | QSPI0_IO0   |  |  |  |

| QSPI0_IO1   | -       | -      | QSPI0_IO1   |  |  |  |

### 4.1.8 HyperFlash Boot 1 (1.8-V products)

Boot from HyperFlash connected to SPI multi-I/O bus space (1.8-V products).

Table 4.9 shows the pins for which the boot program sets functions in this boot mode.

An example of connection supported by this boot mode is shown in Figure 5.15.

#### Table 4.9 Pins used in HyperFlash boot 1

| Pin Name               | Port    |        |                        |  |  |

|------------------------|---------|--------|------------------------|--|--|

|                        | RZ/A1HM | RZ/A1L | RZ/A2M                 |  |  |

| QSPI0_SSL              | -       | -      | QSPI0_SSL              |  |  |

| QSPI0_SPCLK            | -       | -      | QSPI0_SPCLK            |  |  |

| QSPI1_SPCLK            | -       | -      | QSPI1_SPCLK            |  |  |

| QSPI0_IO3 to QSPI0_IO0 | -       | -      | QSPI0_IO3 to QSPI0_IO0 |  |  |

| QSPI1_IO3 to QSPI1_IO0 | -       | -      | QSPI1_IO3 to QSPI1_IO0 |  |  |

| QSPI1_SSL              | -       | -      | QSPI1_SSL              |  |  |

| RPC_RESET#             | -       | -      | RPC_RESET#             |  |  |

#### 4.1.9 OctaFlash Boot (1.8-V products)

Boot from OctaFlash connected to OctaFlash space (1.8-V products).

Table 4.10 shows the pins for which the boot program sets functions in this boot mode.

In this boot mode, after released from the reset state, because read is performed from the OctaFlash setting as shown in Table 4.11, ensure that products which satisfy these are used.

An example of connection supported by this boot mode is shown in Figure 5.20.

#### Table 4.10 Pins used in OctaFlash boot

| Pin Name         | Port    |        |                  |  |

|------------------|---------|--------|------------------|--|

|                  | RZ/A1HM | RZ/A1L | RZ/A2M           |  |

| OM_SCLK          | -       | -      | OM_SCLK          |  |

| OM_CS0#          | -       | -      | OM_CS0#          |  |

| OM_SIO1, OM_SIO0 | -       | -      | OM_SIO1, OM_SIO0 |  |

#### Table 4.11 Settings for OctaFlash boot

| Item                 | Description                       |

|----------------------|-----------------------------------|

| Bit rate (OM_SCLK)*1 | 13.75 MHz to 16.5 MHz             |

| Opcode               | READ (03h)                        |

| Address cycle        | 3 bytes                           |

| Dummy cycle          | None                              |

| Bus width            | 1-bit                             |

| CPOL                 | Positive polarity                 |

| CPHAR                | Receive data on even number edge  |

| CPHAT                | Transmit data on even number edge |

Note: \*1. Bit rate is dependent on input frequency.

#### 4.1.10 HyperFlash Boot 2 (1.8-V products)

Boot from HyperFlash connected to HyperFlash space (1.8-V products).

Table 4.12 shows the pins for which the boot program sets functions in this boot mode.

An example of connection supported by this boot mode is shown in Figure 5.16.

| Table 4.12 | Pins used in HyperFlash boot 2 |

|------------|--------------------------------|

|------------|--------------------------------|

| Pin Name         | Port    |        |                  |  |

|------------------|---------|--------|------------------|--|

|                  | RZ/A1HM | RZ/A1L | RZ/A2M           |  |

| HM_CS0#          | -       | -      | HM_CS0#          |  |

| HM_CK            | -       | -      | HM_CK            |  |

| HM_CK#           | -       | -      | HM_CK#           |  |

| HM_DQ7 to HM_DQ0 | -       | -      | HM_DQ7 to HM_DQ0 |  |

| HM_RWDS          | -       | -      | HM_RWDS          |  |

| HM_RESET#        | -       | -      | HM_RESET#        |  |

#### 4.1.11 Points of caution when selecting flash memory for use as boot memory

When selecting flash memory used for serial flash boot, Octal-SPI flash boot OctaFlash boot, select a product which can receive the read command issued by LSI of this series when released from the reset state (refer to Figure 4.1). The selection criteria are shown below.

1. Flash memory with independent reset pin

When cancelling busy state and initializing operation mode by reset signal input, if the reset pin is multiplexed and set as pin for another function, the reset may not be received and initialization may not be possible.

E.g.: If the RESET#/SIO3 pin is set to SIO3, reset input may not be received.

- 2. Flash memory that is initialized to a 3-byte address cycle and 1-bit command bit width by reset signal Flash memory that fulfills these requires are shown below.

- Flash memory that can set the address cycle and command bit width in a volatile register

or

- Flash memory that can set the address cycle and command bit width using a command Both types should initialize to a 3-byte address cycle and 1-bit command bit width by reset signal. Do

not set 4-byte address cycle or 4-bit command bit width to a non-volatile register.

Figure 4.1 Read command sequence

## 4.2 Clock Mode

#### 4.2.1 Clock Mode Setting Pin

LSI of this series can switches clock modes by the setting of the MD\_CLKS pin while the RES# pin is set to low level. Depending on the clock mode, for RZ/A1, the clock provision source is determined, and for RZ/A2M, the clock input frequency range is determined.

The relationship between the RZ/A1 clock mode setting pin and clock I/O is shown in Table 4.13, and the relationship between the RZ/A2M clock mode setting pin and clock I/O is shown in Table 4.14.

| Table 4.13 | Clock mode setting pin and clock I/O relationship (RZ/A1) |

|------------|-----------------------------------------------------------|

|------------|-----------------------------------------------------------|

| Clock | MD_CLK                                  | Clock I/O                |                       |                     |  |  |

|-------|-----------------------------------------|--------------------------|-----------------------|---------------------|--|--|

| Mode  | Mode Supply source Input frequency CKIO |                          | CKIO output frequency |                     |  |  |

| 0     | 0                                       | EXTAL/crystal resonator  | 10 MHz to 13.33 MHz   | 50 MHz to 66.67 MHz |  |  |

| 1     | 1                                       | USB_X1/crystal resonator | 48 MHz <sup>*1</sup>  | 64 MHz              |  |  |

Note: \*1. For acceptable error range, refer to Table 3.1 Clock pin.

#### Table 4.14 Clock mode setting pin and clock I/O relationship (RZ/A2M)

| Clock | MD_CLK | Clock I/O               |                  |                                     |  |

|-------|--------|-------------------------|------------------|-------------------------------------|--|

| Mode  |        | Supply source           | Input frequency  | CKIO output frequency <sup>*1</sup> |  |

| 0     | 0      | EXTAL/crystal resonator | 10 MHz to 12 MHz | 27.5 MHz to 132 MHz (Bφ)            |  |

| 1     | 1      | EXTAL/crystal resonator | 20 MHz to 24 MHz | 27.5 MHz to 66 MHz (P1φ)            |  |

Note: \*1. The CKIO frequency range changes according to the CKIO selection register (CKIOSEL [1:0]) setting value. For details, refer to RZ/A2M Group User's Manual: Hardware.

# 5. External Memory

## 5.1 Connectable Memory

Table 5.1 shows the memory which can be connected to LSI of this series, the supported controllers, and the maximum operating frequency.

Figure 5.1 to Figure 5.27 show examples of connection for various memories.

| Connectable                  | Supported<br>Controller                          | Maximum Operating Frequency     |                                    |                                    | Connection                    |

|------------------------------|--------------------------------------------------|---------------------------------|------------------------------------|------------------------------------|-------------------------------|

| Memory                       |                                                  | RZ/A1HM                         | RZ/A1L                             | RZ/A2M                             | Diagram                       |

| Parallel NOR<br>flash memory | Bus State<br>Controller                          | 66.67 MHz                       | 66.67 MHz                          | 132 MHz*1                          | Figure 5.1 to<br>Figure 5.3   |

| SDRAM                        |                                                  | 66.67 MHz                       | 66.67 MHz                          | 132 MHz <sup>*1</sup>              | Figure 5.4 to<br>Figure 5.6   |

| EEPROM                       | RSPI                                             | 33.33 MHz                       | 33.33 MHz                          | 33 MHz                             | Figure 5.7                    |

|                              | I2C Bus<br>Interface                             | 400 kHz<br>(High speed<br>mode) | 400 kHz<br>(High speed<br>mode)    | 1 MHz<br>(High speed<br>mode plus) | Figure 5.8                    |

| Serial flash                 | RSPI                                             | 33.33 MHz                       | 33.33 MHz                          | 33 MHz                             | Figure 5.9                    |

| memory                       | SPIBSC                                           | 66.67 MHz/SDR                   | 66.67 MHz/DDR*2<br>66.67 MHz/SDR*3 | 66 MHz/DDR                         | Figure 5.10 to<br>Figure 5.13 |

| Xccela flash<br>memory       | SPIBSC                                           | -                               | -                                  | 132 MHz/DDR                        | Figure 5.14                   |

| HyperFlash                   | SPIBSC                                           | -                               | -                                  | 132 MHz/DDR                        | Figure 5.15                   |

|                              | HyperBus                                         | -                               | -                                  | 132 MHz/DDR                        | Figure 5.16                   |

| HyperRAM                     | Controller                                       | -                               | -                                  | 132 MHz/DDR                        | Figure 5.17                   |

| OctaFlash                    | SPIBSC                                           | -                               | -                                  | 132 MHz/DDR                        | Figure 5.19                   |

|                              | Octa Memory                                      | -                               | -                                  | 132 MHz/DDR                        | Figure 5.20                   |

| OctaRAM                      | Controller                                       | -                               | -                                  | 132 MHz/DDR                        | Figure 5.21                   |

| NAND flash<br>memory         | NAND Flash<br>Memory<br>Controller <sup>*4</sup> | 16.67 MHz                       | -                                  | 33 MHz                             | Figure 5.23                   |

| eSD, SD card                 | SD Host                                          | 33.33 MHz                       | 33.33 MHz                          | 132 MHz                            | Figure 5.24                   |

|                              | Interface*5                                      | (High Speed)                    | (High Speed)                       | (UHS-I/SDR104)                     | Figure 5.25                   |

| eMMC, MMC                    | MMC Host<br>Interface <sup>*5</sup>              | 33.33 MHz<br>(High Speed)       | 33.33 MHz<br>(High Speed)          | 132 MHz<br>(HS200)                 | Figure 5.26<br>Figure 5.27    |

Table 5.1 List of connectable memory

Notes: \*1. Can connect only to 324-pin BGA package.

\*2. For RZ/A1LU group.

\*3. For RZ/A1L group, RZ/A1LC group.

\*4. NAND Flash Controller for RZ/A2M.

\*5. SD/MMC Host Interface for RZ/A2M.

## 5.2 Parallel NOR Flash Memory

RZ/A1 can connect to 8-, 16- and 32-bit width data buses while RZ/A2M can connect to 8- and 16-bit width data buses.

When a parallel NOR flash memory is used as a boot memory, and the pins from A25 to A21 are used, place pull-down resistors for these pins. In addition, LSI of this series and the flash memory must be reset at the same time.

Figure 5.1 to Figure 5.3 show examples of parallel NOR flash memory connection.

# 5.3 SDRAM

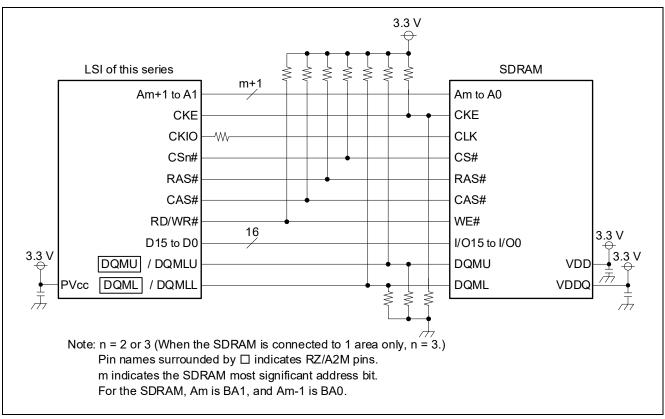

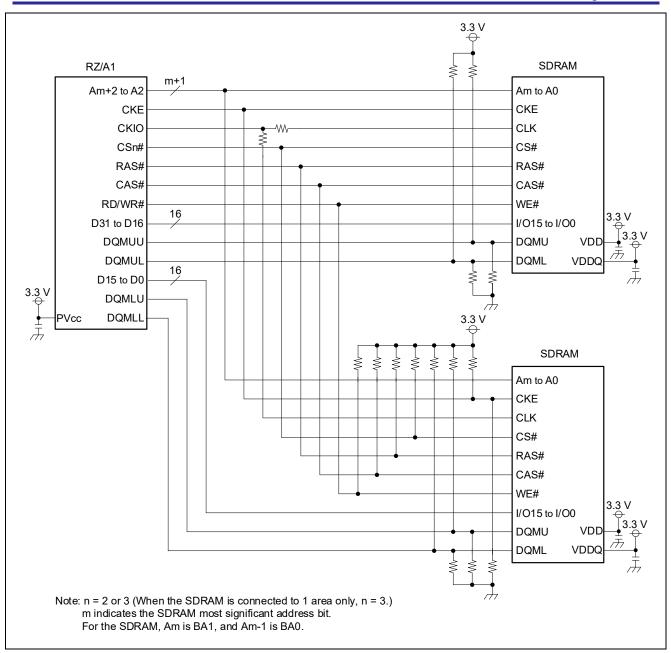

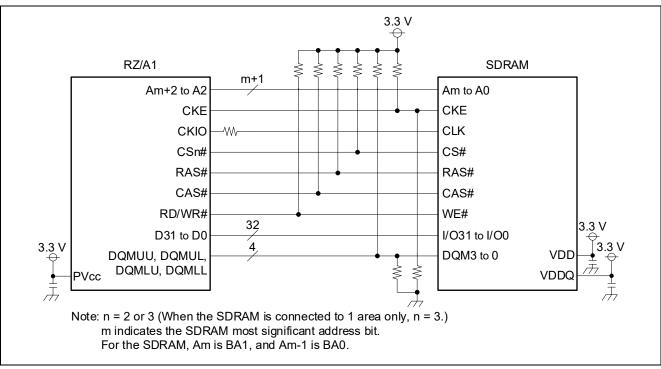

RZ/A1 can connect to 16- and 32-bit width data buses while RZ/A2M can connect to 16-bit width data bus.

Change the treatment of CKE and DQM pins to match the SDRAM initialization sequence.

Figure 5.4 to Figure 5.6 show examples of SDRAM connection.

Figure 5.4 Example of SDRAM connection 1 (16-bit width, connection to 1 x 16-bit product)

Figure 5.5 Example of SDRAM connection 2 (32-bit width, connection to 2 x 16-bit products (RZ/A1))

Figure 5.6 Example of SDRAM connection 3 (32-bit width, connection to 1 x 32-bit product (RZ/A1))

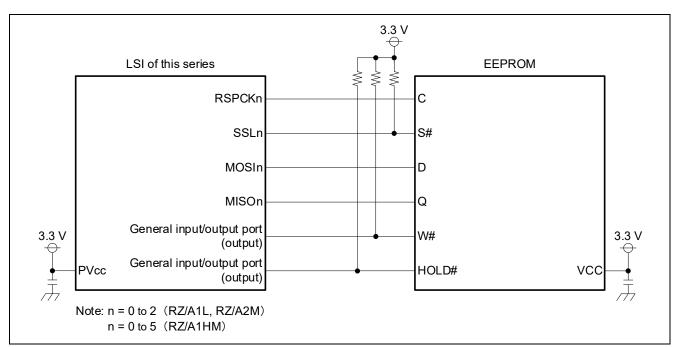

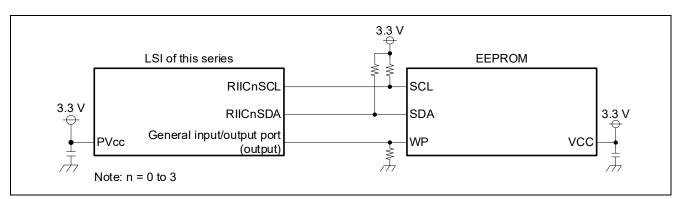

## 5.4 EEPROM

Change the treatment of W#, HOLD# and WP pins to match EEPROM polarity.

Figure 5.7 and Figure 5.8 show examples of connection between EEPROM and various controllers.

## Figure 5.7 Example of EEPROM connection 1 (RSPI)

Figure 5.8 Example of EEPROM connection 2 (I2C Bus Interface)

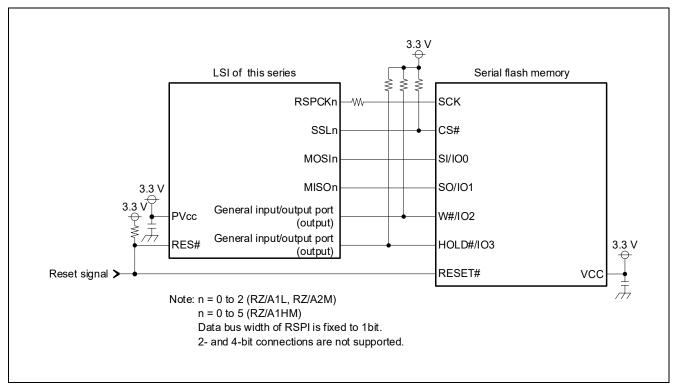

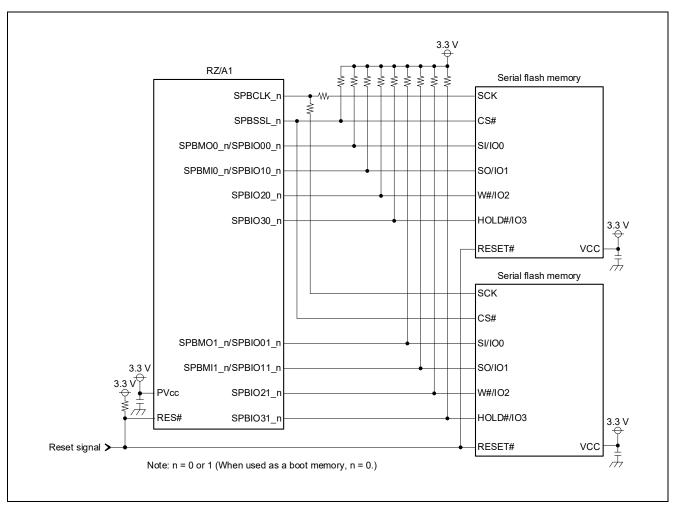

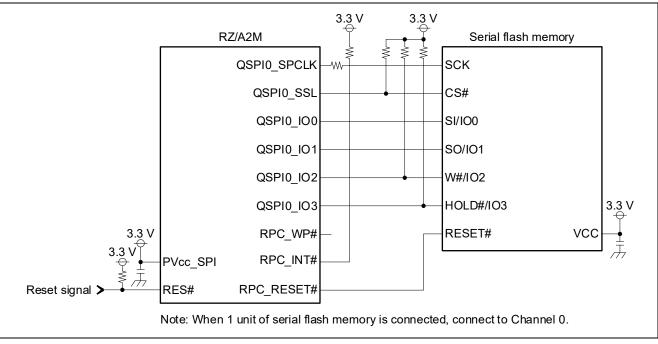

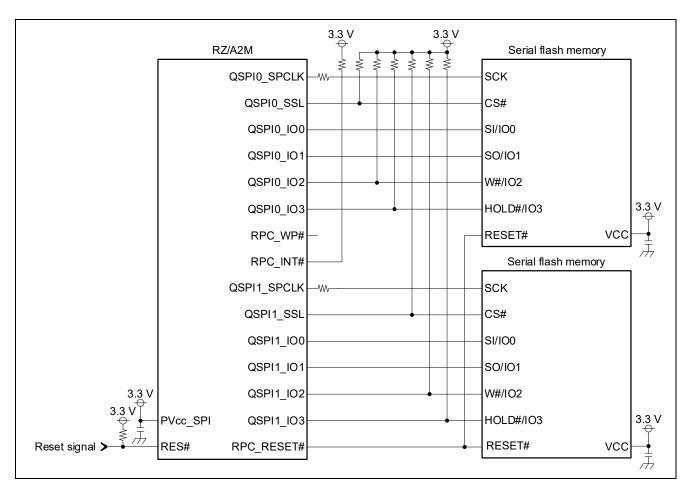

## 5.5 Serial Flash Memory

RZ/A1 can connect to 1-, 2- and 4-bit width data buses while RZ/A2M can connect to 1- and 4-bit width data buses. In the case of RZ/A2M, when 2 units of serial flash are connected, 2 serial flash memory devices are connected in parallel to implement an 8-bit bus interface.

When using serial flash memory as boot memory, use the flash memory having an independent reset pin, and ensure that it must be reset at the same time as LSI of this series.

For RZ/A2M, connect the RPC\_RESET# pin that outputs the reset which is synchronized to the RES# input to the flash memory RESET# pin.

For points of caution when selecting serial flash memory, refer to "4.1.11 Points of caution when selecting flash memory for use as boot memory".

Change the treatment of pins so that the data I/O pin and the multiplexed function pins match the serial flash polarity.

Figure 5.9 to Figure 5.13 show examples of connection between serial flash memory and various controllers.

Figure 5.9 Example of serial flash memory connection 1 (RSPI)

Figure 5.10 Example of serial flash memory connection 2 (SPIBSC, 4-bit bus width, connection to 1 x 4-bit product) (RZ/A1)

Figure 5.11 Example of serial flash memory connection 3 (SPIBSC, 8-bit bus width, connection to 2 x 4-bit products) (RZ/A1)

Figure 5.12 Example of serial flash memory connection 4 (SPIBSC, 4-bit bus width, connection to 1 x 4-bit product) (RZ/A2M)

Figure 5.13 Example of serial flash memory connection 5 (SPIBSC, 8-bit bus width, connection to 2 x 4-bit products) (RZ/A2M)

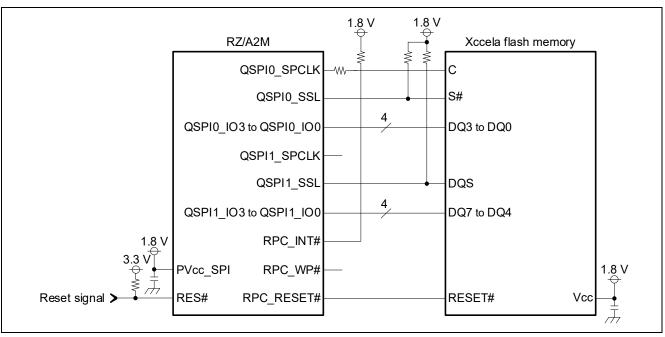

## 5.6 Xccela Flash Memory

When using Xccela flash memory as boot memory, connect the RPC\_RESET# pin that outputs the reset which is synchronized to the RES# input to the Xccela flash memory RESET# pin.

For points of caution when selecting Xccela flash memory, refer to "4.1.11 Points of caution when selecting flash memory for use as boot memory".

Figure 5.14 shows an example of Xccela flash memory connection.

Figure 5.14 Example of Xccela flash memory connection

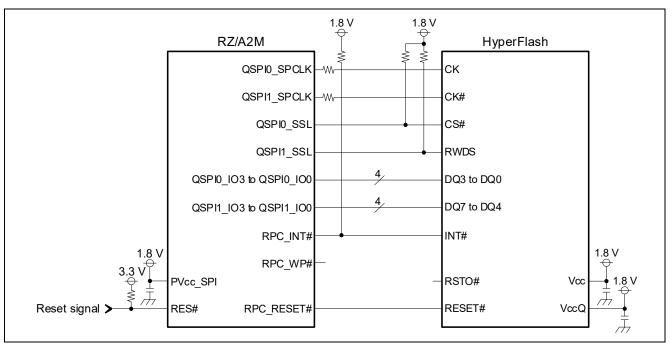

## 5.7 HyperBus Memory

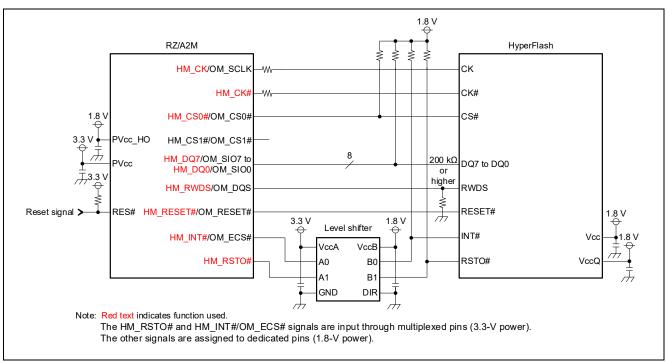

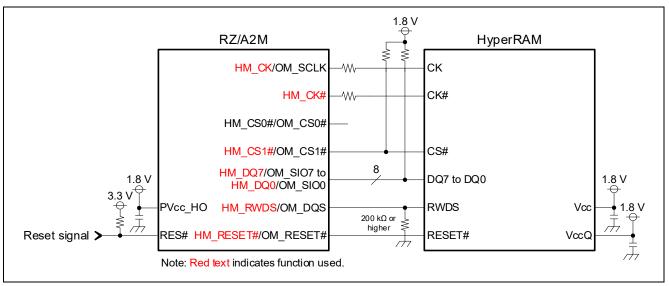

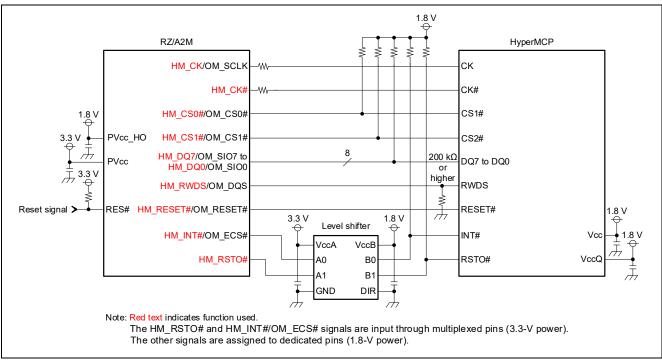

When HyperBus memory is connected to a HyperBus Controller (Figure 5.16 to Figure 5.18), ensure to place a pull-down resistor of 200 k $\Omega$  or more for the HyperBus memory RWDS pin.

## 5.7.1 HyperFlash

When using HyperFlash as boot memory, connect the RPC\_RESET# pin that outputs the reset which is synchronized to the RES# input or the HM\_RESET#/OM\_RESET# pin to the HyperFlash RESET# pin.

Figure 5.15 and Figure 5.16 show examples of HyperFlash and controller connection.

Figure 5.15 Example of HyperFlash connection 1 (SPIBSC)

Figure 5.16 Example of HyperFlash connection 2 (HyperBus Controller)

## 5.7.2 HyperRAM

Figure 5.17 shows an example of HyperRAM connection.

Figure 5.17 Example of HyperRAM connection

## 5.7.3 HyperMCP

HyperMCP is a multi-chip module that contains HyperFlash and HyperRAM.

Connect the HyperMCP CS1# pin to HM\_CS0# pin and the CS2# pin to HM\_CS1# pin.

Figure 5.18 shows an example of HyperMCP connection.

Figure 5.18 Example of HyperMCP connection

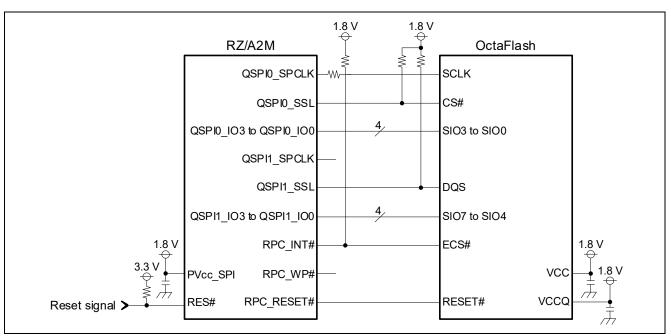

## 5.8 Octa Memory

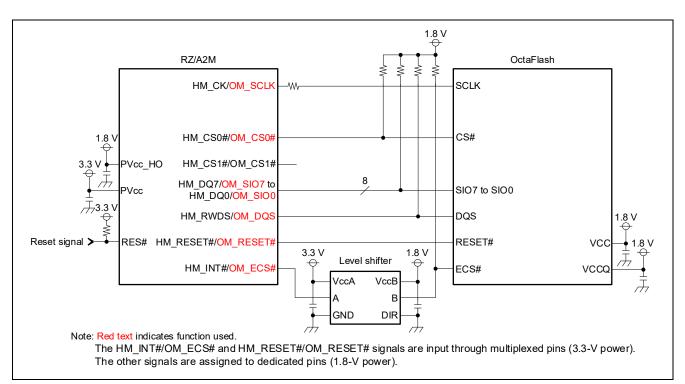

## 5.8.1 OctaFlash

When using OctaFlash as boot memory, connect the RPC\_RESET# pin that outputs the reset which is synchronized to the RES# input or the HM\_RESET#/OM\_RESET# pin to the OctaFlash RESET# pin.

For points of caution when selecting OctaFlash memory, refer to "4.1.11 Points of caution when selecting flash memory for use as boot memory".

Figure 5.19 and Figure 5.20 show examples of OctaFlash and controller connection.

Figure 5.19 Example of OctaFlash connection 1 (SPIBSC)

Figure 5.20 Example of OctaFlash connection 2(Octa Memory Controller)

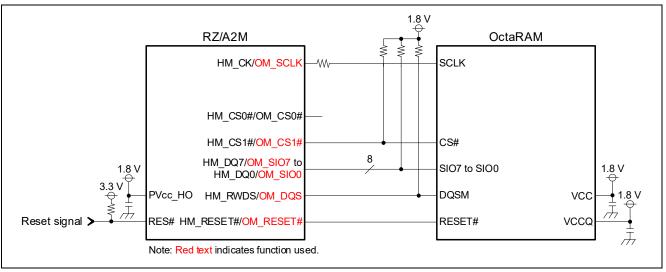

## 5.8.2 OctaRAM

Figure 5.21 shows an example of OctaRAM connection.

Figure 5.21 Example of OctaRAM connection

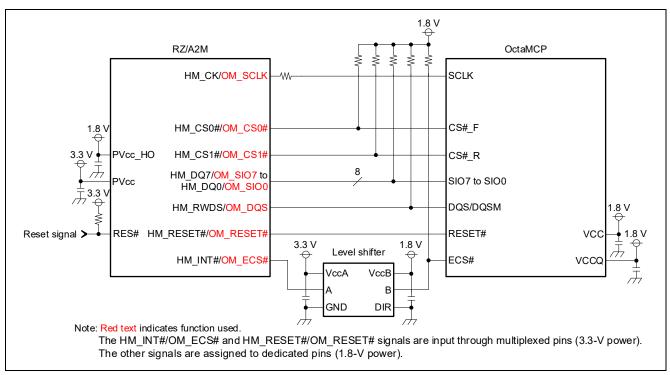

## 5.8.3 OctaMCP

OctaMCP is a multi-chip module that contains OctaFlash and OctaRAM.

Connect the OctaMCP CS#\_F pin to OM\_CS0# pin and the CS#\_R pin to OM\_CS1# pin.

Figure 5.22 shows an example of OctaMCP connection.

Figure 5.22 Example of OctaMCP connection

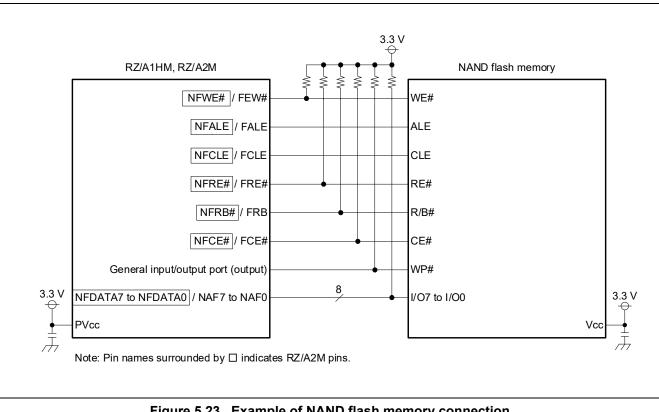

#### 5.9 NAND Flash Memory

The RZ/A2M NAND Flash Controller has an on-chip ECC unit, and bit error correction is possible. However, the RZ/A1 NAND Flash Memory Controller does not have the ECC function. Therefore, when use NAND flash memory on RZ/A1, ensure that NAND flash memory with ECC function is used.

Figure 5.23 shows an example of NAND flash memory connection.

Note: Use ONFi 1.x specification (excluding timing mode 3, 4, and 5) NAND flash devices with RZ/A2M.

Figure 5.23 Example of NAND flash memory connection

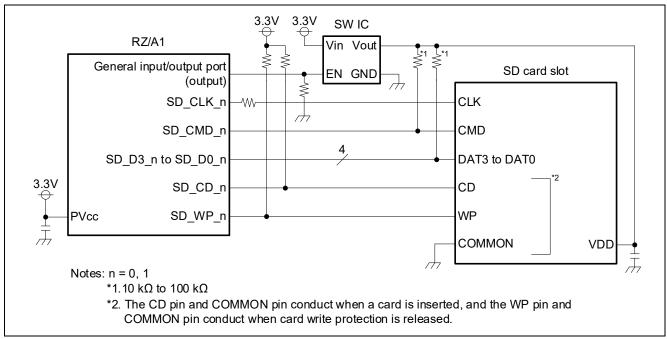

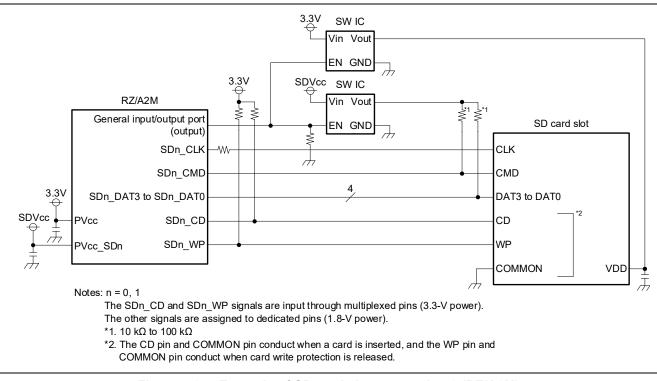

## 5.10 SD Card

Change the treatment of CD pin<sup>\*1</sup> and WP pin<sup>\*2</sup> to match the system specification. Figures 5.24 and 5.25 are examples where the CD and WP pins are low active. To reverse the logic, pull down the CD and WP pins and supply 3.3V to the COMMON pin.

For CMD and DAT3 to DAT0 pins, pull-up of 10 k $\Omega$  to 100 k $\Omega.$

If use the eSD boot, pleas supply power to SD card when power is turned on.

For RZ/A2M, when operation starts, supply 3.3 V to SDVcc, and switch between 1.8 V and 3.3 V in accordance with the operation mode.

Figure 5.24 and Figure 5.25 show examples of SD card slot connection.

Notes: \*1. It's a card detection pin. Pin names are SD\_CD\_n in RZ/A1 and SDn\_CD in RZ/A2M. (n = 0, 1) \*2. It's a write protect pin. Pin names are SD\_WP\_n in RZ/A1 and SDn\_WP in RZ/A2M. (n = 0, 1)

Figure 5.24 Example of SD card slot connection 1 (RZ/A1)

Figure 5.25 Example of SD card slot connection 2 (RZ/A2M)

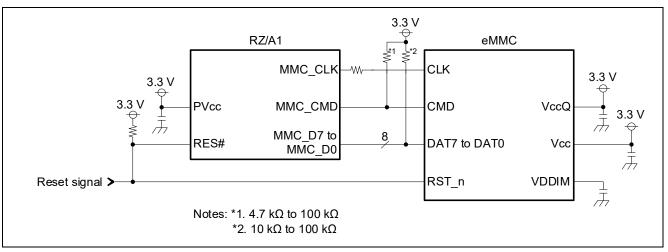

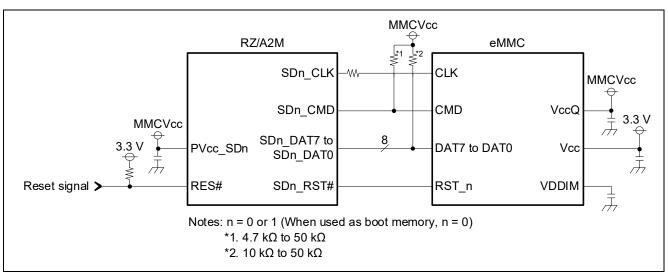

## 5.11 eMMC

RZ/A2M can connect to 1-, 4- and 8-bit width data buses on Channel 0, and 1- and 4-bit width data buses on Channel 1.

For RZ/A1, use pull-up resistors of 4.7 k $\Omega$  to 100 k $\Omega$  for the CMD pin and pull-up resistors of 10 k $\Omega$  to 100 k $\Omega$  on the DAT7 to DAT0 pins.

For RZ/A2M, use pull-up resistors of 4.7 k $\Omega$  to 50 k $\Omega$  for the CMD pin and pull-up resistors of 10k $\Omega$  to 50 k $\Omega$  for the DAT7 to DAT0 pins. Also, when operation starts, supply 3.3 V to MMCVcc, and switch between 1.8-V and 3.3-V in accordance with the operation mode.

When an eMMC is used as a boot memory, ensure that it must be reset at the same time as LSI of this series.

For RZ/A2M, connect the SDn\_RST# pin to the eMMC RST\_n pin.

Figure 5.26 and Figure 5.27 show examples of eMMC connection.

Figure 5.27 Example of eMMC connection 2 (RZ/A2M)

## 6. Debugger Interface

## 6.1 Characteristics

The debugger interface for LSI of this series is a serial I/O interface with the JTAG interface and the CoreSight debug interface<sup>\*1</sup>, with a TAP controllers for the boundary scan and CoreSight debug function.

The boundary scan controller is selected by setting the BSCANP pin to high level, and when it is set to low level, the CoreSight debug TAP controller is selected. Table 6.1 shows the JTAG pin mode table.

Note: \*1. For details on CoreSight, refer to Arm Ltd. Technical Reference Manual.

## Table 6.1 JTAG pin mode table

| BSCANP | JTAG Pin Mode                           |

|--------|-----------------------------------------|

| 0      | Normal operation (CoreSight debug mode) |

| 1      | Boundary scan mode                      |

## 6.2 Treatment of TRST# Pin

TRST# pin is for use as the debugger interface module initialization signal input pin. Set TRST# to low level for a specified time period when power is turned on, regardless whether or not the debugger interface module function is used.

When designing a board that can use an emulator, ensure that TRST# is set to low level at power on, and that the TRST# pin can be controlled independently. When the emulator is not used, either fix to low level, or connect to same signal as RES# pin.

## 6.3 Example of Emulator Connection

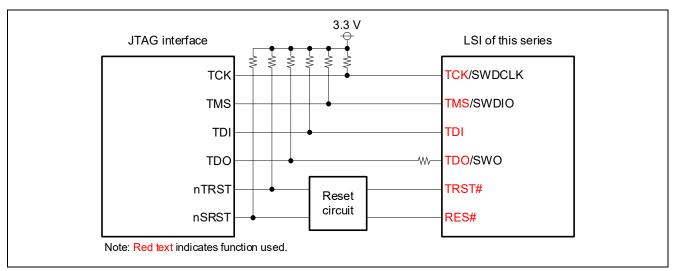

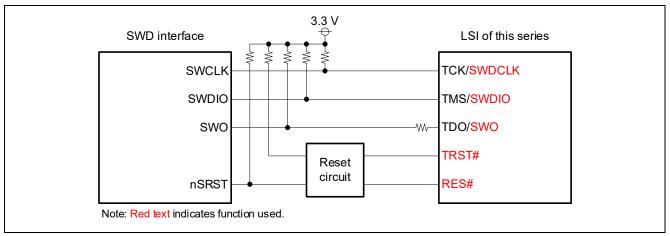

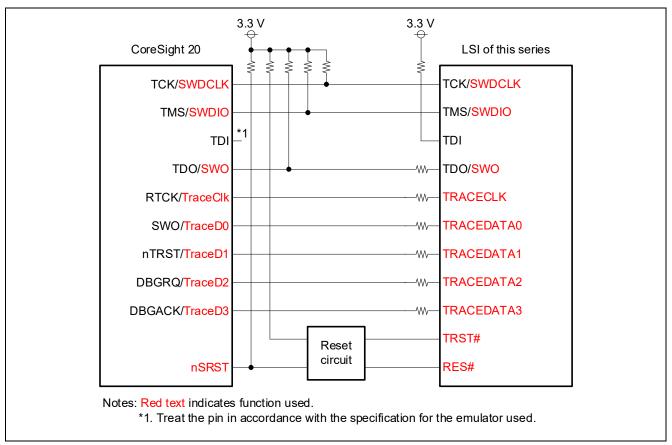

Figure 6.1 shows an example of reset circuit and Figure 6.2 to Figure 6.4 show the examples of emulator connection. When the interface pins that are not in the examples of VTREF and DBGACK connection are used, treat the pins in accordance with the emulator specifications. For LSI of this series, treat unconnected pins in accordance with "7.2 Treatment of Unused Pins".

The dotted line in Figure 6 shows the "reset circuit" part of the following figure.

Figure 6.1 Example of reset circuit

## 6.3.1 JTAG Interface

Figure 6.2 shows an example of JTAG interface connection.

Figure 6.2 Example of JTAG interface connection

## 6.3.2 SWD Interface

Figure 6.3 shows an example of SWD interface connection.

Figure 6.3 Example of SWD interface connection

## 6.3.3 TRACE Interface

Figure 6.4 shows an example of TRACE interface connection.

| TRACE interface    |          | LSI of this series       |

|--------------------|----------|--------------------------|

| TraceClk           | W        | TRACECLK                 |

| TraceCtl -         |          | TRACECTL                 |

| TraceD3 to TraceD0 | <b>4</b> | TRACEDATA3 to TRACEDATA0 |

## Figure 6.4 Example of TRACE interface connection

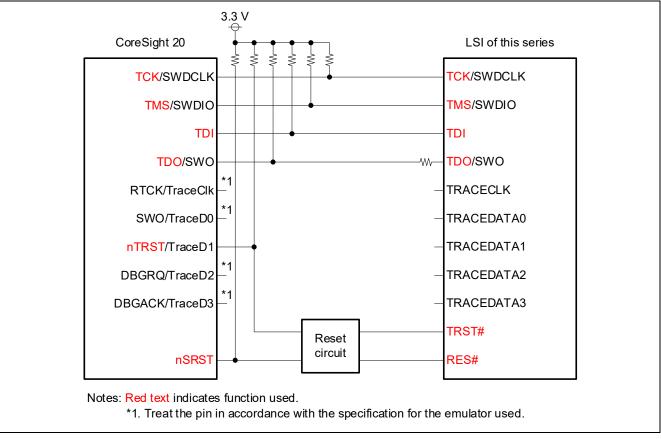

## 6.3.4 Connection to CoreSight 20 Connector

Because the CoreSight 20 connector is multiplexed to nTRST and TraceD1, when using the TRACE function, it is necessary to connect using the SWD interface. When connected to the JTAG interface, the TRACE function cannot be used.

Figure 6.5 shows an example of SWD and TRACE interface connection and Figure 6.6 shows an example of JTAG interface connection.

Figure 6.5 Example of CoreSight 20 connection 1 (SWD and TRACE interface connection)

Figure 6.6 Example of CoreSight 20 connection 2 (JTAG interface connection)

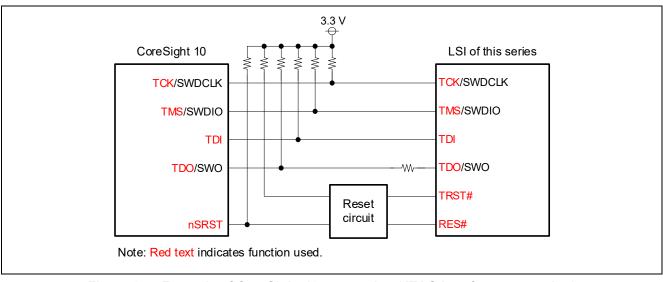

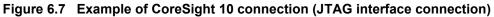

## 6.3.5 Connection to CoreSight 10 Connector

Even when the nTRST pin does not exist, as in the CoreSight 10 connector, when powering on, the TRST# pins on LSI of this series must be fixed to low level, and a signal separate from the RES# pin should be input.

Figure 6.7 shows an example of connection to CoreSight 10.

## 7. Treatment of Pins

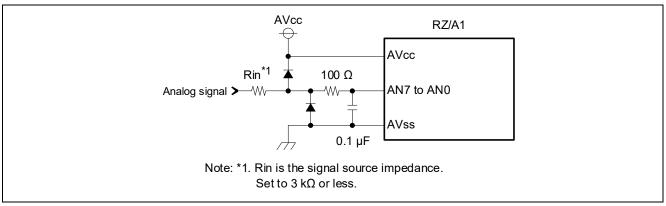

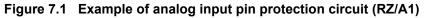

## 7.1 Analog Pin Protection Circuit

Design a protection circuit as shown in Figure 7.1 and Figure 7.2 to protect the analog input pin<sup>\*1</sup> from abnormal voltage (such as excessive surges). Furthermore, determine the circuit constants based on the actual use conditions.

Note:

\*1. RZ/A1

: AN7 to AN0

RZ/A2M

: AN007 to AN000

Figure 7.2 Example of analog input pin protection circuit (RZ/A2M)

## 7.2 Treatment of Unused Pins

Table 7.1 shows the treatment of unused pins for RZ/A1, and Table 7.2 shows the treatment of unused pins for RZ/A2M. Treat the unused pins as shown in each of the tables.

| Table 7.1 | Treatment of unused pins (RZ/A1) |

|-----------|----------------------------------|

|-----------|----------------------------------|

| Module               | Pin Name                                   | Handling                                                                                             |  |  |  |

|----------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|

| Interrupt Controller | NMI                                        | Fixed to high level (pull-up <sup>*1</sup> or connect to the power supply)                           |  |  |  |

| USB2.0               | DP1, DP0, DM1, DM0, VBUS1, VBUS0           | Connect to USBDPVss (QFP)                                                                            |  |  |  |

| Host/Function        |                                            | Connect to Vss (BGA package)                                                                         |  |  |  |

| Module               | REFRIN                                     | Connect to USBAPVcc via a 5.6 k $\Omega$ ± 20% resistor                                              |  |  |  |

|                      | USBAVcc, USBDVcc, USBUVcc                  | Supply power at 1.18 V.                                                                              |  |  |  |

|                      | USBAPVcc, USBDPVcc                         | Supply power at 3.3 V.                                                                               |  |  |  |

|                      | USBAPVss, USBDPVss, USBAVss, USBDVss,      | Connect to ground.                                                                                   |  |  |  |

|                      | USBUVss                                    | ő                                                                                                    |  |  |  |

|                      | USB X1                                     | Fix the level on the pin (pull-up <sup>*1</sup> or down <sup>*1</sup> , or connect to                |  |  |  |

|                      | _                                          | the power supply or ground level).                                                                   |  |  |  |

|                      | USB X2                                     | Open-circuit                                                                                         |  |  |  |

| A/D Converter        | AVref                                      | Connect to AVcc.                                                                                     |  |  |  |

|                      | AVcc                                       | Supply power at 3.3 V.                                                                               |  |  |  |