Renesas Synergy<sup>™</sup> Platform

## S7G2 MCUs High-Speed USB 2.0 Board Design Guidelines

R01AN3040EU0101 Rev.1.01 Nov 18, 2016

#### Introduction

This document describes the guidelines for High-Speed USB 2.0 board design.

#### **Verification Kits**

The application explained in this document can be verified on the following kits:

- PE-HMI1

- DK\_S7G2

This list is not all-inclusive and this document should be reviewed during any High-Speed USB 2.0 board design using the Renesas Synergy<sup>™</sup> S7G2 microcontroller.

**Note:** The contents in this document are provided as a reference example based on the USB specification; the signal system quality is not guaranteed. When implementing this example into an existing system, the overall system should be thoroughly evaluated, and the user should integrate at their own discretion.

#### Contents

| 1. | Introduction                                                 | .2  |

|----|--------------------------------------------------------------|-----|

|    | USB Transmission Line<br>1 Routing Guidelines (from USB.org) |     |

|    | Power Supply and Ground Pattern                              |     |

| 4. | VBUS Power Supply Circuit                                    | .8  |

| 5. | RREF Pin                                                     | . 9 |

| 6. | EMI/ESD Workarounds                                          | . 9 |

| 6. | 1 Signal Quality                                             | 10  |

### 1. Introduction

This document is described by using the pin names of S7G2. Table 1 lists the outline of the BGA 224 and BGA 176 module pins while Table 2 lists the outline of the LQFP 176 USB 2.0 module pins.

| Table 1 | S7G2 BGA 224 (BGA 176) USB 2.0 High-Speed Pins |

|---------|------------------------------------------------|

|---------|------------------------------------------------|

| Pin number               | Pin Name                         | I/O | Name                                    | Function                                                                                                                                       |

|--------------------------|----------------------------------|-----|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| F14 (F14)*               | USBHS_DP                         | I/O | USB D+ data                             | Connect to D+ pin of USB bus.                                                                                                                  |

| F15 (F15)*               | USBHS_DM                         | I/O | USB D- data                             | Connect to D- pin of USB bus.                                                                                                                  |

| K13 (K13)*               | USBHS_VBUS                       | Ι   | VBUS input                              | USB cable connection monitor input pin.                                                                                                        |

| G13 (G13)*               | USBHS_RREF                       | Ι   | Reference input                         | USBHS reference current source<br>pin. This pin should be connected<br>to the<br>AVSS_USBHS pin through a<br>resistor of 2.2 k $\Omega$ (±1%). |

| H13 (H13)*               | AVCC_USBHS                       | I   | Transceiver analog pin<br>power supply  | 3.3V analog power supply for<br>pins.                                                                                                          |

| G14 (G14)*               | AVSS_USBHS                       | I   | Transceiver analog pin<br>ground        | Analog ground pin for the USBHS.<br>Must be shorted to the<br>PVSS_USBHS pin.                                                                  |

| F13 (F13)*               | VCC_USBHS                        | I   | Transceiver digital pin<br>power supply | 3.3V digital power supply for pins.                                                                                                            |

| F12 (F12)*<br>F13 (F13)* | VSS1_USBHS<br>VSS2_USBHS         | I   | Transceiver digital pin<br>ground       | 3.3V digital ground for pins.                                                                                                                  |

| G15 (G15)*               | PVSS_USBHS                       | Ι   | Power supply for I/O circuit            | PLL circuit ground pin for the<br>USBHS. Must be shorted to the<br>AVSS_USBHS pin.                                                             |

| C14 (B15)*               | USBHS_EXCEN                      | 0   | Low-power control signal for OTG        | This pin should be connected to the OTG power supply IC.                                                                                       |

| B15 (D13)*               | USBHS_ID                         | I   | MicroAB ID signal                       | This pin should be connected to the OTG power supply IC.                                                                                       |

| L15 (L15)*<br>L14 (L14)* | USBHS_OVRCURA<br>USBHS_OVRCURB   | I   | Overcurrent detection                   | Overcurrent pin for USB.                                                                                                                       |

| H9(J12)*                 | USBHS_VBUSEN-A<br>USBHS_VBUSEN-B | 0   | VBUS Enable                             | VBUS power enable pin for USB.                                                                                                                 |

\*Note: The () in the pin number denotes the pin number for the 176 pin package.

| Pin      | Pin Name                         | I/O | Name                                    | Function                                                                                                                                    |

|----------|----------------------------------|-----|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| number   |                                  |     |                                         |                                                                                                                                             |

| 32       | USBHS_DP                         | I/O | USB D+ data                             | USB bus D+ data pin.                                                                                                                        |

| 31       | USBHS_DM                         | I/O | USB D- data                             | USB bus D- data pin.                                                                                                                        |

| 17       | USBHS_VBUS                       | 1   | VBUS input                              | USB cable connection monitor input pin.                                                                                                     |

| 27       | USBHS_RREF                       | 1   | Reference input                         | USBHS reference current source pin.<br>This pin should be connected to the<br>AVSS_USBHS pin through a resistor of<br>2.2 k $\Omega$ (±1%). |

| 26       | AVCC_USBHS                       | I   | Transceiver analog<br>pin power supply  | 3.3V analog power supply for pins.                                                                                                          |

| 28       | AVSS_USBHS                       | I   |                                         | Analog ground pin for the USBHS. Must<br>be shorted to the PVSS_USBHS pin.                                                                  |

| 34       | VCC_USBHS                        | I   | Transceiver digital pin<br>power supply | 3.3V digital power supply for pins.                                                                                                         |

| 33<br>30 | VSS1_USBHS<br>VSS2_USBHS         | I   | Transceiver digital pin<br>ground       | 3.3V digital ground for pins.                                                                                                               |

| 29       | PVSS_USBHS                       | I   |                                         | PLL circuit ground pin for the USBHS.<br>Must be shorted to the AVSS_USBHS<br>pin.                                                          |

| 42       | USBHS_EXCEN                      | 0   | Low-power control signal for OTG        | This pin should be connected to the OTG power supply IC.                                                                                    |

| 43       | USBHS_ID                         | I   | MicroAB ID signal                       | This pin should be connected to the OTG power supply IC.                                                                                    |

| 15       | USBHS_OVRCURA                    | I   | Overcurrent detection                   | Overcurrent pin for USB.                                                                                                                    |

| 14       | USBHS_OVRCURB                    |     |                                         |                                                                                                                                             |

| 16       | USBHS_VBUSEN-A<br>USBHS_VBUSEN-B | 0   | VBUS Enable                             | VBUS power enable pin for USB.                                                                                                              |

#### Table 2 S7G2 LQFP 176 USB 2.0 High-Speed Pins

#### 2. USB Transmission Line

The USB transmission line refers to the printed circuit board wiring pattern that connects the USB connector to the S7G2 microcontroller (MCU). USB 2.0 has three communication modes: High-Speed, Full-Speed and Low-Speed. High-Speed mode can transmit and receive at up to 480 Mbps. Therefore, for USB High-Speed, the board traces between the S7G2 MCU and the USB connector must be designed as a high-frequency circuit transmission line. Impedance control is required for the USB transmission lines. Notes on designing the wiring pattern of the USB transmission lines are described below:

- The differential characteristic impedance required for the USB transmission lines is the differential impedance 90  $\Omega$ +/-15%.

- The common-mode characteristic impedance should be 21  $\Omega$  to 39  $\Omega$  (the impedance from any one USB signal trace to ground should be 42  $\Omega$  to 78  $\Omega$ ).

- The circuit board USB transmission lines on Host and Device sides of the USB connection must not add more than 4 ns to the total delay between the Host Controller and the Device Controller. Table 3 shows how this breaks down to the acceptable USB transmission line delays on the Host and the Device side.

Table 3

Recommended Value for the Wiring Pattern Length of USB Transmission Line

|                          | Maximum Delay Time<br>(USB Specification) | Wiring Length  | D+ and D- Wiring Length<br>Differential |

|--------------------------|-------------------------------------------|----------------|-----------------------------------------|

| Host Controller          | 3 ns                                      | 300 mm or less | 2.5 mm or less                          |

| Peripheral<br>Controller | 1 ns                                      | 100 mm or less | 2.5 mm or less                          |

- The pattern width and pattern pitch for impedance control vary depending on board thickness, material, and layer configuration. Contact the board manufacturer for more details.

- The wiring pattern length of the USB transmission lines from the S7G2 to the USB connector must be designed not to exceed the maximum delay time which is regulated by the USB specification. Table 2 lists the recommended values for the wiring pattern length of USB transmission lines for Host and Device.

- The lower layer of the USB transmission lines must be a ground plane. The ground plane must be at least 2 mm wider than the USB transmission lines. The power supply ground should be the same as the ground plane GND.

- Do not allocate other signal lines near the USB transmission lines. Particularly lines of heavily fluctuating signals, such as clock and data bus lines, must be allocated far from the USB transmission lines. Moreover, the USB transmission lines and other lines must not cross.

- The same layer (surface layer) as the USB transmission lines should be allocated 1 mm from the USB transmission lines, and grounded with a guard ring.

- USB transmission lines should be allocated on the same layer without passing through a hole. In addition, wiring should not be stretch or diverge widely.

- The USB transmission lines should be wired with uniform spaces.

- The USB transmission lines should be allocated far from the oscillator, power supply circuit, and other I/O connectors.

- The USB transmission lines should be wired with straight lines. If they are bent, they should be bent gently in an arc or up to 135 degrees, and not bent at acute angles (right angles).

- It is recommended that the clock, reset, read, write and chip select signals should be grounded with a guard ring.

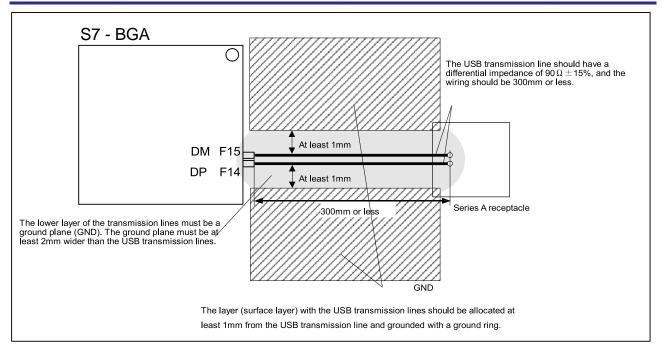

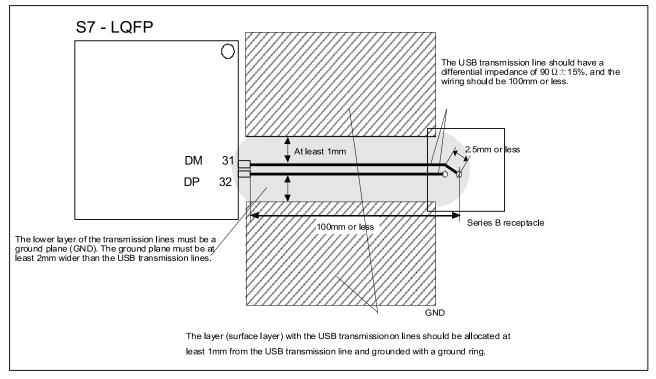

Figure 1 shows a design example of a Host controller USB transmission line pattern. Figure 2 shows a design example of a Device controller USB transmission line pattern.

Figure 1 Design Example of a Host Controller USB Transmission Line Pattern

Figure 2 Design Example of a Device Controller USB Transmission Line Pattern

## 2.1 Routing Guidelines (from USB.org)

The High-Speed USB validation efforts focused on a four-layer motherboard where the first layer is a signal layer, the second layer is power, the third layer is ground and the fourth is a signal layer. This results in placing most of the routing on the fourth layer closest to the ground layer, and allowing a higher component density on the first layer.

- Place the high-speed USB host controller and major components on the unrouted board first.

- With minimum trace lengths, route high-speed clock and high-speed USB differential pairs first. Maintain maximum possible distance between high-speed clocks/periodic signals to high speed USB differential pairs and any connector leaving the PCB (such as, I/O connectors, control and signal headers, or power connectors).

- Route high-speed USB signals on bottom whenever possible.

- Route high-speed USB signals using a minimum of vias and corners. This reduces signal reflections and impedance changes.

- When it becomes necessary to turn 90°, use two 45° turns or an arc instead of making a single 90° turn. This reduces reflections on the signal by minimizing impedance discontinuities.

- Do not route USB traces under crystals, oscillators, clock synthesizers, magnetic devices or ICs that use and/or duplicate clocks.

- Stubs on high speed USB signals should be avoided, as stubs will cause signal reflections and affect signal quality. If a stub is unavoidable in the design, no stub should be greater than 200 mils.

- Route all traces over continuous planes (VCC or GND), with no interruptions. Avoid crossing over anti-etch if at all possible. Crossing over anti-etch (plane splits) increases inductance and radiation levels by forcing a greater loop area. Likewise, avoid changing layers with high-speed traces as much as practical. It is preferable to change layers to avoid crossing a plane split. Refer to Section 3.6 Plane Splits, Voids and Cut-Outs (Anti-Etch) for more details on plane splits.

- Separate signal traces into similar categories and route similar signal traces together (such as routing differential pairs together).

- Keep high-speed USB signals clear of the core logic set. High current transients are produced during internal state transitions and can be very difficult to filter out.

- Follow the 20\*h rule of thumb by keeping traces at least 20\*(height above the plane) away from the edge of the plane (VCC or GND, depending on the plane the trace is over). For the suggested stack-up the height above the plane is 4.5 mils. This calculates to a 90-mil spacing requirement from the edge of the plane. This helps prevent the coupling of the signal onto adjacent wires and also helps prevent free radiation of the signal from the edge of the PCB.

Use the following separation guidelines. Figure 3 provides an illustration of the recommended trace spacing.

- Maintain parallelism between USB differential signals with the trace spacing needed to achieve 90 ohms differential impedance. Deviations will normally occur due to package breakout and routing to connector pins. Just ensure the amount and length of the deviations are kept to the minimum possible.

- Use an impedance calculator to determine the trace width and spacing required for the specific board stack-up being used. 7.5- mil traces with 7.5-mil spacing results in approximately 90 ohms differential trace impedance.

- Minimize the length of high-speed clock and periodic signal traces that run parallel to high speed USB signal lines, to minimize crosstalk. Based on EMI testing experience, the minimum suggested spacing to clock signals is 50 mils.

- Based on simulation data, use 20-mil minimum spacing between high-speed USB signal pairs and other signal traces for optimal signal quality. This helps to prevent crosstalk.

Figure 3 Recommended Trace Spacing

#### 3. Power Supply and Ground Pattern

Notes on designing a power supply/ground pattern are described below:

• Power supplies and ground patterns should be separated into digital and analog. Table 3 and Table 4 list the power supply and ground classifications.

#### Table 4 USB Power Supply Classifications

|               | Power Supply Cla               | Power Supply Classifications    |                                 |                              |  |  |

|---------------|--------------------------------|---------------------------------|---------------------------------|------------------------------|--|--|

| S7G2 Pin Name | Analog Power<br>Supply (3.3 V) | Digital Power<br>Supply (3.3 V) | Digital Power<br>Supply (1.8 V) | Digital Core<br>Power Supply |  |  |

| AVCC_USBHS    | 0                              |                                 |                                 |                              |  |  |

| VCC_USBHS     |                                | 0                               |                                 |                              |  |  |

0: Indicates power used.

#### Table 5 USB Ground Classifications

| S7G2 Pin Name/ USB   | Ground Classifications |                      |  |  |  |

|----------------------|------------------------|----------------------|--|--|--|

| Connector            | Analog Ground (AGND)   | Digital Ground (GND) |  |  |  |

| AVSS1_USBHS          | 0                      |                      |  |  |  |

| VSS1_USBHS           |                        | 0                    |  |  |  |

| PVSS_USBHS           |                        | 0                    |  |  |  |

| USB Connector Ground |                        | 0                    |  |  |  |

| (Including Frame     |                        |                      |  |  |  |

0: Indicates the power used.

- The patterns of power supplies and grounds should be designed with as wide a surface layer as possible.

- Tantalum capacitors or ceramic capacitors having excellent high-frequency characteristics are recommended as power supply capacitors.

- Aluminum electrolytic capacitors affect the jitter value when measuring the EYE pattern. The capacitors should be thoroughly designed and tested before use.

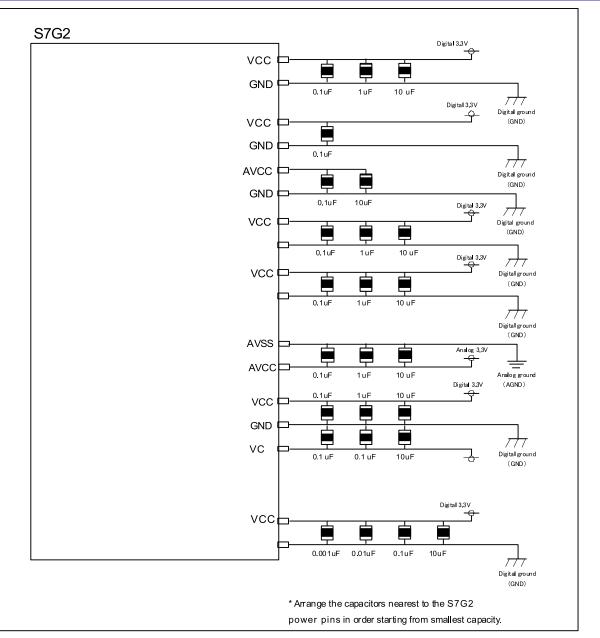

- It is recommended to place the capacitors for the S7G2 USB Power pins as close to possible to the S7G2, with the smallest capacity closest. Figure 4 shows an example of decoupling capacitor placement.

- Please connect digital ground and analog ground by one point near S7G2 MCU.

Figure 4 Example of Decoupling Capacitor Allocation

## 4. VBUS Power Supply Circuit

Notes on designing the VBUS power supply circuit are described below:

- When the S7G2 is used as a Host controller, the additional capacitance of the VBUS line should be designed to be 120 uF or more.

- When the S7G2 is used as a Device controller, the additional capacity of the VBUS line should be designed to be within 1.0 uF to 10 uF.

- The VBUS line should include a filter circuit as an overshoot may be caused by inconsistent impedance when the USB cable is connected. The 1.0-uF to 10-uF capacitor and 100- $\Omega$  to 1-k $\Omega$  resistor should be added as a filter circuit. The constant should be defined after confirming that an overshoot has not occurred on the board. Also, a resistor of more than 1 k $\Omega$  should not be added.

- When the S7G2 is used as a Host controller, the VBUS power should be supplied to the Device devices. A power supply switch IC with over-current protection for the USB power bus (hereinafter called "USB power supply switch IC") is recommended for the VBUS power supply control. Make sure to consider the maximum current of the VBUS power supply line. This current is based on the current amount used by the system and the USB Device

devices connected. In addition, refer to the USB power supply switch IC datasheet used for VBUS power supply control circuit.

#### 5. RREF Pin

Notes on designing the circuit around the REFRIN pin are described below:

- A resistor of 2.2 k $\Omega$ +/-1% (hereinafter called "standard resistor") should be allocated between the RREF pin and AGND.

- A standard resistor should be allocated as close as possible to the S7G2.

- The RREF pin, the standard resistor, and AGND should be connected with a bold, minimal pattern.

- The standard resistor and AGND should be connected in an exclusive pattern, and then connected to the analog ground. The pattern should be designed to avoid common impedance with other signals.

- To prevent cross talk, heavily fluctuating signals such as D+, D-, clocks, address data, and control signals should neither cross nor go side by side with standard resistor and patterns. It is recommended that standard resistor and patterns be grounded with a guard ring.

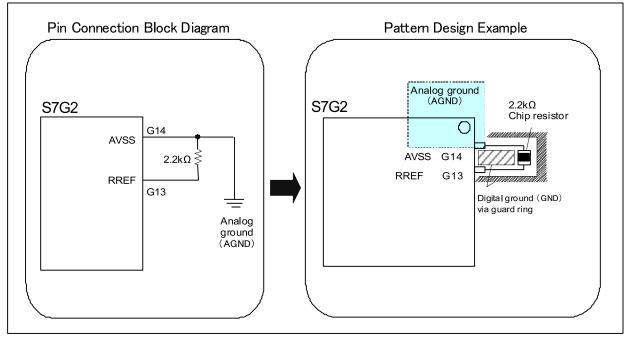

Figure 5 shows the block diagram of the pin connection and the design example of pattern around the REFRIN pin.

#### Figure 5 Pin Connection and Design Example of Pattern around the RREF Pin on BGA 224 Pin Module

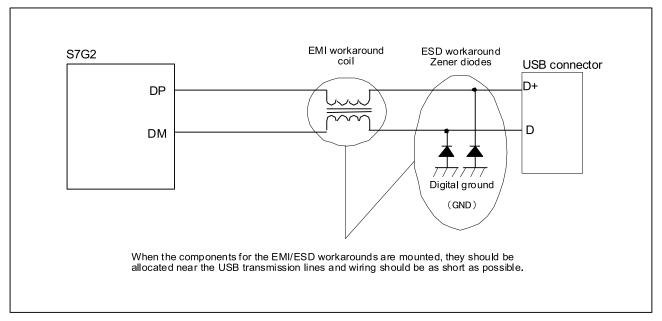

#### 6. EMI/ESD Workarounds

Notes on EMI/ESD workarounds are described below:

- When components for EMI/ESD workarounds such as coils and diodes are mounted on the USB transmission lines, they should be allocated near the USB transmission lines and the wiring should be as short as possible.

- The components for the EMI/ESD workarounds must be USB 2.0 compliant. Also, by mounting EMI/ESD workaround components, inconsistent impedance may occur on the USB transmission lines, and the waveform may become distorted. Components for use should be selected after thorough evaluation.

Figure 6 shows the block diagram of a connection example when the components for EMI/ESD workarounds are used.

#### Renesas Synergy<sup>™</sup> Platform S7G2 MCUs High-Speed USB 2.0 Board Design Guidelines

Figure 6 Connection Example When Components for EMI/ESD Workarounds are used

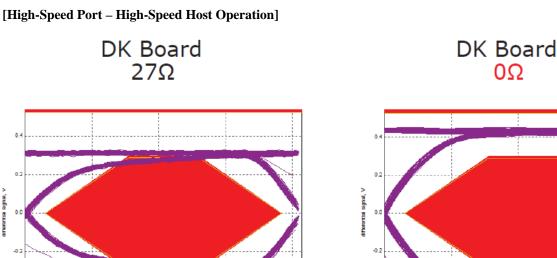

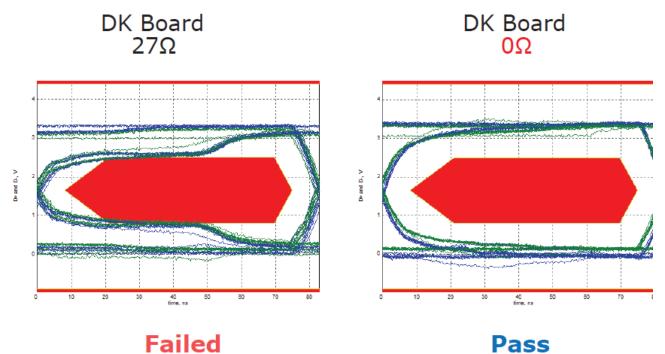

## 6.1 Signal Quality

Below is shown an example of good USB High-Speed signal quality using a 0- $\Omega$  resistor on the DK-S7G2 development boards (resistors R9 & R10). The eye patterns below are representative of what a high quality signal will look like on the DK boards.

2.0

0.5

1.0 time, na

Failed

0.0

1.0 time. na

Pass

[High-Speed Port – Full-Speed Host Operation]

#### Website and Support

Support: https://synergygallery.renesas.com/support

Technical Contact Details:

- America: <u>https://renesas.zendesk.com/anonymous\_requests/new</u>

- Europe: <u>https://www.renesas.com/en-eu/support/contact.html</u>

- Japan: <u>https://www.renesas.com/ja-jp/support/contact.html</u>

All trademarks and registered trademarks are the property of their respective owners.

## **Revision History**

|      |              | Descript | tion                 |

|------|--------------|----------|----------------------|

| Rev. | Date         | Page     | Summary              |

| 1.00 | Oct 7, 2015  | -        | Initial version      |

| 1.01 | Nov 18, 2016 | -        | Minor format changes |

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for

the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use

of these circuits, software, or information.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries. (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 1) Release Electronics as used in this document means reflexas Electronics corporation and also includes its majority-owner

(Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

Refer to "http://www.renesas.com/" for the latest and detailed information

# RENESAS

#### SALES OFFICES

**Renesas Electronics Corporation**

http://www.renesas.com

Renesas Electronics America Inc. 2801 Scott Boulevard Santa Clara, CA 95050-2549, U.S.A Tel: +1-408-588-6000, Fax: +1-408-588-6130 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-585-100, Fax: +44-1628-585-900 Renesas Electronics Europe GmbH Germany Arcadiastrasse 10, 40472 Düsseldorf, German Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100191, P.R.China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, P. R. China 200333 Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Ini Tel: +65-6213-0200, Fax: +65-6213-0300 Innovation Centre, Singapore 339949 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HALII Stage, Indiranagar, Bangalore, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics, Korea Co., Ltd. 12F., 234 Teheran-ro, Gangnam-Gu, Seoul, 135-080, Korea Tel: +82-2-558-3737, Fax: +82-2-558-5141