# **Data Sheet**

# RAA462113FYL#AC2

# CMOS Image Sensor (PDAF)

R18DS0033EJ0100 Rev. 1.00 Feb 15, 2021

#### 1. Outline

# 1.1 Description

The RAA462113FYL is BSI CMOS Image Sensor that achieved High-sensitivity, Low-noise and Low-power with 8M pixels for UHD (Ultra High Definition). The sensor features HDR (High Dynamic Range), PDAF (Phase Detection Auto Focus) functions and selectable output formats, MIPI-CSI2 or SLVS, which support 60fps (12bit digital output).

### 1.2 Features

**Table 1 Features**

| Category               | Item                                       | Description                         |  |  |  |  |

|------------------------|--------------------------------------------|-------------------------------------|--|--|--|--|

|                        | CLGA                                       | 144pin (pitch=1.0mm)                |  |  |  |  |

| PKG (Package)          | CLGA                                       | 15.0mm x 13.3mm                     |  |  |  |  |

|                        | Optical format                             | 1/1.9 inch                          |  |  |  |  |

|                        | Effective area                             | 3872(H) x 2192(V)                   |  |  |  |  |

| Sensor                 | HOB (Horizontal Optical Black)             | 32 pixels                           |  |  |  |  |

| Serisor                | VOB (Vertical Optical Black)               | 32 pixels                           |  |  |  |  |

|                        | Unit cell size                             | 1.85um x 1.85um                     |  |  |  |  |

|                        | Primary color filter array                 | Bayer pattern                       |  |  |  |  |

| Dower Supply           | Power supply voltage                       | 1.2V, 1.8V, 2.8V                    |  |  |  |  |

| Power Supply           | Power consumption                          | 0.9W @ 60fps (typ.)                 |  |  |  |  |

|                        | UHD (Ultra High Definition)                | Single exposure                     |  |  |  |  |

| Read Mode              | Of ID (Oltra Flight Definition)            | Max. 60fps (Active area:3840x2160)  |  |  |  |  |

| Nead Mode              | UHD-HDR (High Dynamic Range)               | Double exposure (Line by Line)      |  |  |  |  |

|                        | OTID-TIDIX (Flight Dynamic Trange)         | Max. 30fps (Active area:3840x2160)) |  |  |  |  |

| Output Mode            | MIPI-CSI2 (Camera Serial Interface)        | RAW12, RAW10                        |  |  |  |  |

| ·                      | SLVS (Scalable Low Voltage Signaling)      | 12bit, LSB-first                    |  |  |  |  |

| Output I/E (Interfece) | Output lane                                | 8lane+1clock, 4lane+1clock          |  |  |  |  |

| Output I/F (Interface) | Data rate                                  | 891Mbps, 445.5Mbps / lane           |  |  |  |  |

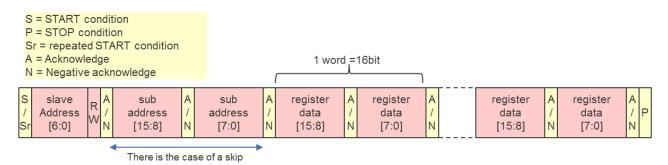

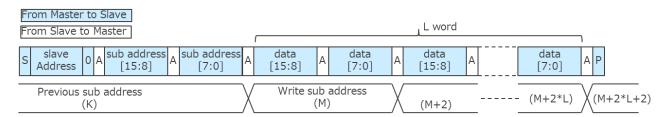

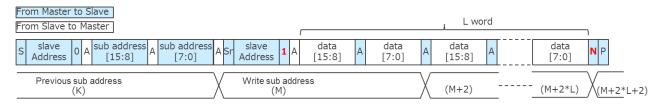

| Serial Communication   | I2C (Inter-Integrated Circuit)             | Fast mode, Fast mode plus           |  |  |  |  |

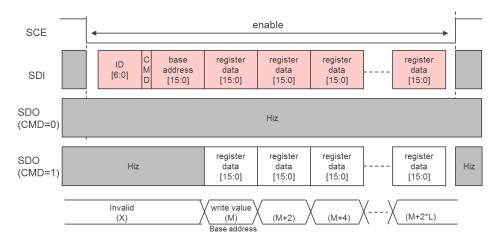

| Serial Communication   | 4-wire (SCE, SCK, SDI, SDO)                | 2address=1word=16bit, MSB-first     |  |  |  |  |

| A/D Converter, Gain    | Resolution of A/D converter                | 12bit                               |  |  |  |  |

| A/D Conventer, Gain    | Gain amplifier                             | Analog: 0~30dB, Digital: 0~24dB     |  |  |  |  |

|                        | Input: TRIG                                | Start trigger for Multi-sensor      |  |  |  |  |

| Timing Assist          | Output: SACK                               | Register write enable during movie  |  |  |  |  |

|                        | Output: SYNC                               | Start of frame                      |  |  |  |  |

| PDAF Assist            | Phase Detection Auto Focus assist function | L-open pixel                        |  |  |  |  |

| ו טאו אפאופנ           | Thase Detection Auto Focus assist function | R-open pixel                        |  |  |  |  |

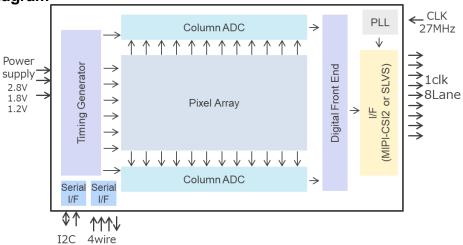

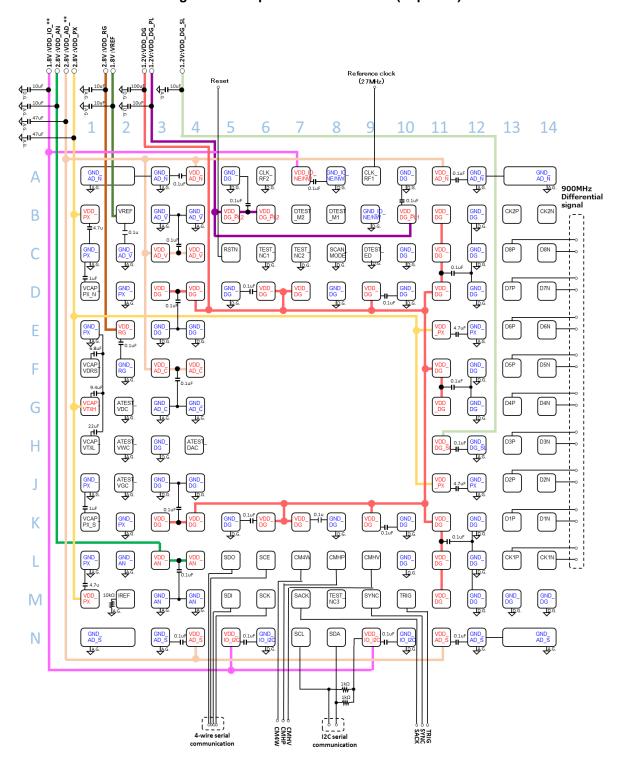

## 1.3 Block Diagram

Figure 1 Block diagram

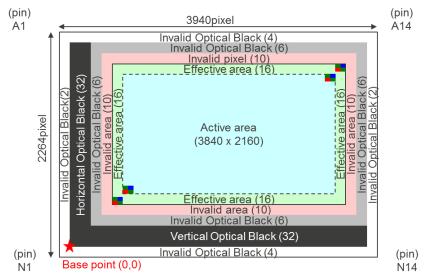

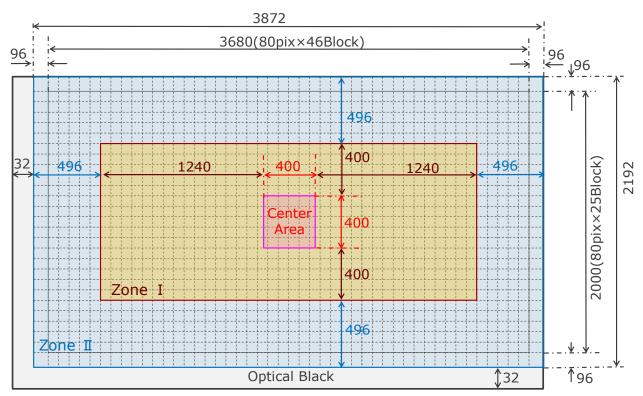

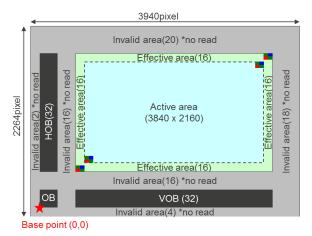

# 1.4 Pixel Array Structure

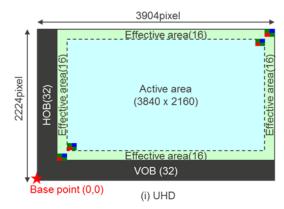

Figure 2 Pixel array structure (Top view)

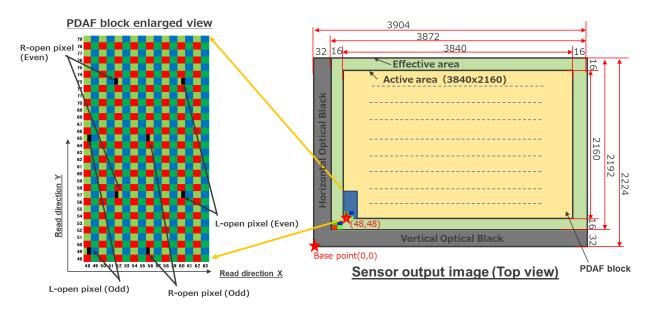

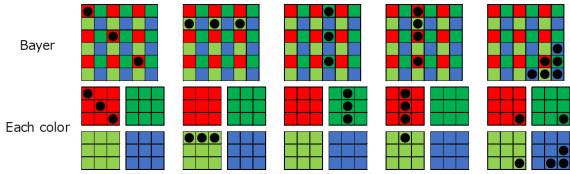

## 1.5 PDAF pixel coordinates

## L-open / R-open pixel coordinates (Unit: pixels)

Sensor don't output Invalid data; refer to section 4.1 Read Mode.

PDAF pixel coordinates in sensor output image is shown in next expression; refer to Figure 3.

#### L-open pixel (Odd)

$$X = 16m + 48 (m = 0, 1, 2, 3, \dots, 239)$$

$$Y = 16n + 49 (n = 0, 1, 2, 3, \dots, 134)$$

#### L-open pixel (Even)

$$X = 16m + 60 (m = 0, 1, 2, 3, \dots, 239)$$

$$Y = 16n + 57 (n = 0, 1, 2, 3, \dots, 134)$$

#### R-open pixel (Odd)

$$X = 16m + 56 (m = 0, 1, 2, 3, \dots, 239)$$

$$Y = 16n + 49 (n = 0, 1, 2, 3, \dots, 134)$$

#### R-open pixel (Even)

$$X = 16m + 52 (m = 0, 1, 2, 3, \dots, 239)$$

$$Y = 16n + 57 (n = 0, 1, 2, 3, \dots, 134)$$

Figure 3 PDAF pixel coordinates

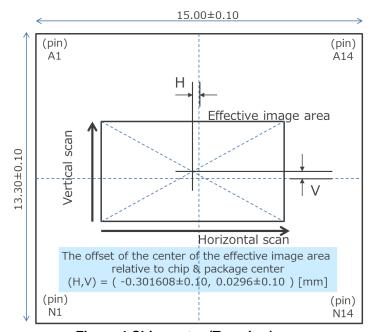

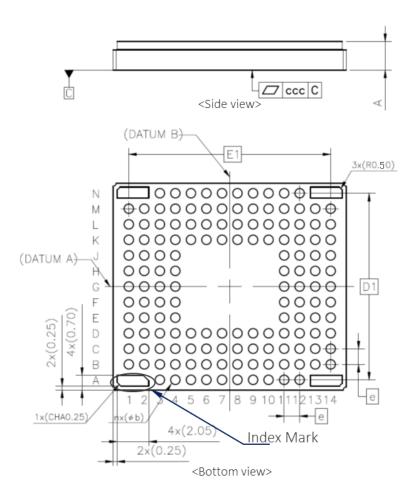

# 1.6 PKG Structure

Figure 4 Chip center (Top view)

| Reference | Dimen | sion in Millir | meters |

|-----------|-------|----------------|--------|

| Symbol    | Min.  | Nom.           | Max.   |

| D         | 13.20 | 13.30          | 13.40  |

| D2        | 12.70 | 12.80          | 12.90  |

| E         | 14.90 | 15.00          | 15.10  |

| E2        | 14.40 | 14.50          | 14.60  |

| D1        | -     | 12.00          | -      |

| E1        | -     | 13.00          | -      |

| А         | -     | -              | 2.03   |

| b         | -     | 0.60           | -      |

| е         | -     | 1.00           | -      |

| ccc       | -     | -              | 0.05   |

| n         | -     | 144            | -      |

Figure 5 PKG structure

# 2 Pin Description

# 2.1 Pin Description

Table 2 Pin description (Power / Analog / Ground)

| No. | Pin Name   | I/O | Description                       | Note |

|-----|------------|-----|-----------------------------------|------|

| 1   | VDD_PX     | PWR | Analog power supply (2.8V)        |      |

| 2   | VDD_RG     | PWR | Analog power supply (2.8V)        |      |

| 3   | VDD_AN     | PWR | Analog power supply (2.8V)        |      |

| 4   | VDD_AD_N   | PWR | Analog power supply (2.8V)        |      |

| 5   | VDD_AD_S   | PWR | Analog power supply (2.8V)        |      |

| 6   | VDD_AD_V   | PWR | Analog power supply (2.8V)        |      |

| 7   | VDD_AD_C   | PWR | Analog power supply (2.8V)        |      |

| 8   | VDD_IO_N   | PWR | Digital power supply (1.8V)       |      |

| 9   | VDD_IO_I2C | PWR | Digital power supply (1.8V)       |      |

| 10  | VDD_DG     | PWR | Digital power supply (1.2V)       |      |

| 11  | VDD_DG_SL  | PWR | Analog power supply (1.2V)        |      |

| 12  | VDD_DG_PL1 | PWR | Analog power supply (1.2V)        |      |

| 13  | VDD_DG_PL2 | PWR | Analog power supply (1.2V)        |      |

| 14  | VCAP_VTXH  | PWR | Analog power supply (2.8V)        |      |

| 15  | VCAP_VDRS  | AIO | Capacitor connection (6.8uF)      |      |

| 16  | VCAP_VTXL  | AIO | Capacitor connection (22uF)       |      |

| 17  | VCAP_PX_N  | AIO | Capacitor connection (1.0uF)      |      |

| 18  | VCAP_PX_S  | AIO | Capacitor connection (1.0uF)      |      |

| 19  | IREF       | AIO | Resister connection (10kΩ)        |      |

| 20  | VREF       | Al  | Reference voltage (1.8V)          |      |

| 21  | GND_PX     | GND | Analog ground                     |      |

| 22  | GND_RG     | GND | Analog ground                     |      |

| 23  | GND_AN     | GND | Analog ground                     |      |

| 24  | GND_AD_N   | GND | Analog ground                     |      |

| 25  | GND_AD_S   | GND | Analog ground                     |      |

| 26  | GND_AD_V   | GND | Analog ground                     |      |

| 27  | GND_AD_C   | GND | Analog ground                     |      |

| 28  | GND_IO_N   | GND | Digital ground                    |      |

| 29  | GND_IO_I2C | GND | Digital ground                    |      |

| 30  | GND_DG     | GND | Digital ground                    |      |

| 31  | GND_DG_SL  | GND | Analog ground (Dedicated to SLVS) |      |

# Table 3 Pin description (Interface)

| No. | Pin Name | I/O | Description                                                          | Note |

|-----|----------|-----|----------------------------------------------------------------------|------|

| 34  | D1P      | DO  | MIPI-CSI2 / SLVS output (Data lane-1 positive polarity)              |      |

| 35  | D1N      | DO  | MIPI-CSI2 / SLVS output (Data lane-1 negative polarity)              |      |

| 36  | D2P      | DO  | MIPI-CSI2 / SLVS output (Data lane-2 positive polarity)              |      |

| 37  | D2N      | DO  | MIPI-CSI2 / SLVS output (Data lane-2 negative polarity)              |      |

| 38  | D3P      | DO  | MIPI-CSI2 / SLVS output (Data lane-3 positive polarity)              |      |

| 39  | D3N      | DO  | MIPI-CSI2 / SLVS output (Data lane-3 negative polarity)              |      |

| 40  | D4P      | DO  | MIPI-CSI2 / SLVS output (Data lane-4 positive polarity)              |      |

| 41  | D4N      | DO  | MIPI-CSI2 / SLVS output (Data lane-4 negative polarity)              |      |

| 42  | D5P      | DO  | MIPI-CSI2 / SLVS output (Data lane-5 positive polarity)              |      |

| 43  | D5N      | DO  | MIPI-CSI2 / SLVS output (Data lane-5 negative polarity)              |      |

| 44  | D6P      | DO  | MIPI-CSI2 / SLVS output (Data lane-6 positive polarity)              |      |

| 45  | D6N      | DO  | MIPI-CSI2 / SLVS output (Data lane-6 negative polarity)              |      |

| 46  | D7P      | DO  | MIPI-CSI2 / SLVS output (Data lane-7 positive polarity)              |      |

| 47  | D7N      | DO  | MIPI-CSI2 / SLVS output (Data lane-7 negative polarity)              |      |

| 48  | D8P      | DO  | MIPI-CSI2 / SLVS output (Data lane-8 positive polarity)              |      |

| 49  | D8N      | DO  | MIPI-CSI2 / SLVS output (Data lane-8 negative polarity)              |      |

| 50  | CK1P     | DO  | MIPI-CSI2 / SLVS output (Clock lane positive polarity)               |      |

| 51  | CK1N     | DO  | MIPI-CSI2 / SLVS output (Clock lane negative polarity)               |      |

| 52  | CLK_RF1  | DI  | Reference clock signal input (27MHz)                                 |      |

| 53  | RSTN     | DI  | System reset (Low: reset, High: release)                             |      |

| 54  | SDA      | DIO | Data input / output for I2C serial communication                     |      |

| 55  | SCL      | DI  | Clock input for I2C serial communication                             |      |

| 56  | SCE      | DI  | Data input for 4-wire serial communication                           |      |

| 57  | SCK      | DI  | Clock input for 4-wire serial communication                          |      |

| 58  | SDI      | DI  | Data input for 4-wire serial communication                           |      |

| 59  | SDO      | DO  | Data output for 4-wire serial communication                          |      |

| 60  | TRIG     | DI  | Data input for Synchronization                                       |      |

| 61  | SYNC     | DO  | Timing pulse of Start of Frame                                       |      |

| 62  | SACK     | DO  | Timing pulse of serial communication write enable                    |      |

| 63  | CM4W     | DI  | Mode select (Low: I2C, High: 4-wire)                                 |      |

| 64  | CMHP     | DI  | I2C mode select (Low: fast-mode, High: fast-mode plus)               |      |

| 65  | CMHV     | DI  | I2C driver select for large load capacitor or Pull-up voltage > 2.5V |      |

# **Table 4 Pin description (Test)**

| No. | Pin Name  | I/O | Description                                                         | Note |

|-----|-----------|-----|---------------------------------------------------------------------|------|

| 66  | CK2P      | DO  | Test pin (No connection)                                            |      |

| 67  | CK2N      | DO  | Test pin (No connection)                                            |      |

| 68  | CLK_RF2   | DI  | Test pin (It must be connected to Digital ground by users.)         |      |

| 69  | ATEST_VDC | Al  | Test pin (It must be connected to Analog ground by users.)          |      |

| 70  | ATEST_VWC | Al  | Test pin (It must be connected to Analog ground by users.)          |      |

| 71  | ATEST_VGC | Al  | Test pin (It must be connected to Analog ground by users.)          |      |

| 72  | ATEST_DAC | AO  | Test pin (No connection)                                            |      |

| 73  | DTEST_ED  | DI  | Test pin with pull down which internally connects to Digital ground |      |

| 74  | DTEST_M1  | DO  | Test pin (No connection)                                            |      |

| 75  | DTEST_M2  | DO  | Test pin (No connection)                                            |      |

| 76  | SCAN_MODE | DI  | Test pin with pull down which internally connects to Digital ground |      |

| 77  | TEST_NC1  | DIO | Test pin (No connection)                                            |      |

| 78  | TEST_NC2  | DIO | Test pin (No connection)                                            |      |

| 79  | TEST_NC3  | DO  | Test pin (No connection)                                            |      |

# 2.2 Pin Assignment

# Table 5 Pin assignment (Top view)

|   | 1         | 2          | 3               | 4             | 5               | 6                                       | 7                    | 8                  | 9                     | 10             | 11              | 12         | 13         | 14     |

|---|-----------|------------|-----------------|---------------|-----------------|-----------------------------------------|----------------------|--------------------|-----------------------|----------------|-----------------|------------|------------|--------|

| A | G N D _   | A D _N     | G N D _A D _N   | V D D _A D _N | G N D _D G      | CLK_RF2                                 | V D D _ ID _N E /N W | G N D _1D _N E,N W | V D D _A D _N         | G N D _A D _N  | GND_            | A D _N     |            |        |

| В | VDD_PX    | VREF       | GND_AD_V        | GND_AD_V      | VDD_DG_PL2      | VDD_DG_PL2                              | DTEST_M 2            | DTEST_M 1          | G N D _ ID _ N E ,N W | VDD_DG_PL1     | V D D _D G      | G N D _D G | C K 2P     | CK2N   |

| C | GND_PX*   | GND_AD_V   | $VDD\_AD\_V$    | $VDD\_AD\_V$  | RSTN            | TEST_NC1                                | TEST_NC2             | SCAN_MODE          | DTEST_ED              | GND_DG         | V D D _D G      | G N D _D G | D 8P       | D 8N   |

| D | VCAP_PX_N | GND_PX*    | V D D _D G      | V D D _D G    | G N D _D G      | V D D _D G                              | V D D _D G           | G N D _D G         | V D D _D G            | GND_DG         | V D D _D G      | G N D _D G | D 7P       | D 7N   |

| E | GND_PX*   | V D D _R G | G N D _D G      | G N D _D G    |                 |                                         |                      |                    |                       |                | VDD_PX          | G N D _P X | D 6P       | D 6N   |

| F | VCAP_VDRS | G N D _R G | V D D _ A D _ C | VDD_AD_C      |                 |                                         |                      |                    |                       |                | V D D _D G      | G N D _D G | D 5P       | D 5N   |

| G | VCAP_VTXH | ATEST_VDC  | GND_AD_C        | GND_AD_C      |                 |                                         |                      |                    |                       |                | V D D _D G      | G N D _D G | D 4P       | D 4N   |

| Н | VCAP_VTXL | ATEST_VW C | G N D _D G      | ATEST_DAC     |                 |                                         |                      |                    |                       |                | V D D _D G _S L | GND_DG_SL  | D 3P       | D 3N   |

| J | GND_PX*   | ATEST_VGC  | G N D _D G      | G N D _D G    |                 |                                         |                      |                    |                       |                | VDD_PX          | G N D _P X | D 2P       | D 2N   |

| K | VCAP_PX_S | GND_PX*    | V D D _D G      | V D D _D G    | G N D _D G      | V D D _D G                              | V D D _D G           | G N D _D G         | V D D _D G            | GND_DG         | V D D _D G      | G N D _D G | D 1P       | D 1N   |

| L | GND_PX*   | GND_AN *   | V D D _A N      | V D D _A N    | SDO             | SDO SCE CM4W CMHP CMHV GND_DG VDD_DG GN |                      |                    |                       |                |                 |            |            | CK1N   |

| M | VDD_PX    | REF        | GND_AN *        | GND_AN *      | SDI             | SCK                                     | SACK                 | TEST_NC3           | SYNC                  | TR IG          | VDD_DG          | GND_DG     | G N D _D G | GND_DG |

| N | G N D _   | AD_S       | GND_AD_S        | VDD_AD_S      | V D D _10 _12 C | G N D _10 _12 C                         | SCL                  | SDA                | V D D _ 10 _ 12 C     | G N D _1D _12C | VDD_AD_S        | GND_AD_S   | GND_       | AD_S   |

Figure 6 Example of external circuit (Top view)

# 3. Electrical Characteristics

# 3.1 Absolute Maximum Ratings

# Table 6 Absolute maximum ratings

| Item                                                                                                                                                                                                                                                                                                                                  | Symbol | Min     | Max      | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|----------|------|

| VDD_PX, VDD_RG, VDD_AD_N, VDD_AD_S, VDD_AD_V VDD_AD_C,VDD_AN, VCAP_VTXH,VREF,IREF, VCAP_VDRS VCAP_PX_N, VCAP_PX_, VDD_IO_N, VDD_IO_I2C SDA, SCL,SCE,SCK,SDI,CM4W, CMHP, CMHV CLK_RF1, RSTN,TRIG,SDO, SACK, SYNC ATEST_VDC, ATEST_VWC,ATEST_VGC,ATEST_DAC DTEST_ED, SCAN_MODE,CLK_RF2, DTEST_M1, DTEST_M2 TEST_NC1, TEST_NC2, TEST_NC3 | AVH    | -0.3    | 3.6V     | V    |

| VCAP_VTXL                                                                                                                                                                                                                                                                                                                             | AVN    | -0.9    | 0.3      | V    |

| VDD_DG, VDD_DG_PL1, VDD_DG_PL2, VDD_DG_SL D*P, D*N, {*: Lane Number (1~8) },CK1P, CK1N,CK2P, CK2N                                                                                                                                                                                                                                     | AVL    | -0.3    | 1.32     | V    |

| Storage temperature                                                                                                                                                                                                                                                                                                                   | Tstg   | -20     | 110      | °C   |

| Operating temperature                                                                                                                                                                                                                                                                                                                 | Та     | -20     | 85       | °C   |

| Storage and operating humidity                                                                                                                                                                                                                                                                                                        | -      | No cond | ensation | %    |

# 3.2 Power Supply

**Table 7 Power supply voltage**

| Item                                                                                                  | Symbol | Min  | Тур  | Max  | Unit | Condition |

|-------------------------------------------------------------------------------------------------------|--------|------|------|------|------|-----------|

| 2.8V power supply (analog)  VDD_PX, VDD_RG  VDD_AD_N, VDD_AD_S  VDD_AD_V, VDD_AD_C  VDD_AN, VCAP_VTXH | VDA28  | 2.66 | 2.80 | 2.94 | V    |           |

| 1.8V power supply (digital)  VDD_IO_N, VDD_IO_I2C                                                     | VDD18  | 1.71 | 1.80 | 1.89 | V    |           |

| 1.8V power supply (analog)  VREF                                                                      | VDA18  | 1.71 | 1.80 | 1.89 | V    |           |

| 1.2V power supply (digital)  VDD_DG                                                                   | VDD12  | 1.14 | 1.20 | 1.26 | V    |           |

| 1.2V power supply (analog)  VDD_DG_PL1, VDD_DG_PL2  VDD_DG_SL                                         | VDA12  | 1.14 | 1.20 | 1.26 | V    |           |

# **Table 8 Current consumption**

| Item                                                                                              | Symbol | Min | Тур | Max | Unit | Condition |

|---------------------------------------------------------------------------------------------------|--------|-----|-----|-----|------|-----------|

| 2.8V power supply (analog) VDD_PX, VDD_RG VDD_AD_N, VDD_AD_S VDD_AD_V, VDD_AD_C VDD_AN, VCAP_VTXH | IVDA28 | -   | 190 | 210 | mA   |           |

| 1.8V power supply (digital) VDD_IO_N, VDD_IO_I2C                                                  | IVDD18 | -   | 0.1 | 4   | mA   |           |

| 1.8V power supply (analog) VREF                                                                   | IVDA18 | -   | 0.1 | 1   | mA   |           |

| 1.2V power supply (digital) VDD_DG                                                                | IVDD12 | -   | 300 | 340 | mA   |           |

| 1.2V power supply (analog) VDD_DG_PL1, VDD_DG_PL2 VDD_DG_SL                                       | IVDA12 | -   | 9   | 12  | mA   |           |

#### 3.3 Pixel Characteristics

#### 3.3.1 Image Sensor Characteristics

Table 9 Sensor characteristics w/o PDAF Pixels

Tj=60°C, power supply voltage: typical if not specified

| Item                  | Symbol   | Min  | Тур | Max | Unit | Condition |

|-----------------------|----------|------|-----|-----|------|-----------|

| Sensitivity           | SENS_G   | 2100 | -   | -   | LSB  | *1        |

| Sensitivity ratio R/G | SENS_R/G | 35   | -   | 49  | %    | *1,*2     |

| Sensitivity ratio B/G | SENS_B/G | 64   | -   | 88  | %    | *1,*2     |

| Maximum output        | OUT_MAX  | 4000 | -   | -   | LSB  |           |

| Dark Shading          | D_SHAD   | -    | -   | 17  | LSB  | *3        |

| Line crawl R          | LINE_C_R | -6   |     | 6   | %    | *4        |

| Line crawl G          | LINE_C_G | -6   |     | 6   | %    | *4        |

| Line crawl B          | LINE_C_B | -6   |     | 6   | %    | *4        |

Light Source: D50 (defined in JIS8720 5000K) telecentric illuminator with heat-absorbing filter HOYA HA-50 and color correction filter HOYA CM500S.

#### \*1 Sensitivity

- (1) Apply 5x5 pixels median filter for image data, R/Gb/Gr/B respectively. ----- (a)

- (2) For image (a), calculate average of R/Gb/Gr/B data on center area ----- (b) center area: please refer to Figure 7.

- (3) calculate data(b) offset level (OB data) ----- SENS\_R/SENS\_G((Gr+Gb)/2)/SENS\_B

- \*2 Sensitivity ratio

- (1) calculate SENS\_R/SENS\_G ----- SENS\_R/G

- (2) calculate SENS\_B/SENS\_G ----- SENS\_B/G

- \*3 Dark shading

- (1) ZoneII divide to 48×27 blocks. 1 block is 80×80, 96×96, 96×80 or 80×96 pixels. Please refer to Figure 7.

- (2) Averaging output data in a block, R/G/B respectively.

- (3) SHADE\_R/G/B=(MAX-MIN)/(Ave.@center area)

- \*4 Line Crawl R/G/B

- (1) ZoneII divide to 48×27 blocks. Please refer to Figure 7.

- (2) Averaging output data in a block, Gb and Gr respectively. ----- AVE\_Gb/AVE\_Gr

- (3) LINE\_C\_R/G/B= $(AVE_Gr-AVE_Gb)/{(AVE_Gr+AVE_Gb)/2}\times100$

- <Lighting condition> LINE\_C\_R : Red LINE\_C\_G : Green LINE\_C\_B : Blue

Figure 7 Pixel characteristics calculation area

**Table 10 Sensor characteristics of PDAF Pixels**

Tj=60°C, power supply voltage: typical if not specified

| Item                            | Symbol              | Min  | Тур | Max | Unit | Condition |

|---------------------------------|---------------------|------|-----|-----|------|-----------|

| Sensitivity ratio L-open/R-open | SENS_PL/PR          | 0.67 | 1   | 1.5 | -    | *1        |

| PDAF Sensitivity                | SENS_PL,<br>SENS_PR | 656  | -   | -   | LSB  | *1        |

Note) This chip doesn't have the function to correct the sensitivity ratio; L-open/R-open inside. When you use PDAF function, please correct the sensitivity ratio to 1 in calculation.

Ex. You should multiply R-open PDAF output data by SENSE\_PL/PR or multiply L-open PDAF pixel output data by 1/(SENSE\_PL/PR).

Light Source: D50 (defined in JIS8720 5000K) telecentric illuminator with heat-absorbing filter HOYA HA-50 and color correction filter HOYA CM500S.

- \*1 PDAF Sensitivity, Sensitivity ratio L-open/R-open

- (1) Apply 5x5 pixels median filter for image data, L-open/R-open respectively. ----- (a)

- (2) For image (a), calculate average of L-open/R-open data of all PDAF pixels ----- (b)

- (3) calculate data(b) offset level (OB data) ----- SENS\_PL, SENS\_PR

- (4) calculate SENS\_PL/SENS\_PR----- SENS\_PL/PR

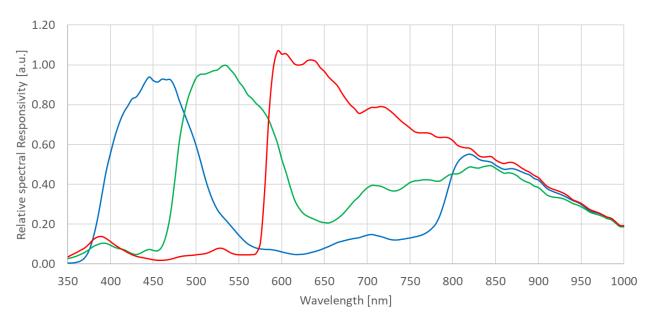

# 3.3.2 Spectral Characteristics

Figure 8 Spectral characteristics

Note: Spectral characteristics has possibility to change in sensor development.

# 3.3.3 Pixel Defect Specifications

#### **Table 11 Pixel defect specifications**

Tj=60°C, power supply voltage: typical if not specified

| Item                                                 | Symbol    | Min | Тур | Max  | Unit  | Condition |

|------------------------------------------------------|-----------|-----|-----|------|-------|-----------|

| Shine spot defect at Dark                            | WHI       | 1   | 1   | 1999 | pixel | *1        |

| Shine/Black spot defect at Bright (w/o PDAF)         | SHIN      | -   | -   | 1999 | pixel | *2        |

| Shine spot defect at Dark (PDAF)                     | WHI_P     |     |     | 31   | pixel | *3        |

| Shine/Black spot defect at Bright (PDAF)             | SHIN_P    | -   | -   | 31   | pixel | *4        |

| Pixel defect pattern (Mass defect)                   | MASS_D    | -   | -   | 0    | pixel | *5        |

| PDAF pixel spot defect in any 16x8 PDAF pixel region | MASS_PDAF |     |     | 1    | pixel | *6        |

- \*1 Shine spot defect at Dark

- (1) Take dark image @ Analog Gain 30dB----- (a)

- (2) Apply 5x5 pixels median filter for image data ----- (b)

- (3) Calculate (a)-(b) each pixel on zone II----- (c)

- (4) Count shine spot defect on data\_(c)

- \*2 Shine/Black spot defect at Bright

- (1) Take image @ Analog Gain 0dB----- (a)

- (2) Apply 5x5 pixels median filter for image data (R, Gb, Gr and B respectively) ----- (b)

- (3) Calculate (a)-(b) each pixel on zone II----- (c)

- (4) Calculate I/((b)-Dark\_offset) x 100 each pixel on zone II----- (d)

- (5) Shine spot defect is over 15% on data (d)

- (6) Black spot defect is under -15% on data (d)

- \*3 Shine spot defect at Dark (PDAF)

- (1) Take image and pick up PDAF image data @ Analog gain 30dB ----- (a)

- (2) Apply 5x5 pixel median filter for PDAF image data ----- (b)

- (3) Calculate (a)-(b) each pixel ----- (c)

- (4) Count shine spot defect on data\_(c).

- \*4 Shine/Black spot defect at Bright(PDAF)

- (1) Take image and pick up PDAF image data @ Analog Gain 0dB----- (a)

- (2) Apply 5x5 pixels median filter for PDAF image data ----- (b)

- (3) Calculate (a)-(b) each pixel ----- (c)

- (4) Calculate I/((b)-Dark\_offset) x 100 each pixel ----- (d)

- (5) Shine spot defect is over 15% on data (d)

- (6) Black spot defect is under -15% on data (d)

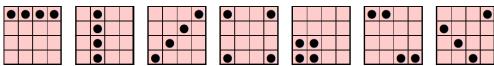

- \*5 Pixel defect pattern

Devices which include three or less pixel defects at each color in 3 x 3 Bayer area are not rejected.

Figure 9 Examples of allowed pixel defect patterns

However, devices which include following pattern (1) or (2) are rejected.

Pattern (1): Devices which include four or more pixels defect at each color in 4 x 4 Bayer area are rejected.

Figure 10 Examples of not allowed pixel defect patterns

Pattern (2): Devices which include consecutive defects at all colors in 3 x 3 Bayer area even including three pixel defects at each color are rejected.

Bayer

Each color

Figure 11 Examples of not allowed pixel defect patterns

Devices which include two L-open PDAF pixel defects in each 16 x 8 PDAF L-open pixel area are rejected.

Devices which include two R-open PDAF pixel defects in each 16 x 8 PDAF R-open pixel area are rejected.

<sup>\*6</sup> PDAF pixel spot defect in each 16 x 8 PDAF pixel region

# 3.4 Digital I/O (Input/Output)

Table 12 DC characteristics (Common)

Digital input pin: CLK\_RF1, RSTN, TRIG, CM4W, CMHP, CMHV Digital output pin: SYNC, SACK

Ta=25°C, power supply voltage: typical if not specified

| ia 20 0, points capping remages typical in not of |        |               |     |               |      |           |  |

|---------------------------------------------------|--------|---------------|-----|---------------|------|-----------|--|

| Item                                              | Symbol | Min           | Тур | Max           | Unit | Condition |  |

| Digital Input Voltage at High                     | VIH    | VDD18<br>x0.8 |     | VDD18<br>+0.2 | ٧    |           |  |

| Digital Input Voltage at Low                      | VIL    | -0.2          |     | VDD18<br>x0.2 | ٧    |           |  |

| Digital Output Voltage at High                    | VOH    | VDD18<br>-0.2 |     | -             | V    | IOH=1mA   |  |

| Digital Output Voltage at Low                     | VOL    |               |     | 0.20          | V    | IOL=1mA   |  |

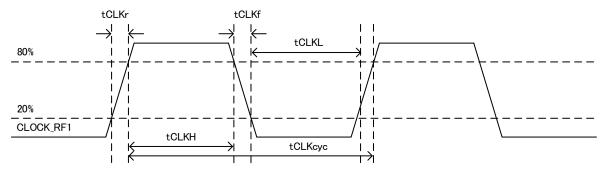

Table 13 AC characteristics (Clock)

Clock: CLK\_RF1

| Ta | =25°C, p | ower sup | ply voltage: typical if not specifi | ied |

|----|----------|----------|-------------------------------------|-----|

| p  | Max      | Unit     | Condition                           |     |

|    |          |          |                                     |     |

| Item                   | Symbol  | Min                  | Тур   | Max                  | Unit | Condition |

|------------------------|---------|----------------------|-------|----------------------|------|-----------|

| Clock cycle time       | tCLKcyc | typ<br>-20<br>ppm    | 1/27M | typ<br>+20<br>ppm    | s    |           |

| High level pulse width | tCLKH   | tCLKc<br>yc<br>x0.42 |       | tCLKc<br>yc<br>x0.58 | S    |           |

| Low level pulse width  | tCLKL   | tCLKc<br>yc<br>x0.42 |       | tCLKc<br>yc<br>x0.58 | S    |           |

| Clock Rise Time        | tCLKr   |                      |       | 1                    | ns   | 20% - 80% |

| Clock Fall Time        | tCLKf   |                      |       | 1                    | ns   | 80% - 20% |

| Clock Jitter           | tCLKj   | -15                  |       | +15                  | ps   |           |

Figure 12 CLK\_RF1 waveform

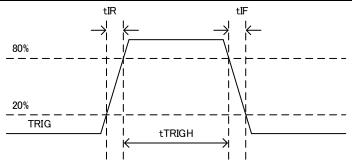

Table 14 AC characteristics (Digital input pin)

Digital input pin: TRIG, RSTN, CM4W, CMHP, CMHV Ta=25°C, power supply voltage: typical if not specified

| Item                            | Symbol | Min | Тур | Max  | Unit | Condition |

|---------------------------------|--------|-----|-----|------|------|-----------|

| Rise Time                       | tR     |     |     | 5    | ns   | 20% - 80% |

| Fall Time                       | tF     |     |     | 5    | ns   | 80% - 20% |

| High level pulse width for TRIG | tTRIGH | 75  |     | 3000 | ns   |           |

Figure 13 TRIG waveform

# 3.5 Serial Communication3.5.1 I2C

## Table 15 I2C bus DC characteristics

| Item                                                                               | Symbol | Min                 | Тур | Max                   | Unit | Condition                |

|------------------------------------------------------------------------------------|--------|---------------------|-----|-----------------------|------|--------------------------|

| Pull-up voltage                                                                    | VDI    | 1.72                | 1.8 |                       | V    |                          |

| Pull-up resistor                                                                   | RP     | VDI<br>*0.7<br>/3   |     | 250/<br>0.8473<br>/CB | kΩ   | fast mode                |

| (CB=total capacitance of one bus line in pF)                                       | RP     | VDI<br>*0.7<br>/20  |     | 120/<br>0.8473<br>/CB | K22  | fast mode plus           |

| LOW level input voltage                                                            | VIL    | -0.5                |     | VDI<br>*0.3           | ٧    |                          |

| HIGH level input voltage                                                           | VIH    | VDI<br>*0.7         |     | VDI<br>+0.5           | V    |                          |

| Hysteresis of Schmitt trigger inputs                                               | VHYS   | VDI<br>*0.05        |     | -                     | ٧    |                          |

| LOW level output voltage (open drain) at 2mA sink current                          | VOL    | 0                   |     | VDI<br>*0.2           | ٧    |                          |

| HIGH level output voltage                                                          | VOH    | *0.8                |     | -                     | V    |                          |

| Low level output current (VOL=0.4V)                                                | IOL    | 3<br>20             |     | -                     | mA   | fast mode fast mode plus |

| Output fall time from VIHmin to VILmax with bus capacitance (CB)                   | tOF    | VDDI<br>*20<br>/5.5 |     | 250                   | 50   | fast mode : <400pF       |

| from 10 pF to 400 pF                                                               | ioi    | VDDI<br>*20<br>/5.5 |     | 120                   | ns   | fast mode plus : <550pF  |

| Pulse width of spikes which shall be suppressed by the input filter                | tSP    | 0                   |     | 50                    | ns   |                          |

| Input current each I/O pin<br>with an input voltage<br>between 0.1 VDI and 0.9 VDI | lt     | -10                 |     | 10                    | uA   |                          |

| Input/Output capacitance (SDA)                                                     | CI/O   | -                   |     | 8                     | рF   |                          |

| Input capacitance (SCL)                                                            | CI     | -                   |     | 6                     | pF   |                          |

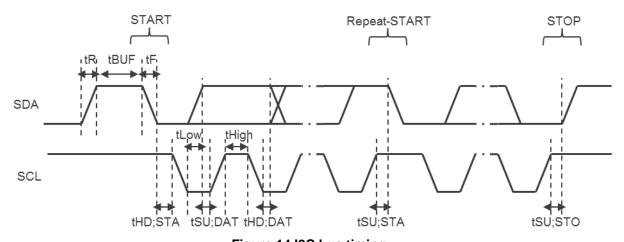

Table 16 I2C bus timing characteristics

| Item                                                                           | Symbol  | Min                | Тур | Max  | Unit | Condition      |

|--------------------------------------------------------------------------------|---------|--------------------|-----|------|------|----------------|

| 001 1 1 (                                                                      | (0.0)   | 0                  | -   | 400  |      | fast mode      |

| SCL clock frequency                                                            | fSCL    | 0                  | -   | 1000 | kHz  | fast mode plus |

| Hold time (repeated) START                                                     |         | 0.6                | -   | -    |      | fast mode      |

| condition. After this period, the first clock pulse is generated               | tHD;STA | 0.26               | -   | -    | us   | fast mode plus |

| LOW period of the SCL clock                                                    | tLOW    | 1.3                | -   | -    | 110  | fast mode      |

| LOW period of the SCL clock                                                    | ILOVV   | 0.5                | -   | -    | us   | fast mode plus |

| HIGH period of the SCL clock                                                   | tHIGH   | 0.6                | -   | -    | us   | fast mode      |

| HIGH period of the SCL clock                                                   | เกเษก   | 0.26               | -   | -    | us   | fast mode plus |

| Setup time for a repeated                                                      | tSU;STA | 0.6                | -   | -    | us   | fast mode      |

| START condition                                                                | 130,314 | 0.26               | -   | -    | us   | fast mode plus |

| Data hold time                                                                 | tHD;DAT | 0                  | -   | 0.9  | 110  | fast mode      |

| Data fiold time                                                                | IND,DAT | 0                  | -   | 0.45 | us   | fast mode plus |

| Data set-up time                                                               | tSU;DAT | 100                | -   | -    | 20   | fast mode      |

| Data set-up time                                                               | ISU,DAT | 50                 | -   | -    | ns   | fast mode plus |

| Rise time of both SDA and                                                      |         | 20                 | -   | 300  |      | fast mode      |

| SCL signals (CB=total capacitance of one bus line in pF)                       | tR      | -                  | -   | 120  | ns   | fast mode plus |

| Fall time of both SDA and SCL signals (CB=total capacitance                    | tF      | VDI<br>*20<br>/5.5 | -   | 300  | ns   | fast mode      |

| of one bus line in pF)                                                         | ur      | VDI<br>*20<br>/5.5 | -   | 120  | 115  | fast mode plus |

| Set-up time for STOP condition                                                 | tSU;STO | 0.6                | -   | -    | us   | fast mode      |

| Set-up time for STOL condition                                                 | 130,310 | 0.26               | -   | -    | us   | fast mode plus |

| Bus free time between                                                          | tBUF    | 1.3                | -   | -    | us   | fast mode      |

| a STOP and START condition                                                     | וטטו    | 0.5                | -   | -    | us   | fast mode plus |

| Capacitive load for each bus line                                              | СВ      | 10                 | -   | 400  | pF   | fast mode      |

| Capacitive load for each bus lifte                                             | СВ      | 10                 | -   | 550  | PΓ   | fast mode plus |

| Noise margin at the LOW level for each connected device (including hysteresis) | VnL     | 0.18               | -   | -    | ٧    |                |

Figure 14 I2C bus timing

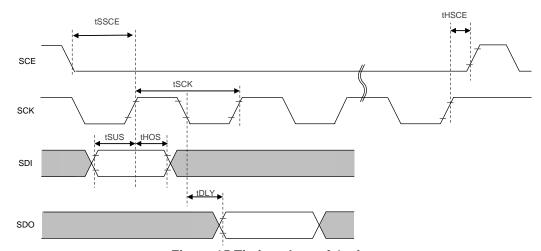

## 3.5.2 4-wire

Table 17 4-wire DC/AC characteristics

Input Pin: SCE, SCK, SDI

Output Pin: SDO Ta=25°C, power supply voltage: typical if not specified

|                                   |        |       | 1 u – | 20 0, pov | rci suppiy | voltage. typical ii flot specified |

|-----------------------------------|--------|-------|-------|-----------|------------|------------------------------------|

| Item                              | Symbol | Min   | Тур   | Max       | Unit       | Condition                          |

| District to and Make on a station | VIH    | VDD18 |       | VDD18     | V          |                                    |

| Digital Input Voltage at High     | VIII   | x0.8  |       | +0.2      | V          |                                    |

| Digital Input Voltage at Low      | VIL    | -0.2  |       | VDD18     | V          |                                    |

| Digital input voltage at Low      | VIL    | · · · |       | x0.2      |            |                                    |

| Digital Output Valtage at Lligh   | VOH    | VDD18 |       |           | V          | IOH=1mA                            |

| Digital Output Voltage at High    | VOH    | -0.2  |       | - V       | V          | IOH=IIIIA                          |

| Digital Output Valtage at Law     | \/OI   |       |       | 0.00      | \/         | IOI 4 == A                         |

| Digital Output Voltage at Low     | VOL    | -     |       | 0.20      | V          | IOL=1mA                            |

| SCE setup time                    | tSSCE  | 40    |       | -         | ns         |                                    |

| SCE hold time                     | tHSCE  | 40    |       | -         | ns         |                                    |

| SCK Cycle time                    | tSCK   | 93    |       | -         | ns         |                                    |

| SDI input setup time              | tSUS   | 20    |       | -         | ns         |                                    |

| SDI input hold time               | tHOS   | 20    |       | -         | ns         |                                    |

| SDO output delay                  | tDLY   | -     |       | 30        | ns         | output capacitance 5pF             |

Figure 15 Timing chart of 4-wire

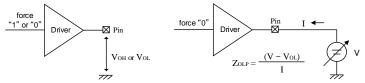

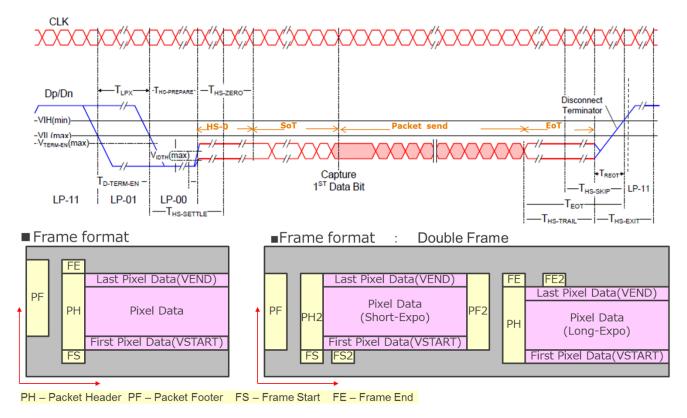

# 3.6 Image data output Interfaces

# 3.6.1 MIPI-CSI2 (Low-power mode)

Table 18 Low-power mode DC characteristics

Ta=25°C, power supply voltage: typical if not specified

| Item                               | Symbol           | Min | Тур | Max | Unit | Condition |

|------------------------------------|------------------|-----|-----|-----|------|-----------|

| Thevenin output high level         | V <sub>OH</sub>  | 1.1 | 1.2 | 1.3 | V    | *1        |

| Thevenin output low level          | V <sub>OL</sub>  | -50 |     | 50  | mV   | *1        |

| Output impedance of LP transmitter | Z <sub>OLP</sub> | 110 |     |     | Ω    |           |

<sup>\*1:</sup> The value is specified when the output pin is unloaded.

Figure 16 Load circuits for CSI2 Low-power mode

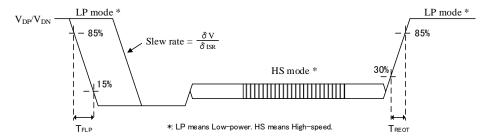

Table 19 Low-power mode AC characteristics

| Item                                                                                                               | Symbol              | Min                                     | Тур | Max | Unit  | Condition |

|--------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------|-----|-----|-------|-----------|

| Load capacitance condition                                                                                         |                     | 0                                       | -   | 70  | pF    |           |

| 15%-85% fall time                                                                                                  | T <sub>FLP</sub>    | -                                       | -   | 25  | ns    |           |

| 30%-85% rise time                                                                                                  | T <sub>REOT</sub>   | -                                       | -   | 35  | ns    |           |

| Slew rate @ C <sub>LOAD</sub> = 0pF                                                                                | δV/δt <sub>SR</sub> | -                                       | -   | 500 | mV/ns | *1        |

| Slew rate @ C <sub>LOAD</sub> = 5pF                                                                                |                     | -                                       | -   | 300 | mV/ns | *1        |

| Slew rate @ C <sub>LOAD</sub> = 20pF                                                                               |                     | -                                       | -   | 250 | mV/ns | *1        |

| Slew rate @ C <sub>LOAD</sub> = 70pF                                                                               |                     | -                                       | -   | 150 | mV/ns | *1        |

| Slew rate @ C <sub>LOAD</sub> = 0 to 70pF<br>(Falling Edge Only)                                                   |                     | 30                                      | -   | -   | mV/ns | *2        |

| Slew rate @ C <sub>LOAD</sub> = 0 to 70pF<br>(Rising Edge Only)                                                    |                     | 30                                      | -   | -   | mV/ns | *3        |

| Slew rate @ C <sub>LOAD</sub> = 0 to 70pF<br>(Rising Edge Only)<br>VO,INST : instantaneous output<br>voltage in mV |                     | 30 –<br>0.075<br>(VO,I<br>NST –<br>700) | -   | -   | mV/ns | *4        |

<sup>\*1:</sup> When the output voltage is between VOL and VOH.

<sup>\*4:</sup> When the output voltage is between 700mV and 930mV.

Figure 17 CSI2 Low-power and High-speed

<sup>\*2:</sup> When the output voltage is between 400mV and 930mV.

<sup>\*3:</sup> When the output voltage is between 400mV and 700mV.

# 3.6.2 SLVS and MIPI-CSI2 (High-speed mode)

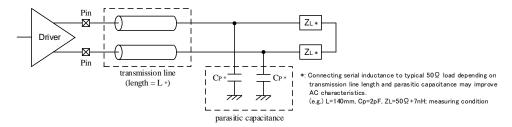

Figure 18 Load circuits for SLVS and CSI2 High-speed mode

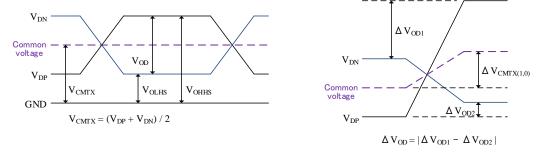

# Table 20 MIPI-CSI2 High-speed mode DC characteristics

Ta=25°C, power supply voltage: typical if not specified

| Item                                                                       | Symbol                  | Min | Тур | Max  | Unit | Condition |

|----------------------------------------------------------------------------|-------------------------|-----|-----|------|------|-----------|

| HS transmit static common-mode voltage                                     | V <sub>СМТХ</sub>       | 150 | 200 | 250  | mV   |           |

| V <sub>CMTX</sub> mismatch when output is Differential-1 or Differential-0 | ΔV <sub>CMTX(1,0)</sub> | •   |     | 5    | mV   |           |

| HS transmit differential voltage                                           | Vod                     | 140 | 200 | 270  | mV   |           |

| V <sub>OD</sub> mismatch when output is Differential-1 or Differential-0   | ΔV <sub>OD</sub>        | -   | -   | 14   | mV   |           |

| HS output high voltage                                                     | V <sub>OHHS</sub>       | -   | -   | 360  | mV   |           |

| Single ended output impedance                                              |                         | 40  | 50  | 62.5 | Ω    |           |

| Single ended output impedance mismatch                                     |                         | -   | -   | 10   | %    |           |

**Table 21 SLVS DC characteristics**

| Item                                                           | Symbol                  | Min | Тур | Max | Unit | Condition |

|----------------------------------------------------------------|-------------------------|-----|-----|-----|------|-----------|

| Common-mode voltage                                            | V <sub>CMTX</sub>       | 150 | -   | 250 | mV   |           |

| VCMTX mismatch when output is Differential-1 or Differential-0 | ΔV <sub>CMTX(1,0)</sub> | -   | ı   | 50  | mV   |           |

| Differential output voltage                                    | V <sub>OD</sub>         | 70  | -   | -   | mV   |           |

| Single ended high output voltage                               | Vohhs                   |     | -   | 380 | mV   |           |

| Single ended low output voltage                                | Volhs                   | 40  | -   | -   | mV   |           |

| Vсмтх mismatch of lane-to-lane                                 |                         | -   | -   | 100 | mV   | *1        |

<sup>\*1:</sup> The voltage between the highest  $V_{\text{CMTX}}$  and the lowest  $V_{\text{CMTX}}$  among all output lanes.

Figure 19 DC characteristics for SLVS and CSI2 High-speed mode

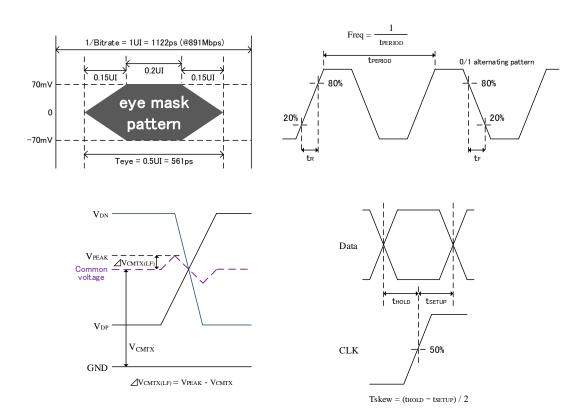

Table 22 MIPI-CSI2 High-speed mode AC characteristics

Ta=25°C, power supply voltage: typical if not specified

| Item                            | Symbol                            | Min    | Тур   | Max   | Unit        | Condition |

|---------------------------------|-----------------------------------|--------|-------|-------|-------------|-----------|

| Output bit rate condition       | Bitrate                           | -      | 891   | -     | Mbps        |           |

| Data clock frequency            | Freq                              | -      | 445.5 | -     | MHz         |           |

| Common-level variation          | $\Delta V_{\text{CMTX(LF)}}$      | -      | -     | 25    | $mV_{PEAK}$ |           |

| Data to Clock skew              | Tskew                             | -168.4 | -     | 168.4 | ps          |           |

| Clock jitter                    |                                   | -      | -     | 224.4 | ps          | *1        |

| 20%-80% rise time and fall time | 4                                 | -      | -     | 0.3   | UI          |           |

|                                 | t <sub>R</sub> and t <sub>F</sub> | 150    | -     | -     | ps          |           |

<sup>\*1:</sup> The value is specified as jitter of unit interval (UI).

**Table 23 SLVS AC characteristics**

| Item                      | Symbol         | Min | Тур   | Max | Unit | Condition |

|---------------------------|----------------|-----|-------|-----|------|-----------|

| Output bit rate condition | Bitrate        | -   | 891   | -   | Mbps |           |

| Data clock frequency      | Freq           | -   | 445.5 | -   | MHz  |           |

| Eye opening               | Teye           | 0.5 | -     | -   | UI   |           |

| 20%-80% Rise time         | t <sub>R</sub> |     | -     | 0.3 | UI   |           |

| 20%-80% Fall time         | t <sub>F</sub> | -   | -     | 0.3 | UI   |           |

Figure 20 AC characteristics for SLVS and CSI2 High-speed mode

## 4. Imaging Format

#### 4.1 Read Mode

Table 24 explains the read modes and the maximum frame rates.

- UHD: 3904 x 2224 pixels, Single Exposure.

- UHD-HDR: 3904 x 2224 pixels, Double Exposure (Long exposure & Short exposure, Line by Line).

Each mode, except UHD 10bit mode has two selectable output interfaces, SLVS or MIPI.

#### Table 24 Read mode

EXP: Exposure, 2: Long & Short,

| No. | Read mode  | Maximum frame rate | ADC resolution | The number of pixels |          | Output I/ |           |                  |             |           |       |         |

|-----|------------|--------------------|----------------|----------------------|----------|-----------|-----------|------------------|-------------|-----------|-------|---------|

|     |            | [frame/sec]        | [bit]          | EXP                  | Н        | V         | Format    | Lane             | Data rate   |           |       |         |

| 1-1 | UHD        | 60                 | 10             | 1                    | 2004niv  | 0004=iv   | 2224niy   | 2224niv          | 2224niy     | MIPI-CSI2 | 8data | 901Mbpa |

| 1-2 | טחט        | 60                 | 12             | 1                    | 3904pix. | 2224pix.  | SLVS      | 1clock           | 891Mbps     |           |       |         |

| 2-1 | UHD        | 60                 | 10             | 1                    | 3904pix. | 2224pix.  | MIPI-CSI2 | 8data<br>1clock  | 891Mbps     |           |       |         |

| 3-1 | UHD        | 30                 | 12             | 1                    | 3904pix. | 2224pix.  | MIPI-CSI2 | 4data            | 891Mbps     |           |       |         |

| 3-2 | טחט        | 30                 | 12             | '                    | 3904pix. | 2224pix.  | SLVS      | 1clock           |             |           |       |         |

| 4-1 | UHD        | 20                 | 10             | 1                    | 2004niy  | 2224pix.  | MIPI-CSI2 | 8data            | 445 EMbpo   |           |       |         |

| 4-2 | UHD        | 30                 | 12             | '                    | 3904pix. |           | SLVS      | 1clock           | 445.5Mbps   |           |       |         |

| 5-1 | LILID LIDD | 20                 | 40             | 2                    | 2004=:   | 2024=1-4  | MIPI-CSI2 | 8data            | 0041141     |           |       |         |

| 5-2 | UHD-HDR    | 30                 | 12             | 2                    | 3904pix. | 2224pix.  | SLVS      | 1clock           | 891Mbps     |           |       |         |

| 6-1 | UHD-HDR    | 15                 | 10             | 2                    | 2004niy  | 2224niy   | MIPI-CSI2 | 8data            | 115 FMbpo   |           |       |         |

| 6-2 | טחט-חטא    | 15                 | 12             | 2                    | 3904pix. | 2224pix.  | SLVS      | 1clock 445.5Mbps | equivic.c++ |           |       |         |

Figure 21 shows the pixel array structure. 16 pixels in the horizontal invalid area between HOB and Effective, which corresponds to the sum of Invalid Optical Black (6 pixels) and Invalid (10 pixels) depicted in Figure 2, will not be read out. As well as the horizontal invalid areas, 16 pixels in the vertical invalid area between VOB and Effective will not be read out. Therefore, the number of pixels to be read out will be 3904 x 2224.

Regarding to the order of pixels to be read, the first will be the pixel on the lower left corner (Figure 21 Base Point). The next to be read will be the right of the first pixel. In other words, the order of pixels to be read will be rightward from Base Point.

There isn't the read mode to output only PDAF data without normal image data inside chip.

# 4.1.2 HDR (Line by Line)

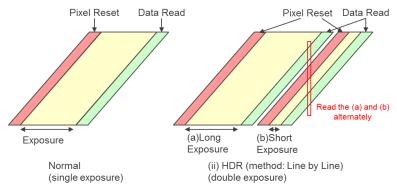

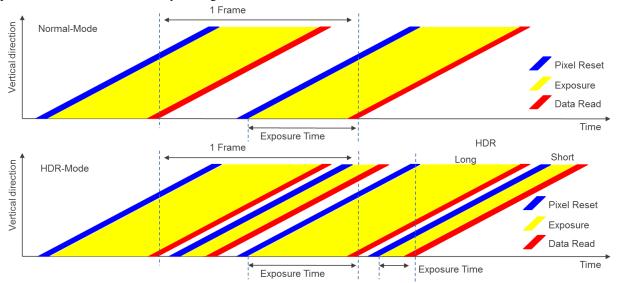

Figure 23 indicates the operation of HDR, which will enlarge the sensor dynamic range. Compared with Frame by Frame HDR, Line by Line HDR will realize small time lag between the long exposure and the short exposure.

Figure 21 Pixel array structure (Readout area)

Figure 22 Pixel data

Figure 23 HDR (Line by Line)

## 4.2 Output I/F Format

## 4.2.1 Protocol #1 (SLVS)

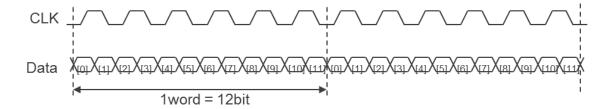

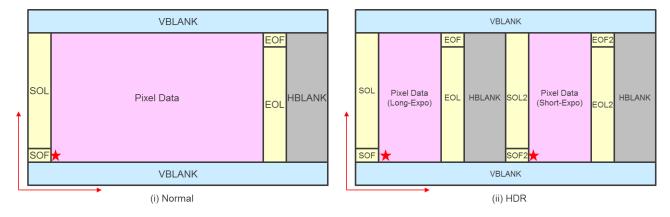

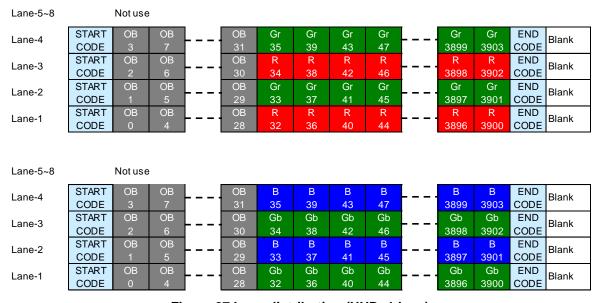

Figure 24 and Figure 25 shows the data format of source synchronous SLVS. The typical source synchronous clock's rise edge shall be at the center of data [0]. A word consists of 12bit data. A frame consists of pixel data, SOL, SOF, EOL, EOF (synchronous codes), VBLANK and HBLANK (dummy data) as follows.

SOL: Start of LineSOF: Start of FrameEOL: End of LineEOF: End of Frame

VBLANK: Vertical BlankHBLANK: Horizontal Blank

Be careful that there are eight synchronous codes in case of HDR (long exposure and short exposure).

Figure 24 Timing chart of CLK and Data

Figure 25 Data format

Table 25 Setting value (Synchronous code and dummy data)

| Category         | Name                  | Data  | Value<br>( 1 <sup>st</sup> _2 <sup>nd</sup> _3 <sup>rd</sup> _4 <sup>th</sup> ) | Note                   |

|------------------|-----------------------|-------|---------------------------------------------------------------------------------|------------------------|

|                  | SOF (start of frame)  | 4word | FFF_000_000_"XXX"                                                               | XXX is set by register |

|                  | EOF (end of frame)    | 4word | FFF_000_000_"XXX"                                                               | XXX is set by register |

|                  | SOL (start of line)   | 4word | FFF_000_000_"XXX"                                                               | XXX is set by register |

| Synobronous ands | EOL (end of line)     | 4word | FFF_000_000_"XXX"                                                               | XXX is set by register |

| Synchronous code | SOF2 (start of frame) | 4word | FFF_000_000_"XXX"                                                               | XXX is set by register |

|                  | EOF2 (end of frame)   | 4word | FFF_000_000_"XXX"                                                               | XXX is set by register |

|                  | SOL2 (start of line)  | 4word | FFF_000_000_"XXX"                                                               | XXX is set by register |

|                  | EOL2(end of line)     | 4word | FFF_000_000_"XXX"                                                               | XXX is set by register |

| D D4-            | VBLANK                | 1word | "XXX"                                                                           | XXX is set by register |

| Dummy Data       | HBLANK                | 1word | "XXX"                                                                           | XXX is set by register |

|         | START | ОВ      | OB  | ОВ  | ОВ  | Gr | Gr | Gr | Gr |   | Gr   | Gr   | END       |        |

|---------|-------|---------|-----|-----|-----|----|----|----|----|---|------|------|-----------|--------|

| Lane-8  | CODE  |         | 15  | 23  | 31  | 39 | 47 | 55 | 63 |   | 3895 | 3903 | CODE      | Blank  |

| Lane-7  | START | OB      | OB  | ОВ  | OB  | R  | R  | R  | R  | L | R    | R    | END       | Blank  |

| Laile-7 | CODE  | 6       | 14  | 22  | 30  | 38 | 46 | 54 | 62 |   | 3894 | 3902 | CODE      | DIAIIK |

| Lane-6  | START | OB      | OB  | OB  | ОВ  | Gr | Gr | Gr | Gr | L | Gr   | Gr   | END Blank |        |

| Lane-0  | CODE  | 5       | 13  | 21  | 29  | 37 | 45 | 53 | 61 |   | 3893 | 3901 | CODE      | Dialik |

| Lane-5  | START | ОВ      | OB  | ОВ  | OB  | R  | R  | R  | R  |   | R    | R    | END       | Blank  |

| Lane-5  | CODE  | 4       | 12  | 20  | 28  | 36 | 44 | 52 | 60 |   | 3892 | 3900 | CODE      | Dialik |

| Lane-4  | START | OB      | OB  | OB  | OB  | Gr | Gr | Gr | Gr | L | Gr   | Gr   | END       | Blank  |

| Lano i  | CODE  | 3       | 11  | 19  | 27  | 35 | 43 | 51 | 59 |   | 3891 | 3899 | CODE      | Diame  |

| Lane-3  | START | OB      | OB  | OB  | OB  | R  | R  | R  | R  |   | R    | R    | END       | Blank  |

| Lano o  | CODE  | 2       | 10  | 18  | 26  | 34 | 42 | 50 | 58 |   | 3890 | 3898 | CODE      | Diame  |

| Lane-2  | START | OB      | OB  | OB  | OB  | Gr | Gr | Gr | Gr |   | Gr   | Gr   | END       | Blank  |

| Lano L  | CODE  | 1       | 9   | 17  | 25  | 33 | 41 | 49 | 57 |   | 3889 | 3897 | CODE      | Diame  |

| Lane-1  | START | OB      | OB  | OB  | ОВ  | R  | R  | R  | R  |   | R    | R    | END       | Blank  |

|         | CODE  | 0       | 8   | 16  | 24  | 32 | 40 | 48 | 56 |   | 3888 | 3896 | CODE      |        |

|         |       |         |     |     |     |    |    |    |    |   |      |      |           |        |

|         | OTABT | 0.5     | 0.5 | 0.5 | 0.0 |    |    |    |    | 1 |      | _    | END       | 1      |

| Lane-8  | START | OB<br>- | OB  | OB  | OB  | В  | В  | В  | В  |   | В    | В    | END       | Blank  |

|         | CODE  | 7       | 15  | 23  | 31  | 39 | 47 | 55 | 63 |   | 3895 | 3903 | CODE      |        |

| Lane-7  | START | OB      | OB  | OB  | OB  | Gb | Gb | Gb | Gb |   | Gb   | Gb   | END       | Blank  |

|         | CODE  | 6       | 14  | 22  | 30  | 38 | 46 | 54 | 62 |   | 3894 | 3902 | CODE      |        |

| Lane-6  | START | OB<br>- | OB  | ОВ  | ОВ  | В  | В  | В  | В  |   | В    | В    | END       | Blank  |

|         | CODE  | 5       | 13  | 21  | 29  | 37 | 45 | 53 | 61 |   | 3893 | 3901 | CODE      |        |

| Lane-5  | START | OB      | OB  | OB  | OB  | Gb | Gb | Gb | Gb |   | Gb   | Gb   | END       | Blank  |

|         | CODE  | 4       | 12  | 20  | 28  | 36 | 44 | 52 | 60 |   | 3892 | 3900 | CODE      |        |

| Lane-4  | START | OB      | OB  | ОВ  | ОВ  | В  | В  | В  | В  |   | В    | В    | END       | Blank  |

|         | CODE  | 3       | 11  | 19  | 27  | 35 | 43 | 51 | 59 |   | 3891 | 3899 | CODE      |        |

| Lane-3  | START | OB      | OB  | OB  | OB  | Gb | Gb | Gb | Gb |   | Gb   | Gb   | END       | Blank  |

|         | CODE  | 2       | 10  | 18  | 26  | 34 | 42 | 50 | 58 |   | 3890 | 3898 | CODE      |        |

| Lane-2  | START | OB      | OB  | OB  | OB  | В  | В  | В  | В  |   | В    | В    | END       | Blank  |

|         | CODE  | 1       | 9   | 17  | 25  | 33 | 41 | 49 | 57 |   | 3889 | 3897 | CODE      |        |

| Lane-1  | START | OB      | OB  | OB  | OB  | Gb | Gb | Gb | Gb |   | Gb   | Gb   | END       | Blank  |

| Lane-i  | CODE  | 0       | 8   | 16  | 24  | 32 | 40 | 48 | 56 |   | 3888 | 3896 | CODE      | DIAIIK |

Figure 26 Lane distribution (UHD, 8-lane)

Figure 27 Lane distribution (UHD, 4-lane)

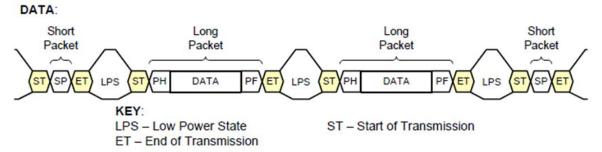

## 4.2.2 Protocol #2 (MIPI-CSI2)

This protocol is based on the MIPI CSI2 specification. \*MIPI: Mobile Industry Processor Interface Alliance

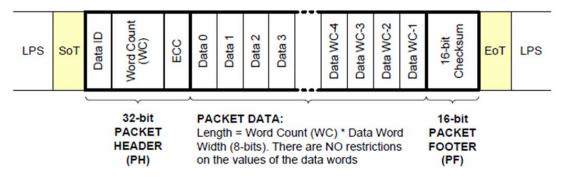

This protocol has two types of packet structures, Short Packet and Long Packet. For each packet structure, exit from the Low Power State followed by the Start of Transmission sequence indicates the start of the packet. The End of Transmission sequence followed by the Low Power State indicates the end of the packet.

Figure 28 MIPI-CSI2

Figure 29 MIPI-CSI2 format

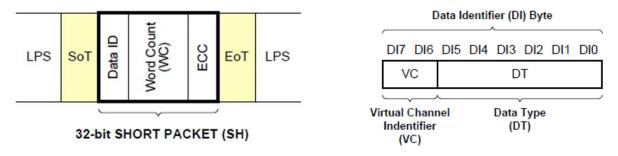

#### Structure of Short Packet

Figure 30 Short packet

#### ➤ SoT

Start of Transmission (8bit) = 00011101.

#### Data ID

Data Identifier byte contains Virtual Channel Identifier (2bit) and Data Type (6bit).

Virtual Channel Identifier allows both long exposure and short exposure images within a single data stream.

Virtual Channel Identifier = 00 at the long exposure image of HDR mode.

Virtual Channel Identifier = 01 at the short exposure image of HDR mode.

Data Type = 000000, when the packet is Frame Start Code.

Data Type = 000001, when the packet is Frame End Code.

#### > WC

Word Count (16bit) = 0x0000.

#### ➤ ECC

Hamming-Modified Code (8bit) to correct single-bit error and to detect 2-bit errors in the packet header.

#### ➤ EoT

End of Transmission = all one-state, when the last payload data bit is zero-state.

End of Transmission = all zero-state, when the last payload data bit is one-state.

#### Structure of Long Packet

Figure 31 Long packet

#### ➤ SoT

Start of Transmission (8bit) = 00011101.

#### Data ID

Data Identifier byte contains Virtual Channel Identifier (2bit) and Data Type (6bit).

Virtual Channel Identifier allows both long exposure and short exposure images within a single data stream.

Virtual Channel Identifier = 00 at the long exposure image of HDR mode.

Virtual Channel Identifier = 01 at the short exposure image of HDR mode.

Data Type = 101011, when the data format is RAW10.

Data Type = 101100, when the data format is RAW12.

#### > WC

Word Count (16bit) defines the number of 8-bit data words in the payload data. Neither the Packet Header nor the Packet Footer is included in the Word Count.

#### > ECC

Hamming-Modified Code (8bit) to correct single-bit error and to detect 2-bit errors in the packet header.

#### Checksum

Cyclic Redundancy Code (16bit) to detect possible errors in the payload data.

#### ➤ FoT

End of Transmission = all one-state, when the last payload data bit is zero-state. End of Transmission = all zero-state, when the last payload data bit is one-state.

#### Supported Data Format

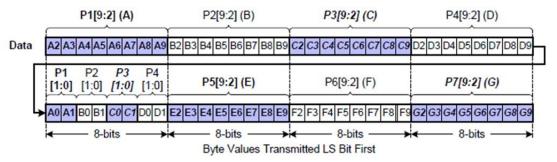

#### RAW10

The transmission of 10-bit Raw Data is done by packing the four 10-bit pixel data to look like 8-bit data format.

- 1st byte is upper 8-bits of 1st pixel data.

- 2<sup>nd</sup> byte is upper 8-bits of 2<sup>nd</sup> pixel data. 3<sup>rd</sup> byte is upper 8-bits of 3<sup>rd</sup> pixel data.

- 4<sup>th</sup> byte is upper 8-bits of 4<sup>th</sup> pixel data. 5<sup>th</sup> byte is lower 2-bits of 1<sup>st</sup>, 2<sup>nd</sup>, 3<sup>rd</sup> and 4<sup>th</sup> pixel data.

Figure 32 RAW10 format

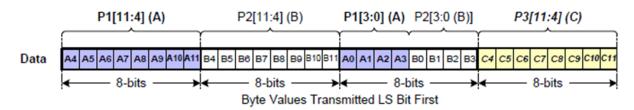

#### RAW12

The transmission of 12-bit Raw Data is done by packing the two 12-bit pixel data to look like 8-bit data format. 1st byte is upper 8-bits of 1st pixel data.

- 2<sup>nd</sup> byte is upper 8-bits of 2<sup>nd</sup> pixel data.

- 3<sup>rd</sup> byte is lower 4-bits of 1<sup>st</sup> and 2<sup>nd</sup> pixel data.

Figure 33 RAW12 format

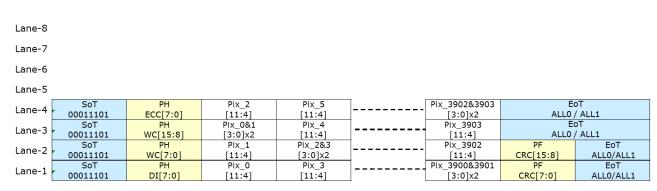

#### Lane Distribution

4-Lane and 8-Lane system are supported as follows.

|         | SoT      | Pix_2                          | Pix_6&7 | Pix_13    | L        | Pix_3901      | Ec            | T         |

|---------|----------|--------------------------------|---------|-----------|----------|---------------|---------------|-----------|

| Lane-8  | 00011101 | [11:4]                         | [3:0]x2 | [11:4]    |          | [11:4]        | ALLO / ALL1   |           |

| 1200 7  | SoT      | Pix_0&1                        |         |           | Pix_3900 | Ed            |               |           |

| Lane-7  | 00011101 | [3:0]x2                        | [11:4]  | [11:4]    |          | [11:4]        | ALLO /        | ALL1      |

| Lane-6  | SoT      | Pix_1                          | Pix_6   | Pix_10&11 |          | Pix_3898&3899 | PF            | EoT       |

| Laile-6 | 00011101 | [11:4]                         | [11:4]  | [3:0]x2   |          | [3:0]x2       | CRC[15:8]     | ALLO/ALL1 |

| lana E  | SoT      | Pix_0                          | Pix_4&5 | Pix_11    |          | Pix_3899      | PF            | EoT       |

| Lane-5  | 00011101 | 00011101 [11:4] [3:0]x2 [11:4] |         | [11:4]    | CRC[7:0] | ALLO/ALL1     |               |           |

| Lane-4  | SoT      | PH                             | Pix_5   | Pix_10    |          | Pix_3898      | Pix_3902&3903 | EoT       |

| Lane-4  | 00011101 | ECC[7:0]                       | [11:4]  | [11:4]    |          | [11:4]        | [3:0]x2       | ALLO/ALL1 |

| Lane-3  | SoT      | PH                             | Pix_4   | Pix_8&9   |          | Pix_3896&3897 | Pix_3903      | EoT       |

| Laile-3 | 00011101 | WC[15:8]                       | [11:4]  | [3:0]x2   |          | [3:0]x2       | [11:4]        | ALLO/ALL1 |

| Lane-2  | SoT      | PH                             | Pix_2&3 | Pix_9     |          | Pix_3897      | Pix_3902      | EoT       |

| Lane-2  | 00011101 | 101 WC[7:0] [3:0]x2 [11:4]     |         | [11:4]    | [11:4]   | ALLO/ALL1     |               |           |

| lana 1  | SoT      | PH                             | Pix_3   | Pix_8     |          | Pix_3896      | Pix_3900&3901 | EoT       |

| Lane-1  | 00011101 | DI[7:0]                        | [11:4]  | [11:4]    | 19799    | [11:4]        | [3:0]x2       | ALLO/ALL1 |

Figure 34 UHD RAW12 (8-lane)

Figure 35 UHD RAW12 (4-lane)

#### 5. Sensor Control

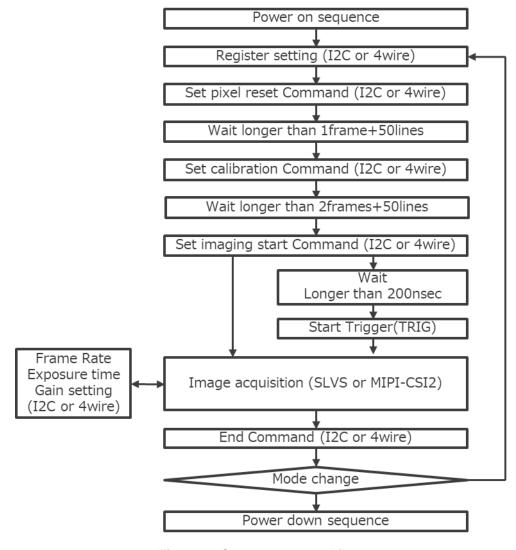

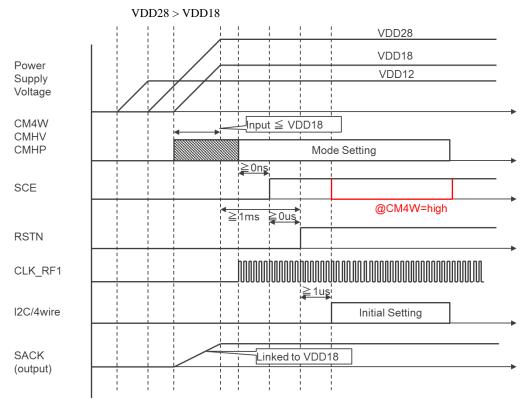

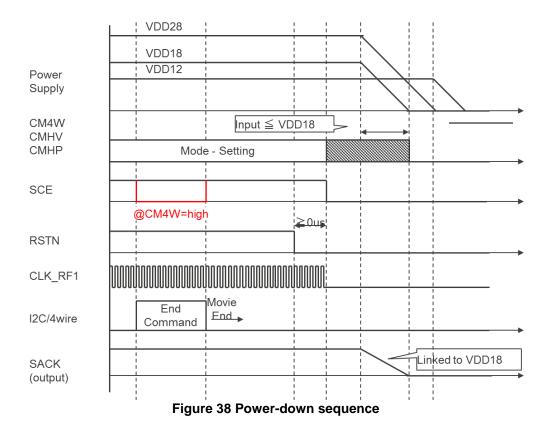

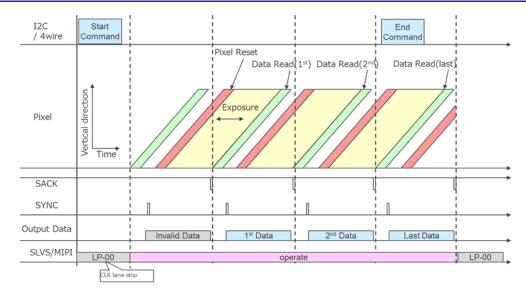

### 5.1 Sequence

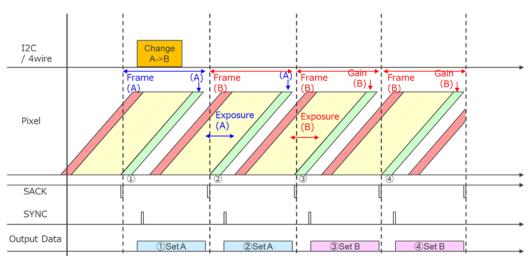

Sequence control flow of this device is shown in Figure 36. Figure 37 and Figure 38 shows the power-up and power-down sequence, respectively. Be careful that the output voltage of SACK will follow VDD18, because the power supply of the output buffer is 1.8V power supply voltage. All registers should be written from front to back at the initial power-up sequence. In case of Control Pin CM4W = Low (I2C fast mode / fast mode plus), SCE should keep High drawn by the black lines in Figure 37 and Figure 38 during the serial communication (I2C). In case of Control Pin CM4W = High (4-wire), SCE should become Low drawn by the red lines in Figure 37 and Figure 38 during the serial communication (4-wire). In case of mode change with the output frequency's change, RSTN should be set to Low before register setting (I2C or 4wire).

Table 26 describes the wait time to run Start command after setting all registers. Please take care of the necessary wait time which depends on the serial communication mode. Major registers relating image acquisitions (Frame rate, Exposure time, Gain) should not be changed during the imaging operation.

Figure 36 Sequence control flow

Table 26 Wait time between the end of register setting and start command

| Serial communication mode | Frequency | Register write time | Wait time |  |

|---------------------------|-----------|---------------------|-----------|--|

| I2C fast mode             | 400kHz    | 20.6 ms             | 0.0ms     |  |

| I2C fast mode plus        | 1.0MHz    | 8.3 ms              | 8.0ms     |  |

| 4-wire                    | 10MHz     | 0.8 ms              | 13.9ms    |  |

Figure 37 Power-up sequence

Figure 39 Data acquisition

Figure 40 Setting sequence of movie

# **Table 27 Register setting**

| Register setting            | Setting<br>sequence of<br>movie | Latency from the register setting | Constraint                                                                              |  |  |  |

|-----------------------------|---------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------|--|--|--|

| Frame Rate                  | Support                         | After 2frame data                 | Write once at burst mode.                                                               |  |  |  |

| Exposure Time               | Support                         | After 2frame data                 | 2. Don't write registers while SACK = low.     3. Don't write registers during the next |  |  |  |

| Gain                        | Support                         | After 2frame data                 | frame after Gain Setting was changed.                                                   |  |  |  |

| HDR: ON/OFF                 | Not support                     | -                                 |                                                                                         |  |  |  |

| Output Rate(891/445.5 Mbps) | Not support                     | -                                 |                                                                                         |  |  |  |

| Output Lane( 8/4 lane )     | Not support                     | -                                 | Hardware reset and initial settings are required                                        |  |  |  |

| Format(SLVS / MIPI )        | Not support                     | -                                 | Toquitou                                                                                |  |  |  |

| Other                       | Not support                     | -                                 |                                                                                         |  |  |  |

## 5.2 Register Setting

The commonly used registers are introduced in this section.

#### **5.2.1 OPECODE**

OPECODE is short for Operation-code.

#### **Table 28 OPECODE**

| OPECODE                      | State transition | Note                              |

|------------------------------|------------------|-----------------------------------|

| Start command (self-mode)    | Movie start      |                                   |

| Start command (Trigger-mode) | Ready mode       | Movie start when TRIG is asserted |

| End command                  | Movie end        |                                   |

| Pixel reset command          | Idle             |                                   |

| Calibration command          | Idle             |                                   |

## 5.2.2 Frame Rate Setting

It is possible to set arbitrary frame rate by setting VBLANK period and the exposure time.

- Minimum frame rate = 1fps

- Maximum frame rate = 60fps (Refer Table 24)

# 5.2.3 Exposure Time Setting

Figure 41 indicates long exposure time and short exposure time for HDR, compared with non-HDR. X-axis is time and Y-axis is horizontal line number of the pixel array. The formula filled in Table 29 explains the possible setting of the exposure time, which will be set by the register "1H\_width".

Figure 41 Exposure time

# **Table 29 Exposure time**

1H\_width: internal period (7.22us/14.4us)

|      | Normal                | HDR @ long             | HDR @ short  |

|------|-----------------------|------------------------|--------------|

| Max  | 1 frame – 8 x1H_width | 1 frame – 66 x1H_width | 44 x1H_width |

| Min  | 4 x1H_with            | 7 x1H_with             | 7 x1H_with   |

| Step | 1H_width              | 1H_width               | 1H_width     |

### 5.2.4 Gain Setting

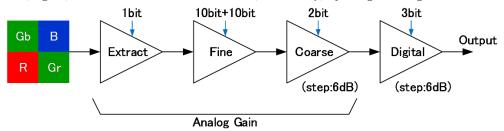

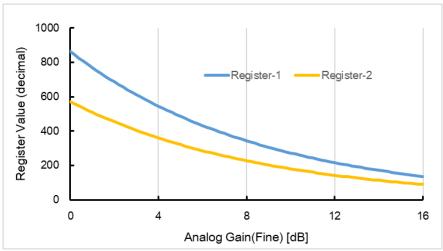

Block diagram (Figure 42) and Gain setting table (Table 30) summarizes how users can set their arbitrary gain.

- Analog Gain (Extract): 1bit register is assigned to select 0dB or 2.44dB.

- Analog Fine Gain (Fine): Two sets of 10bits registers setting provide fine tuning as shown in Figure 44.

- Analog Gain (Coarse): Can be selected 0dB to 12.04dB (6.02dB step) by using 2bits registers.

- Digital Gain (Digital): Can be selected 0dB to 24.08dB (6.02dB step) by using 3bits registers.

Figure 42 Gain diagram

Table 30 Recommended gain setting (Estimated)

| No | Total Gain        | Analog Gair | Analog Gain |                  |              |  |  |  |

|----|-------------------|-------------|-------------|------------------|--------------|--|--|--|

| NO | Total Gain        | Extra       | Coarse      | Fine             | Digital Gain |  |  |  |

| Α  | 0.00dB ~ 2.44dB   | 0.00dB      |             | 0.00dB ~ 2.44dB  |              |  |  |  |

| В  | 2.44dB ~ 6.02dB   |             | 0.00dB      | 0.00dB ~ 3.58dB  | 0.0040       |  |  |  |

| С  | 6.02dB ~ 12.04dB  |             |             |                  |              |  |  |  |

| D  | 12.04dB ~ 18.06dB | 6.02dB      |             | 3.58dB ~ 9.60dB  | 0.00dB       |  |  |  |

| Е  | 18.06dB ~ 24.08dB |             |             |                  | _            |  |  |  |

| F  | 24.08dB ~ 30.11dB | 2.44dB      |             |                  |              |  |  |  |

| G  | 30.11dB ~ 36.13dB |             | 12 04dB     |                  | 6.02dB       |  |  |  |

| Н  | 36.13dB ~ 42.15dB |             | 12.04dB     | 9.60dB ~ 15.63dB | 12.04dB      |  |  |  |

| 1  | 42.15dB ~ 48.17dB |             |             |                  | 18.06dB      |  |  |  |

| J  | 48.17dB ~ 54.19dB |             |             |                  | 24.08dB      |  |  |  |

Figure 43 Example of analog gain setting (Fine)

## 5.3. Serial Communication

There are three types of serial communication modes, I2C fast mode, I2C fast mode plus and 4-wire (Table 31). Each mode can be selected by control pins (CM4W, CMHP and CMHV).

**Table 31 Hardware control of serial communication**

| Serial         |        |      | e control<br>D, high=VDD18) |      | Condition | on of CB          | Data control |                                 |  |

|----------------|--------|------|-----------------------------|------|-----------|-------------------|--------------|---------------------------------|--|

| mode           | mode   | CM4W | CMHP CMHV                   |      | 1.8V      | VDI @ typ<br>2.5V | 3.3V         | sensor control<br>Write (/Read) |  |

| I2C            | Normal |      | Low                         | Low  | Any       | <300pF            | <200pF       |                                 |  |

| fast-mode      | High   | Low  | Low                         | High | -         | >300pF            | >200pF       | I2C                             |  |

| I2C            | Normal | Low  | Lliab                       | Low  | Any       | <300pF            | <200pF       | 120                             |  |

| fast-mode plus | High   |      | High                        | High | -         | >300pF            | >200pF       |                                 |  |

| 4-wire         | -      | High | Low                         | Low  | -         | -                 | -            | 4wire                           |  |

Table 32 Serial communication setting and control