#### **General Description**

Operating from a 2.7 V to 5.5 V power supply, the SLG59H1342C is a self-powered, high-performance, 70 m $\Omega$  nFET load switch designed for high-side power-rail applications up to 1.5 A. When ON, internal reverse-current protection will quickly open the switch in the event of a reverse-voltage condition is detected (a  $V_{OUT} > V_{IN} + 50$  mV condition opens the switch). When OFF, an internal back-to-back reverse-current blocking circuit prevents reverse path leakage current.

#### **Features**

- Integrated 1.5 A Continuous I<sub>DS</sub> nFET Load Switch

- Integrated Low RDS<sub>ON</sub> nFET switch: 70 mΩ

- Input Voltage: 2.7 V to 5.5 V

- Operating Temperature: -40 °C to 85 °C

- Resistor-adjustable Active Current Limit

- ±10% accuracy for 0.27 A to 1.81 A Current Limit Thresholds

- ±15% accuracy for < 0.27 A Current Limit Thresholds

- Open Drain FLT Signaling

- · Input Over-Voltage Protection

- Absolute V<sub>IN</sub> maximum voltage rating: 28 V<sub>DC</sub>

- Over-temperature Protection

- · Under-Voltage Lockout

- · True Reverse-Current Blocking

- · Active Low ON signal control

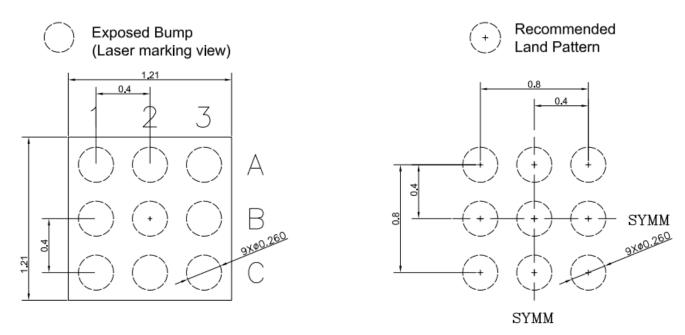

- Low  $\theta_{JA}$ , 9-pin 1.21 mm x 1.21 mm, 0.4 mm pitch 9L WLCSP Packaging

- · Pb-Free / Halogen-Free / RoHS compliant

#### **Pin Configuration**

Pin A1 Index Mark

1 2 3

A'OUT' (GND) (IN)

B (OUT) (GND) (IN)

**9L WLCSP** (Laser Marking View)

#### **Applications**

- · Fast Turn On/Off power rail switching

- · Frequent wake & sleep power cycle

- · Mobile devices and portable devices

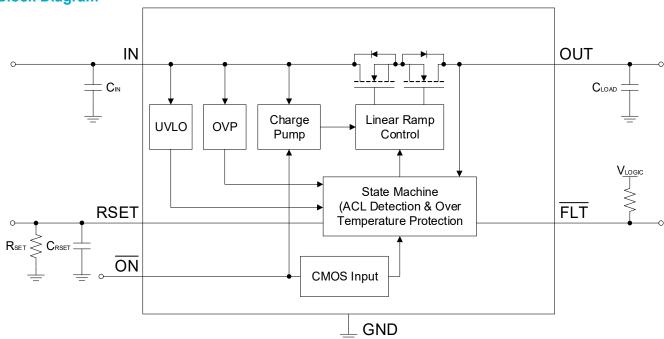

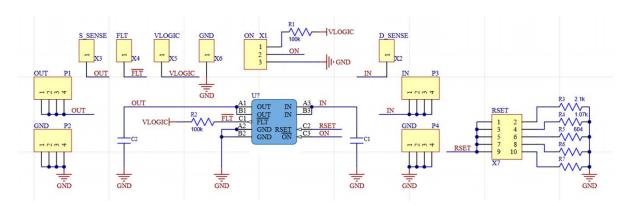

## **Block Diagram**

## SLG59H1342C

A Reverse Blocking 70 m $\Omega$ , 1.5 A nFET Load Switch in 1.46 mm $^2$  WLCSP

## **Pin Description**

| Pin#   | Pin Name | Type   | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, B1 | OUT      | MOSFET | Output terminal connection of the n-channel MOSFET. Capacitors used at OUT should be rated at a voltage higher than maximum input voltage ever present.                                                                                                                                                                                                                                                         |

| A2, B2 | GND      | GND    | Ground connection. Connect this pin to system analog or power ground plane.                                                                                                                                                                                                                                                                                                                                     |

| A3, B3 | IN       | MOSFET | Input terminal connection of the n-channel MOSFET. Capacitors used at IN should be rated at a voltage higher than maximum input voltage ever present.                                                                                                                                                                                                                                                           |

| C1     | FLT      | Output | An open drain output, FLT is asserted within TFLT <sub>LOW</sub> when a current-limit condition is detected.                                                                                                                                                                                                                                                                                                    |

| C2     | RSET     | Input  | A 1%-tolerance, metal-film resistor between 6.49 k $\Omega$ and 604 $\Omega$ sets the SLG59H1342C's active current limit. A 6.49 k $\Omega$ resistor sets the SLG59H1342C's active current limit to 0.16 A and a 604 $\Omega$ resistor sets the active current limit to 1.81 A. In addition, it is recommended to bypass the RSET pin to GND with a 10 pF capacitor.                                            |

| C3     | ŌN       | Input  | A high-to-low transition on this pin initiates the operation of the SLG59H1342C. ON is an asserted LOW, level-sensitive CMOS input with ON_V <sub>IL</sub> < 0.65 V and ON_V <sub>IH</sub> > 1.15 V. While there is an internal pull-down circuit to GND (~14 M $\Omega$ ), connect this pin directly to a general-purpose output (GPO) of a microcontroller, an application processor, or a system controller. |

### **Ordering Information**

| Part Number   | Туре                     | Production Flow             |

|---------------|--------------------------|-----------------------------|

| SLG59H1342C   | WLCSP 9L                 | Industrial, -40 °C to 85 °C |

| SLG59H1342CTR | WLCSP 9L (Tape and Reel) | Industrial, -40 °C to 85 °C |

#### **Absolute Maximum Ratings**

| Parameter                | Description                                           | Conditions                                                                                                                              | Min. | Тур. | Max. | Unit |

|--------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>IN</sub>          | Power Switch Input Voltage                            |                                                                                                                                         |      |      | 28   | V    |

| V <sub>OUT</sub> to GND  | Power Switch Output Voltage to GND                    | Continuous                                                                                                                              | -0.3 |      | 6    | V    |

| ON, FLT, RSET to GND     | ON, FLT, and RSET Pin<br>Voltages to GND              |                                                                                                                                         | -0.3 |      | 6    | V    |

| T <sub>S</sub>           | Storage Temperature                                   |                                                                                                                                         | -65  |      | 140  | °C   |

| ESD <sub>HBM</sub>       | ESD Protection                                        | Human Body Model                                                                                                                        | 2000 | -    |      | V    |

| ESD <sub>CDM</sub>       | ESD Protection                                        | Charged Device Model                                                                                                                    | 1000 |      |      | V    |

| ESD <sub>SYS</sub>       | IEC 61000-4-2 System ESD                              | Air Gap (V <sub>IN</sub> , V <sub>OUT</sub> , V <sub>ON</sub> to GND)                                                                   | 15   |      |      | kV   |

| ESDSYS                   | 1EC 01000-4-2 System ESD                              | Contact (V <sub>IN</sub> , V <sub>OUT</sub> , V <sub>ON</sub> to GND)                                                                   | 8    |      |      | kV   |

| MSL                      | Moisture Sensitivity Level                            |                                                                                                                                         |      | 1    | 1    |      |

| $\theta_{JA}$            | Package Thermal<br>Resistance,<br>Junction-to-Ambient | 1.21 x 1.21 mm 9L WLCSP; Determined using a 0.5 in <sup>2</sup> , 1 oz. copper pad under each IN and OUT terminal and FR4 pcb material. |      | 76   |      | °C/W |

| MOSFET IDS <sub>PK</sub> | Peak Current from IN to OUT                           | Maximum pulsed switch current, pulse width < 1 ms, 1% duty cycle                                                                        |      |      | 2.1  | Α    |

Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Electrical Characteristics**

Typical values are at  $V_{IN}$  = 5 V,  $C_{IN}$  = 1  $\mu$ F,  $C_{LOAD}$  = 1  $\mu$ F, and  $T_A$  = 25 °C. Min/Max values are  $T_A$  = -40 °C to 85 °C; unless otherwise noted.

| Parameter                | Description                                       | Conditions                                                                                  | Min. | Тур. | Max. | Unit |

|--------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>IN</sub>          | Power Switch Input Voltage                        | -40 °C to 85 °C                                                                             | 2.7  |      | 5.5  | V    |

| V                        | V <sub>IN</sub> Undervoltage Lockout              | V <sub>IN</sub> ↑                                                                           |      | 2.45 |      | V    |

| V <sub>IN(UVLO)</sub>    | Threshold                                         | V <sub>IN</sub> ↓                                                                           |      | 2.25 |      | V    |

| V                        | V <sub>IN</sub> Overvoltage Lockout               | V <sub>IN</sub> ↑                                                                           | 5.4  | 5.6  | 5.8  | V    |

| V <sub>IN(OVP)</sub>     | Threshold                                         | V <sub>IN</sub> ↓                                                                           |      | 5.3  |      | V    |

| V <sub>IN(OVP)_HYS</sub> | V <sub>IN</sub> Overvoltage Lockout<br>Hysteresis | V <sub>IN</sub> ↓                                                                           |      | 300  |      | mV   |

| t <sub>OVP</sub>         | OVP Response Time                                 | $V_{IN}$ step from 5.5 V to 6 V;<br>$I_{DS}$ = 0.5 A, $C_{LOAD}$ = 1 $\mu$ F; $T_A$ = 25 °C | 1    |      | 10   | μs   |

| I <sub>IN</sub>          | Power Switch Current (Pin A3, B3)                 | When OFF, No load; V <sub>OUT</sub> = Open;<br>V <sub>ON</sub> = 5 V                        |      | 0.5  | 2    | μA   |

|                          | , , ,                                             | When ON, No load                                                                            |      | 80   | 115  | μA   |

| I <sub>ON_LKG</sub>      | ON Pin Input Leakage                              | V <sub>ON</sub> = 0 V to 5 V                                                                |      |      | 1    | μA   |

## **Electrical Characteristics (continued)**

Typical values are at  $V_{IN}$  = 5 V,  $C_{IN}$  = 1  $\mu$ F,  $C_{LOAD}$  = 1  $\mu$ F, and  $T_A$  = 25 °C. Min/Max values are  $T_A$  = -40 °C to 85 °C; unless otherwise noted.

| Parameter                 | Description                                    | Conditions                                                                                                                                                                                               | Min. | Тур. | Max. | Unit |

|---------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                           |                                                | V <sub>IN</sub> = 3.0 V, I <sub>DS</sub> = 0.5 A                                                                                                                                                         |      | 90   |      | mΩ   |

|                           |                                                | V <sub>IN</sub> = 3.5 V, I <sub>DS</sub> = 0.5 A                                                                                                                                                         |      | 80   |      | mΩ   |

|                           |                                                | V <sub>IN</sub> = 3.7 V, I <sub>DS</sub> = 0.5 A                                                                                                                                                         |      | 75   | 105  | mΩ   |

| RDS <sub>ON</sub>         | ON Resistance                                  | V <sub>IN</sub> = 4.0 V, I <sub>DS</sub> = 0.5 A                                                                                                                                                         |      | 75   |      | mΩ   |

|                           |                                                | V <sub>IN</sub> = 4.5 V, I <sub>DS</sub> = 0.5 A                                                                                                                                                         | -    | 75   |      | mΩ   |

|                           |                                                | V <sub>IN</sub> = 5.0 V, I <sub>DS</sub> = 0.5 A                                                                                                                                                         | -    | 70   | 100  | mΩ   |

|                           |                                                | V <sub>IN</sub> = 5.5 V, I <sub>DS</sub> = 0.5 A                                                                                                                                                         |      | 70   |      | mΩ   |

| MOSFET IDS                | Current from IN to OUT                         | Continuous                                                                                                                                                                                               |      |      | 1.5  | Α    |

|                           | Active Current Limit I                         | $V_{IN}$ = 5 V; $R_{SET}$ = 2.1 k $\Omega$ ; $C_{IN}$ = 30 $\mu$ F; $C_{RSET}$ = 10 pF; $V_{OUT}$ > 1.68 V; $C_{LOAD}$ = 1 $\mu$ F                                                                       | 0.47 | 0.52 | 0.57 | А    |

| I <sub>LIMIT</sub>        | Active Current Limit, I <sub>ACL</sub>         | $\begin{aligned} &V_{IN} = 5 \text{ V; } R_{SET} = 1.07 \text{ k}\Omega; C_{IN} = 30 \mu\text{F;} \\ &C_{RSET} = 10 \text{ pF; } V_{OUT} > 1.68 \text{ V;} \\ &C_{LOAD} = 4.4 \mu\text{F} \end{aligned}$ | 0.92 | 1.02 | 1.12 | Α    |

| T <sub>ACL</sub>          | Active Current Limit Response Time             | I <sub>DS</sub> > I <sub>ACL</sub> , V <sub>OUT</sub> ≤ V <sub>IN</sub>                                                                                                                                  |      | 7    |      | μs   |

| T <sub>HACL</sub>         | Hard Active Current Limit Response Time        | I <sub>DS</sub> > I <sub>ACL</sub> , V <sub>OUT</sub> = 0 V                                                                                                                                              |      | 6    |      | μs   |

| I <sub>FET_OFF</sub>      | MOSFET OFF Leakage Current                     | V <sub>ON</sub> = 5.5 V; V <sub>OUT</sub> = 0 V, V <sub>IN</sub> = 5.5 V                                                                                                                                 | 1    | 0.5  | 4    | μA   |

| V <sub>RVD_T</sub>        | Reverse-voltage Detect Threshold Voltage       | V <sub>OUT</sub> – V <sub>IN</sub> ;                                                                                                                                                                     |      | 50   |      | mV   |

| T <sub>RVD_T</sub>        | Reverse-voltage Detect Threshold Response Time |                                                                                                                                                                                                          |      | 2    |      | μs   |

| V <sub>RVD_HYS</sub>      | Reverse-voltage Detect Hysteresis              |                                                                                                                                                                                                          | 1    | 50   |      | mV   |

| I <sub>REVERSE</sub>      | MOSFET Reverse Leakage Current                 | V <sub>IN</sub> = 0 V, ON = HIGH,<br>V <sub>OUT</sub> = 5.5 V                                                                                                                                            | -    | 10   |      | μA   |

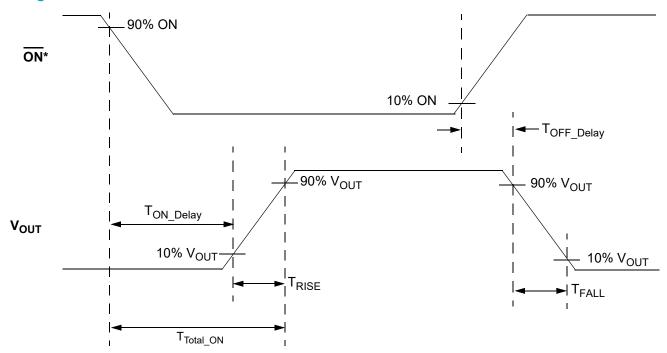

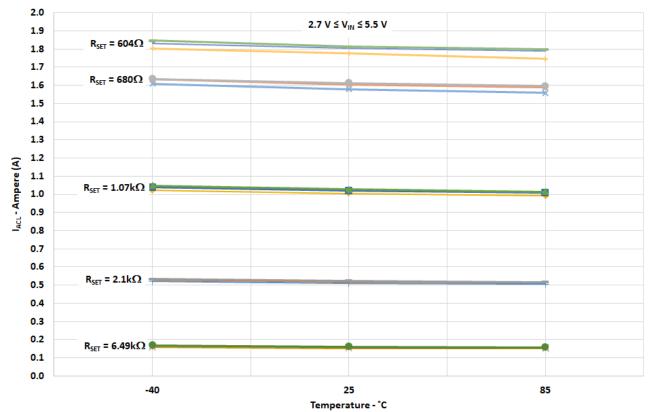

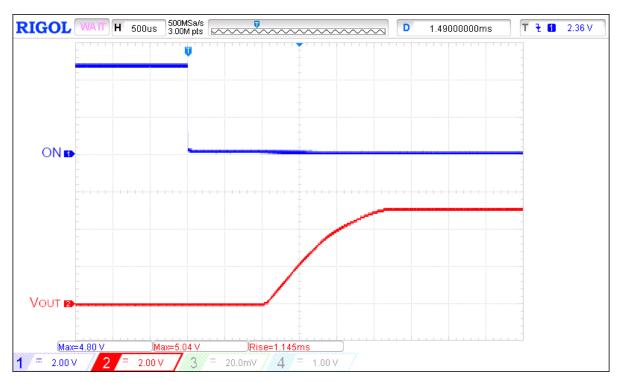

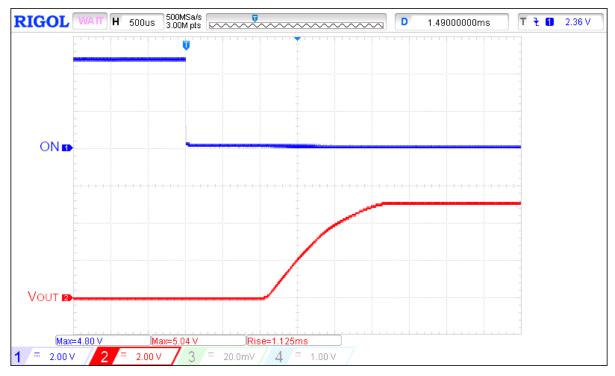

| T <sub>ON_Delay</sub>     | ON Delay Time                                  | 90% ON to 10% $V_{OUT} \uparrow$ ;<br>$V_{IN} = 5 \text{ V}$ ; $R_{LOAD} = 100 \Omega$ ,<br>$C_{LOAD} = 1 \mu\text{F}$                                                                                   | -    | 1.1  |      | ms   |

| T <sub>Total_ON</sub>     | Total Turn ON Time                             | 90% ON to 90% $V_{OUT} \uparrow$ ;<br>$V_{IN} = 5 V$ ; $R_{LOAD} = 100 \Omega$ ,<br>$C_{LOAD} = 1 \mu F$                                                                                                 | -    | 2.2  |      | ms   |

| T <sub>RISE</sub>         | V <sub>OUT</sub> Rise Time                     | 10% $V_{OUT}$ to 90% $V_{OUT}$ ↑;<br>$V_{IN}$ = 5 V; $R_{LOAD}$ = 100 Ω,<br>$C_{LOAD}$ = 1 μF                                                                                                            |      | 1.1  |      | ms   |

| T <sub>OFF_Delay</sub>    | OFF Delay Time                                 | 10% ON to 90% $V_{OUT}\downarrow$ ;<br>$V_{IN}$ = 5 V; $R_{LOAD}$ = 100 $\Omega$ ,<br>$C_{LOAD}$ = 1 $\mu F$                                                                                             | -    | 10   |      | μs   |

| T <sub>FALL</sub>         | V <sub>OUT</sub> Fall Time                     | 90% $V_{OUT}$ to 10% $V_{OUT}$ ;<br>ON = LOW-to-HIGH; $V_{IN}$ = 5 V;<br>$R_{LOAD}$ = 100 $\Omega$ , $C_{LOAD}$ = 1 $\mu F$                                                                              |      | 250  |      | μs   |

| TFLT <sub>LOW</sub>       | FLT Assertion Time                             | Abnormal Step Load Current event to FLT ↓;                                                                                                                                                               | -    | 8    |      | ms   |

| FLT <sub>VOL</sub>        | FLT Output Low Voltage                         | I <sub>SINK</sub> = 10 mA; V <sub>IN</sub> = 5 V;                                                                                                                                                        | -    | 0.1  | 0.2  | V    |

| ' L'VOL                   | 1 Li Output Low Voltage                        | I <sub>SINK</sub> = 10 mA; V <sub>IN</sub> = 3.5 V;                                                                                                                                                      | -    | 0.15 | 0.3  | V    |

| I <del>FLT</del> _Leakage | FLT Output High Leakage Current                | V <sub>IN</sub> = 5 V; Switch is in On state                                                                                                                                                             | -    |      | 1    | μA   |

#### **Electrical Characteristics (continued)**

Typical values are at  $V_{IN}$  = 5 V,  $C_{IN}$  = 1  $\mu$ F,  $C_{LOAD}$  = 1  $\mu$ F, and  $T_A$  = 25 °C. Min/Max values are  $T_A$  = -40 °C to 85 °C; unless otherwise noted.

| Parameter          | Description                             | Conditions                       | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------------------------|----------------------------------|------|------|------|------|

| ON_V <sub>IH</sub> | High Input Voltage on ON pin            | V <sub>IN</sub> = 2.7 V to 5.5 V | 1.15 |      |      | V    |

| ON_V <sub>IL</sub> | Low Input Voltage on ON pin             | V <sub>IN</sub> = 2.7 V to 5.5 V | -0.3 | 0    | 0.65 | V    |

| THERMON            | Thermal Protection Shutdown Threshold   |                                  |      | 150  |      | °C   |

| THERMOFF           | Thermal Protection Restart<br>Threshold |                                  |      | 130  |      | °C   |

#### **Timing Parameter Details**

\*Rise and Fall Times of the ON Signal are 100 ns

### **Typical Performance Characteristics**

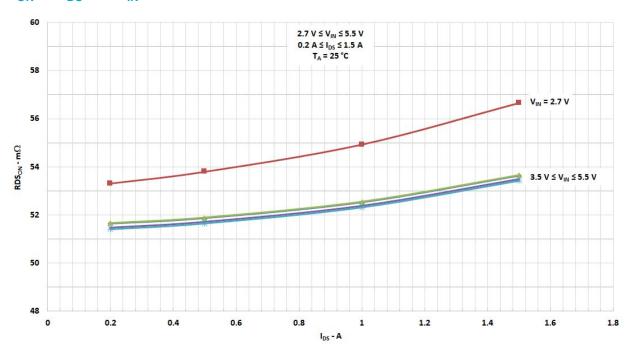

## $RDS_{ON}$ vs. $I_{DS}$ and $V_{IN}$

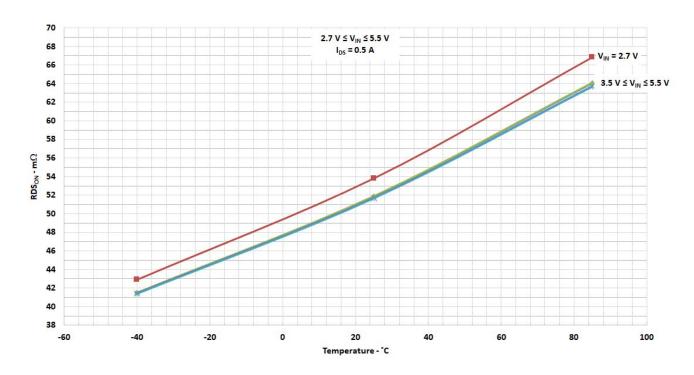

### RDS<sub>ON</sub> vs. Temperature and V<sub>IN</sub>

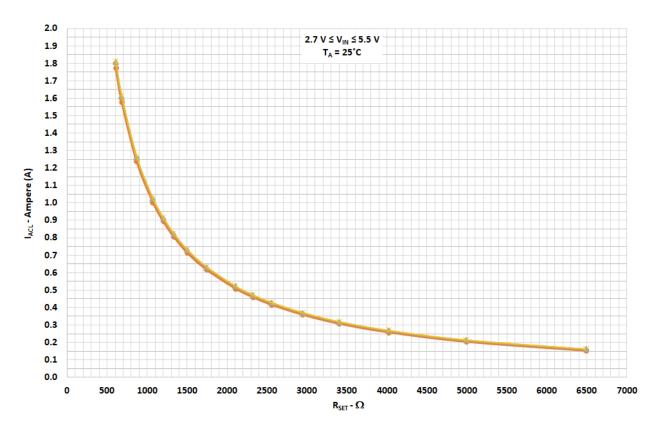

## $I_{\mbox{\scriptsize ACL}}$ vs. $R_{\mbox{\scriptsize SET}}$ and $V_{\mbox{\scriptsize IN}}$

$I_{ACL}$  vs. Temperature,  $V_{IN}$ , and  $R_{SET}$

A Reverse Blocking 70 mΩ, 1.5 A nFET Load Switch in 1.46 mm<sup>2</sup> WLCSP

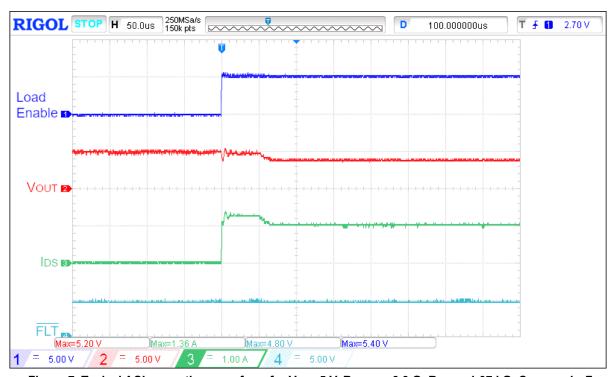

#### **Typical Turn ON Operation Waveforms**

Figure 1. Typical Turn ON operation waveform for V  $_{IN}$  = 5 V,  $R_{LOAD}$  = 100  $\Omega,\,C_{LOAD}$  = 1  $\mu F$

Figure 2. Typical Turn ON operation waveform for  $V_{IN}$  = 5 V,  $R_{LOAD}$  = 100  $\Omega$ ,  $C_{LOAD}$  = 4.4  $\mu F$

A Reverse Blocking 70 mΩ, 1.5 A nFET Load Switch in 1.46 mm<sup>2</sup> WLCSP

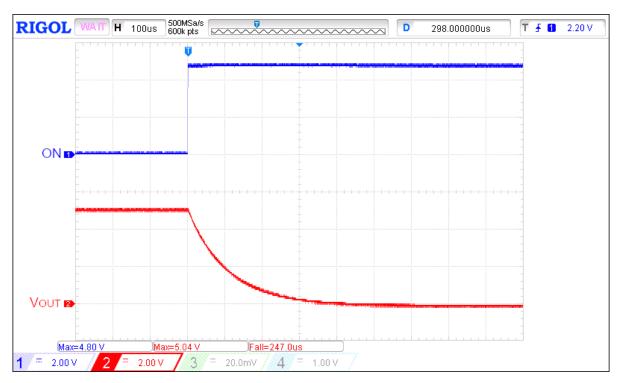

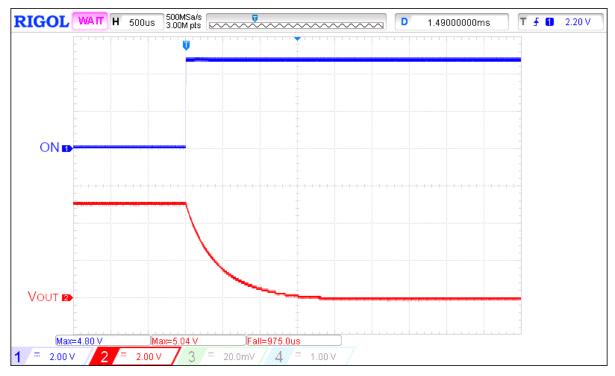

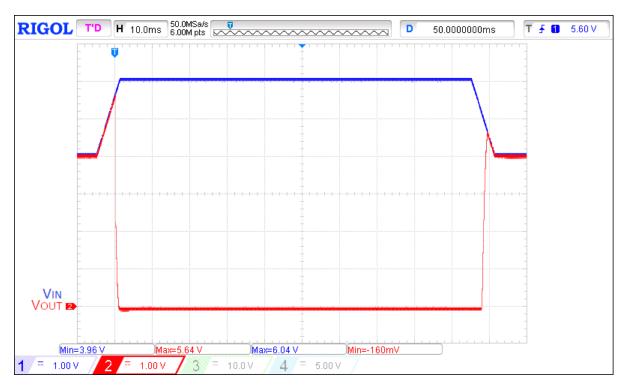

#### **Typical Turn OFF Operation Waveforms**

Figure 3. Typical Turn OFF operation waveform for V<sub>IN</sub> = 5 V, R<sub>LOAD</sub> = 100  $\Omega$ , C<sub>LOAD</sub> = 1  $\mu$ F

Figure 4. Typical Turn OFF operation waveform for  $V_{IN}$  = 5 V,  $R_{LOAD}$  = 100  $\Omega$ ,  $C_{LOAD}$  = 4.4  $\mu F$

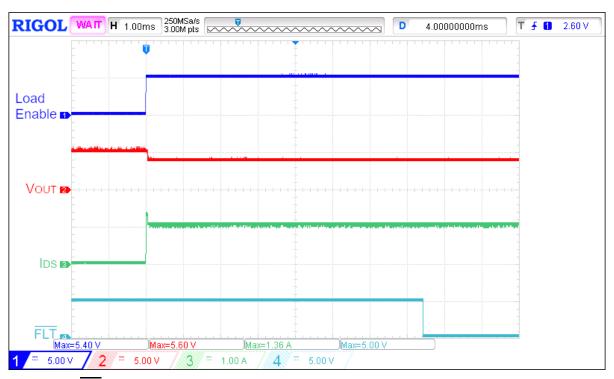

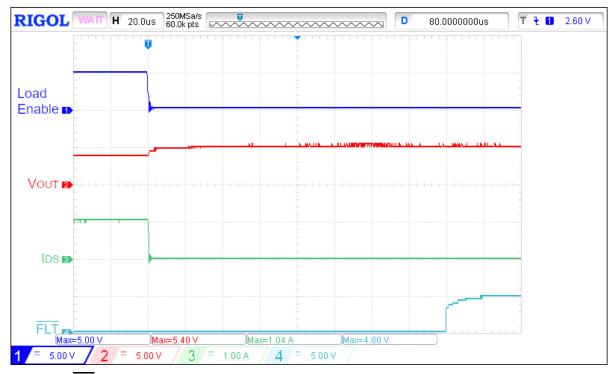

## **Typical FLT Operation Waveforms**

Figure 5.  $\overline{FLT}$  assertion operation waveform for  $V_{IN}$  = 5 V,  $R_{LOAD}$  = 4  $\Omega$ ,  $R_{SET}$  = 1.07 k $\Omega$ ,  $C_{LOAD}$  = 1  $\mu F$

Figure 6. FLT de-assertion operation waveform for  $V_{IN}$  = 5 V,  $R_{LOAD}$  = 4  $\Omega$ ,  $R_{SET}$  = 1.07 k $\Omega$ ,  $C_{LOAD}$  = 1  $\mu F$

#### **Typical ACL Operation Waveforms**

Figure 7. Typical ACL operation waveform for V $_{IN}$  = 5 V, R $_{LOAD}$  = 3.9  $\Omega$ , R $_{SET}$  = 1.07 k $\Omega$ , C $_{LOAD}$  = 1  $\mu F$

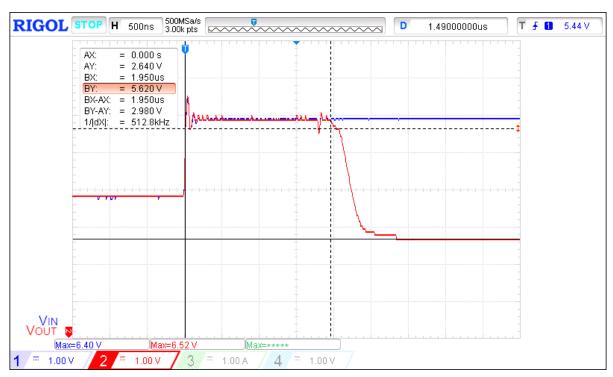

#### **Typical OVP Operation Waveforms**

Figure 8. OVP Response operation waveform for V<sub>IN</sub> step from 4 V to 6 V, no R<sub>LOAD</sub>, no C<sub>LOAD</sub>

Figure 9. Typical Overvoltage Protection operation waveform for  $V_{IN}$  step from 4 V to 6 V to 4 V, no  $R_{LOAD}$ , no  $C_{LOAD}$

A Reverse Blocking 70 mΩ, 1.5 A nFET Load Switch in 1.46 mm<sup>2</sup> WLCSP

#### SLG59H1342C Current Limiting Operation

After power up the output current is initially limited to the Active Current Limit ( $I_{ACL}$ ) specification listed in the Electrical Characteristics table. The ACL monitor's response time is very fast and is triggered within a few microseconds to sudden (transient) changes in load current. When a load current overload is detected, the ACL monitor increases the FET resistance to keep the current from exceeding the power switch's  $I_{ACL}$  threshold. During active current-limit operation,  $V_{OUT}$  is also reduced by  $I_{ACL}$  x RDS $_{ON(ACL)}$ .

When a current-limit event is detected, the  $\overline{\text{FLT}}$  signal becomes asserted in approximately  $\overline{\text{TFLT}}_{\text{LOW}}$  and the SLG59H1342C operates in constant current mode with the output current set by  $R_{\text{SET}}$  (see  $R_{\text{SET}}$ -Current Limit Table). The SLG59H1342C continues to operate in constant current mode indefinitely until the current-limit event has elapsed.

#### SLG59H1342C FLT Operation

As previously stated in the Pin Description section, the <u>open-drain FLT</u> output is asserted when an active-c<u>urrent limit (ACL)</u> condition is detected. Th<u>is output</u> becomes as<u>serted</u> in TFLT<sub>LOW</sub> upon the detection of a fault condition. If the <u>ON</u> pin is toggled LOW-to-HIGH while the <u>FLT</u> output is low, the <u>FLT</u> output is deasserted without delay.

#### Setting the SLG59H1342C Output Current Limit with R<sub>SET</sub>

The current-limit operation of the SLG59H1342C begins by choosing the appropriate  $\pm 1\%$ -tolerance R<sub>SET</sub> value for the application. The recommended range for R<sub>SET</sub> is:

$$6.49 \text{ k}\Omega \ge R_{\text{SET}} \ge 604 \Omega$$

which corresponds to an output constant current limit in the following range:

$$0.16 \text{ A} \le I_{ACL} \le 1.81 \text{ A}$$

Table 1: Setting Current Limit Threshold vs.  $R_{SET}$ ,  $C_{IN}$  = 30  $\mu$ F,  $C_{RSET}$  = 10 pF

| R <sub>SET</sub> (Ω) | Min.<br>Current<br>Limit (A) | Typ.<br>Current<br>Limit (A) | Max.<br>Current<br>Limit (A) | Recommended<br>Max. C <sub>LOAD</sub> (μF) |

|----------------------|------------------------------|------------------------------|------------------------------|--------------------------------------------|

| 604                  | 1.63                         | 1.81                         | 1.99                         | 220                                        |

| 680                  | 1.45                         | 1.61                         | 1.77                         | 220                                        |

| 866                  | 1.13                         | 1.26                         | 1.39                         | 220                                        |

| 1070                 | 0.92                         | 1.02                         | 1.12                         | 220                                        |

| 1200                 | 0.82                         | 0.91                         | 1.00                         | 220                                        |

| 1330                 | 0.74                         | 0.82                         | 0.90                         | 220                                        |

| 1500                 | 0.66                         | 0.73                         | 0.80                         | 220                                        |

| 1740                 | 0.57                         | 0.63                         | 0.69                         | 220                                        |

| 2100                 | 0.47                         | 0.52                         | 0.57                         | 220                                        |

| 2320                 | 0.42                         | 0.47                         | 0.52                         | 10                                         |

| 2550                 | 0.38                         | 0.43                         | 0.47                         | 4.4                                        |

| 2940                 | 0.33                         | 0.37                         | 0.41                         | 2.2                                        |

| 3400                 | 0.29                         | 0.32                         | 0.35                         | 2.2                                        |

| 4020                 | 0.24                         | 0.27                         | 0.30                         | 1                                          |

| 4990                 | 0.18                         | 0.21                         | 0.24                         | 1                                          |

| 6490                 | 0.13                         | 0.16                         | 0.19                         | 0.47                                       |

## A Reverse Blocking 70 mΩ, 1.5 A nFET Load Switch in 1.46 mm<sup>2</sup> WLCSP

#### **Power Dissipation Considerations**

The junction temperature of the SLG59H1342C depends on factors such as board layout, ambient temperature, external air flow over the package, load current, and the RDS<sub>ON</sub> generated voltage drop across each power MOSFET. While the primary contributor to the increase in the junction temperature of the SLG59H1342C is the power dissipation of its power MOSFETs, its power dissipation and the junction temperature in nominal operating mode can be calculated using the following equations:

$$PD_{TOTAL} = RDS_{ON} \times I_{DS}^{2}$$

where:

$\mbox{PD}_{\mbox{TOTAL}}$  = Total package power dissipation, in Watts (W)  $\mbox{RDS}_{\mbox{ON}}$  = Power MOSFET ON resistance, in Ohms ( $\Omega$ )  $\mbox{I}_{\mbox{DS}}$  = Output current, in Amps (A) and

$$T_J = PD_{TOTAL} \times \theta_{JA} + T_A$$

where:

T<sub>J</sub> = Die junction temperature, in Celsius degrees (°C)

$\theta_{JA}$  = Package thermal resistance, in Celsius degrees per Watt (°C/W) – highly dependent on pcb layout

T<sub>A</sub> = Ambient temperature, in Celsius degrees (°C)

In nominal operating mode, the SLG59H1342C's power dissipation can also be calculated by taking into account the voltage drop across the switch ( $V_{IN}$  -  $V_{OUT}$ ) and the magnitude of the switch's output current ( $I_{DS}$ ):

$$PD_{TOTAL} = (V_{IN} - V_{OUT}) \times I_{DS}$$

or  $PD_{TOTAL} = (V_{IN} - (R_{LOAD} \times I_{DS})) \times I_{DS}$

where:

PD<sub>TOTAL</sub> = Total package power dissipation, in Watts (W)

V<sub>IN</sub> = Switch input Voltage, in Volts (V)

$R_{LOAD}$  = Output Load Resistance, in Ohms ( $\Omega$ )

I<sub>DS</sub> = Switch output current, in Amps (A)

V<sub>OUT</sub> = Switch output voltage, or R<sub>LOAD</sub> x I<sub>DS</sub>

In current-limit mode, the SLG59H1342C's power dissipation can be calculated by taking into account the voltage drop across the power switch  $(V_{IN}-V_{OUT})$  and the magnitude of the output current in current-limit mode  $(I_{ACL})$ :

PD =

$$(V_{IN}-V_{OUT}) \times I_{ACL}$$

or

PD =  $(V_{IN} - (R_{I,OAD} \times I_{ACL})) \times I_{ACL}$

where:

PD = Power dissipation, in Watts (W)  $V_{IN}$  = Input Voltage, in Volts (V)  $R_{LOAD}$  = Load Resistance, in Ohms ( $\Omega$ )  $I_{ACL}$  = Output limited current, in Amps (A)  $V_{OUT}$  =  $R_{LOAD}$  x  $I_{ACL}$

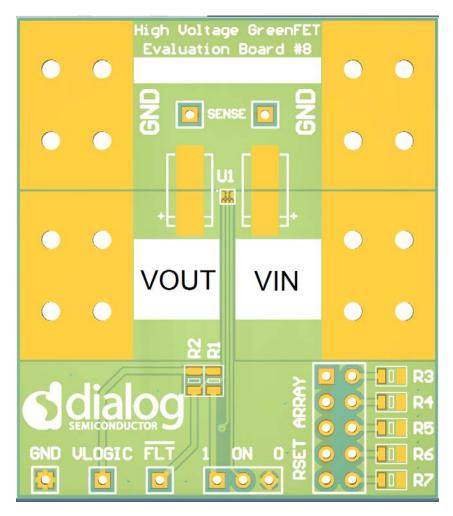

#### **Layout Guidelines**

- 1. Since the VIN and VOUT pins dissipate most of the heat generated during high-load current operation, it is highly recommended to make power traces as short, direct, and wide as possible. A good practice is to make power traces with an absolute minimum widths of 15 mils (0.381 mm) per Ampere. A representative layout, shown in Figure 10. illustrates proper techniques for heat to transfer as efficiently as possible out of the device;

- 2. To minimize the effects of parasitic trace inductance on normal operation, it is recommended to connect input  $C_{IN}$  and output  $C_{LOAD}$  low-ESR capacitors as close as possible to the SLG59H1342Cs VIN and VOUT pins;

- 3. The GND pin should be connected to system analog or power ground plane.

#### SLG59H1342C Evaluation Board:

4. A High Voltage GreenFET Evaluation Board for SLG59H1342C is designed according to the statements above and is illustrated on Figure 10. Please note that evaluation board has Sense pads. They cannot carry high currents and dedicated only for RDS<sub>ON</sub> evaluation.

Figure 10. SLG59H1342C Evaluation Board

Figure 11. SLG59H1342C Evaluation Board Connection Circuit

#### **Basic EVB Configuration**

- 1. Connect oscilloscope probes to VIN, VOUT, ON, etc.;

- 2. Turn on Power Supply and set desired  $V_{\text{IN}}$  from 2.7 V...5.5 V range;

- 3. Toggle ON signal High or Low to observe SLG59H1342C operation;

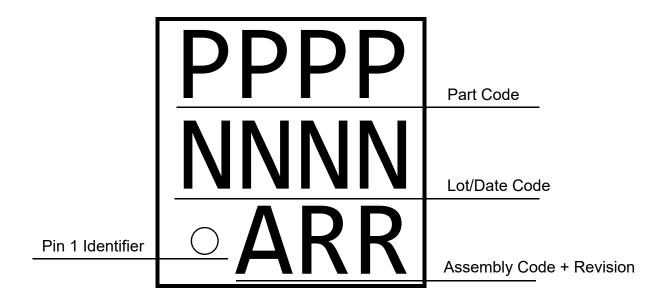

## **Package Top Marking System Definition**

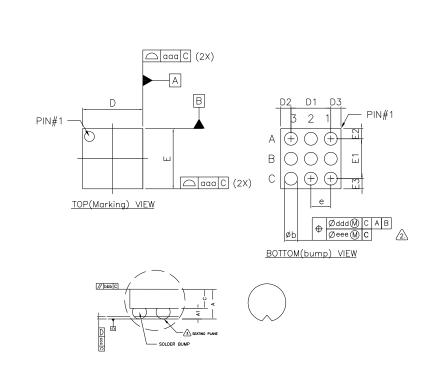

#### **Package Drawing and Dimensions**

#### 9 Pin WLCSP Green Package 1.21x 1.21 mm

| Symbol | Dime   | nsions in r | nm     | Dime   | ensions in | inch   |

|--------|--------|-------------|--------|--------|------------|--------|

| Symbol | MIN    | NOM         | MAX    | MIN    | NOM        | MAX    |

| Α      | 0.5470 | 0.5860      | 0.6250 | 0.0215 | 0.0231     | 0.0246 |

| A1     | 0.1870 | 0.2080      | 0.2290 | 0.0074 | 0.0082     | 0.0090 |

| С      | 0.3530 | 0.3780      | 0.4030 | 0.0139 | 0.0149     | 0.0159 |

| D      | 1.1850 | 1.2100      | 1.2350 | 0.0467 | 0.0476     | 0.0486 |

| E      | 1.1850 | 1.2100      | 1.2350 | 0.0467 | 0.0476     | 0.0486 |

| b      | 0.2340 | 0.2600      | 0.2860 | 0.0092 | 0.0102     | 0.0113 |

| D1     |        | 0.8000      |        |        | 0.0315     |        |

| D2     |        | 0.2050      |        |        | 0.0081     |        |

| D3     |        | 0.2050      |        | 177.7  | 0.0081     |        |

| E1     |        | 0.8000      |        |        | 0.0315     |        |

| E2     |        | 0.2050      |        |        | 0.0081     |        |

| E3     |        | 0.2050      |        |        | 0.0081     |        |

| е      |        | 0.4000      |        |        | 0.0157     |        |

| aaa    | 3      | 0.025       | 33     | -      | 0.001      |        |

| bbb    |        | 0.060       |        |        | 0.002      |        |

| ссс    |        | 0.030       |        |        | 0.001      |        |

| ddd    |        | 0.050       |        |        | 0.002      |        |

| eee    |        | 0.050       |        |        | 0.002      |        |

#### NOTF:

1. CONTROLLING DIMENSION : MILLIMETER.

2.

DIMENSION IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER, PARALLEL TO PRIMARY DATUM C

PRIMARY DATUM C AND SEATING PLANE ARE DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS

4. THE SOLDER BALL SIZE PRIOR REFLOW IS 250 UM.

REV: REVISION NOTE:

A NEW DRAWING

Datasheet Revision 1.02 27-Jan-2023

#### **Recommended Landing Pattern**

TOP(marking view)

Solder mask detail (not to scale)

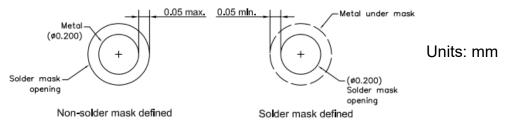

#### **Recommended Reflow Soldering Profile**

For successful reflow of the SLG59H1342C a recommended thermal profile is illustrated below:

Note: This reflow profile is for classification/preconditioning and are not meant to specify board assembly profile. Actual board assembly profiles should be developed based on specific process needs and board designs and should not exceed parameters depicted on figure above.

Please see more information on IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 0.553 mm<sup>3</sup> (nominal).

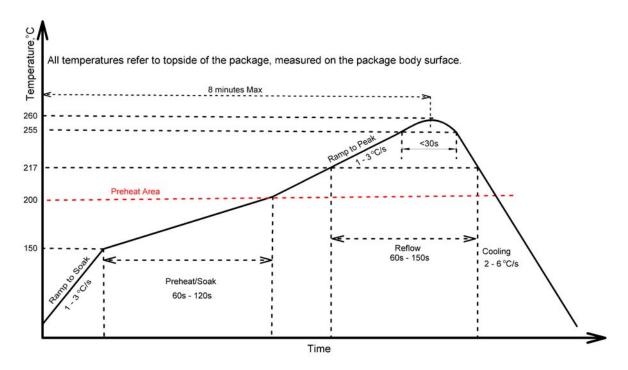

### **Tape and Reel Specifications**

| Dookogo                                    | # of | Nominal                | Max      | Units   | Reel &           | Leade   | r (min)        | Trailer | (min)          | Tape          | Part          |

|--------------------------------------------|------|------------------------|----------|---------|------------------|---------|----------------|---------|----------------|---------------|---------------|

| Package<br>Type                            | Pins | Package Size<br>[mm]   | per Reel | per Box | Hub Size<br>[mm] | Pockets | Length<br>[mm] | Pockets | Length<br>[mm] | Width<br>[mm] | Pitch<br>[mm] |

| WLCSP9L<br>1.21 x 1.21<br>mm 0.4P<br>Green |      | 1.21 x 1.21 x<br>0.586 | 3,000    | 3,000   | 178 / 60         | 100     | 400            | 100     | 400            | 8             | 4             |

### **Carrier Tape Drawing and Dimensions**

| Package<br>Type                            | PocketBTM<br>Length | PocketBTM<br>Width | Pocket<br>Depth | Index<br>Hole<br>Pitch | Pocket<br>Pitch | Index Hole<br>Diameter | Index Hole<br>to Tape<br>Edge | Index Hole<br>to Pocket<br>Center | Tape<br>Width | Tape<br>Thickness |

|--------------------------------------------|---------------------|--------------------|-----------------|------------------------|-----------------|------------------------|-------------------------------|-----------------------------------|---------------|-------------------|

|                                            | A0                  | В0                 | K0              | P0                     | P1              | D0                     | E                             | F                                 | W             | Т                 |

| WLCSP 9L<br>1.21x 1.21<br>mm 0.4P<br>Green | 1.38                | 1.38               | 0.7             | 4                      | 4               | 1.5                    | 1.75                          | 3.5                               | 8             | 0.2               |

Note: 1.Orientation in carrier: Pin1 is at upper left corner (Quadrant 1).

Refer to EIA-481 specification

## SLG59H1342C

A Reverse Blocking 70 m $\Omega$ , 1.5 A nFET Load Switch in 1.46 mm $^2$  WLCSP

## **Revision History**

| Date        | Version | Change                                                                                                                                                                |

|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27-Jan-2023 | 1.02    | Updated Block Diagram and Pin description with C <sub>RSET</sub> recommendation Updated I <sub>REVERSE</sub> condition for VIN = 0 V Fixed typos in Layout Guidelines |

| 29-Aug-2022 | 1.01    | Fixed typo in Scope shots                                                                                                                                             |

| 15-Jul-2022 | 1.0     | Production Release                                                                                                                                                    |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.