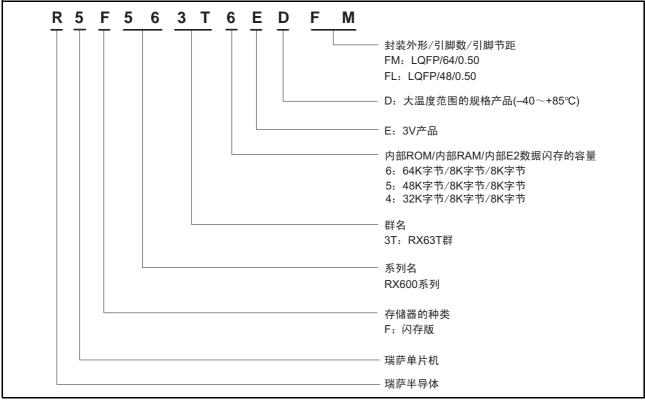

# RX63T群

用户手册 硬件篇

瑞萨32位单片机 RX族/RX600系列

本资料所记载的内容,均为本资料发行时的信息,瑞萨电子对于本资料所记载的产品或者规格可能会作改动,恕不另行通知。

请通过瑞萨电子的主页确认发布的最新信息。

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by vol.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

#### 注意事项

- 1. 本文档中所记载的关于电路、软件和其他相关信息仅用于说明半导体产品的操作和应用实例。用户如在设备设计中应 用本文档中的电路、软件和相关信息,请自行负责。对于用户或第三方因使用上述电路、软件或信息而遭受的任何损 失,瑞萨电子不承担任何责任。

- 2. 在准备本文档所记载的信息的过程中,瑞萨电子已尽量做到合理注意,但是,瑞萨电子并不保证这些信息都是准确无误的。用户因本文档中所记载的信息的错误或遗漏而遭受的任何损失,瑞萨电子不承担任何责任。

- 3. 对于因使用本文档中的瑞萨电子产品或技术信息而造成的侵权行为或因此而侵犯第三方的专利、版权或其他知识产权的行为,瑞萨电子不承担任何责任。本文档所记载的内容不应视为对瑞萨电子或其他人所有的专利、版权或其他知识产权作出任何明示、默示或其它方式的许可及授权。

- 4. 用户不得更改、修改、复制或者以其他方式部分或全部地非法使用瑞萨电子的任何产品。对于用户或第三方因上述更改、修改、复制或以其他方式非法使用瑞萨电子产品的行为而遭受的任何损失,瑞萨电子不承担任何责任。

- 5. 瑞萨电子产品根据其质量等级分为两个等级: "标准等级"和"高质量等级"。每种瑞萨电子产品的推荐用途均取决于产品的质量等级,如下所示:

标准等级: 计算机、办公设备、通讯设备、测试和测量设备、视听设备、家用电器、机械工具、个人电子设备以及 工业机器人等。

高质量等级: 运输设备(汽车、火车、轮船等)、交通控制系统、防灾系统、预防犯罪系统以及安全设备等。

瑞萨电子产品无意用于且未被授权用于可能对人类生命造成直接威胁的产品或系统及可能造成人身伤害的产品或系统 (人工生命维持装置或系统、植埋于体内的装置等)中,或者可能造成重大财产损失的产品或系统 (核反应堆控制系统、军用设备等)中。在将每种瑞萨电子产品用于某种特定应用之前,用户应先确认其质量等级。不得将瑞萨电子产品用于超出其设计用途之外的任何应用。对于用户或第三方因将瑞萨电子产品用于其设计用途之外而遭受的任何损害 或损失,瑞萨电子不承担任何责任。

- 6. 使用本文档中记载的瑞萨电子产品时,应在瑞萨电子指定的范围内,特别是在最大额定值、电源工作电压范围、移动电源电压范围、热辐射特性、安装条件以及其他产品特性的范围内使用。对于在上述指定范围之外使用瑞萨电子产品而产生的故障或损失,瑞萨电子不承担任何责任。

- 7. 虽然瑞萨电子一直致力于提高瑞萨电子产品的质量和可靠性,但是,半导体产品有其自身的具体特性,如一定的故障 发生率以及在某些使用条件下会发生故障等。此外,瑞萨电子产品均未进行防辐射设计。所以请采取安全保护措施, 以避免当瑞萨电子产品在发生故障而造成火灾时导致人身事故、伤害或损害的事故。例如进行软硬件安全设计(包括 但不限于冗余设计、防火控制以及故障预防等)、适当的老化处理或其他适当的措施等。由于难于对微机软件单独进 行评估,所以请用户自行对最终产品或系统进行安全评估。

- 8. 关于环境保护方面的详细内容,例如每种瑞萨电子产品的环境兼容性等,请与瑞萨电子的营业部门联系。使用瑞萨电子产品时,请遵守对管制物质的使用或含量进行管理的所有相应法律法规(包括但不限于《欧盟 RoHS 指令》)。对于因用户未遵守相应法律法规而导致的损害或损失,瑞萨电子不承担任何责任。

- 9. 不可将瑞萨电子产品和技术用于或者嵌入日本国内或海外相应的法律法规所禁止生产、使用及销售的任何产品或系统中。也不可将本文档中记载的瑞萨电子产品或技术用于与军事应用或者军事用途有关的任何目的(如大规模杀伤性武器的开发等)。在将本文档中记载的瑞萨电子产品或技术进行出口时,应当遵守相应的出口管制法律法规,并按照上述法律法规所规定的程序进行。

- 10. 向第三方分销或处分产品或者以其他方式将产品置于第三方控制之下的瑞萨电子产品买方或分销商,有责任事先向上 述第三方通知本文档规定的内容和条件;对于用户或第三方因非法使用瑞萨电子产品而遭受的任何损失,瑞萨电子不 承担任何责任。

- 11. 在事先未得到瑞萨电子书面认可的情况下,不得以任何形式部分或全部转载或复制本文档。

- 12. 如果对本文档所记载的信息或瑞萨电子产品有任何疑问,或者用户有任何其他疑问,请向瑞萨电子的营业部门咨询。

- (注1) 瑞萨电子: 在本文档中指瑞萨电子株式会社及其控股子公司。

- (注2) 瑞萨电子产品: 指瑞萨电子开发或生产的任何产品。

## 产品使用时的注意事项

本文对适用于单片机所有产品的"使用时的注意事项"进行说明。有关个别的使用时的注意事项请参照正 文。此外,如果在记载上有与本手册的正文有差异之处,请以正文为准。

#### 1. 未使用的引脚的处理

【注意】将未使用的引脚按照正文的"未使用引脚的处理"进行处理。

CMOS产品的输入引脚的阻抗一般为高阻抗。如果在开路的状态下运行未使用的引脚,由于感应现象,外加LSI周围的噪声,在LSI内部产生穿透电流,有可能被误认为是输入信号而引起误动作。 未使用的引脚,请按照正文的"未使用引脚的处理"中的指示进行处理。

#### 2. 通电时的处理

【注意】通电时产品处于不定状态。

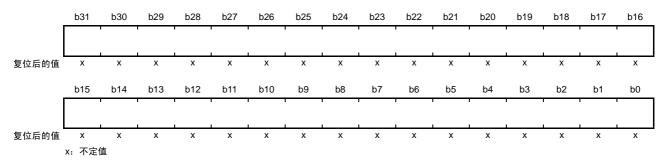

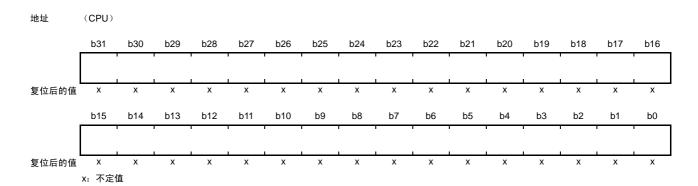

通电时, LSI内部电路处于不确定状态, 寄存器的设定和各引脚的状态不定。通过外部复位引脚对产品进行复位时, 从通电到复位有效之前的期间, 不能保证引脚的状态。

同样,使用内部上电复位功能对产品进行复位时,从通电到达到复位产生的一定电压的期间,不能保证引脚的状态。

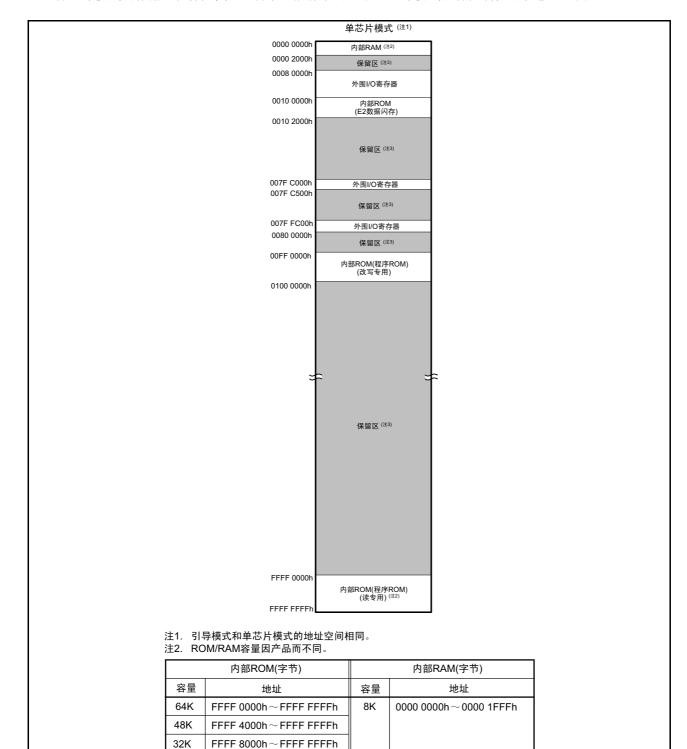

#### 3. 禁止存取保留地址 (保留区)

【注意】禁止存取保留地址 (保留区)

在地址区域中,有被分配将来用作功能扩展的保留地址 (保留区)。因为无法保证存取这些地址时的运行,所以不能对保留地址 (保留区)进行存取。

#### 4. 关于时钟

【注意】复位时,请在时钟稳定后解除复位。

在程序运行中切换时钟时,请在要切换成的时钟稳定之后进行。复位时,在通过使用外部振荡器(或者外部振荡电路)的时钟开始运行的系统中,必须在时钟充分稳定后解除复位。另外,在程序运行中,切换成使用外部振荡器(或者外部振荡电路)的时钟时,在要切换成的时钟充分稳定后再进行切换。

#### 5. 关于产品间的差异

【注意】在变更不同型号的产品时,请对每一个产品型号进行系统评价测试。

即使是同一个群的单片机,如果产品型号不同,由于内部ROM、版本模式等不同,在电特性范围内有时特性值、动作容限、噪声耐量、噪声辐射量等也不同。因此,在变更不认同型号的产品时,请对每一个型号的产品进行系统评价测试。

# 本手册的使用方法

#### 1 目的和对象

本手册是一本帮助用户理解本单片机的硬件功能和电特性的手册。它以使用本手册来设计应用系统的用户为对象。在使用本手册时,需要具备电路、逻辑电路以及单片机的基础知识。

本手册由产品概要、CPU、系统控制功能、外围功能、电特性、使用时的注意事项几大部分组成。

必须在充分确认注意事项后使用本单片机。注意事项记录在各章的正文中、各章的最后和注意事项章节中。

修订记录归纳了对旧版本记载内容的更正或追加的主要位置。并不是修订内容的全部记载。详情请确认本手册的正文。

RX63T 群准备了以下的文献。请使用最新的文献。最新版本刊登在瑞萨电子的主页上。

| 文献的种类                    | 记载内容                                       | 资料名              | 资料号             |

|--------------------------|--------------------------------------------|------------------|-----------------|

| Short Sheet              | 硬件的概要                                      | _                | _               |

| 数据表                      | 硬件的概要和电特性                                  | _                | _               |

| 用户手册 硬件篇                 | 硬件规格 (引脚排列、存储器映像、外围<br>功能规格、电特性、时序) 和运行的说明 | RX63T 群 用户手册 硬件篇 | 本硬件手册           |

| 用户手册 软件篇                 | CPU 指令集的说明                                 | RX 族 用户手册 软件篇    | R01US0028CJ0100 |

| 应用手册                     | 应用例子参考程序等                                  | _                | _               |

| RENESAS TECHNICAL UPDATE | 产品规格、文档等的快速公告                              | _                | _               |

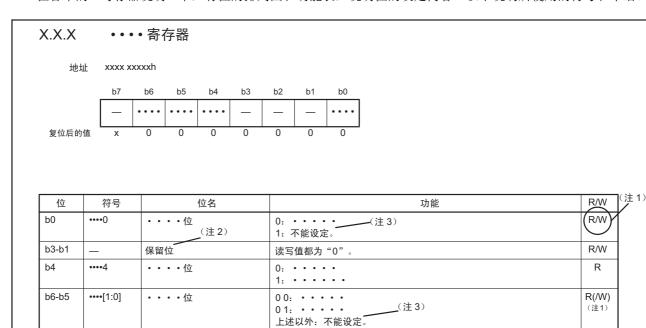

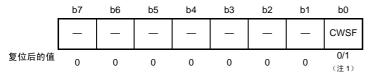

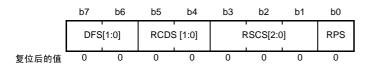

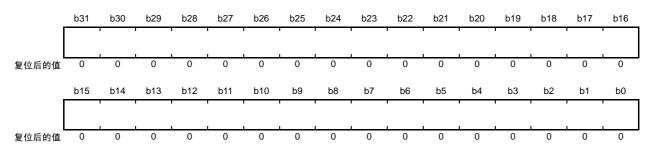

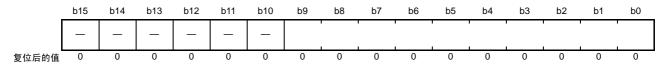

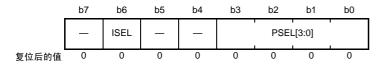

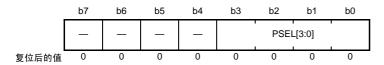

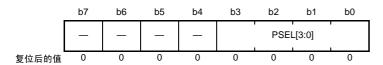

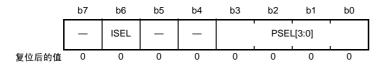

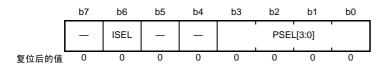

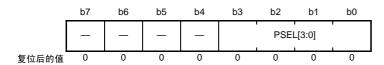

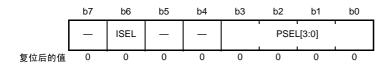

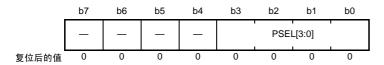

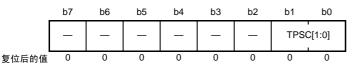

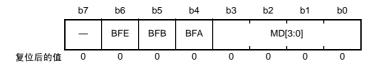

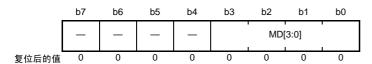

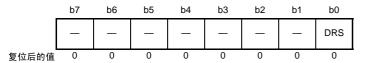

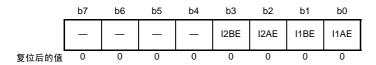

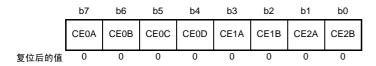

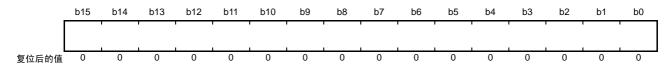

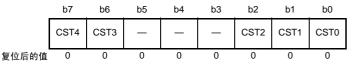

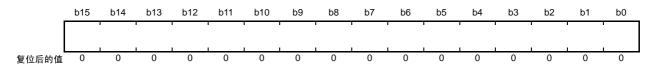

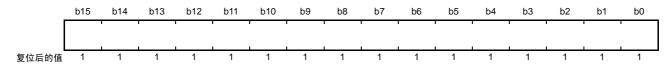

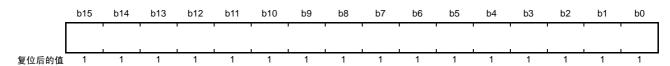

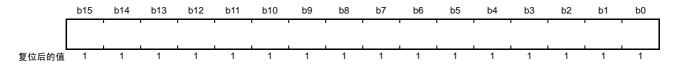

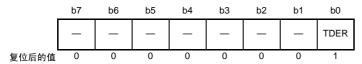

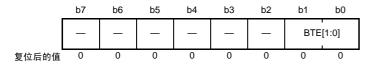

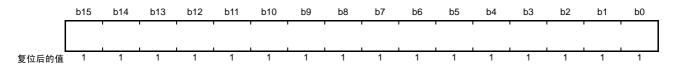

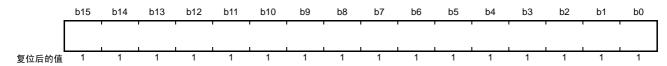

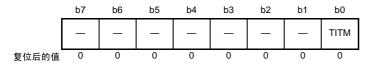

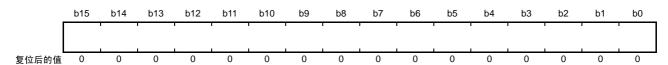

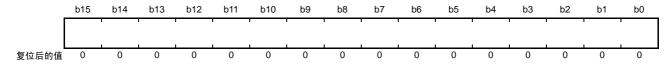

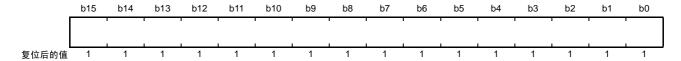

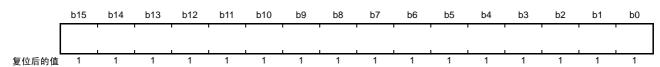

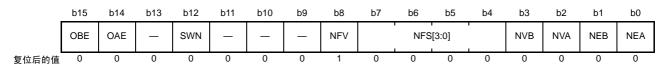

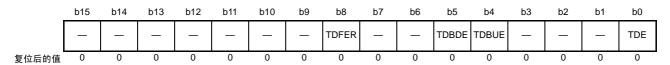

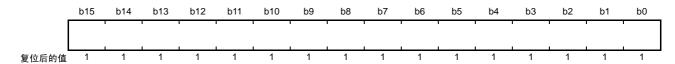

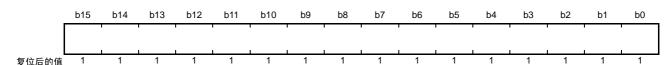

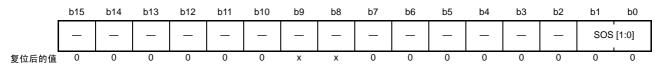

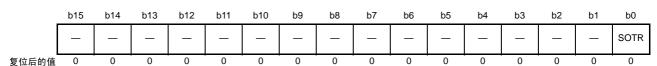

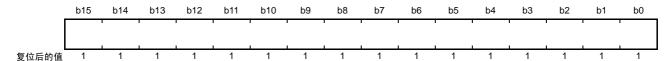

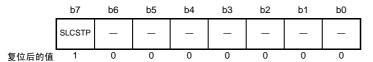

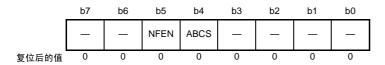

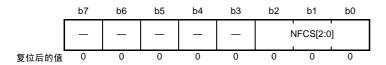

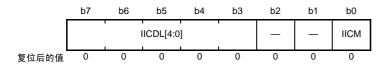

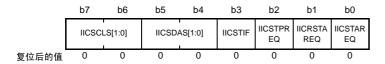

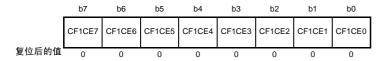

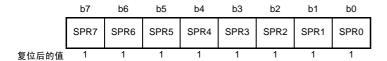

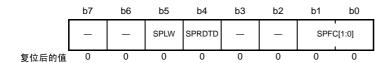

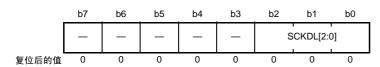

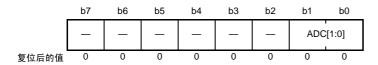

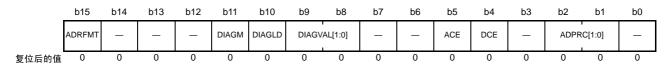

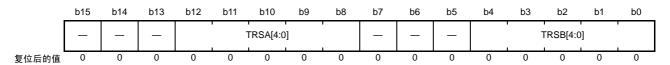

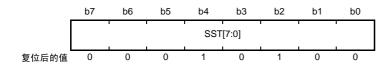

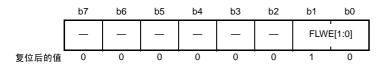

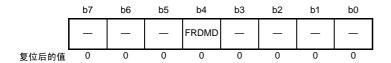

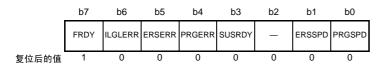

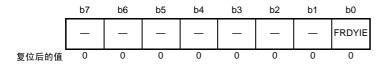

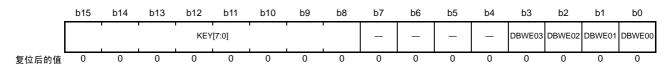

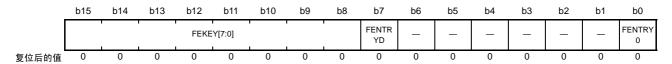

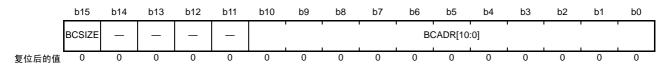

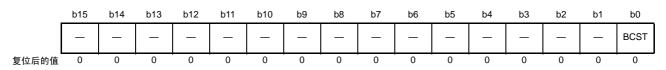

#### 2 寄存器的表示

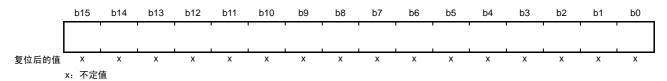

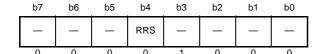

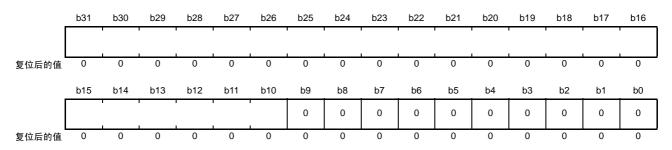

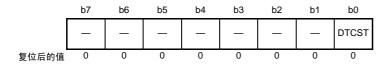

在各章的"寄存器说明"中,有位的排列图和功能表,说明位的设定内容。以下说明所使用的符号和术语。

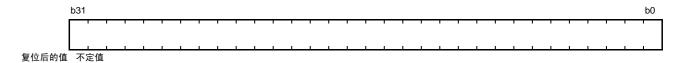

读取值为不定值,写无效。

R

注1. R/W : 可读写。

b7

R(/W): 可读写, 但是有写数据的限制。

限制内容请参照各寄存器的说明和注释。

R: 可写,写数据无效。

保留位

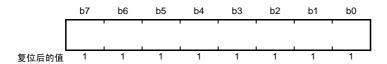

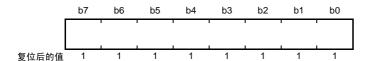

注2. 保留位。只能写指定值,如果写的值不是指定的值,就不保证运行。

注3. 不能设定。如果设定,就不保证运行。

# 3 省略语及简称的说明

| 省略/简称 | 全称                                           | 备注                |

|-------|----------------------------------------------|-------------------|

| ACIA  | Asynchronous Communication Interface Adapter | 异步通信接口适配器         |

| bps   | bits per second                              | 位 / 秒;每秒传送位数      |

| CRC   | Cyclic Redundancy Check                      | 循环冗余校验            |

| DMA   | Direct Memory Access                         | 直接存储器存取           |

| DMAC  | Direct Memory Access Controller              | DMA 控制器           |

| GSM   | Global System for Mobile Communications      | 全球数字移动电话系统        |

| Hi-Z  | High Impedance                               | 高阻抗               |

| IEBus | Inter Equipment bus                          | -                 |

| I/O   | Input/Output                                 | 输入/输出             |

| IrDA  | Infrared Data Association                    | 红外线数据协会           |

| LSB   | Least Significant Bit                        | 最低有效位             |

| MSB   | Most Significant Bit                         | 最高有效位             |

| NC    | Non-Connection                               | 未连接引脚             |

| PLL   | Phase Locked Loop                            | 锁相环路              |

| PWM   | Pulse Width Modulation                       | 脉宽调制              |

| SFR   | Special Function Registers                   | 特殊功能寄存器           |

| SIM   | Subscriber Identity Module                   | ISO-7816 规定的 IC 卡 |

| UART  | Universal Asynchronous Receiver/Transmitter  | 通用异步收发器           |

| VCO   | Voltage Controlled Oscillator                | 电压控制振荡器           |

# 目 录

| 特点  |                          | 1  |

|-----|--------------------------|----|

| 1.  | 概要                       | 2  |

| 1.1 | 规格概要                     |    |

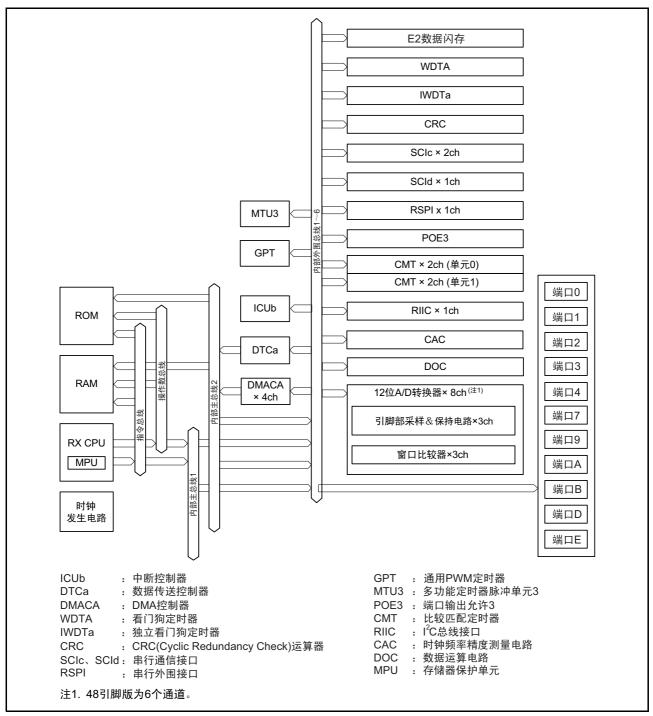

| 1.2 | 产品一览表                    | 7  |

| 1.3 | 框图                       |    |

| 1.4 |                          |    |

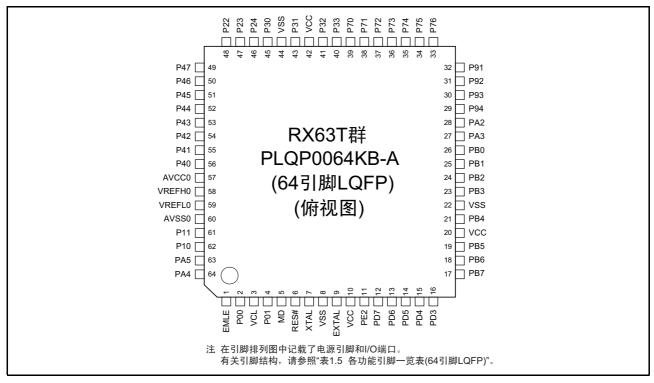

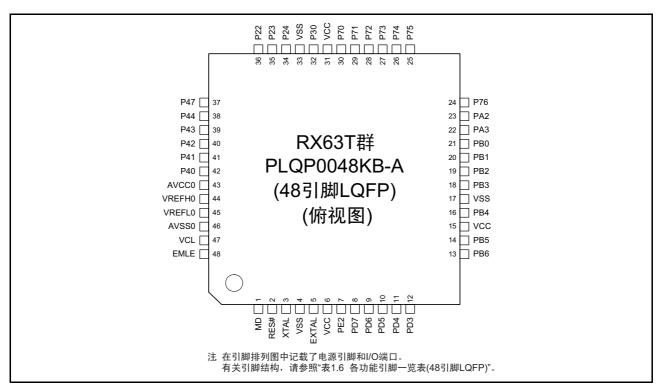

| 1.5 | 引脚排列图                    |    |

| 2.  | CPU                      | 18 |

| 2.1 | 特点                       | 18 |

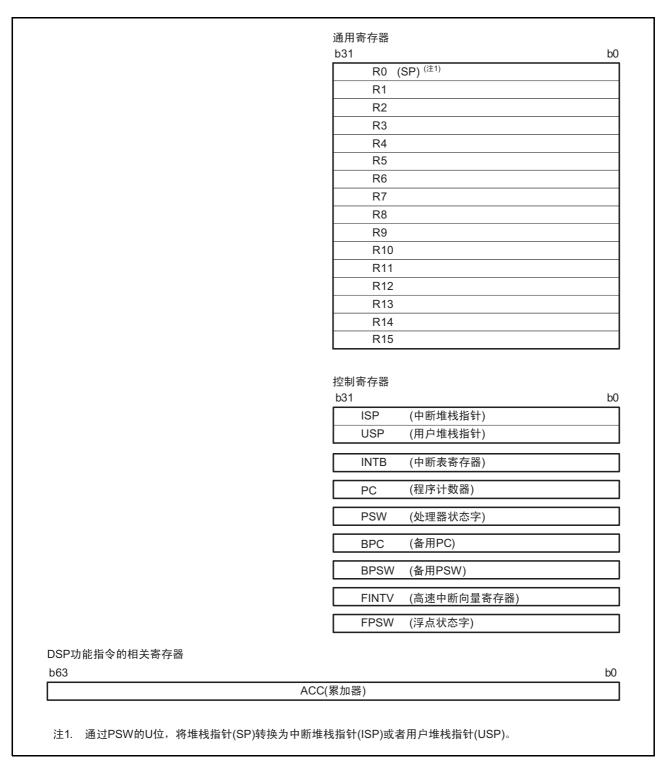

| 2.2 | CPU 寄存器组                 | 19 |

| 2.2 | 2.1 通用寄存器(R0~R15)        | 20 |

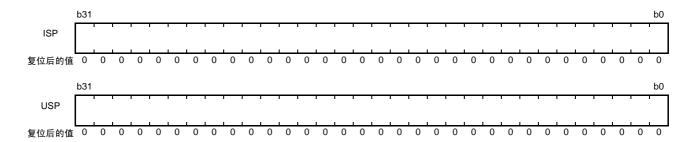

| 2.2 | 2.2 控制寄存器                | 20 |

| 2.2 | 2.3 DSP 功能指令的相关寄存器       | 25 |

| 2.3 | 处理器模式                    | 26 |

| 2.3 | 3.1 管理模式                 | 26 |

| 2.3 | 3.2 用户模式                 | 26 |

| 2.3 | 3.3 特权指令                 | 26 |

| 2.3 | 3.4 处理器模式之间的转移           | 26 |

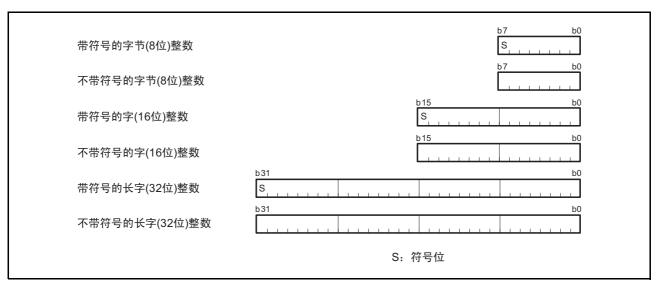

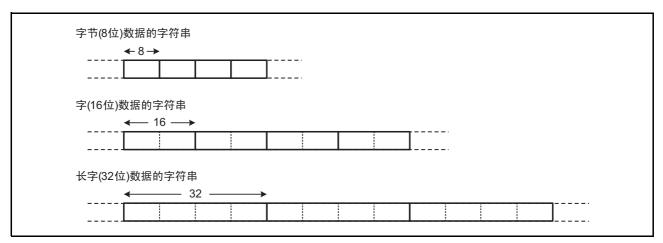

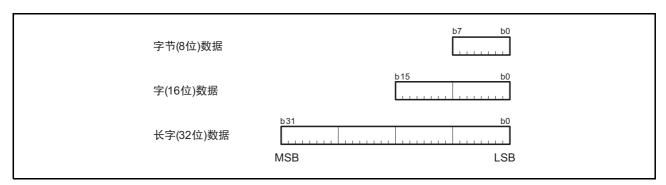

| 2.4 | 数据类型                     | 27 |

| 2.4 | 4.1 整数                   | 27 |

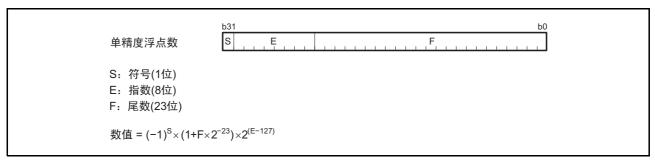

| 2.4 | 4.2 浮点数                  | 27 |

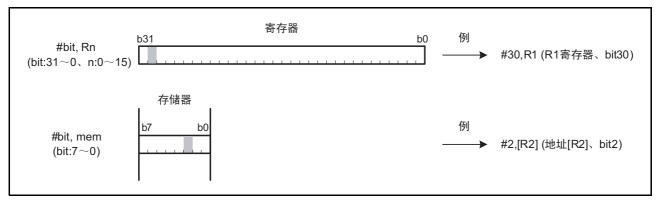

| 2.4 | 4.3 位                    | 28 |

| 2.4 | 4.4 字符串                  | 28 |

| 2.5 | 字节序                      | 29 |

| 2.5 | 5.1 字节序的设定               | 29 |

| 2.5 | 5.2 I/O 寄存器的存取           | 32 |

| 2.5 | 5.3 存取 I/O 寄存器时的注意事项     | 33 |

| 2.5 | 5.4 数据排列                 | 33 |

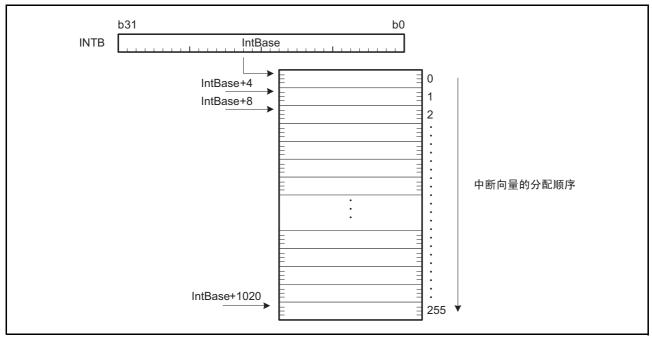

| 2.6 | 向量表                      | 34 |

| 2.6 | 6.1 固定向量表                | 34 |

| 2.6 | 6.2 可变向量表                | 34 |

| 2.7 | 指令操作                     | 35 |

| 2.7 | 7.1 RMPA 指令和字符串操作指令的数据预取 | 35 |

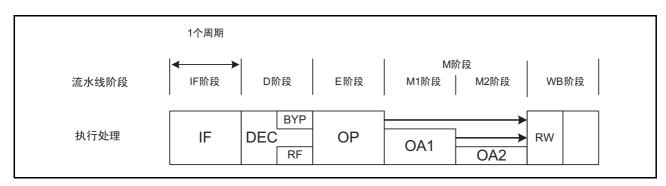

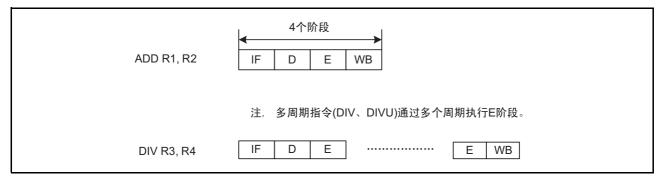

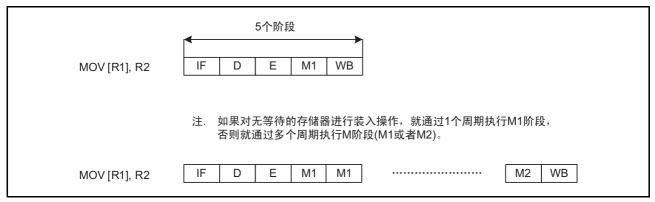

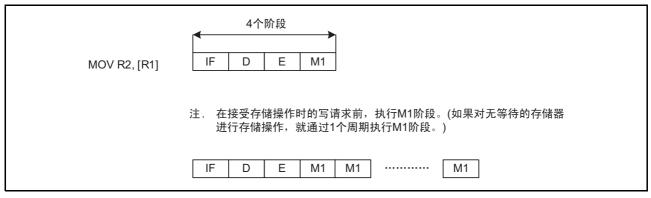

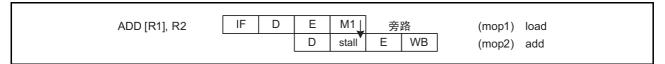

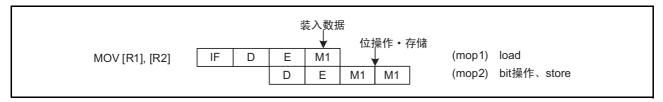

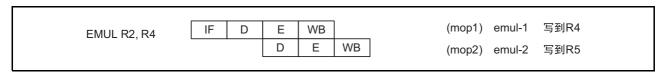

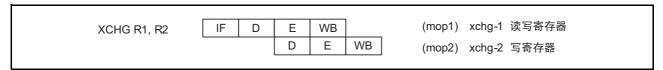

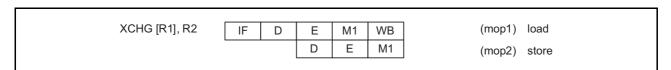

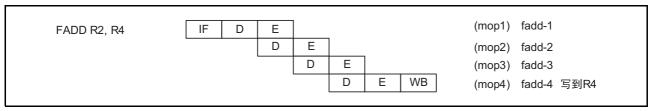

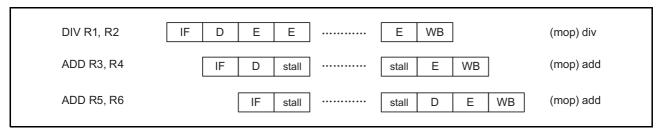

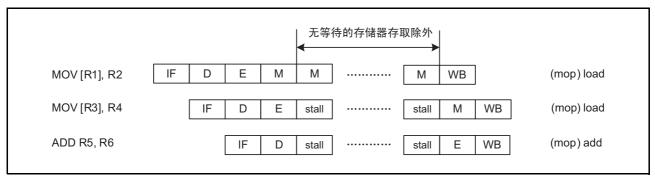

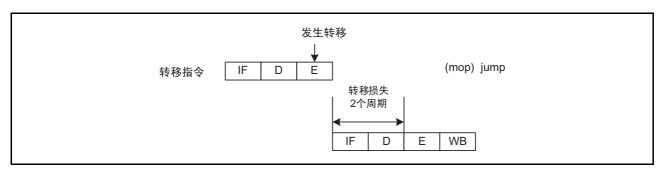

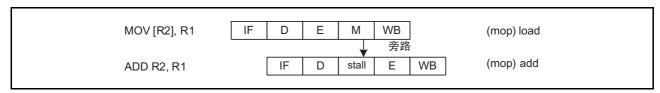

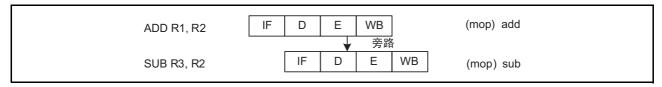

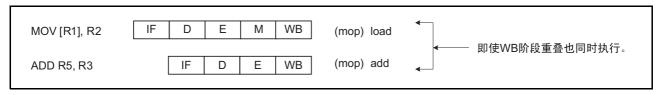

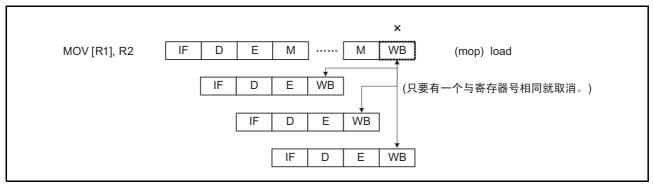

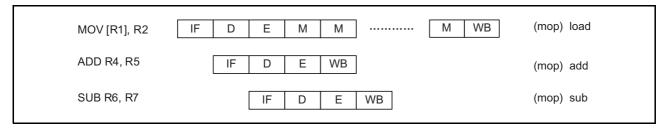

| 2.8 | 流水线                      | 36 |

| 2.8 | 8.1 概要                   | 36 |

| 2.8 | 8.2   指令和流水线处理           | 37 |

| 2.8 | 8.3 指令处理时间的计算方法          | 44 |

| 2.8 | 8.4 中断响应周期数              | 44 |

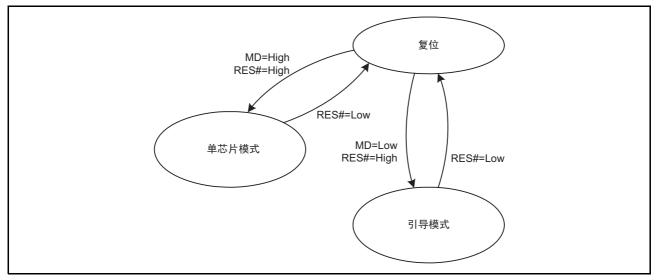

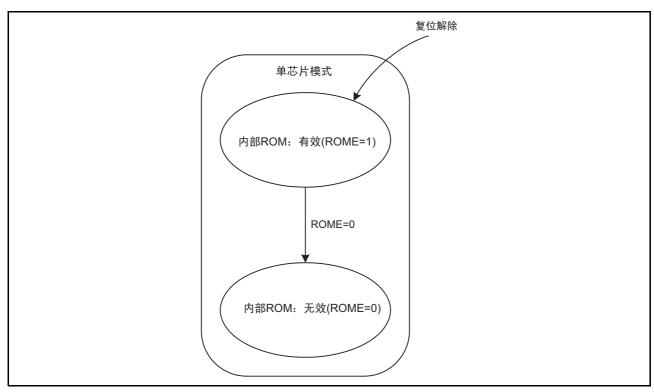

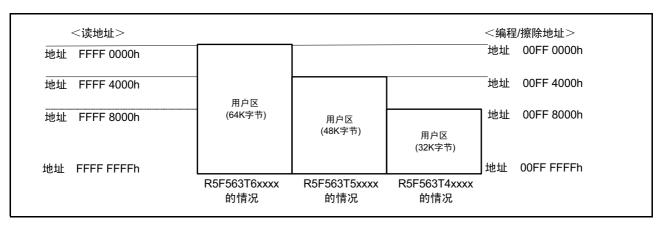

| 3.  | 运行模式                     |    |

| 3.1 | 运行模式的种类和选择               | 45 |

| 3.2 | 寄存器说明                    | 46 |

| 3.2 | 2.1 模式监视寄存器 (MDMONR)     | 46 |

| 3.2 | 2.2 系统控制寄存器 0 (SYSCR0)   | 46 |

| 3.2 | 2.3 系统控制寄存器 1 (SYSCR1)   | 47 |

| 3.3 | 运行模式的说明                  | 47 |

| 3.3 | 3.1 单芯片模式                | 47 |

| 3.3.2               | 引导模式                                     | 47 |

|---------------------|------------------------------------------|----|

| 3.4 运               | 行模式的转移                                   | 48 |

| 3.4.1               | 通过模式引脚进行运行模式的转移                          | 48 |

| 3.4.2               | 通过设定寄存器进行运行模式的转移                         | 48 |

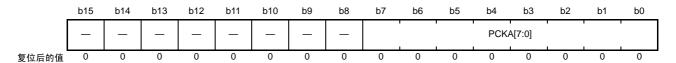

| 4. 地址               | 空间                                       | 49 |

| 4.1 地               | 址空间                                      |    |

| 5. I/O <del>i</del> | 寄存器                                      | 50 |

|                     | <b>)</b> 寄存器地址一览表 (地址顺序)                 |    |

|                     | .,,                                      |    |

|                     | T                                        |    |

|                     | 要                                        |    |

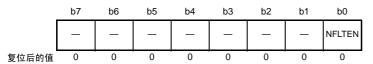

|                     | 存器说明                                     |    |

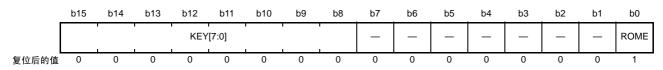

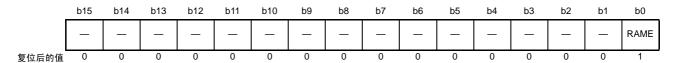

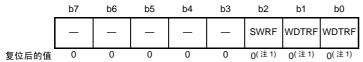

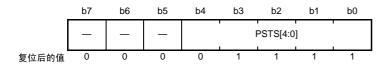

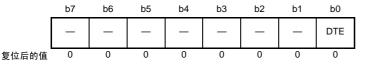

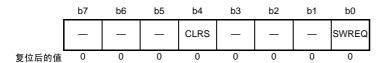

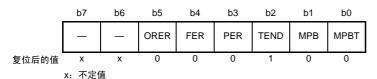

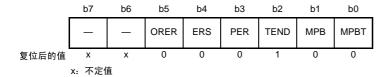

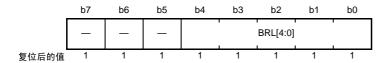

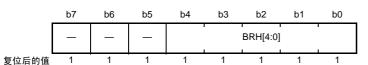

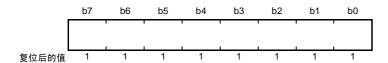

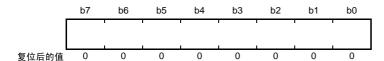

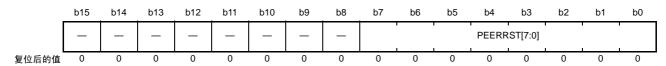

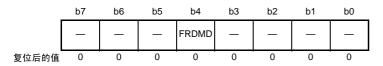

| 6.2.1<br>6.2.2      | 复位状态寄存器 0 (RSTSR0)<br>复位状态寄存器 1 (RSTSR1) |    |

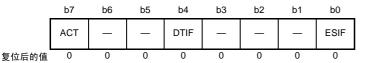

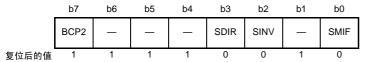

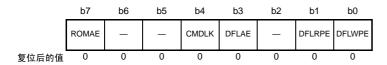

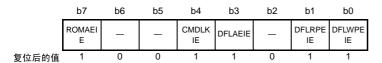

| 6.2.3               | 复位状态寄存器 2 (RSTSR2)                       |    |

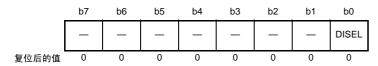

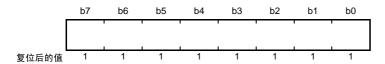

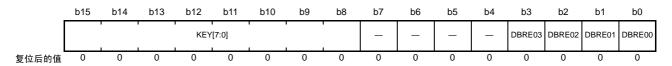

| 6.2.4               |                                          |    |

|                     | 行说明                                      |    |

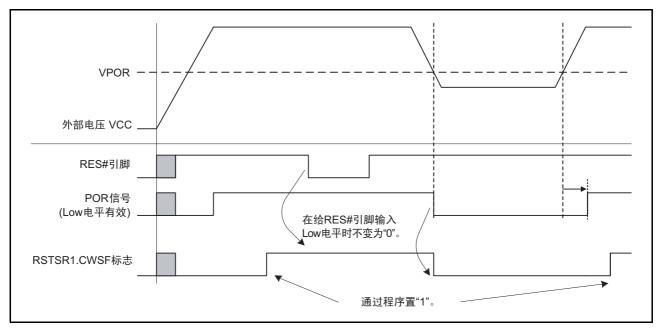

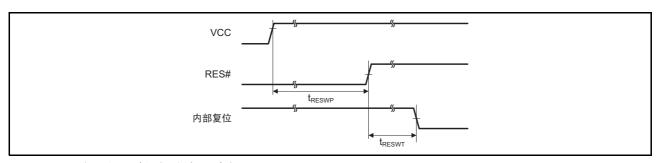

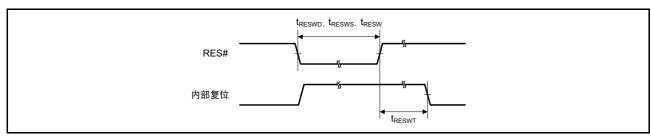

| 6.3.1               | 引脚复位                                     |    |

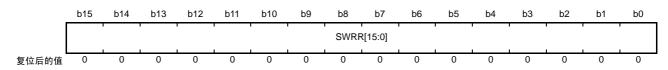

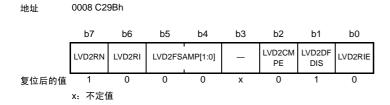

| 6.3.2               | 上电复位和电压监视 0 复位                           |    |

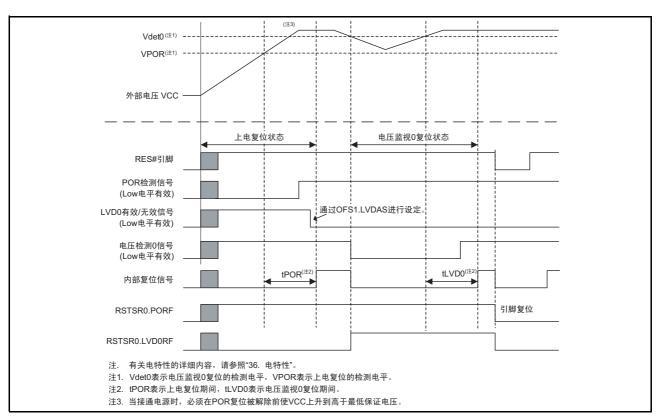

| 6.3.3               | 电压监视 1 复位和电压监视 2 复位                      |    |

| 6.3.4               | 深度软件待机复位                                 |    |

| 6.3.5               | 独立看门狗定时器复位                               |    |

| 6.3.6               | 看门狗定时器复位                                 |    |

| 6.3.7               | 软件复位                                     | 78 |

| 6.3.8               | 冷启动 / 热启动判断功能                            | 79 |

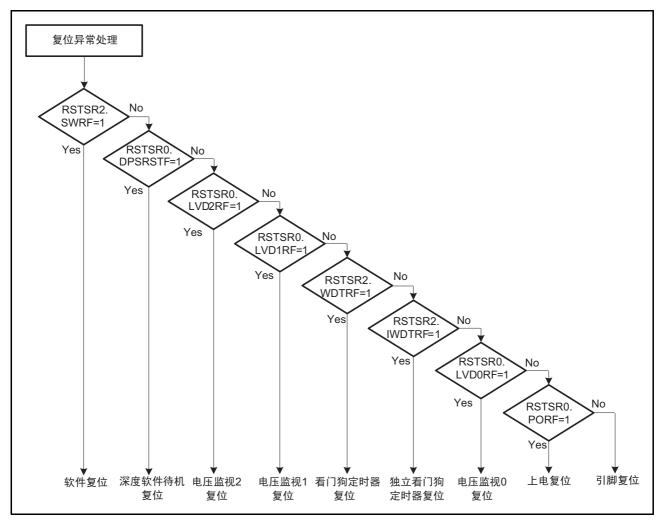

| 6.3.9               | 复位发生源的判断                                 | 80 |

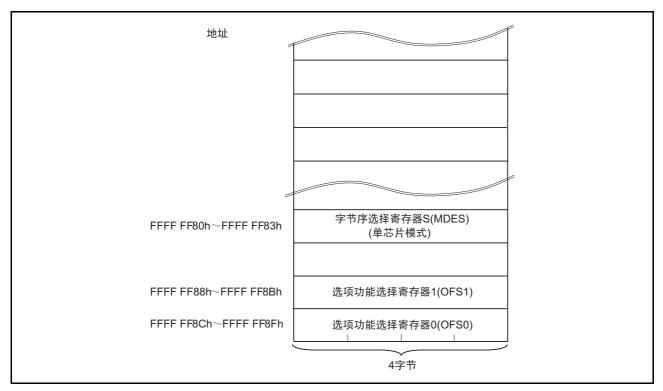

| 7. 选项               | ī设定存储器                                   | 81 |

| 7.1 概               | 要                                        | 81 |

| 7.2 寄               | 存器说明                                     | 82 |

| 7.2.1               | 选项功能选择寄存器 0 (OFS0)                       | 82 |

| 7.2.2               | 选项功能选择寄存器 1 (OFS1)                       | 86 |

| 7.2.3               | 字节序选择寄存器 S (MDES)                        |    |

|                     | 用时的注意事项                                  |    |

| 7.3.1               | 选项设定存储器的设定例子                             | 87 |

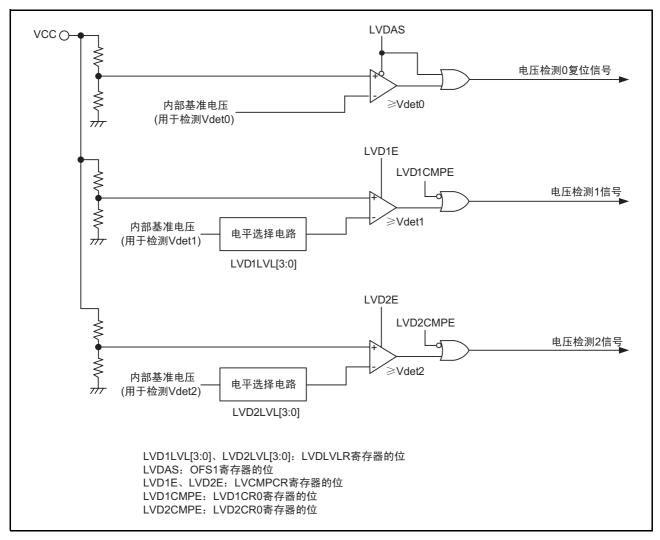

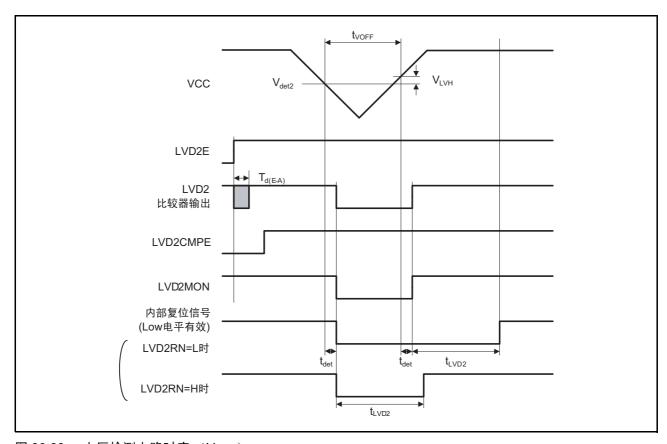

| 8. 电压               | · 检测电路 (LVDA)                            | 88 |

| 8.1 概               | 要                                        | 88 |

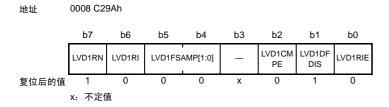

|                     | 存器说明                                     |    |

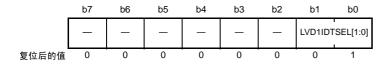

| 8.2.1               | 电压监视 1 电路的控制寄存器 1 (LVD1CR1)              | 91 |

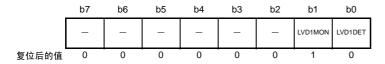

| 8.2.2               | 电压监视 1 电路的状态寄存器 (LVD1SR)                 | 91 |

| 8.2.3               | 电压监视 2 电路的控制寄存器 1 (LVD2CR1)              |    |

| 8.2.4               | 电压监视 2 电路的状态寄存器 (LVD2SR)                 | 92 |

| 8.2.5               | 电压监视电路的控制寄存器 (LVCMPCR)                   | 93 |

| 8.2.6               | 电压检测电平选择寄存器 (LVDLVLR)                    |    |

| 8.2.7               | 电压监视 1 电路的控制寄存器 0 (LVD1CR0)              |    |

| 8.2.8               | 电压监视 2 电路的控制寄存器 0 (LVD2CR0)              |    |

|                     | CC 输入电压的监视                               |    |

| 8.3.1               | Vdet0 的监视                                |    |

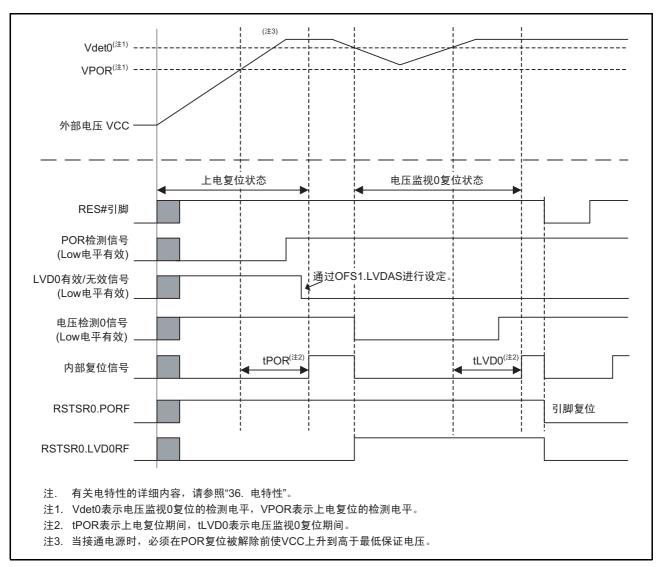

| 8.3.2               | Vdet1 的监视                                | 98 |

| 8.        | 3.3          | Vdet2 的监视                    | 98  |

|-----------|--------------|------------------------------|-----|

| 8.4       |              | E监视 0 复位                     |     |

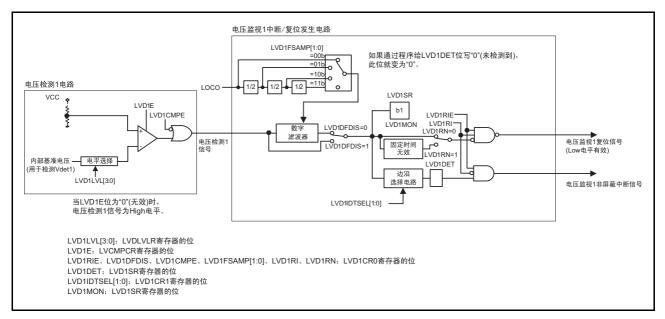

| 8.5       |              | E监视 1 中断和电压监视 1 复位           |     |

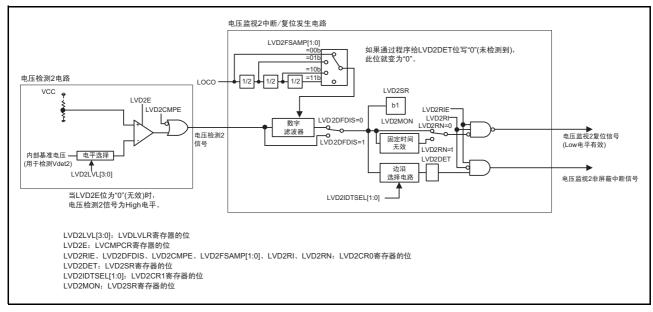

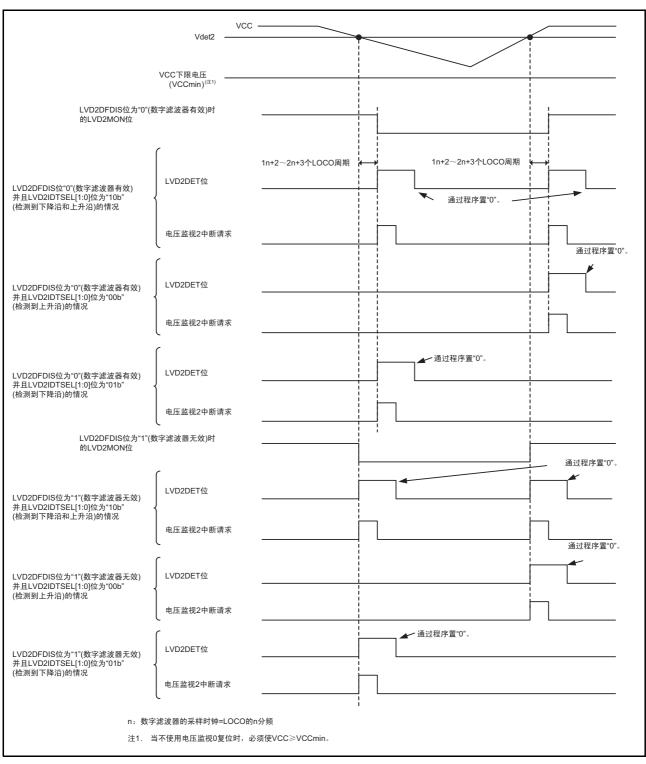

| 8.6       | 电归           | E监视 2 中断和电压监视 2 复位           | 102 |

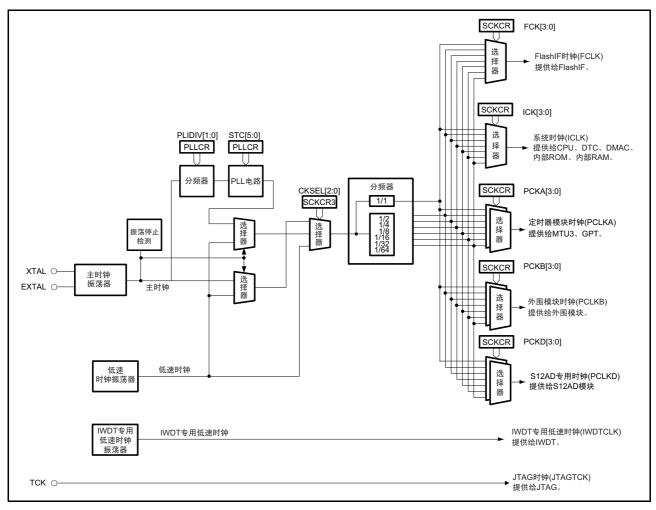

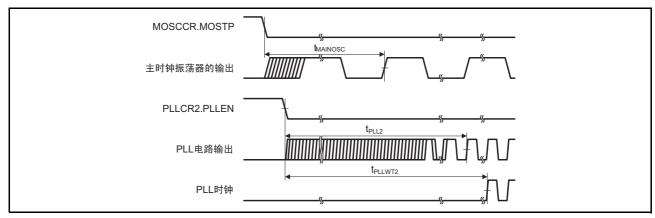

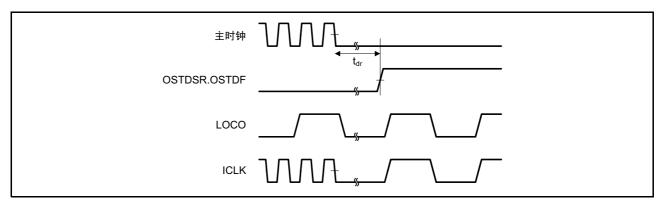

| 9.        | 时钟约          | 发生电路                         | 104 |

| 9.1       | 概要           | ξ                            | 104 |

| 9.2       | 寄存           | <b>7器说明</b>                  |     |

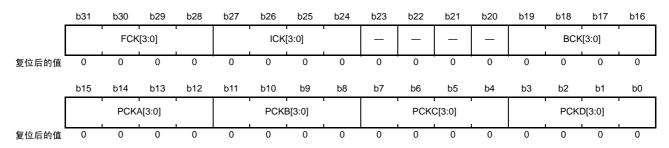

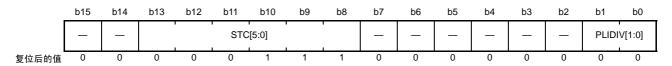

| 9.        | 2.1          | 系统时钟控制寄存器 (SCKCR)            | 106 |

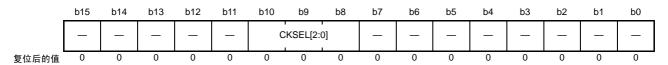

| 9.        | 2.2          | 系统时钟控制寄存器 3 (SCKCR3)         |     |

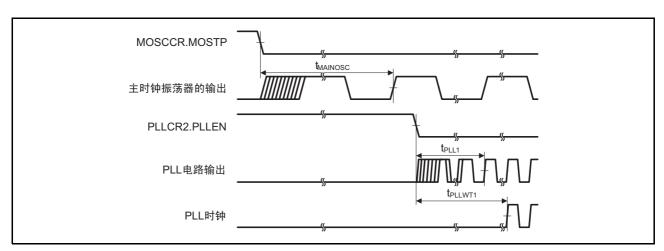

| 9.        | 2.3          | PLL 控制寄存器 (PLLCR)            |     |

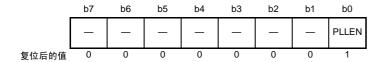

| 9.        | 2.4          | PLL 控制寄存器 2 (PLLCR2)         |     |

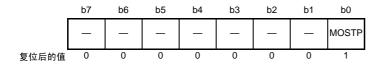

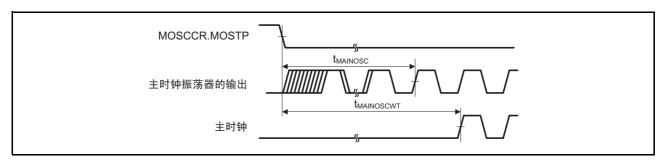

|           | 2.5          | 主时钟振荡器的控制寄存器 (MOSCCR)        |     |

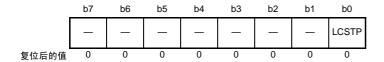

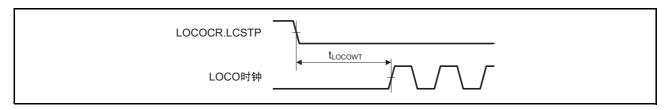

|           | 2.6          | 低速内部振荡器的控制寄存器(LOCOCR)        |     |

|           | 2.7          | IWDT 专用内部振荡器的控制寄存器 (ILOCOCR) |     |

|           | 2.8          | 振荡停止检测控制寄存器 (OSTDCR)         |     |

|           | 2.9          | 振荡停止检测状态寄存器 (OSTDSR)         |     |

|           | 2.10         | 主时钟振荡器的强制振荡控制寄存器 (MOFCR)     |     |

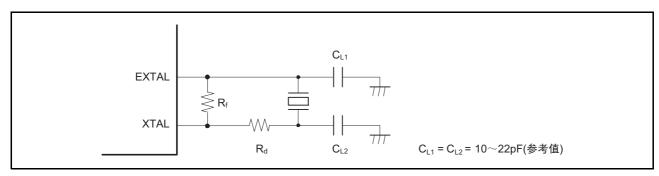

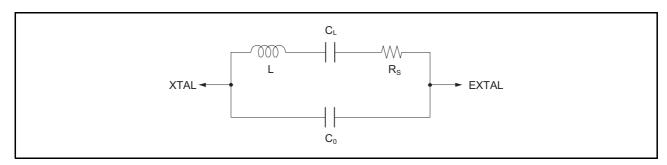

| 9.3       |              | 寸钟振荡器                        |     |

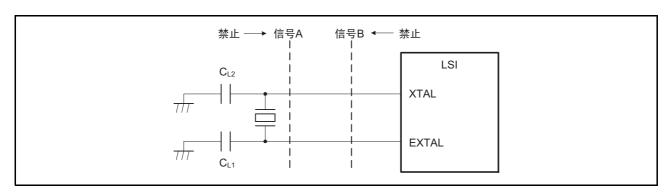

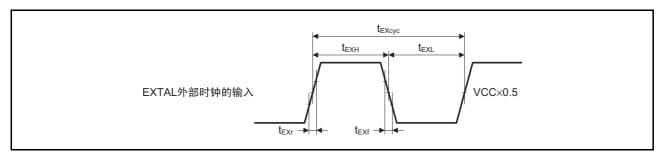

|           | 3.1          | 连接谐振器的方法                     |     |

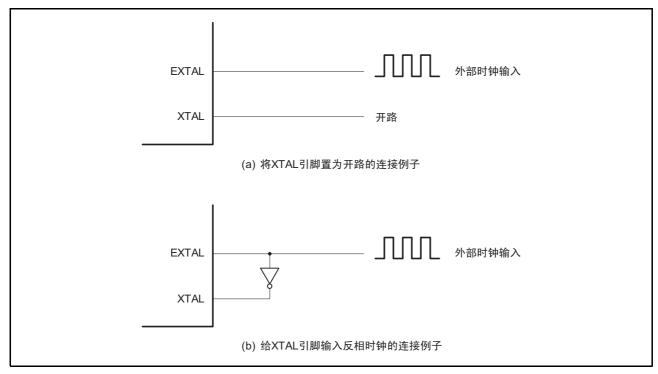

|           | 3.2          | 输入外部时钟的方法                    |     |

|           | 3.3          | 有关外部时钟输入的注意事项                |     |

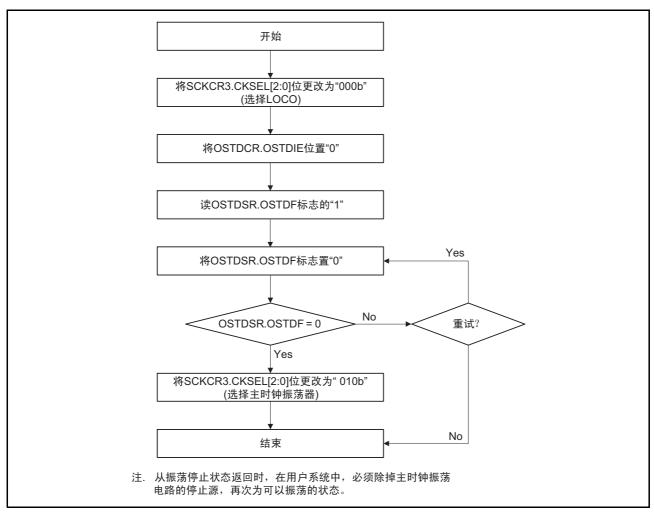

| 9.4       |              | 易停止检测功能<br>振荡停止检测和检测后的运行     |     |

|           | 4.1          | 振荡停止位测和位测户的运行振荡停止检测中断        |     |

| 9.<br>9.5 | 4.2          | 振汤停止位测中断<br>. 电路             |     |

| 9.5       |              | 7 电时                         |     |

|           | гу п<br>.6.1 | 系统时钟                         |     |

|           | 6.2          | 定时器模块时钟                      |     |

| -         | 6.3          | 外围模块时钟                       |     |

|           | 6.4          | S12AD 时钟                     |     |

|           | 6.5          | FlashIF 时钟                   |     |

|           | 6.6          | CAC 时钟                       |     |

|           | 6.7          | IWDT 专用低速时钟                  |     |

| -         | 6.8          | JTAG 时钟                      |     |

| 9.7       |              | 接谐振器时的引脚设定                   |     |

| 9.8       |              | 月时的注意事项                      |     |

| 9.        | 8.1          | 有关时钟发生电路的注意事项                | 122 |

| 9.        | 8.2          | 有关谐振器的注意事项                   | 122 |

| 9.        | 8.3          | 设计电路板时的注意事项                  | 122 |

| 10.       | 时钟频          | 频率精度测量电路 (CAC)               | 123 |

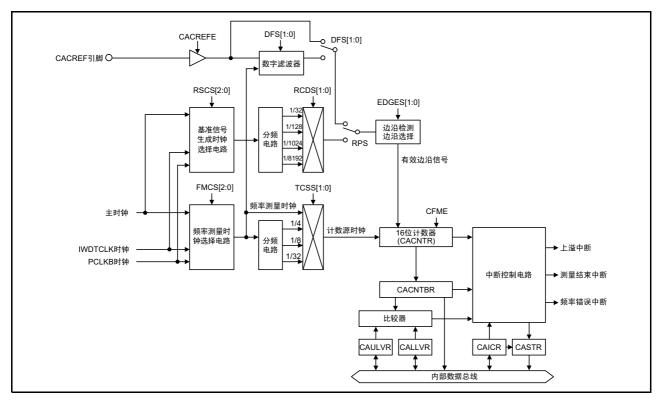

| 10.1      | 概要           | Б<br>5                       | 123 |

| 10.2      | 2 寄存         | 7器说明                         | 124 |

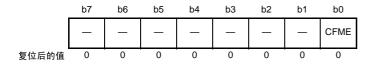

| 10        | 0.2.1        | CAC 控制寄存器 0 (CACR0)          | 124 |

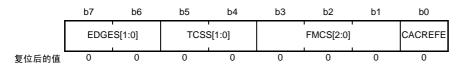

| 10        | 0.2.2        | CAC 控制寄存器 1 (CACR1)          |     |

| 10        | 0.2.3        | CAC 控制寄存器 2 (CACR2)          | 126 |

| 10        | 0.2.4        | CAC 中断控制寄存器 (CAICR)          | 127 |

| 10        | 0.2.5        | CAC 状态寄存器 (CASTR)            |     |

| 10        | 0.2.6        | CAC 上限值设定寄存器 (CAULVR)        |     |

|           | 0.2.7        | CAC 下限值设定寄存器 (CALLVR)        |     |

| 10        | 0.2.8        | CAC 计数器的缓冲寄存器 (CACNTBR)      | 129 |

| 10.3 运行 | 亍说明                                |     |

|---------|------------------------------------|-----|

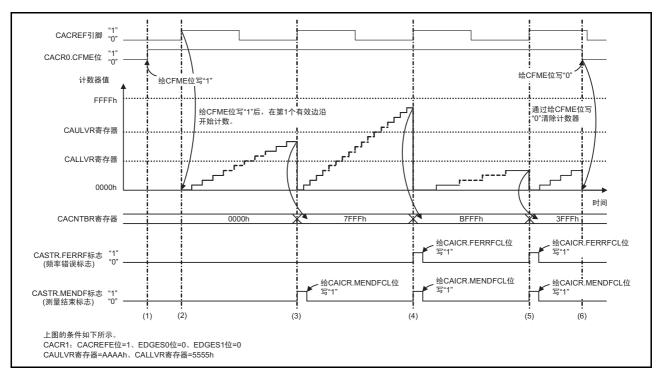

| 10.3.1  | 以 CACREF 引脚输入为基准测量时钟频率             | 130 |

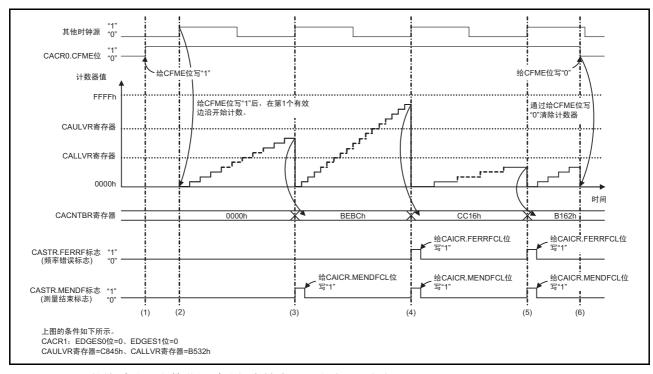

| 10.3.2  | 以其他时钟源为基准测量时钟频率                    | 131 |

| 10.3.3  | CACREF 引脚的数字滤波器功能                  | 132 |

| 10.4 中陸 | 所请求                                |     |

| 10.5 使月 | <b>目时的注意事项</b>                     |     |

| 10.5.1  | 模块停止功能的设定                          | 132 |

| 11. 低功績 | 耗功能                                | 133 |

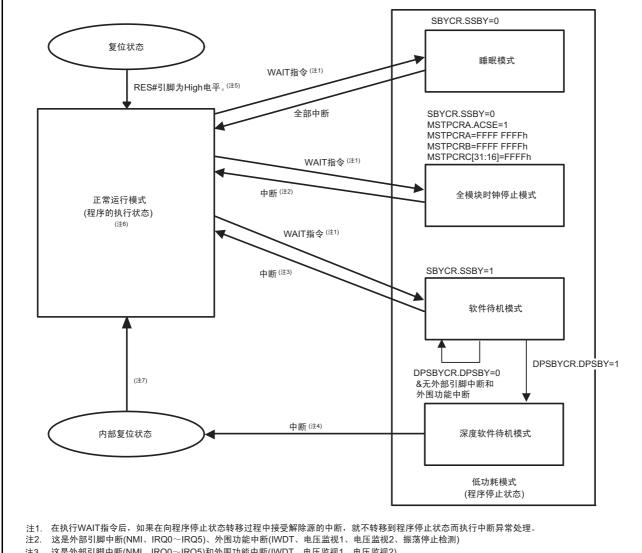

|         | 要                                  |     |

|         | 字器说明                               |     |

| 11.2.1  | 待机控制寄存器 (SBYCR)                    | 136 |

| 11.2.2  | 模块停止控制寄存器 A (MSTPCRA)              | 137 |

| 11.2.3  | 模块停止控制寄存器 B (MSTPCRB)              |     |

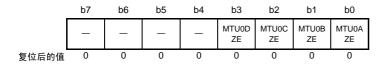

| 11.2.4  | 模块停止控制寄存器 C (MSTPCRC)              |     |

| 11.2.5  | 主时钟振荡器的等待控制寄存器 (MOSCWTCR)          | 140 |

| 11.2.6  | PLL 等待控制寄存器 (PLLWTCR)              | 141 |

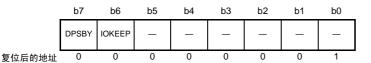

| 11.2.7  | 深度待机控制寄存器 (DPSBYCR)                |     |

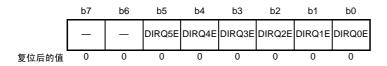

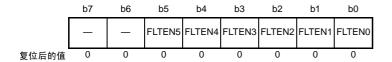

| 11.2.8  | 深度待机中断允许寄存器 0 (DPSIER0)            |     |

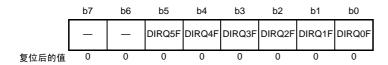

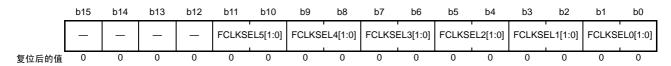

| 11.2.9  | 深度待机中断允许寄存器 2 (DPSIER2)            |     |

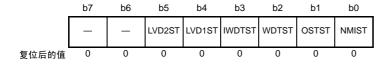

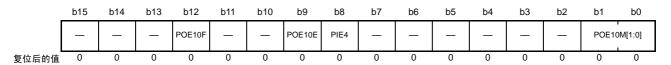

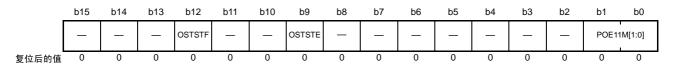

| 11.2.10 | 深度待机中断标志寄存器 0 (DPSIFR0)            | 145 |

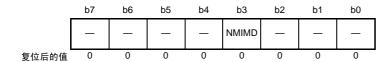

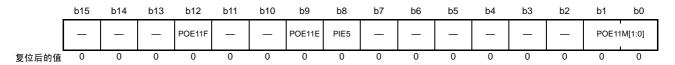

| 11.2.11 | 深度待机中断标志寄存器 2 (DPSIFR2)            |     |

| 11.2.12 | 深度待机中断边沿寄存器 0(DPSIEGR0)            |     |

| 11.2.13 | 深度待机中断边沿寄存器 2 (DPSIEGR2)           |     |

| 11.2.14 | 深度待机备用寄存器 (DPSBKRy)(y=0 $\sim$ 31) |     |

|         | 过转换时钟来降低功耗                         |     |

|         | 央停止功能                              |     |

|         | 为耗状态                               |     |

| 11.5.1  | 睡眠模式                               |     |

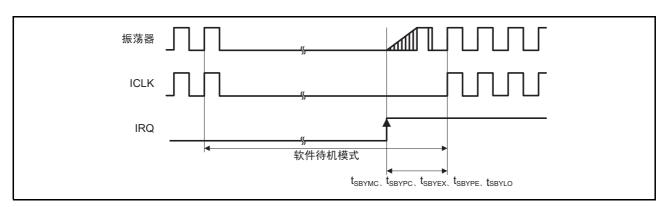

| 11.5.2  | 全模块时钟停止模式                          |     |

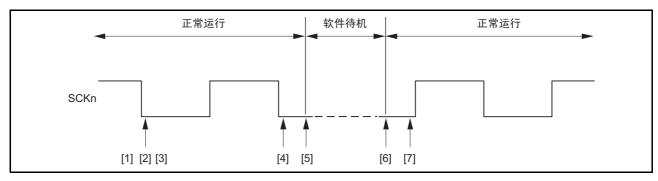

| 11.5.3  | 软件待机模式                             |     |

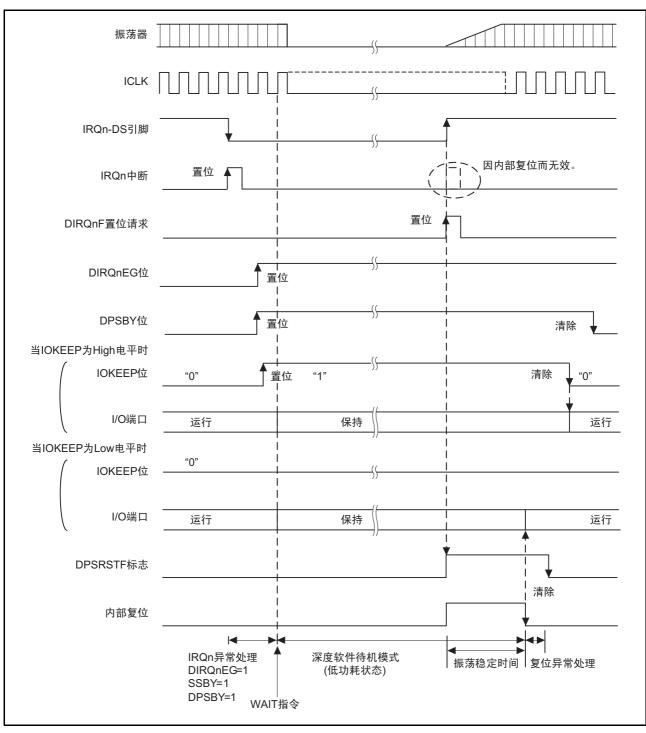

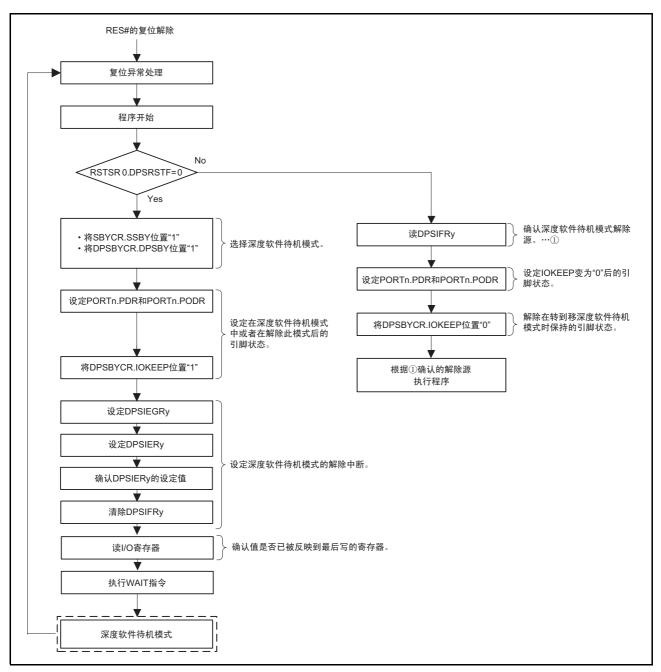

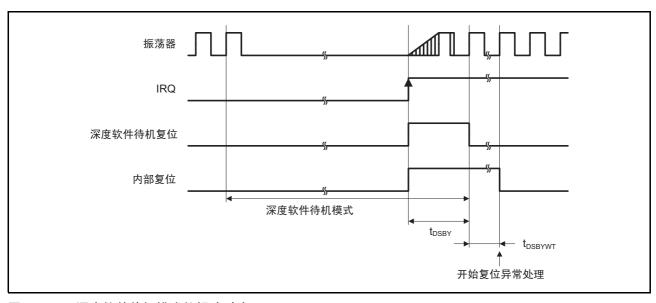

| 11.5.4  | 深度软件待机模式                           |     |

|         | <b>目时的注意事项</b>                     |     |

| 11.6.1  | I/O 端口状态                           |     |

| 11.6.2  | DMAC 和 DTC 的模块停止                   |     |

| 11.6.3  | 内部外围模块的中断                          |     |

| 11.6.4  | MSTPCRA、 MSTPCRB 和 MSTPCRC 寄存器的写操作 |     |

| 11.6.5  | 通过 DIRQnE 位 (n=0 ~ 5) 控制输入缓冲器      |     |

| 11.6.6  | WAIT 指令的执行时序                       |     |

| 11.6.7  | 睡眠模式中通过 DMAC 和 DTC 进行的寄存器改写        |     |

| 11.6.8  | 从软件待机模式返回时的注意事项 (可参照 63N)          | 158 |

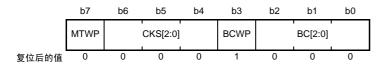

| 12. 寄存  | 器写保护功能                             | 159 |

| 12.1 寄存 | 字器说明                               |     |

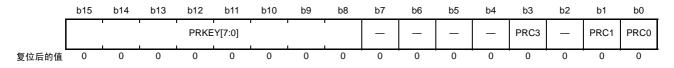

| 12.1.1  | 保护寄存器(PRCR)                        | 160 |

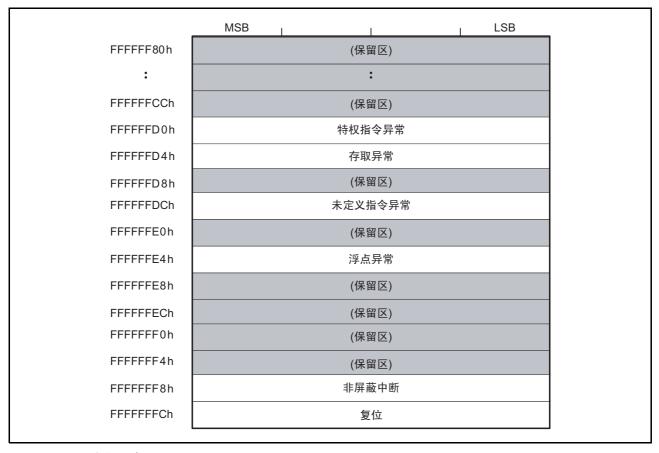

| 13. 异常统 | 处理                                 | 161 |

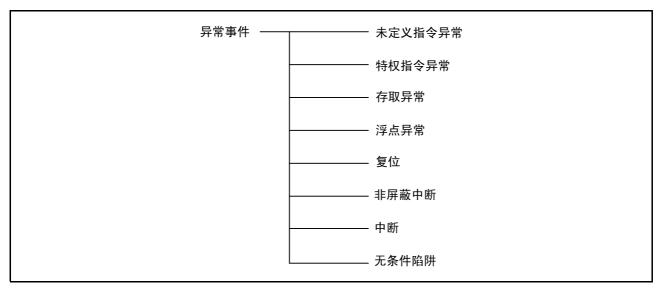

|         | <del>〜</del> 工<br>常事件              |     |

| 13.1.1  | 未定义指令异常                            |     |

| 13.1.2  | 特权指令异常                             |     |

| 13.1.3  | 存取异常                               |     |

|         | 泛 占 是 堂                            | 162 |

| 13.1.5             | 复位                                       | 162 |

|--------------------|------------------------------------------|-----|

| 13.1.6             | 非屏蔽中断                                    | 162 |

| 13.1.7             | 中断                                       | 162 |

| 13.1.8             | 无条件陷阱                                    | 162 |

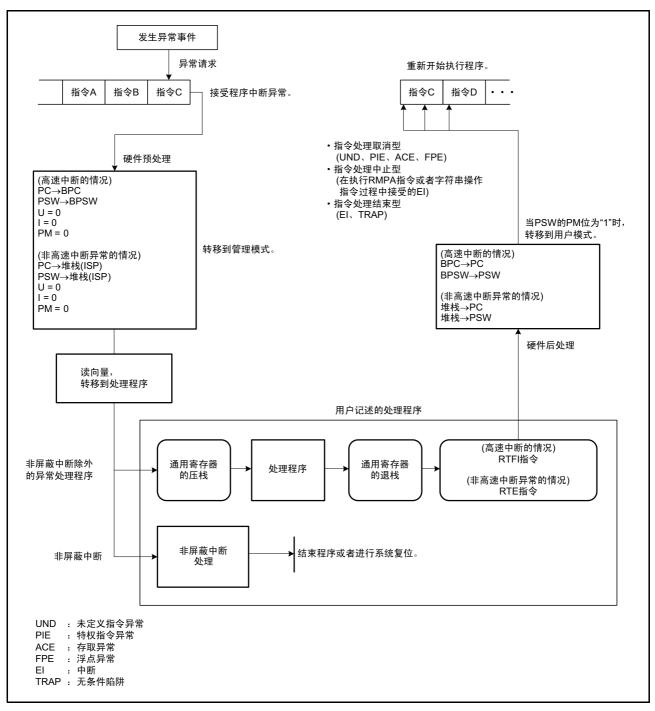

| 13.2 异             | 常处理步骤                                    | 163 |

| 13.3 异             | 常事件的接受                                   | 165 |

| 13.3.1             | 接受时序和被保存的 PC 值                           | 165 |

| 13.3.2             | 向量和 PC、 PSW 的保存位置                        | 165 |

| 13.4 接             | 受异常 / 从异常返回时的硬件处理                        | 166 |

| 13.5 硬             | 件预处理                                     | 167 |

| 13.5.1             | 未定义指令异常                                  | 167 |

| 13.5.2             | 特权指令异常                                   | 167 |

| 13.5.3             | 存取异常                                     | 167 |

| 13.5.4             | 浮点异常                                     | 167 |

| 13.5.5             | 复位                                       | 167 |

| 13.5.6             | 非屏蔽中断                                    | 168 |

| 13.5.7             | 中断                                       | 168 |

| 13.5.8             | 无条件陷阱                                    | 168 |

| 13.6 从             | 异常处理程序的返回                                | 169 |

| 13.7 异             | 常事件的优先级                                  | 169 |

| I nter             |                                          |     |

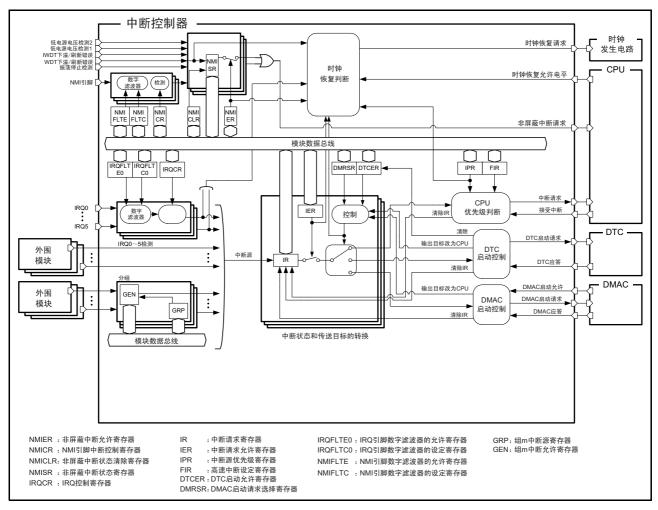

|                    | 控制器(ICUb)                                |     |

| ***                | 要                                        |     |

|                    | 存器说明                                     |     |

| 14.2.1             | 中断请求寄存器 n (IRn) (n= 中断向量号)               |     |

| 14.2.2             | 中断请求允许寄存器 m (IERm) (m=02h ~ 1Fh)         |     |

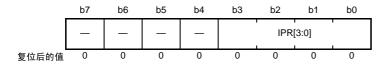

| 14.2.3             | 中断源优先级寄存器 n (IPRn) (n=000 ~ 250)         |     |

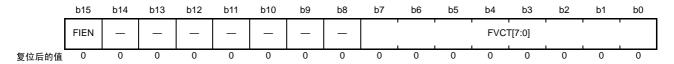

| 14.2.4             | 高速中断设定寄存器(FIR)                           |     |

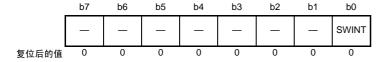

| 14.2.5             | 软件中断启动寄存器 (SWINTR)                       |     |

| 14.2.6             | DTC 启动允许寄存器 n (DTCERn) (n= 中断向量号)        |     |

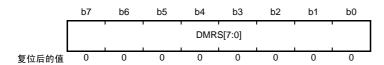

| 14.2.7             | DMAC 启动请求选择寄存器 m (DMRSRm)(m=DMAC 通道号)    |     |

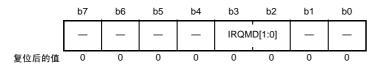

| 14.2.8             | IRQ 控制寄存器 i(IRQCRi)(i=0~5)               |     |

| 14.2.9             | IRQ 引脚数字滤波器的允许寄存器 0 (IRQFLTE0)           |     |

| 14.2.10            | (1,1,1,2,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1 |     |

| 14.2.11            | 11 // 11 // 12 / 13 / 14 HI (17/11/2017) |     |

| 14.2.12            | 11 /2 1 1/2 2 1 1/4 1/4 1/4              |     |

| 14.2.13            |                                          |     |

| 14.2.14            |                                          |     |

| 14.2.15<br>14.2.16 |                                          |     |

| 14.2.10            |                                          |     |

| 14.2.17            |                                          |     |

|                    | 量表                                       |     |

| 14.3  HJ           | 里衣                                       |     |

| 14.3.1             | 市断问重衣<br>高速中断的向量表地址                      |     |

| 14.3.2             | 非屏蔽中断的向量表地址                              |     |

|                    | 围模块中断请求组的功能                              |     |

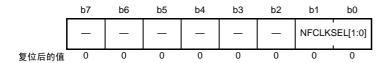

| 14.4 9r<br>14.4.1  | 中断请求组                                    |     |

|                    | 断的运行说明                                   |     |

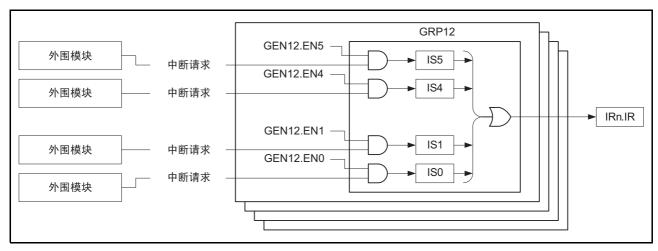

| 14.5 +             | 中断检测                                     |     |

| 14.5.1             | 中断请求的允许 / 禁止                             |     |

| 14.5.2             | 中断请求目标的选择                                |     |

| 17.5.5             | 91 1747 日 707日 7021十                     |     |

| 14.5.4                                     | 优先级的判断                                    | 204 |

|--------------------------------------------|-------------------------------------------|-----|

| 14.5.4                                     | 高速中断                                      |     |

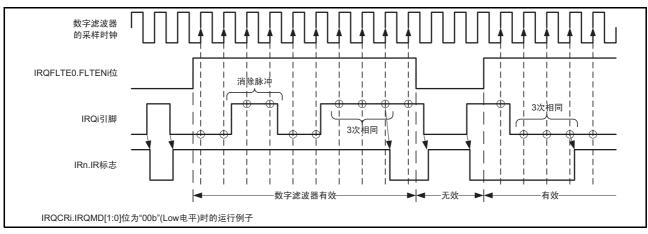

| 14.5.6                                     | 数字滤波器                                     |     |

| 14.5.7                                     | 数于滤波器···································· |     |

|                                            | 帮前为两个别<br>帮蔽中断的运行说明                       |     |

|                                            | · 城中朝的运行 说明                               |     |

| 14.7 //\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | 以耗状态的返回                                   |     |

|                                            | 从全模块时钟停止模式的返回                             |     |

| 14.7.2                                     |                                           |     |

| 14.7.3                                     | 从软件待机模式的返回                                |     |

|                                            | ]时的注意事项<br>使用非屏蔽中断时的 WAIT 指令的注意事项         |     |

| 14.8.1                                     | 使用非屏敝中断时的 WAII 指令的注息争项                    |     |

| 15. 总线.                                    |                                           | 208 |

| 15.1 概要                                    | i                                         |     |

| ,,                                         | ·<br>注说明                                  |     |

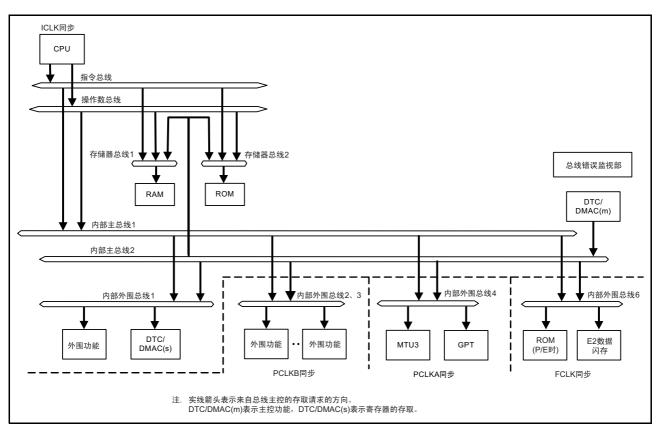

| 15.2.1                                     | CPU 总线                                    |     |

| 15.2.2                                     | 存储器总线                                     |     |

| 15.2.3                                     | 内部主总线                                     |     |

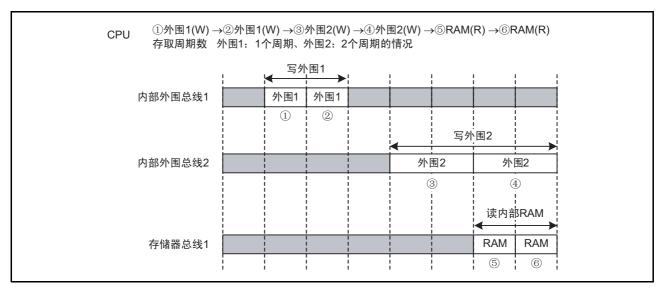

| 15.2.4                                     | 内部外围总线                                    |     |

| 15.2.5                                     | 写缓冲器功能 (内部外围总线)                           |     |

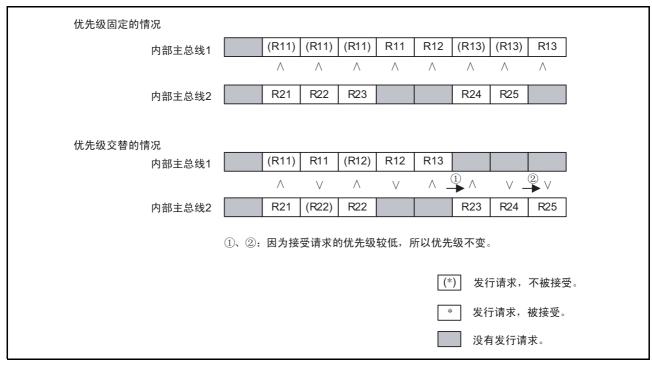

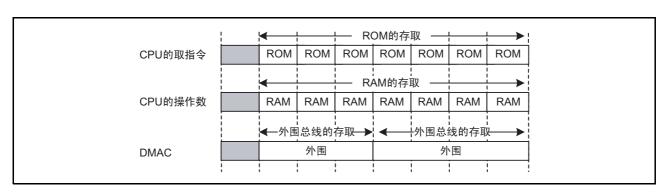

| 15.2.6                                     | 并行运行                                      |     |

| 15.2.7                                     | 限制事项                                      |     |

|                                            | · King + · A                              |     |

| 15.3.1                                     | 总线错误状态清除寄存器(BERCLR)                       |     |

| 15.3.2                                     | 总线错误监视允许寄存器(BEREN)                        |     |

| 15.3.3                                     | 总线错误状态寄存器 1(BERSR1)                       |     |

| 15.3.4                                     | 总线错误状态寄存器 2(BERSR2)                       |     |

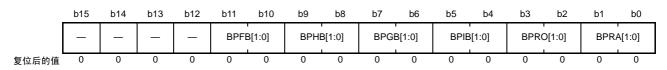

| 15.3.5                                     | 总线优先级控制寄存器(BUSPRI)                        |     |

|                                            | 法错误监视部                                    |     |

| 15.4.1                                     | 总线错误的种类                                   |     |

| 15.4.2                                     | 发生总线错误时的运行                                |     |

| 15.4.3                                     | 总线错误的发生条件                                 |     |

|                                            |                                           |     |

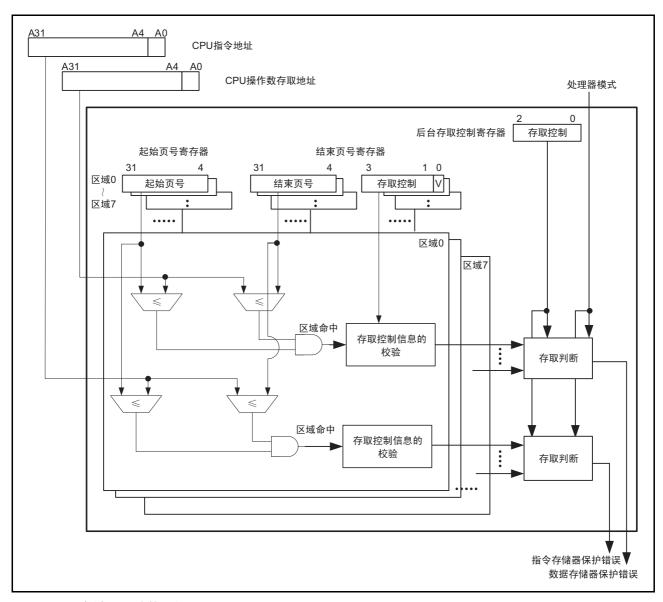

| 16. 存储器                                    | B保护单元 (MPU)                               | 219 |

| 16.1 概要                                    | •                                         |     |

| 16.1.1                                     | 存取控制的种类                                   |     |

| 16.1.2                                     | 存取控制区域                                    | 221 |

| 16.1.3                                     | 后台区域                                      |     |

| 16.1.4                                     | 区域的重叠                                     |     |

| 16.1.5                                     | 跨区域的指令和数据                                 |     |

| 16.2 寄存                                    | ·器说明                                      |     |

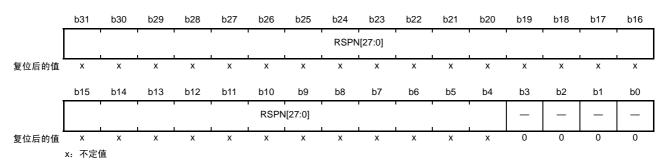

| 16.2.1                                     | 区域 n 起始页号寄存器 (RSPAGEn)(n=0 $\sim$ 7)      |     |

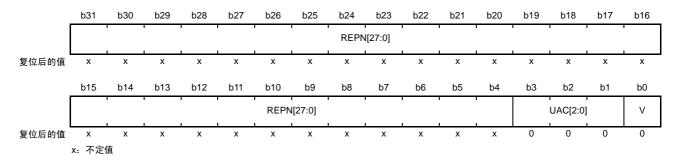

| 16.2.2                                     | 区域 n 结束页号寄存器 (REPAGEn)(n=0 $\sim$ 7)      |     |

| 16.2.3                                     | 存储器保护功能有效化寄存器 (MPEN)                      | 224 |

| 16.2.4                                     | 后台存取控制寄存器 (MPBAC)                         |     |

| 16.2.5                                     | 存储器保护错误状态清除寄存器(MPECLR)                    |     |

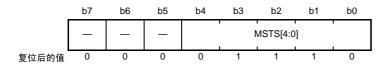

| 16.2.6                                     | 存储器保护错误状态寄存器 (MPESTS)                     | 227 |

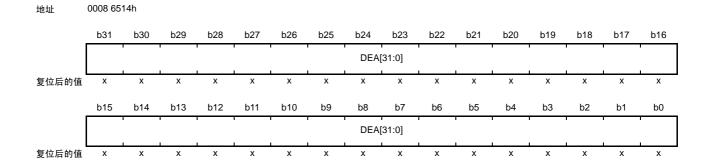

| 16.2.7                                     | 数据存储器保护错误地址寄存器 (MPDEA)                    | 228 |

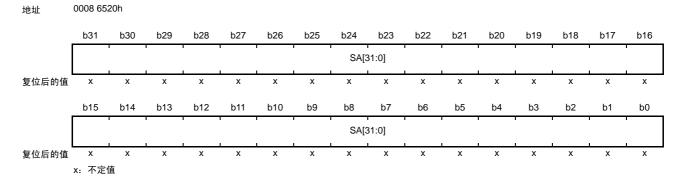

| 16.2.8                                     | 区域查找地址寄存器 (MPSA)                          | 228 |

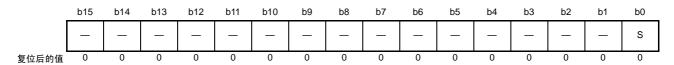

| 16.2.9                                     | 区域查找操作寄存器 (MPOPS)                         | 229 |

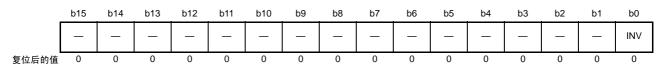

| 16.2.10                                    | 区域无效化操作寄存器 (MPOPI)                        | 229 |

| 16.2.11                                    | 指令命中区域寄存器(MHITI)                          | 230 |

| 16.2.12    | 数据命中区域寄存器 (MHITD)                                                                              | 232 |

|------------|------------------------------------------------------------------------------------------------|-----|

| 16.3 功能    |                                                                                                | 234 |

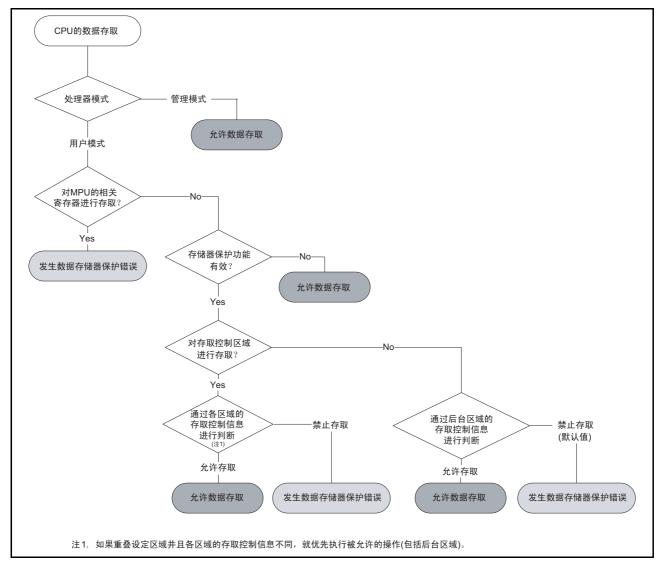

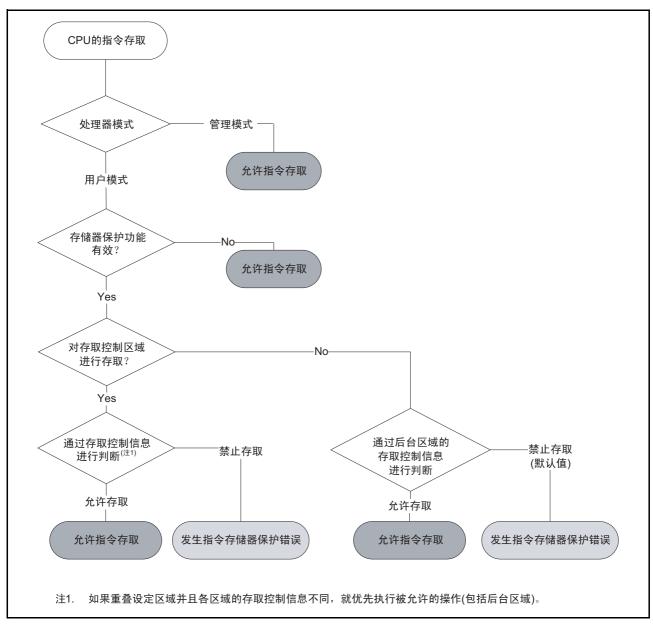

| 16.3.1     | 存储器保护功能                                                                                        | 234 |

| 16.3.2     | 区域查找功能                                                                                         |     |

| 16.3.3     | 存储器保护单元相关寄存器的保护                                                                                |     |

| 16.3.4     | 存储器保护功能的存取判断流程                                                                                 |     |

| 16.4 存储    | 器保护功能的使用步骤                                                                                     | 237 |

| 16.4.1     | 存取控制信息的设定                                                                                      | 237 |

| 16.4.2     | 存储器保护功能的有效化                                                                                    | 237 |

| 16.4.3     | 向用户模式的转移                                                                                       |     |

| 16.4.4     | 发生存储器保护错误时的处理                                                                                  |     |

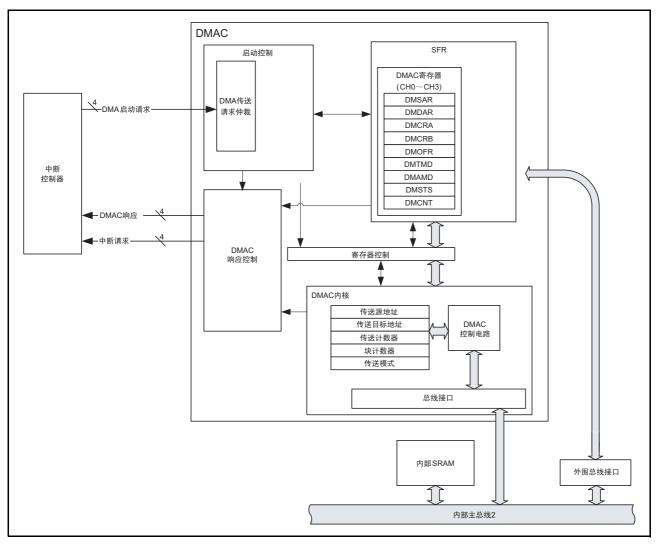

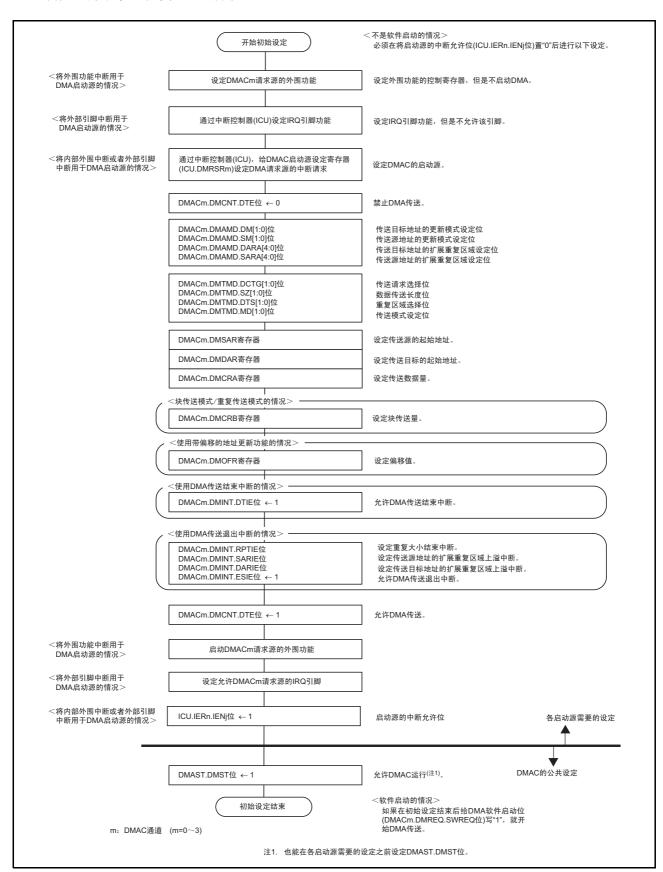

| 17 DMA :   | 空制器 (DMACA)                                                                                    | 230 |

|            |                                                                                                |     |

|            | 器说明                                                                                            |     |

| 17.2.1     | DMA 传送源地址寄存器 (DMSAR)                                                                           |     |

| 17.2.1     | DMA 传送目标地址寄存器 (DMDAR)                                                                          |     |

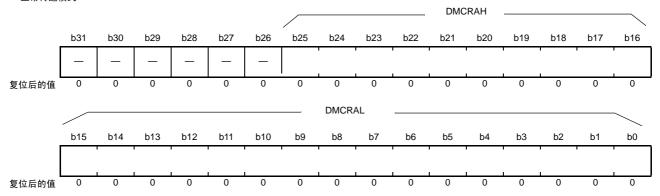

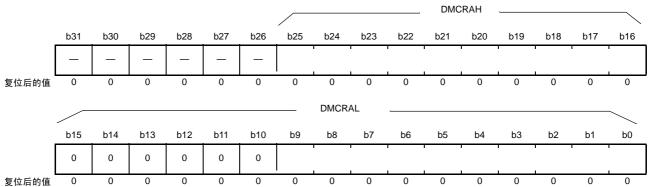

| 17.2.2     | DMA 传送计数寄存器 (DMCRA)                                                                            |     |

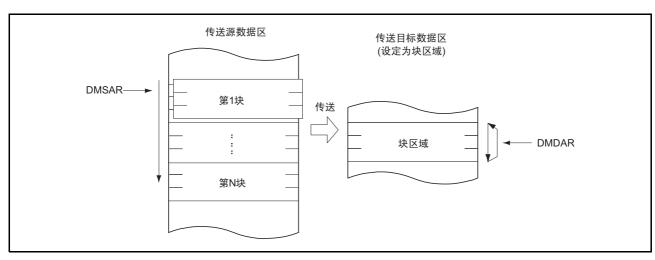

| 17.2.3     | DMA 块传送计数寄存器 (DMCRB)                                                                           |     |

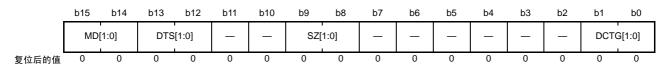

| 17.2.4     | DMA 失传这样数可存储(DMCRD)  DMA 传送模式寄存器 (DMTMD)                                                       |     |

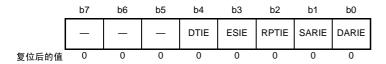

| 17.2.5     | DMA 中断设定寄存器 (DMINT)                                                                            |     |

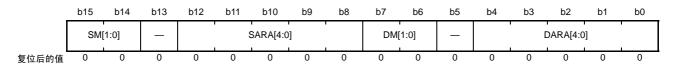

| 17.2.0     | DMA 地址模式寄存器 (DMAMD)                                                                            |     |

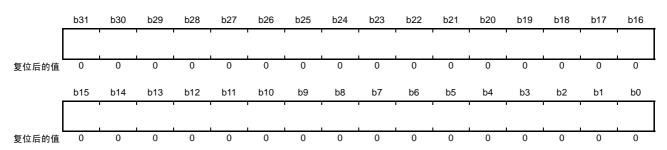

| 17.2.7     | DMA 偏移寄存器 (DMOFR)                                                                              |     |

| 17.2.8     | DMA 传送允许寄存器 (DMCNT)                                                                            |     |

| 17.2.9     | DMA 软件启动寄存器 (DMREQ)                                                                            |     |

| 17.2.10    | DMA 状态寄存器 (DMSTS)                                                                              |     |

| 17.2.11    | DMA <b></b>                                                                                    |     |

| 17.2.12    | DMA 相切條件心控制可存备(DMCSL)  DMA 模块启动寄存器 (DMAST)                                                     |     |

|            | - DMA 侯吠后幼司任益(DMAS1)                                                                           |     |

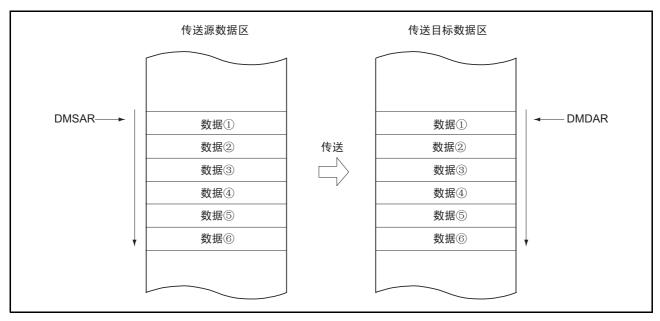

| 17.3 A1    | 传送模式                                                                                           |     |

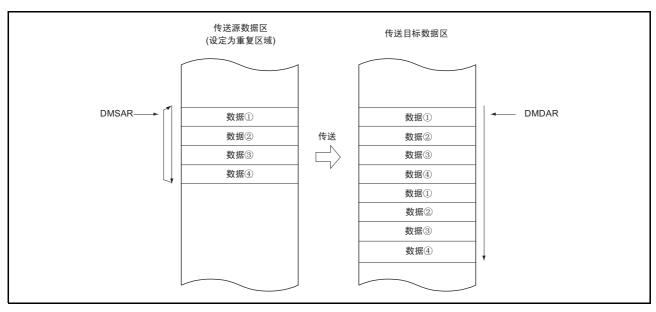

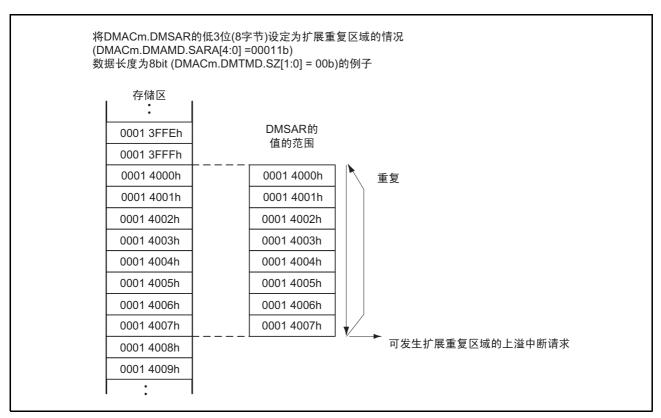

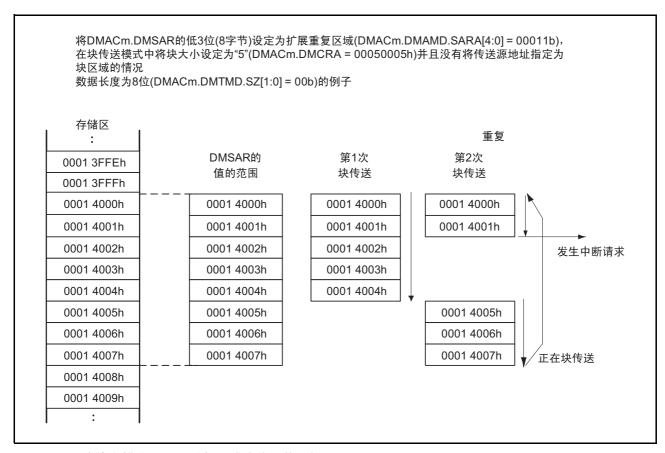

| 17.3.1     | 扩展重复区域功能                                                                                       |     |

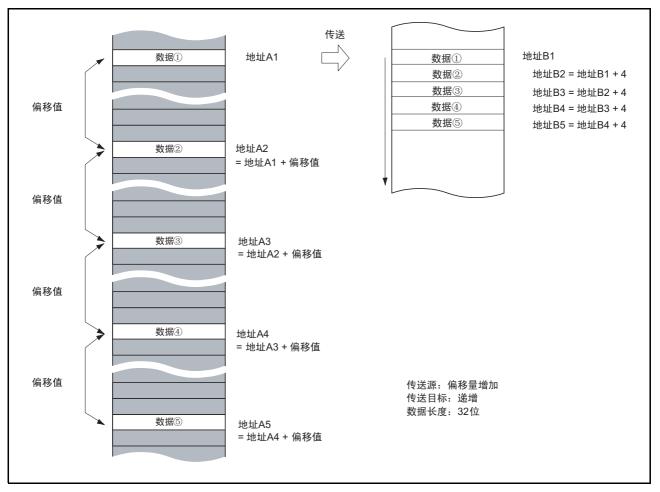

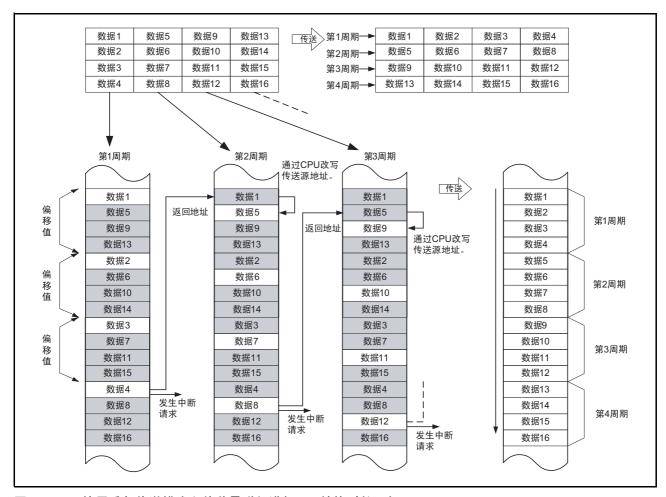

| 17.3.2     | 带偏移的地址更新功能                                                                                     |     |

| 17.3.4     | 启动源                                                                                            |     |

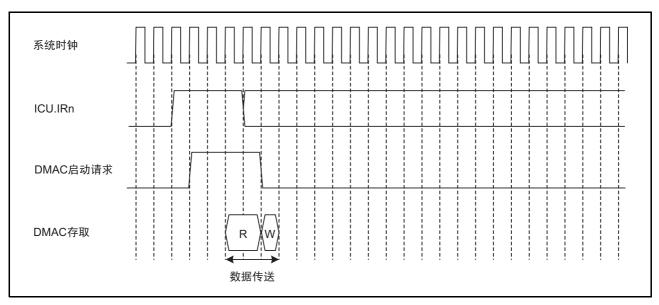

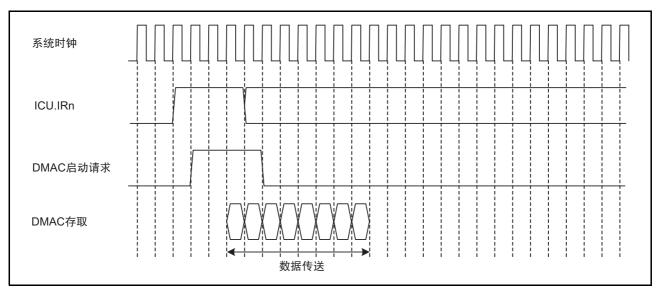

| 17.3.4     | 运行时序                                                                                           |     |

| 17.3.5     | DMAC 的执行周期                                                                                     |     |

| 17.3.7     | DMAC 的风行 / 河河                                                                                  |     |

| 17.3.7     | DMA 传送的开始                                                                                      |     |

| 17.3.9     | DMA 传送过程中的寄存器                                                                                  |     |

| 17.3.10    | 通道的优先级                                                                                         |     |

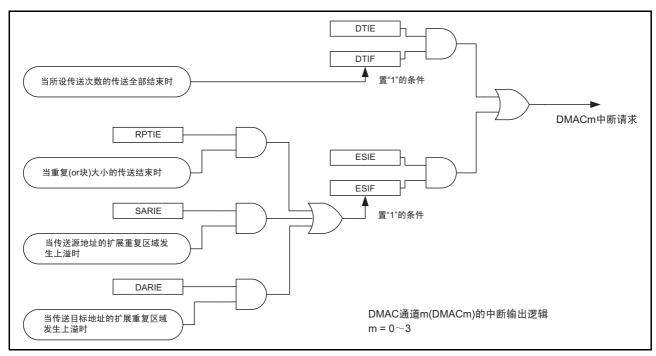

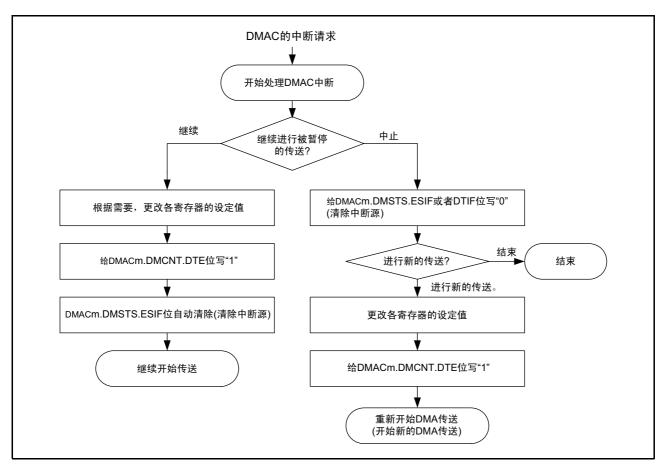

|            | <b>A</b> 传送的结束                                                                                 |     |

| 17.4 DIVIZ | 通过设定的总数据传送结束传送                                                                                 |     |

| 17.4.1     | 通过重复大小结束中断结束传送                                                                                 |     |

| 17.4.3     | 通过扩展重复区域上溢中断结束传送                                                                               |     |

|            | 是是D                                                                                            |     |

|            | 耗功能                                                                                            |     |

|            | 时的注意事项                                                                                         |     |

| 17.7 风雨    | 外围模块的 <b>DMA</b> 传送情况                                                                          |     |

| 17.7.1     | 有关 DMA 运行过程中的寄存器存取                                                                             |     |

| 17.7.2     | 有关保留区的 DMA 传送                                                                                  |     |

| 17.7.3     | 因设定 DMA 启动源标志控制寄存器 (DMCSL)而产生的各传送结束中断请求                                                        |     |

| 17.7.5     | 中断控制器的 DMAC 启动请求寄存器 (ICU.DMRSRm)的设定                                                            |     |

| 17.7.6     | 保留或者重新开始 DMA 启动的方法                                                                             |     |

| 2          | NI- EN - 24 EL - 1-4/17   7 EL - 24 EL - 24 EL 4/4   EN - 1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1- |     |

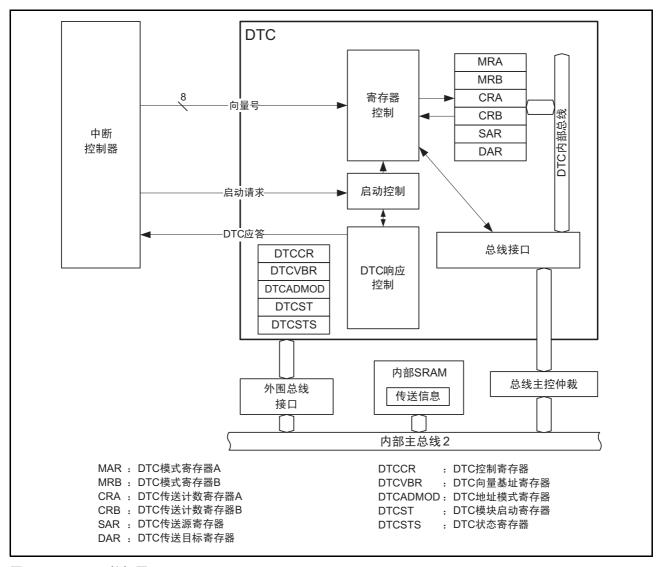

| 18. 数据传    | 送控制器 (DTCa)                        | 273 |

|------------|------------------------------------|-----|

| 18.1 概要    |                                    | 273 |

| 18.2 寄存    | 器说明                                | 275 |

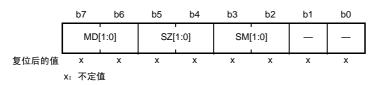

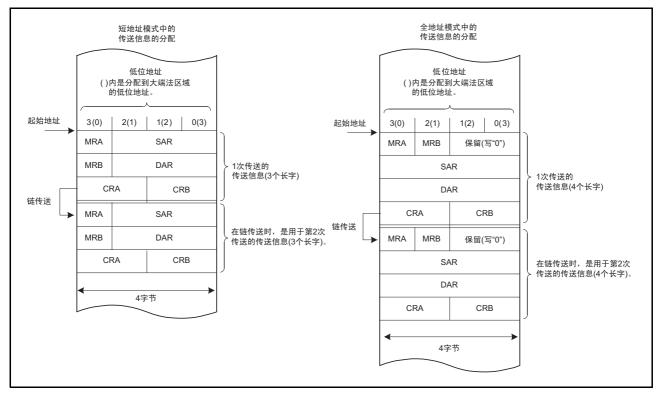

| 18.2.1     | DTC 模式寄存器 A (MRA)                  | 275 |

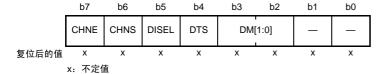

| 18.2.2     | DTC 模式寄存器 B (MRB)                  | 276 |

| 18.2.3     | DTC 传送源寄存器 (SAR)                   | 277 |

| 18.2.4     | DTC 传送目标寄存器 (DAR)                  | 277 |

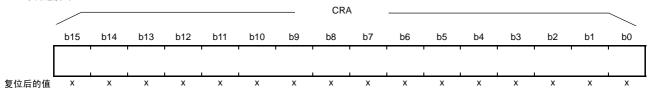

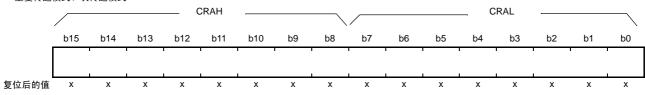

| 18.2.5     | DTC 传送计数寄存器 A (CRA)                | 278 |

| 18.2.6     | DTC 传送计数寄存器 B (CRB)                | 279 |

| 18.2.7     | DTC 控制寄存器 (DTCCR)                  | 279 |

| 18.2.8     | DTC 向量基址寄存器 (DTCVBR)               | 280 |

| 18.2.9     | DTC 地址模式寄存器 (DTCADMOD)             | 280 |

| 18.2.10    | DTC 模块启动寄存器 (DTCST)                |     |

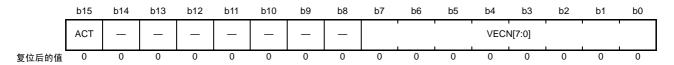

| 18.2.11    | DTC 状态寄存器 (DTCSTS)                 | 282 |

| 18.3 启动    | 源                                  |     |

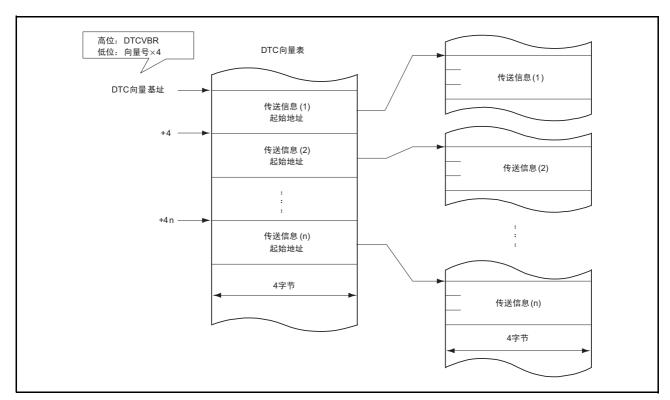

| 18.3.1     | 传送信息的分配和 DTC 向量表                   |     |

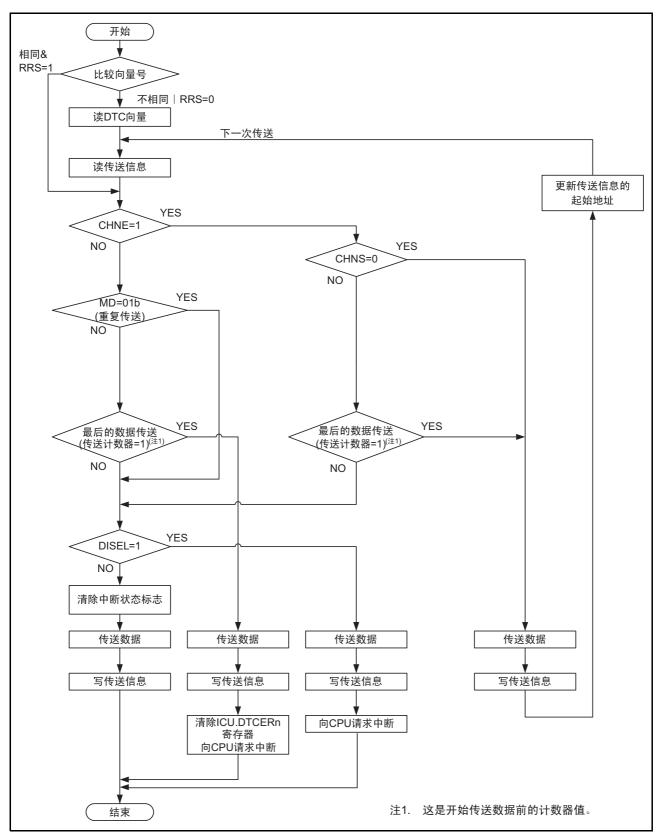

| 18.4 运行    | 说明                                 |     |

| 18.4.1     | 传送信息的跳读功能                          | 286 |

| 18.4.2     | 传送信息的回写省略功能                        |     |

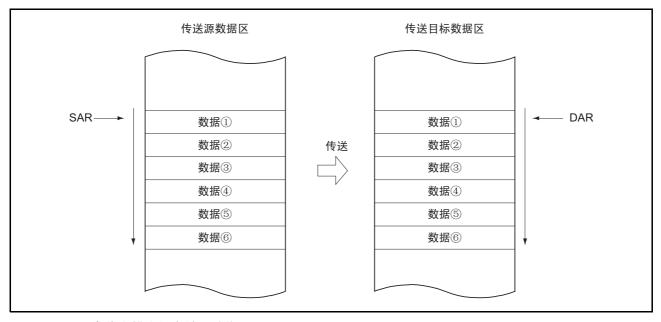

| 18.4.3     | 正常传送模式                             |     |

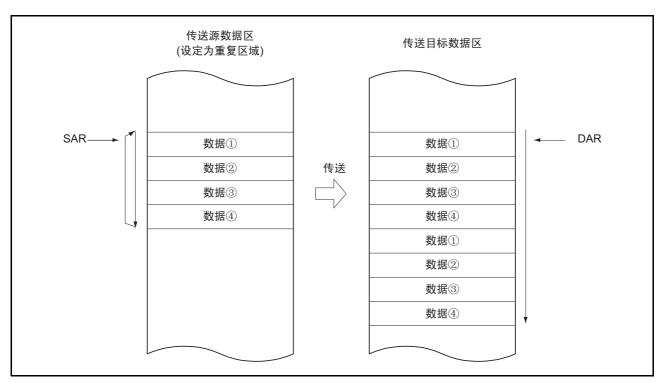

| 18.4.4     | 重复传送模式                             | 289 |

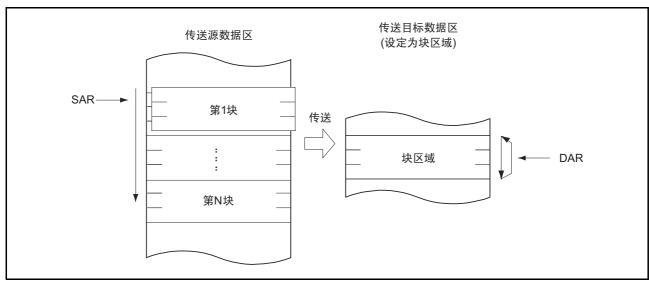

| 18.4.5     | 块传送模式                              |     |

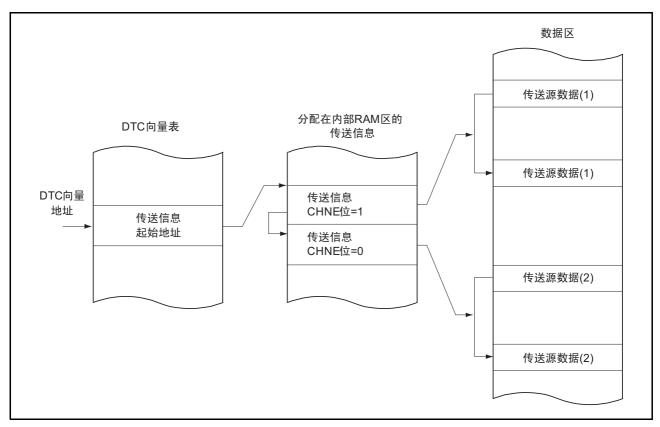

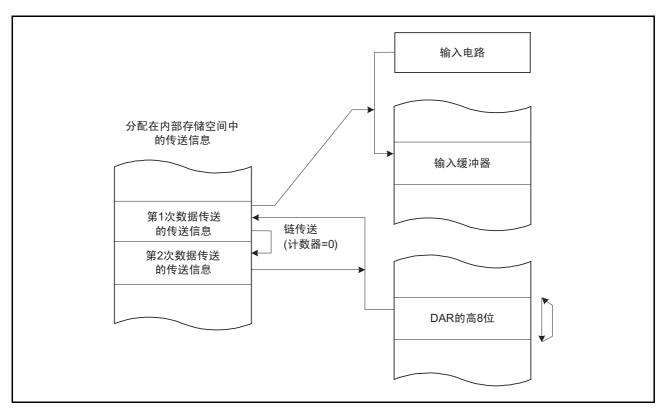

| 18.4.6     | 链传送                                |     |

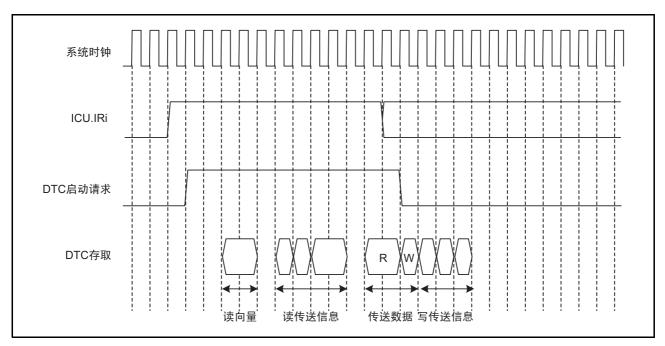

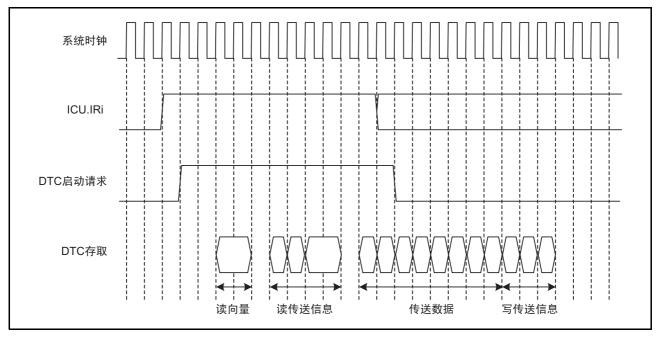

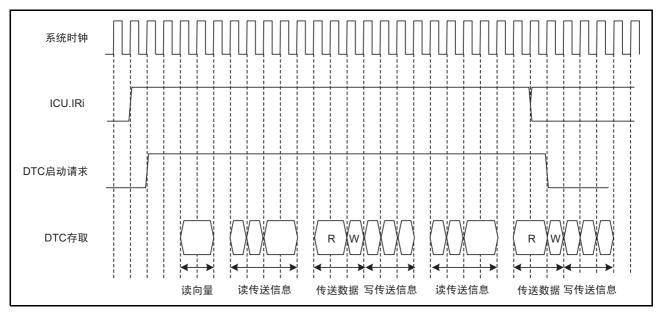

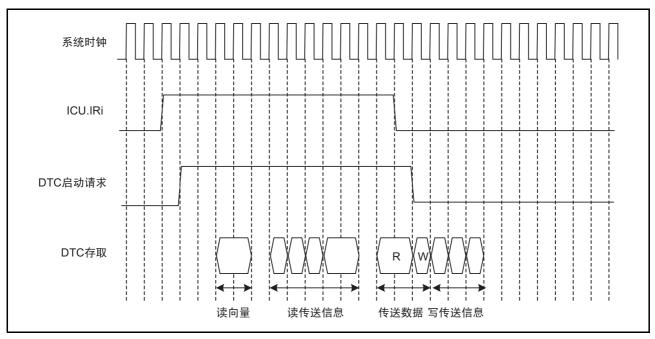

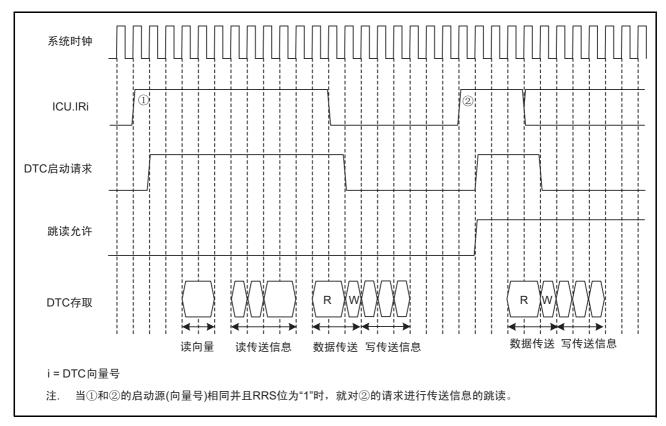

| 18.4.7     | 运行时序                               |     |

| 18.4.8     | DTC 的执行周期                          |     |

| 18.4.9     | DTC 的总线权释放时序                       |     |

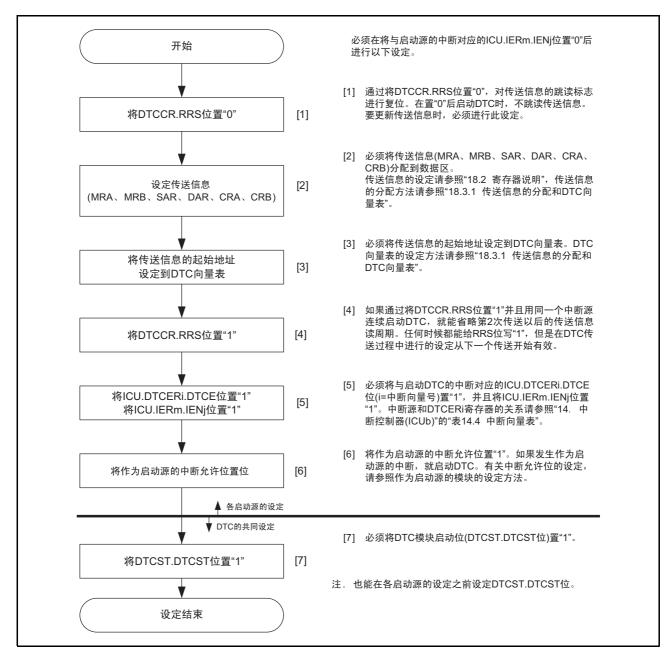

|            | 的设定步骤                              |     |

|            | 的使用例子                              |     |

| 18.6.1     | 正常传送                               |     |

| 18.6.2     | 计数器为 "0" 时的链传送                     |     |

|            | 源                                  |     |

|            | 耗功能                                |     |

|            | 时的注意事项                             |     |

| 18.9.1     | 传送信息起始地址 / 传送源地址 / 传送目标地址          |     |

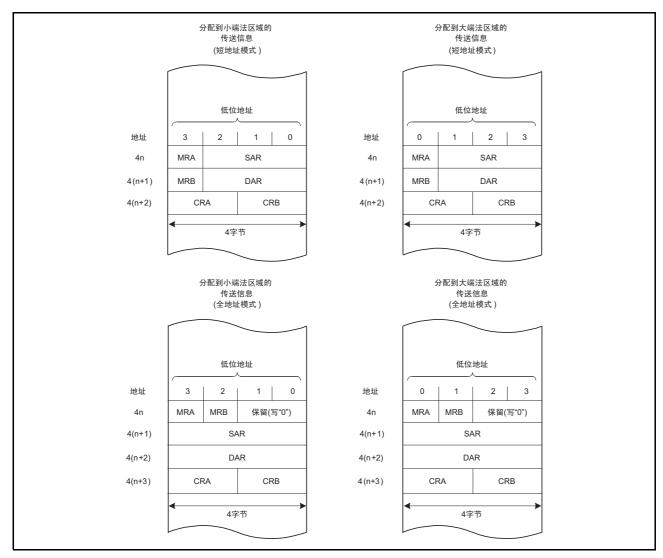

|            | 传送信息的分配                            |     |

| 18.9.3     | 中断控制器的 DTC 启动允许寄存器 (ICU.DTCERn)的设定 | 300 |

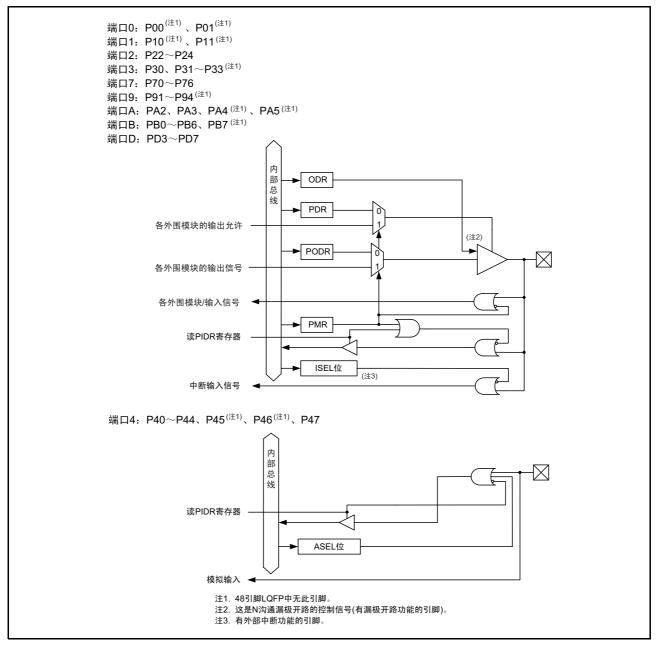

| 19. I/O 端I | <u> </u>                           | 301 |

|            |                                    |     |

| ,,         | / 输出端口的结构                          |     |

|            | 7 棚田桐口切知村<br>器说明                   |     |

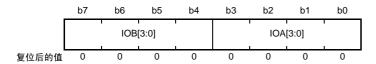

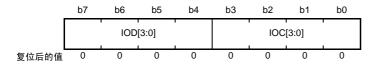

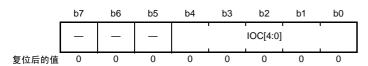

| 19.3.1     | 端口方向寄存器 (PDR)                      |     |

| 19.3.1     | 端口菊田菊仔舔(PDR)端口输出数据寄存器(PODR)        |     |

| 19.3.2     | 端口输入数据寄存器(PIDR)                    |     |

| 19.3.3     | 端口模式寄存器(PMR)                       |     |

| 19.3.4     | 漏口侯八司行命(FMK)                       |     |

| 19.3.5     | 漏极开路控制寄存器 1 (ODR1)                 |     |

|            | 用引脚的外理                             | 308 |

| 20. 多功             | 能引脚控制器 (MPC)                                                      | 309  |

|--------------------|-------------------------------------------------------------------|------|

| 20.1 概             | 要                                                                 | 309  |

| 20.2 寄             | 存器说明                                                              | 312  |

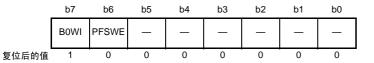

| 20.2.1             | 写保护寄存器 (PWPR)                                                     | 312  |

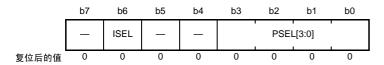

| 20.2.2             | P0n 引脚功能控制寄存器 (P0nPFS) (n=0、1)                                    | 313  |

| 20.2.3             | Pln 引脚功能控制寄存器 (PlnPFS) (n=0、1)                                    | 314  |

| 20.2.4             | P2n 引脚功能控制寄存器 (P2nPFS) (n=2 ~ 4)                                  | 315  |

| 20.2.5             | P3n 引脚功能控制寄存器 (P3nPFS) (n=0~3)                                    | 316  |

| 20.2.6             | P4n 引脚功能控制寄存器 (P4nPFS)(n=0 $\sim$ 7)                              | 317  |

| 20.2.7             | P7n 引脚功能控制寄存器 (P7nPFS)(n=0 $\sim$ 6)                              | 317  |

| 20.2.8             | P9n 引脚功能控制寄存器 (P9nPFS) (n=1 ~ 4)                                  | 318  |

| 20.2.9             | PAn 引脚功能控制寄存器 (PAnPFS) (n=2 ~ 5)                                  | 319  |

| 20.2.10            | PBn 引脚功能控制寄存器 (PBnPFS) (n=0 ~ 7)                                  | 320  |

| 20.2.11            | PDn 引脚功能控制寄存器 (PDnPFS) (n=3 ~ 7)                                  | 322  |

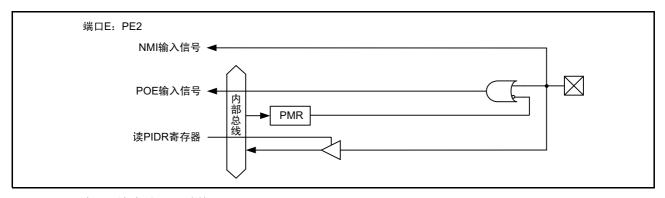

| 20.2.12            | PE2 引脚功能控制寄存器 (PE2PFS)                                            | 322  |

| 20.3 使             | 用时的注意事项                                                           | 323  |

| 20.3.1             | 引脚输入/输出功能的设定步骤                                                    | 323  |

| 20.3.2             | 设定 MPC 寄存器时的注意事项                                                  |      |

| 20.3.3             | 使用模拟功能时的注意事项                                                      | 323  |

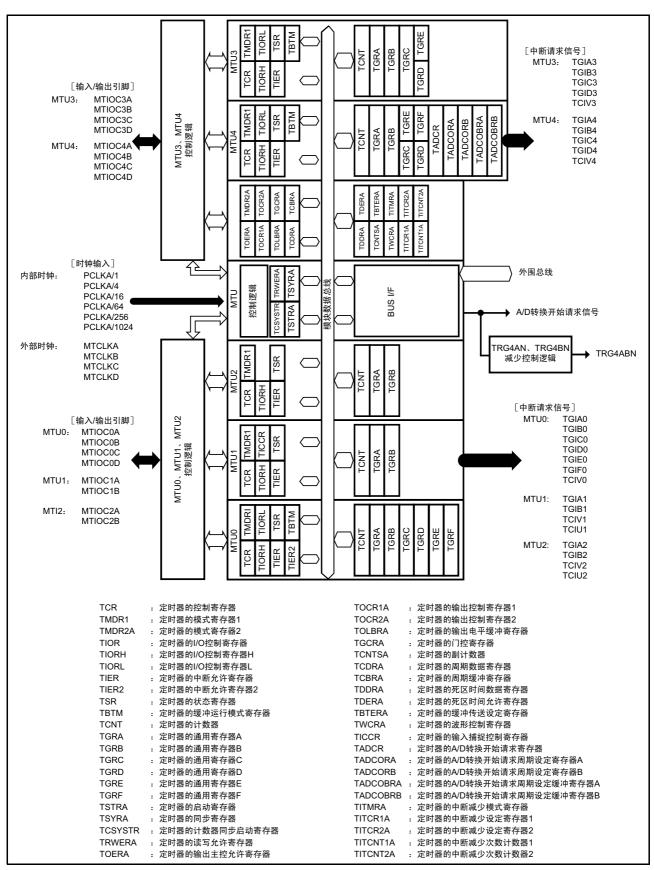

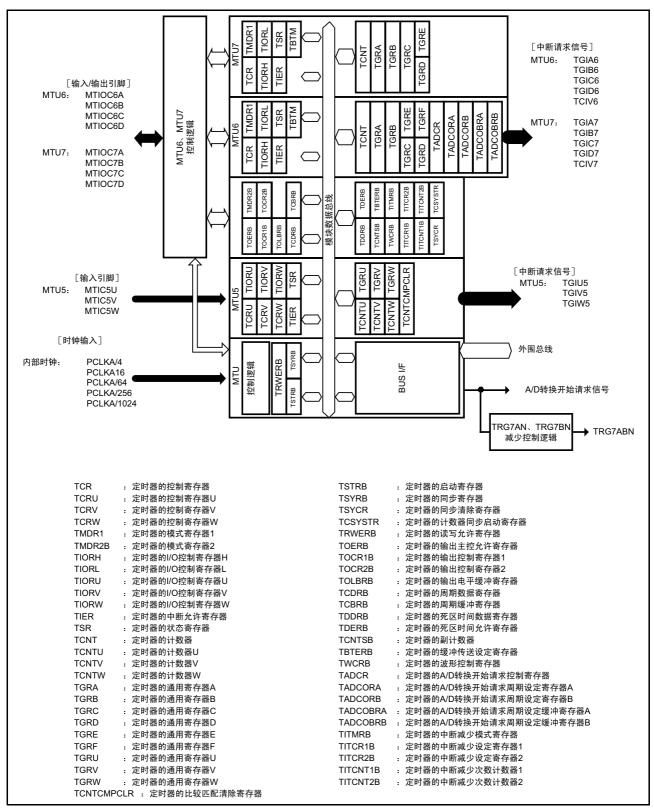

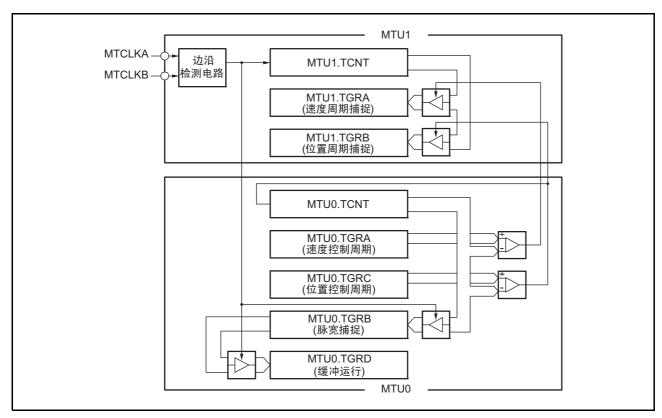

| 04 성대              | 能定时器脉冲单元 3 (MTU3)                                                 | 20.4 |

|                    | 能走門爺脉冲車儿3(MTU3)要                                                  |      |

| ***                | 安<br>存器说明                                                         |      |

| 21.2 可·<br>21.2.1  | 任命说明<br>定时器的控制寄存器 (TCR)                                           |      |

|                    | 定时器的模式寄存器 1 (TMDR1)                                               |      |

| 21.2.2             | 定时器的模式寄存器 2 (TMDR2A、 TMDR2B)                                      |      |

| 21.2.3             | 定时器的 I/O 控制寄存器 (TIOR)                                             |      |

| 21.2.4             | 定时器的比较匹配清除寄存器(TCNTCMPCLR)                                         |      |

| 21.2.5             | 定时器的中断允许寄存器(TER)定时器的中断允许寄存器(TIER)                                 |      |

| 21.2.6             | 定时器的状态寄存器 (TSR)                                                   |      |

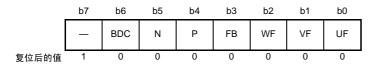

| 21.2.7             | 定时器的缓冲运行传送模式寄存器 (TBTM)                                            |      |

| 21.2.8             |                                                                   |      |

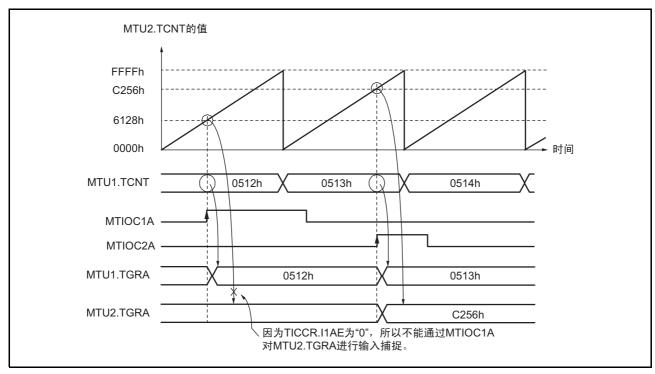

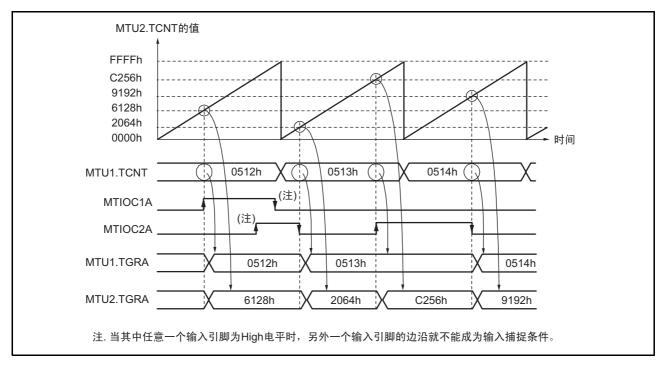

| 21.2.9             | 定时器的输入捕捉控制寄存器(TICCR)                                              |      |

| 21.2.10            | 定时器的同步清除寄存器 (TSYCR)<br>定时器的计数器 (TCNT)                             |      |

| 21.2.11<br>21.2.12 |                                                                   |      |

|                    |                                                                   |      |

| 21.2.13            | / C                                                               |      |

| 21.2.14            | )C. 1                                                             |      |

| 21.2.15            |                                                                   |      |

| 21.2.16            | )C: 4 HH H4 ()( 4)(4)   14 HH ( ================================= |      |

| 21.2.17            | 定时器的输出主控允许寄存器 (TOER) 定时器的输出控制寄存器 1 (TOCR1A、TOCR1B)                |      |

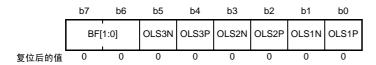

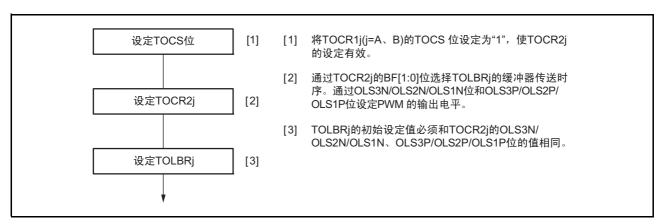

| 21.2.18            |                                                                   |      |

| 21.2.19            | / =                                                               |      |

| 21.2.20            | 7 = 1 7 = 7 111                                                   |      |

| 21.2.21            | 定时器的门控寄存器 A (TGCRA)                                               |      |

| 21.2.22            | , e , iii ii, , p, , , , , , , iii ii ii ii ii ii ii ii i         |      |

| 21.2.23            | 7 = 1                                                             |      |

| 21.2.24            | / =                                                               |      |

| 21.2.25            | 7 = 1 7 = 17 11                                                   |      |

| 21.2.26            | , = ,, ,                                                          |      |

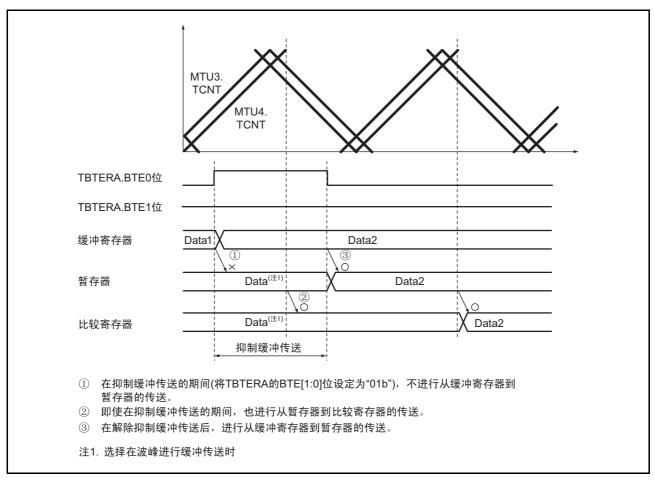

| 21.2.27            | 定时器的缓冲传送设定寄存器(TBTERA、TBTERB)                                      |      |

| 21.2.28            | / · · · · · · · · · · · · · · · · · · ·                           |      |

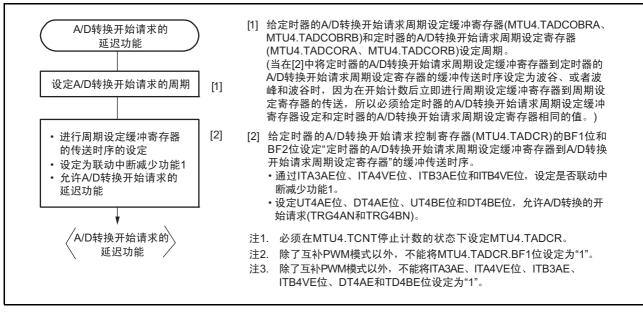

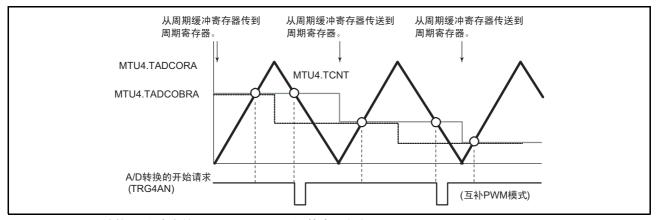

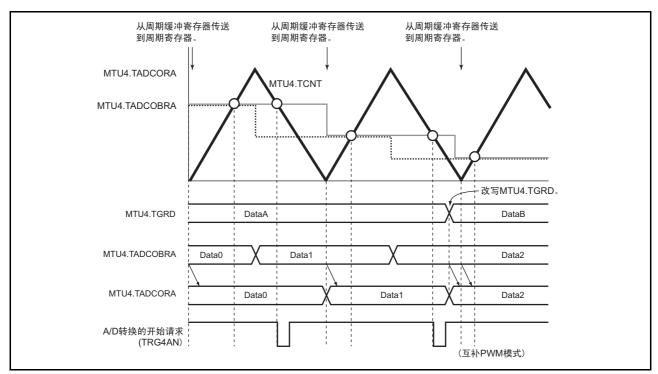

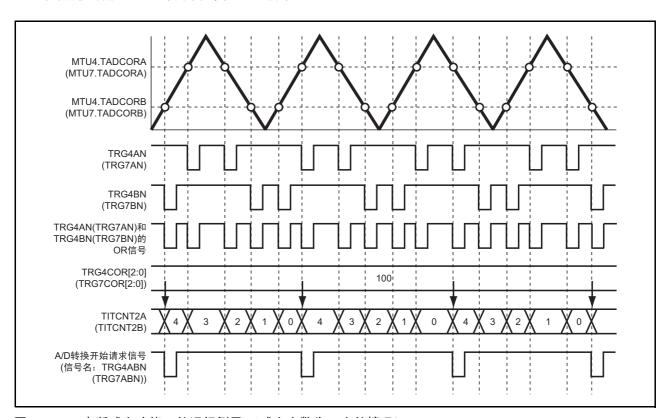

| 21.2.29            | 定时器的 A/D 转换开始请求控制寄存器 (TADCR)                                      | 383  |

| 21.2.30 | 定时器的 A/D 转换开始请求周期设定寄存器 (TADCORA、TADCORB)      | 387 |

|---------|-----------------------------------------------|-----|

| 21.2.31 | 定时器的 A/D 转换开始请求周期设定缓冲寄存器 (TADCOBRA、 TADCOBRB) | 387 |

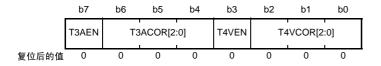

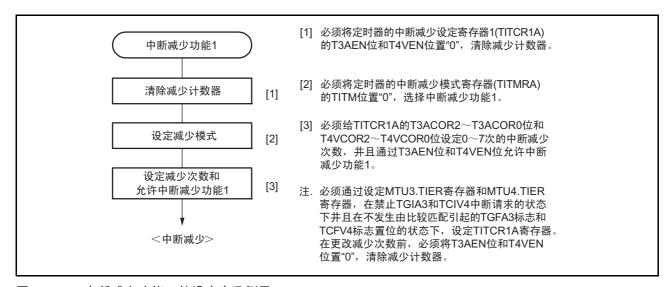

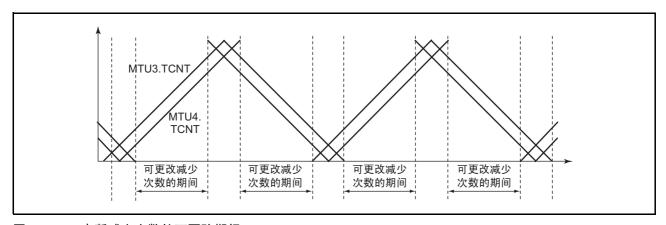

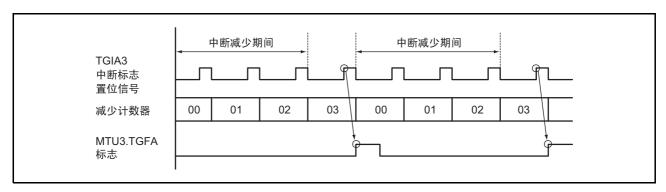

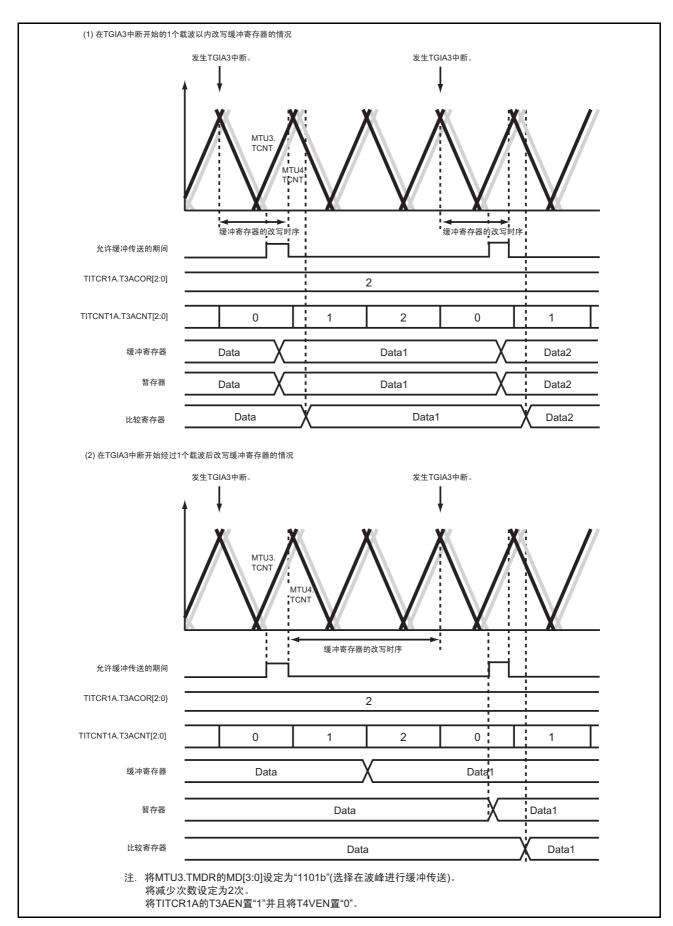

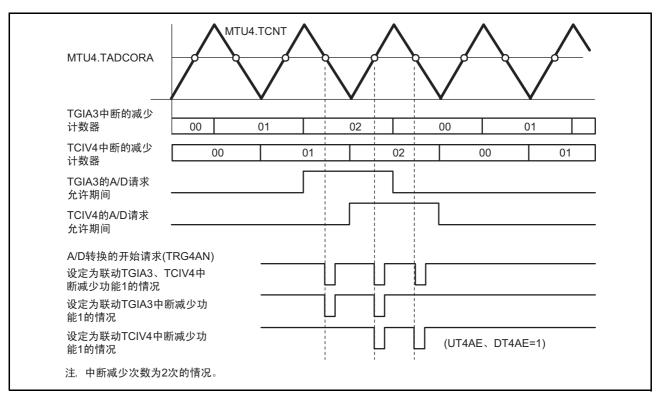

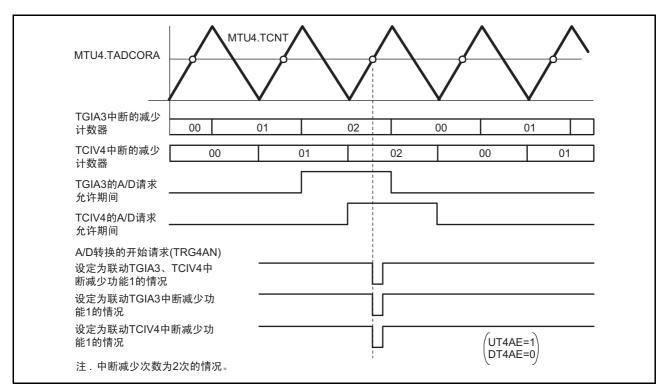

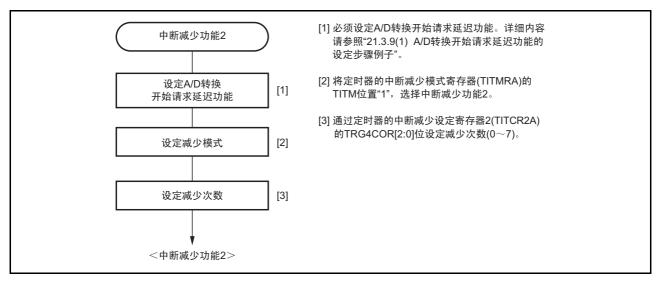

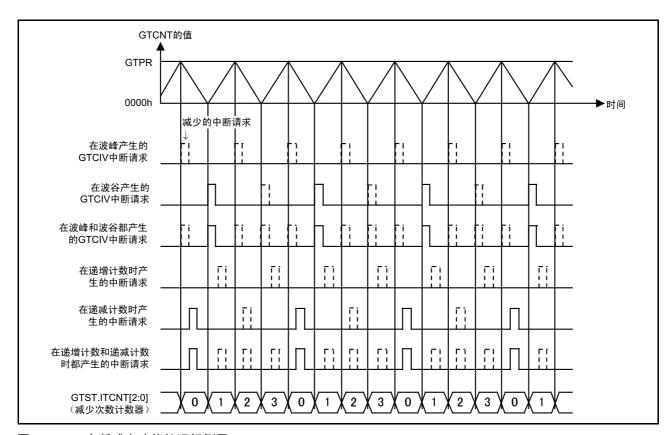

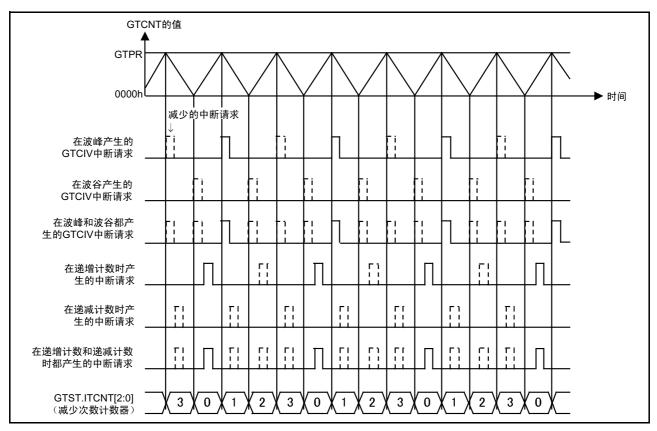

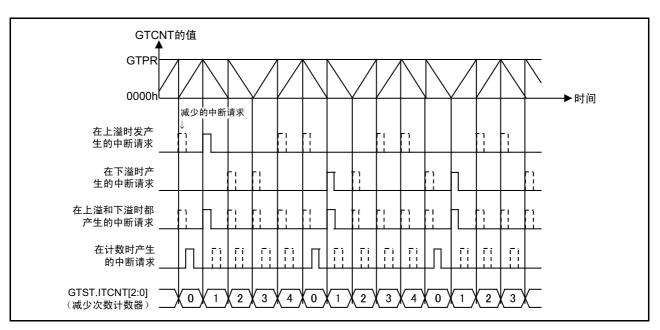

| 21.2.32 | 定时器的中断减少模式寄存器 (TITMRA、TITMRB)                 | 388 |

| 21.2.33 | 定时器的中断减少设定寄存器 1 (TITCR1A、TITCR1B)             | 389 |

| 21.2.34 | 定时器的中断减少次数计数器 1 (TITCNT1A、TITCNT1B)           | 391 |

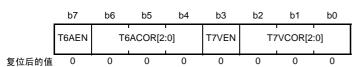

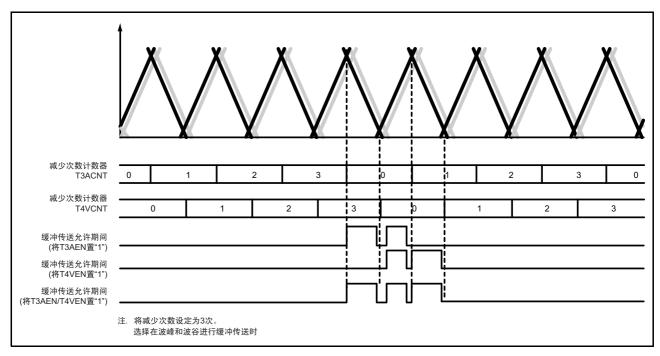

| 21.2.35 | 定时器的中断减少设定寄存器 2 (TITCR2A、TITCR2B)             |     |

| 21.2.36 | 定时器的中断减少次数计数器 2 (TITCNT2A、TITCNT2B)           | 395 |

| 21.2.37 | 和总线主控的接口                                      | 396 |

| 21.3 运行 | 说明                                            | 397 |

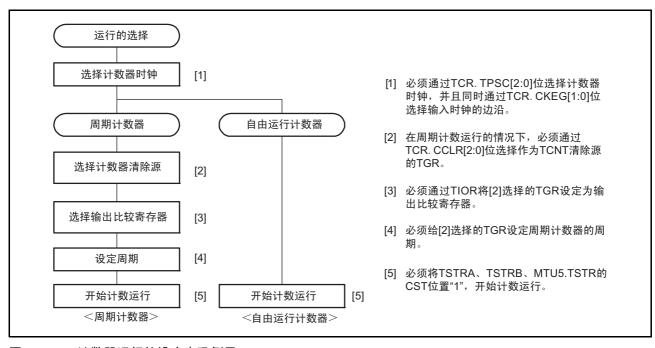

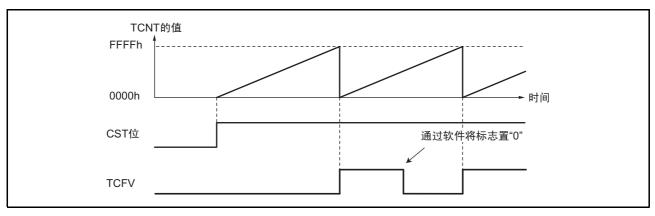

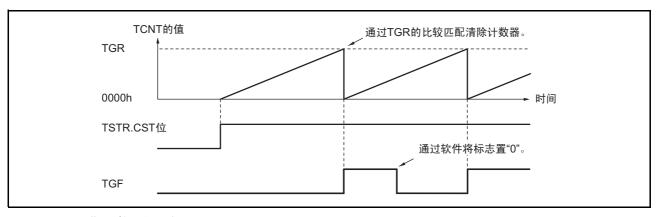

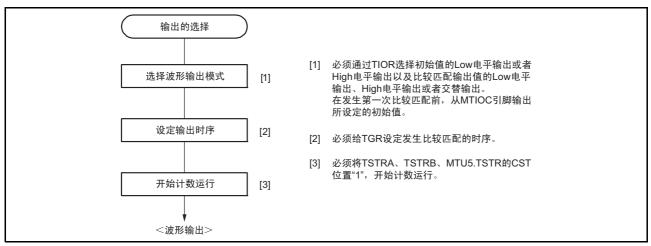

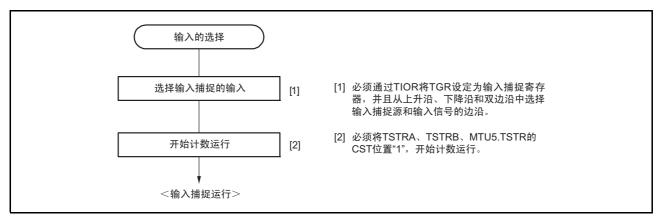

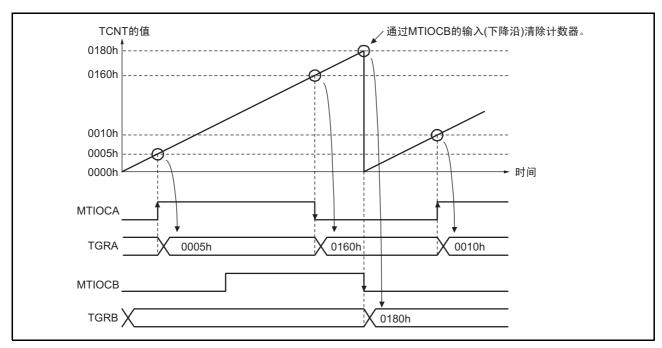

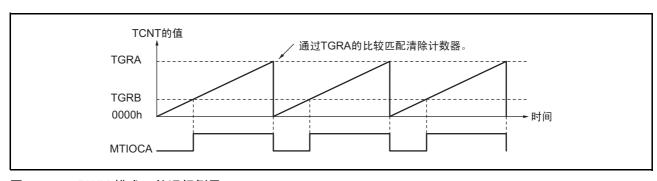

| 21.3.1  | 基本运行                                          | 397 |

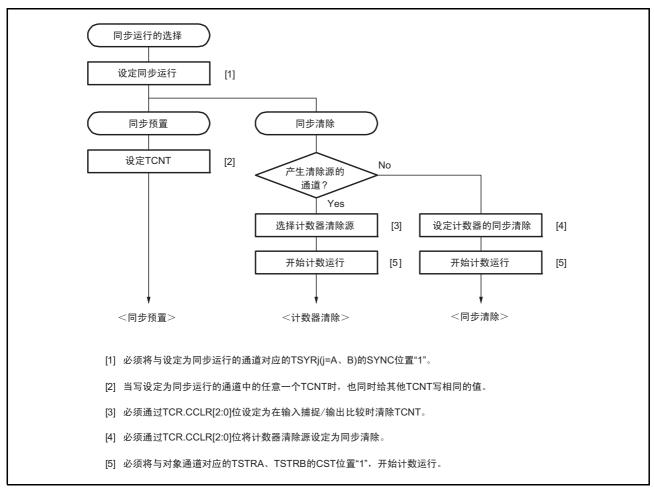

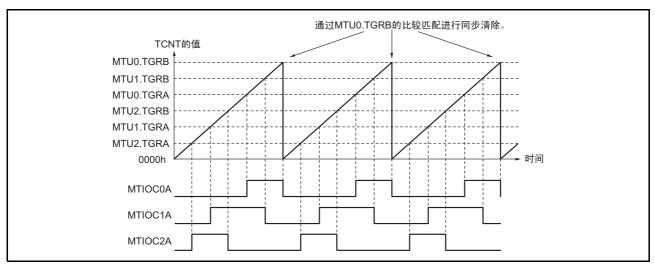

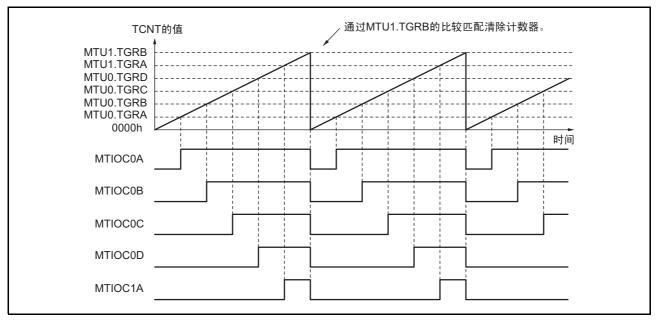

| 21.3.2  | 同步运行                                          | 401 |

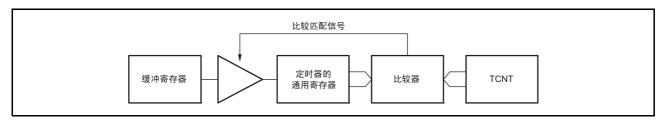

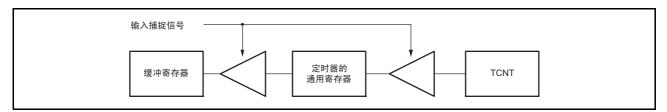

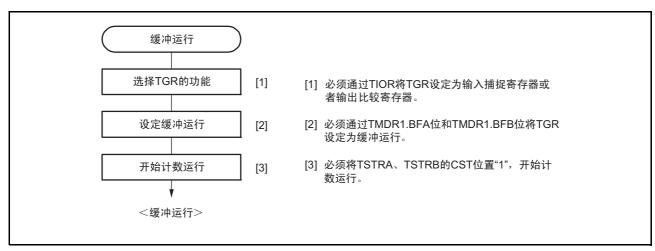

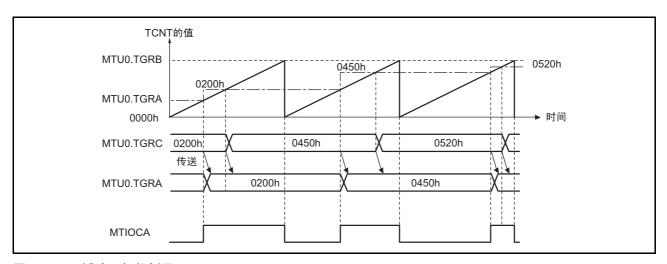

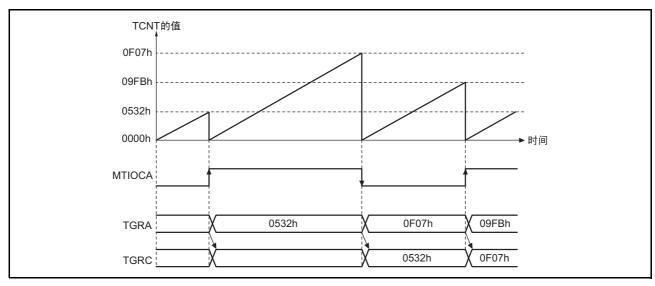

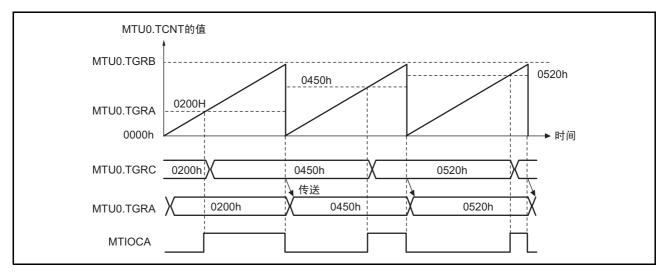

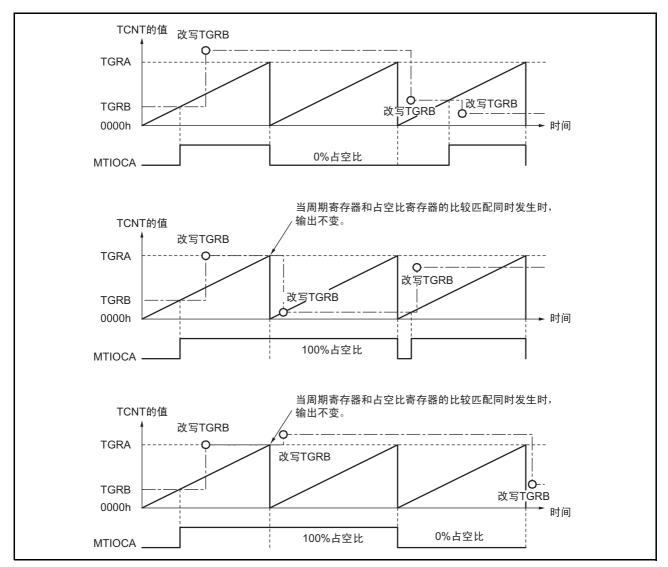

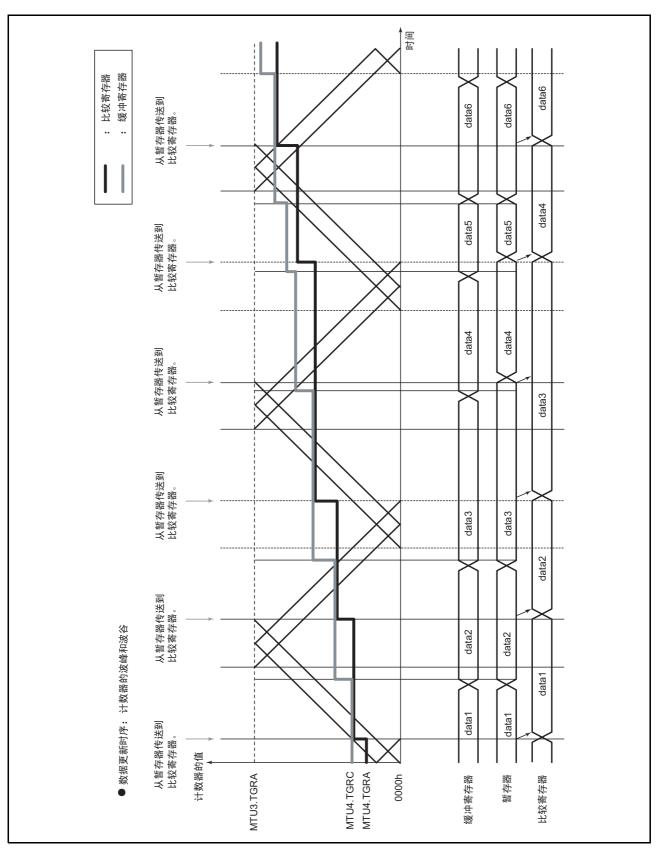

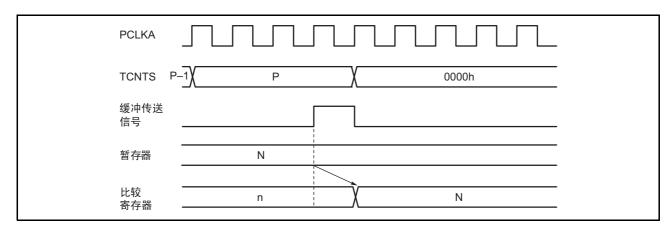

| 21.3.3  | 缓冲运行                                          |     |

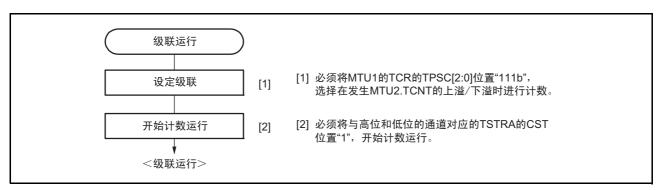

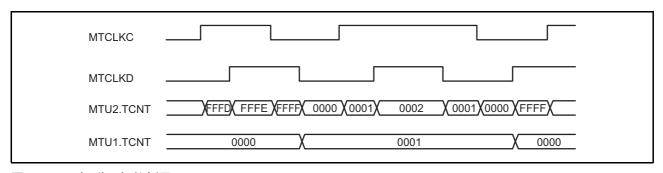

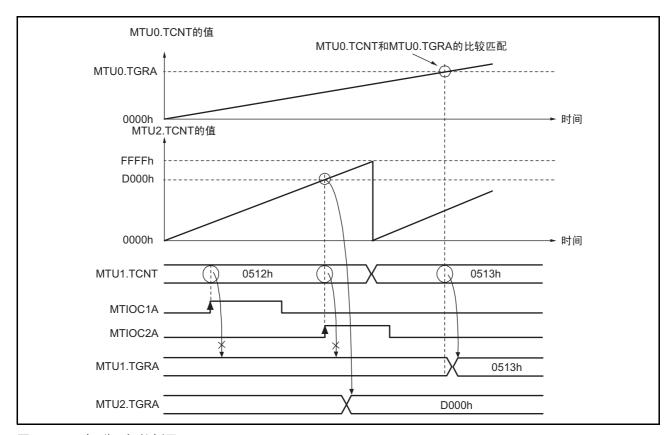

| 21.3.4  | 级联运行                                          |     |

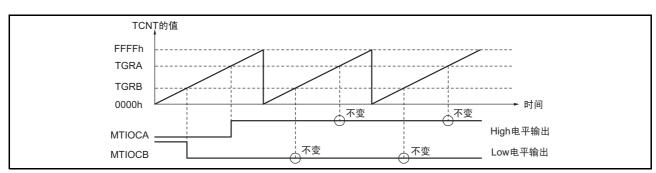

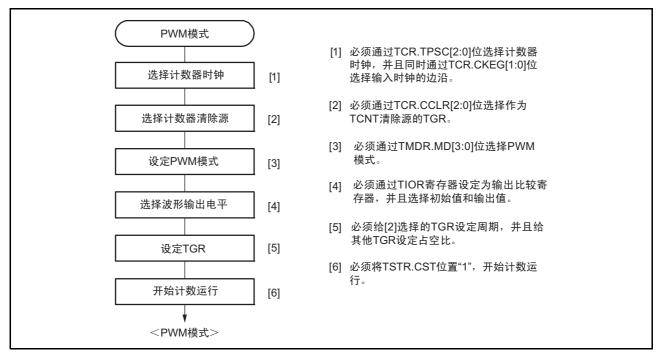

| 21.3.5  | PWM 模式                                        |     |

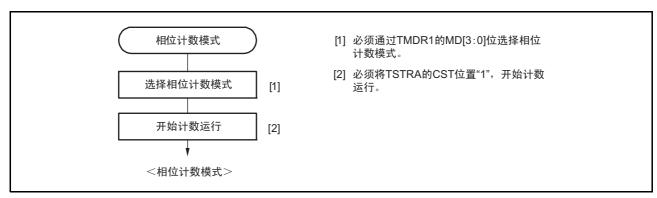

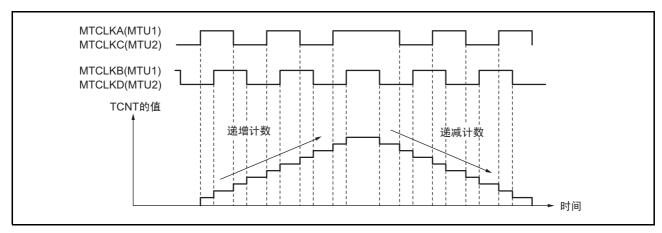

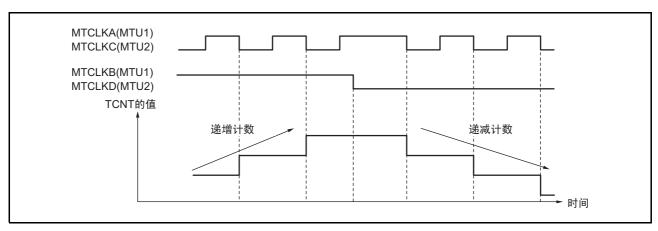

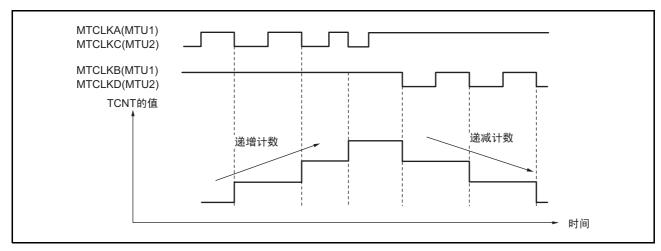

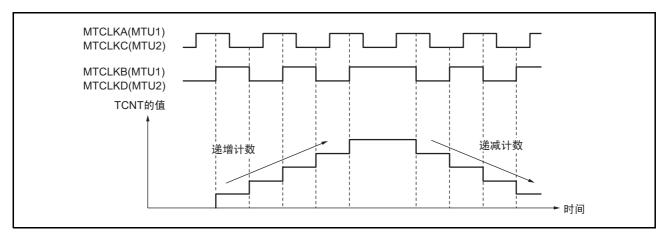

| 21.3.6  | 相位计数模式                                        |     |

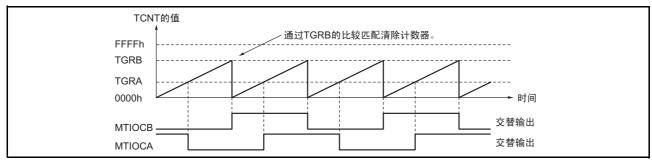

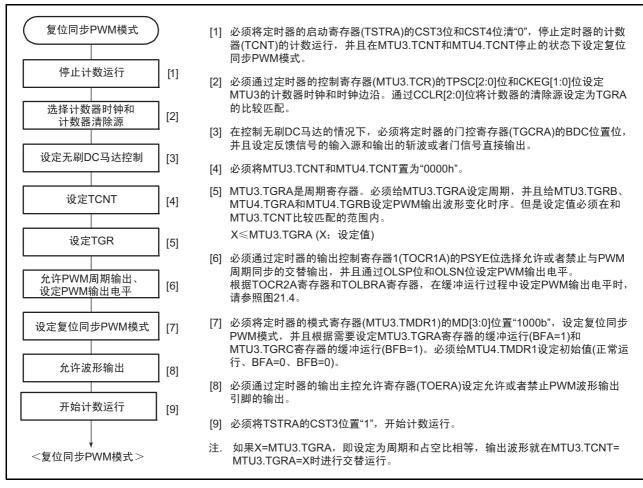

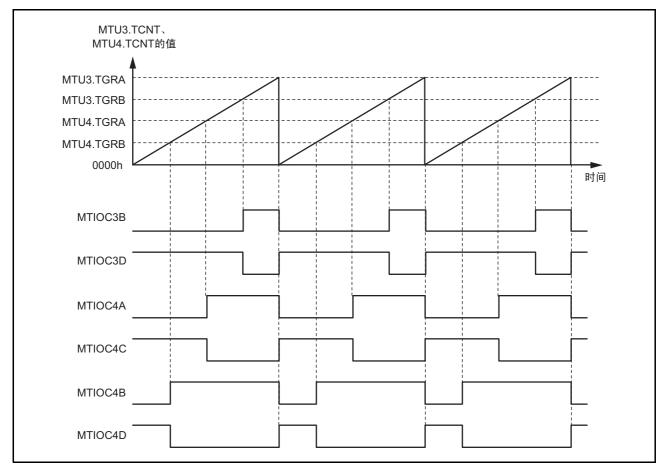

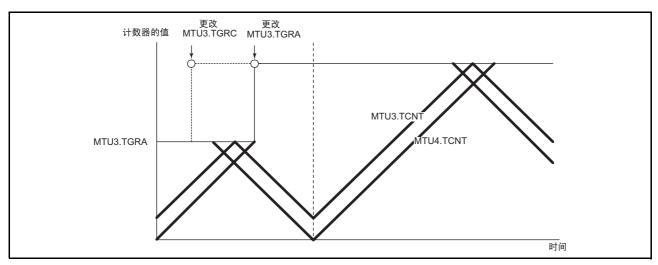

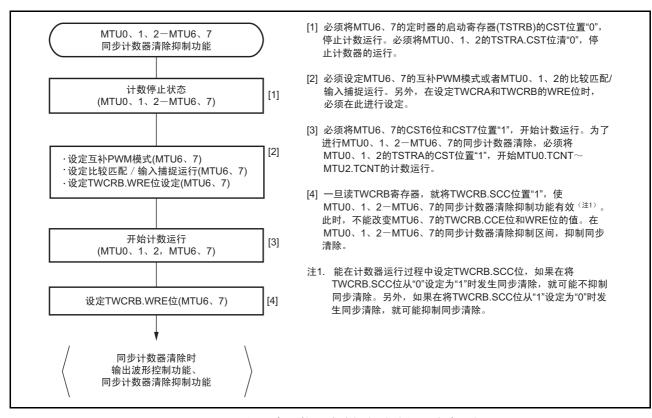

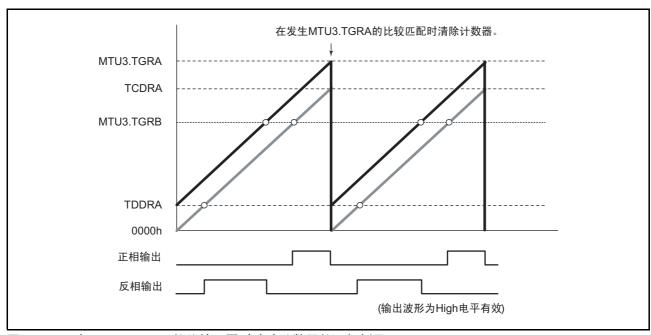

| 21.3.7  | 复位同步 PWM 模式                                   |     |

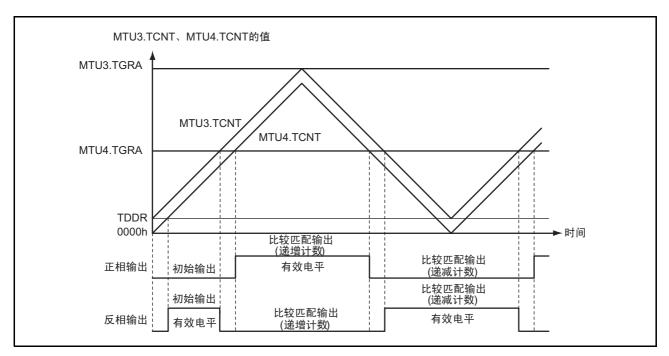

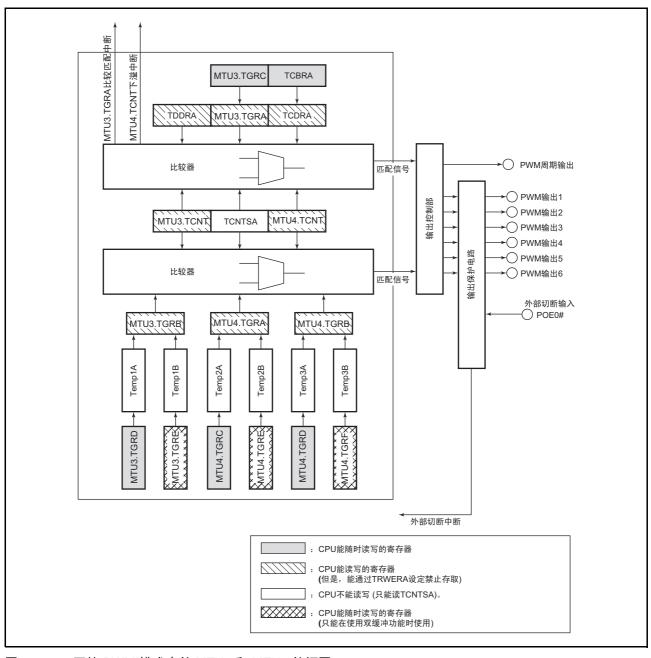

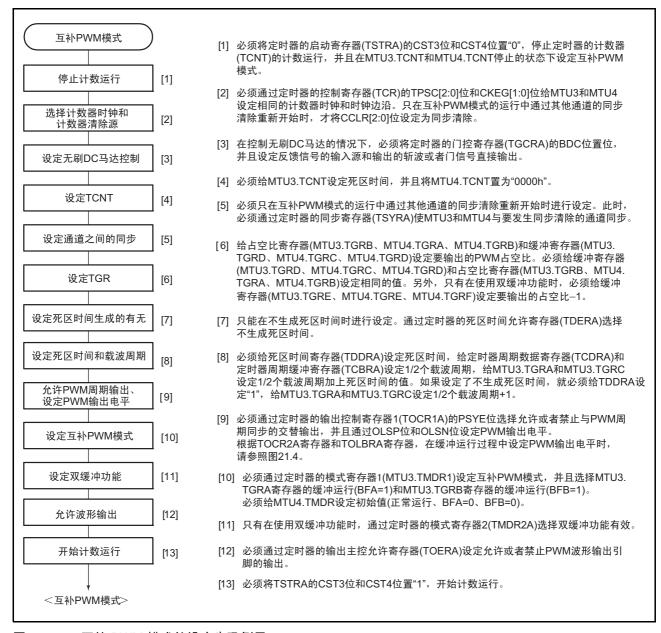

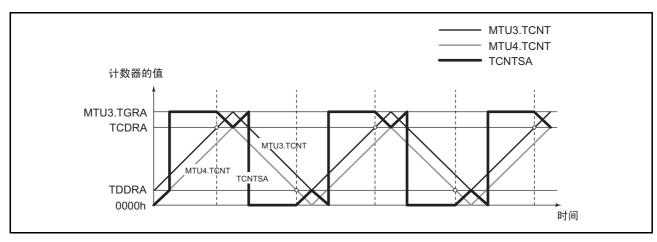

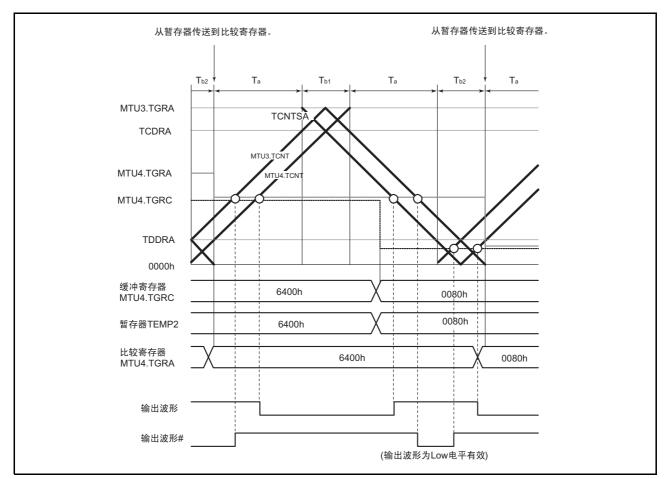

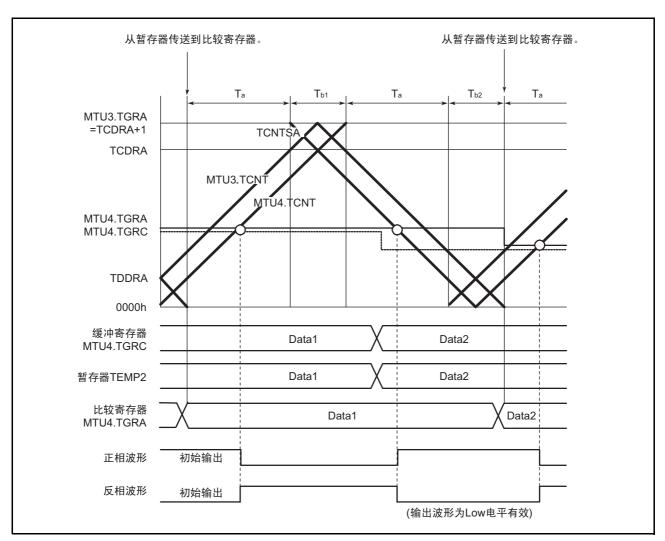

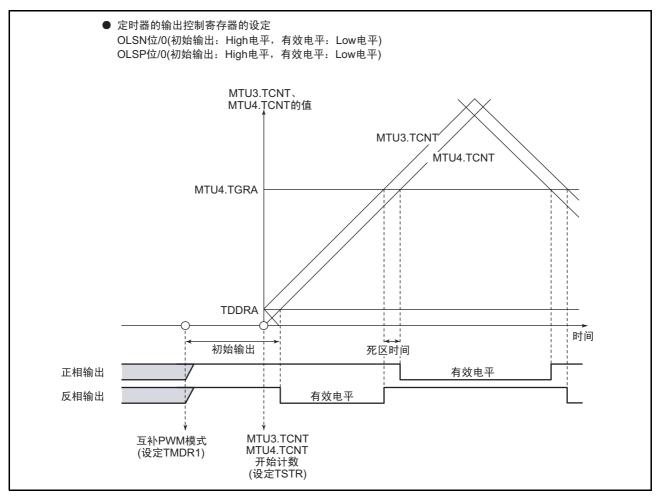

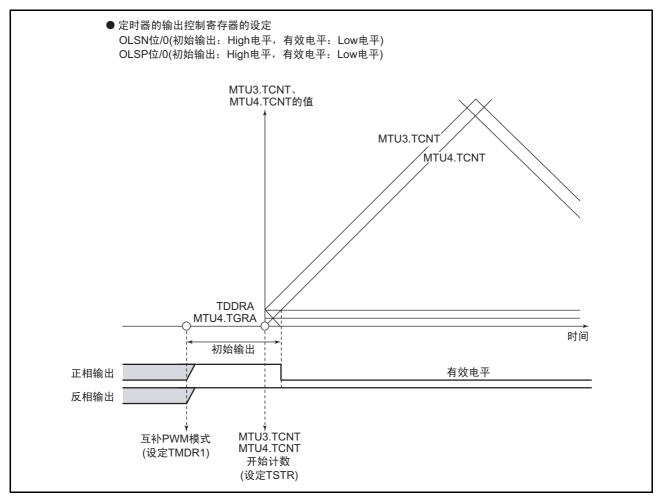

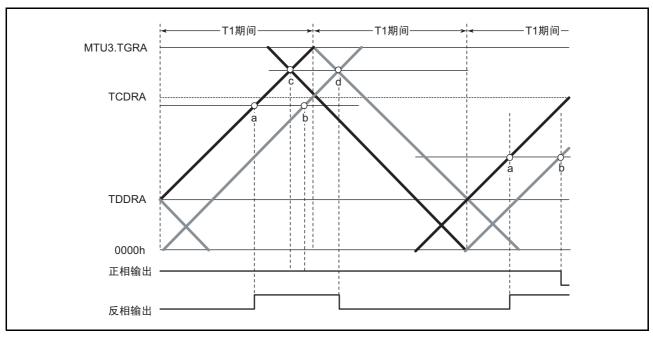

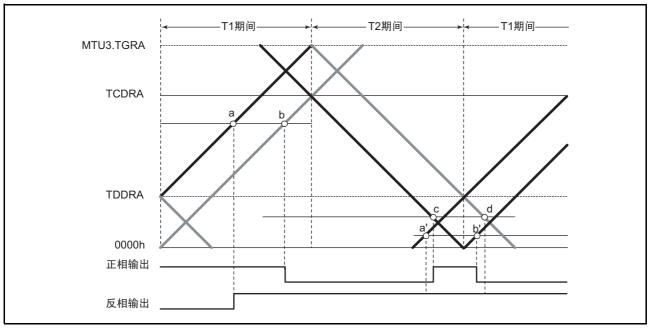

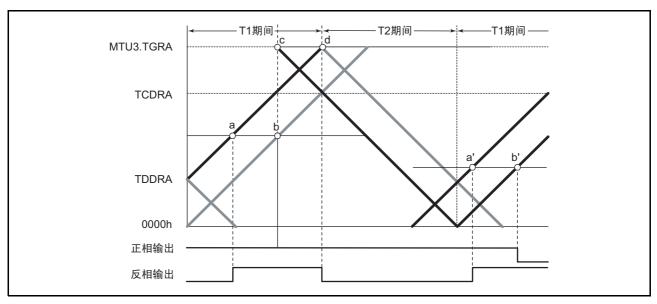

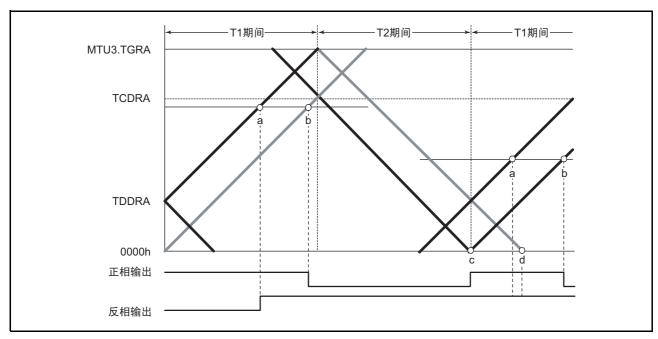

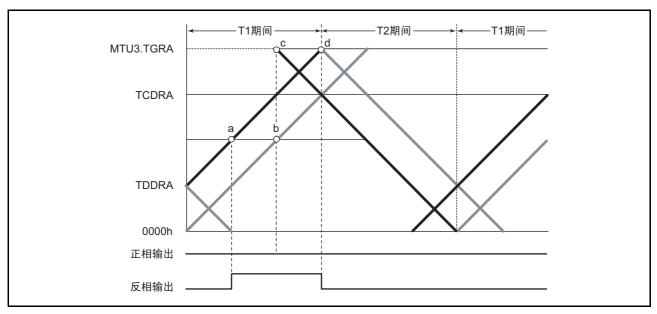

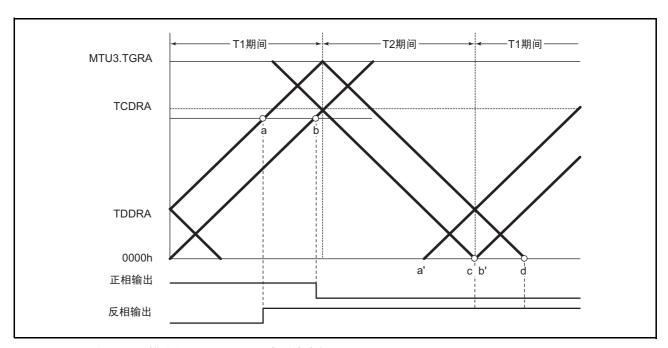

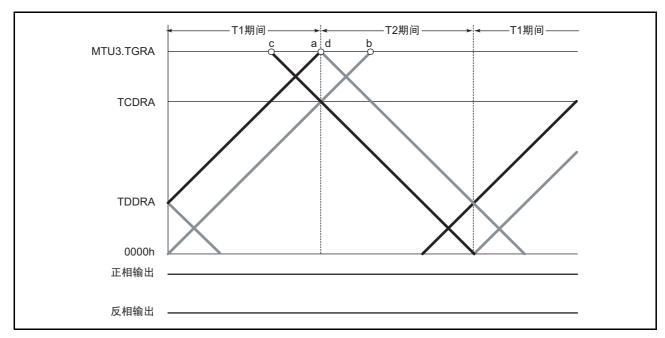

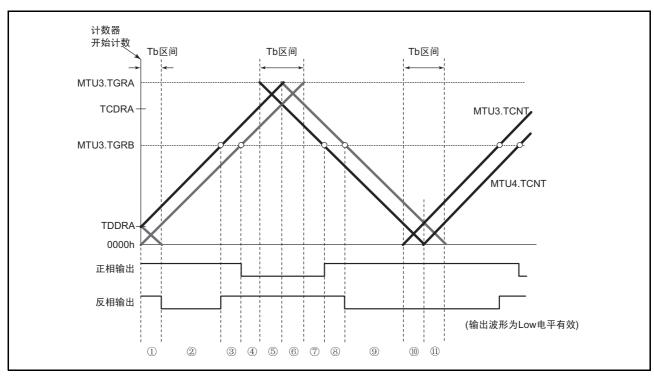

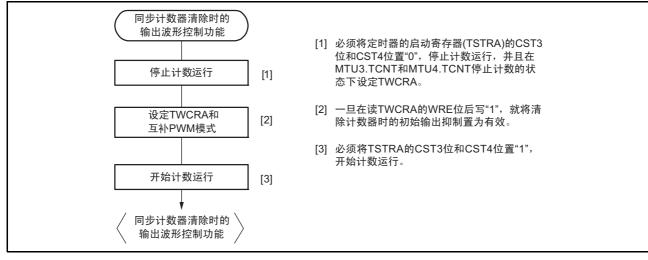

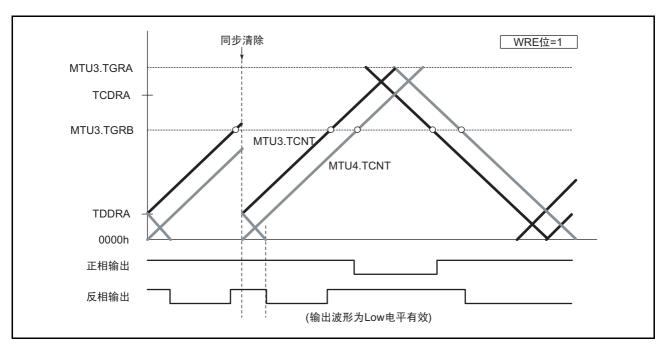

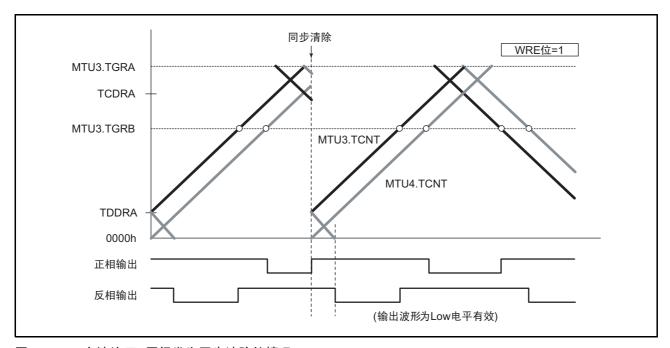

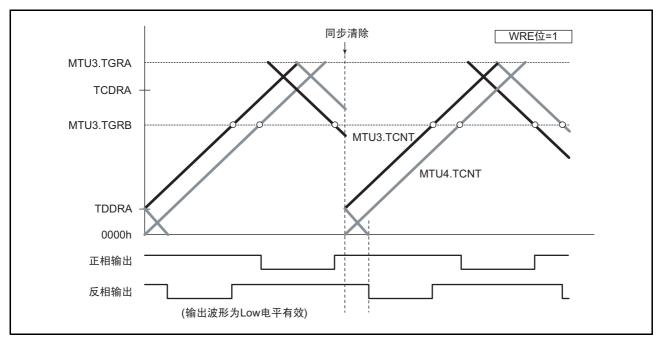

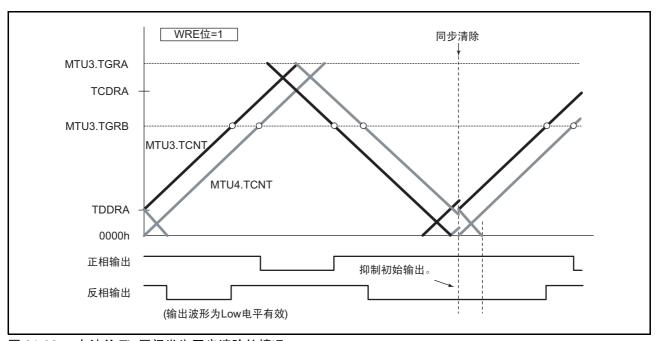

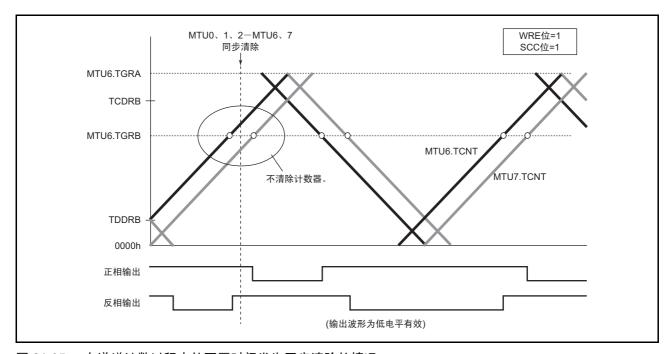

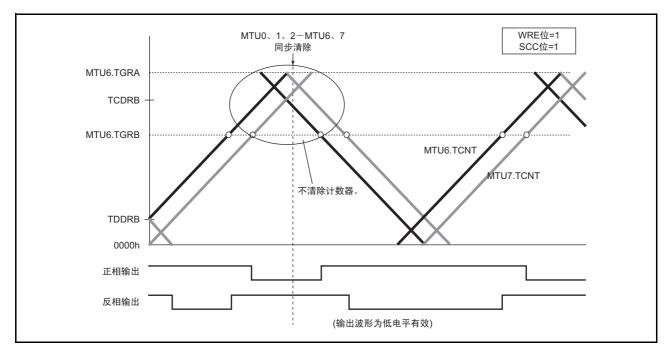

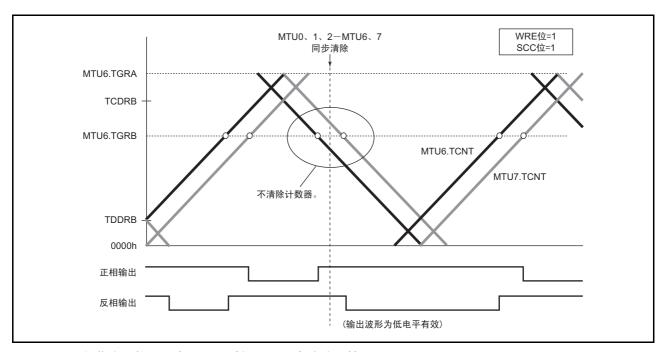

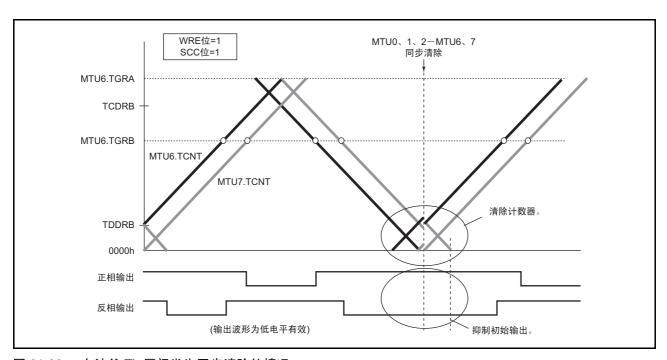

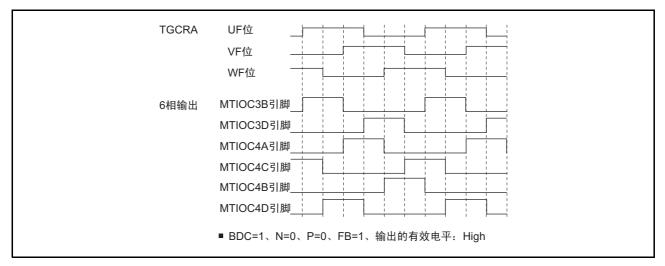

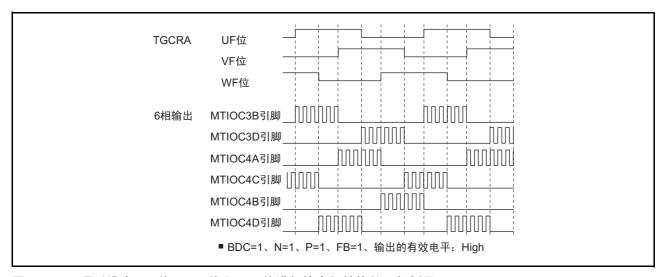

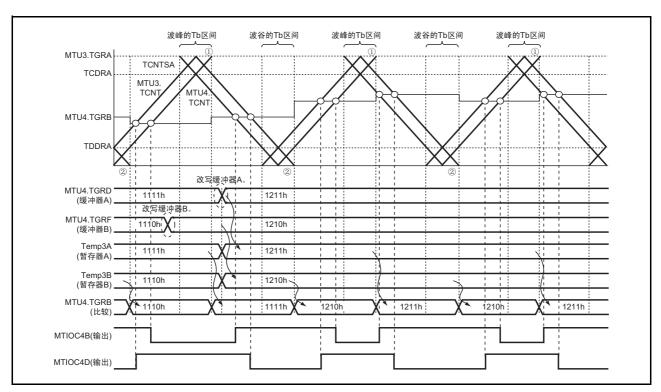

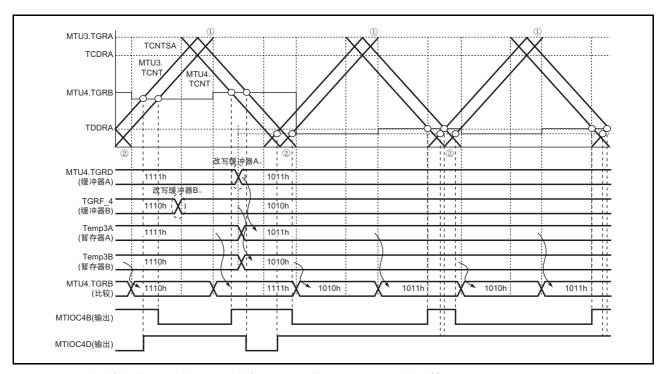

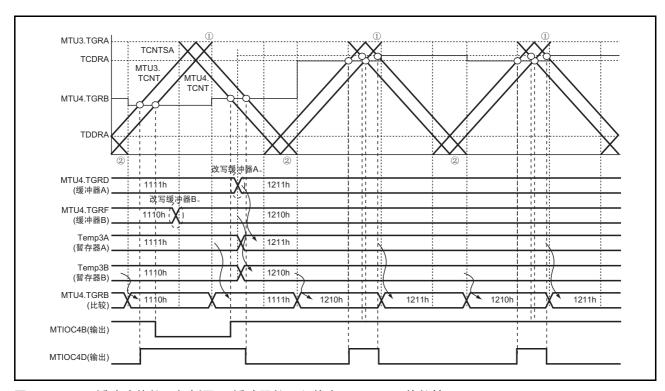

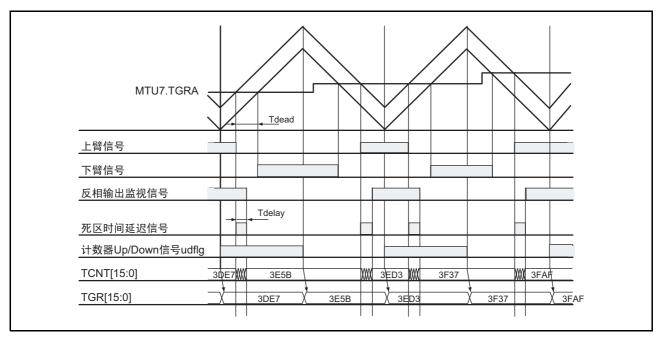

| 21.3.8  | 互补 PWM 模式                                     |     |

| 21.3.9  | A/D 转换开始请求的延迟功能                               |     |

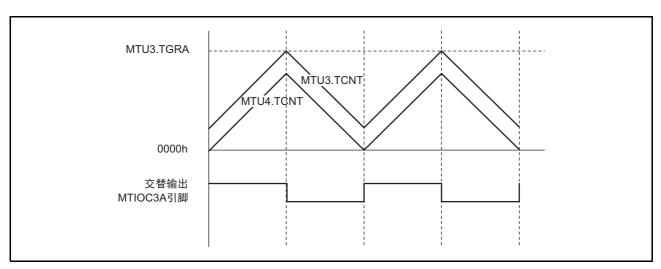

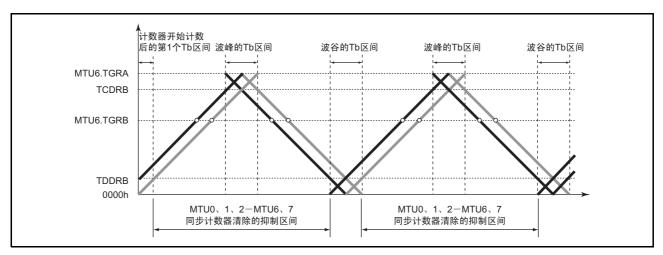

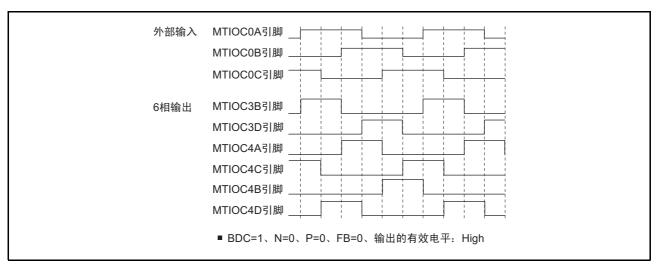

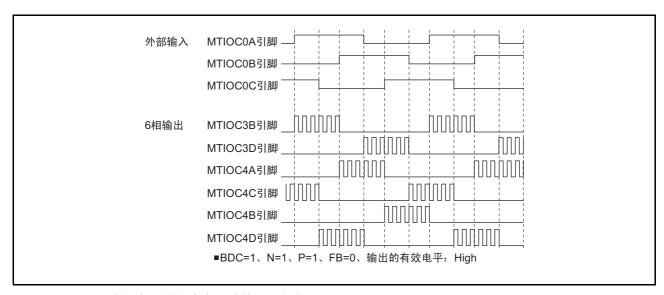

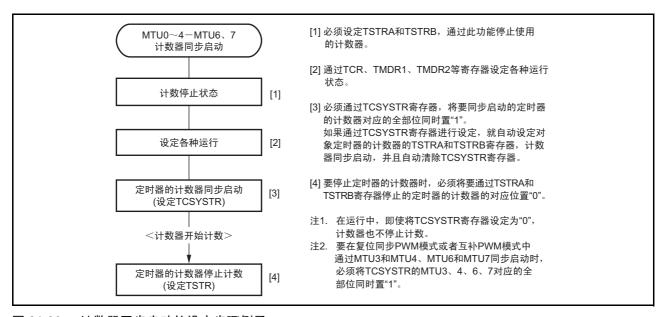

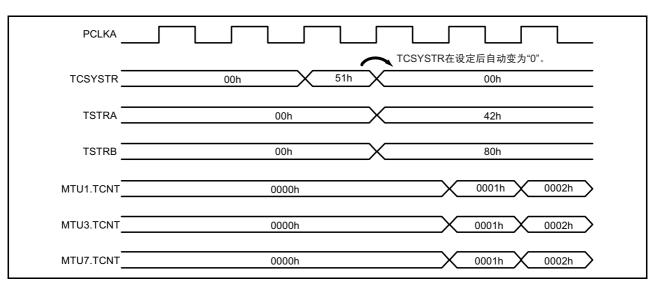

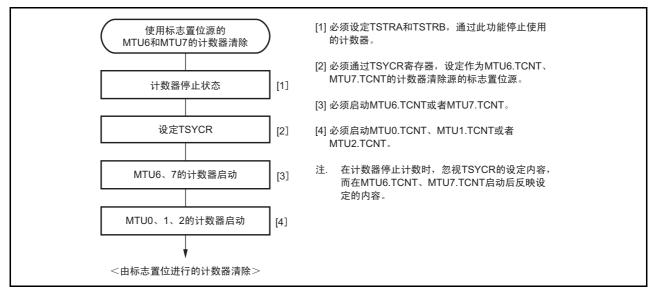

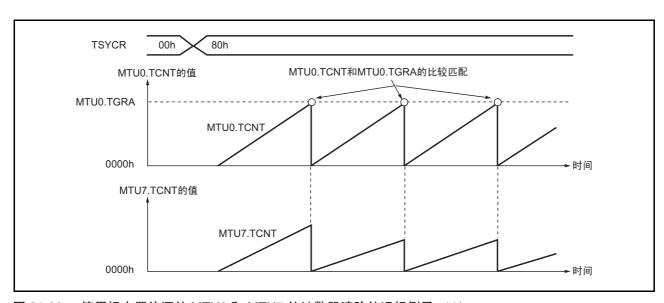

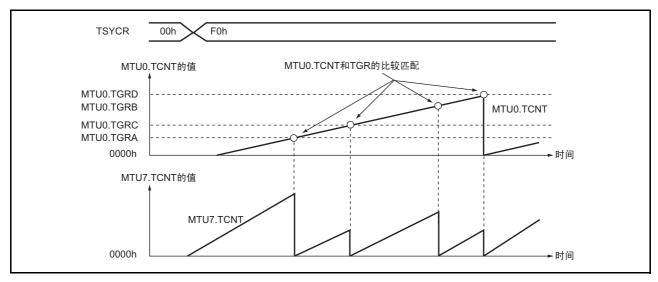

| 21.3.10 | MTU0 ~ 4 - MTU6、7的同步运行                        |     |

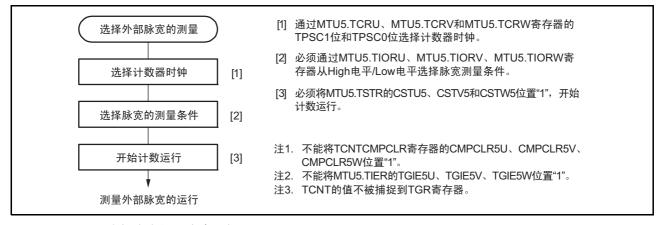

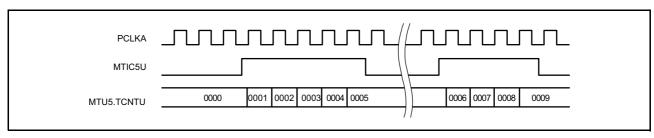

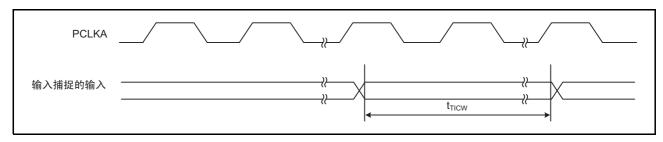

| 21.3.11 | 外部脉宽的测量功能                                     | 466 |

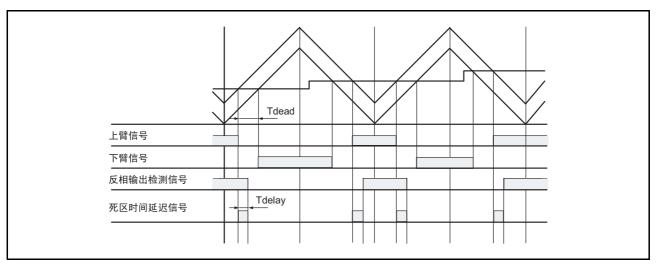

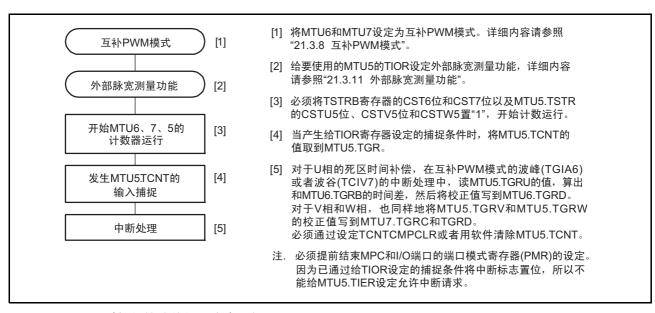

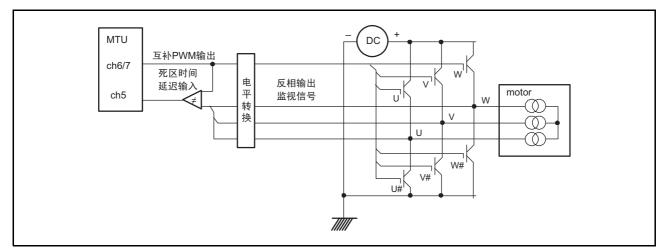

| 21.3.12 | 死区时间的补偿功能                                     |     |

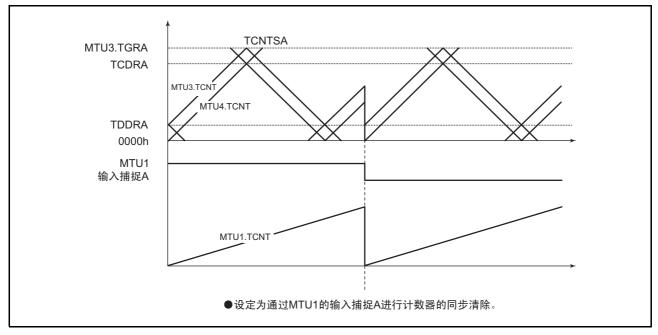

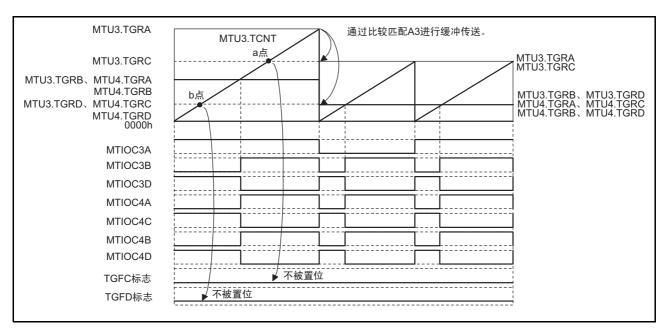

| 21.3.13 | 在互补 PWM 的"波峰/波谷"进行的 TCNT 捕捉运行                 | 468 |

| 21.4 中断 | 源                                             |     |

| 21.4.1  | 中断源和优先级                                       |     |

| 21.4.2  | DTC 的启动                                       |     |

| 21.4.3  | A/D 转换器的启动                                    |     |

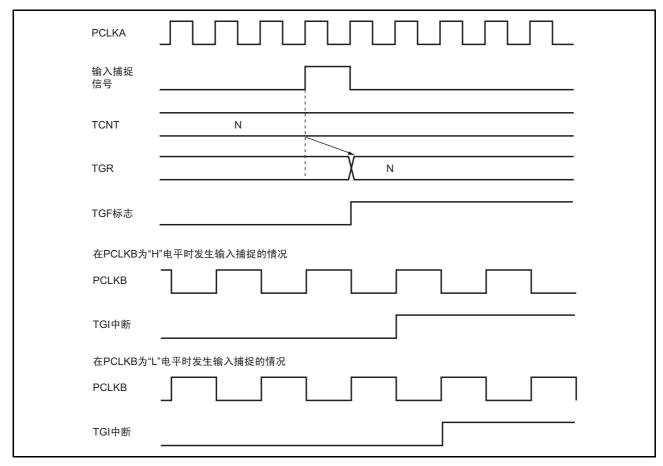

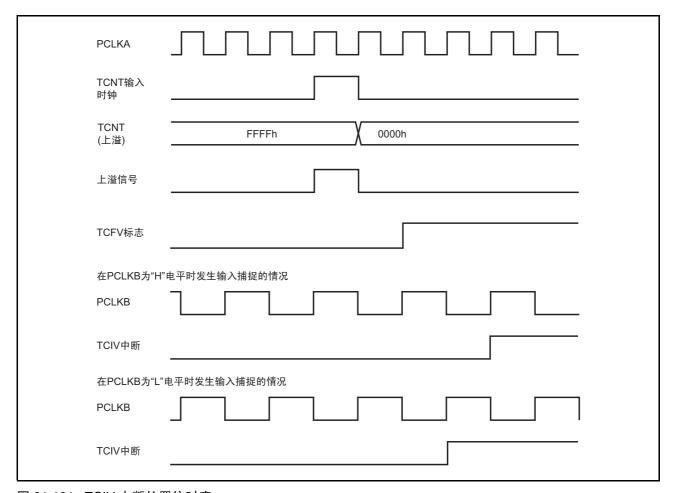

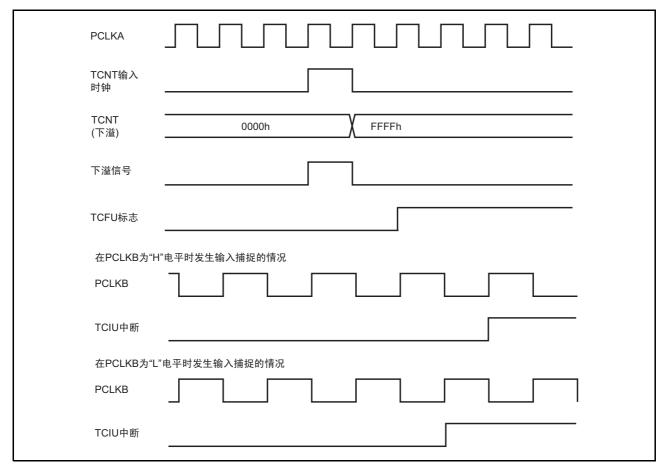

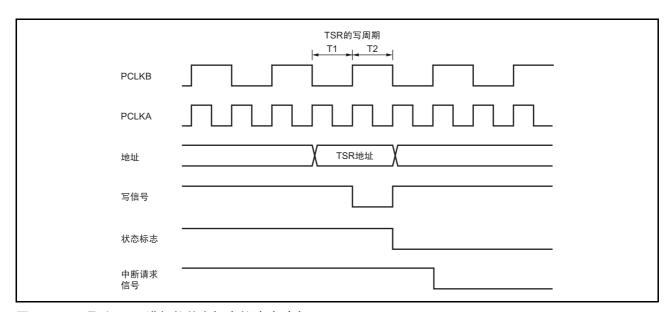

| 21.5 运行 | 时序                                            |     |

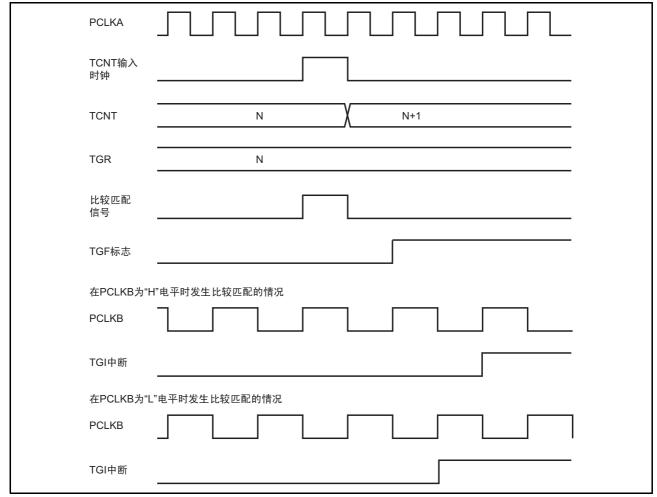

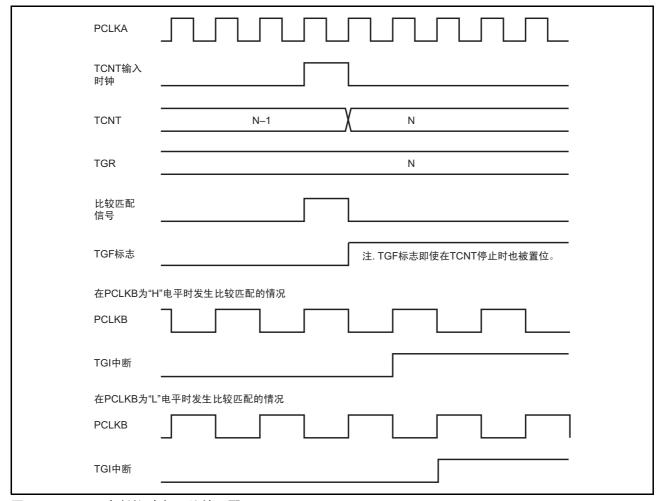

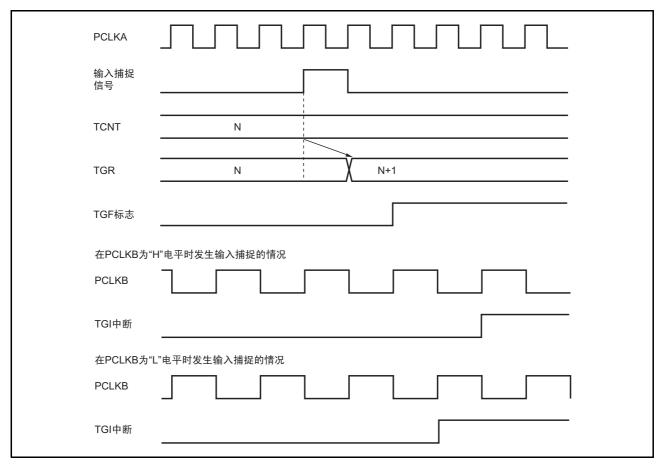

| 21.5.1  | 输入/输出时序                                       |     |

| 21.5.2  | 中断信号的时序                                       |     |

|         | 时的注意事项                                        |     |

| 21.6.1  | 模块时钟停止模式的设定                                   |     |

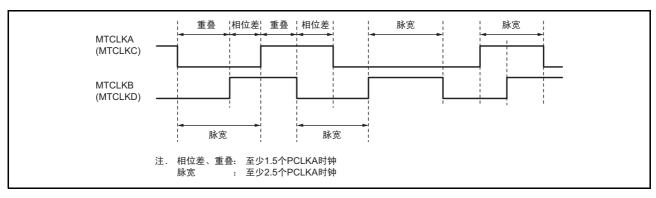

| 21.6.2  | 输入时钟的限制事项                                     |     |

| 21.6.3  | 设定周期时的注意事项                                    |     |

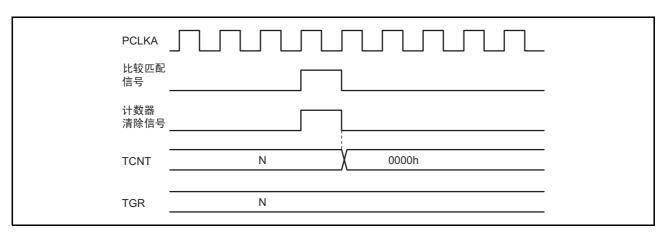

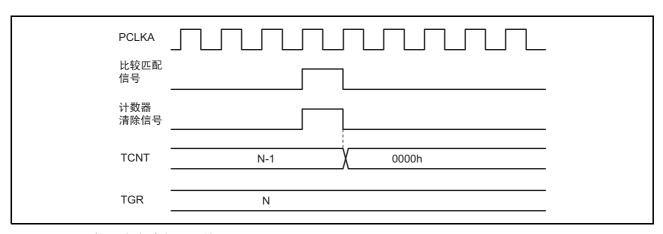

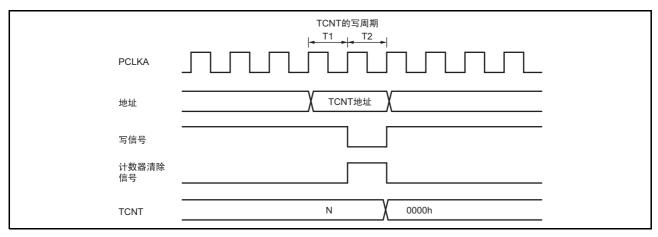

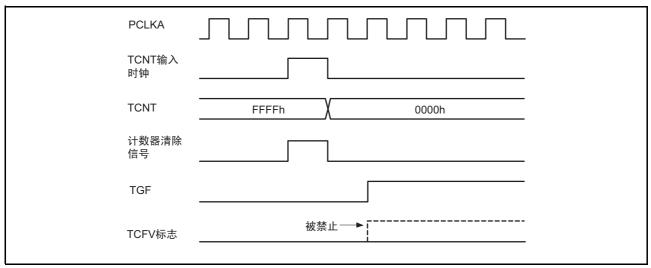

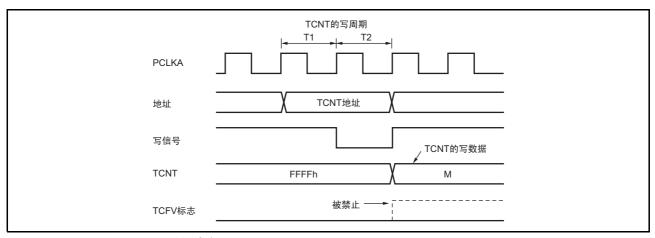

| 21.6.4  | TCNT 的写和清除的竞争                                 |     |

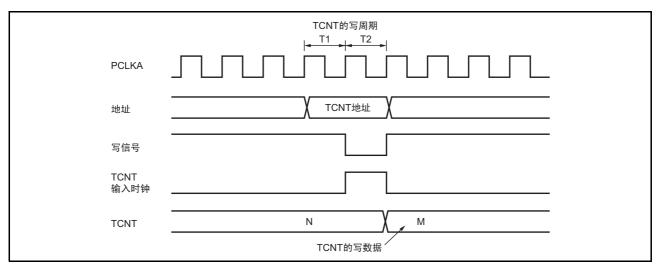

| 21.6.5  | TCNT 的写和递增计数的竞争                               |     |

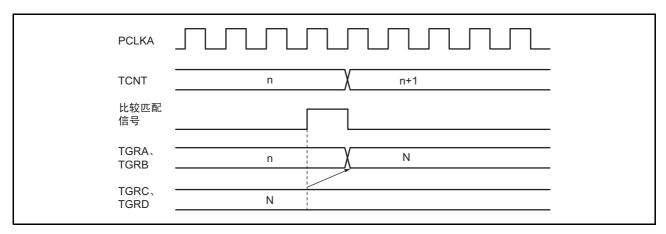

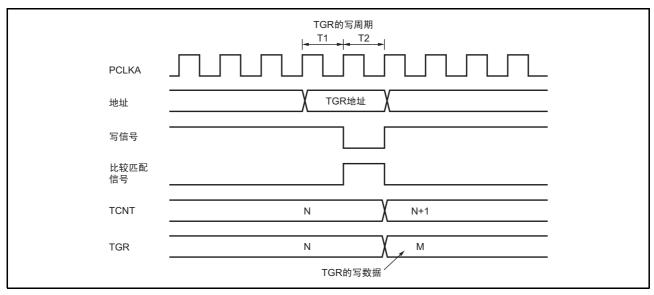

| 21.6.6  | TGR 的写和比较匹配的竞争                                |     |

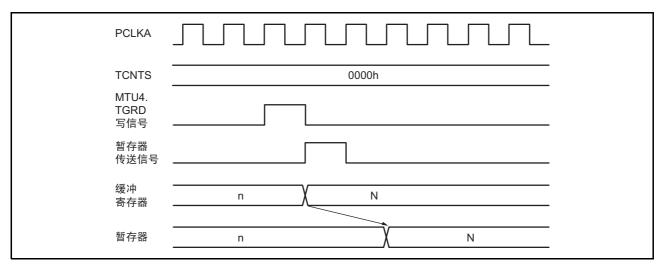

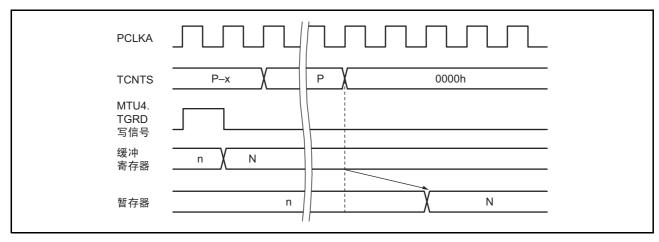

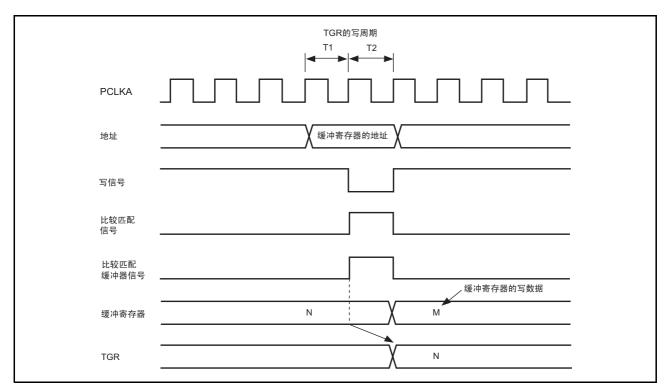

| 21.6.7  | 缓冲寄存器的写和比较匹配的竞争                               |     |

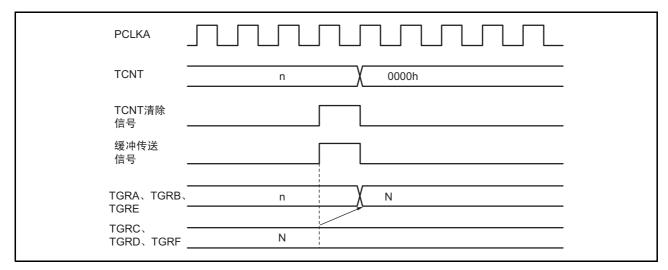

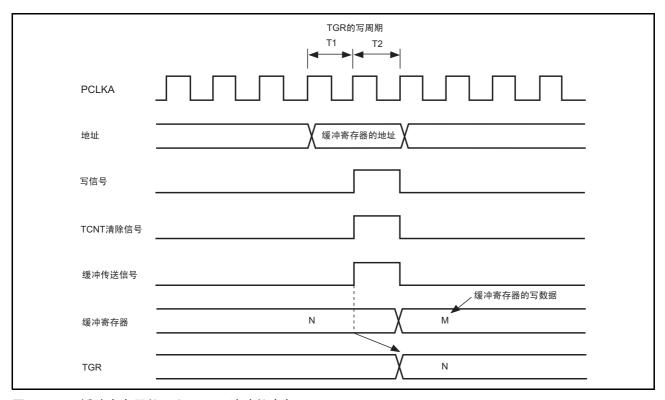

| 21.6.8  | 缓冲寄存器的写和 TCNT 清除的竞争                           |     |

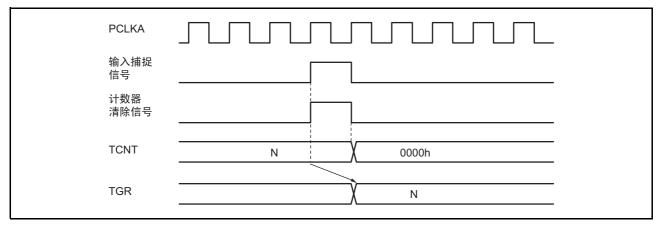

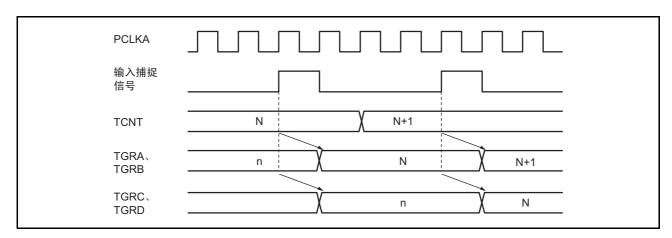

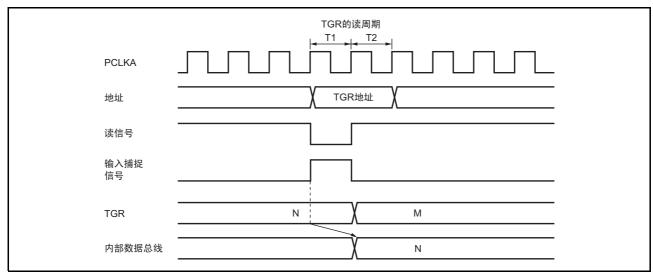

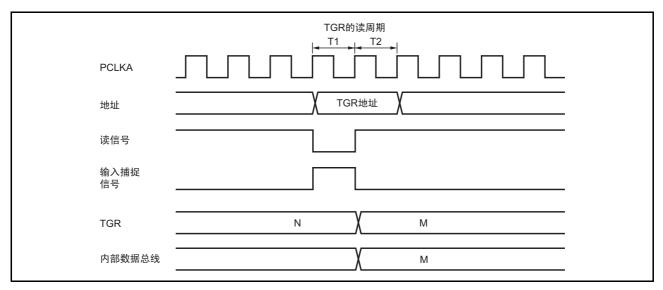

| 21.6.9  | TGR 寄存器的读和输入捕捉的竞争                             |     |

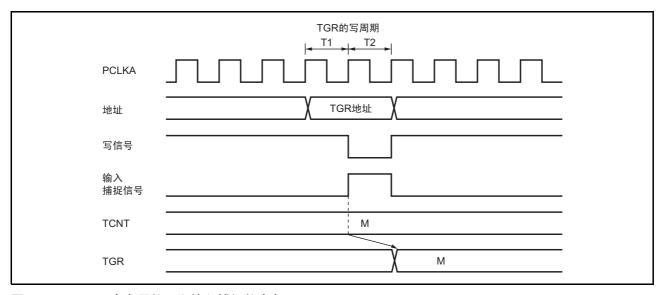

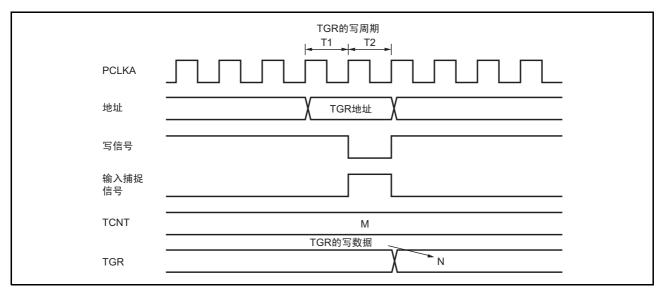

| 21.6.10 | TGR 寄存器的写和输入捕捉的竞争                             |     |

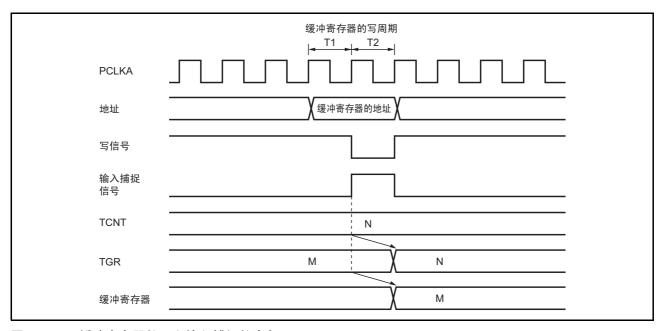

| 21.6.11 | 缓冲寄存器的写和输入捕捉的竞争                               |     |

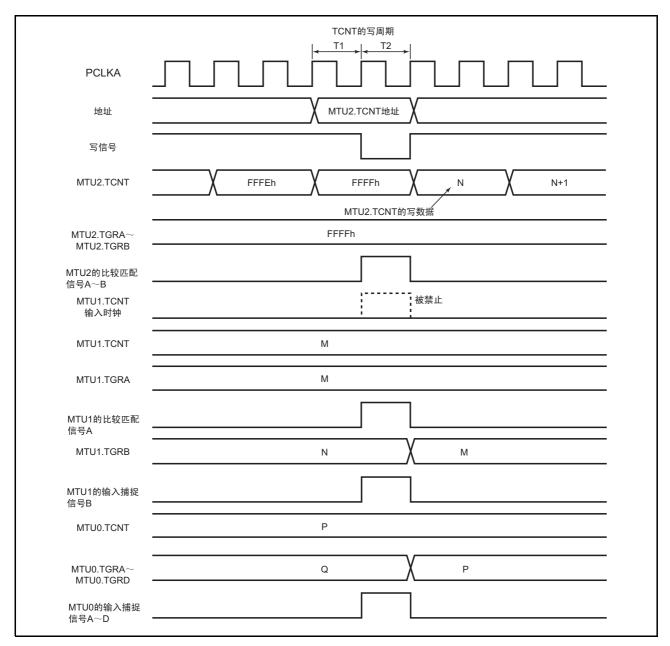

| 21.6.12 | 级联中的 MTU2.TCNT 的写和上溢 / 下溢的竞争                  |     |

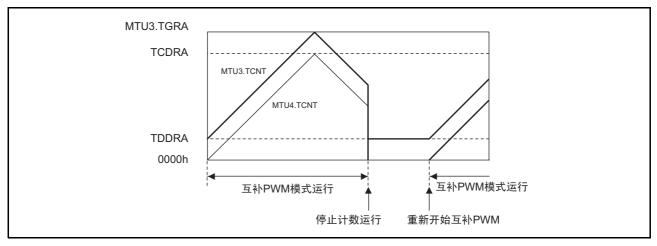

| 21.6.13 | 互补 PWM 模式停止时的计数器值                             |     |

| 21.6.14 | 互补 PWM 模式中的缓冲运行的设定                            |     |

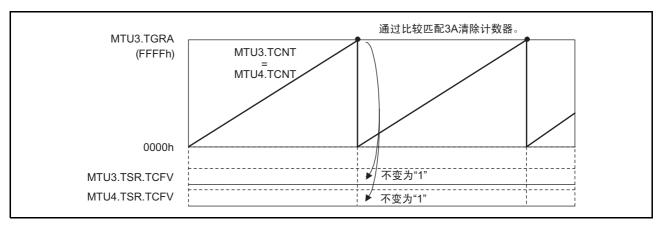

| 21.6.15 | 复位同步 PWM 模式的缓冲运行和比较匹配标志                       |     |

| 21.6.16 | 复位同步 PWM 模式的上溢标志                              |     |

| 21.6.17 | 上溢 / 下溢和计数器清除的竞争                              |     |

| 21.6.18 | TCNT 的写和上溢 / 下溢的竞争                            |     |

| 21.6.19 | 从正常运行或者 PWM 模式 1 转移到复位同步 PWM 模式时的注意事项         |     |

| 21.6.20 | 互补 PWM 模式、复位同步 PWM 模式的输出电平                    |     |

| 21.6.21 | 级联中的 MTU1.TCNT 和 MTU2.TCNT 的同时输入捕捉            |     |

| 21 6 22 | 中断减少功能 2                                      | 495 |

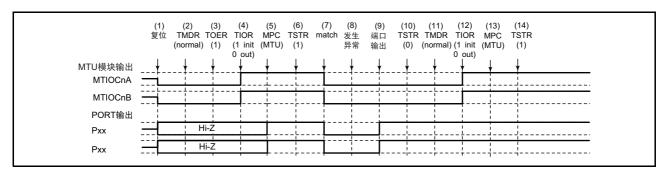

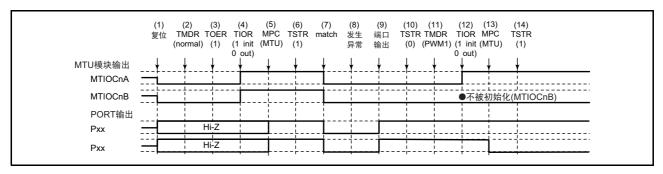

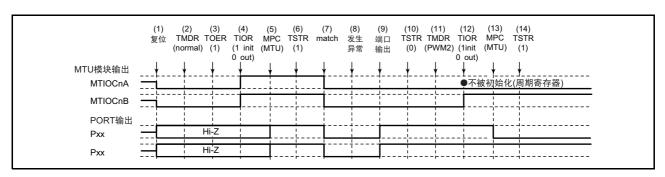

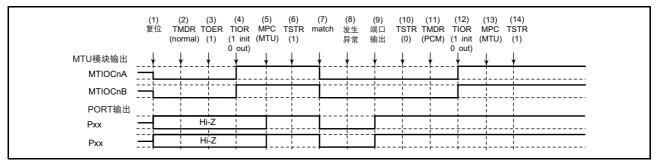

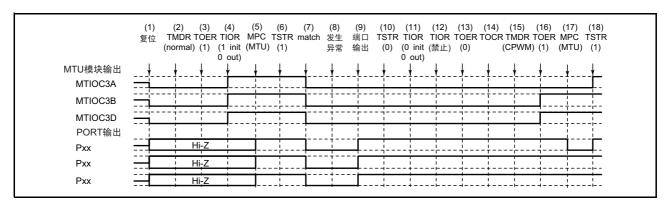

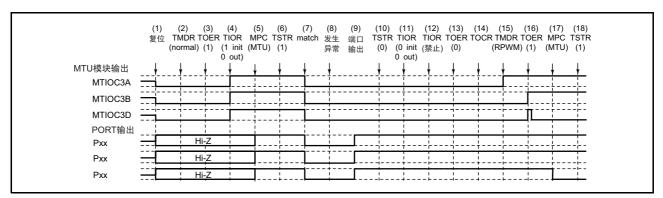

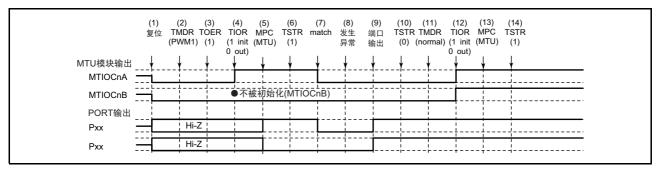

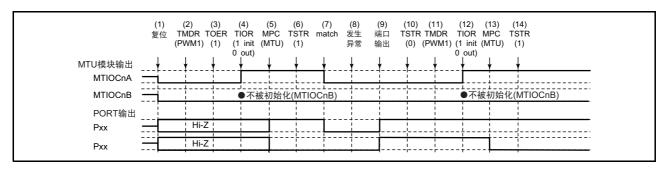

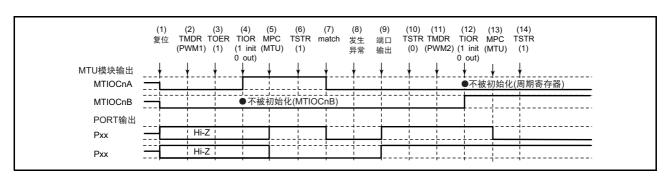

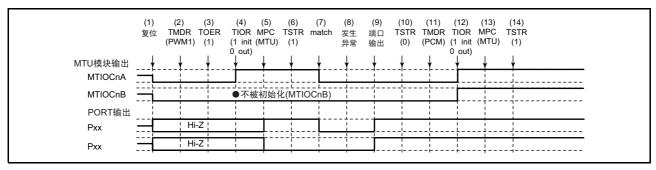

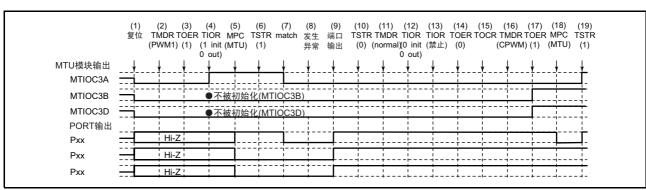

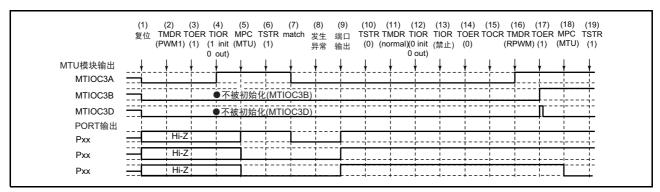

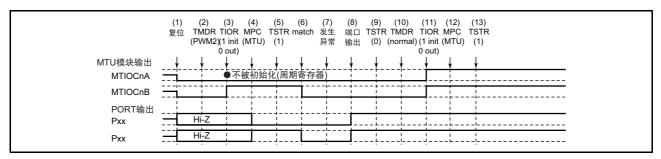

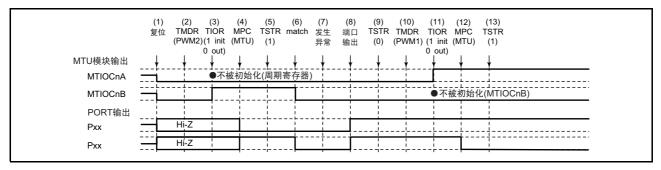

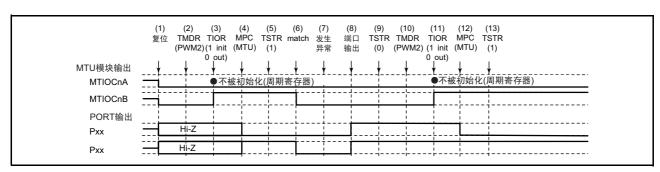

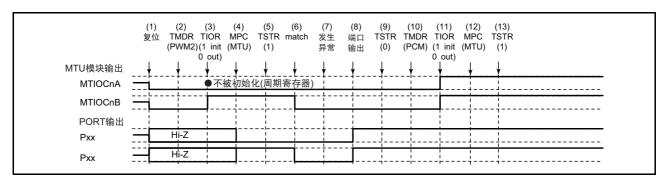

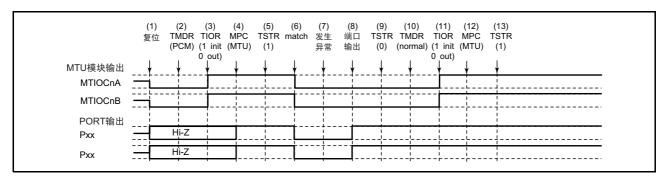

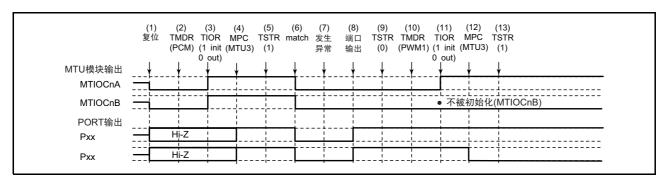

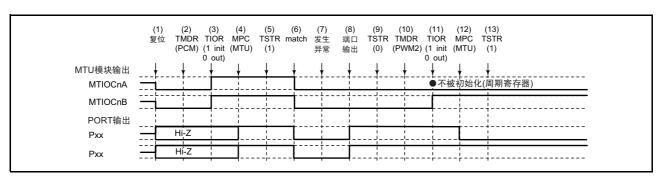

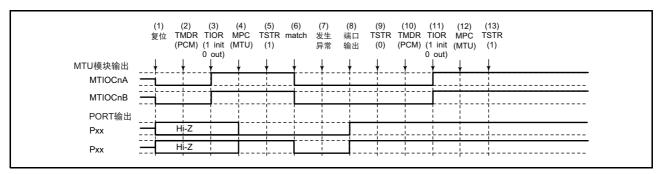

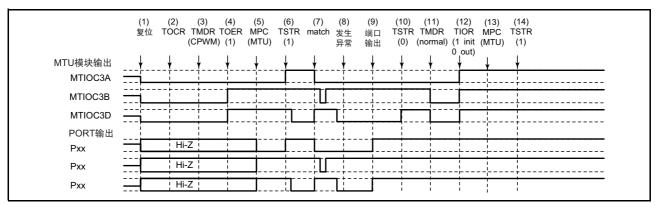

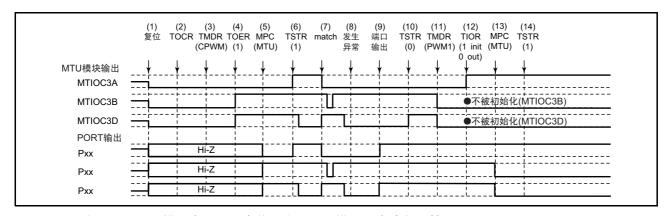

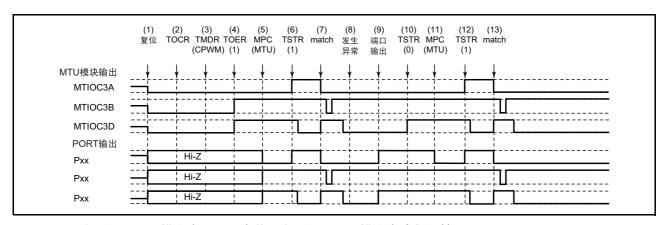

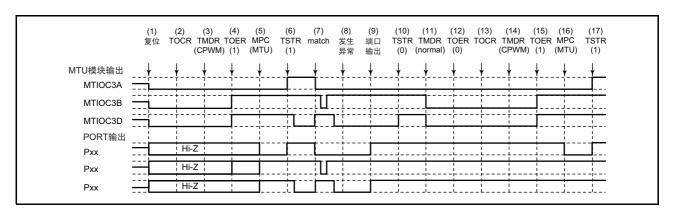

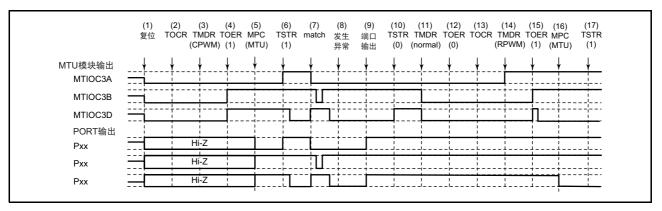

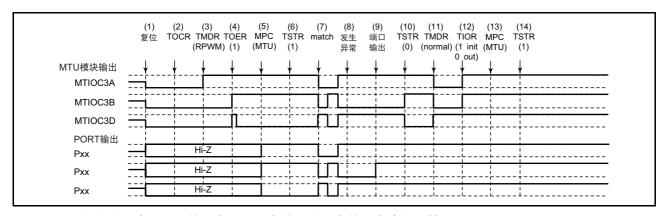

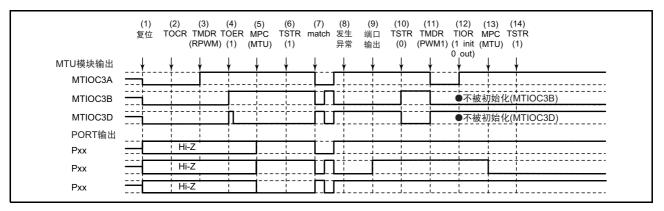

| 21.7 MTU | J 输出引脚的初始化方法                                    | 496 |

|----------|-------------------------------------------------|-----|

| 21.7.1   | 运行模式                                            | 496 |

| 21.7.2   | 因运行过程中的异常而重新设定时的运行                              | 496 |

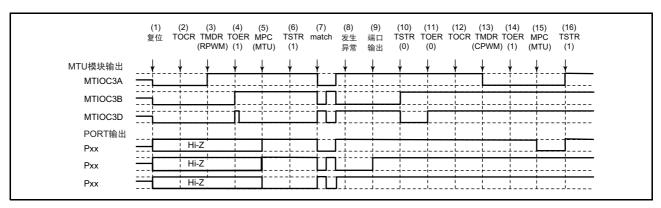

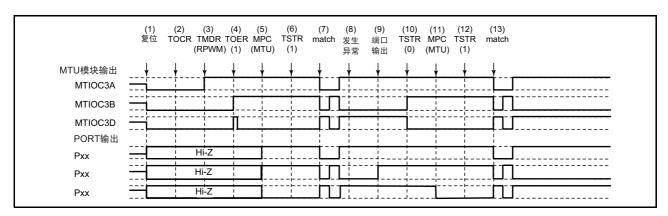

| 21.7.3   | 因运行过程中的异常而对引脚进行初始化的步骤以及模式转移的概要                  | 497 |

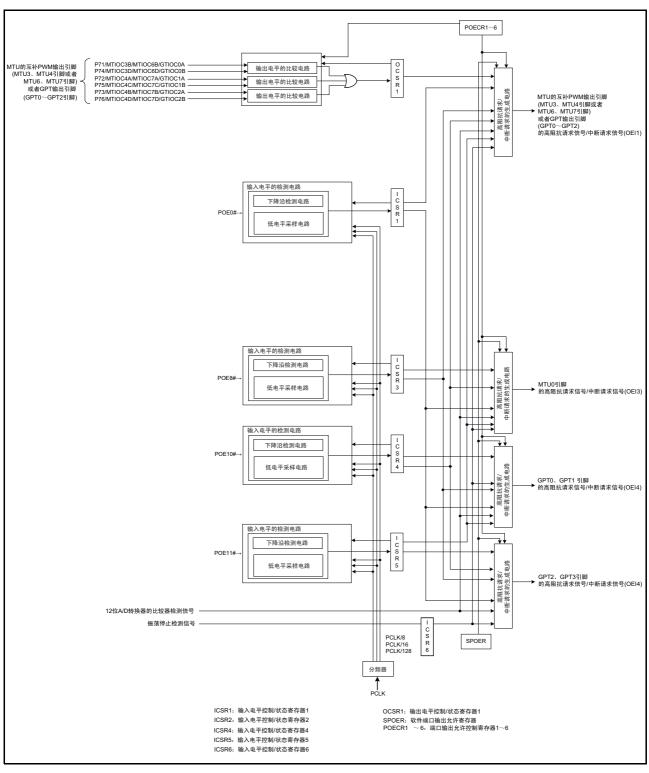

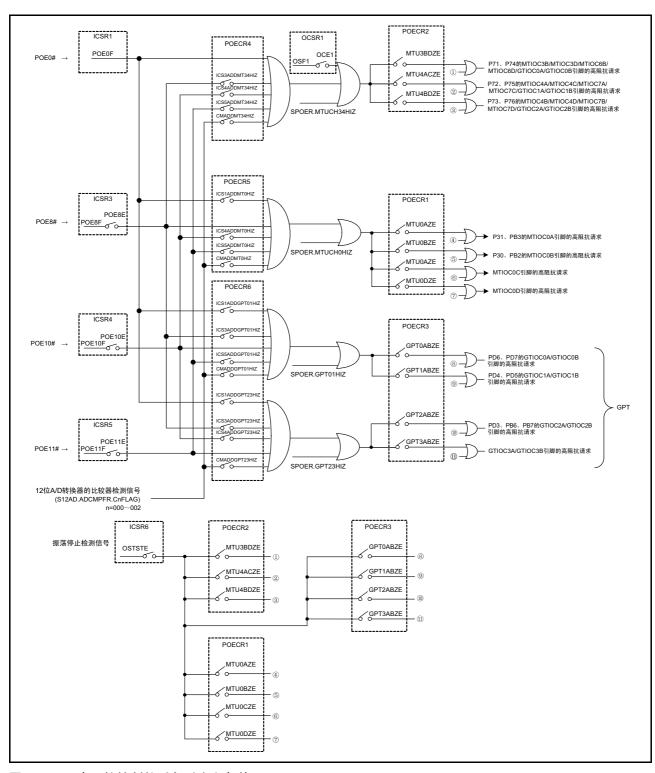

| 22. 端口箱  | ì出允许3(POE3)                                     | 519 |

| 22.1 概要  |                                                 | 519 |

| 22.2 寄存  | 器说明                                             | 522 |

| 22.2.1   | 输入电平控制 / 状态寄存器 1 (ICSR1)                        | 522 |

| 22.2.2   | 输出电平控制 / 状态寄存器 1 (OCSR1)                        | 523 |

| 22.2.3   | 有效电平寄存器 1 (ALR1)                                | 524 |

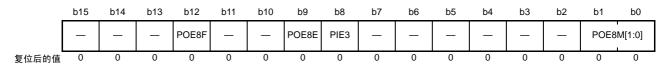

| 22.2.4   | 输入电平控制 / 状态寄存器 3 (ICSR3)                        | 526 |

| 22.2.5   | 输入电平控制 / 状态寄存器 4 (ICSR4)                        | 527 |

| 22.2.6   | 输入电平控制 / 状态寄存器 5 (ICSR5)                        | 528 |

| 22.2.7   | 软件端口输出允许寄存器 (SPOER)                             | 529 |

| 22.2.8   | 端口输出允许控制寄存器 1 (POECR1)                          | 531 |

| 22.2.9   | 端口输出允许控制寄存器 2 (POECR2)                          | 532 |

| 22.2.10  | 端口输出允许控制寄存器 3 (POECR3)                          | 533 |

| 22.2.11  | 端口输出允许控制寄存器 4 (POECR4)                          | 534 |

| 22.2.12  | 端口输出允许控制寄存器 5 (POECR5)                          | 535 |

| 22.2.13  | 端口输出允许控制寄存器 6 (POECR6)                          |     |

| 22.2.14  | 输入电平控制 / 状态寄存器 6 (ICSR6)                        |     |

| 22.3 运行  | ·说明                                             |     |

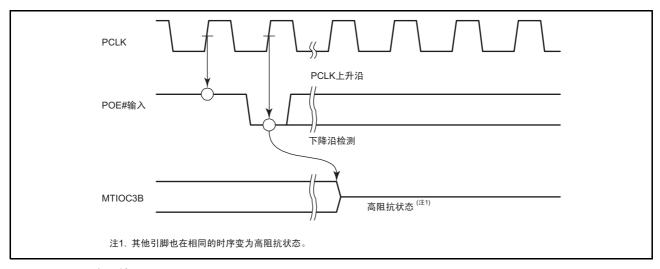

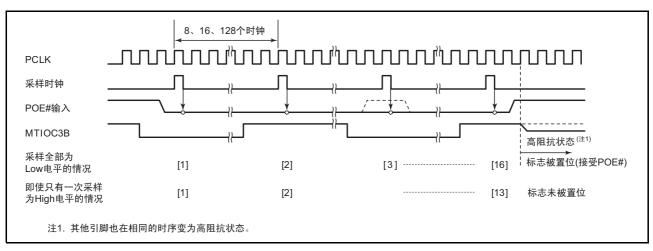

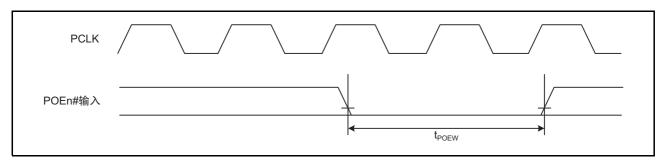

| 22.3.1   | 输入电平的检测                                         |     |

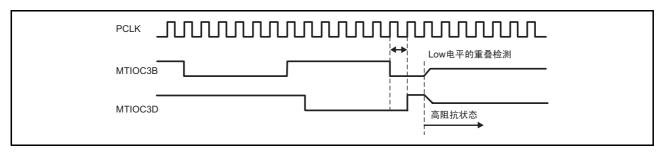

| 22.3.2   | 输出电平的比较                                         |     |

| 22.3.3   | 通过寄存器进行的高阻抗控制                                   |     |

| 22.3.4   | 通过振荡停止检测进行的高阻抗控制                                |     |

| 22.3.5   | 通过比较器检测进行的高阻抗控制                                 |     |

| 22.3.6   | 高阻抗控制条件的追加功能                                    |     |

| 22.3.7   | 高阻抗状态的解除                                        |     |

|          | - P411120 C D C C C C C C C C C C C C C C C C C |     |

|          | 时的注意事项                                          |     |

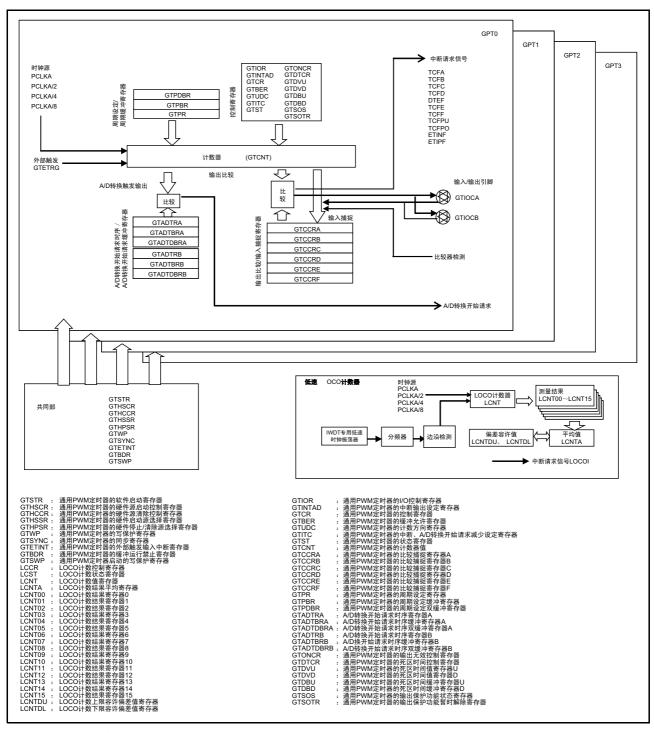

| 23. 通用 F | PWM 定时器 (GPT)                                   | 546 |

|          |                                                 |     |

|          | 器说明                                             |     |

| 23.2.1   | 通用 PWM 定时器的软件启动寄存器 (GTSTR)                      |     |

| 23.2.2   | 通用 PWM 定时器的硬件源启动控制寄存器 (GTHSCR)                  |     |

| 23.2.3   | 通用 PWM 定时器的硬件源清除控制寄存器(GTHCCR)                   |     |

| 23.2.4   | 通用 PWM 定时器的硬件启动源选择寄存器 (GTHSSR)                  |     |

| 23.2.5   | 通用 PWM 定时器的硬件停止 / 清除源选择寄存器 (GTHPSR)             |     |

| 23.2.6   | 通用 PWM 定时器的写保护寄存器 (GTWP)                        |     |

| 23.2.7   | 通用 PWM 定时器的同步寄存器 (GTSYNC)                       |     |

| 23.2.8   | 通用 PWM 定时器的外部触发输入中断寄存器 (GTETINT)                |     |

| 23.2.9   | 通用 PWM 定时器的缓冲运行禁止寄存器 (GTBDR)                    |     |

| 23.2.10  | 通用 PWM 定时器启动的写保护寄存器 (GTSWP)                     |     |

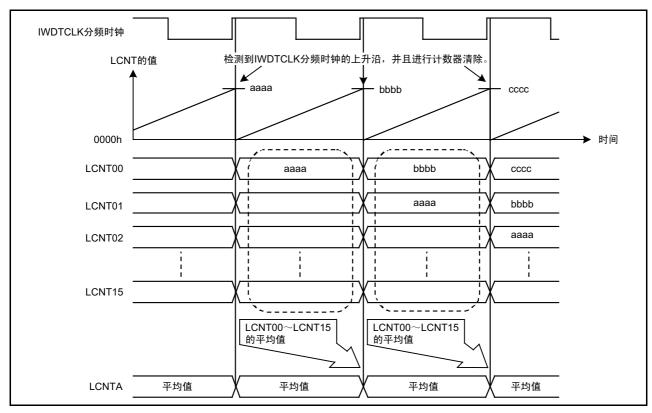

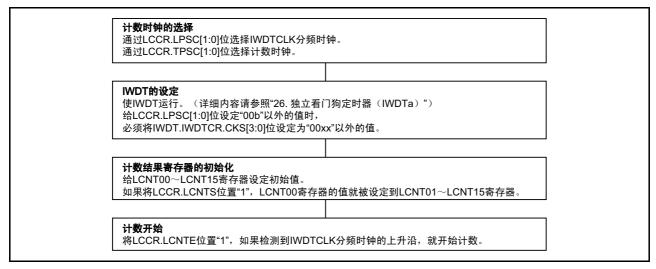

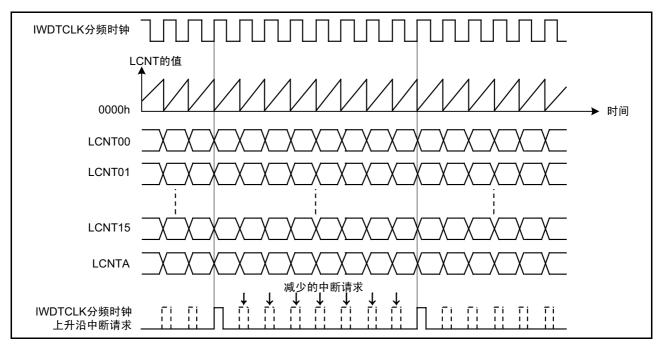

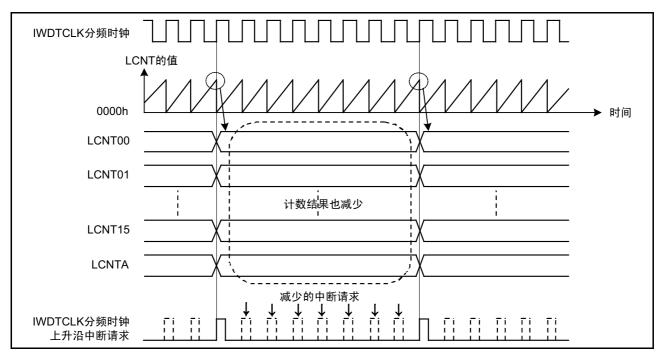

| 23.2.10  | LOCO 计数控制寄存器 (LCCR)                             |     |

| 23.2.11  | LOCO 计数状态寄存器 (LCST)                             |     |

| 23.2.12  | LOCO 计数值寄存器 (LCNT)                              |     |

| 23.2.14  | LOCO 计数结果平均寄存器(LCNTA)                           |     |

| 23.2.14  | LOCO 计数结果寄存器 n(LCNTn)(n=00 ~ 15)                |     |

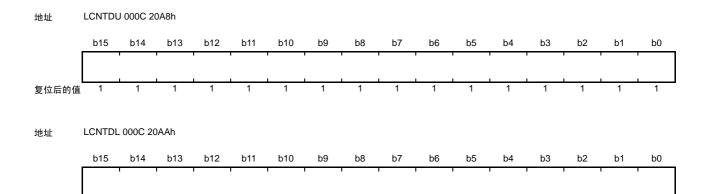

| 23.2.16  | LOCO 计数上限 / 下限容许偏差值寄存器 (LCNTDU、LCNTDL)          |     |

| ,_,_     |                                                 |     |

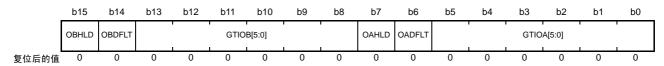

| 23.2.17  | 通用 PWM 定时器的 I/O 控制寄存器 (GTIOR)               | 566 |

|----------|---------------------------------------------|-----|

| 23.2.18  | 通用 PWM 定时器的中断输出设定寄存器 (GTINTAD)              | 570 |

| 23.2.19  | 通用 PWM 定时器的控制寄存器 (GTCR)                     | 572 |

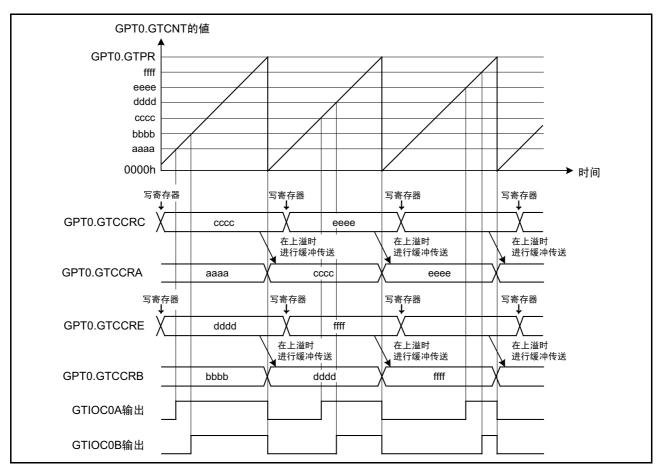

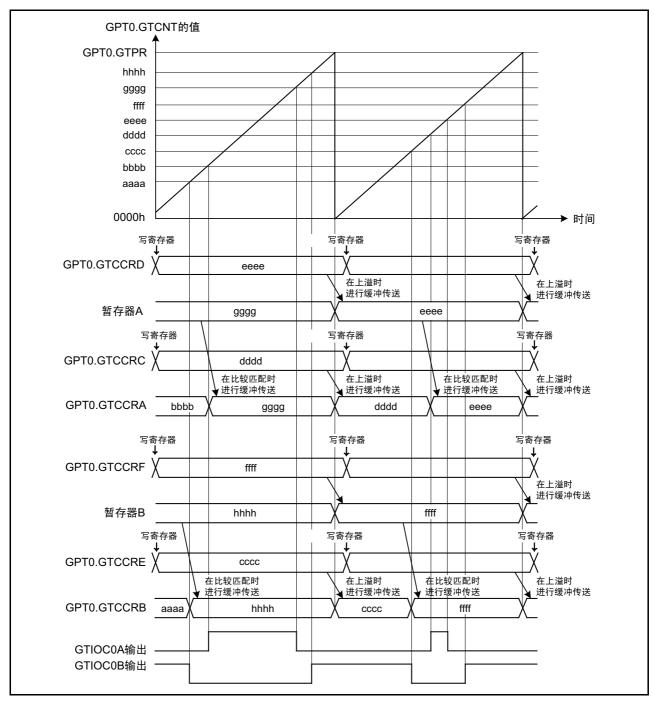

| 23.2.20  | 通用 PWM 定时器的缓冲允许寄存器 (GTBER)                  | 573 |

| 23.2.21  | 通用 PWM 定时器的计数方向寄存器 (GTUDC)                  | 575 |

| 23.2.22  | 通用 PWM 定时器的中断、 A/D 转换开始请求减少设定寄存器 (GTITC)    | 576 |

| 23.2.23  | 通用 PWM 定时器的状态寄存器 (GTST)                     |     |

| 23.2.24  | 通用 PWM 定时器的计数器 (GTCNT)                      | 581 |

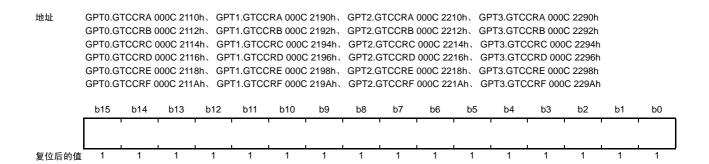

| 23.2.25  | 通用 PWM 定时器的比较捕捉寄存器 m (GTCCRm)(m=A $\sim$ F) | 582 |

| 23.2.26  | 通用 PWM 定时器的周期设定寄存器 (GTPR)                   | 582 |

| 23.2.27  | 通用 PWM 定时器的周期设定缓冲寄存器 (GTPBR)                | 582 |

| 23.2.28  | 通用 PWM 定时器的周期设定双缓冲寄存器 (GTPDBR)              | 583 |

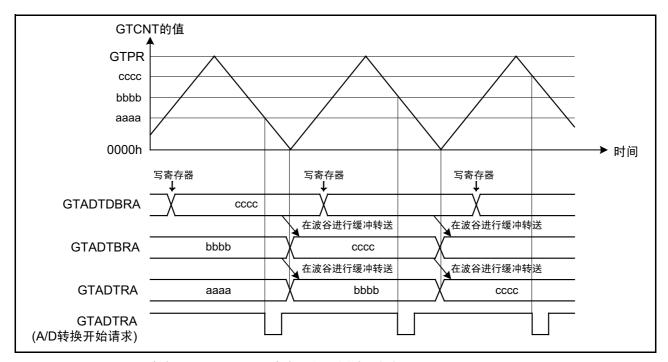

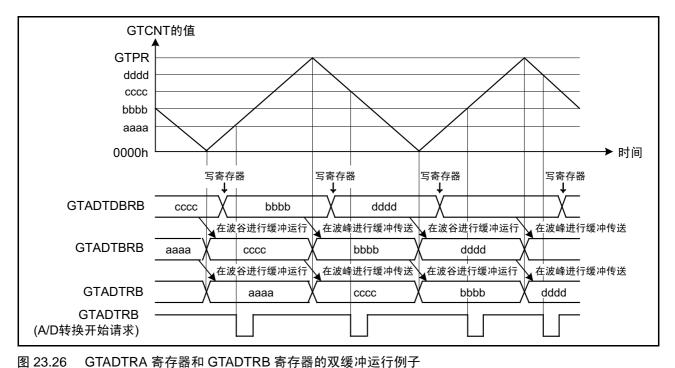

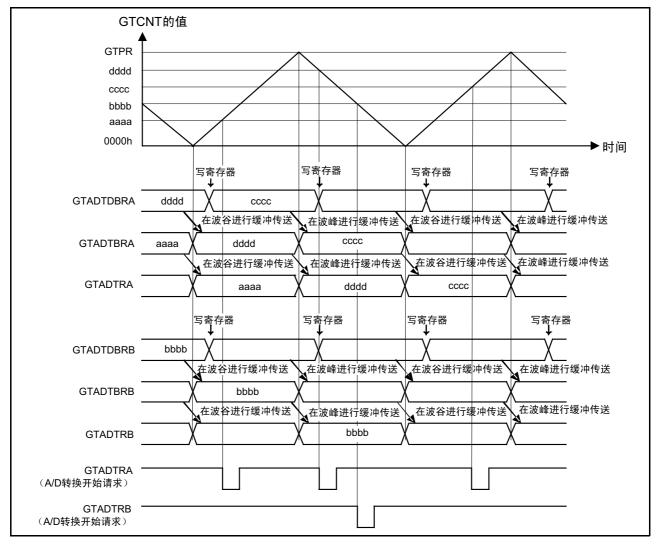

| 23.2.29  | A/D 转换开始请求时序寄存器 m (GTADTRm) (m=A、B)         | 583 |

| 23.2.30  | A/D 转换开始请求时序缓冲寄存器 m (GTADTBRm) (m=A、B)      |     |

| 23.2.31  | A/D 转换开始请求时序双缓冲寄存器 m (GTADTDBRm) (m=A、B)    | 583 |

| 23.2.32  | 通用 PWM 定时器的输出无效控制寄存器 (GTONCR)               | 584 |

| 23.2.33  | 通用 PWM 定时器的死区时间控制寄存器 (GTDTCR)               |     |

| 23.2.34  | 通用 PWM 定时器的死区时间值寄存器 m (GTDVm)(m=U、D)        | 587 |

| 23.2.35  | 通用 PWM 定时器的死区时间缓冲寄存器 m (GTDBm)(m=U、D)       | 587 |

| 23.2.36  | 通用 PWM 定时器的输出保护功能状态寄存器 (GTSOS)              | 588 |

| 23.2.37  | 通用 PWM 定时器的输出保护功能暂时解除寄存器 (GTSOTR)           | 588 |

| 23.3 运行  | 说明                                          | 589 |

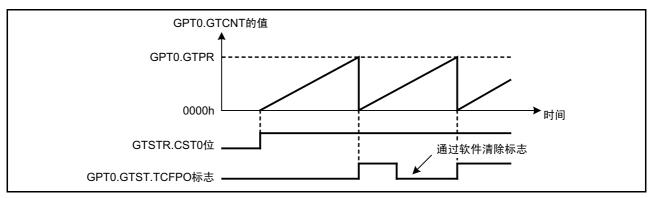

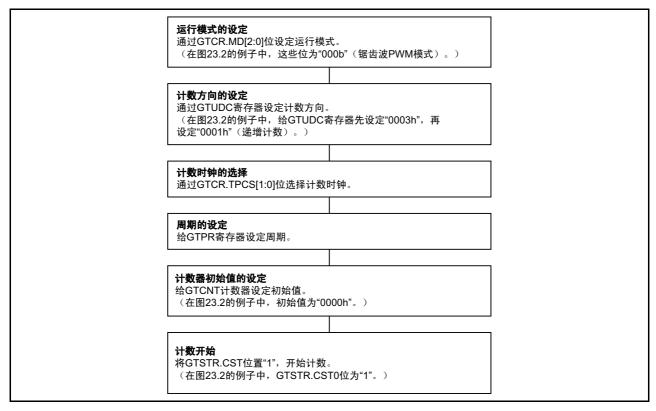

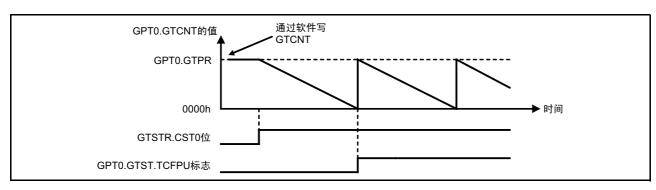

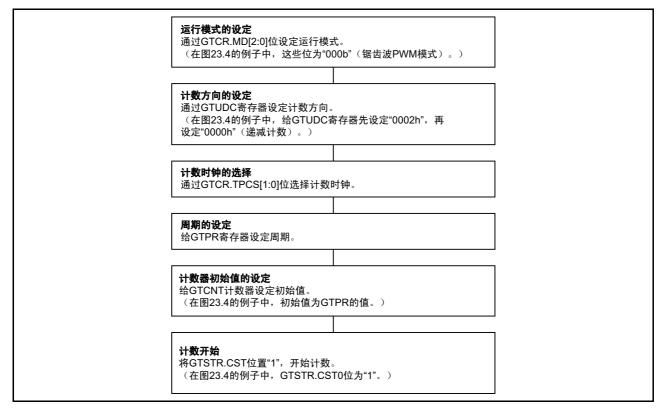

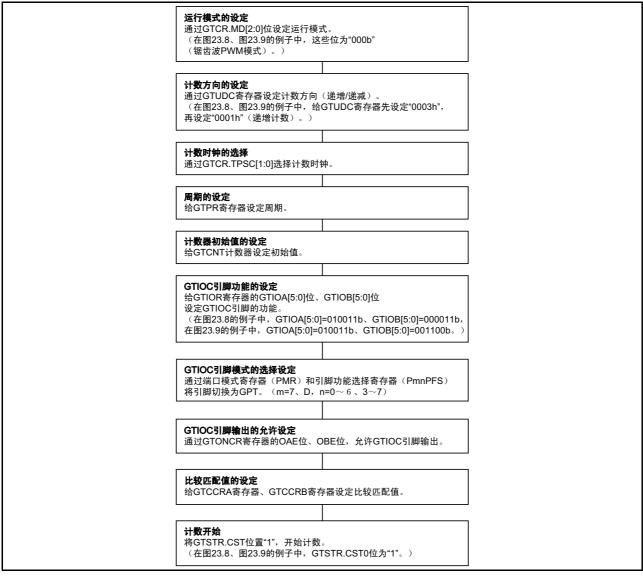

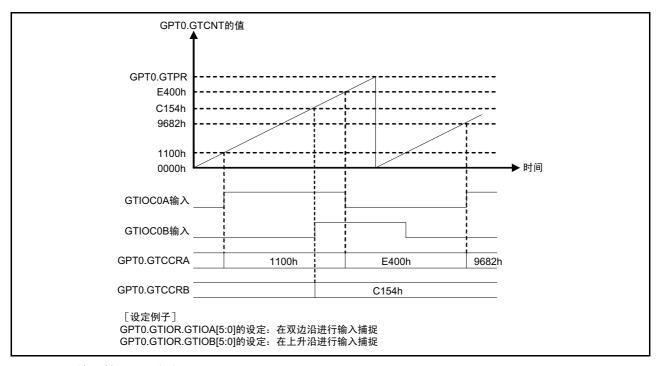

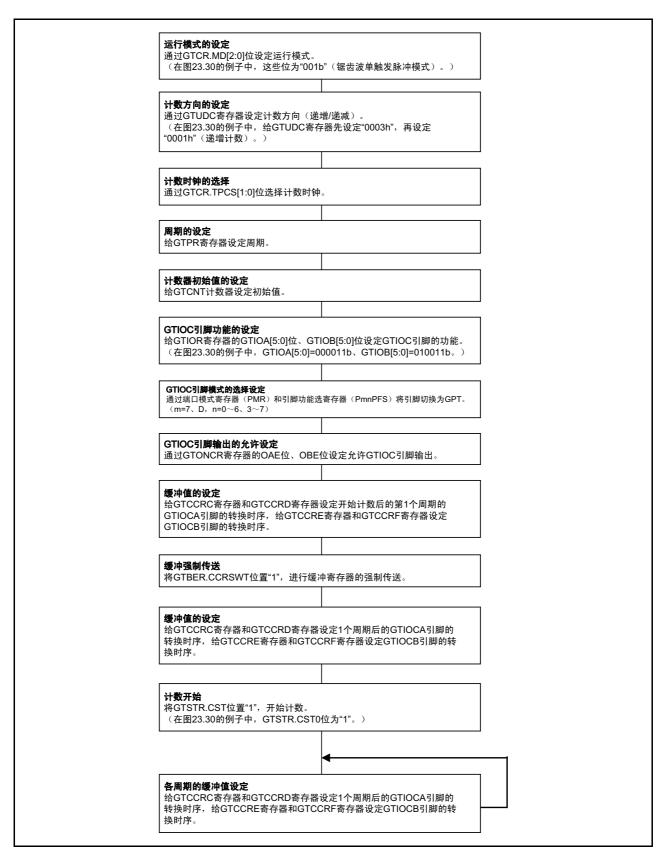

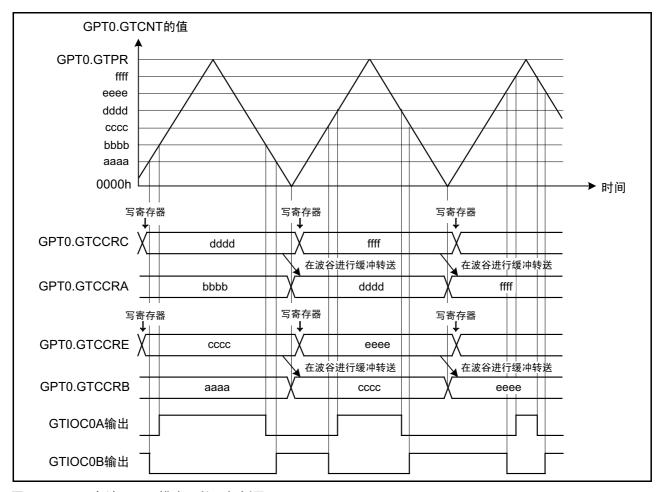

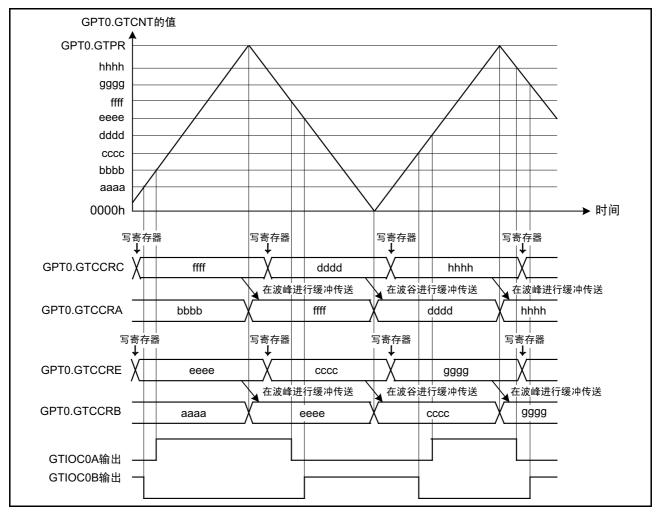

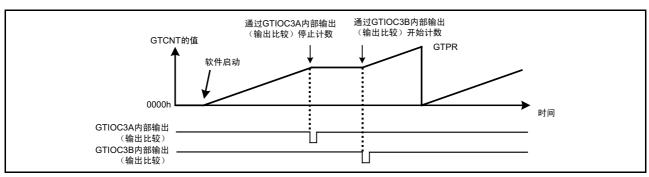

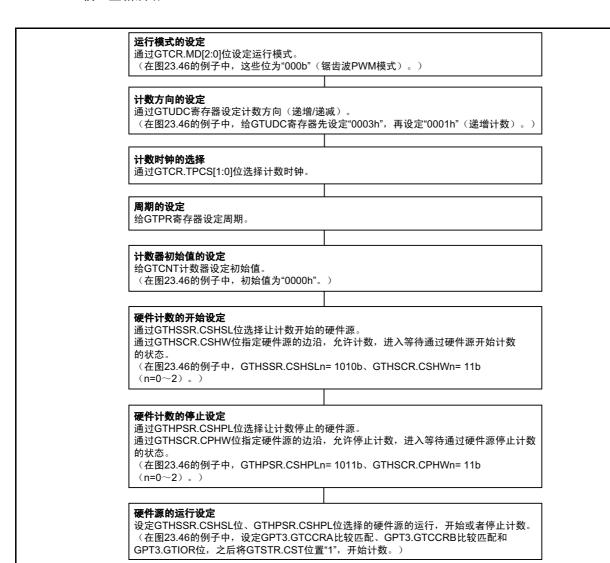

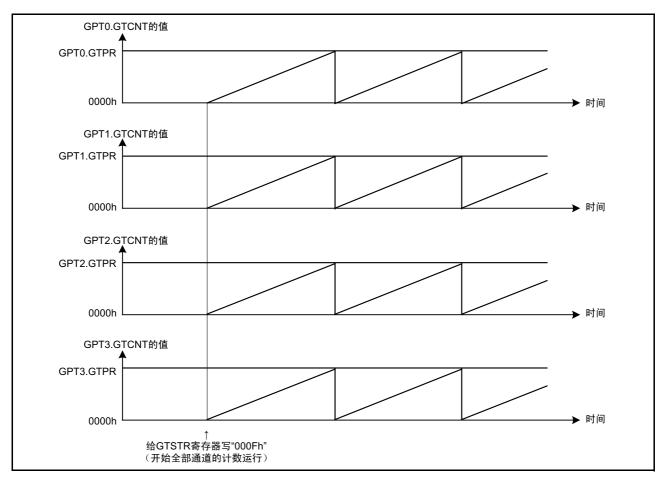

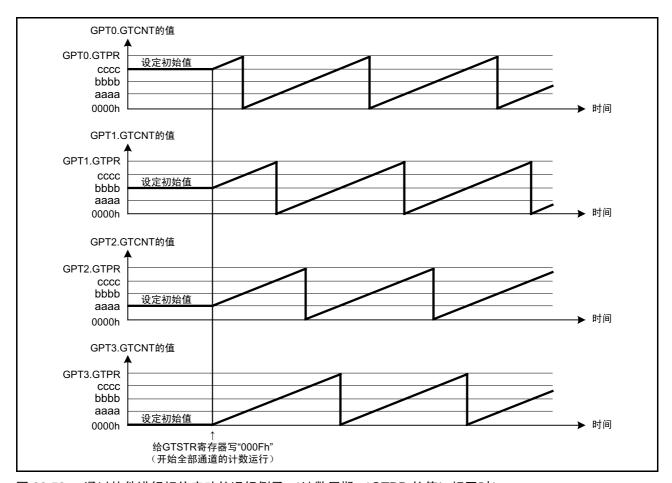

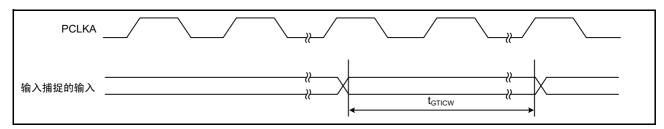

| 23.3.1   | 基本运行                                        | 589 |

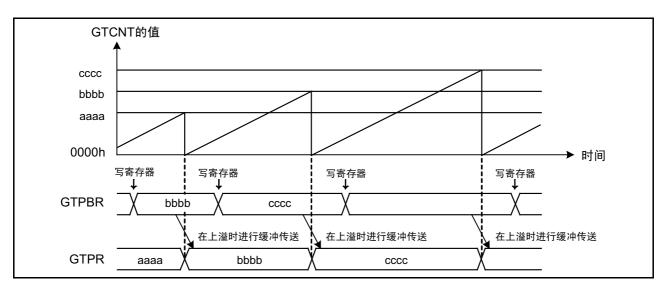

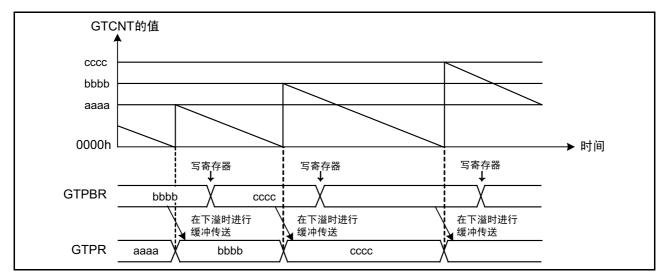

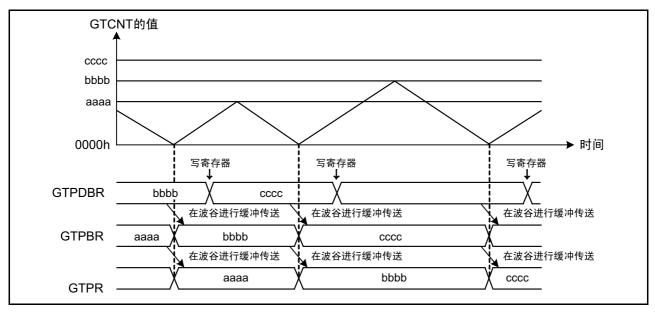

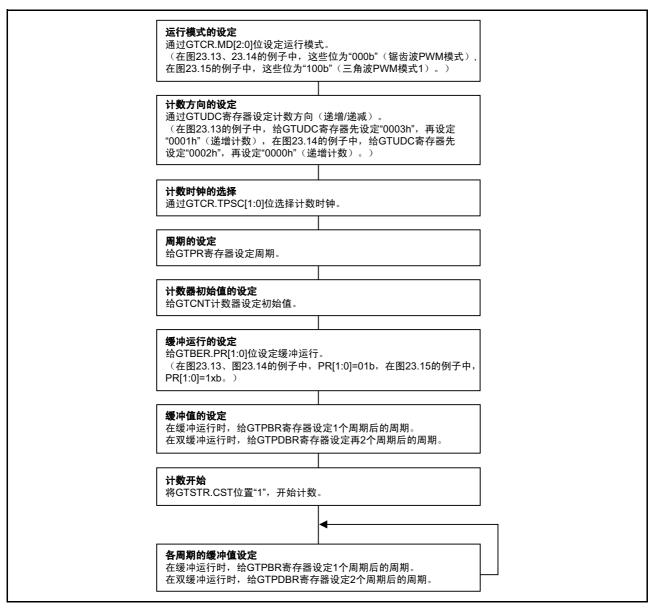

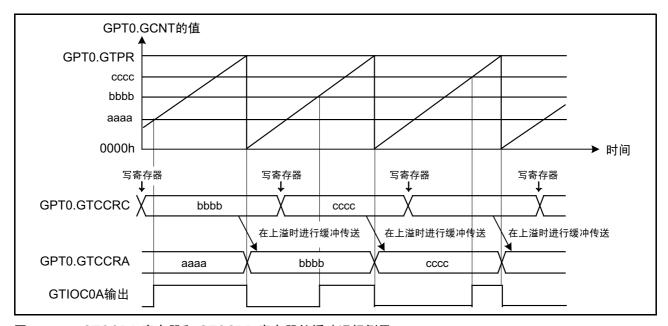

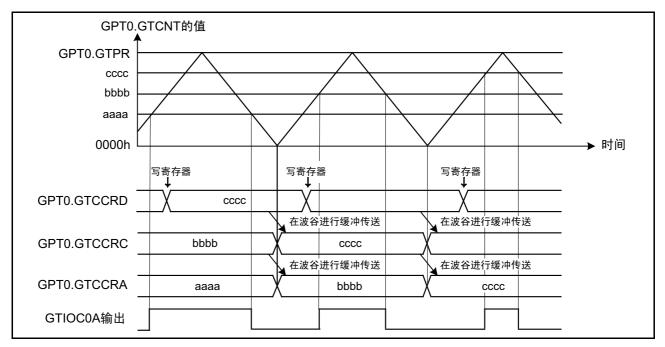

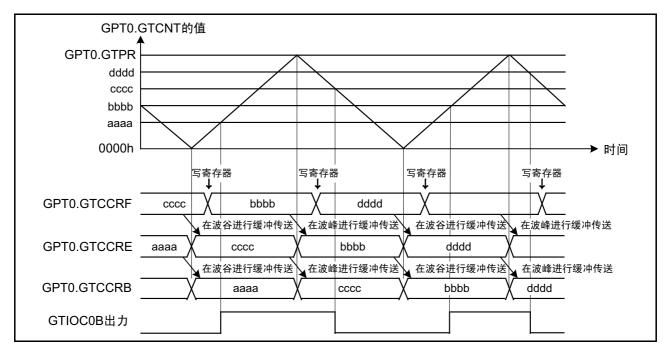

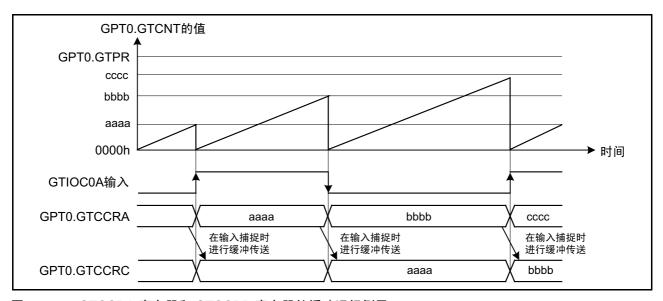

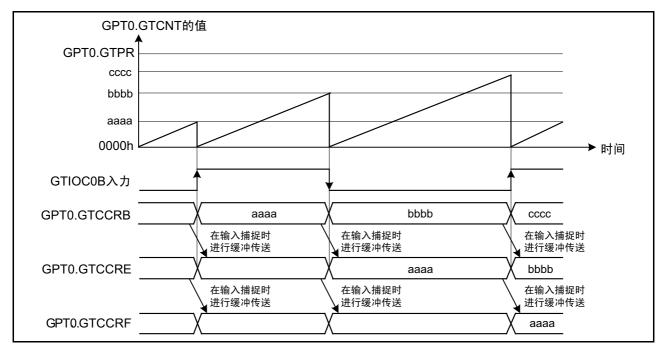

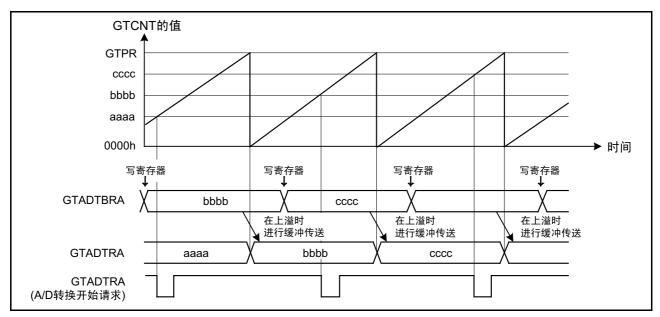

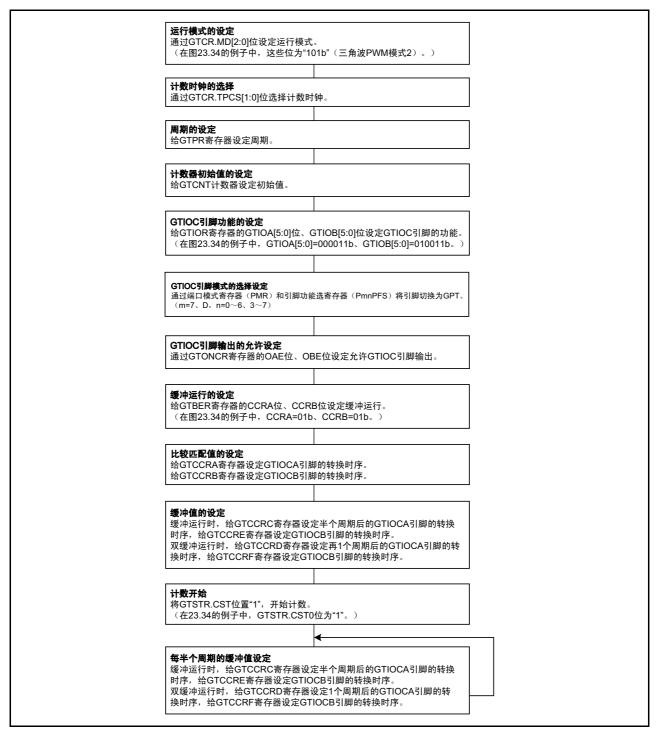

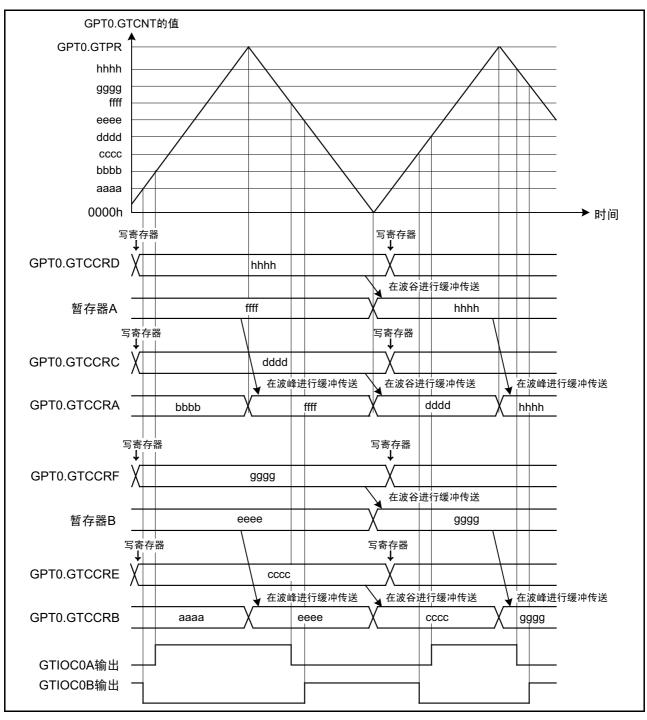

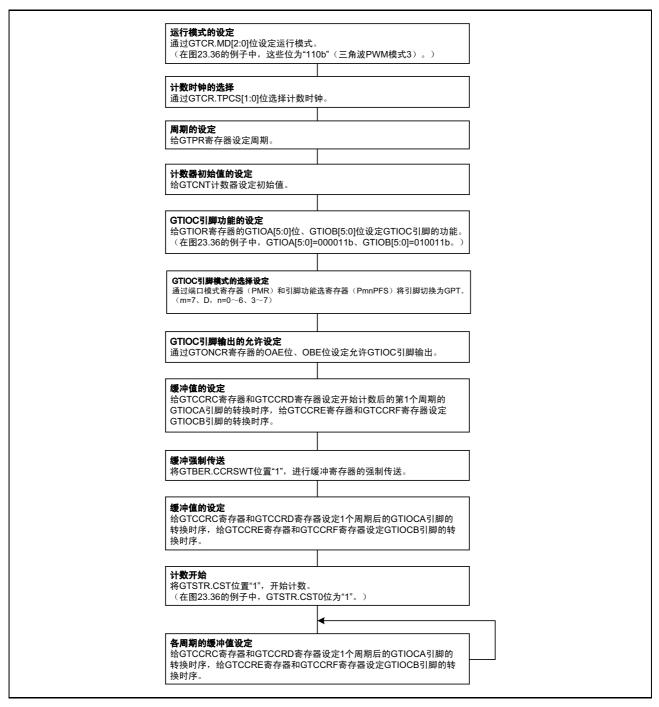

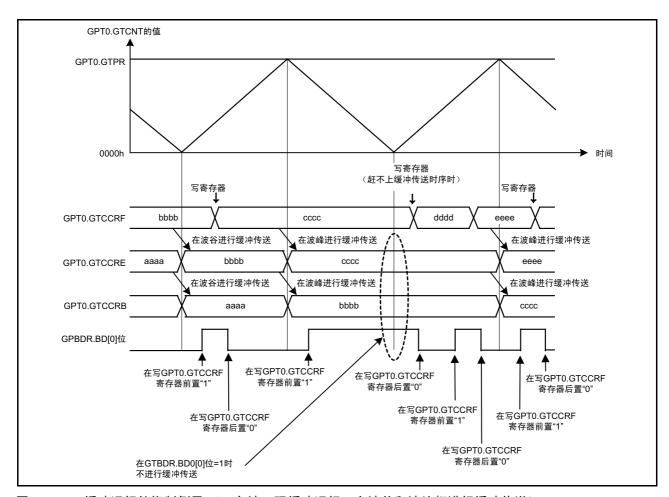

| 23.3.2   | 缓冲运行                                        | 598 |

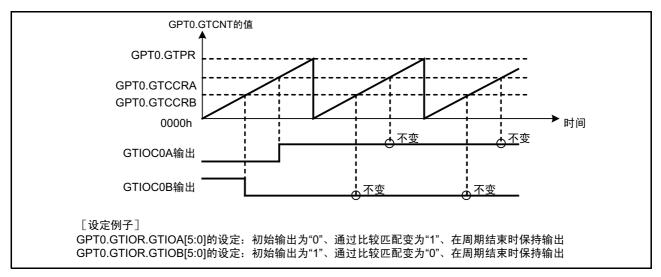

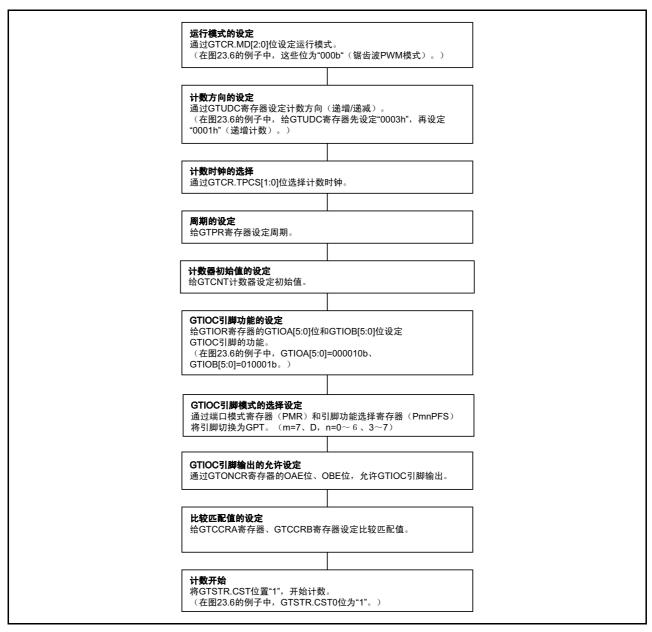

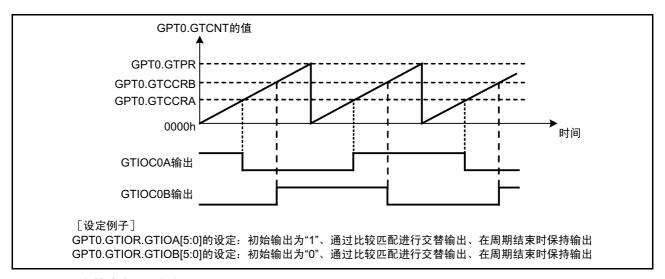

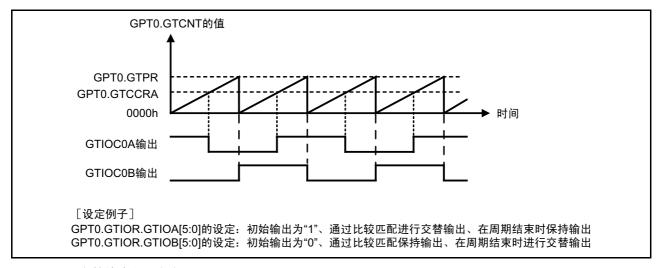

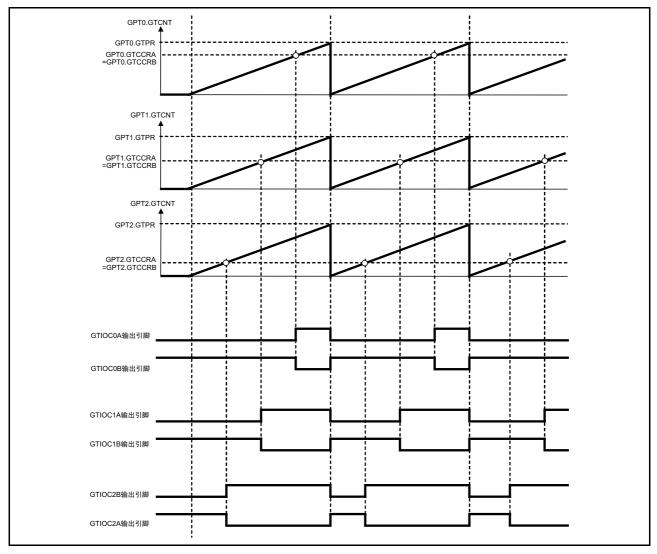

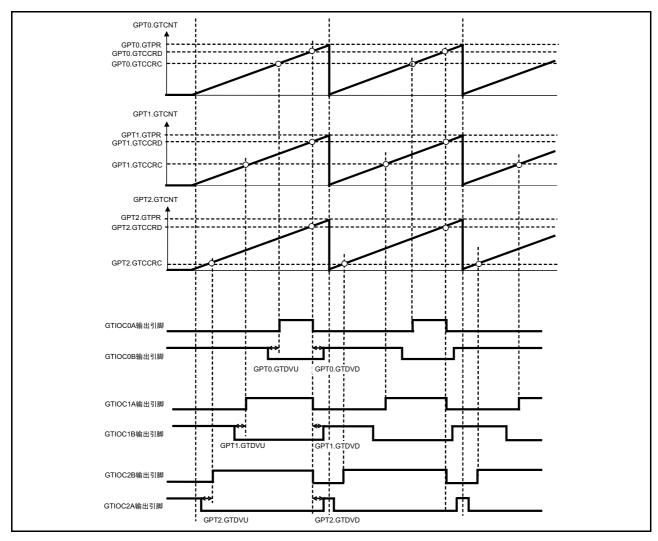

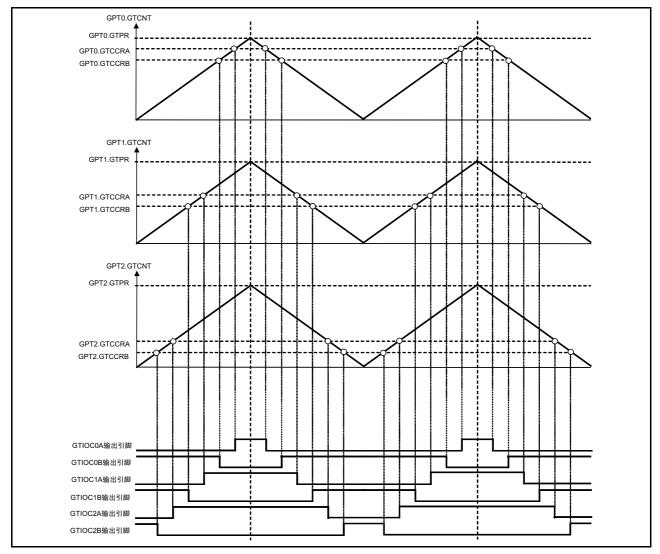

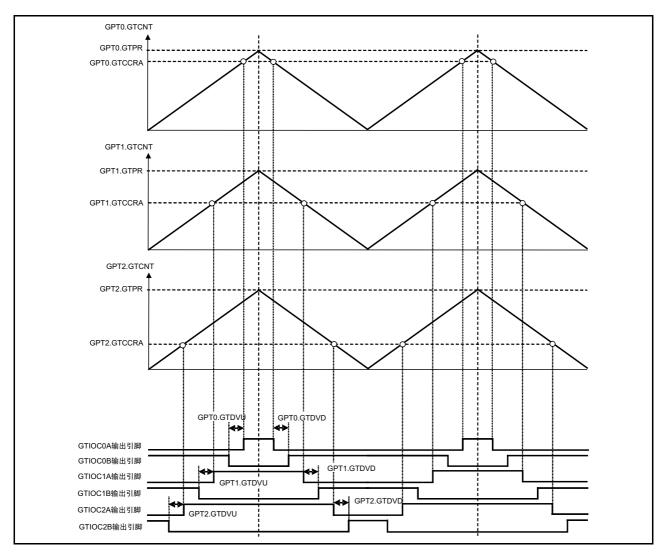

| 23.3.3   | PWM 输出运行模式                                  | 609 |

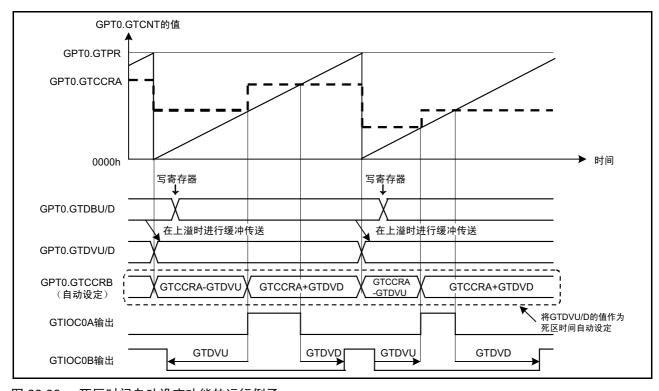

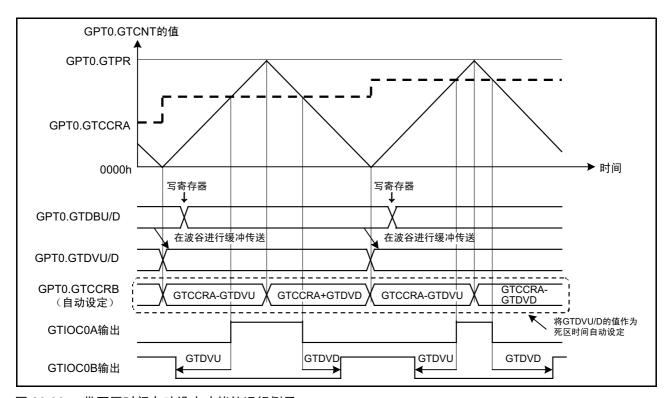

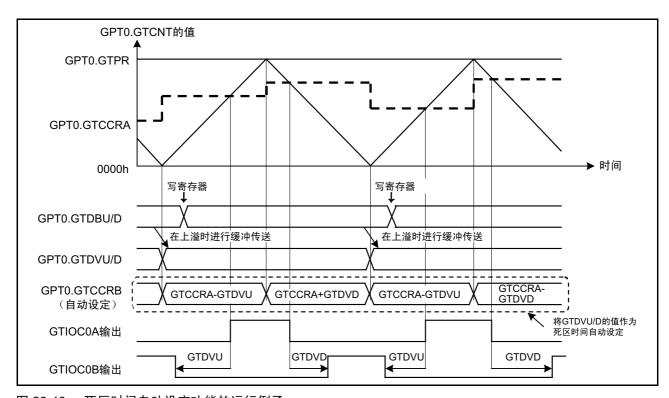

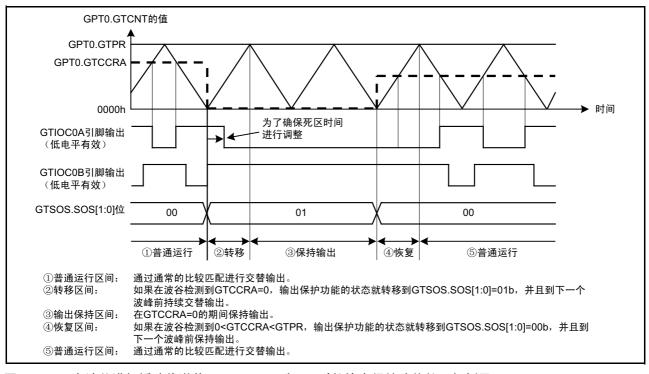

| 23.3.4   | 死区时间自动设定功能                                  | 621 |

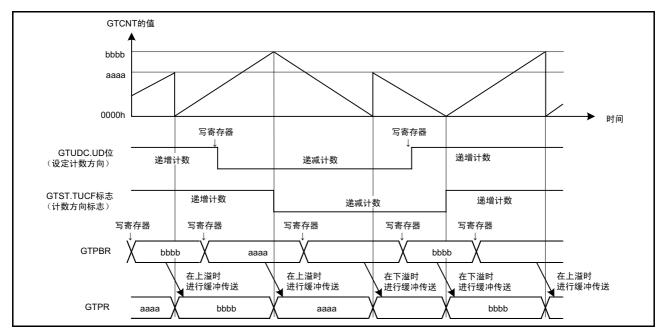

| 23.3.5   | 计数方向转换功能                                    |     |

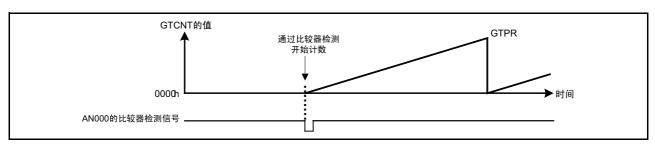

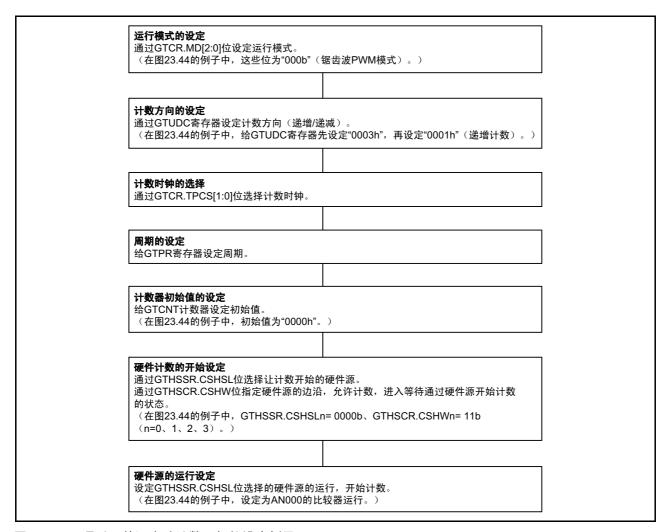

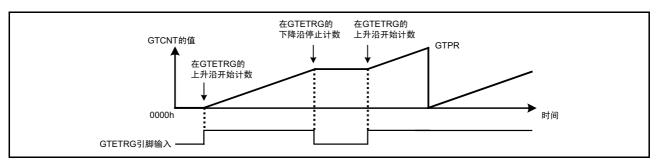

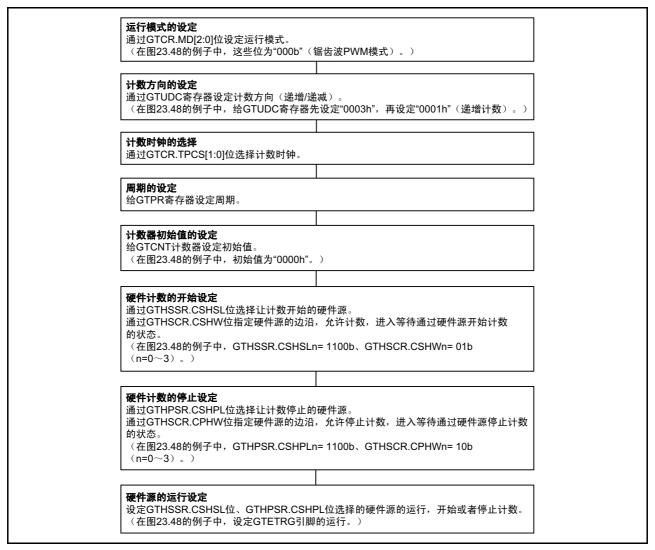

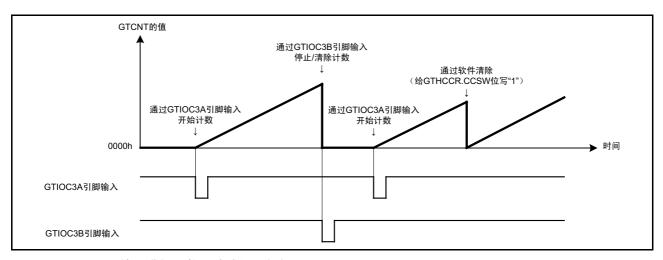

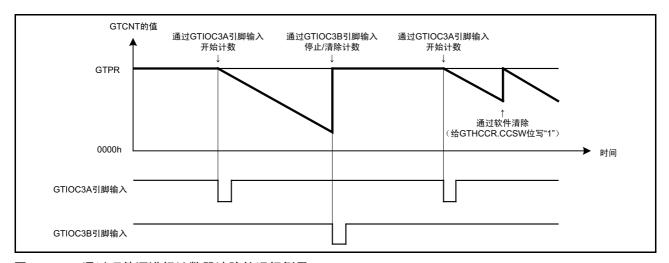

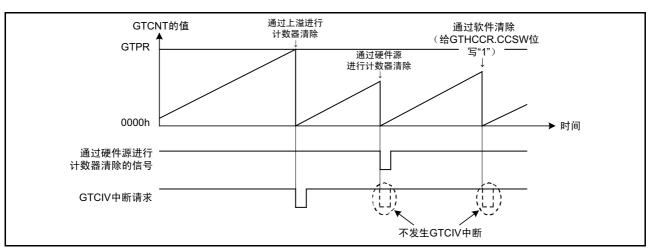

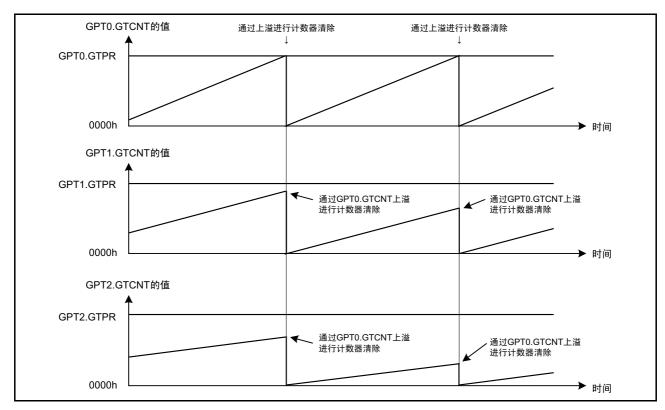

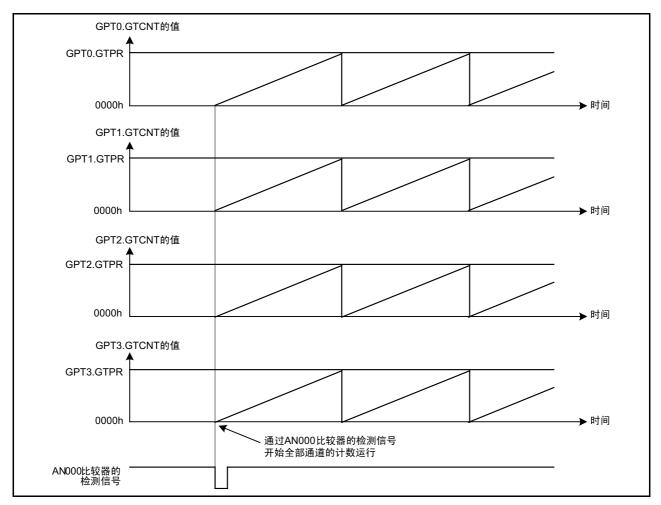

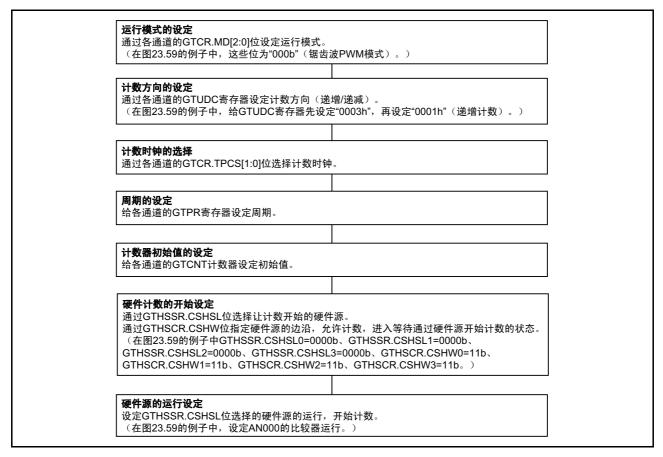

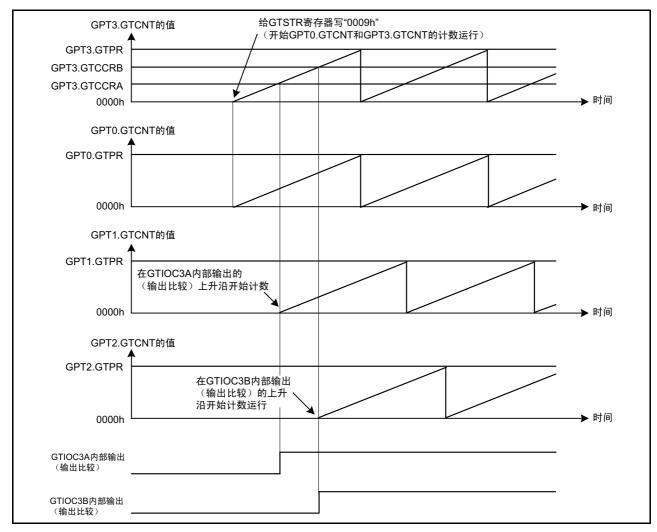

| 23.3.6   | 硬件启动 / 停止、清除运行                              | 626 |

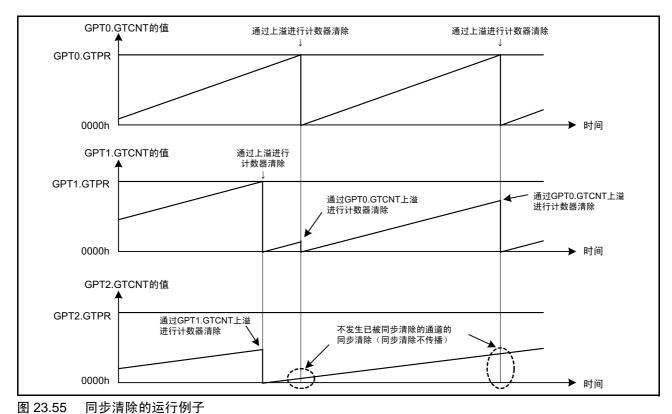

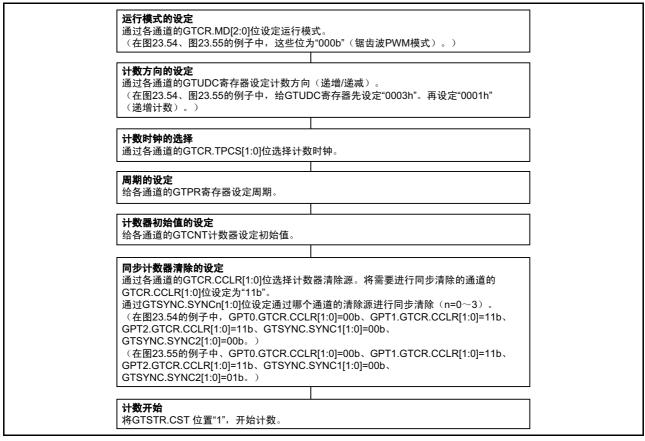

| 23.3.7   | 同步运行                                        |     |

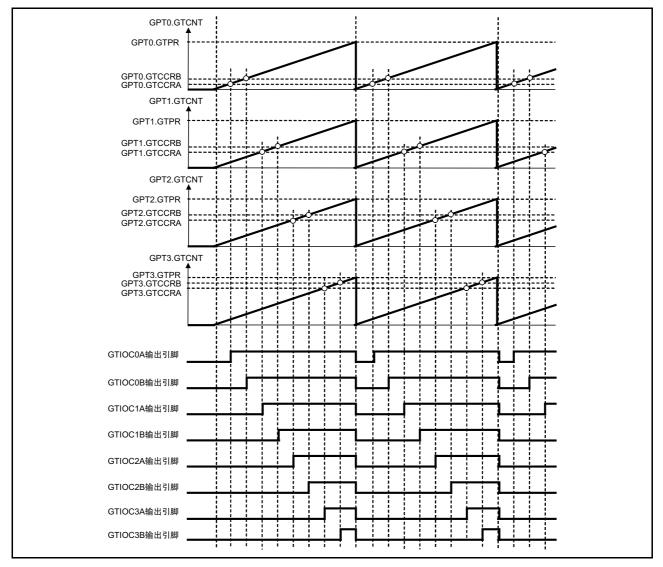

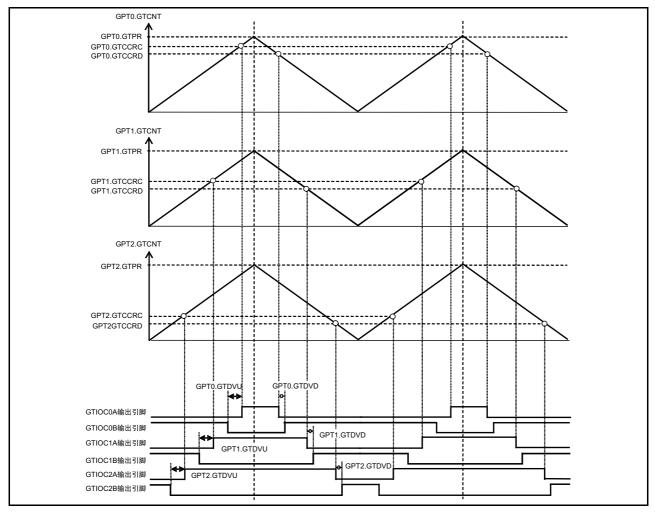

| 23.3.8   | PWM 输出的运行例子                                 |     |

| 23.4 中断  | 源                                           |     |

| 23.4.1   | 中断源和优先级                                     |     |

| 23.4.2   | DTC 的启动                                     |     |

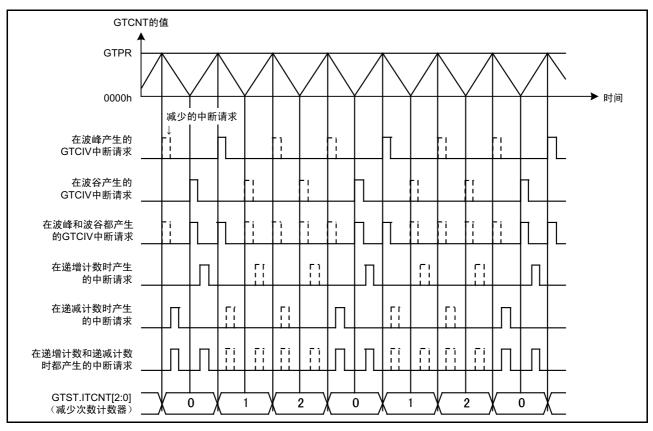

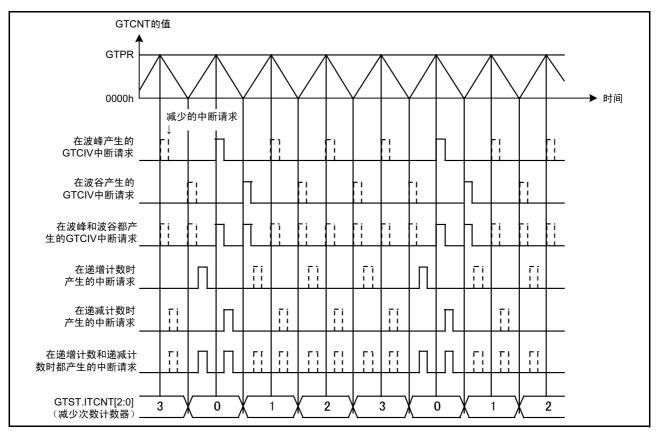

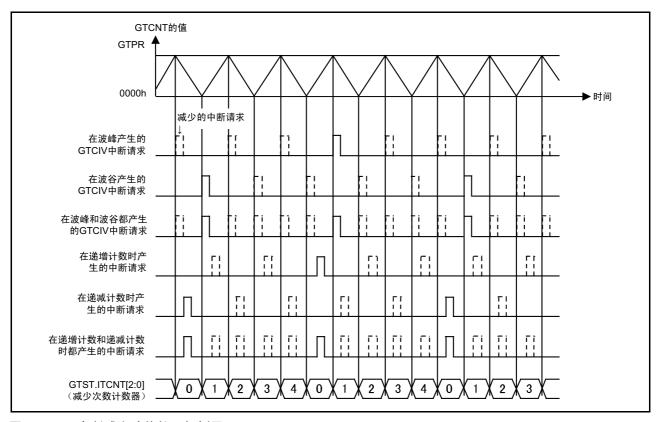

| 23.4.3   | 中断、A/D 转换开始请求的减少功能                          |     |

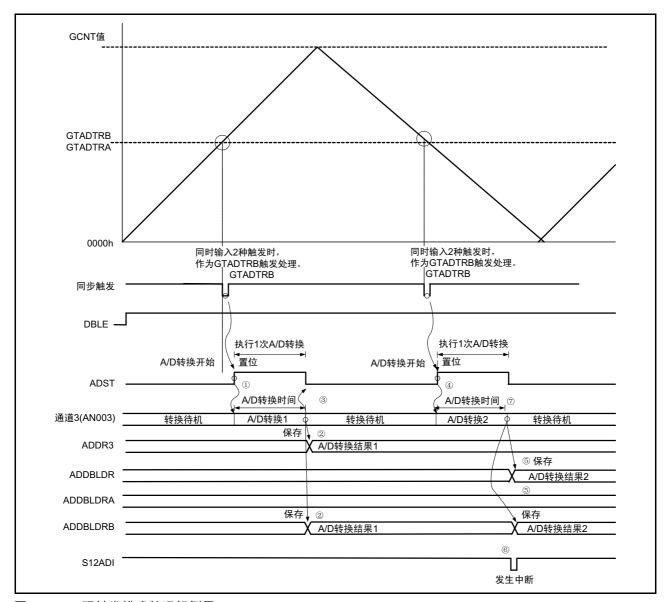

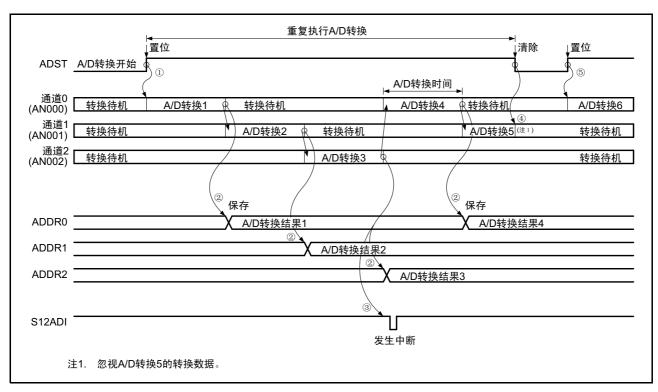

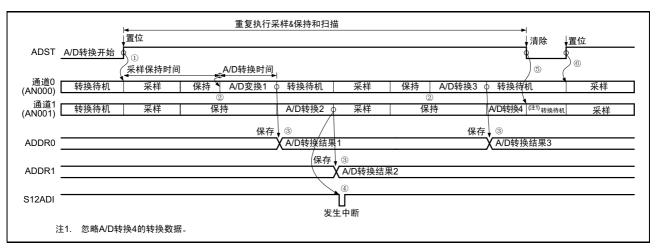

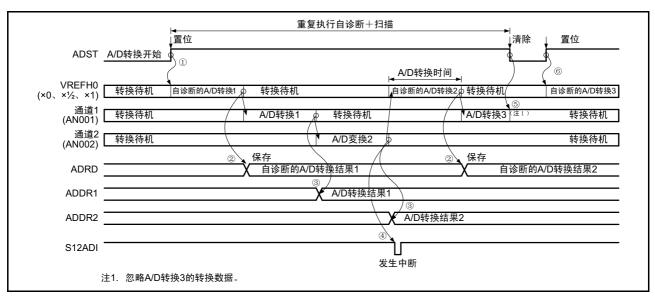

| 23.5 A/D | 转换开始请求                                      | 652 |

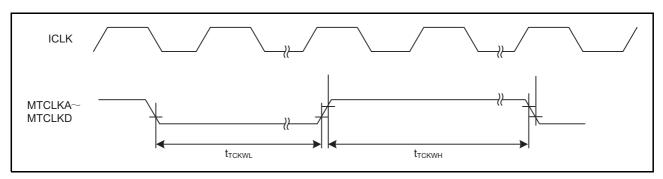

|          | TCLK 计数功能                                   |     |

|          | 功能                                          |     |

| 23.7.1   | 计数器的写保护                                     |     |

| 23.7.2   | 缓冲运行的抑制                                     |     |

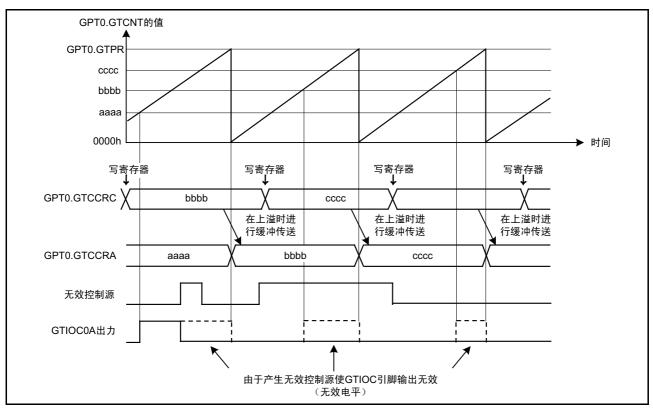

| 23.7.3   | GTIOC 引脚输出的无效控制                             |     |

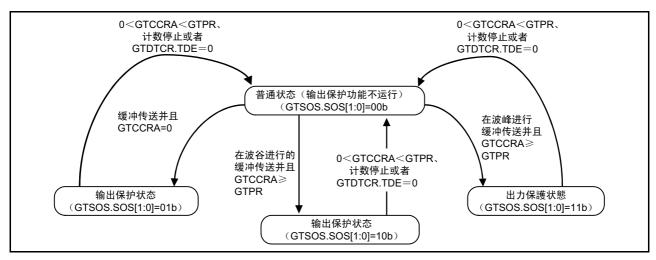

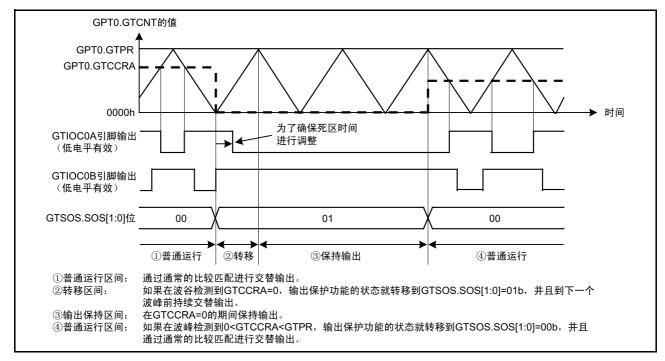

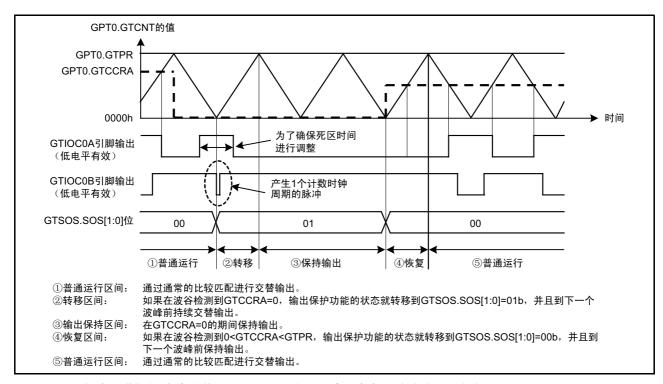

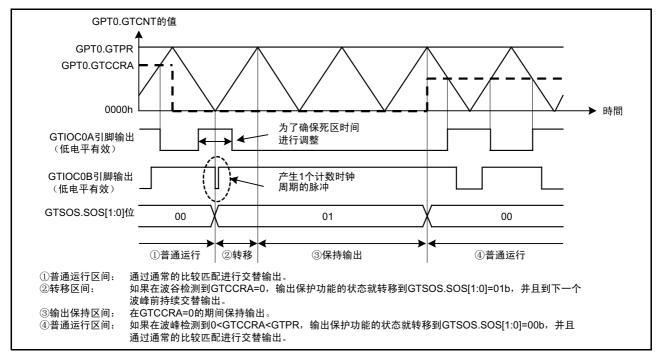

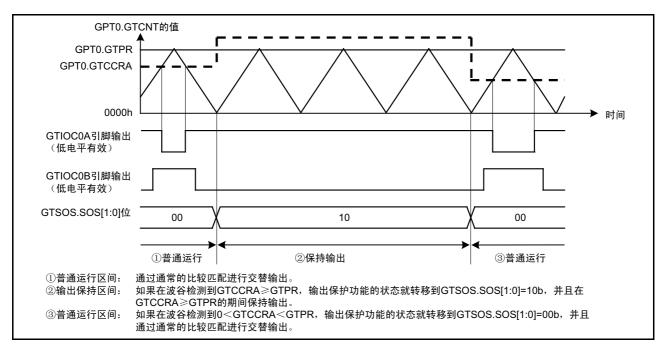

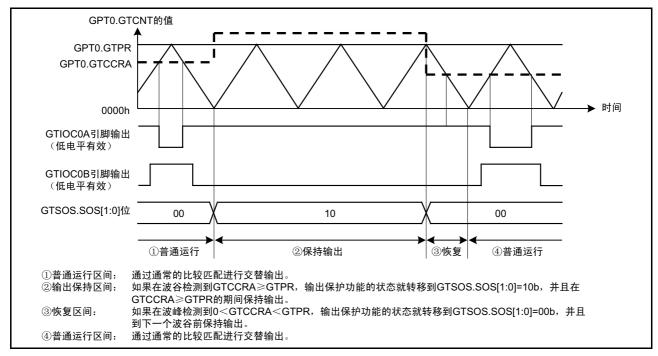

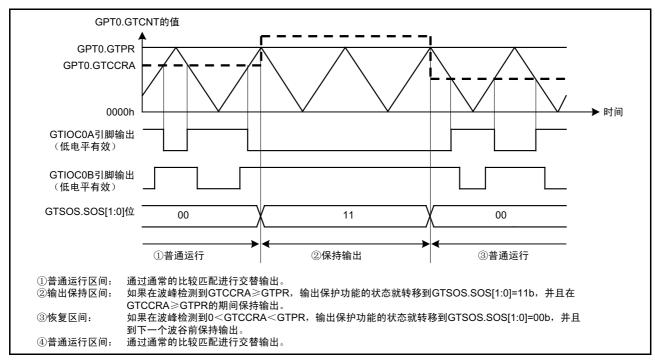

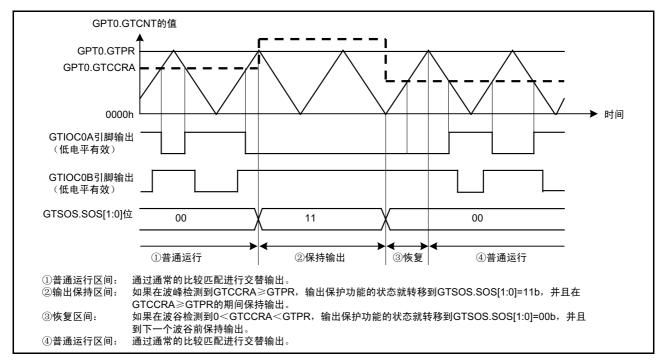

| 23.7.4   | GTIOC 引脚输出的输出保护功能                           |     |

| 23.7.5   | 通过 POE 功能进行 GTIOC 引脚输出的高阻抗控制                |     |

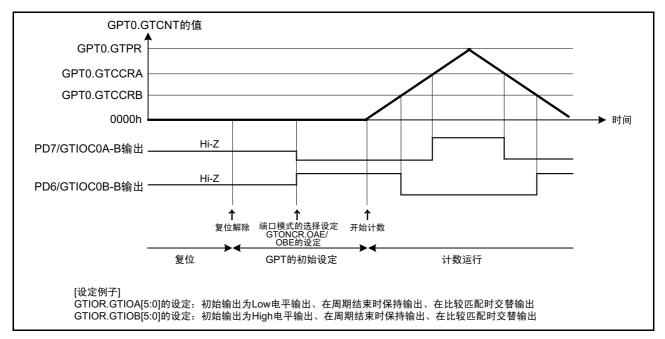

|          | 引脚的初始化方法                                    |     |

| 23.8.1   | 复位后的引脚设定                                    |     |

| 23.8.2   | 因运行中的异常等引起的引脚初始化                            |     |

|          | 时的注意事项                                      |     |

| 23.9.1   | 模块停止功能的设定                                   |     |

| 23.9.2   | 比较匹配运行时的 GTCCRn 寄存器的设定 (n=A、B、C、D、E、F)      |     |

| 23.9.3   | 安全停止定时器的方法                                  |     |

| 23.9.4   | 使用 IWDTCLK 计数功能时的低功耗功能的设定                   | 666 |

| 24. 比较四 | 型配定时器 (CMT)                               | 667 |

|---------|-------------------------------------------|-----|

| 24.1 概要 | fi                                        | 667 |

| 24.2 寄存 | 序器说明                                      | 668 |

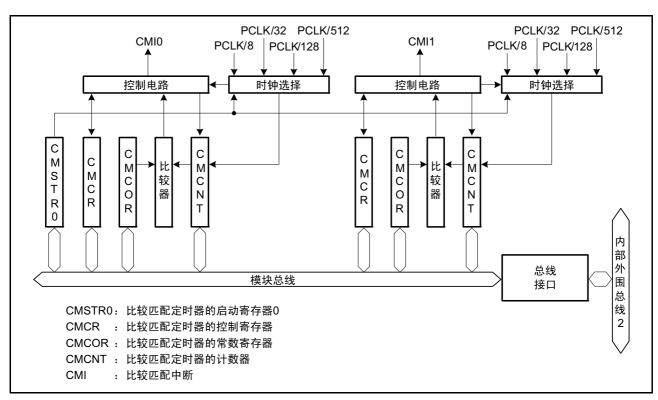

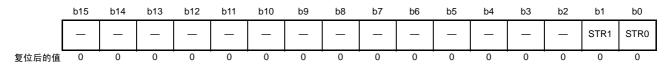

| 24.2.1  | 比较匹配定时器的启动寄存器 0 (CMSTR0)                  | 668 |

| 24.2.2  | 比较匹配定时器的启动寄存器 1 (CMSTR1)                  | 668 |

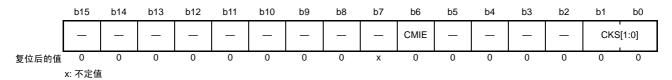

| 24.2.3  | 比较匹配定时器的控制寄存器 (CMCR)                      | 669 |

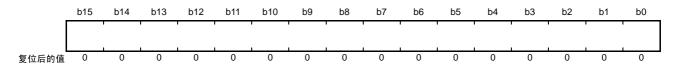

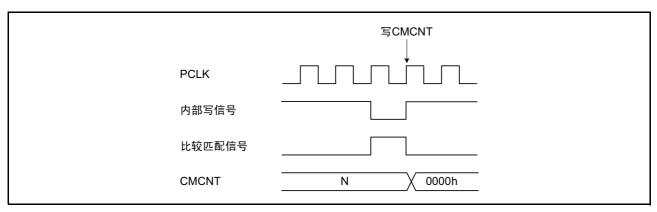

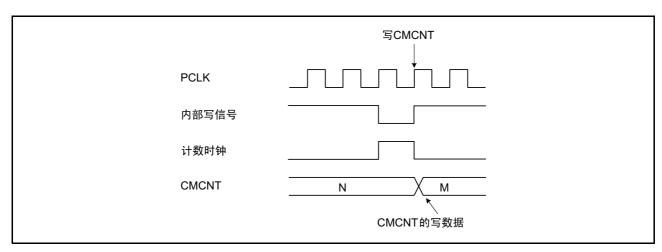

| 24.2.4  | 比较匹配定时器的计数器 (CMCNT)                       | 670 |

| 24.2.5  | 比较匹配定时器的常数寄存器 (CMCOR)                     | 670 |

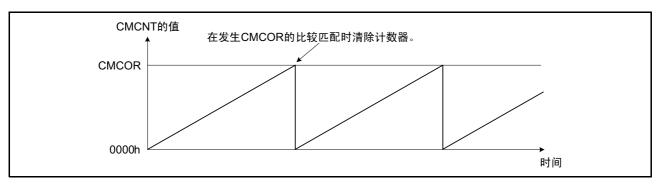

| 24.3 运行 | F说明                                       | 671 |

| 24.3.1  | 周期计数                                      | 671 |

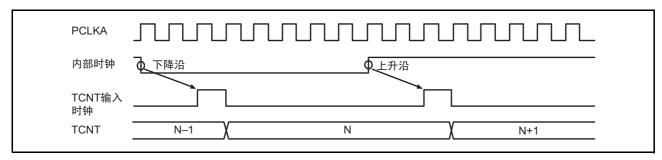

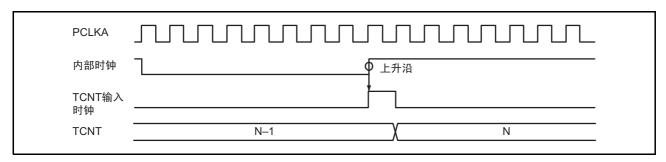

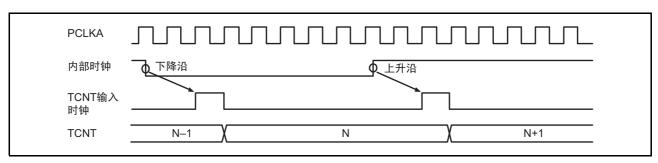

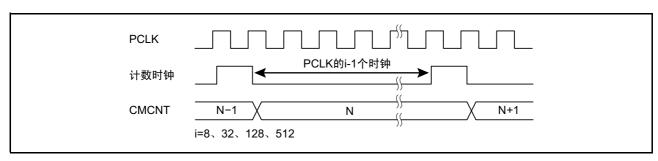

| 24.3.2  | CMCNT 计数器的计数时序                            | 671 |

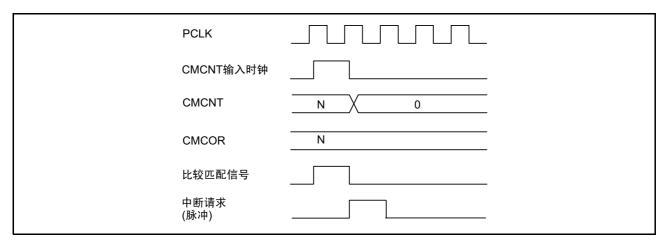

| 24.4 中勝 | Ť                                         | 672 |

| 24.4.1  | 中断源                                       |     |

| 24.4.2  | 比较匹配中断的发生时序                               | 672 |

| 24.5 使月 | ]时的注意事项                                   | 673 |

| 24.5.1  | 模块停止功能的设定                                 | 673 |

| 24.5.2  | CMCNT 计数器的写和比较匹配的竞争                       | 673 |

| 24.5.3  | CMCNT 计数器的写和递增计数的竞争                       | 673 |

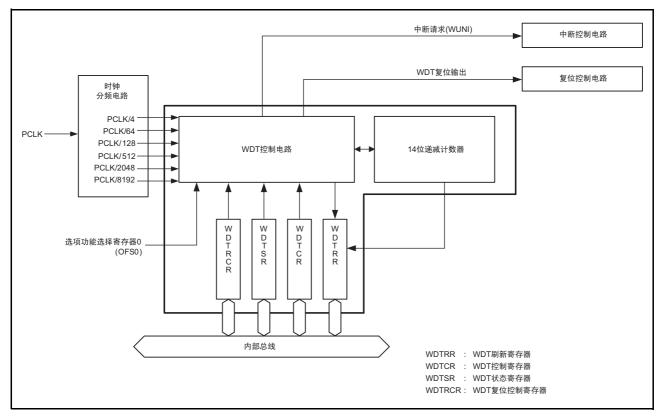

| 25. 看门犭 | 向定时器 (WDTA)                               | 674 |

|         |                                           |     |

| ****    | 字器说明                                      |     |

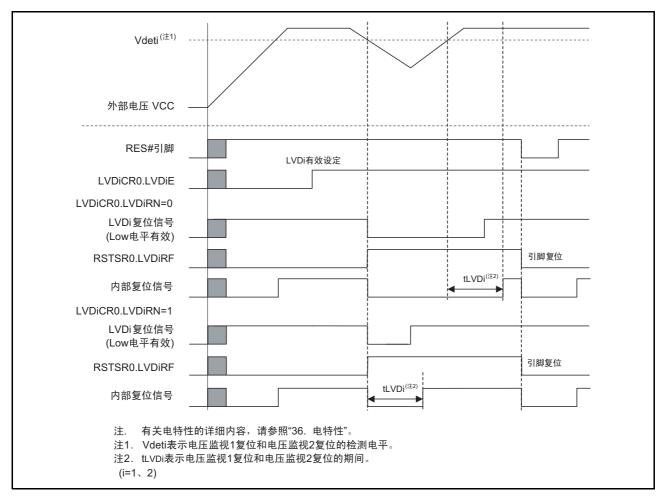

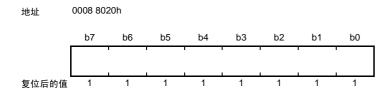

| 25.2.1  | WDT 刷新寄存器 (WDTRR)                         |     |

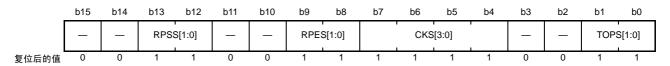

| 25.2.1  | WDT 控制寄存器(WDTCR)                          |     |

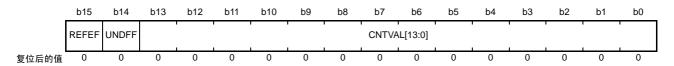

| 25.2.3  | WDT 状态寄存器 (WDTSR)                         |     |

| 25.2.3  | WDT                                       |     |

| 25.2.4  | 选项功能选择寄存器 0 (OFS0)                        |     |

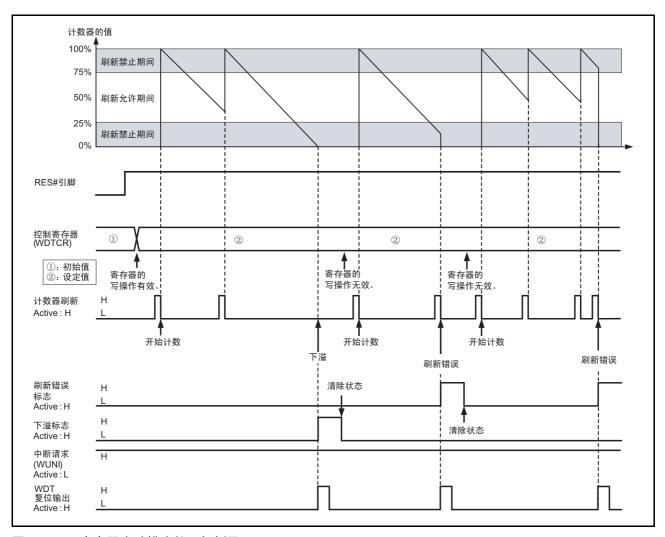

|         | 了说明                                       |     |

| 25.3.1  | 6. 多一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一一  |     |

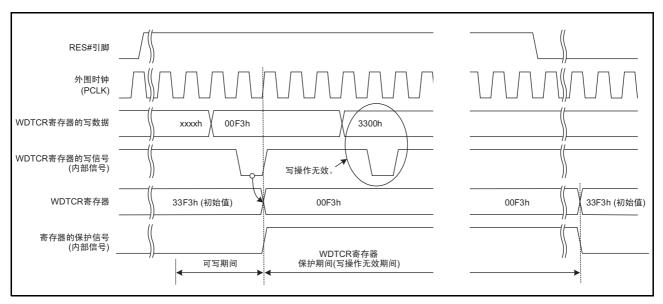

| 25.3.2  | WDTCR 寄存器和 WDTRCR 寄存器的写控制                 |     |

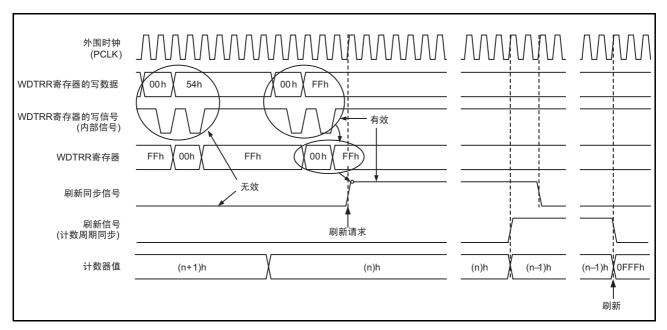

| 25.3.3  | 刷新                                        |     |

| 25.3.4  | 状态标志                                      |     |

| 25.3.5  | 复位输出                                      |     |

| 25.3.6  | 中断源                                       |     |

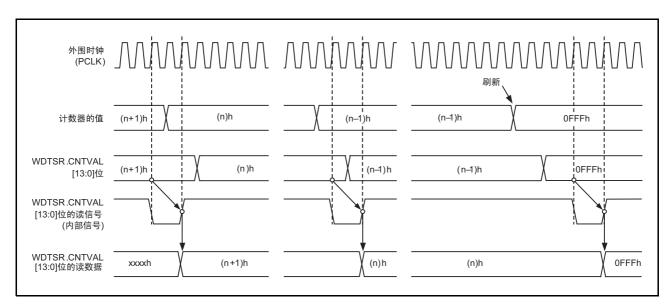

| 25.3.7  | <b>递减计数器值的读操作</b>                         |     |

| 25.3.8  | 选项功能选择寄存器 0 (OFS0) 和 WDT 寄存器的对应           | 687 |

|         |                                           |     |

|         | 膏门狗定时器 (IWDTa)                            |     |

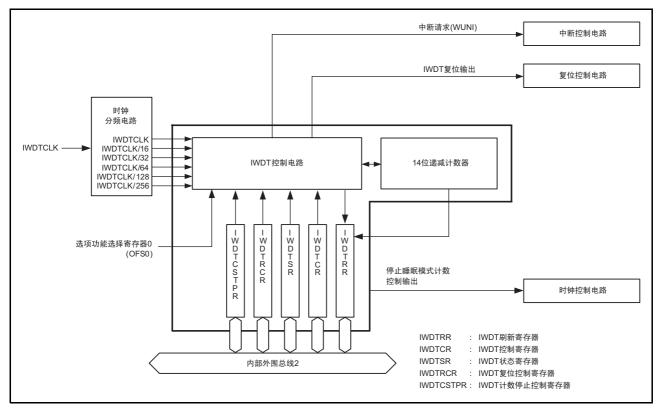

|         | 5                                         |     |

|         | 7器说明                                      |     |

| 26.2.1  | IWDT 刷新寄存器 (IWDTRR)                       |     |

| 26.2.2  | IWDT 控制寄存器 (IWDTCR)                       |     |

| 26.2.3  | IWDT 状态寄存器 (IWDTSR)                       |     |

| 26.2.4  | IWDT 复位控制寄存器 (IWDTRCR)                    |     |

| 26.2.5  | IWDT 计数停止控制寄存器 (IWDTCSTPR)                |     |

| 26.2.6  | 选项功能选择寄存器 0 (OFS0)                        |     |

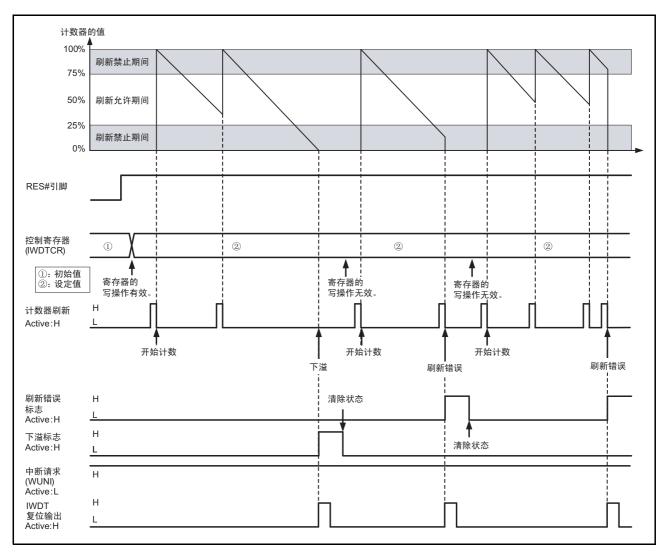

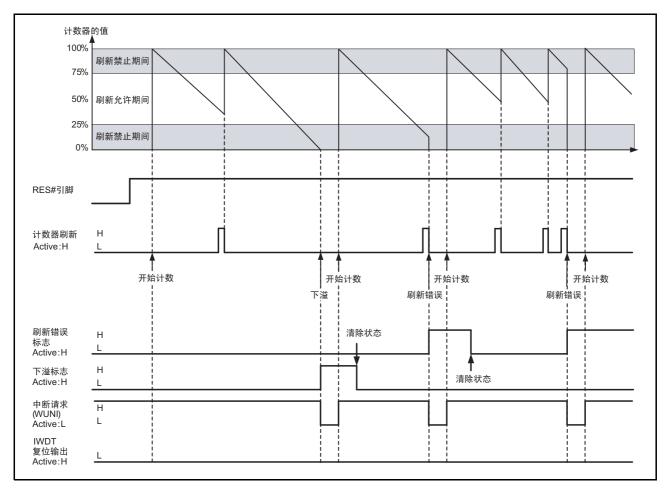

|         | 子说明                                       |     |

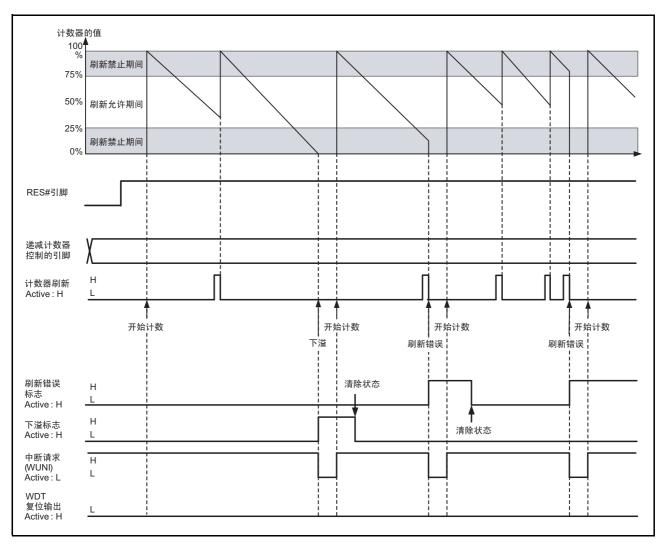

| 26.3.1  | 各计数开始条件下的运行                               |     |

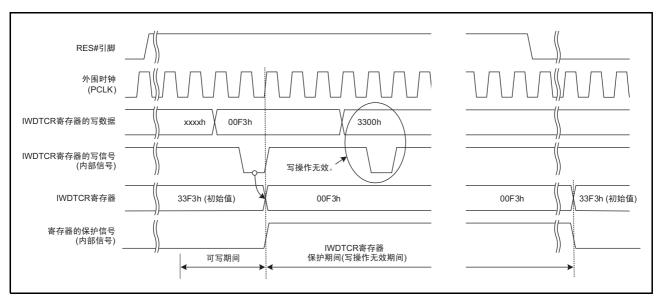

| 26.3.2  | IWDTCR 寄存器、IWDTRCR 寄存器和 IWDTCSTPR 寄存器的写控制 |     |

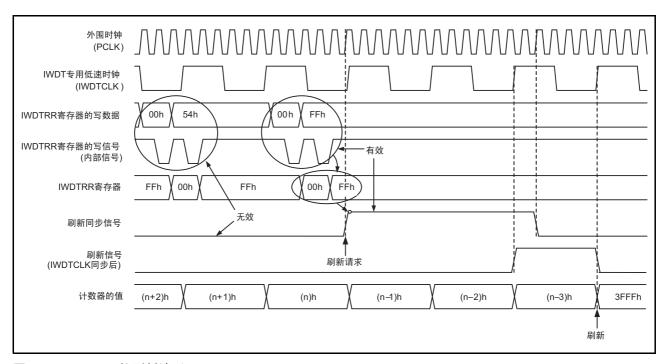

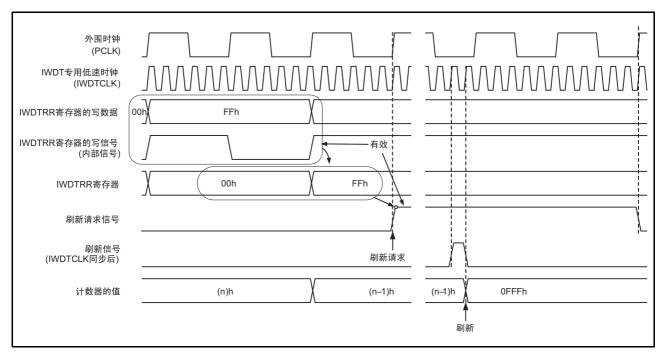

| 26.3.3  | 刷新                                        |     |

| 26.3.4  | 状态标志                                      |     |

| 26.3.5  | 复位输出                                      | /01 |

| 26.3.6           | 中断源                                                     | 702 |

|------------------|---------------------------------------------------------|-----|

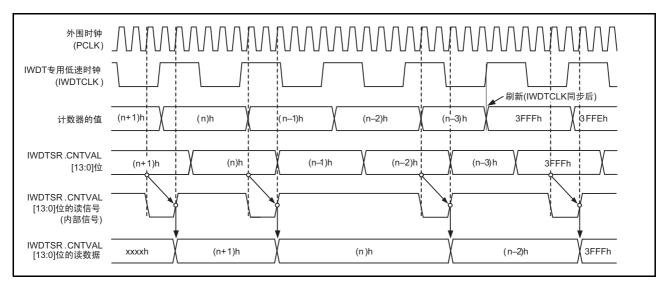

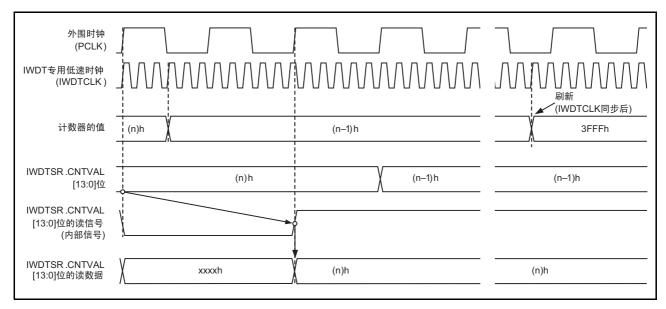

| 26.3.7           | 递减计数器值的读操作                                              | 702 |

| 26.3.8           | 选项功能选择寄存器 0 (OFS0) 和 IWDT 寄存器的对应                        | 703 |

| 26.4 使月          | 月时的注意事项                                                 | 703 |

| 26.4.1           | 刷新                                                      | 703 |

|                  |                                                         |     |

|                  | 通信接口 (SCIc、 SCId)                                       |     |

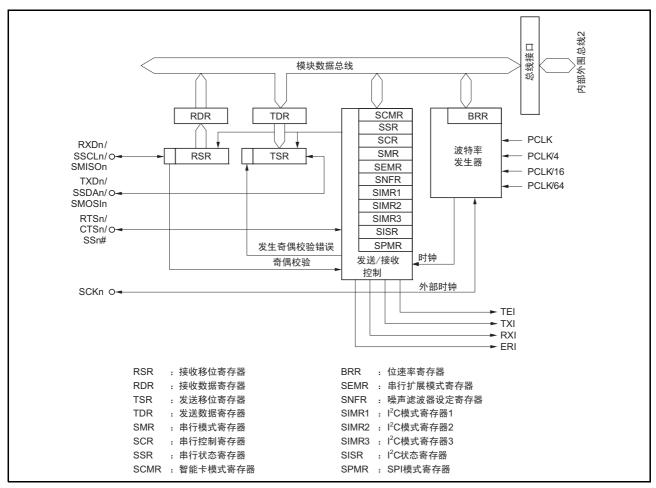

| ***              | 要                                                       |     |

| • /              | 字器说明                                                    |     |

| 27.2.1           | 接收移位寄存器(RSR)                                            |     |

| 27.2.2           | 接收数据寄存器(RDR)                                            |     |

| 27.2.3           | 发送数据寄存器 (TDR)                                           |     |

| 27.2.4           | 发送移位寄存器 (TSR)                                           |     |

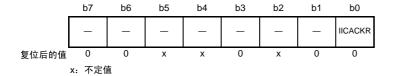

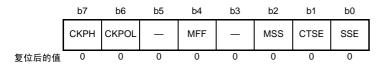

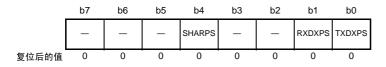

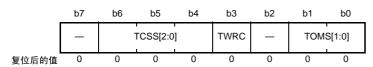

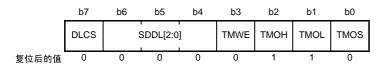

| 27.2.5           | 串行模式寄存器 (SMR)<br>串行控制寄存器 (SCR)                          |     |

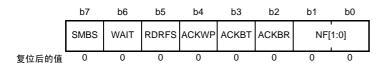

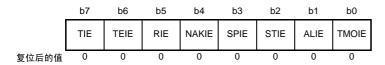

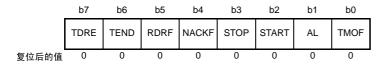

| 27.2.6<br>27.2.7 |                                                         |     |

| 27.2.7           | 串行状态寄存器 (SSR)<br>智能卡模式寄存器 (SCMR)                        |     |

| 27.2.8           | 位速率寄存器 (BRR)                                            |     |

| 27.2.9           | 电行扩展模式寄存器 (SEMR)                                        |     |

| 27.2.10          | 中110 茂侯八司任益(SEMR)                                       |     |

| 27.2.11          | <b>ド戸</b>                                               |     |

| 27.2.12          | I C 侯式司行命 I (SIWRI)<br>I <sup>2</sup> C 模式寄存器 2(SIMR2)  |     |

| 27.2.13          | I C 侯式司行命 2 (SIMR2)<br>I <sup>2</sup> C 模式寄存器 3 (SIMR3) |     |

| 27.2.14          | I <sup>2</sup> C 状态寄存器 (SISR)                           |     |

| 27.2.16          | SPI 模式寄存器 (SPMR)                                        |     |

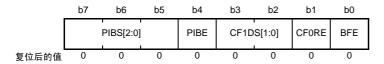

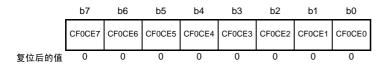

| 27.2.17          | 扩展串行模式有效寄存器(ESMER)                                      |     |

| 27.2.17          | 控制寄存器 0 (CR0)                                           |     |

| 27.2.19          | 控制寄存器 1 (CR1)                                           |     |

| 27.2.19          | 控制寄存器 2 (CR2)                                           |     |

| 27.2.21          | 控制寄存器 3 (CR3)                                           |     |

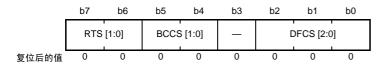

| 27.2.22          | 端口控制寄存器 (PCR)                                           |     |

| 27.2.23          | 中断控制寄存器 (ICR)                                           |     |

| 27.2.24          | 状态寄存器 (STR)                                             |     |

| 27.2.25          | 状态清除寄存器 (STCR)                                          |     |

| 27.2.26          | Control Field 0 数据寄存器 (CF0DR)                           |     |

| 27.2.27          | Control Field 0 比较允许寄存器 (CF0CR)                         |     |

| 27.2.28          | Control Field 0 接收数据寄存器 (CF0RR)                         |     |

| 27.2.29          | 主 Control Field 1 数据寄存器(PCF1DR)                         |     |

| 27.2.30          | 次 Control Field 1 数据寄存器 (SCF1DR)                        | 748 |

| 27.2.31          | Control Field 1 比较允许寄存器 (CF1CR)                         |     |

| 27.2.32          | Control Field 1 接收数据寄存器 (CF1RR)                         |     |

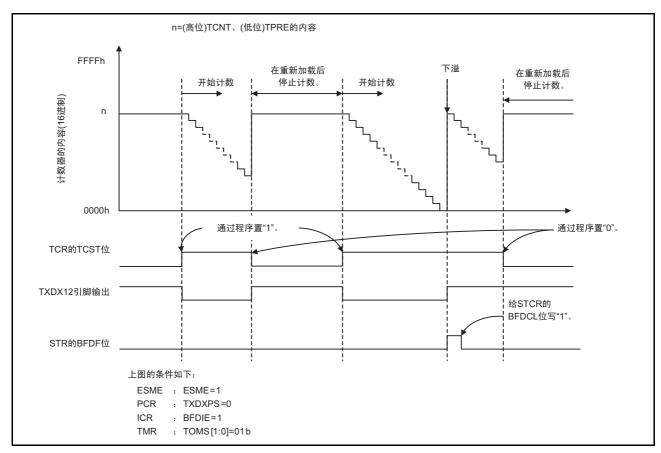

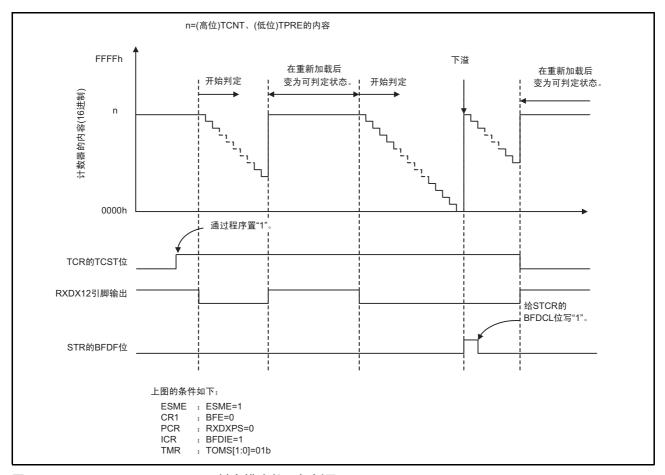

| 27.2.33          | 定时器的控制寄存器 (TCR)                                         | 749 |

| 27.2.34          | 定时器的模式寄存器 (TMR)                                         | 749 |

| 27.2.35          | 定时器的预分频寄存器 (TPRE)                                       | 750 |

| 27.2.36          | 定时器的计数器 (TCNT)                                          | 750 |

| 27.3 异力          | b模式的运行                                                  | 751 |

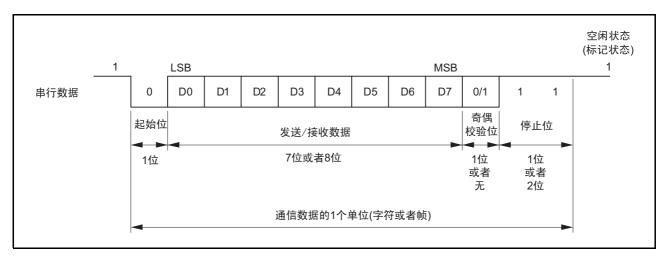

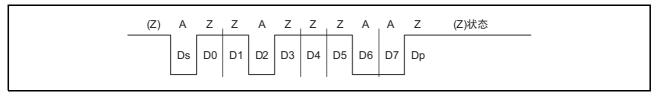

| 27.3.1           | 串行发送 / 接收格式                                             |     |

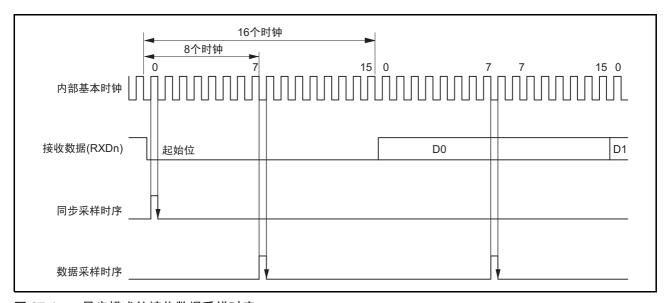

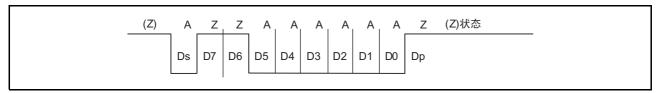

| 27.3.2           | 异步模式的接收数据采样时序和接收容限                                      |     |

| 27.3.3           | 时钟                                                      | 754 |

| 27.3.4           | CTS 和 RTS 功能                                            | 754 |

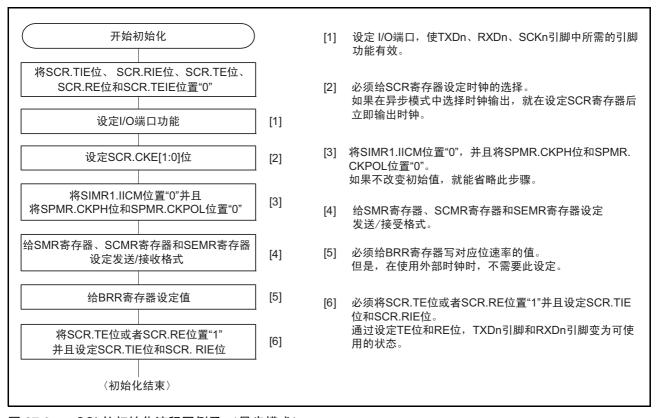

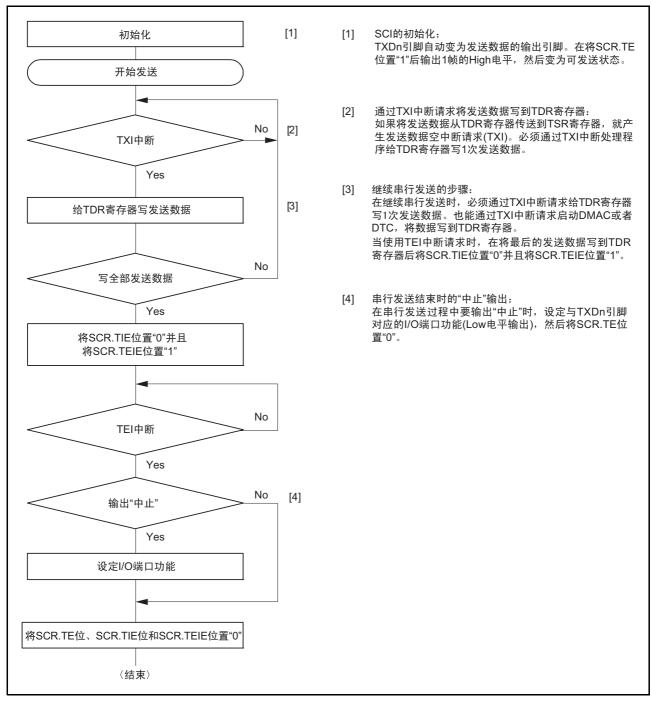

| 27.3.5           | SCI 的初始化 (异步模式)                                         | 755 |

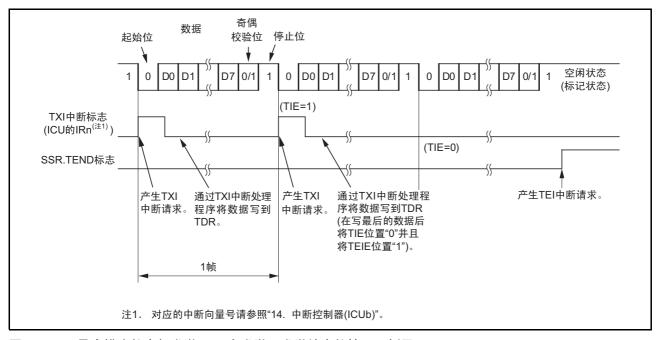

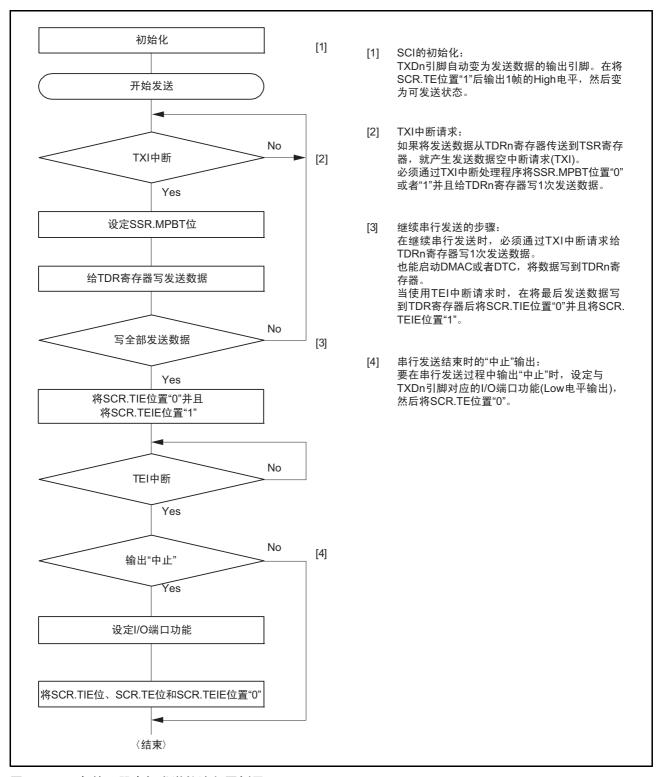

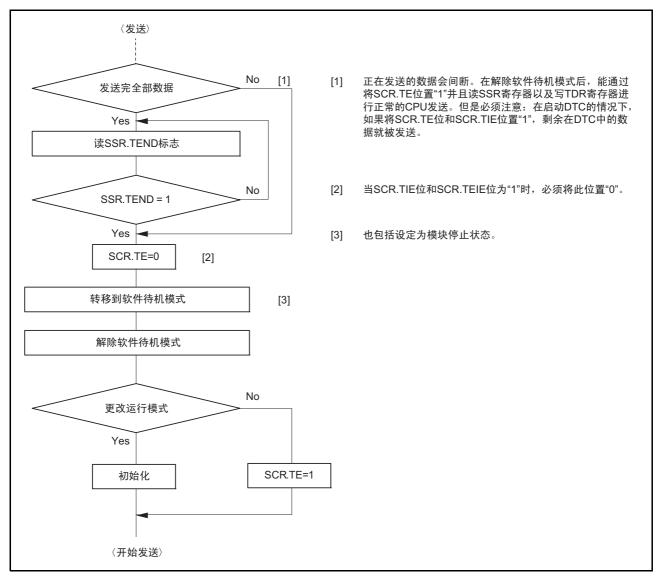

| 27.3.6           | 串行数据的发送 (异步模式)                                          | 756 |

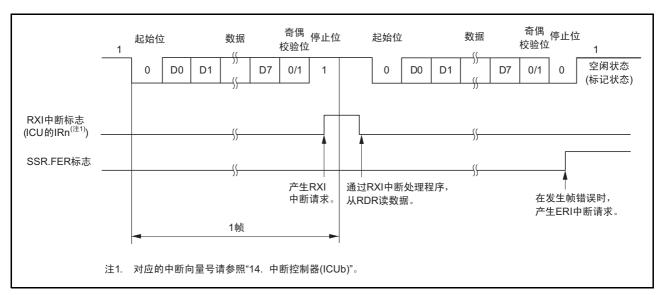

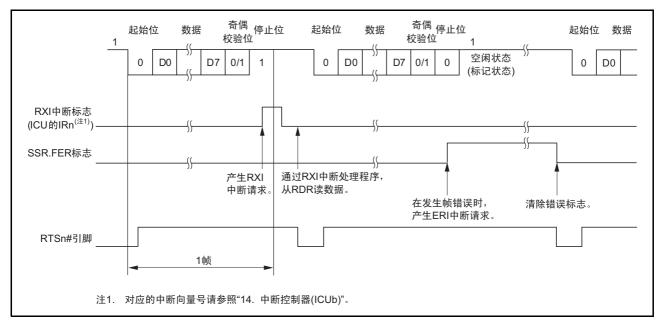

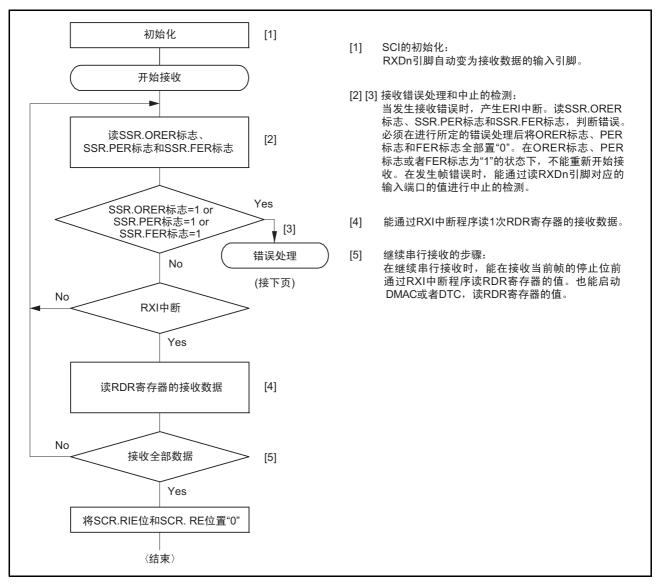

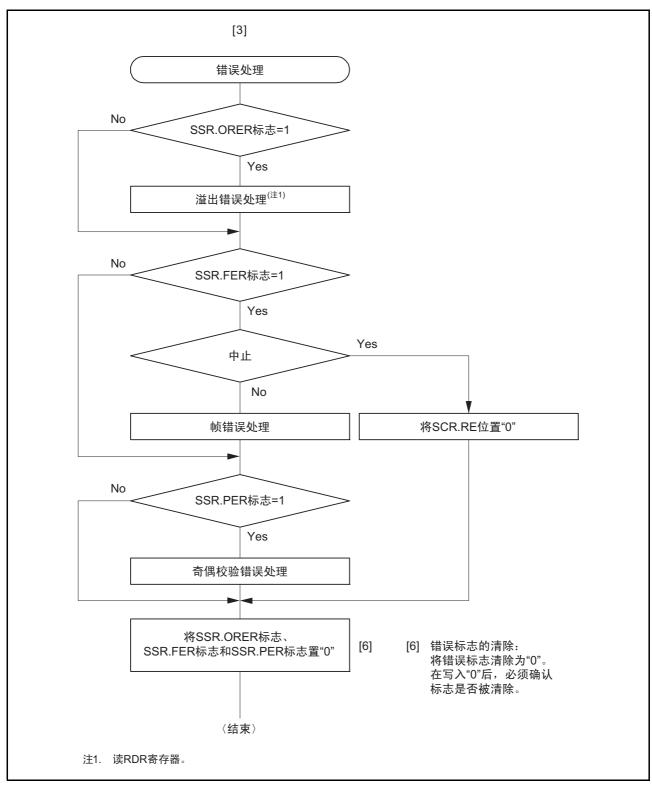

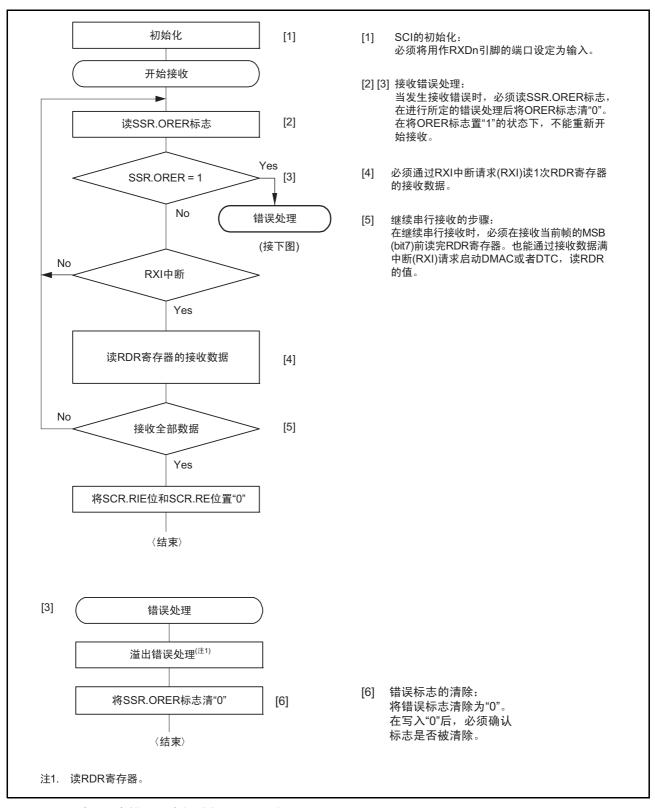

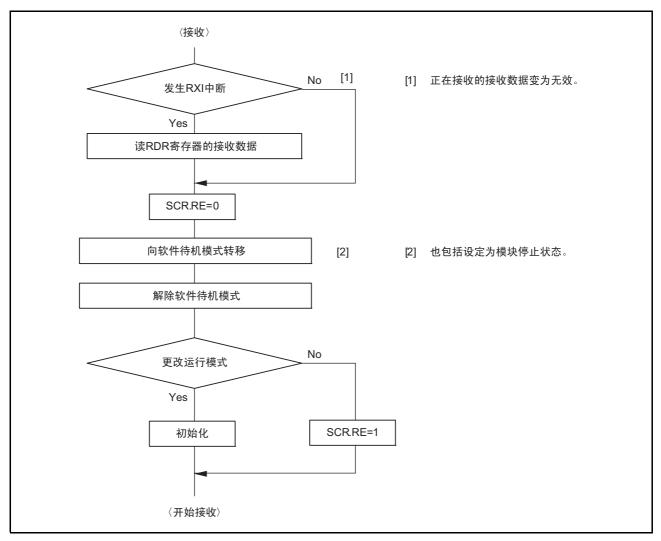

| 27.3.7  | 串行数据的接收 (异步模式)                        | 758 |

|---------|---------------------------------------|-----|

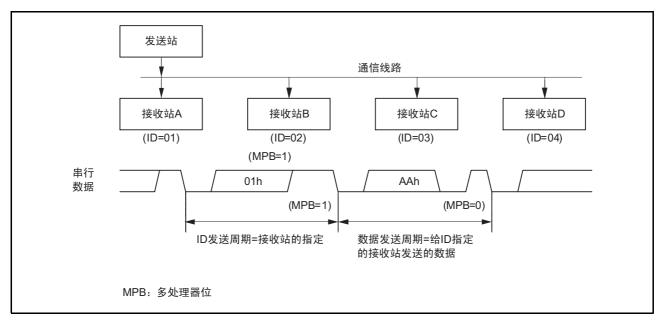

| 27.4 多久 | 处理器通信功能                               |     |

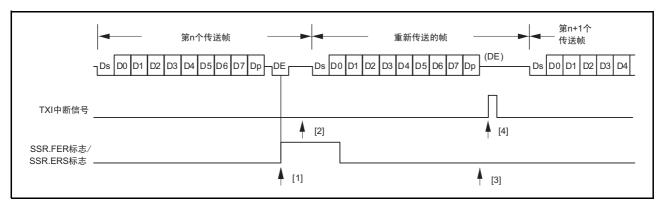

| 27.4.1  | 多处理器串行数据的发送                           | 763 |

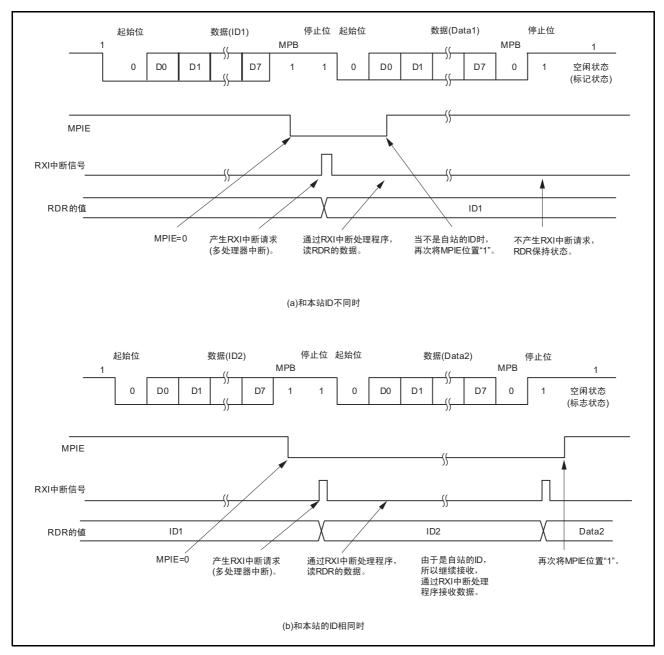

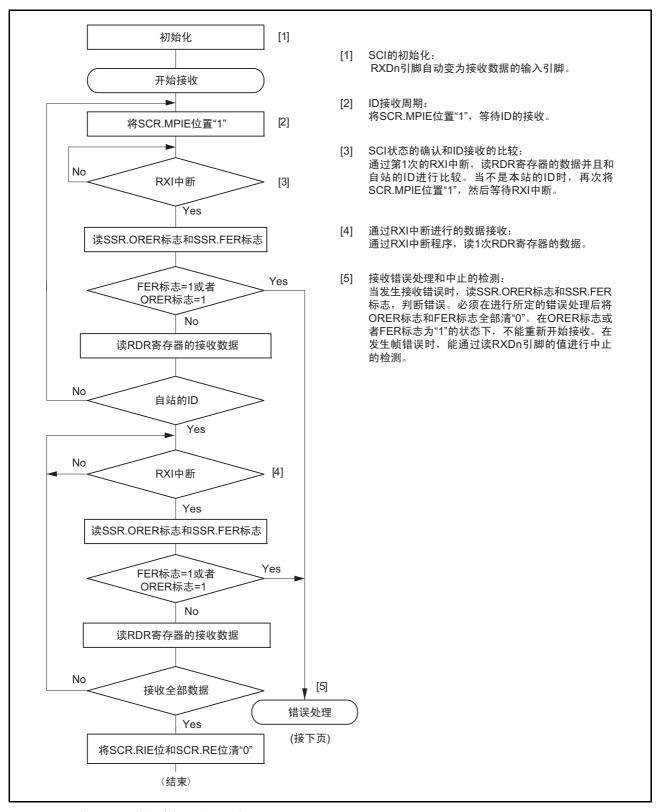

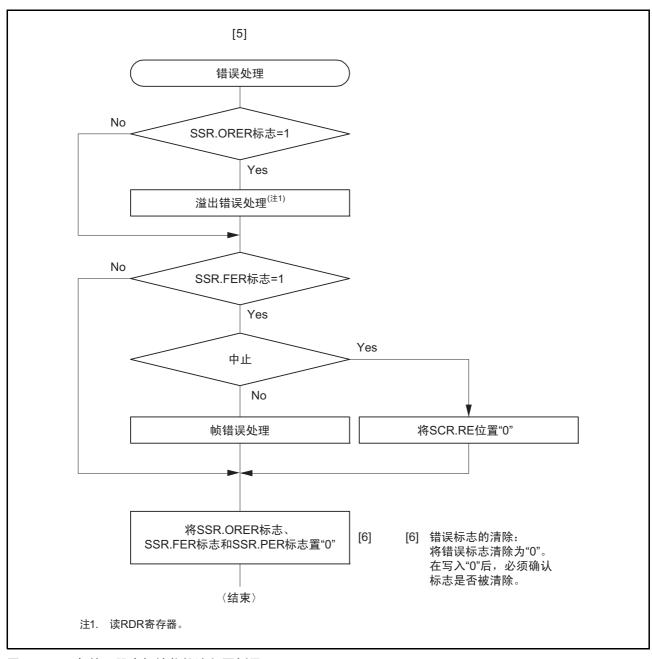

| 27.4.2  | 多处理器串行数据的接收                           | 764 |

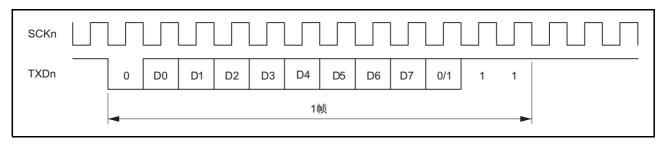

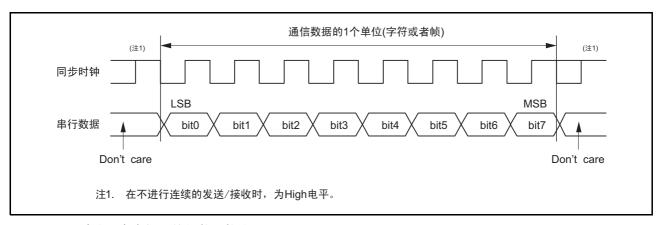

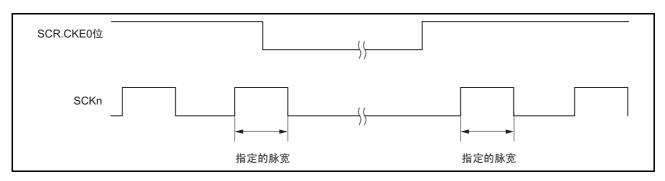

| 27.5 时轮 | 钟同步模式的运行                              | 767 |

| 27.5.1  | 时钟                                    | 767 |

| 27.5.2  | CTS 和 RTS 功能                          | 767 |

| 27.5.3  | SCI 的初始化 (时钟同步模式)                     | 768 |

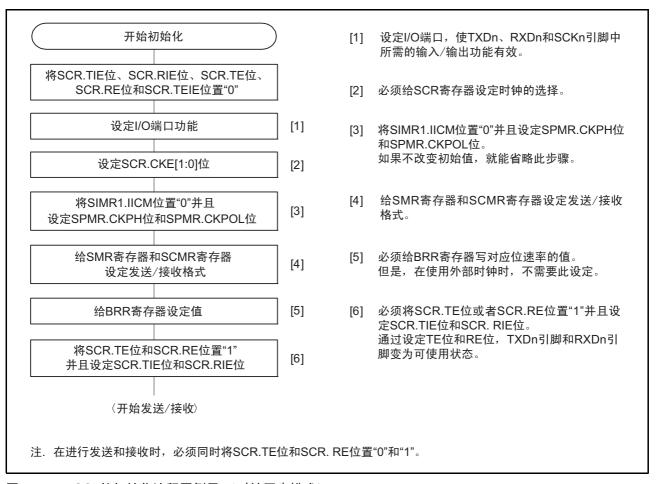

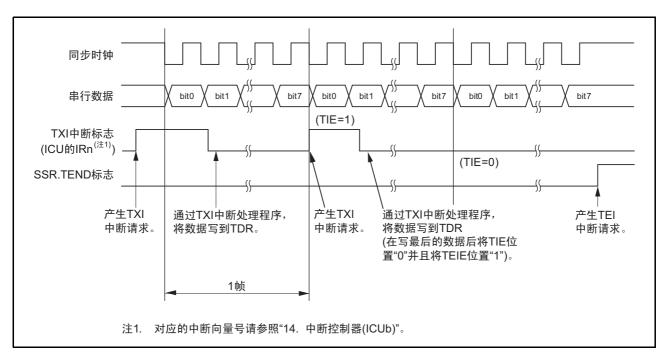

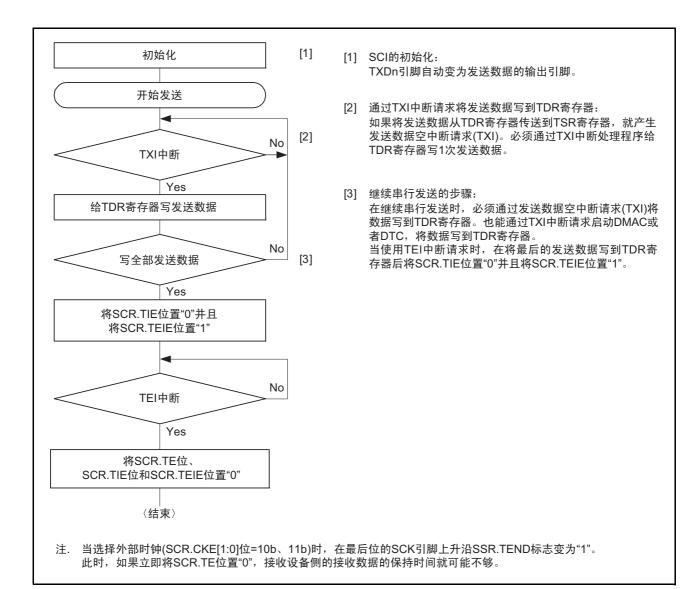

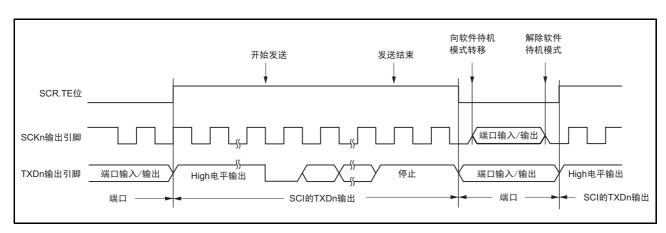

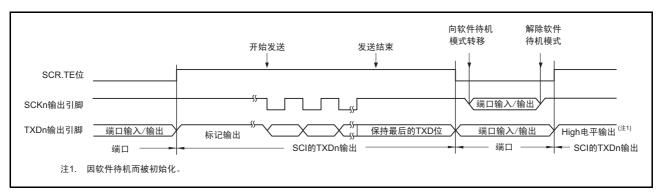

| 27.5.4  | 串行数据的发送 (时钟同步模式)                      | 769 |

| 27.5.5  | 串行数据的接收 (时钟同步模式)                      | 770 |

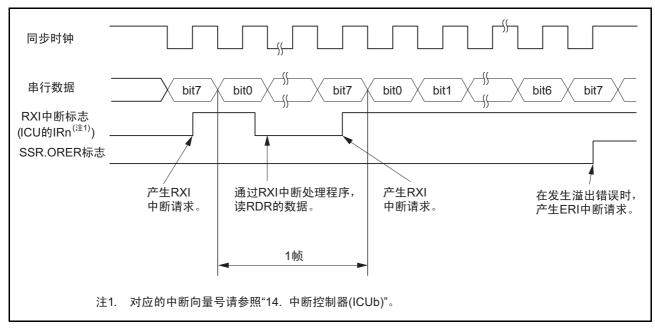

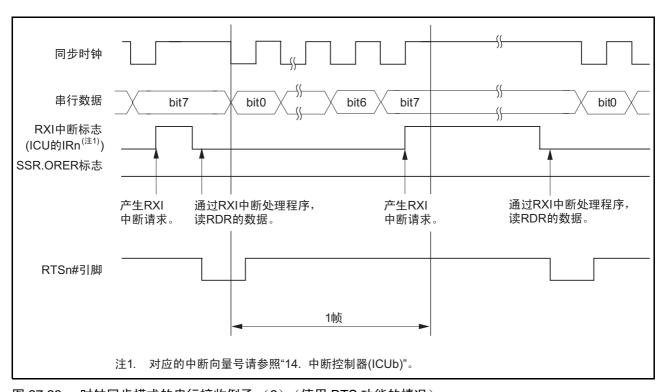

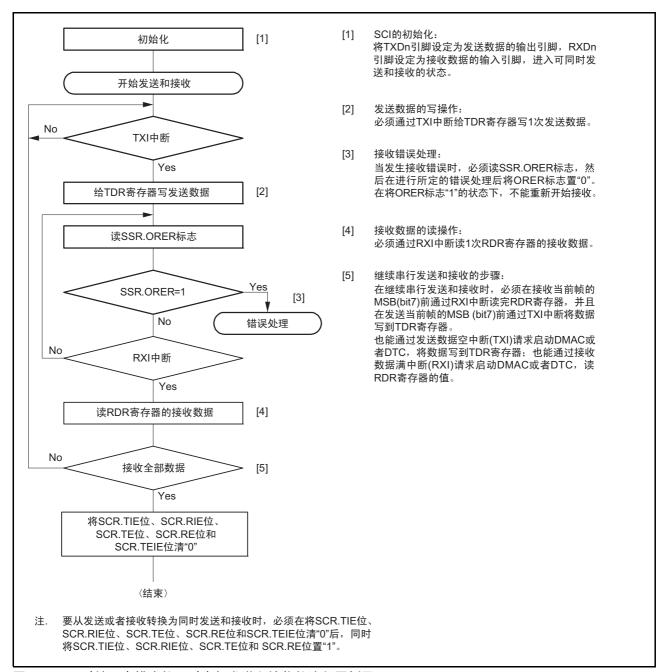

| 27.5.6  | 串行数据的同时发送和接收 (时钟同步模式)                 | 773 |

| 27.6 智能 | 能卡接口模式的运行                             | 774 |

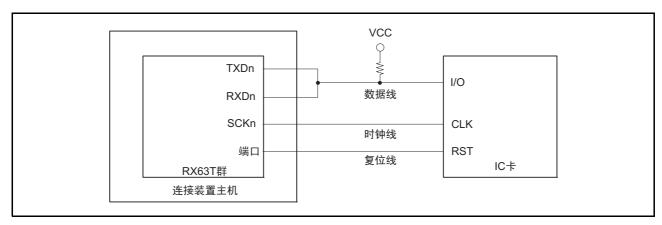

| 27.6.1  | 连接例子                                  | 774 |

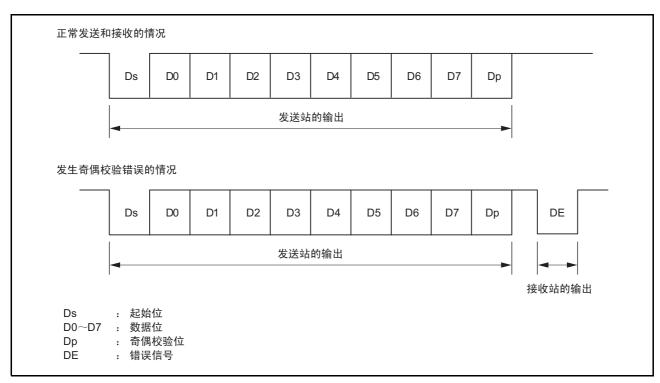

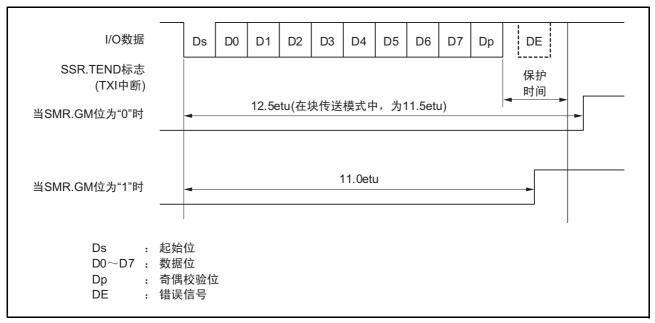

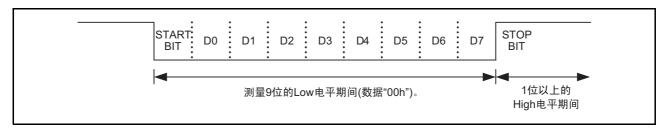

| 27.6.2  | 数据格式 (块传送模式除外)                        | 775 |

| 27.6.3  | 块传送模式                                 | 776 |

| 27.6.4  | 接收数据的采样时序和接收容限                        | 776 |

| 27.6.5  | SCI 的初始化 (智能卡接口模式)                    | 777 |

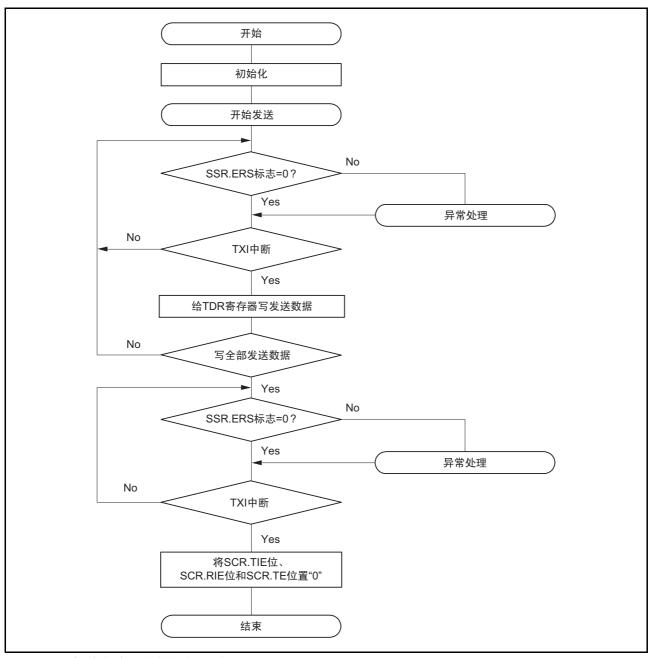

| 27.6.6  | 串行数据的发送 (块传送模式除外)                     | 778 |

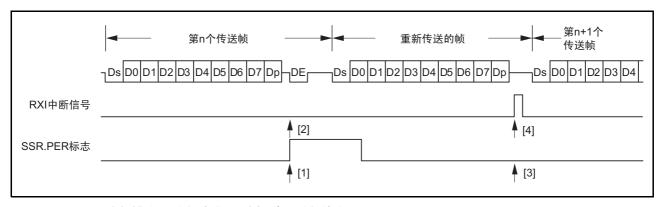

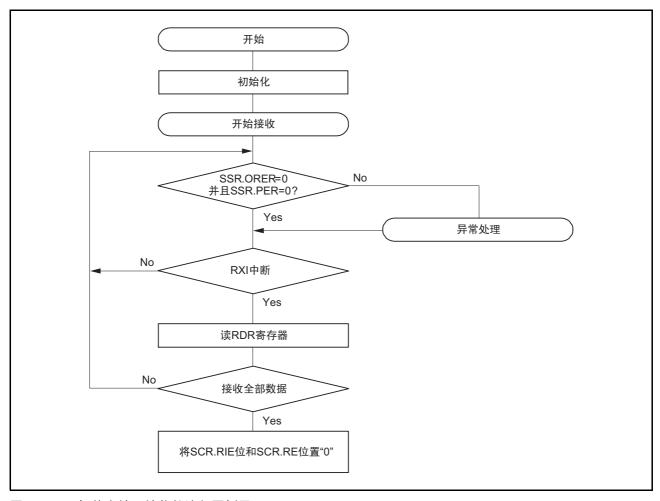

| 27.6.7  | 串行接收 (块传送模式除外)                        |     |

| 27.6.8  | 时钟的输出控制                               | 783 |

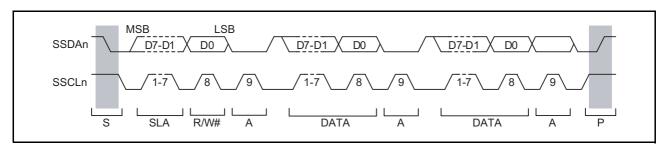

| 27.7 简复 | 易 I <sup>2</sup> C 模式的运行              |     |

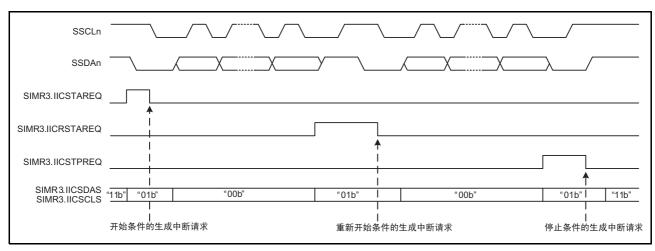

| 27.7.1  | 开始条件、重新开始条件和停止条件的生成                   | 785 |

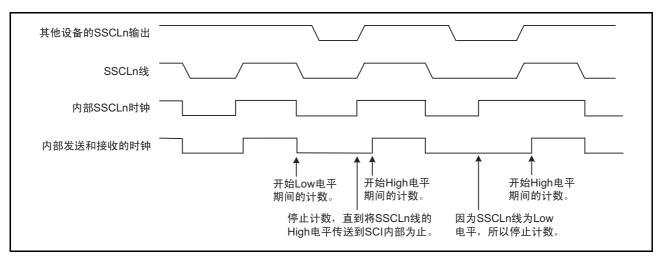

| 27.7.2  | 时钟同步                                  | 786 |

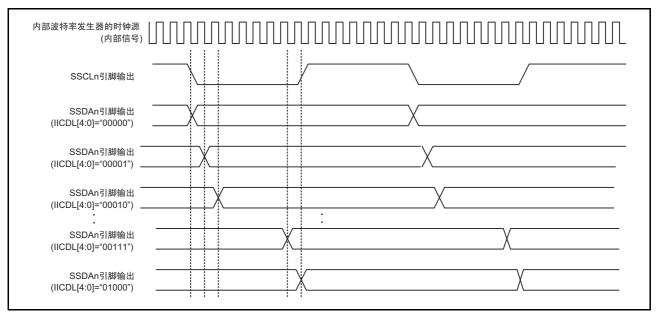

| 27.7.3  | SSDA 输出延迟                             |     |

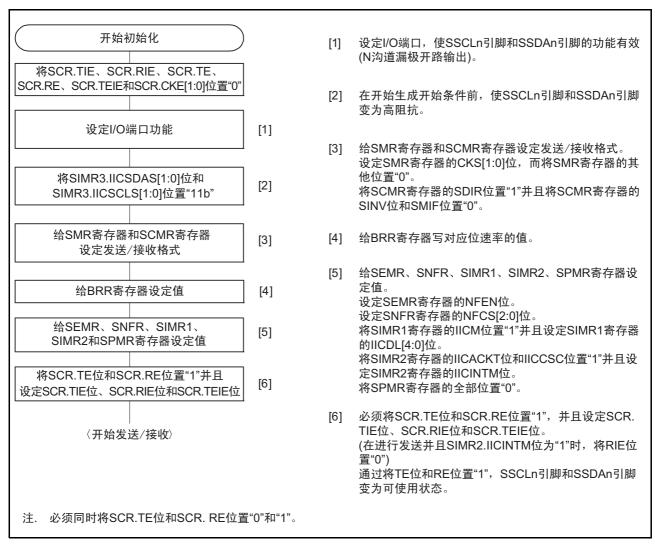

| 27.7.4  | SCI 的初始化 (简易 I <sup>2</sup> C 模式)     | 788 |

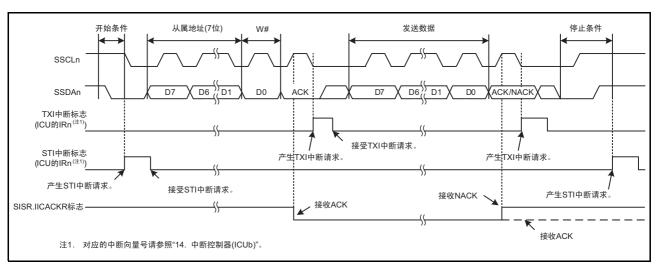

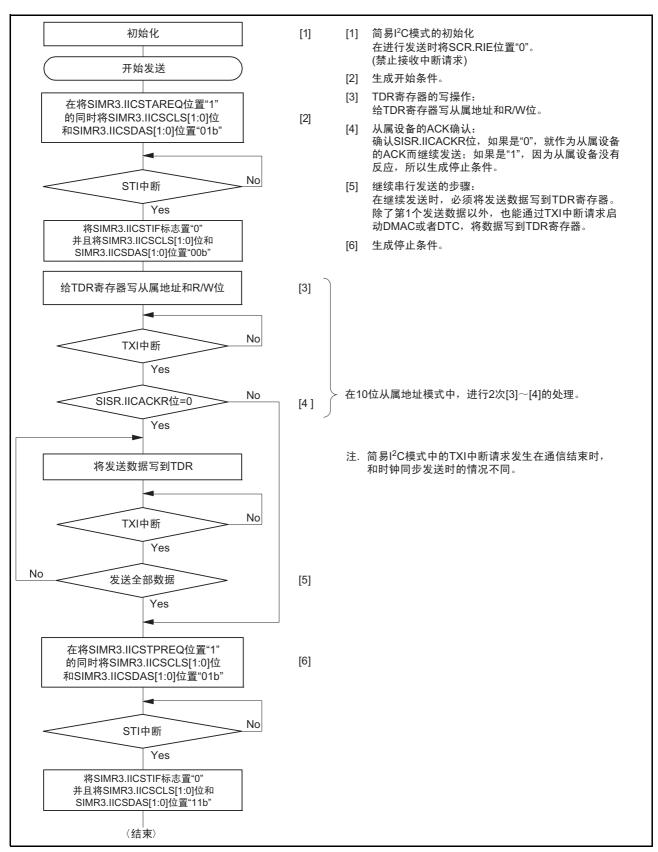

| 27.7.5  | 主控发送 (简易 I <sup>2</sup> C 模式)         |     |

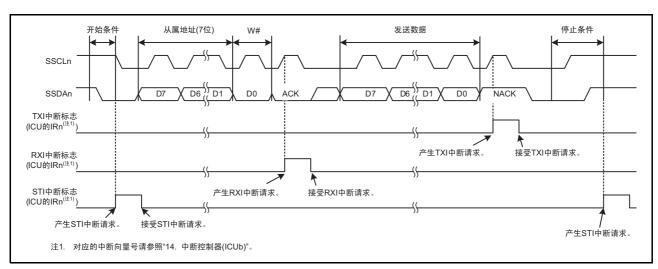

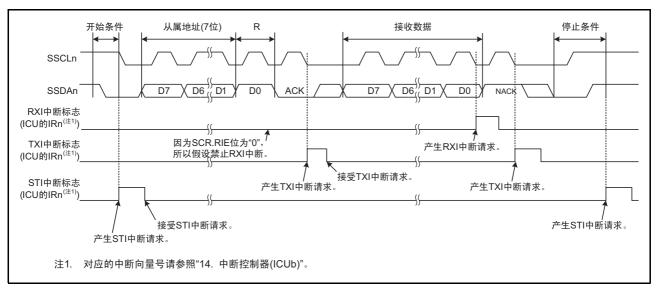

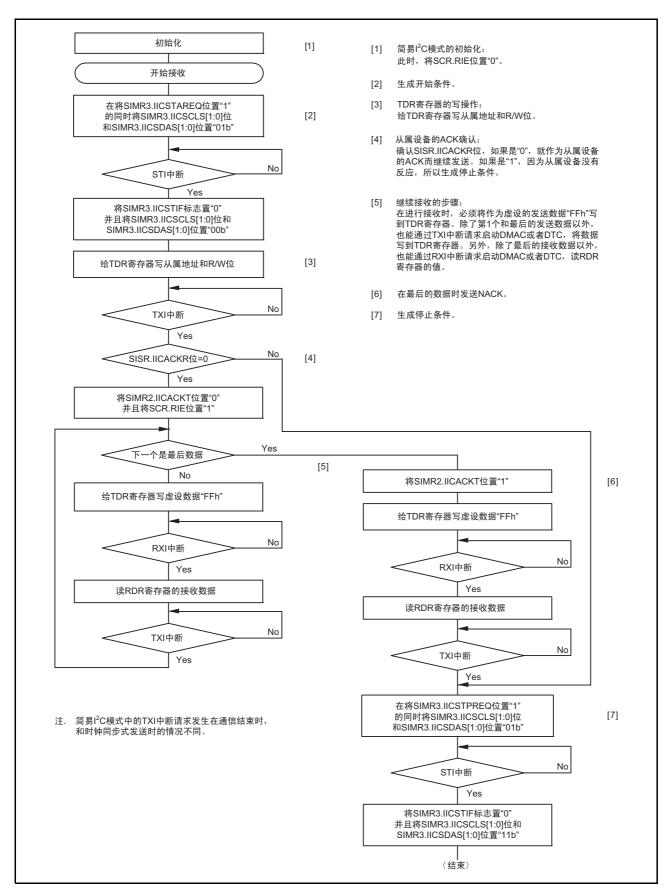

| 27.7.6  | 主控接收 (简易 I <sup>2</sup> C 模式)         | 791 |

| 27.8 简易 | 易 SPI 模式的运行                           | 793 |

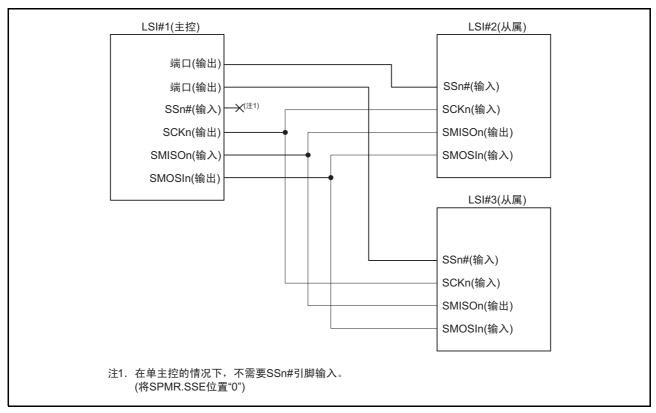

| 27.8.1  | 主控模式、从属模式和各引脚的状态                      | 794 |

| 27.8.2  | 主控模式中的 SS 功能                          |     |

| 27.8.3  | 从属模式中的 SS 功能                          | 794 |

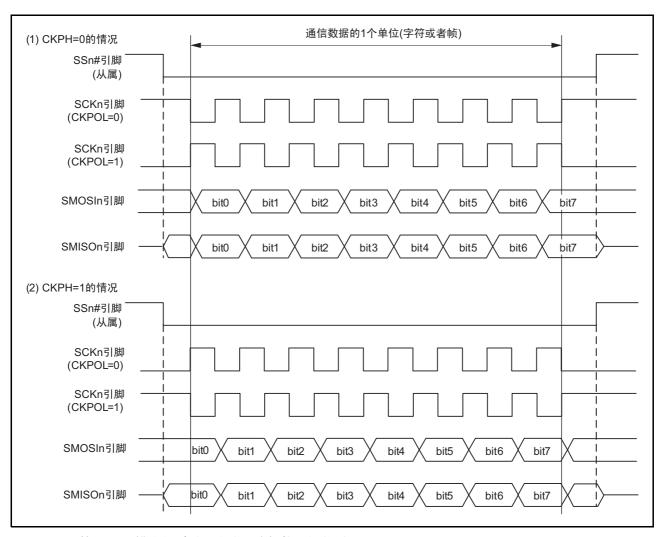

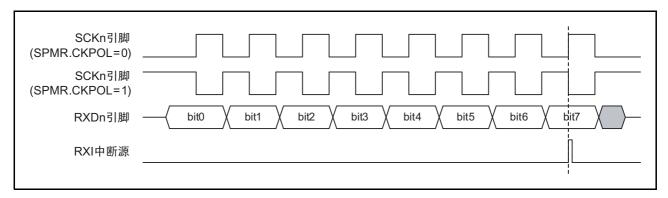

| 27.8.4  | 时钟和发送 / 接收数据的关系                       | 794 |

| 27.8.5  | SCI 的初始化 (简易 SPI 模式)                  |     |

| 27.8.6  | 串行数据的发送和接收 (简易 SPI 模式)                |     |

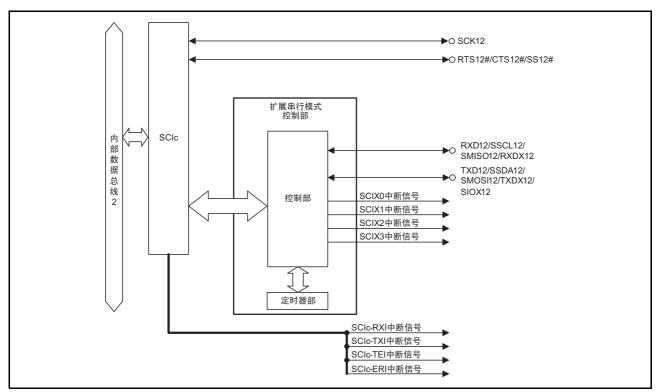

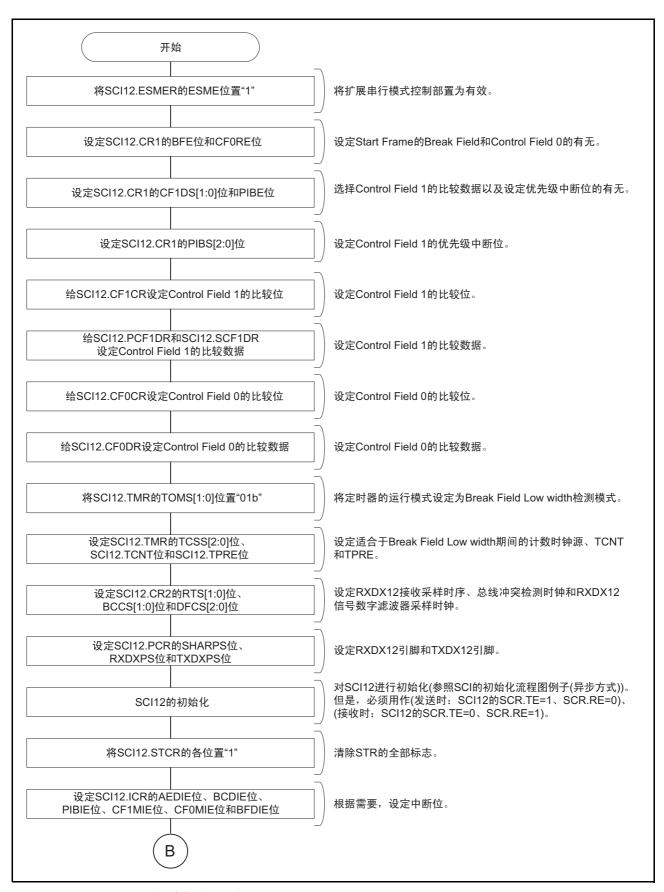

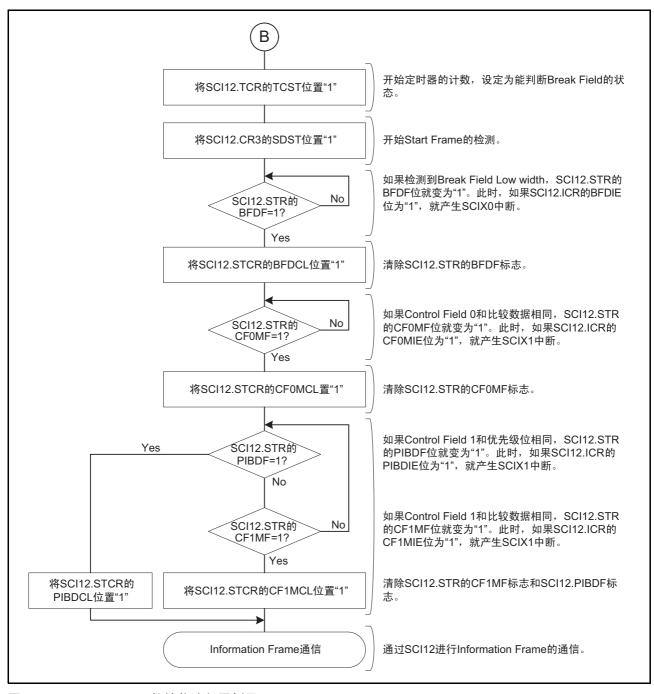

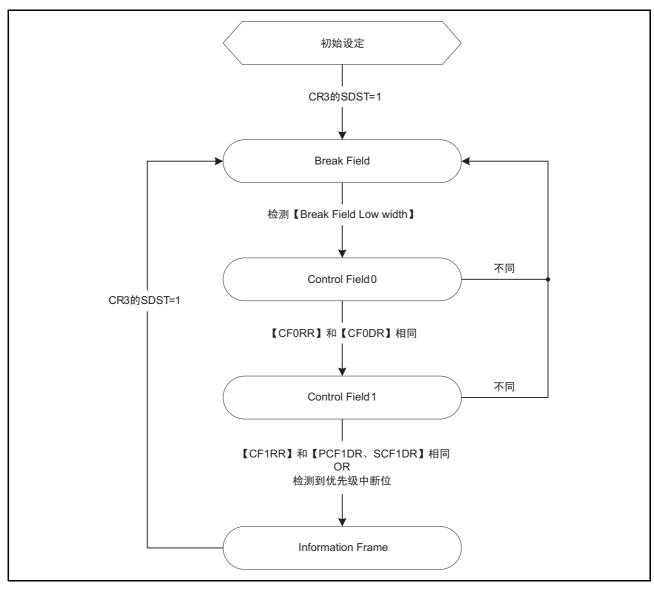

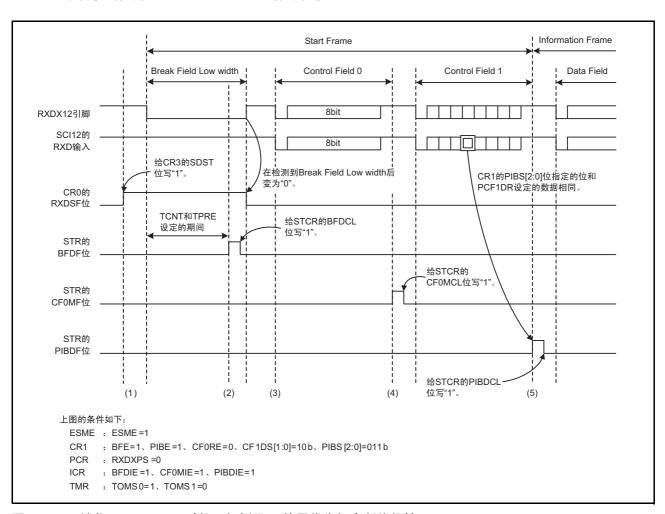

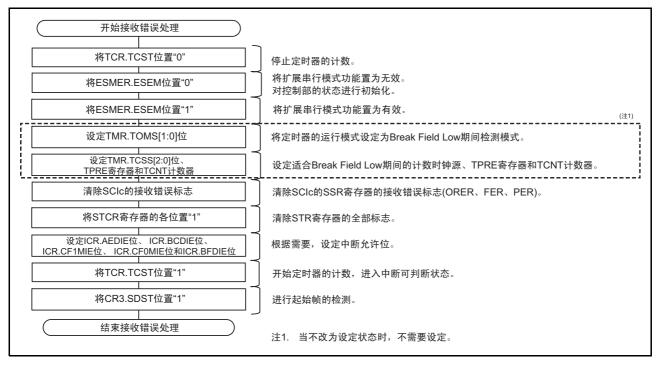

| 27.9 扩展 | 展串行模式控制部的运行说明                         | 796 |

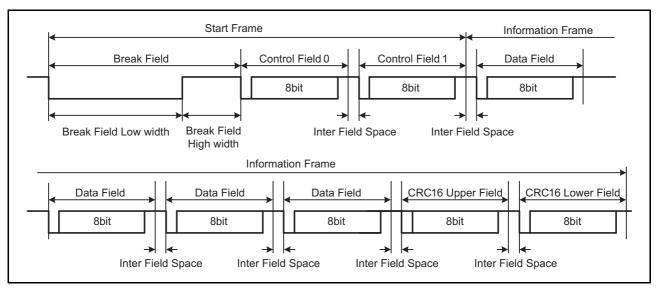

| 27.9.1  | 串行通信协议                                |     |

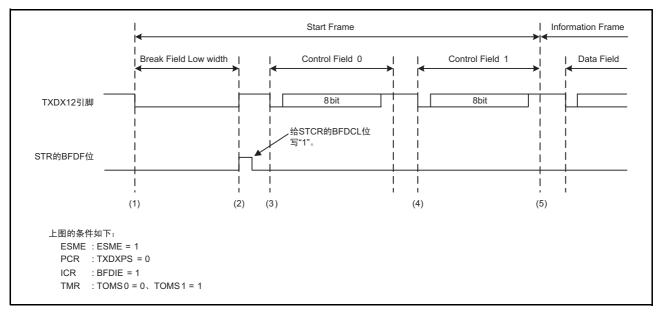

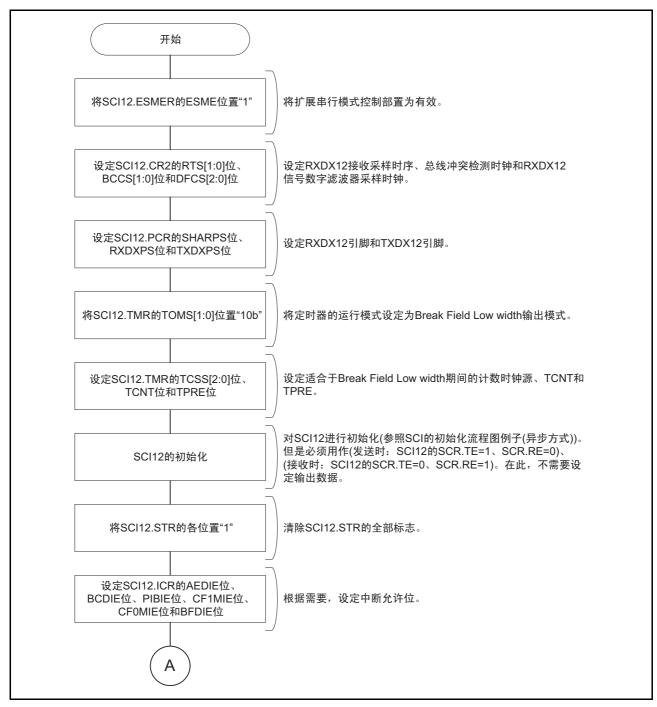

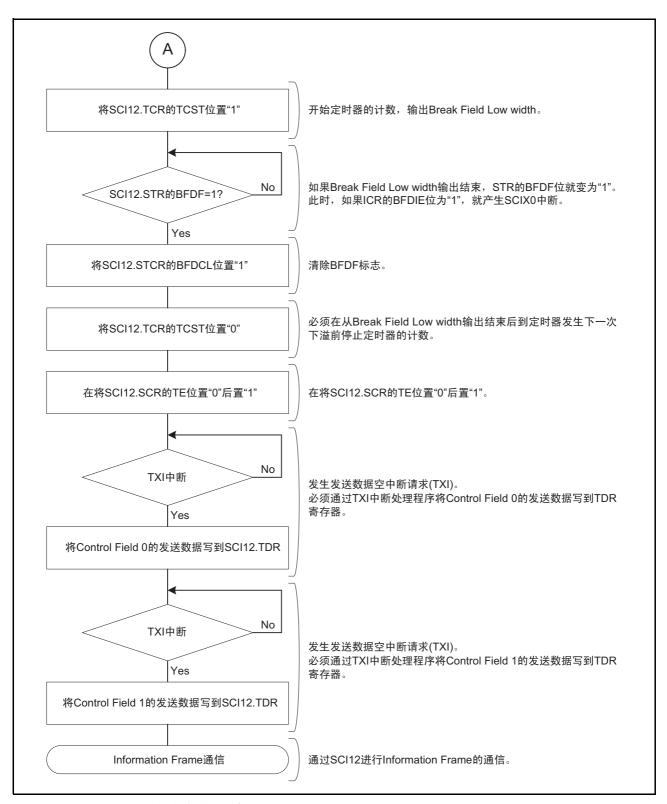

| 27.9.2  | Start Frame 发送                        |     |

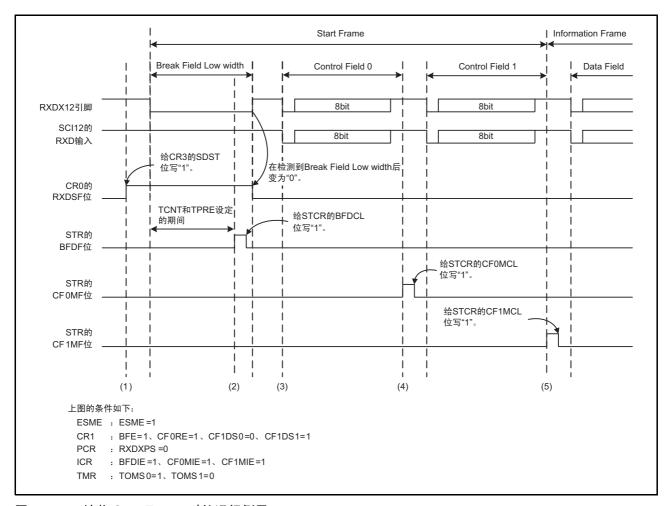

| 27.9.3  | Start Frame 接收                        |     |

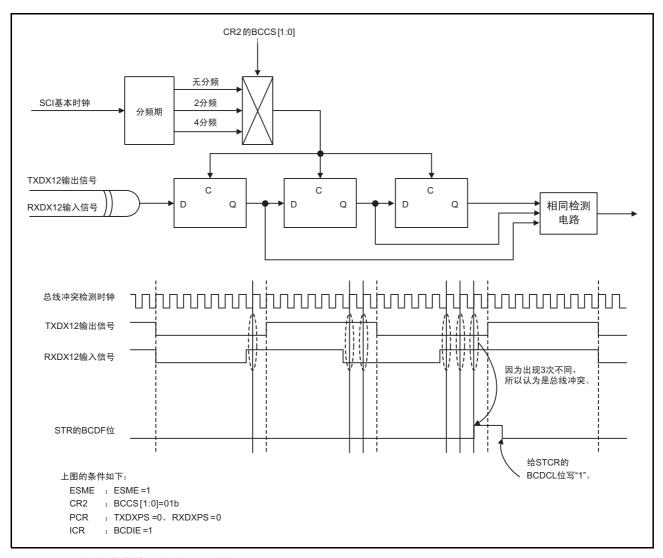

| 27.9.4  | 总线冲突检测功能                              |     |

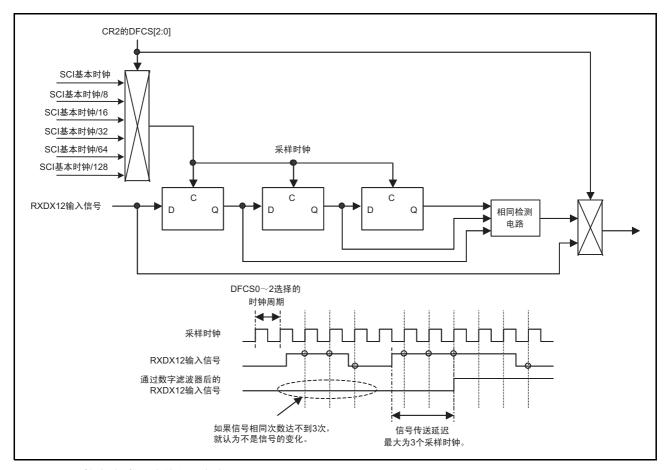

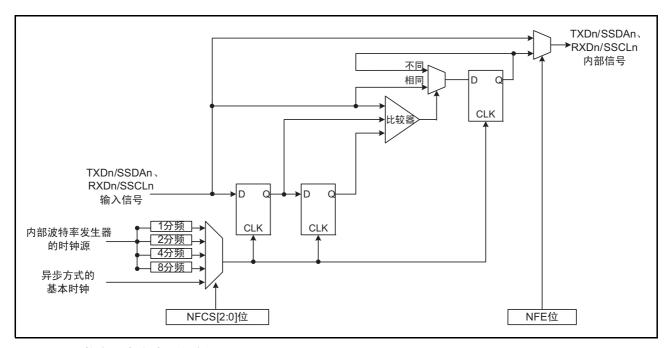

| 27.9.5  | RXDX12 引脚输入的数字滤波器功能                   |     |

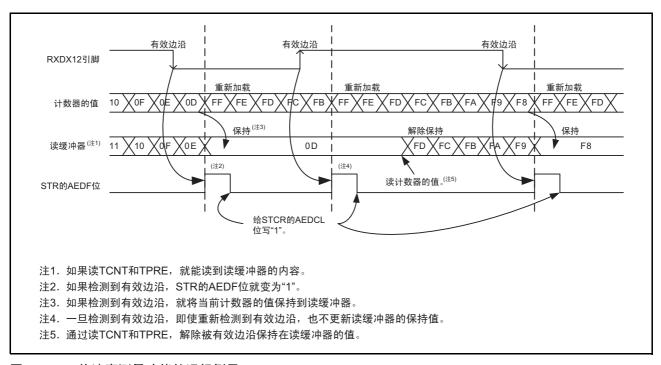

| 27.9.6  | 位速率测量功能                               |     |

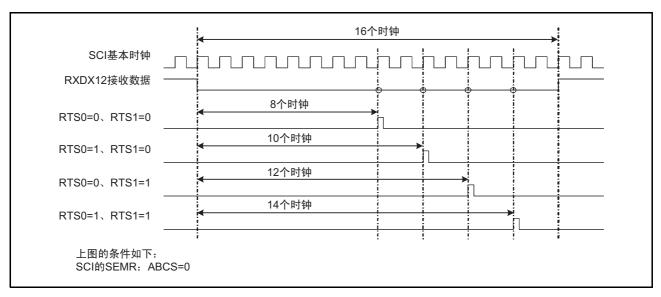

| 27.9.7  | RXDX12 接收数据的采样时序选择功能                  |     |

| 27.9.8  | 定时器                                   |     |

|         | · · · · · · · · · · · · · · · · · · · |     |

|         | 析源                                    |     |

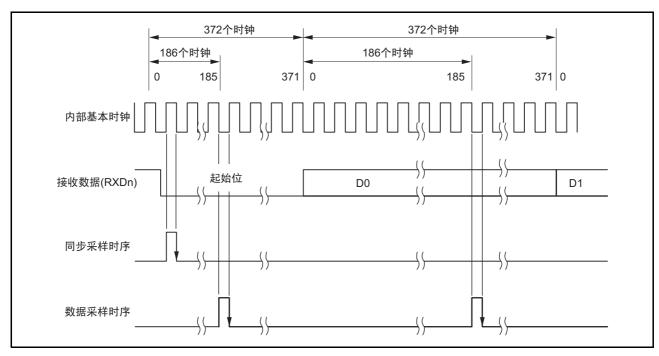

| 27.11.1 | TXI 中断和 RXI 中断的缓冲运行                   |     |

| 27.11.2 | 串行通信接口模式和简易 SPI 模式的中断                 |     |

| 27.11.3 | 智能卡接口模式的中断                            |     |

| 27.11.4 | 简易 I <sup>2</sup> C 模式的中断             |     |

| 27.11.5 | 扩展串行模式控制部的中断请求                        |     |

|         | 用时的注意事项                               |     |

| 27.12.1 | 模块停止功能的设定                             |     |

| _,,,,1  | Des 214 34 HOUA 2000                  |     |

| 27.12.2                | 有关中止的检测和处理                           |     |

|------------------------|--------------------------------------|-----|

| 27.12.3                | 标记状态和中止的发送                           | 816 |

| 27.12.4                | 有关接收错误标志和发送 (只限于时钟同步模式)              |     |

| 27.12.5                | 有关 TDR 寄存器的写操作                       | 816 |

| 27.12.6                | 时钟同步发送时的限制事项                         |     |

| 27.12.7                | 使用 DMAC 或者 DTC 时的限制事项                | 816 |

| 27.12.8                | 有关开始通信的注意事项                          | 817 |

| 27.12.9                | 有关低功耗状态时的运行                          | 817 |

| 27.12.10               | 时钟同步模式的外部时钟输入                        | 819 |

| 27.12.11               | 简易 SPI 模式的限制事项                       | 820 |

| 27.12.12               | 扩展串行模式控制部的使用限制事项 1                   | 820 |

| 27.12.13               | 扩展串行模式控制部的使用限制事项 2                   | 821 |

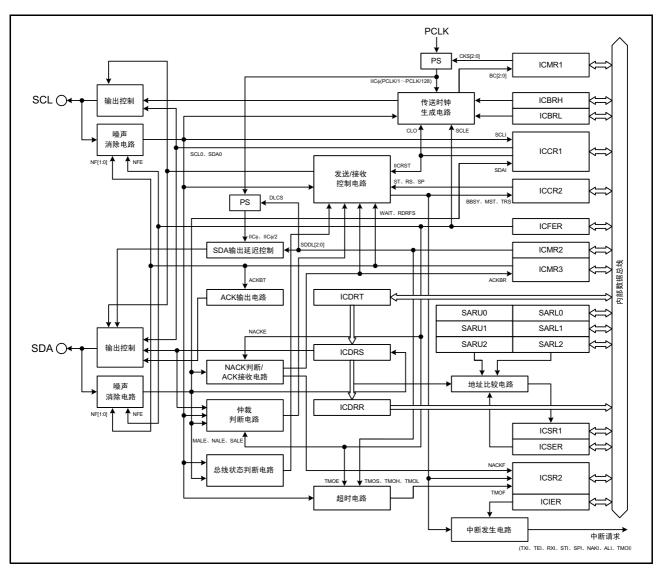

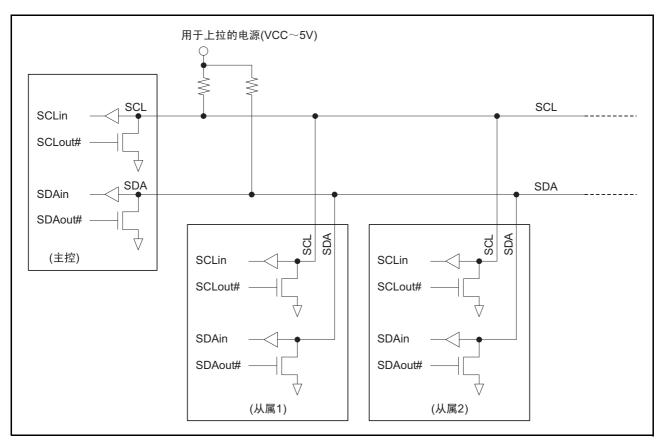

| 28. I <sup>2</sup> C 总 | 线接口 (RIIC)                           | 822 |

| 28.1 概要                | ī<br>5                               | 822 |

| 28.2 寄存                | 序器说明                                 | 825 |

| 28.2.1                 | I <sup>2</sup> C 总线控制寄存器 1 (ICCR1)   | 825 |

| 28.2.2                 | I <sup>2</sup> C 总线控制寄存器 2 (ICCR2)   | 827 |

| 28.2.3                 | I <sup>2</sup> C 总线模式寄存器 1 (ICMR1)   | 830 |

| 28.2.4                 | I <sup>2</sup> C 总线模式寄存器 2 (ICMR2)   |     |

| 28.2.5                 | I <sup>2</sup> C 总线模式寄存器 3 (ICMR3)   | 833 |

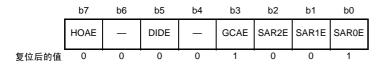

| 28.2.6                 | I <sup>2</sup> C 总线功能允许寄存器 (ICFER)   | 835 |

| 28.2.7                 | I <sup>2</sup> C 总线状态允许寄存器 (ICSER)   |     |

| 28.2.8                 | I <sup>2</sup> C 总线中断允许寄存器 (ICIER)   | 838 |

| 28.2.9                 | I <sup>2</sup> C 总线状态寄存器 1 (ICSR1)   | 840 |

| 28.2.10                | I <sup>2</sup> C 总线状态寄存器 2 (ICSR2)   |     |

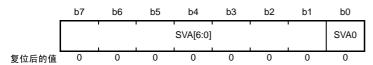

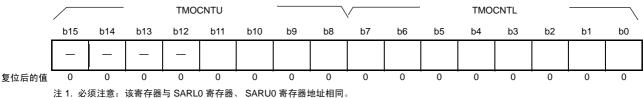

| 28.2.11                | 从属地址寄存器 Ly (SARLy)(y=0 ~ 2)          | 846 |

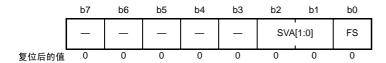

| 28.2.12                | 从属地址寄存器 Uy (SARUy)(y=0 ~ 2)          | 847 |

| 28.2.13                | I <sup>2</sup> C 总线位速率低电平寄存器 (ICBRL) |     |

| 28.2.14                | I <sup>2</sup> C 总线位速率高电平寄存器 (ICBRH) | 848 |

| 28.2.15                | I <sup>2</sup> C 总线发送数据寄存器 (ICDRT)   | 850 |

| 28.2.16                | I <sup>2</sup> C 总线接收数据寄存器 (ICDRR)   | 850 |

| 28.2.17                | I <sup>2</sup> C 总线移位寄存器 (ICDRS)     | 850 |

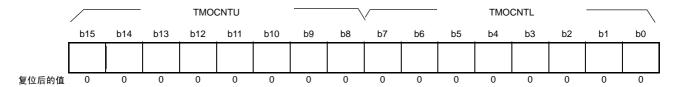

| 28.2.18                | 超时内部计数器 (TMOCNT)                     | 851 |

| 28.3 运行                | F说明                                  | 852 |

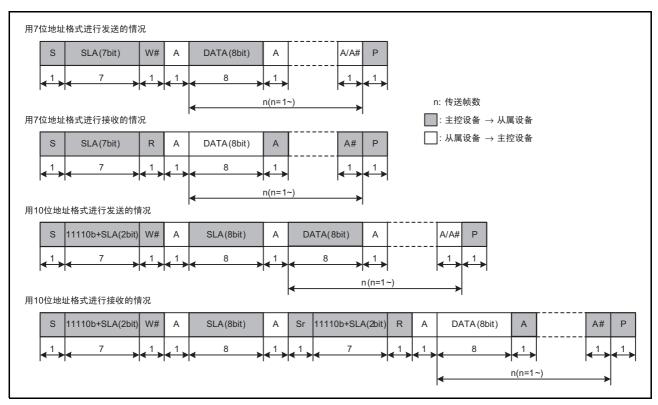

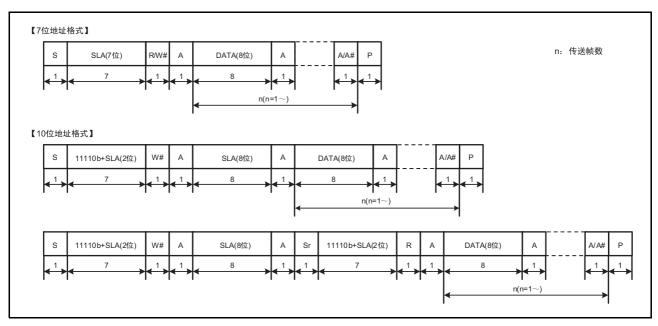

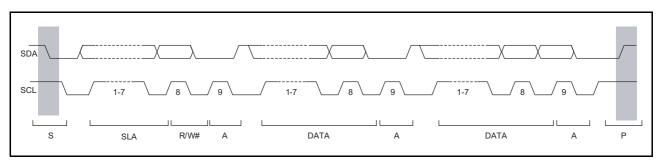

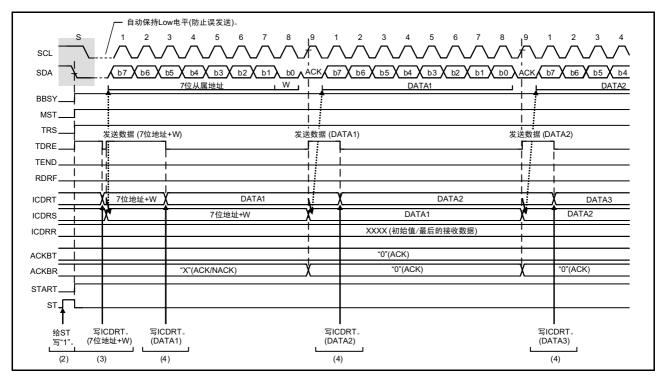

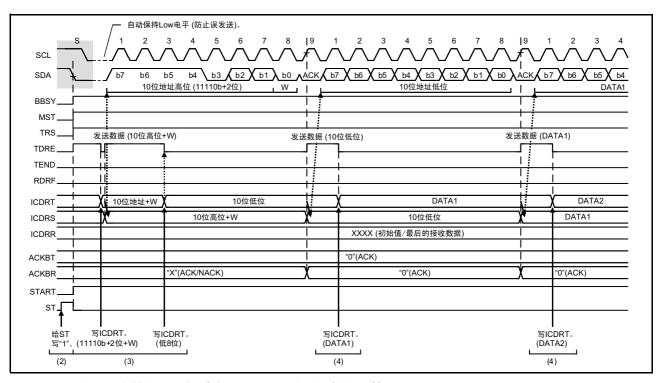

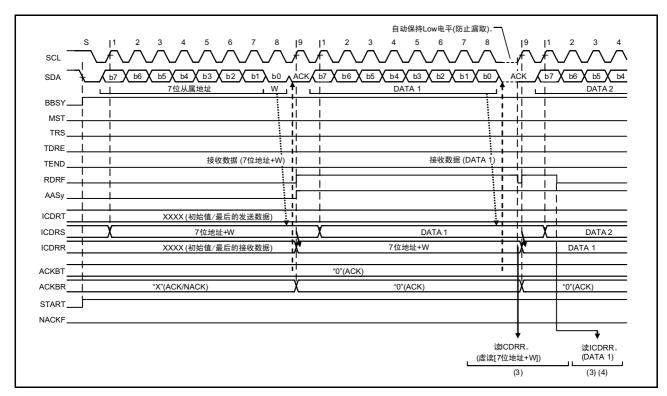

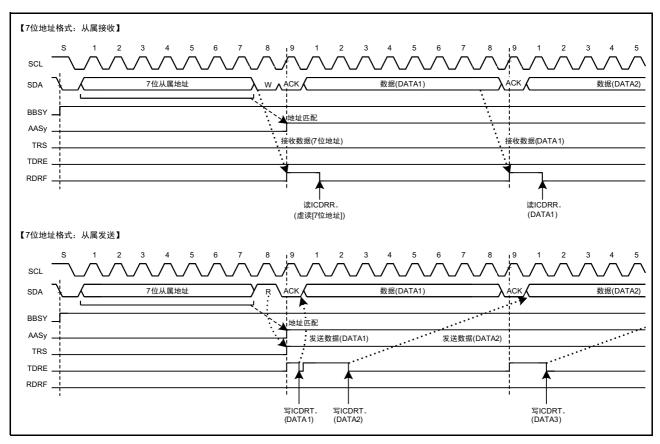

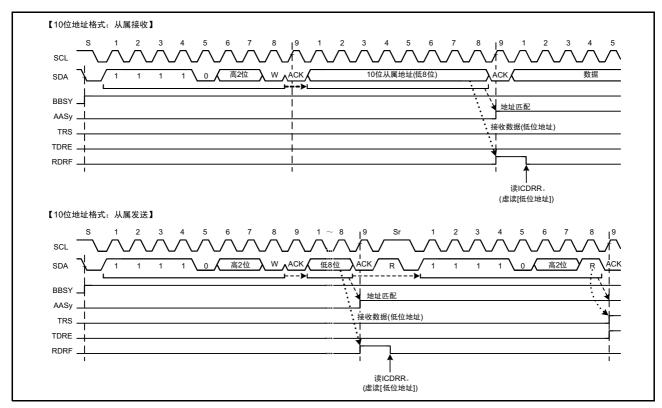

| 28.3.1                 | 通信数据的格式                              | 852 |

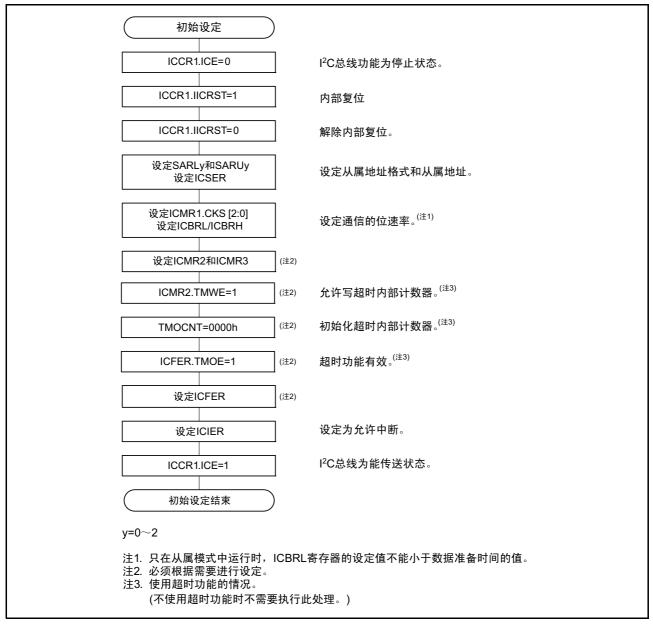

| 28.3.2                 | 初始设定                                 | 853 |

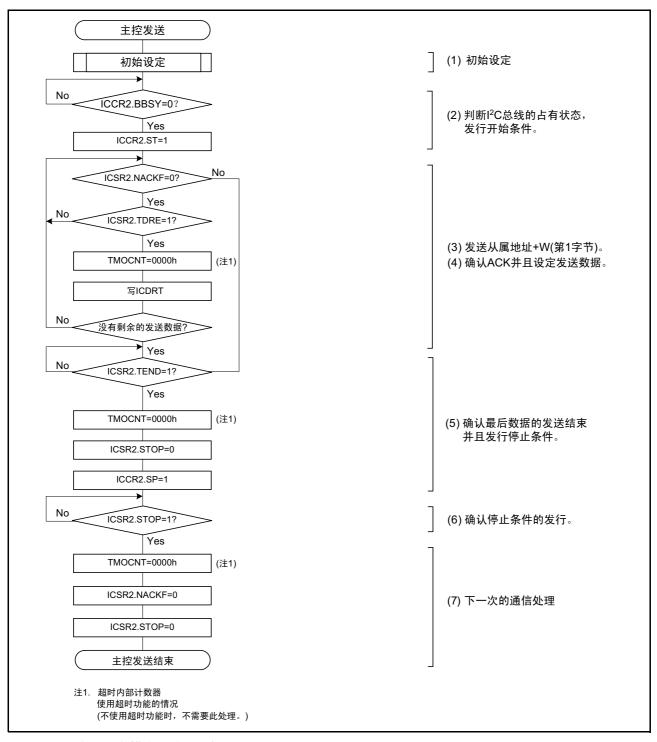

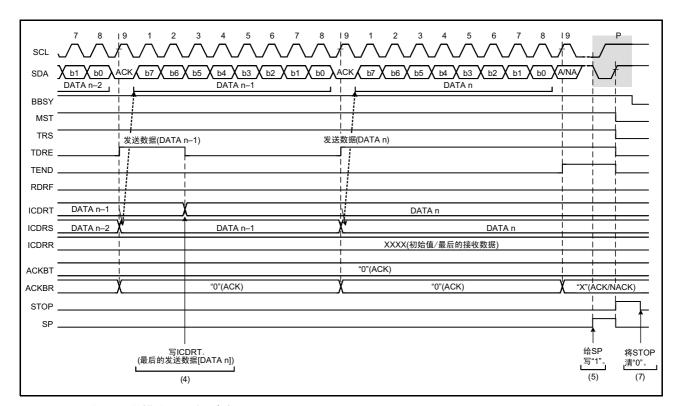

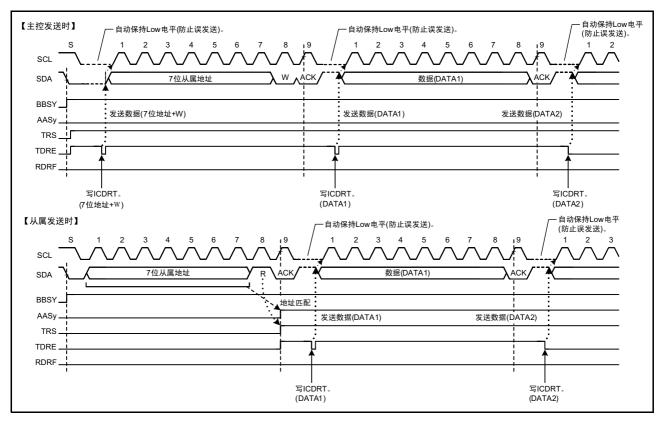

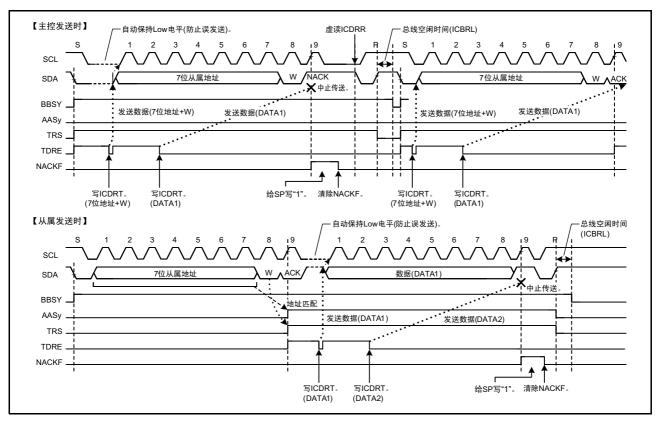

| 28.3.3                 | 主控发送                                 | 854 |

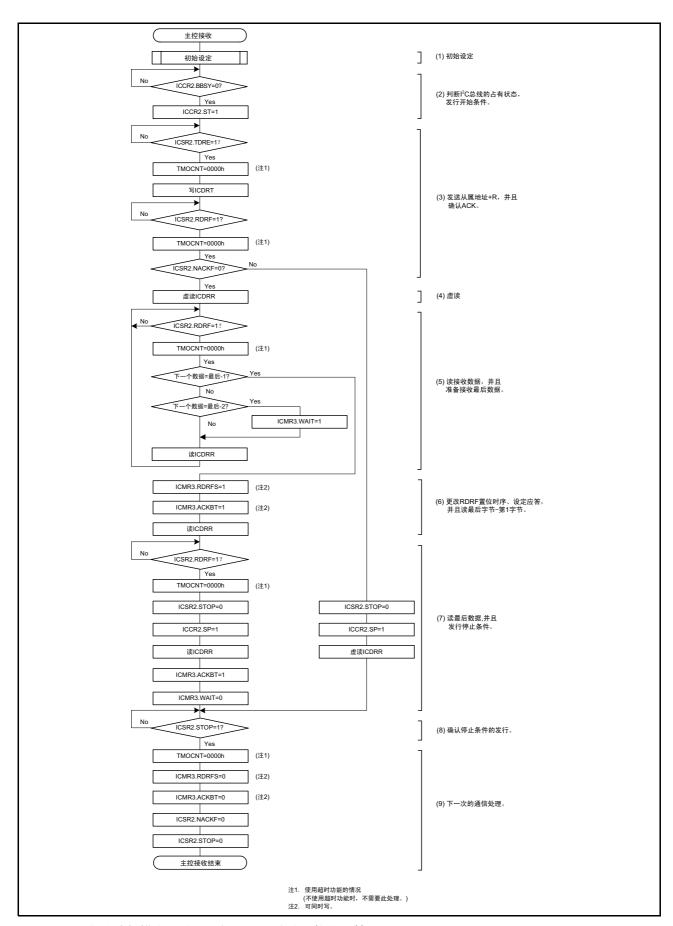

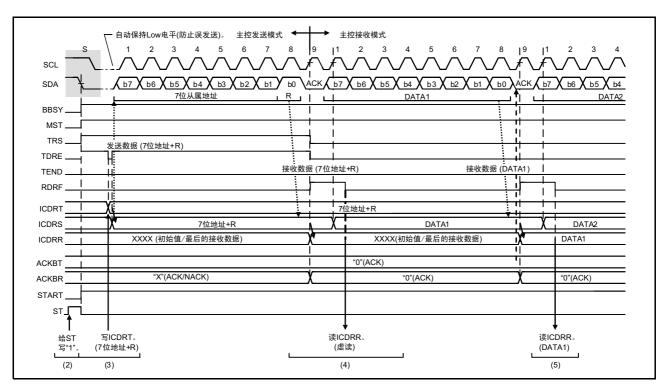

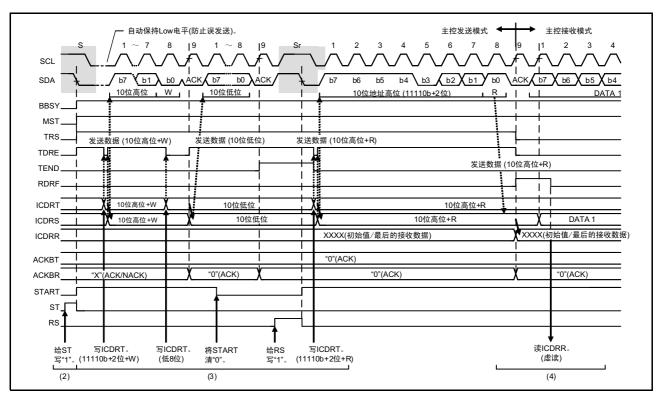

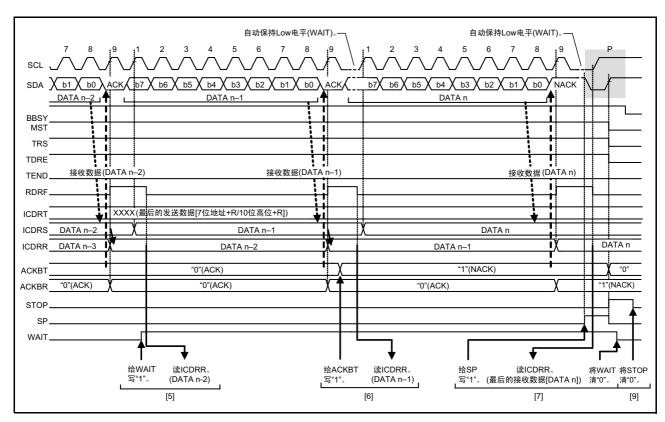

| 28.3.4                 | 主控接收                                 | 858 |

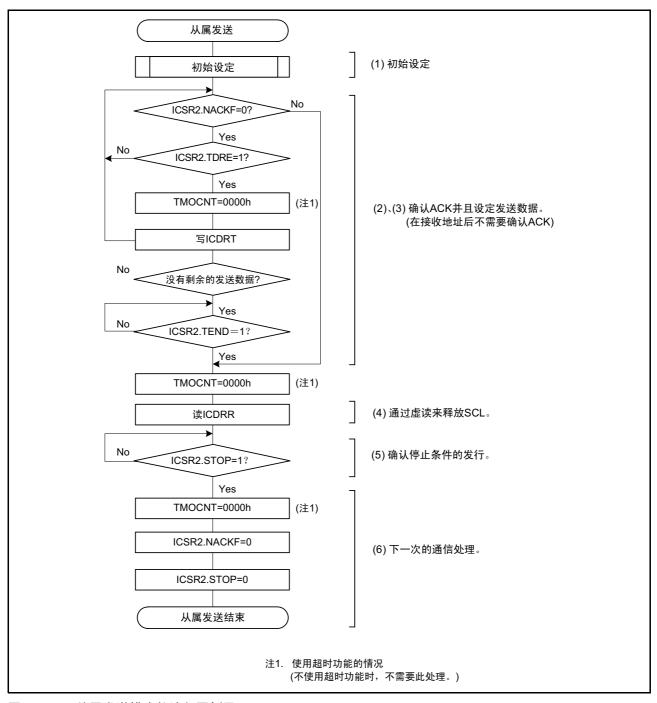

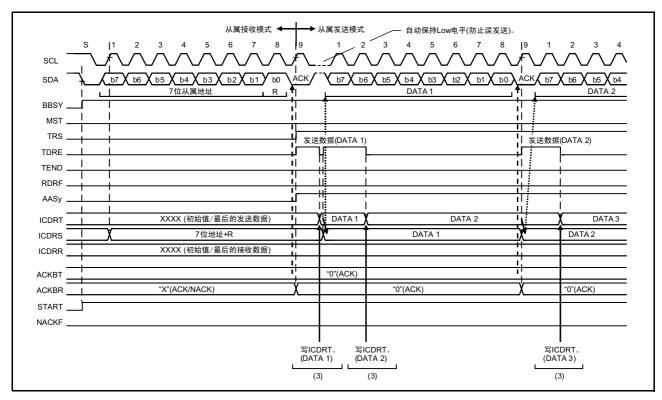

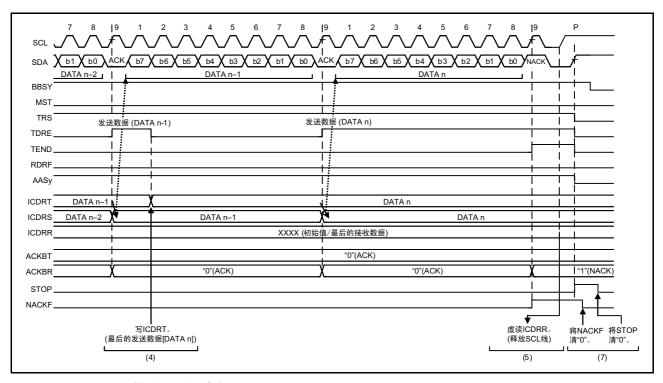

| 28.3.5                 | 从属发送                                 | 861 |

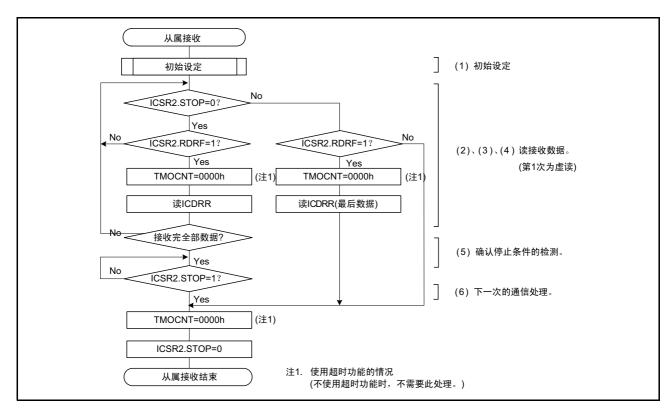

| 28.3.6                 | 从属接收                                 | 864 |

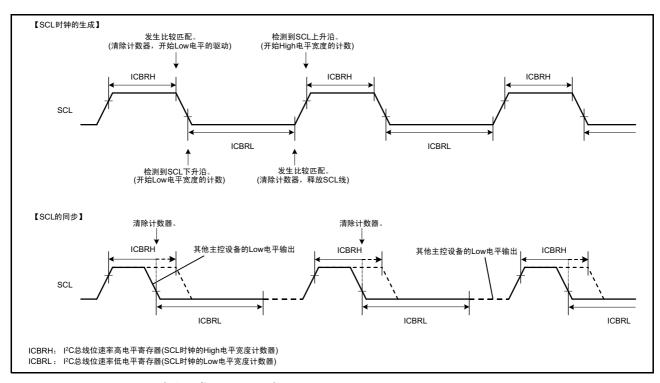

| 28.4 SCL               | . 同步电路                               | 866 |

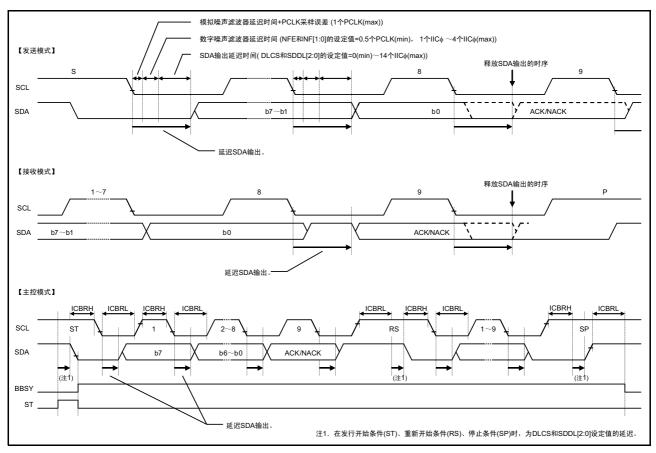

| 28.5 SDA               | A 输出延迟功能                             | 867 |

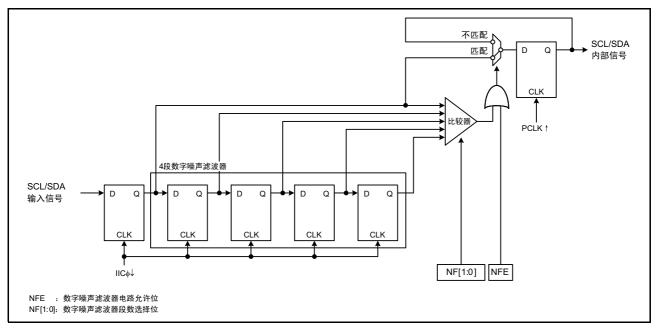

| 28.6 数字                | <sup>2</sup> 噪声滤波器电路                 | 868 |

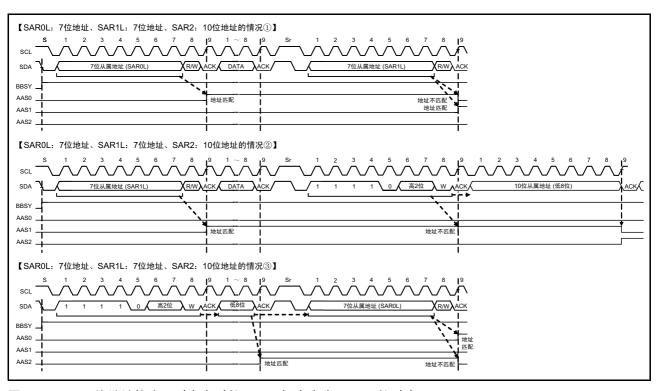

| 28.7 地址                | 上匹配检测功能                              | 869 |

| 28.7.1                 | 从属地址匹配检测功能                           | 869 |

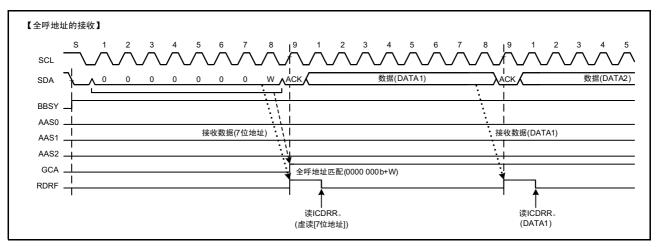

| 28.7.2                 | 全呼地址检测功能                             | 871 |

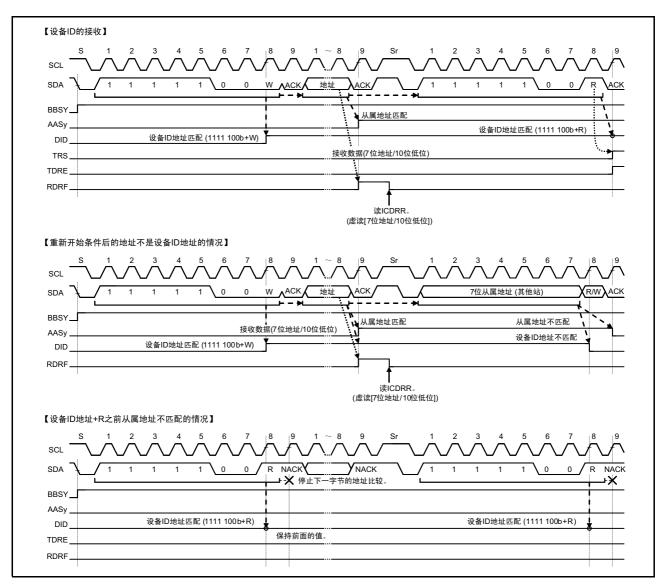

| 28.7.3                 | 设备 ID 地址检测功能                         |     |

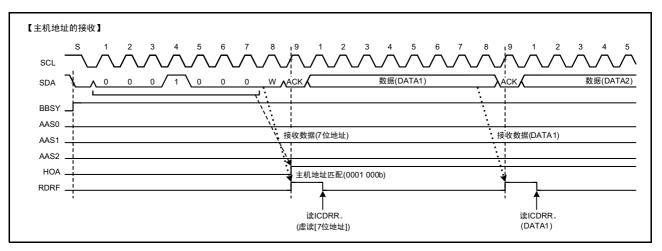

| 28.7.4                 | 主机地址检测功能                             | 873 |

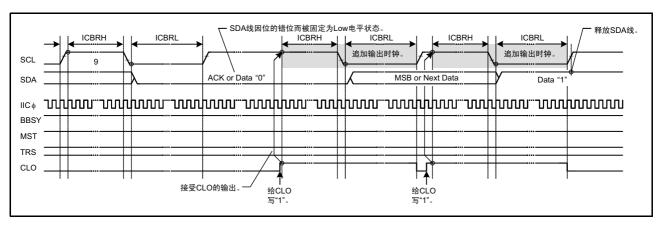

| 28.8 SCL               | . 的 Low 电平自动保持功能                     |     |

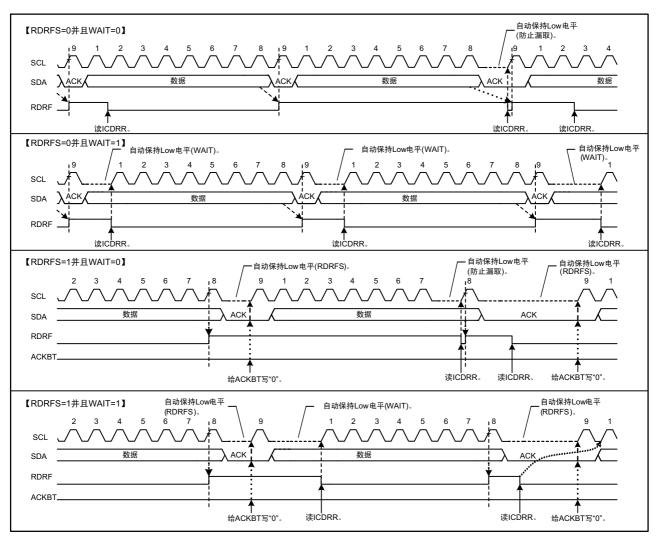

| 28.8.1                 | 发送数据的误发送防止功能                         | 874 |

| 2882                   | NACK 接收佳详由上功能                        | 875 |

| 28.8.3           | 接收数据漏取防止功能                                            | 075 |

|------------------|-------------------------------------------------------|-----|

|                  | 安以致始州弘防正功能                                            |     |

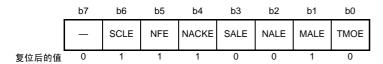

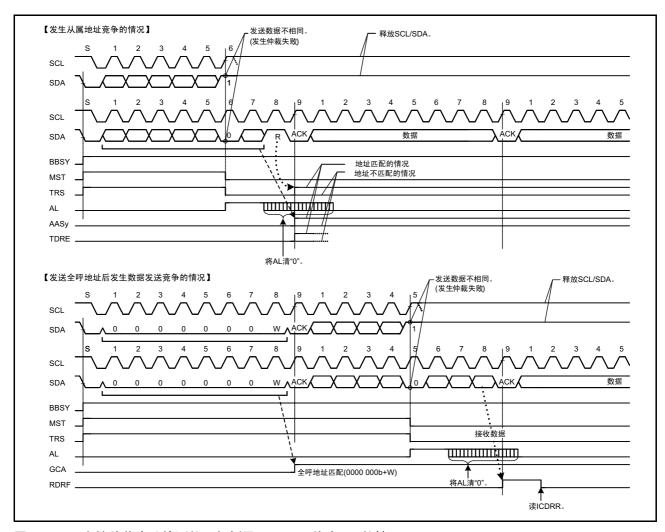

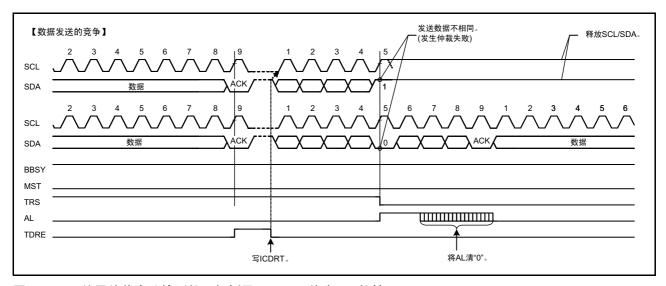

| 28.9.1           | 主控仲裁失败检测功能 (MALE 位)                                   |     |

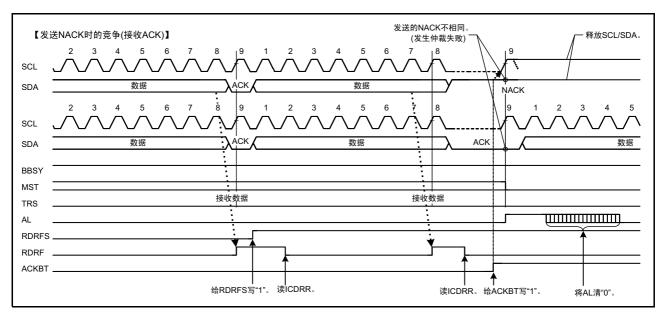

| 28.9.1           | NACK 发送仲裁失败检测功能 (NALE 位)                              |     |

| 28.9.2           | NACK 及这件裁关效检测功能(NALE 位)           从属仲裁失败检测功能 (SALE 位) |     |

|                  | 分条件、重新开始条件和停止条件的发行功能                                  |     |

|                  |                                                       |     |

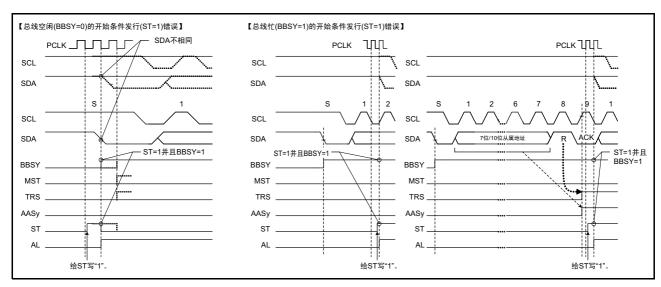

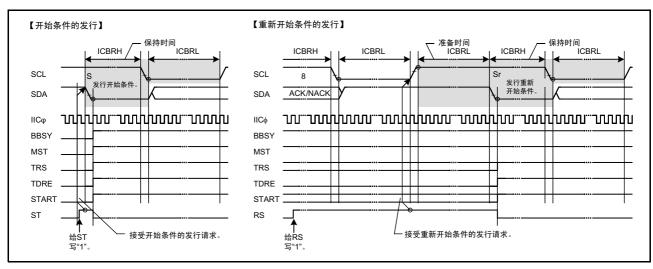

| 28.10.1          | 开始条件的发行                                               |     |

| 28.10.2          | 重新开始条件的发行                                             |     |

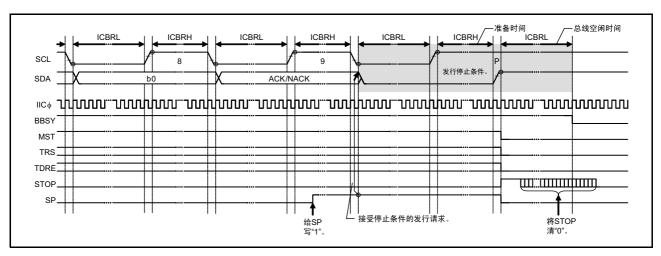

| 28.10.3          | 停止条件的发行                                               |     |

|                  | き意外停机                                                 |     |

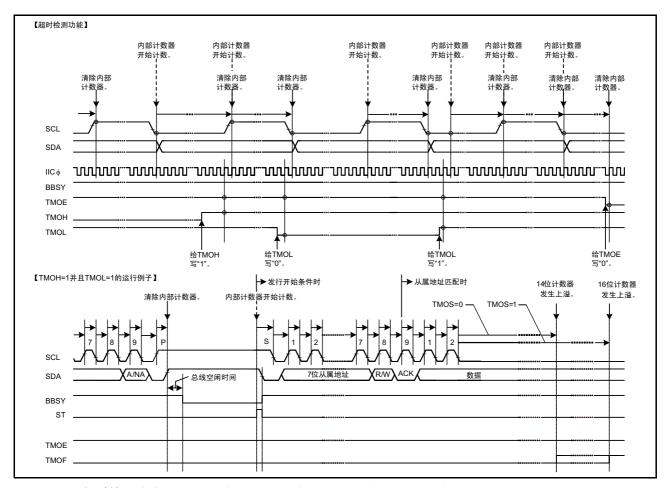

| 28.11.1          | 超时检测功能                                                |     |

| 28.11.2          | SCL 时钟追加输出功能                                          |     |

| 28.11.3          | RIIC/ 内部复位                                            |     |

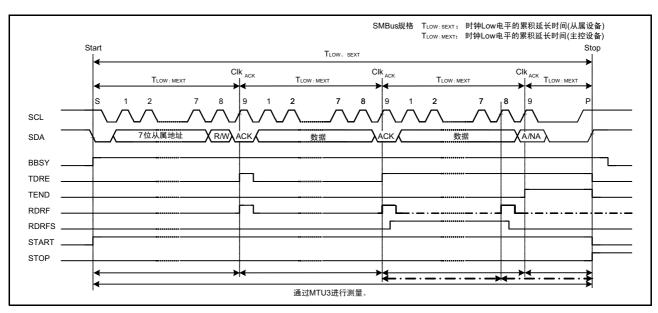

|                  | Bus 运行                                                |     |

| 28.12.1          | SMBus 超时测量                                            |     |

| 28.12.2          | 数据包错误码(PEC)                                           |     |

| 28.12.3          | SMBus 主机通知协议 /Notify ARP master                       |     |

|                  | f源                                                    |     |

| 28.13.1          |                                                       |     |

|                  | 7.状况                                                  |     |

| ~ ~ .            | 时的注意事项                                                |     |

| 28.15.1          | 模块停止功能的设定                                             |     |

| 28.15.2          | 有关开始通信的注意事项                                           | 889 |

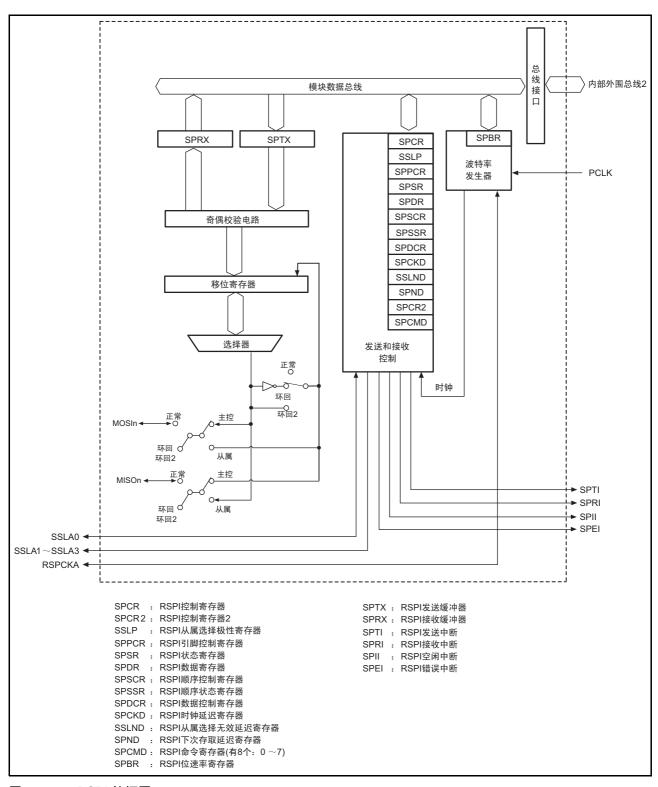

| 29. 串行タ          | 卜围接口 (RSPI)                                           | 890 |

|                  |                                                       |     |

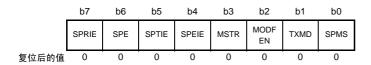

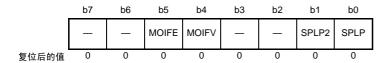

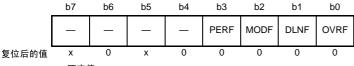

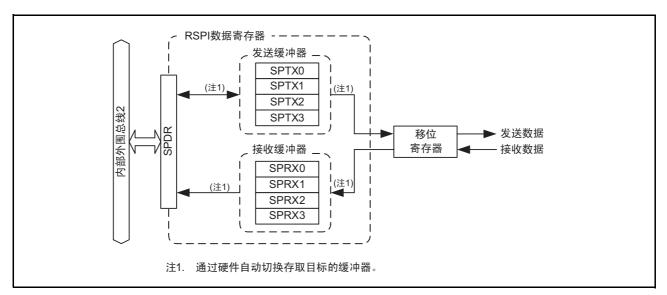

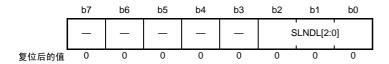

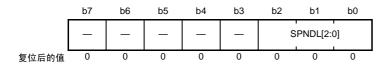

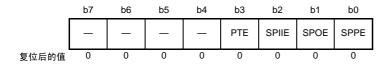

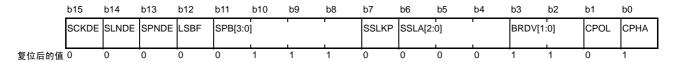

|                  | 字器说明                                                  |     |