# RZ/N1D Group, RZ/N1S Group, RZ/N1L Group

User's Manual: Peripherals

RZ Family RZ/N Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### Contact information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="https://www.renesas.com/contact/">www.renesas.com/contact/</a>.

# General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

- 1. Precaution against Electrostatic Discharge (ESD)

- A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

- 2. Processing at power-on

- The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

- Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements.

Follow the guideline for input signal during power-off state as described in your product documentation.

- 4. Handling of unused pins

- Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

- 5. Clock signals

- After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

- 6. Voltage application waveform at input pin

- Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

- 7. Prohibition of access to reserved addresses

- Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

- 8. Differences between products

- Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

## How to Use This Manual

#### 1. Objective and Target Users

This manual was written to explain the hardware functions and electrical characteristics of this LSI to the target users, i.e. those who will be using this LSI in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logic circuits, and microcomputers.

This manual is organized in the following items: an overview of the product, descriptions of the CPU, system control functions, and peripheral functions, electrical characteristics of the device, and usage notes.

When designing an application system that includes this LSI, take all points to note into account. Points to note are given in their contexts and at the final part of each section, and in the section giving usage notes.

The list of revisions is a summary of major points of revision or addition for earlier versions. It does not cover all revised items. For details on the revised points, see the actual locations in the manual.

The following documents have been prepared for reference.

#### ■ Documents related to RZ/N1

| Document Name                                                                                                                    | Document Number                  |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group DATASHEET                                                                               | R01DS0323EJ****                  |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: System Introduction, Multiplexing, Electrical and Mechanical Information | R01UH0750EJ****                  |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: System Control and Peripheral                                            | R01UH0751EJ****                  |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: Peripherals                                                              | R01UH0752EJ****<br>(this manual) |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: R-IN Engine and Ethernet Peripherals                                     | R01UH0753EJ****                  |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: PWMTimer                                                                 | R01UH0913EJ****                  |

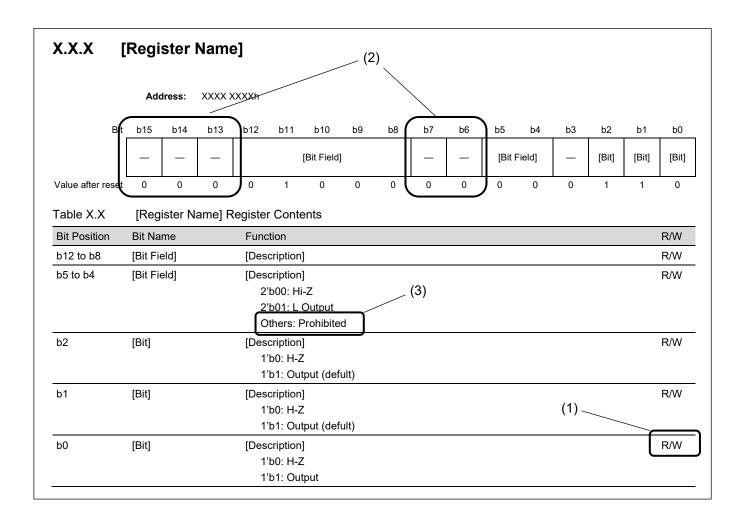

### 2. Description of Registers

Each register description includes a bit chart, illustrating the arrangement of bits, and a table of bits, describing the meanings of the bit settings. The standard format and notation for bit charts and tables are described below.

(1) R/W: The bit or field is readable and writable.

R/(W): The bit or field is readable and writable. However, writing to this bit or field has some limitations. For details on the limitations, see the description or notes of respective registers.

R: The bit or field is readable. Writing to this bit or field has no effect.

W: The bit or field is writable. Reading to this bit or field is not guaranteed.

- (2) Reserved. Make sure to use the specified value when writing to this bit or field; otherwise, the correct operation is not guaranteed.

- (3) Setting prohibited. The correct operation is not guaranteed if such a setting is performed.

## 3. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                   |

|--------------|---------------------------------------------|

| AHB          | Arm Advanced High-performance Bus           |

| APB          | Arm Advanced Peripheral Bus                 |

| AXI          | Arm Advanced eXtensible Interface           |

| bps          | bits per second                             |

| CA7          | Arm Cortex-A7 module                        |

| CM3          | Arm Cortex-M3 module                        |

| CRC          | Cyclic Redundancy Check                     |

| DMA          | Direct Memory Access                        |

| DMAC         | Direct Memory Access Controller             |

| Hi-Z         | High Impedance                              |

| HSR          | High-availability Seamless Redundancy       |

| HW-RTOS      | Hard Ware Real Time OS                      |

| I/O          | Input/Output                                |

| INTC         | Interrupt Controller                        |

| LSB          | Least Significant Bit                       |

| MSB          | Most Significant Bit                        |

| NC           | Non-Connect                                 |

| NoC          | Network-on-Chip                             |

| PLL          | Phase Locked Loop                           |

| PWM          | Pulse Width Modulation                      |

| UART         | Universal Asynchronous Receiver/Transmitter |

| OTP          | One Time Programmable                       |

| PTP          | Precision Time Protocol                     |

| PRP          | Parallel Redundancy Protocol                |

| SoC          | System On Chip                              |

## 4. Description of the Access Size

Access size:

8 bits = Byte

16 bits = Halfword

32 bits = Word

CAN (Controller Area Network): An automotive network specification developed by Robert Bosch GmbH of Germany Arm is a registered trademark of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

# **Table of Contents**

| Sectior | า 1 UA | RT                                                                | 20 |

|---------|--------|-------------------------------------------------------------------|----|

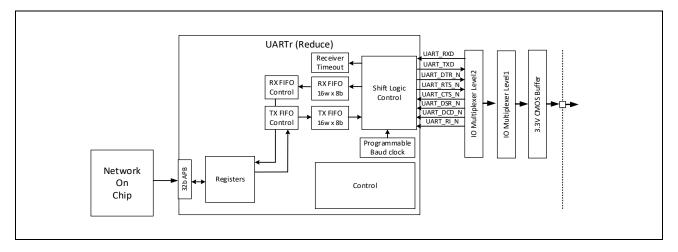

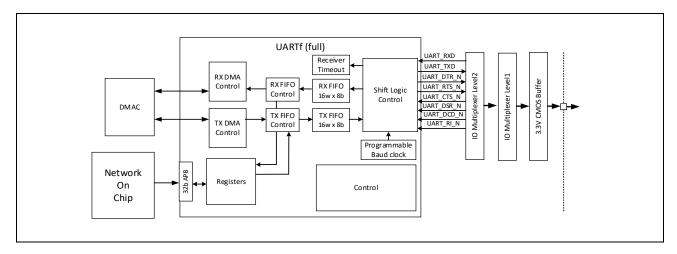

| 1.1     | Over   | riew                                                              | 20 |

| 1.2     | Signa  | l Interfaces                                                      | 22 |

| 1.3     | Regis  | ter Map                                                           | 23 |

|         | 1.3.1  | Register Map UART 1                                               |    |

|         | 1.3.2  | Register Map UART 2                                               |    |

|         | 1.3.3  | Register Map UART 3                                               |    |

|         | 1.3.4  | Register Map UART 4                                               | 26 |

|         | 1.3.5  | Register Map UART 5                                               | 27 |

|         | 1.3.6  | Register Map UART 6                                               | 28 |

|         | 1.3.7  | Register Map UART 7                                               | 29 |

|         | 1.3.8  | Register Map UART 8                                               | 30 |

| 1.4     | Regis  | ter Description                                                   | 31 |

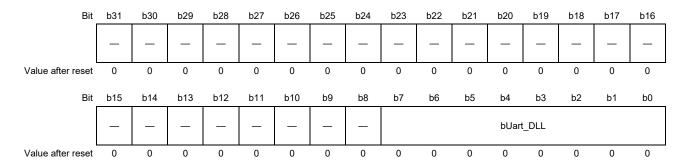

|         | 1.4.1  | rUart DLL — Divisor Latch (Low)                                   | 31 |

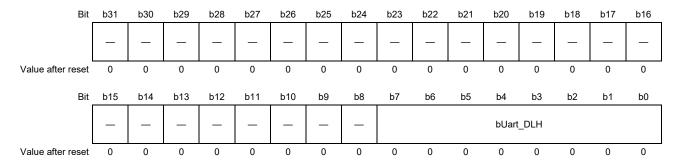

|         | 1.4.2  | rUart_DLH — Divisor Latch (High)                                  | 32 |

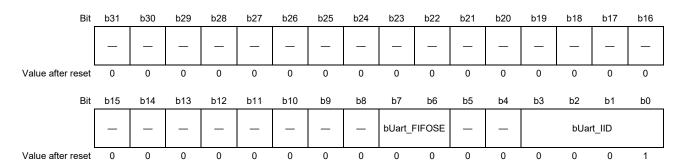

|         | 1.4.3  | rUart_IIR — Interrupt Identification Register                     | 33 |

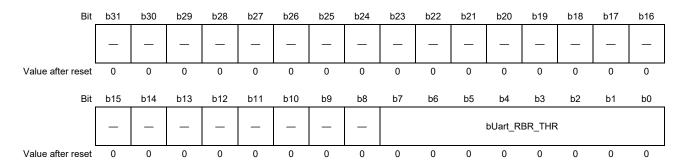

|         | 1.4.4  | rUart_RBR_THR — Receive Buffer/Transmit Holding Register          | 34 |

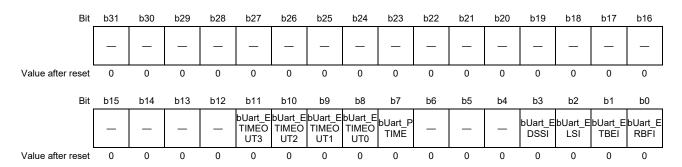

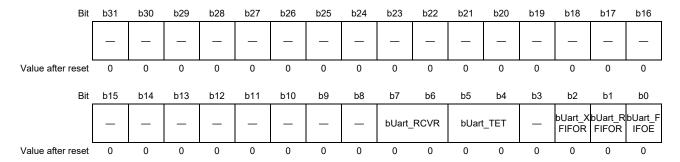

|         | 1.4.5  | rUart_IER — Interrupt Enable Register                             | 35 |

|         | 1.4.6  | rUart_FCR — FIFO Control Register                                 | 37 |

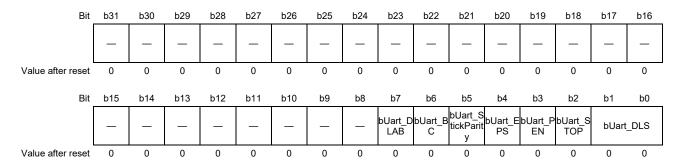

|         | 1.4.7  | rUart_LCR — Line Control Register                                 | 39 |

|         | 1.4.8  | rUart_MCR — Modem Control Register                                | 41 |

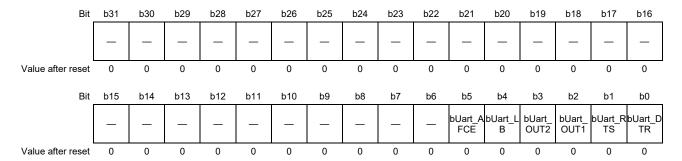

|         | 1.4.9  | rUart_LSR — Line Status Register                                  | 43 |

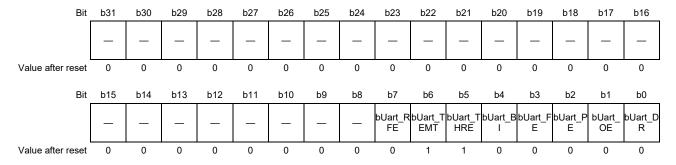

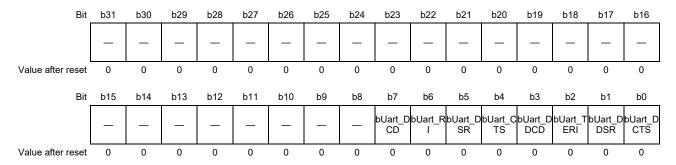

|         | 1.4.10 | rUart_MSR — Modem Status Register                                 | 46 |

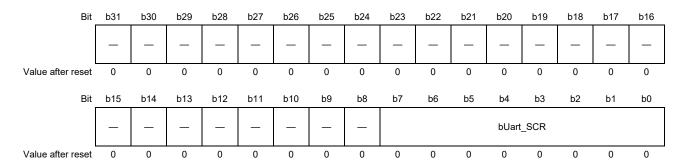

|         | 1.4.11 | rUart_SCR — Scratchpad Register                                   | 48 |

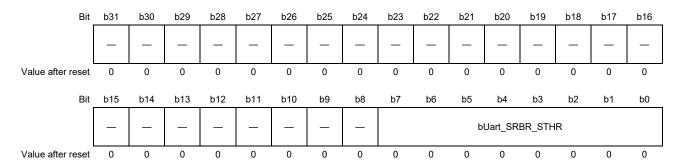

|         | 1.4.12 | rUart_SRBR_STHR — Shadow Receive Buffer/Transmit Holding Register | 49 |

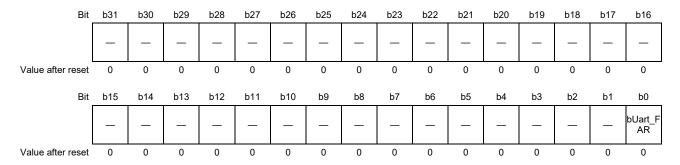

|         | 1.4.13 | rUart_FAR — FIFO Access Register                                  | 50 |

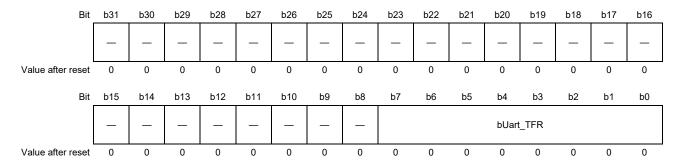

|         | 1.4.14 | rUart_TFR — Transmit FIFO Read                                    | 51 |

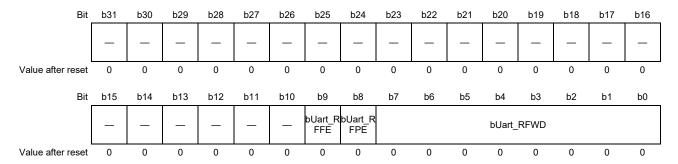

|         | 1.4.15 | rUart_RFW — Receive FIFO Write                                    | 52 |

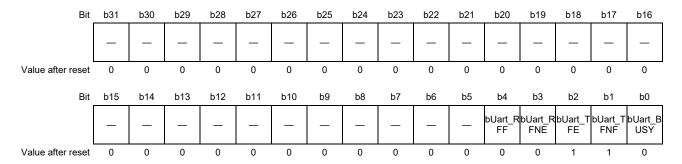

|         | 1.4.16 | rUart_USR — UART Status Register                                  | 53 |

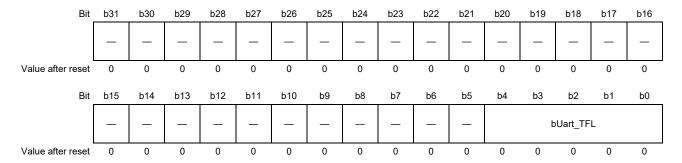

|         | 1.4.17 | rUart_TFL — Transmit FIFO Level                                   | 55 |

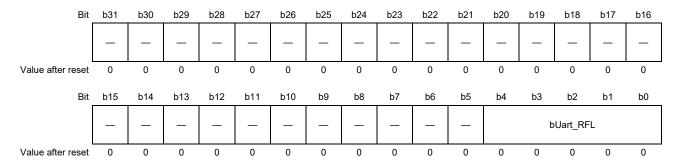

|         | 1.4.18 | rUart_RFL — Receive FIFO Level                                    | 56 |

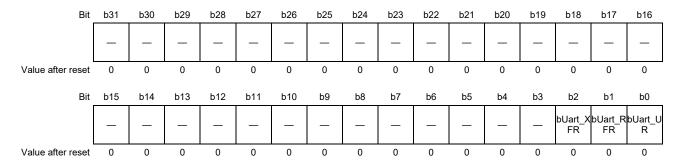

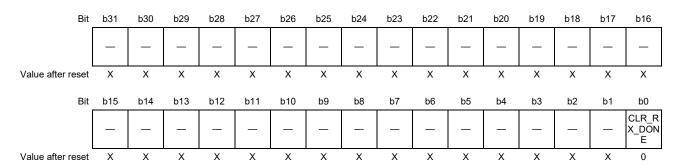

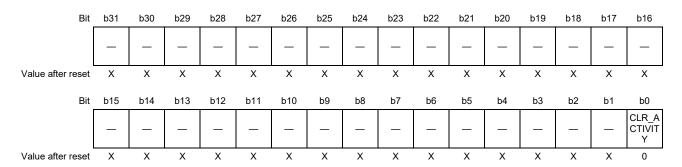

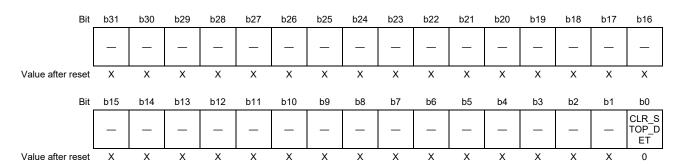

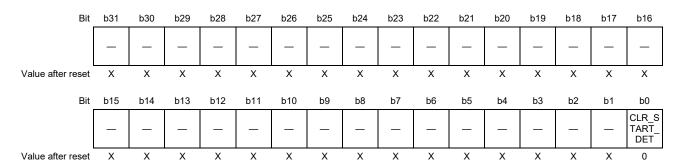

|         | 1.4.19 | rUart_SRR — Software Reset Register                               | 57 |

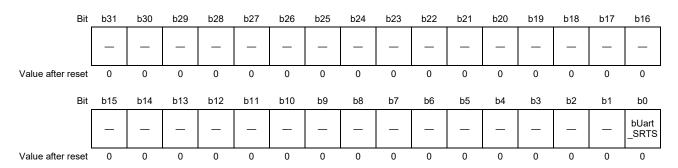

|         | 1.4.20 | rUart_SRTS — Shadow Request to Send                               | 58 |

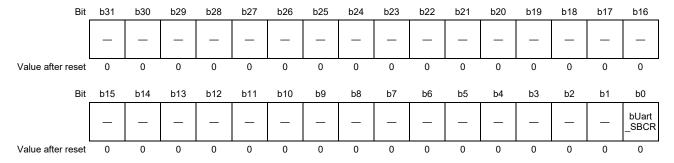

|         | 1.4.21 | rUart_SBCR — Shadow Break Control Register                        | 59 |

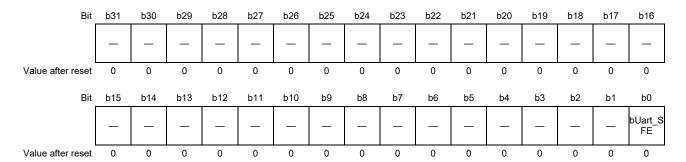

|         | 1.4.22 | rUart_SFE — Shadow FIFO Enable                                    | 60 |

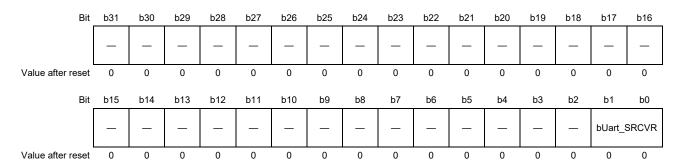

|         | 1.4.23 | rUart_SRT — Shadow RCVR Trigger                                   | 61 |

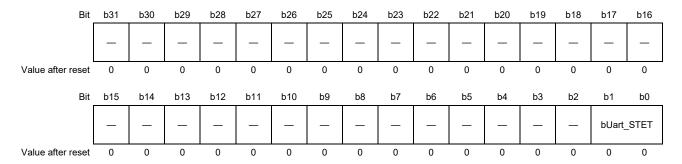

|         | 1.4.24 | rUart_STET — Shadow TX Empty Trigger                              | 62 |

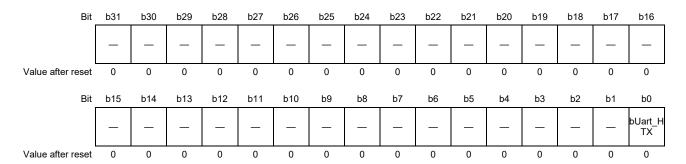

|         | 1.4.25 | rUart_HTX — Halt TX                                               |    |

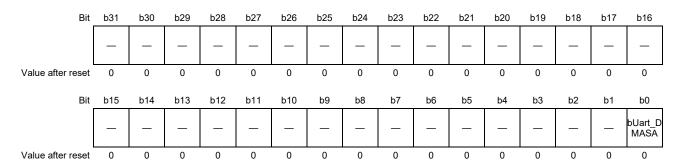

|         | 1.4.26 | rUart_DMASA — DMA Software Acknowledge                            |    |

|         | 1.4.27 | rUart_TO — Time-Out Counter Configuration Register                | 65 |

|        | 1.4.28  | rUart_CTRLTO — Time-Out Control Register                         | 67  |

|--------|---------|------------------------------------------------------------------|-----|

|        | 1.4.29  | rUart_STATUSTO — Time-Out Counter Status Register                | 69  |

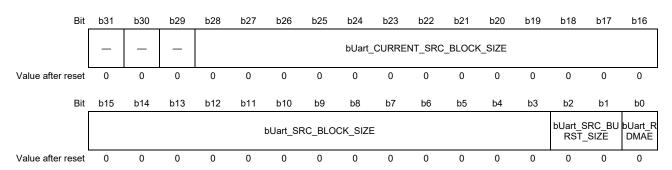

|        | 1.4.30  | rUart_TDMACR — DMA Control Register in Transmit Mode             | 71  |

|        | 1.4.31  | rUart_RDMACR — DMA Control Register in Receive Mode              | 73  |

| 1.5    | Opera   | ation                                                            | 75  |

|        | 1.5.1   | Main Function Blocks Description                                 | 75  |

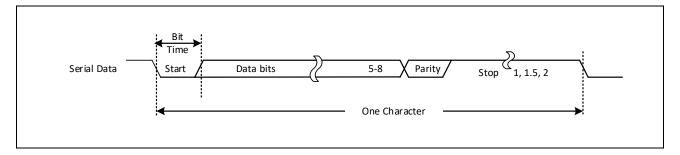

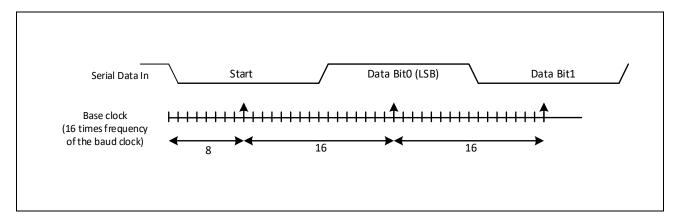

|        | 1.5.    | .1.1 UART (RS232) Serial Protocol                                | 75  |

|        | _       | 1.2 Baud Rate Tolerance to 19200 baud                            |     |

|        |         | 1.3 FIFO Management                                              |     |

|        | _       | Clock Management      Back to Back Character Stream Transmission |     |

|        |         | 1.6 Interrupts                                                   |     |

|        |         | 1.7 Auto Flow Control                                            |     |

|        | 1.5.    | .1.8 Programmable THRE interrupt                                 | 82  |

|        |         | 1.9 DMA Management (Only UART4, 5, 6, 7, 8)                      |     |

|        | _       | 1.10 Transceiver & Receiver Time-Out for MODBUS Management       |     |

|        | 1.5.2   | Usage Notes                                                      | 96  |

| Sectio | n 2 SPI |                                                                  | 97  |

| 2.1    | Overv   | /iew                                                             | 97  |

| 2.2    | Signa   | l Interfaces                                                     | 99  |

| 2.3    | Regis   | ter Map                                                          | 100 |

|        | 2.3.1   | Register Map SPI1 (Master)                                       |     |

|        | 2.3.2   | Register Map SPI2 (Master)                                       |     |

|        | 2.3.3   | Register Map SPI3 (Master)                                       | 102 |

|        | 2.3.4   | Register Map SPI4 (Master)                                       | 103 |

|        | 2.3.5   | Register Map SPI5 (Slave)                                        | 104 |

|        | 2.3.6   | Register Map SPI6 (Slave)                                        | 105 |

| 2.4    | Regis   | ter Description                                                  | 106 |

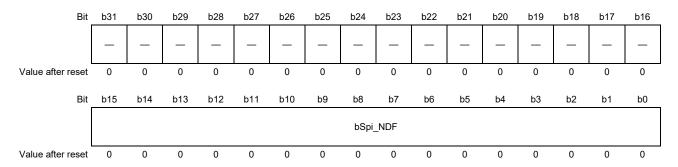

|        | 2.4.1   | rSpi_CTRLR0 — Control Register 0                                 | 106 |

|        | 2.4.2   | rSpi_CTRLR1 — Control Register 1                                 | 108 |

|        | 2.4.3   | rSpi_SSIENR — Enable Register                                    | 109 |

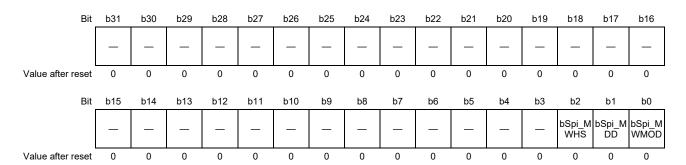

|        | 2.4.4   | rSpi_MWCR — Microwire Control Register                           | 110 |

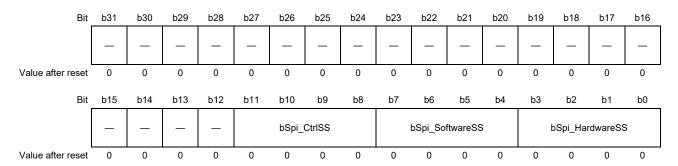

|        | 2.4.5   | rSpi_SER — Slave Enable Register                                 | 111 |

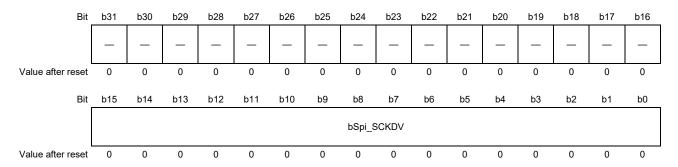

|        | 2.4.6   | rSpi_BAUDR — Baud Rate Select                                    | 113 |

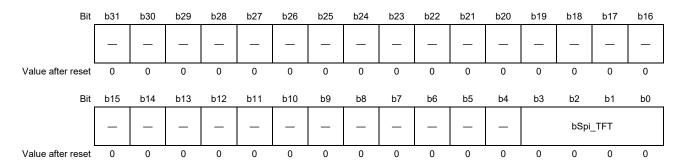

|        | 2.4.7   | rSpi_TXFTLR — Transmit FIFO Threshold Level                      | 114 |

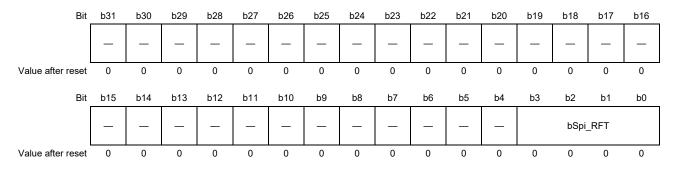

|        | 2.4.8   | rSpi_RXFTLR — Receive FIFO Threshold Level                       | 115 |

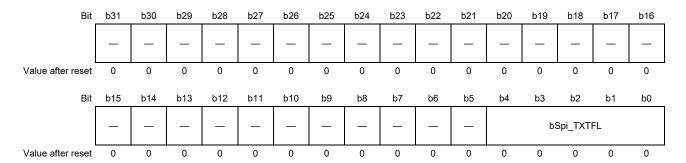

|        | 2.4.9   | rSpi_TXFLR — Transmit FIFO Level Register                        | 116 |

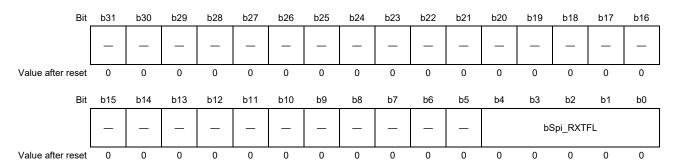

|        | 2.4.10  | rSpi_RXFLR — Receive FIFO Level Register                         | 117 |

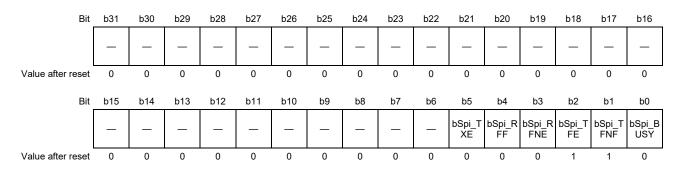

|        | 2.4.11  | rSpi_SR — Status Register                                        | 118 |

|        | 2.4.12  | rSpi_IMR — Interrupt Mask Register                               | 120 |

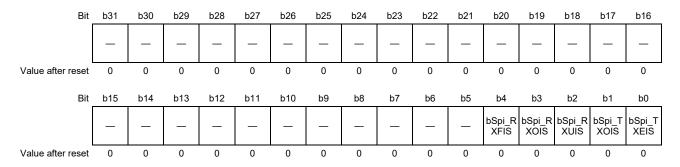

|        | 2.4.13  | rSpi_ISR — Interrupt Status Register                             | 121 |

|        | 2.4.14  | rSpi_RISR — Raw Interrupt Status Register                        | 122 |

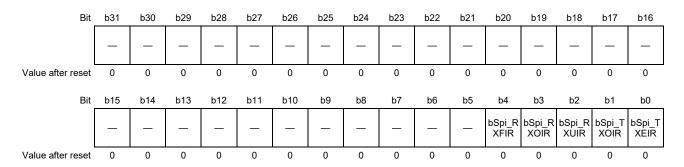

|        | 2.4.15  | rSpi_TXOICR — Transmit FIFO Overflow Interrupt Clear Register    | 123 |

|        |         |                                                                  |     |

|         | 2.4.16   | rSpi_RXOICR — Receive FIFO Overflow Interrupt Clear                                                                                 | Register124 |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------|-------------|

|         | 2.4.17   | rSpi_RXUICR — Receive FIFO Underflow Interrupt Clear                                                                                | Register125 |

|         | 2.4.18   | rSpi_ICR — Interrupt Clear Register                                                                                                 | 126         |

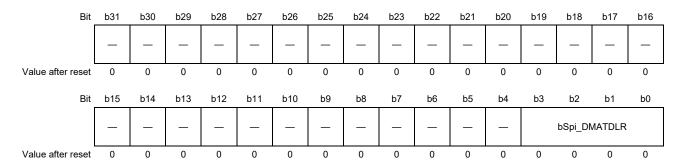

|         | 2.4.19   | rSpi_DMACR — DMA Control Register                                                                                                   | 127         |

|         | 2.4.20   | rSpi_DMATDLR — DMA Transmit Data Level                                                                                              | 128         |

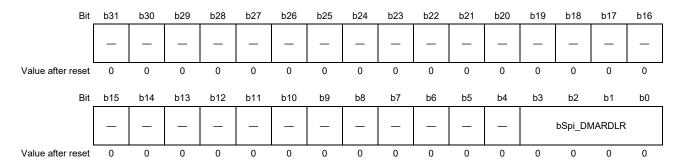

|         | 2.4.21   | rSpi_DMARDLR — DMA Receive Data Level                                                                                               |             |

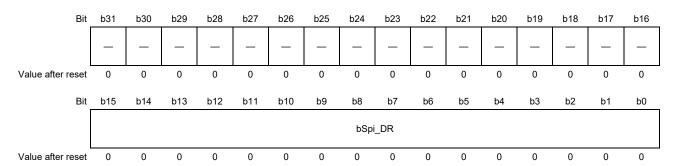

|         | 2.4.22   | rSpi DR — Data Register                                                                                                             |             |

|         | 2.4.23   | rSpi_RX_SAMPLE_DLY — RXD Sample Delay Register                                                                                      | 131         |

|         | 2.4.24   | rSpi_TDMACR — DMA Control Register in Transmit Mod                                                                                  |             |

|         | 2.4.25   | rSpi_RDMACR — DMA Control Register in Receive Mod                                                                                   |             |

| 2.5     | Oper     | ation                                                                                                                               |             |

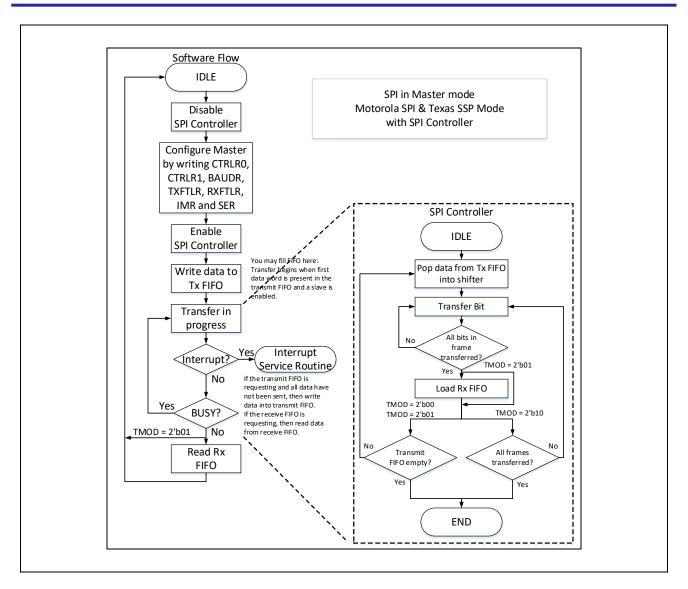

| 2.0     | 2.5.1    | General description                                                                                                                 |             |

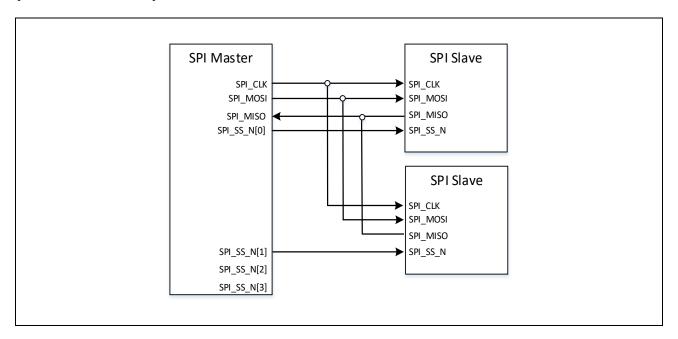

|         | 2.5.1    | Typical Connection between SPI Master & Slave                                                                                       |             |

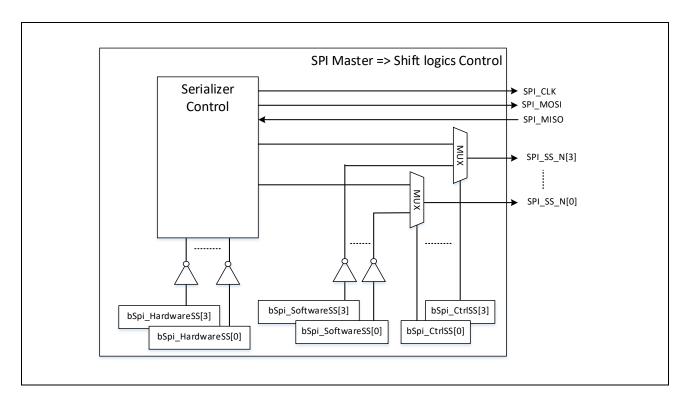

|         | 2.5.2    | Control Slave Select Line by Hardware or Software Mode                                                                              |             |

|         |          | Programmable Prescaler Clock                                                                                                        |             |

|         | 2.5.4    |                                                                                                                                     |             |

|         | 2.5.5    | Data Input Sample Delay                                                                                                             |             |

|         | 2.5.6    | Transmit & Receive FIFO & Control                                                                                                   |             |

|         | 2.5.7    | Interruption Management                                                                                                             |             |

|         | 2.5.8    | Transfer Mode                                                                                                                       | _           |

|         |          | .8.1 Transmit and Receive Mode                                                                                                      |             |

|         |          | .8.2 Transmit Only Mode                                                                                                             |             |

|         |          | .8.4 EEPROM Read Mode                                                                                                               |             |

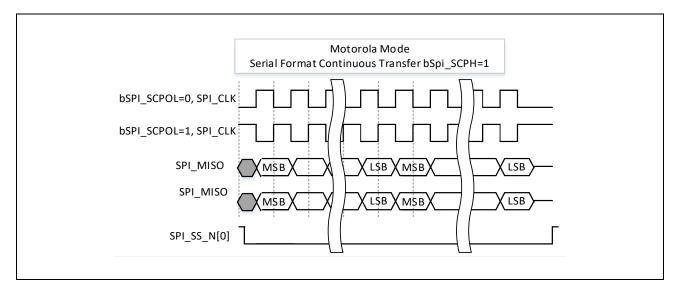

|         | 2.5.9    | Motorola Serial Peripheral Interface                                                                                                |             |

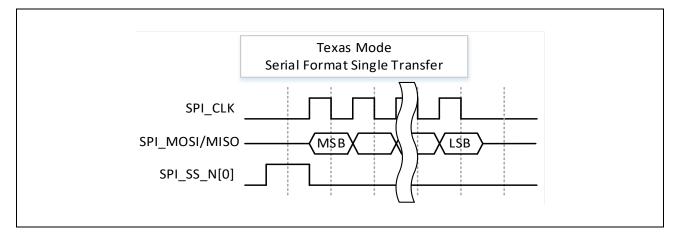

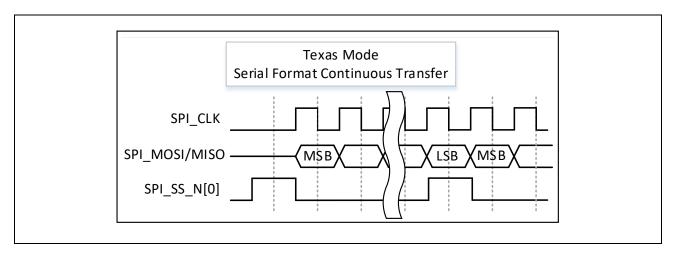

|         | 2.5.10   | Texas Instruments Synchronous Serial Protocol                                                                                       |             |

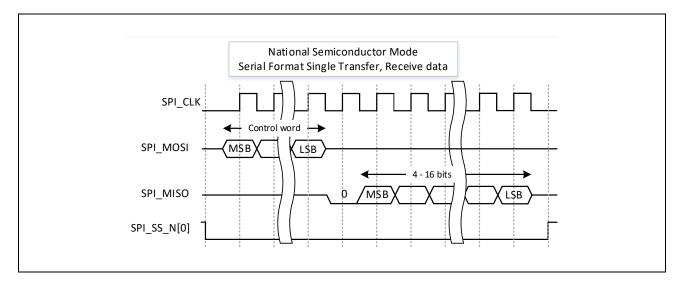

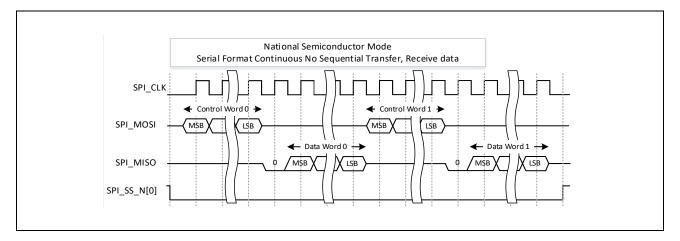

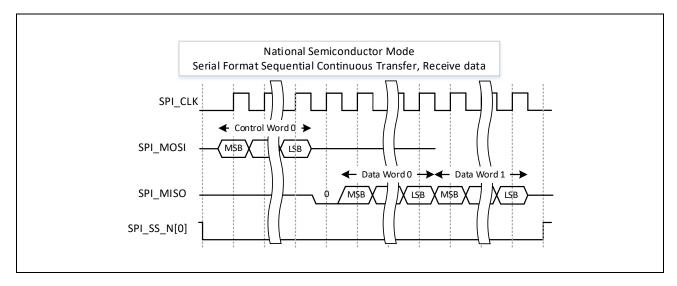

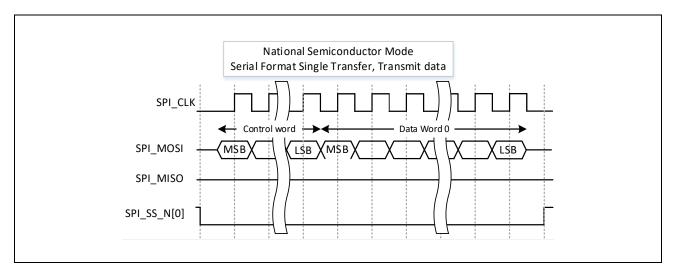

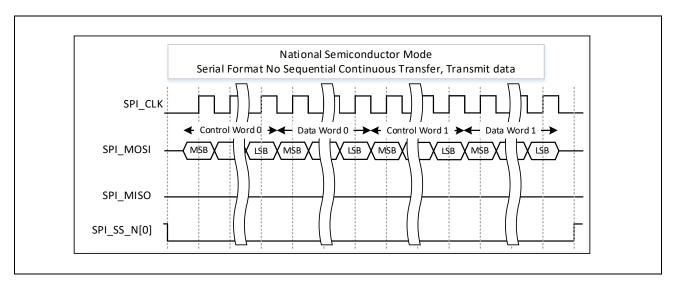

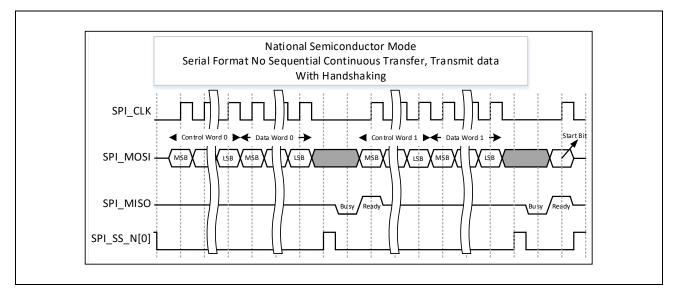

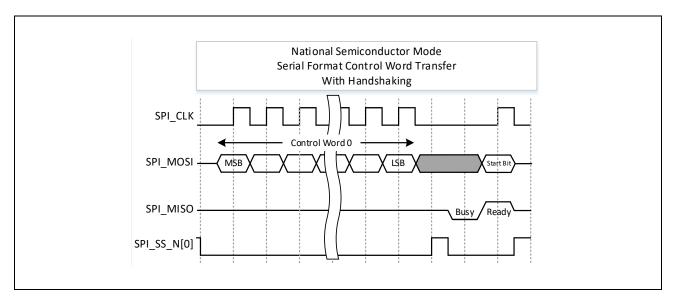

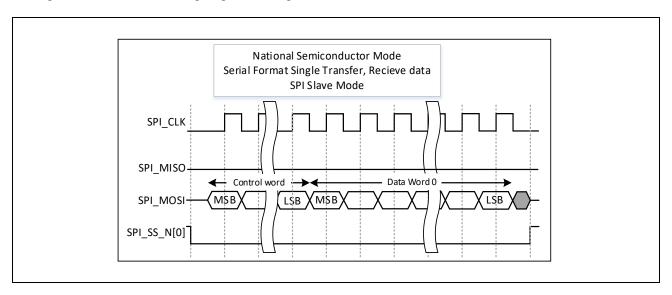

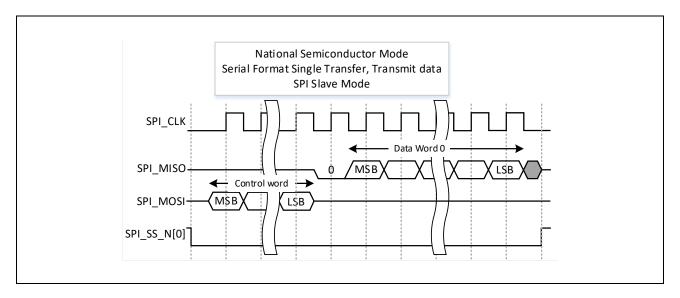

|         | 2.5.11   | National Semiconductor Microwire                                                                                                    |             |

|         | 2.5.12   | DMA Control                                                                                                                         |             |

|         |          | .12.1 Overview on DMA Operation                                                                                                     |             |

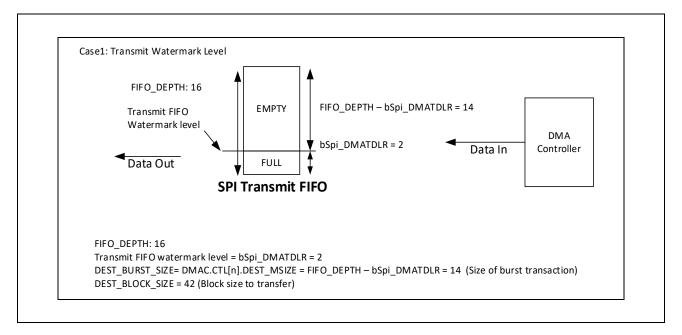

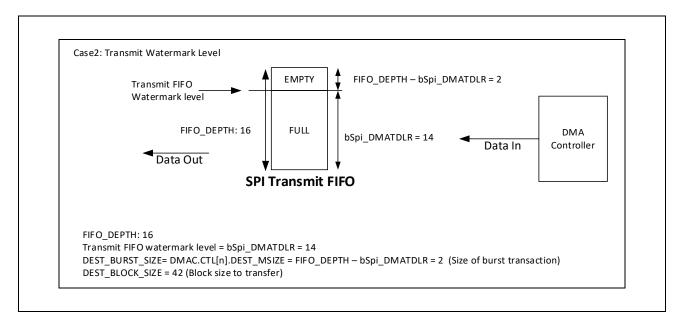

|         |          | .12.2 Transmit Watermark Level and Transmit FIFO Un                                                                                 |             |

|         | 2.5      | .12.3 Choosing the Transmit Watermark Level                                                                                         |             |

|         |          | .12.4 Selecting DEST_MSIZE and Transmit FIFO Overf                                                                                  |             |

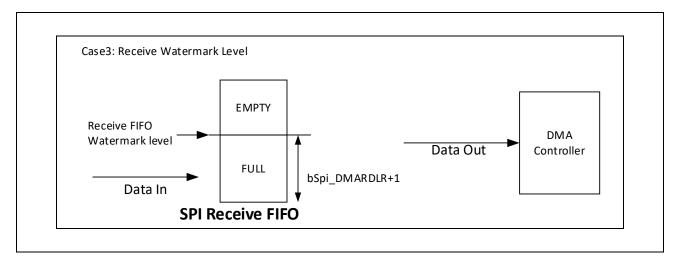

|         | _        | .12.5 Receive Watermark Level and Receive FIFO Over                                                                                 |             |

|         |          | .12.6 Choosing the Receive Watermark Level                                                                                          |             |

| 0.0     |          | <b>5</b> –                                                                                                                          |             |

| 2.6     | ū        | e Notes                                                                                                                             |             |

|         | 2.6.1    | Programming Consideration                                                                                                           |             |

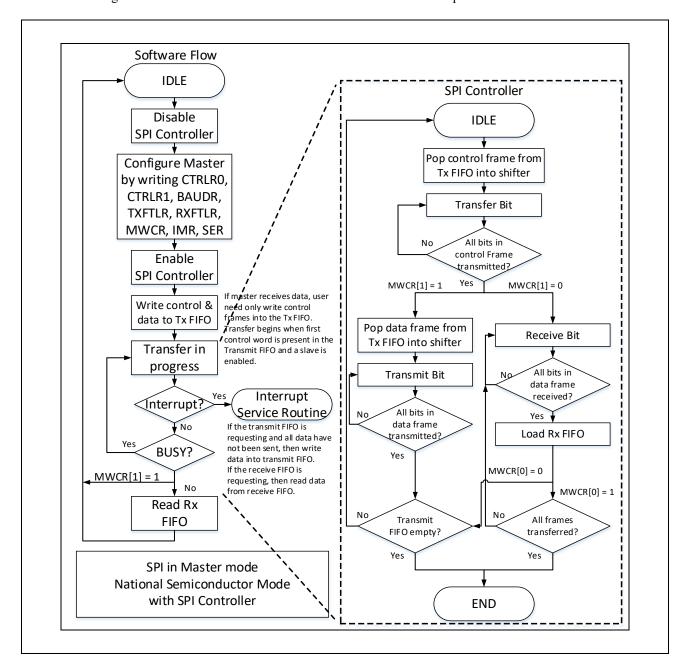

|         | _        | <ul><li>.1.1 Programming Master SPI in Motorola &amp; Texas Mo</li><li>.1.2 Programming Master SPI in National Semiconduc</li></ul> |             |

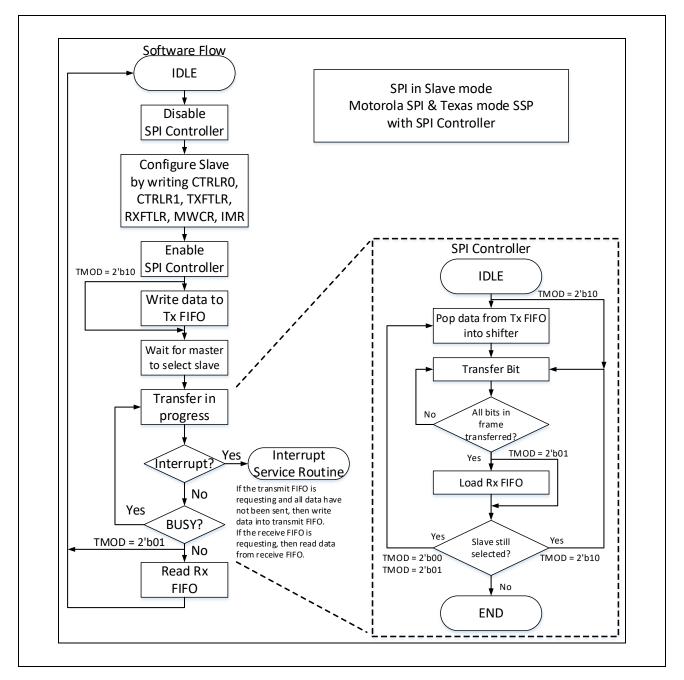

|         |          | .1.3 Programming Slave SPI in Motorola & Texas Mod                                                                                  |             |

|         |          | .1.4 Programming Slave SPI in National Semiconducto                                                                                 |             |

| Section | on 3 I2C | ·                                                                                                                                   | 168         |

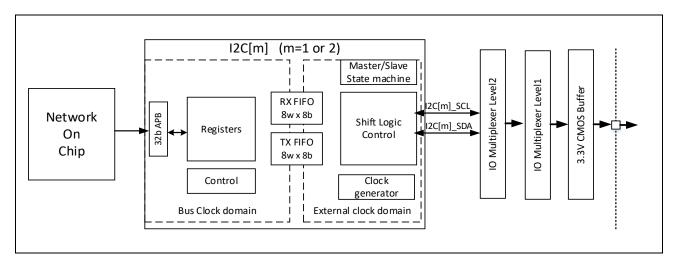

| 3.1     | Over     | /iew                                                                                                                                | 168         |

| 3.2     | Signa    | Il Interfaces                                                                                                                       | 169         |

| 3.3     | Regis    | ster Map                                                                                                                            | 170         |

| 3.3.1    | I2C1 Register Map                                                | 170 |

|----------|------------------------------------------------------------------|-----|

| 3.3.2    | I2C2 Register Map                                                | 171 |

| 3.4 Regi | ster Description                                                 | 172 |

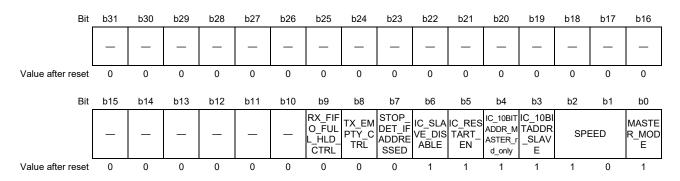

| 3.4.1    | IC_CON — I2C Control Register                                    | 172 |

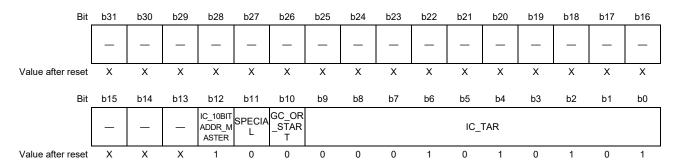

| 3.4.2    | IC_TAR — I2C Target Address Register                             | 174 |

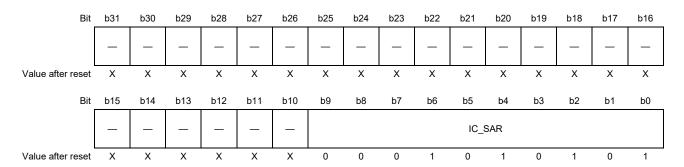

| 3.4.3    | IC_SAR — I2C Slave Address Register                              | 175 |

| 3.4.4    | IC_DATA_CMD — I2C Rx/Tx Data Buffer and Command Register         | 176 |

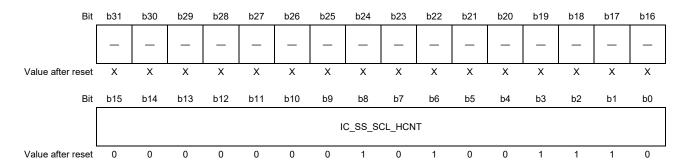

| 3.4.5    | IC_SS_SCL_HCNT — Standard mode I2C Clock SCL High Count Register | 178 |

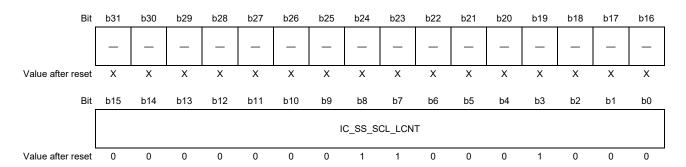

| 3.4.6    | IC_SS_SCL_LCNT — Standard mode I2C Clock SCL Low Count Register  | 179 |

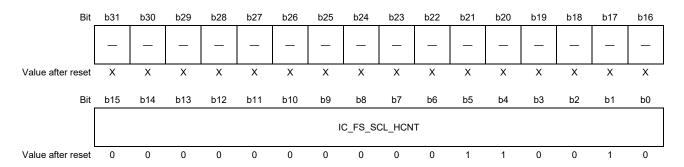

| 3.4.7    | IC_FS_SCL_HCNT — Fast mode I2C Clock SCL High Count Register     | 179 |

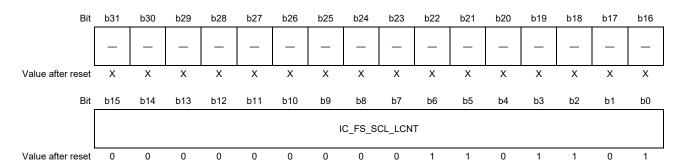

| 3.4.8    | IC_FS_SCL_LCNT — Fast mode I2C Clock SCL Low Count Register      | 180 |

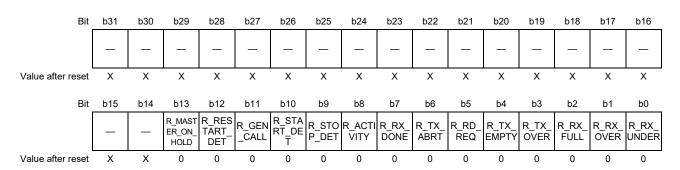

| 3.4.9    | IC_INTR_STAT — I2C Interrupt Status Register                     | 181 |

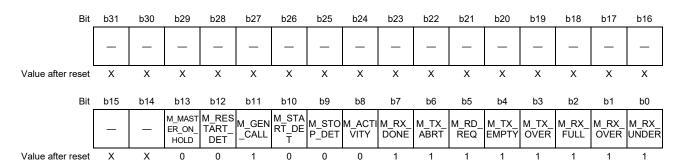

| 3.4.10   | IC_INTR_MASK — I2C Interrupt Mask Register                       | 182 |

| 3.4.11   | IC_RAW_INTR_STAT — I2C Raw Interrupt Status Register             | 184 |

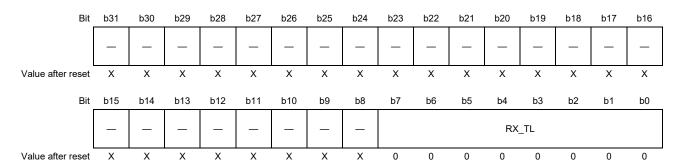

| 3.4.12   | IC_RX_TL — I2C Receive FIFO Threshold Register                   | 187 |

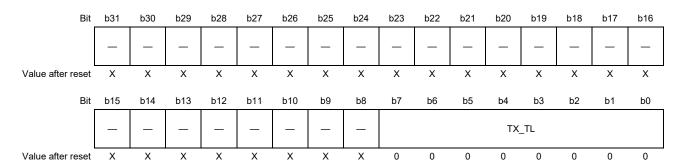

| 3.4.13   | IC_TX_TL — I2C Transmit FIFO Threshold Register                  | 188 |

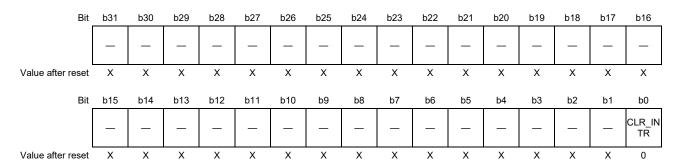

| 3.4.14   | IC_CLR_INTR — Clear Combined and Individual Interrupt Register   |     |

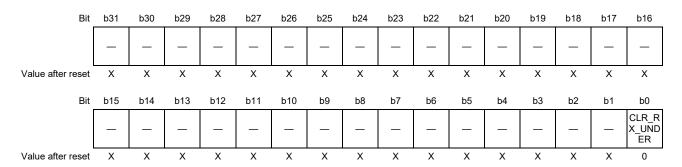

| 3.4.15   | IC CLR RX UNDER — Clear RX UNDER Interrupt Register              |     |

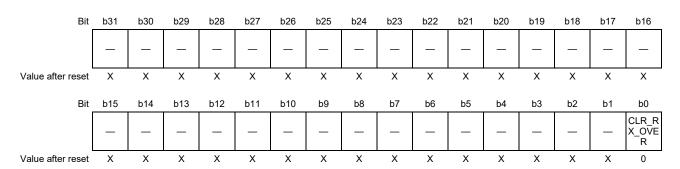

| 3.4.16   | IC_CLR_RX_OVER — Clear RX_OVER Interrupt Register                |     |

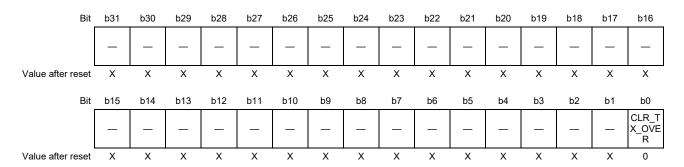

| 3.4.17   | IC_CLR_TX_OVER — Clear TX_OVER Interrupt Register                |     |

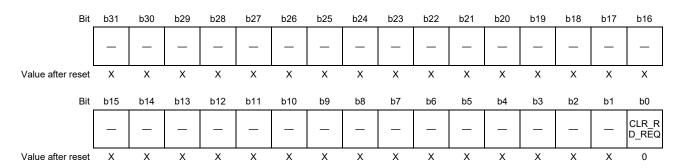

| 3.4.18   | IC_CLR_RD_REQ — Clear RD_REQ Interrupt Register                  |     |

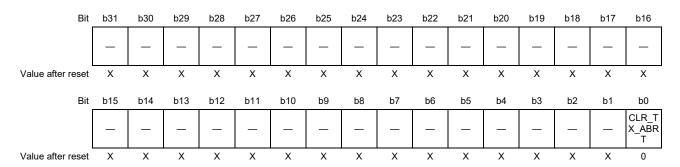

| 3.4.19   | IC_CLR_TX_ABRT — Clear TX_ABRT Interrupt Register                | 191 |

| 3.4.20   | IC_CLR_RX_DONE — Clear RX_DONE Interrupt Register                | 191 |

| 3.4.21   | IC_CLR_ACTIVITY — Clear ACTIVITY Interrupt Register              |     |

| 3.4.22   | IC_CLR_STOP_DET — Clear STOP_DET Interrupt Register              | 192 |

| 3.4.23   | IC_CLR_START_DET — Clear START_DET Interrupt Register            | 193 |

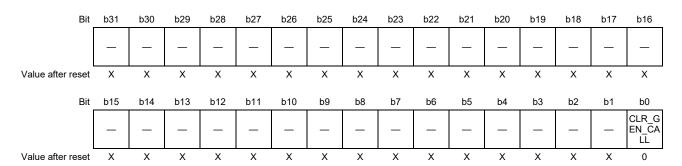

| 3.4.24   | IC CLR GEN CALL — Clear GEN CALL Interrupt Register              | 193 |

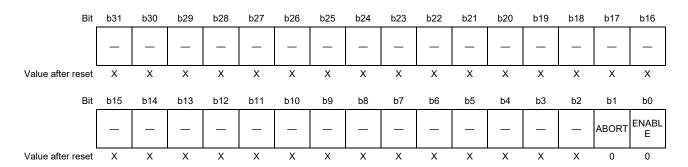

| 3.4.25   | IC_ENABLE — I2C Enable Register                                  |     |

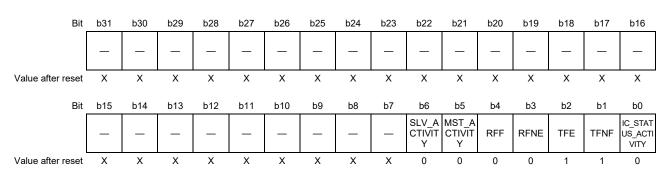

| 3.4.26   | IC STATUS — I2C Status Register                                  |     |

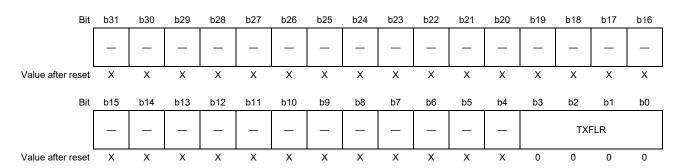

| 3.4.27   | IC_TXFLR — I2C Transmit FIFO Level Register                      | 197 |

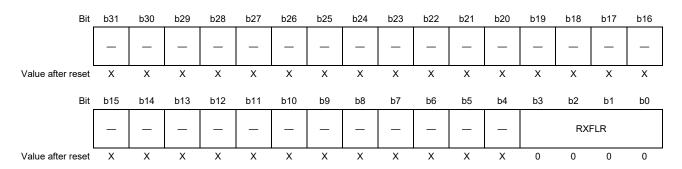

| 3.4.28   | IC_RXFLR — I2C Receive FIFO Level Register                       | 198 |

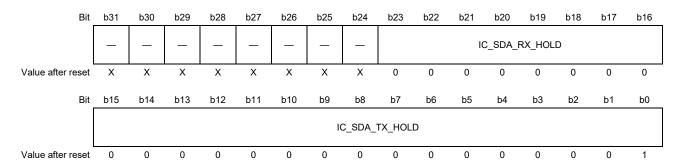

| 3.4.29   | IC_SDA_HOLD — I2C SDA Hold Time Length Register                  |     |

| 3.4.30   | IC_TX_ABRT_SOURCE — I2C Transmit Abort Source Register           |     |

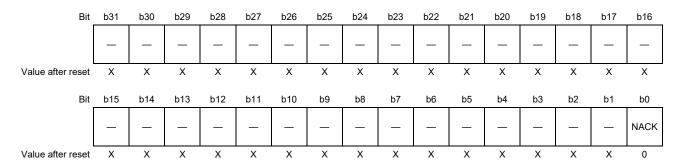

| 3.4.31   | IC_SLV_DATA_NACK_ONLY — Generate Slave Data NACK Register        |     |

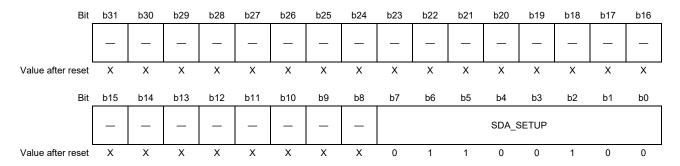

| 3.4.32   | IC_SDA_SETUP — I2C SDA Setup Register                            | 203 |

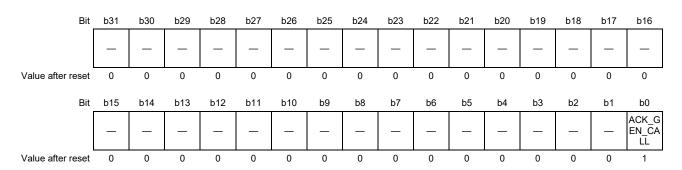

| 3.4.33   | IC_ACK_GENERAL_CALL — I2C ACK General Call Register              |     |

| 3.4.34   | IC_ENABLE_STATUS — I2C Enable Status Register                    |     |

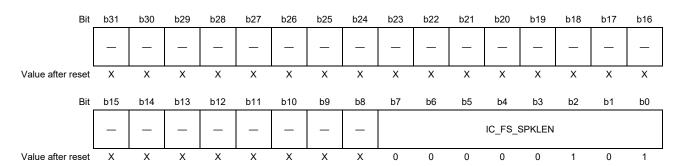

| 3.4.35   | IC_FS_SPKLEN — I2C Sm, Fm Spike Suppression Limit                |     |

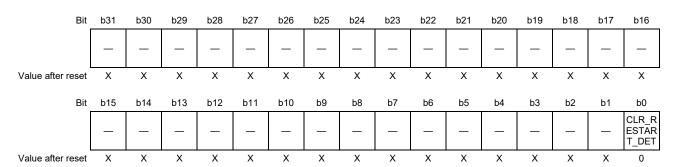

| 3.4.36   | IC_CLR_RESTART_DET — Clear RESTART_DET Interrupt Register        |     |

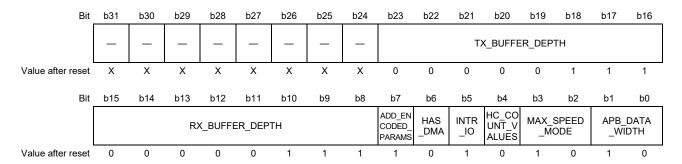

| 3.4.37   | IC_COMP_PARAM_1 — Component Parameter Register 1                 |     |

|          | ration Modes                                                     |     |

| 3.5.1    | Slave Mode Operation                                             |     |

| ა.ი. i   |                                                                  |     |

|        | 3.5        | 1.2 Slave Transmitter Operat | ion for a Single Byte                           | 211  |

|--------|------------|------------------------------|-------------------------------------------------|------|

|        | 3.5        | •                            | n for a Single Byte                             |      |

|        | 3.5        | •                            | for Bulk Transfer                               |      |

|        | 3.5.2      | •                            |                                                 |      |

|        | 3.5<br>3.5 | S S                          | 0BITADDR_MASTER Update                          |      |

|        | 3.5        |                              | ster Receive                                    |      |

|        | 3.5.3      |                              |                                                 |      |

|        | 3.5        | •                            |                                                 |      |

|        | 3.5.4      |                              |                                                 |      |

|        | 3.5        | •                            |                                                 |      |

| 3.6    | Prog       | amming the I2C Controller    |                                                 | 218  |

|        | 3.6.1      | Spike Suppression            |                                                 | 218  |

|        | 3.6.2      | , , , ,                      | ition                                           |      |

|        | 3.6        |                              | Counts                                          |      |

|        | 3.6.3      | SDA Hold Time                |                                                 | 221  |

|        | 3.6        | 3.1 SDA Hold Timings in Red  | ceiver                                          | 221  |

|        | 3.6        | 3.2 SDA Hold Timings in Tra  | nsmitter                                        | 222  |

| Soctio | on 4 Ba    | ic CDIO                      |                                                 | 223  |

|        |            |                              |                                                 |      |

| 4.1    |            |                              |                                                 |      |

| 4.2    | Signa      | Interfaces                   |                                                 | 225  |

| 4.3    | Regi       | er Map                       |                                                 | 226  |

|        | 4.3.1      | Register Map BGPIO1          |                                                 | 226  |

|        | 4.3.2      | Register Map BGPIO2          |                                                 | 226  |

|        | 4.3.3      | Register Map BGPIO3          |                                                 | 227  |

| 4.4    | Regi       | er Description               |                                                 | 228  |

|        | 4.4.1      | rGPIO_swporta_dr — GPIO Por  | t A Data Output Register                        | 228  |

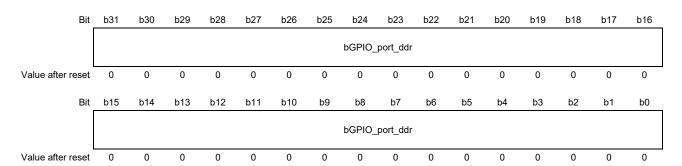

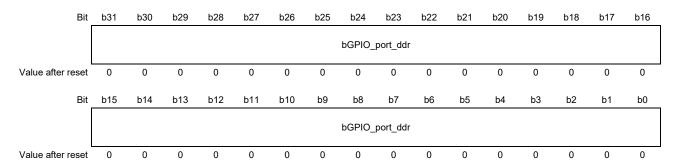

|        | 4.4.2      | rGPIO swporta ddr — GPIO Po  | ort A Data Direction Register                   | 228  |

|        | 4.4.3      |                              | t B Data Output Register                        |      |

|        | 4.4.4      |                              | ort B Data Direction Register                   |      |

|        | 4.4.5      |                              | errupt Enable Register                          |      |

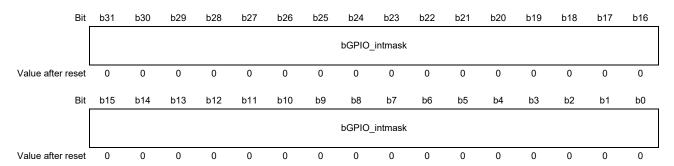

|        | 4.4.6      | <del>-</del>                 | Interrupt Mask Register                         |      |

|        | 4.4.7      | <del>-</del>                 | ort A Interrupt Level Register                  |      |

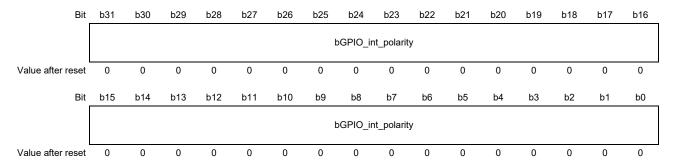

|        | 4.4.8      |                              | t A Interrupt Polarity Register                 |      |

|        | 4.4.9      |                              | Interrupt Status                                |      |

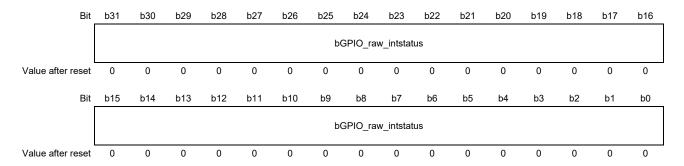

|        | 4.4.10     | <del>-</del>                 | Port A Raw Interrupt Status (Premasking)        |      |

|        | 4.4.11     |                              | A Clear Interrupt Register                      |      |

|        | 4.4.11     | <b>_</b> · _                 | , ,                                             |      |

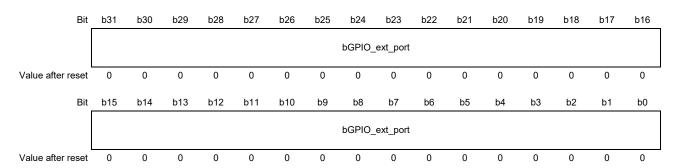

|        |            | <del></del>                  | A Data Input Register                           |      |

|        | 4.4.13     | <del></del>                  | B Data Input Register                           |      |

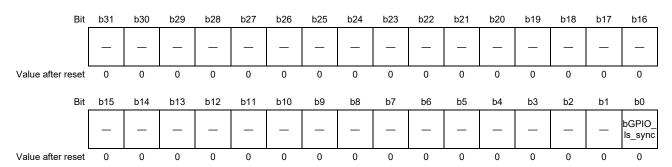

|        | 4.4.14     |                              | Level-Sensitive Synchronization Enable Register |      |

| 4.5    | •          |                              |                                                 |      |

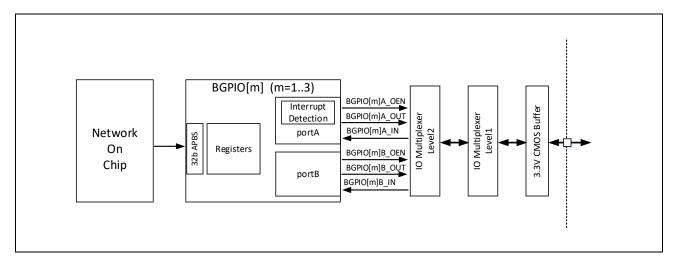

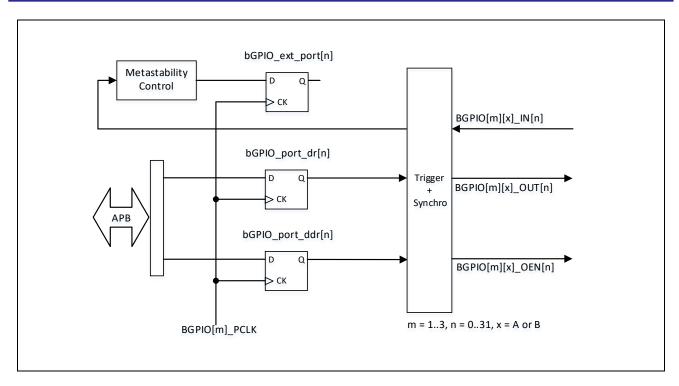

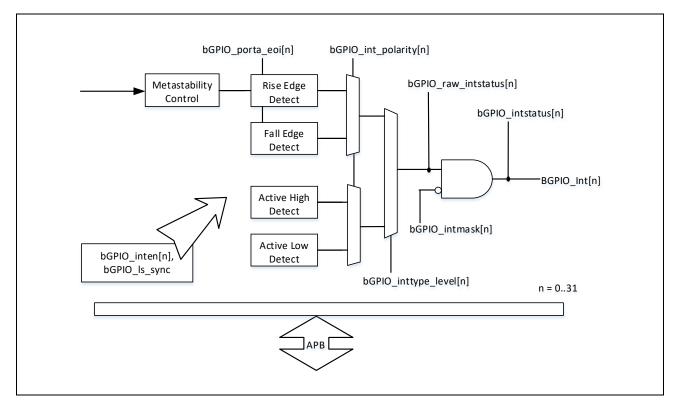

|        | 4.5.1      | •                            | on                                              |      |

|        |            | I I LIGIO X ( ONTROL LIGHT   |                                                 | .1.1 |

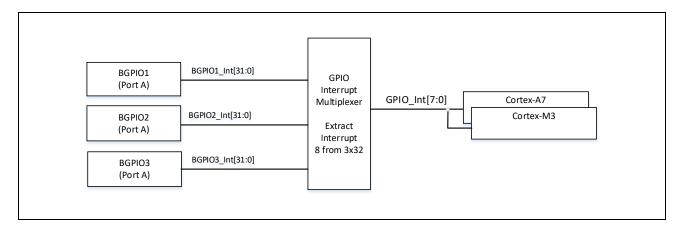

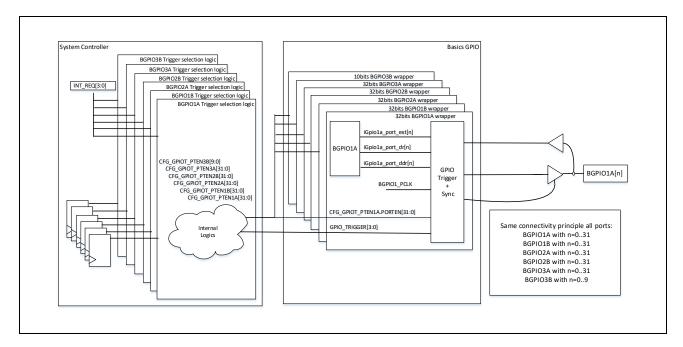

|         |                | 5.1.3<br>5.1.4 | Programmable Interrupts Routed on Cortex-A7 and M3  Trigger Synchronous Operation |     |

|---------|----------------|----------------|-----------------------------------------------------------------------------------|-----|

| 4.6     |                |                |                                                                                   |     |

| 4.0     | 4.6.1          |                | ımming Consideration                                                              |     |

|         | 4.0.1          | i iogia        | inining consideration                                                             | 200 |

| Section | on 5 Tin       | ner Blo        | ck                                                                                | 240 |

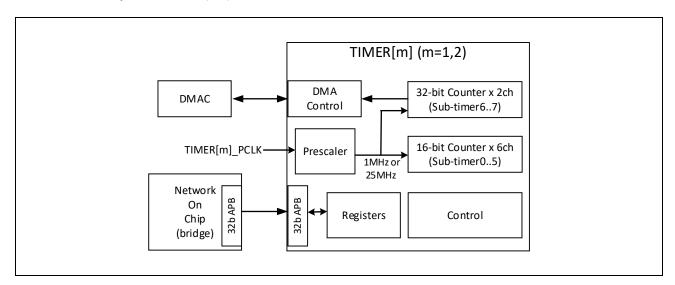

| 5.1     | Over           | view           |                                                                                   | 240 |

| 5.2     | Signa          | al Interfa     | ces                                                                               | 241 |

| 5.3     | Regi           | ster Map       | )                                                                                 | 242 |

|         | 5.3.1          | •              | R1 Register Map                                                                   |     |

|         | 5.3.2          |                | R2 Register Map                                                                   |     |

| 5.4     | Regi           |                | cription                                                                          |     |

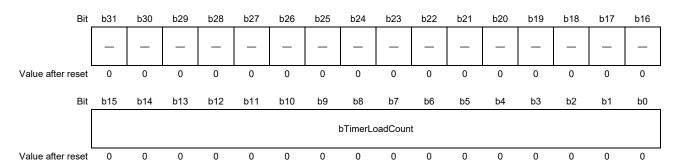

|         | 5.4.1          |                | LoadCount_[n] — Preset Value of Sub-timer[n] (n = 05)                             |     |

|         | 5.4.2          |                | LoadCount_[n] — Preset Value of Sub-timer[n] (n = 67)                             |     |

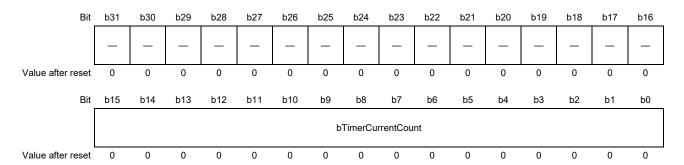

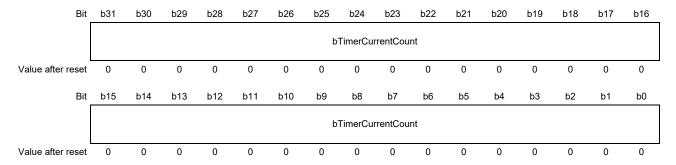

|         | 5.4.3          |                | CurrentCount_[n] — Current Value of Sub-timer[n] (n = 05)                         |     |

|         | 5.4.4          |                | CurrentCount_[n] — Current Value of Sub-timer[n] (n = 67)                         |     |

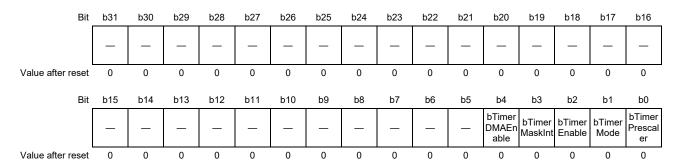

|         | 5.4.5          | rTimer         | Control_[n] — Control Mode of Sub-timer[n] (n = 07)                               | 246 |

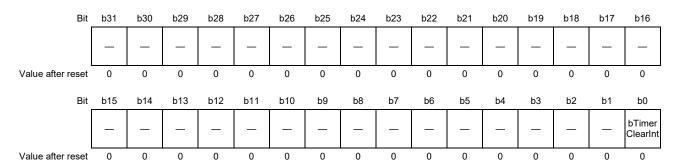

|         | 5.4.6          | rTimer         | ClearInt_[n] — Clears the Interruption of Sub-timer[n] (n = 07)                   | 247 |

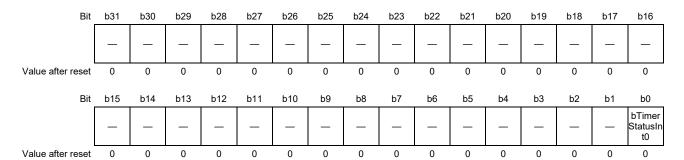

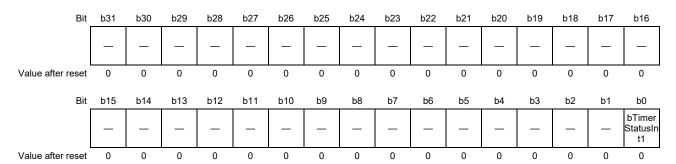

|         | 5.4.7          | rTimer         | StatusInt0_[n] — Interruption Status before Masking of Sub-timer[n] (n = 07)      | 248 |

|         | 5.4.8          | rTimer         | StatusInt1_[n] — Interruption Status after Masking of Sub-timer[n] (n = 07)       | 249 |

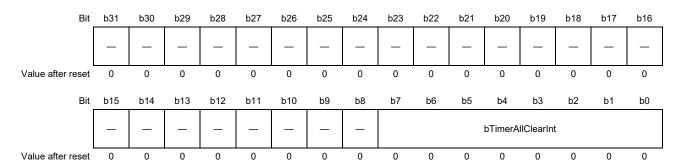

|         | 5.4.9          | rTimer         | AllClearInt — Clear All Interrupt                                                 | 250 |

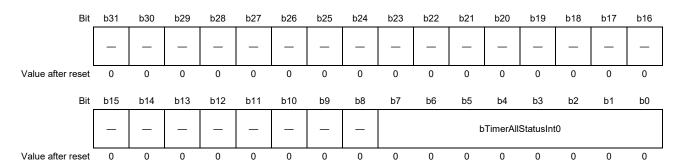

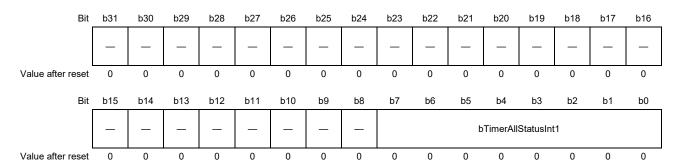

|         | 5.4.10         | rTimer         | AllStatusInt0 — All Interrupts Status before Masking                              | 251 |

|         | 5.4.11         | rTimer         | AllStatusInt1 — All Interrupts Status after Masking                               | 252 |

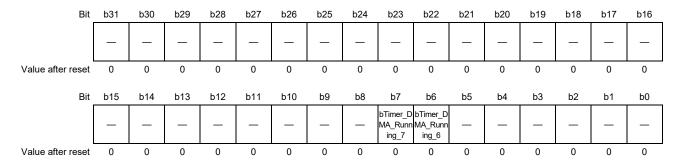

|         | 5.4.12         | rTimer         | _DMA_Pending — TIMER DMA Requests Status                                          | 253 |

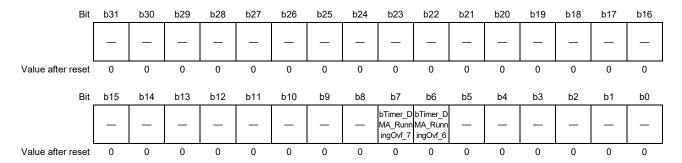

|         | 5.4.13         | rTimer         | _DMA_PendingOvf — TIMER DMA Overflow Status                                       | 254 |

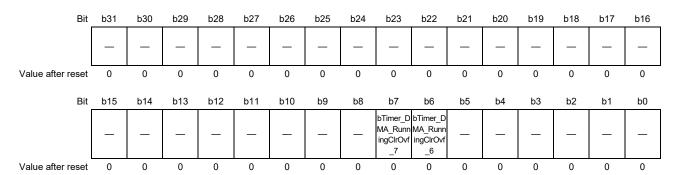

|         | 5.4.14         | rTimer         | _DMA_PendingClrOvf — TIMER DMA Overflow Clear                                     | 255 |

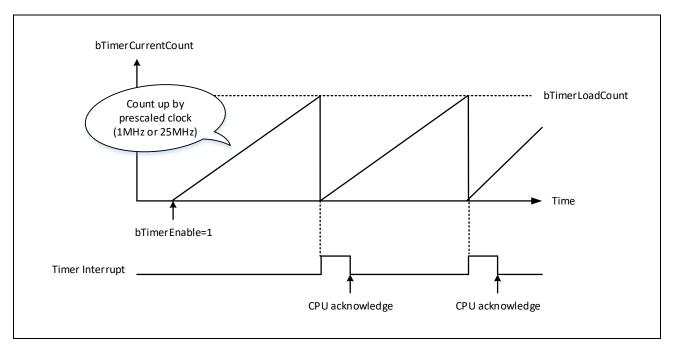

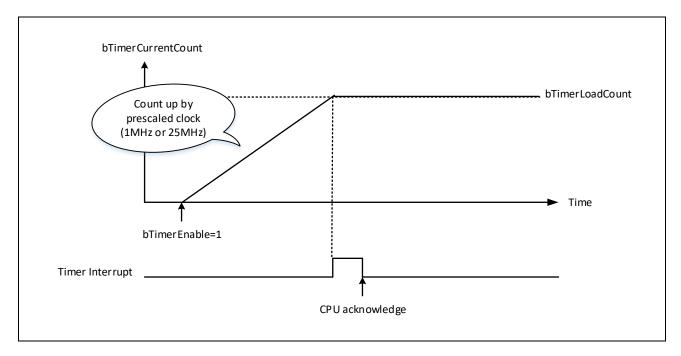

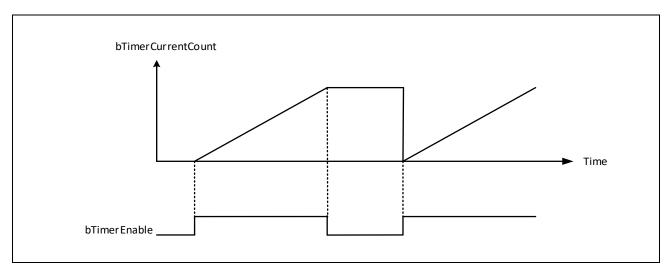

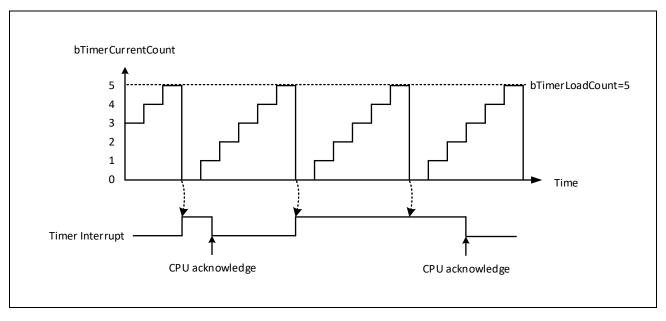

| 5.5     | Oper           | ation          |                                                                                   | 256 |

|         | 5.5.1          | Presca         | aler Counter                                                                      | 256 |

|         | 5.5.2          | Counte         | er 16 or 32 Bits                                                                  | 256 |

|         | 5.5.3          | Interru        | ptionption                                                                        | 259 |

|         | 5.5.4          | DMA C          | Control                                                                           | 260 |

| 5.6     | Usag           | je Notes       |                                                                                   | 261 |

| Section | n 6 CA         | .NI            |                                                                                   | 262 |

| 6.1     |                |                |                                                                                   |     |

| 6.2     |                |                | ces                                                                               |     |

| 6.3     | ŭ              |                |                                                                                   |     |

| 0.3     | _              | -              | )                                                                                 |     |

|         | 6.3.1<br>6.3.2 | _              | er Map (CAN2)                                                                     |     |

| 6.4     |                | •              | er Map (CAN2)                                                                     |     |

| 6.4     | _              |                | cription                                                                          |     |

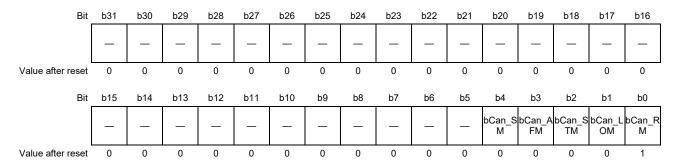

|         | 6.4.1          | _              | MOD — Configuration Mode Register                                                 |     |

|         | 6.4.2          | rcan_0         | CMR — Command Register                                                            | ∠09 |

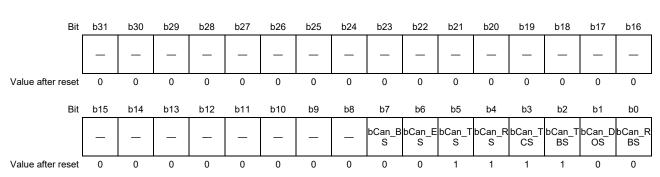

|     | 6.4.3  | rCan_SR — Controller Status Register                           | 271 |

|-----|--------|----------------------------------------------------------------|-----|

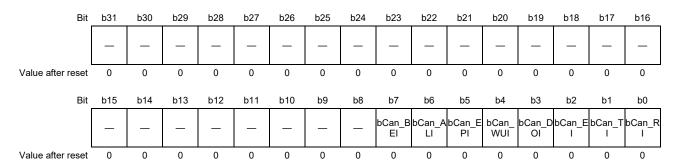

|     | 6.4.4  | rCan_IR — Interrupt Register                                   | 273 |

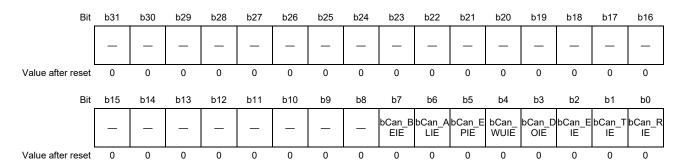

|     | 6.4.5  | rCan_IER — Interrupt Event Register                            | 275 |

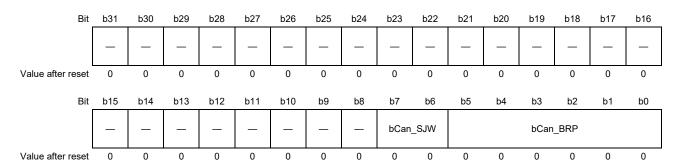

|     | 6.4.6  | rCan_BTR0 — Bus Timing Register 0                              | 276 |

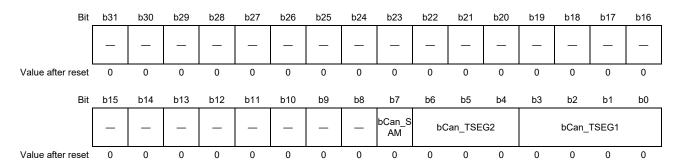

|     | 6.4.7  | rCan_BTR1 — Bus Timing Register 1                              |     |

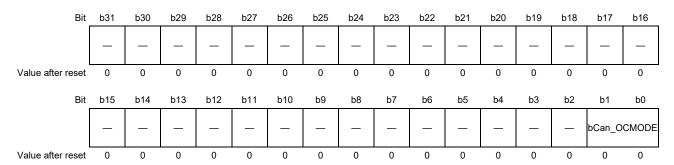

|     | 6.4.8  | rCan OCR — Output Control Register                             | 278 |

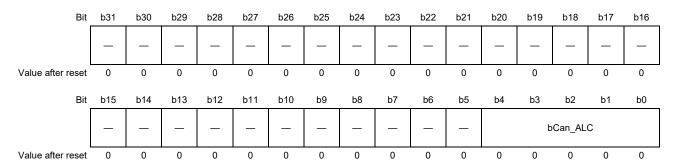

|     | 6.4.9  | rCan_ALC — Arbitration Lost Capture Register                   | 279 |

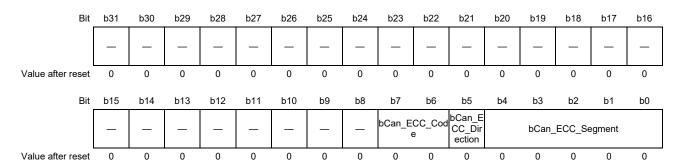

|     | 6.4.10 | rCan_ECC — Error Code Capture Register                         |     |

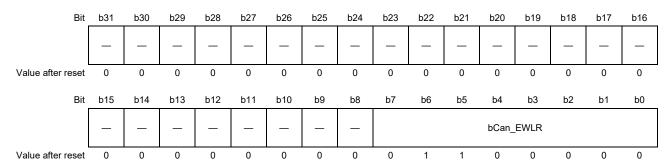

|     | 6.4.11 | rCan_EWLR — Error Warning Limit Register                       |     |

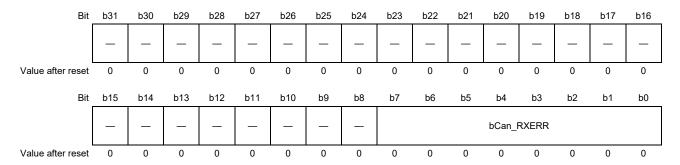

|     | 6.4.12 | rCan_RXERR — Receive Error Counter Register                    |     |

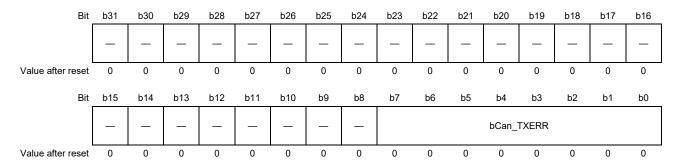

|     | 6.4.13 | rCan_TXERR — Transmit Error Counter Register                   |     |

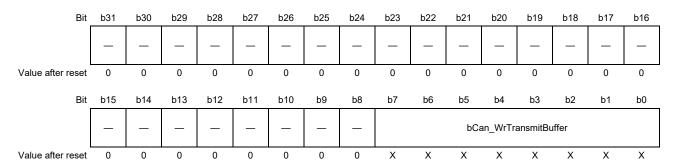

|     | 6.4.14 | rCan_WrTransmitBuffer — Write Transmit Buffer Register         | 286 |

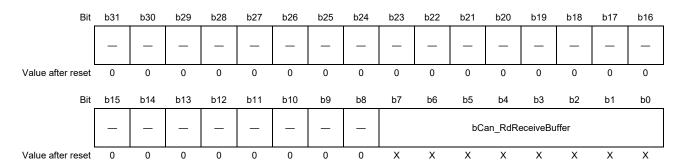

|     | 6.4.15 | rCan_RdReceiveBuffer — Read Receive Buffer Register            | 287 |

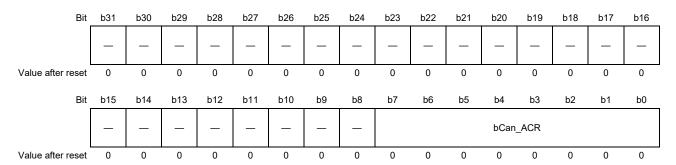

|     | 6.4.16 | rCan_ACR[n] — Acceptance Code Filter [n] Register (n = 03)     | 288 |

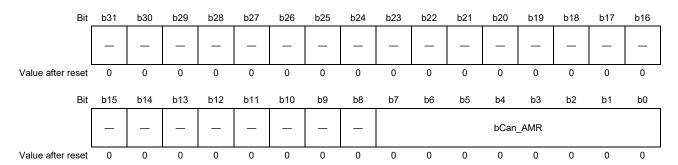

|     | 6.4.17 | rCan_AMR[n] — Acceptance Mask Filter [n] Register (n = 03)     | 289 |

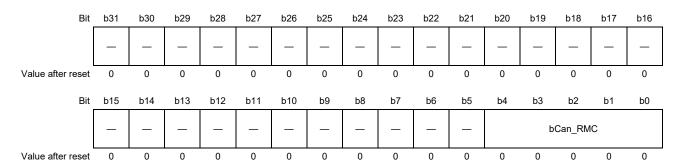

|     | 6.4.18 | rCan_RMC — Receive Message Counter Register                    | 290 |

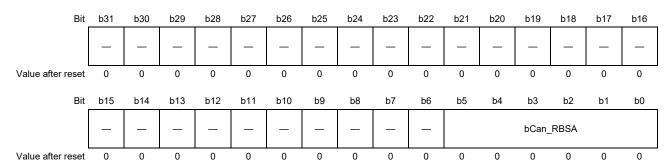

|     | 6.4.19 | rCan_RBSA — Receive Buffer Start Address Register              | 291 |

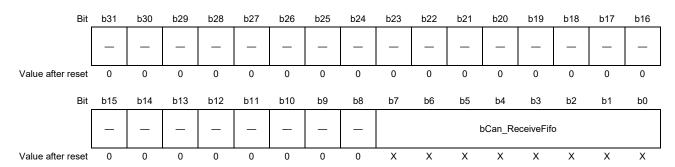

|     | 6.4.20 | rCan_ReceiveFifo — Receive FIFO Register                       | 292 |

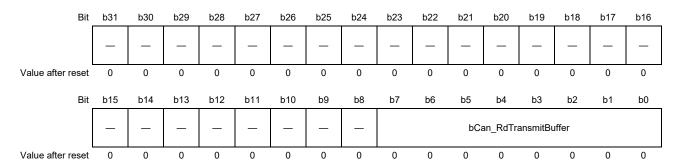

|     | 6.4.21 | rCan_RdTransmitBuffer — Read Transmit Buffer Register          | 293 |

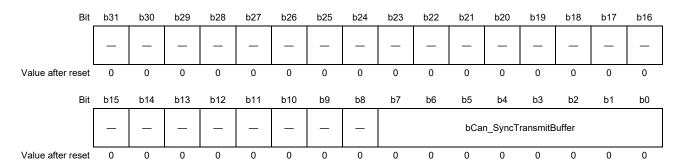

|     | 6.4.22 | rCan_SyncTransmitBuffer — Sync Frame Transmit Buffer Register  | 294 |

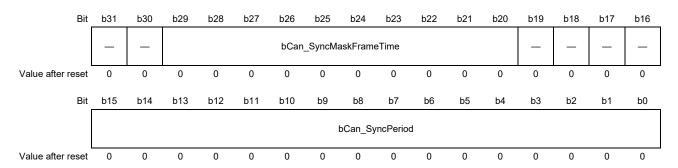

|     | 6.4.23 | rCan_SyncPeriod — Time Window Sync Frame Transmission Register | 295 |

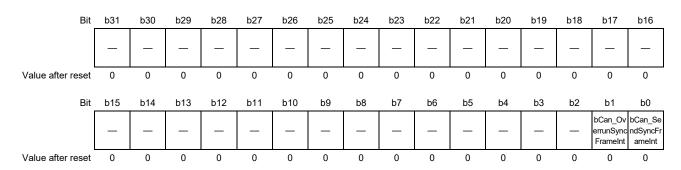

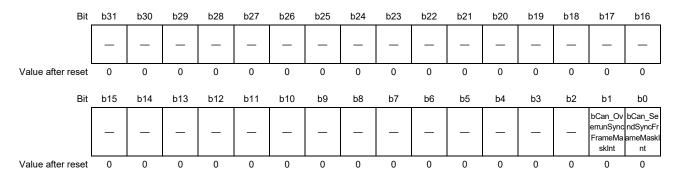

|     | 6.4.24 | rCan_SyncStatusInt — Sync Frame Interrupt Status Register      | 297 |

|     | 6.4.25 | rCan_SyncMaskInt — Sync Frame Mask Interrupt Register          | 299 |

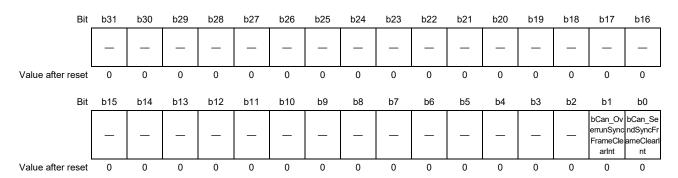

|     | 6.4.26 | rCan_SyncClearInt — Sync Frame Clear Interrupt Register        | 300 |

|     | 6.4.27 | rCan_SyncStatus — Sync Frame Status Configuration Register     | 301 |

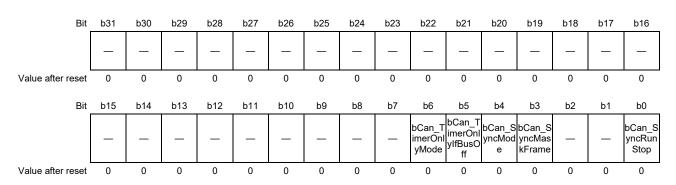

|     | 6.4.28 | rCan_SyncClearSetRunStop — Sync Frame Generation Register      | 303 |

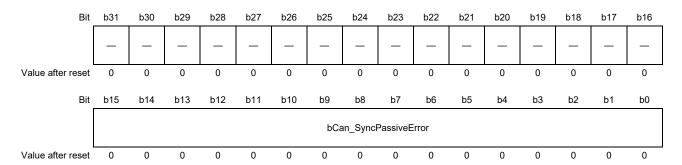

|     | 6.4.29 | rCan_SyncPassiveError — Sync Passive Error Detection Register  | 304 |

| 6.5 | Opera  | ation                                                          | 305 |

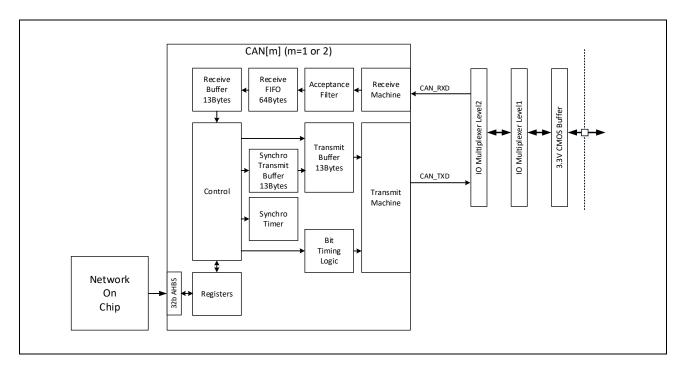

|     | 6.5.1  | Main Features Description                                      | 305 |

|     | 6.5.2  | Operation Mode                                                 | 305 |

|     | 6.5.3  | Transmission                                                   | 306 |

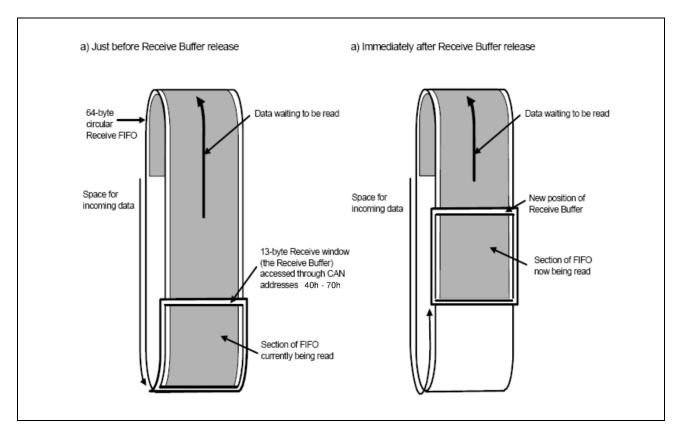

|     | 6.5.4  | Reception                                                      | 307 |

|     | 6.5.5  | Self Reception                                                 | 308 |

|     | 6.5.6  | Sleep Mode                                                     | 309 |

|     | 6.5.7  | Acceptance Filtering                                           | 309 |

|     | 6.5.8  | Interrupts Generation                                          | 312 |

|     |        | .8.1 Receive Interrupts                                        |     |

|     |        | .8.2 Transmit Interrupts                                       |     |

|     |        | .8.3 Error Warning Interrupts                                  |     |

|     |        | .8.5 Wakeup Interrupts                                         |     |

|     | 6.5.   | .8.6 Error Passive Interrupts                                  |     |

|     |        | 8.7 Arbitration Loss Interrupts                                |     |

|     | 6.5.   | .8.8 Bus Error Interrupts                                      | 315 |

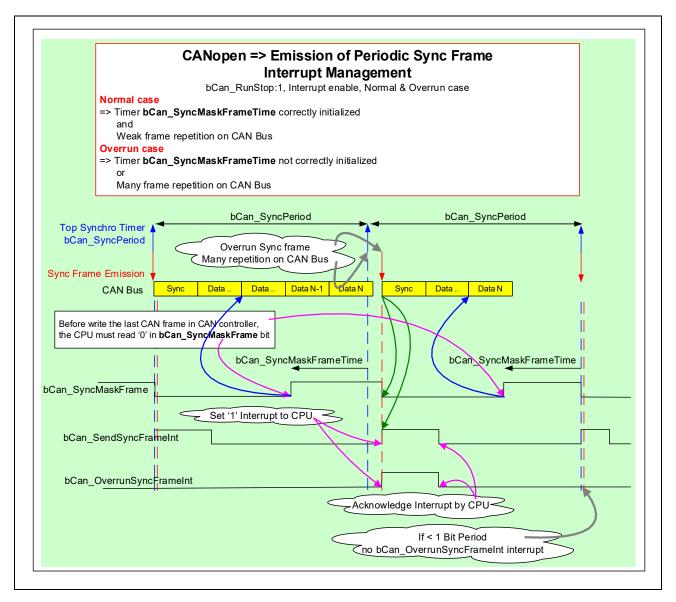

|         |         | 5.8.9              | Transmit "Sync frame" Interrupts                                                 |     |

|---------|---------|--------------------|----------------------------------------------------------------------------------|-----|

|         | 6.5     | 5.8.10             | Transmit Overrun "Sync frame" Interrupts                                         | 316 |

|         | 6.5.9   | Bus A              | Arbitration                                                                      | 317 |

|         | 6.5.10  | Error              | Handling                                                                         | 318 |

|         | 6.5.11  | Trans              | mit Buffer Layout                                                                | 320 |

|         | 6.5     | 5.11.1             | Descriptor Field of the Transmit Buffer                                          | 321 |

|         |         | 5.11.2             | Frame Format (FF)                                                                | 321 |

|         |         | 5.11.3             | Remote Request (RTR)                                                             |     |

|         |         | 5.11.4             | Data Length Code (DLC)                                                           |     |

|         |         | 5.11.5             | Identifier (ID)                                                                  |     |

|         |         | 5.11.6             | Data Field                                                                       |     |

|         | 6.5.12  |                    | ive Buffer Layout                                                                |     |

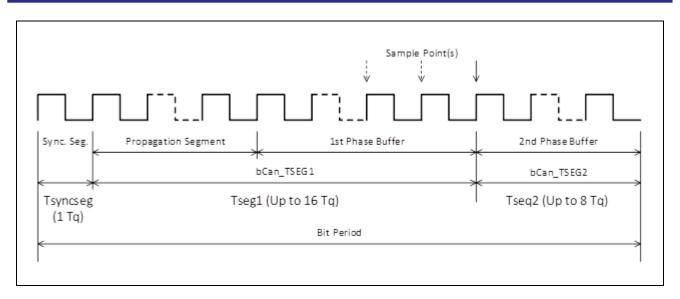

|         | 6.5.13  | Bit Pe             | eriod and Bus Timing Parameters                                                  | 324 |

|         | 6.5.14  | Reset              | t Mode                                                                           | 327 |

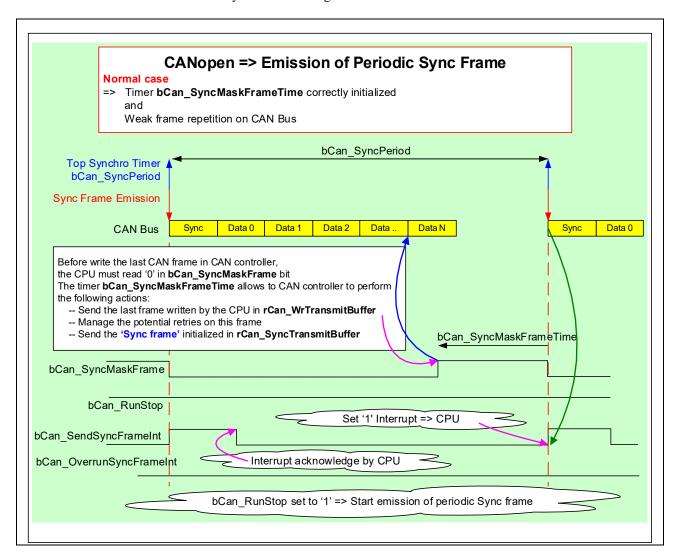

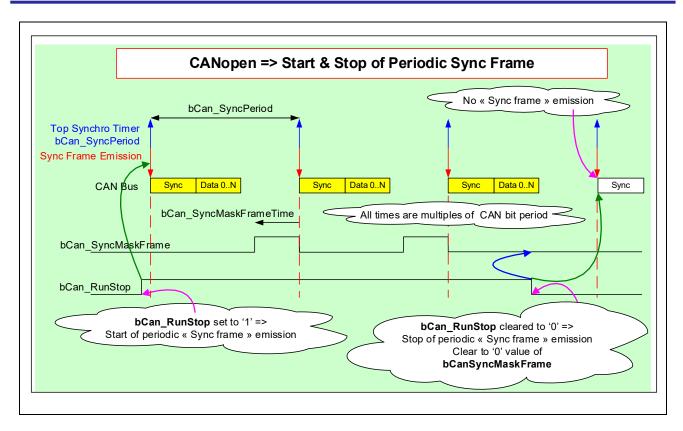

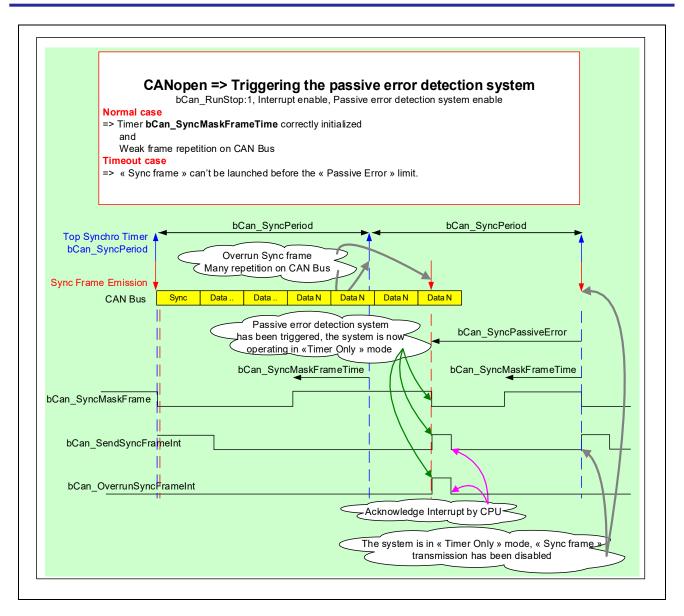

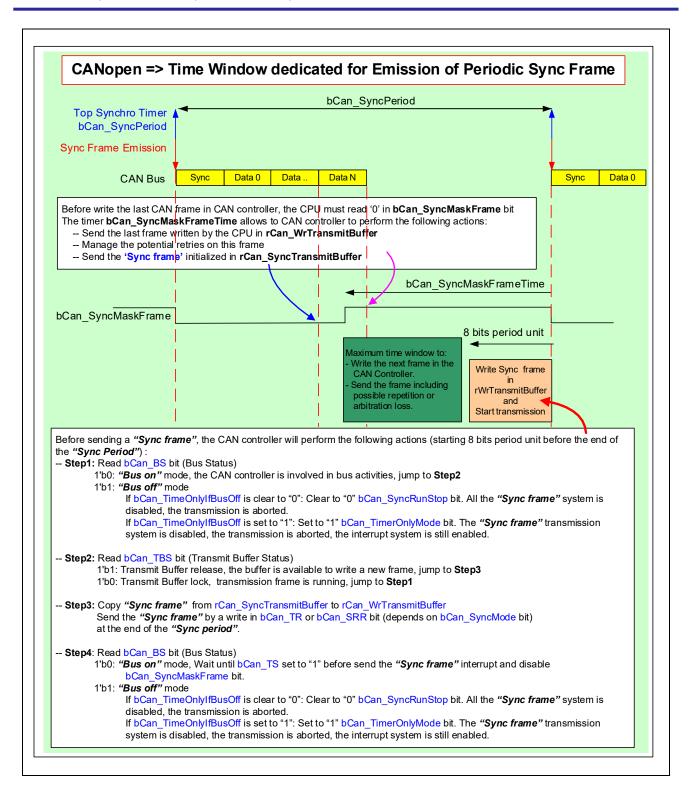

|         | 6.5.15  | Synch              | nronization Frame                                                                | 328 |

|         | 6.5     | 5.15.1             | CANopen Synchronous Frame Configuration                                          | 328 |

|         | 6.5     | 5.15.2             | CANopen Emission of "Sync Frame"                                                 | 333 |

|         | 6.5.16  | Differ             | ence between CAN Controllers and Reference Philips SJA1000 Devices               | 336 |

| 6.6     | Spec    | cial Noti          | ce                                                                               | 337 |

|         | •       |                    |                                                                                  |     |

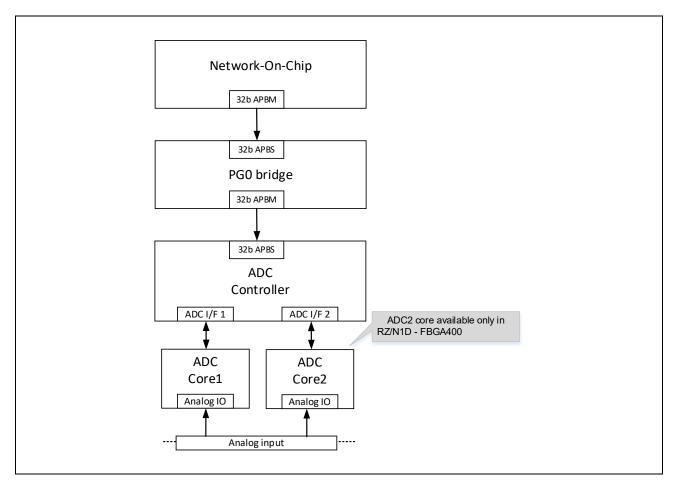

| Section | on 7 AD | C Cor              | ntroller and 12bit A/D Converters                                                | 338 |

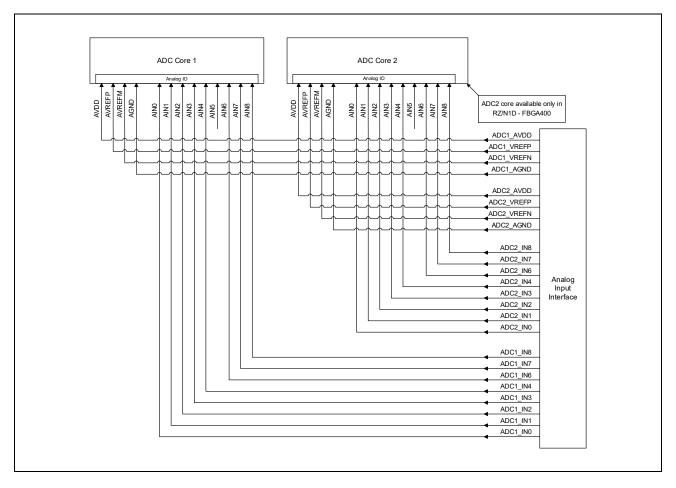

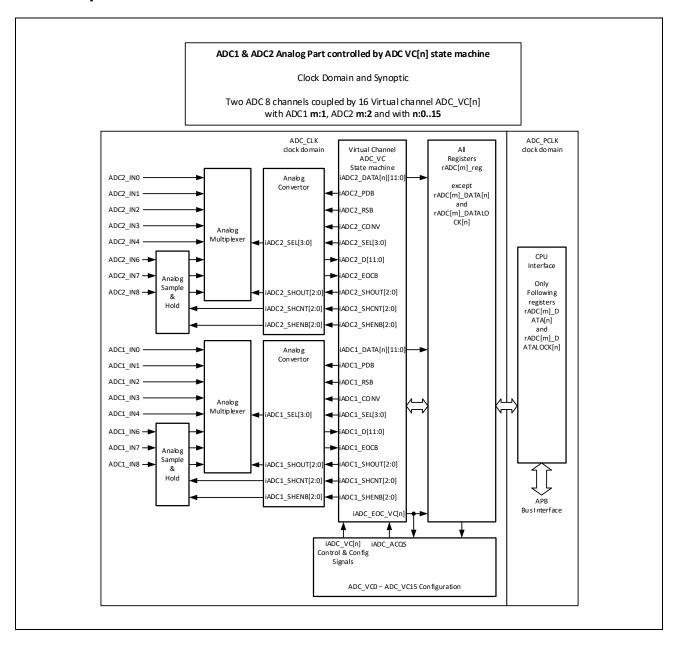

| 7.1     | Over    | view               |                                                                                  | 338 |

|         | 7.1.1   |                    | og Buffer                                                                        |     |

|         |         |                    |                                                                                  |     |

| 7.2     | _       |                    | aces                                                                             |     |

| 7.3     | Regi    | ster Ma            | p                                                                                | 342 |

|         | 7.3.1   | Regis              | ster Map ADC1                                                                    | 342 |

|         | 7.3.2   | Regis              | ster Map ADC2                                                                    | 343 |

| 7.4     | Regi    | ster Des           | scription                                                                        | 344 |

|         | 7.4.1   |                    | ster Description ADC1                                                            |     |

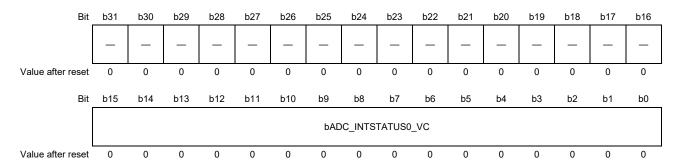

|         |         | •                  | rADC INTSTATUS0 — Interrupt Status Before Masking                                |     |

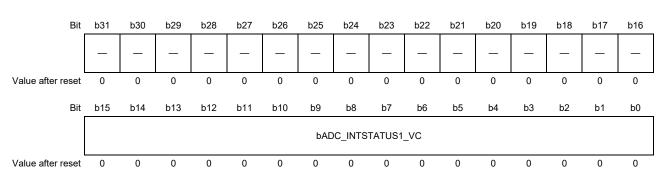

|         |         | 4.1.2              | rADC_INTSTATUS1 — Interrupt Status After Masking                                 |     |

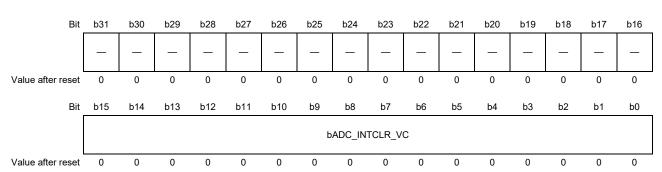

|         |         | 4.1.3              | rADC_INTCLR — Clear Interrupt                                                    |     |

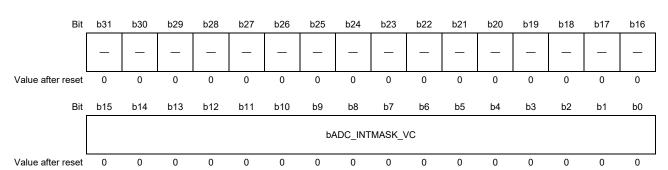

|         | 7.4     | 4.1.4              | rADC_INTMASK — Mask Interrupt                                                    |     |

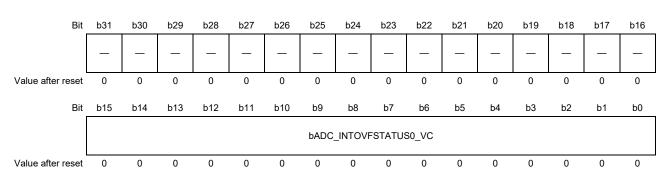

|         | 7.4     | 4.1.5              | rADC_INTOVFSTATUS0 — Interrupt Overflow Before Masking                           | 348 |

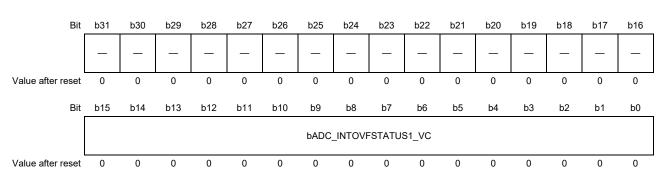

|         | 7.4     | 4.1.6              | rADC_INTOVFSTATUS1 — Interrupt Overflow After Masking                            | 349 |

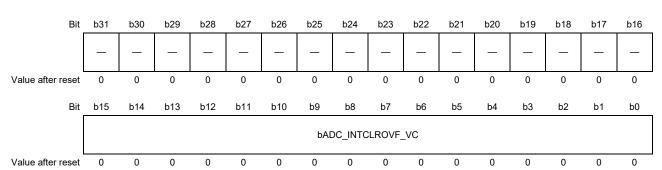

|         |         | 1.1.7              | rADC_INTCLROVF — Clear Interrupt Overflow                                        |     |

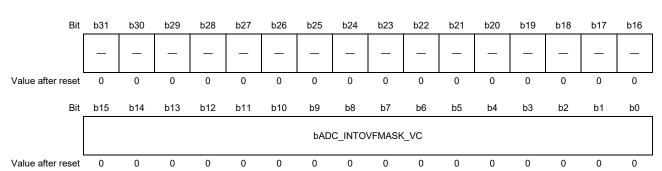

|         |         | 4.1.8              | rADC_INTOVFMASK — Mask Interrupt Overflow                                        |     |

|         |         | 4.1.9              | rADC_PENDING — Start of Operation Pending                                        |     |

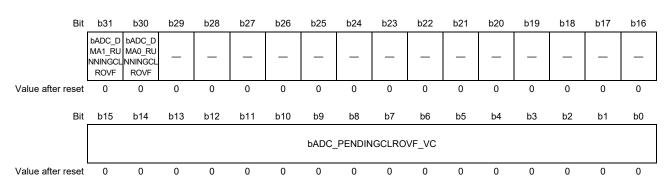

|         |         | 4.1.10             | rADC_PENDINGOVF — Start of Operation Pending Overflow                            |     |

|         |         | 4.1.11<br>4.1.12   | rADC_PENDINGCLROVF — Clear Start of Operation OverflowrADC_CONTROL — ADC Control |     |

|         |         | +. 1. 12<br>4.1.13 | rADC_FORCE — ADC Request                                                         |     |

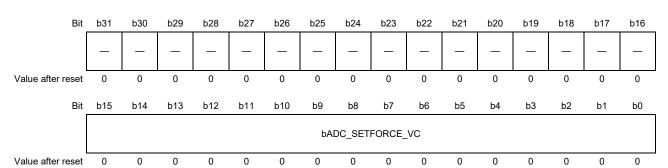

|         |         | 4.1.13<br>4.1.14   | rADC_SETFORCE — Set ADC Request                                                  |     |

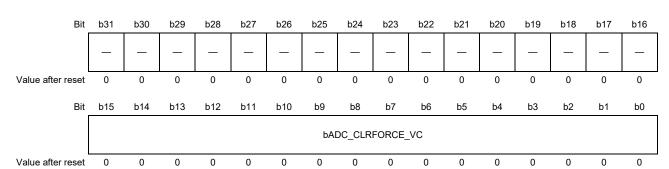

|         |         | 4.1.1 <del>5</del> | rADC_CLRFORCE — Clear ADC Request                                                |     |

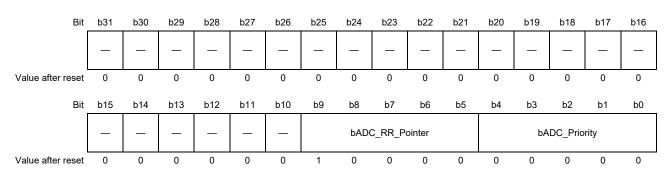

|         |         | 4.1.16             | rADC_PRIORITY — ADC Priority Mode                                                |     |

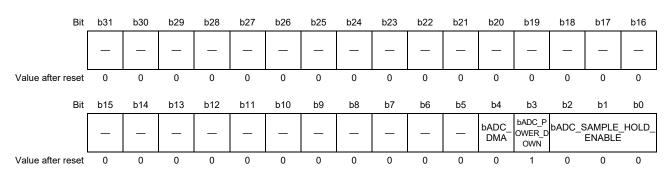

|         |         | 4.1.17             | rADC_CONFIG — ADC Configuration                                                  |     |

|         |         | 4.1.18             | rADC_ACQS — ADC Control Sample and Hold                                          | 364 |

|         | 7.4     | 4.1.19             | rADC_MASKLOCK[n] — Mask Data Locked [n] (n = 03)                                 | 365 |

|         |         |                    |                                                                                  |     |

|        |         | .1.20 rADC_VC[n] — ADC Control Register for Virtual Channel [n] (n = 015)                                                                                    |     |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|        |         | .1.21 rADC1_DATA[n] — ADC1 Conversion Data of Virtual Channel [n] (n = 015)                                                                                  |     |

|        |         | .1.22 rADC1_DATALOCK[n] — ADC1 DataLock[n] Register (n = 015)                                                                                                |     |

|        | 7.4.2   | Register Description ADC2                                                                                                                                    |     |

|        |         | .2.1 rADC2_DATA[n] — ADC2 Conversion Data of Virtual Channel [n] (n = 015)  rADC2_DATALOCK[n] — ADC2 DataLock[n] Register (n = 015)                          |     |

| 7.5    |         | ation                                                                                                                                                        |     |

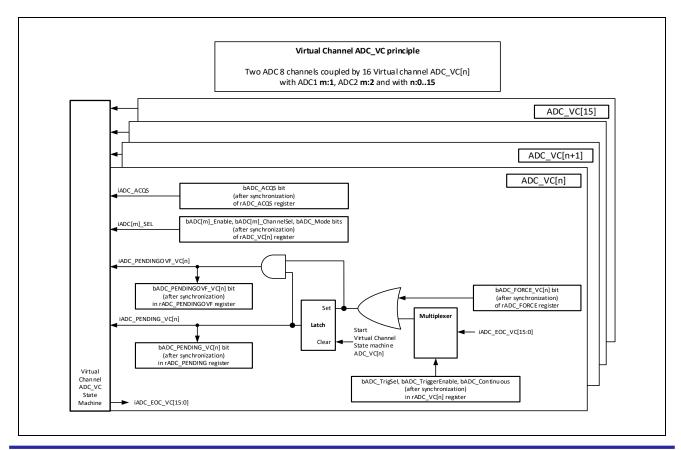

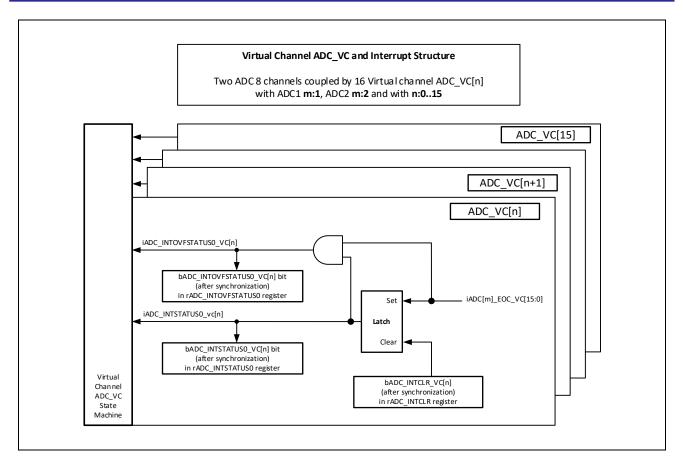

| 1.5    | 7.5.1   | Virtual Channel ADC VC Principle Operation                                                                                                                   |     |

|        |         |                                                                                                                                                              |     |

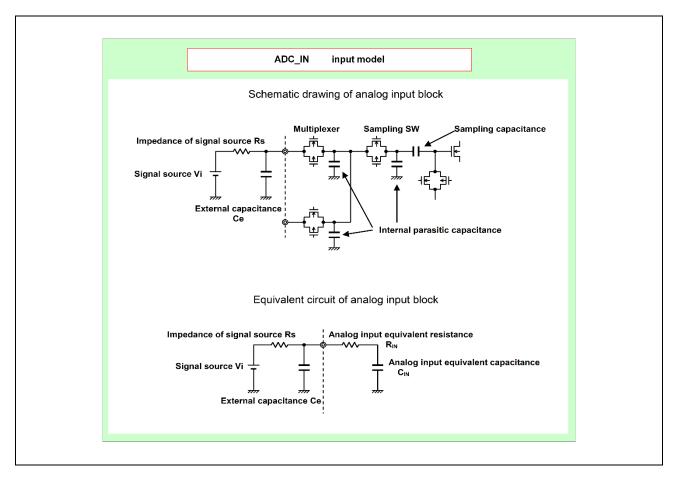

|        | 7.5.2   | Electric ADC Model and Acquisition Sample                                                                                                                    |     |

|        | 7.5.3   | Trigger Selection and Event Management                                                                                                                       |     |

|        | 7.5.4   | Physical Channel Selection                                                                                                                                   |     |

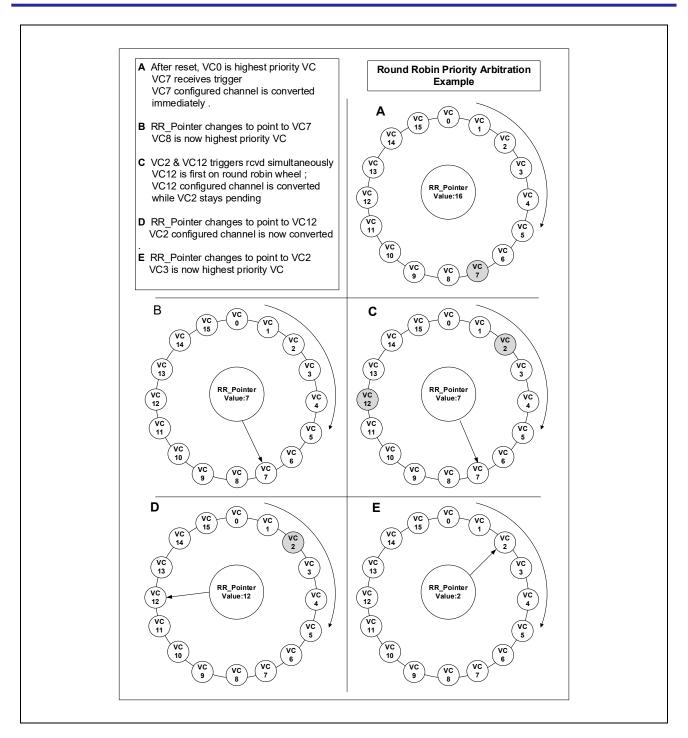

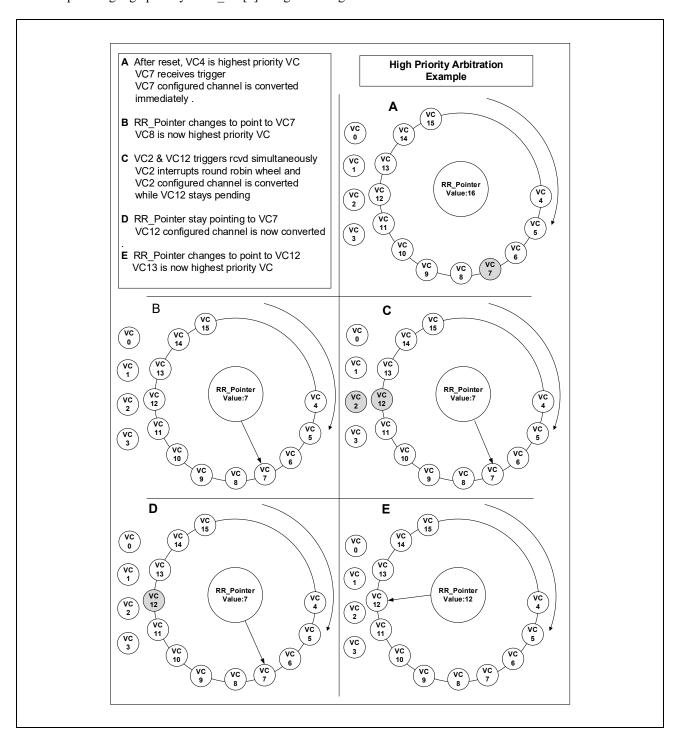

|        | 7.5.5   | ADC Operation Priority                                                                                                                                       |     |

|        | 7.5.6   | Simultaneous Sample and Hold                                                                                                                                 |     |

|        | 7.5.7   | End of Command (EOC) and Interrupt Operation                                                                                                                 |     |

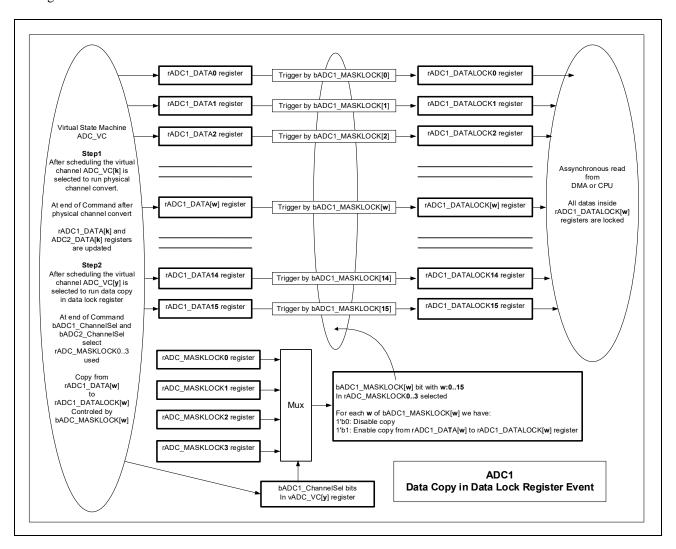

|        | 7.5.8   | Data Copy in Data Lock Register                                                                                                                              |     |

|        | 7.5.9   | Timing                                                                                                                                                       |     |

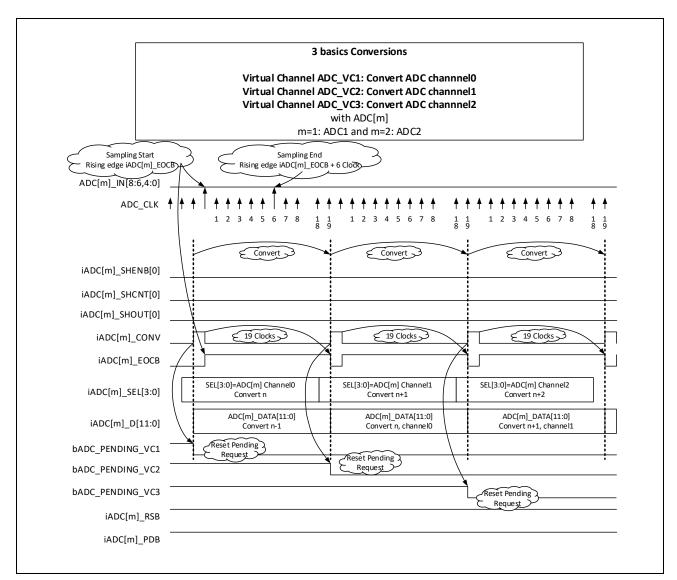

|        |         | .9.1 Basic A/D Conversion on 3 Channels                                                                                                                      |     |

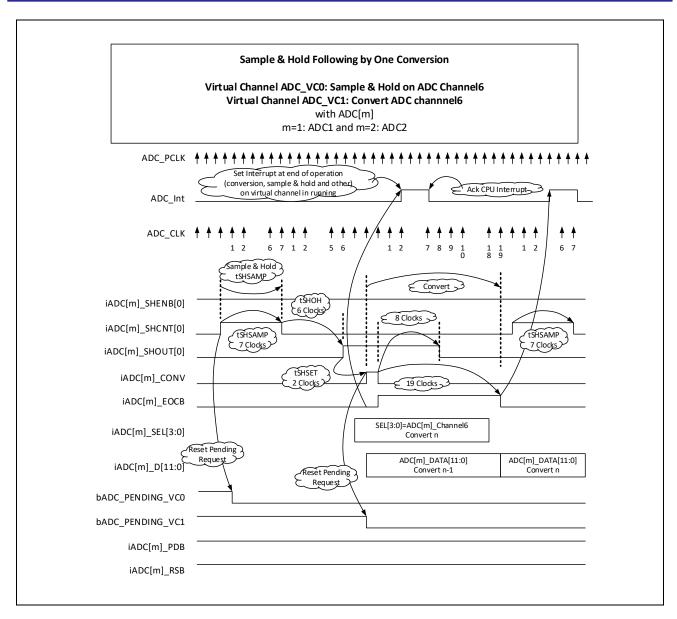

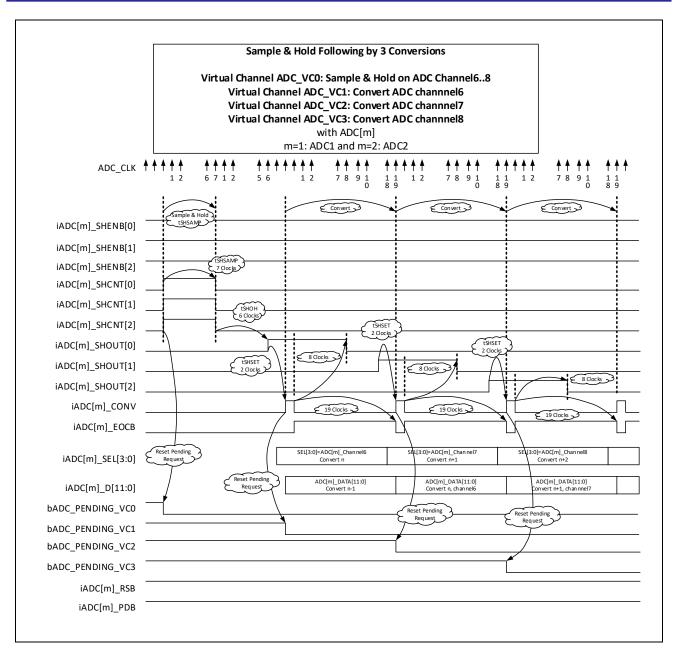

|        | _       | <ul><li>.9.2 Sample &amp; Hold following by A/D Conversion on One Channel</li><li>.9.3 Sample &amp; Hold following by A/D Conversion on 3 Channels</li></ul> |     |

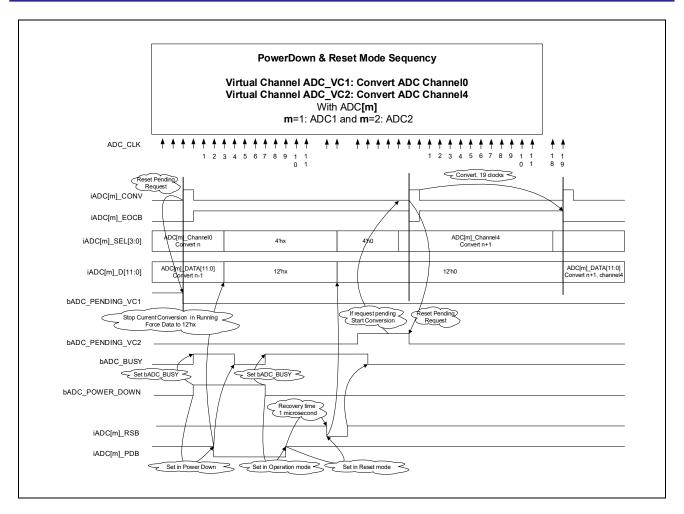

|        |         | .9.4 Power Down                                                                                                                                              |     |

|        |         | .9.5 A/D Conversion Rate                                                                                                                                     |     |

|        | 7.5.10  | DMA control                                                                                                                                                  |     |

|        | 7.5     | .10.1 Overview on DMA Operation                                                                                                                              |     |

| 7.6    | Usag    | e Notes                                                                                                                                                      | 402 |

|        | 7.6.1   | Restriction                                                                                                                                                  | 402 |

| Sectio | n 8 I C | D Controller                                                                                                                                                 | 403 |

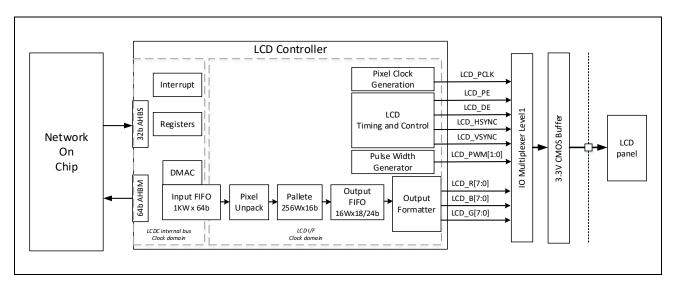

| 8.1    |         | /iew                                                                                                                                                         |     |

|        |         |                                                                                                                                                              |     |

| 8.2    | Ü       | ıl Interfaces                                                                                                                                                |     |

| 8.3    | Regis   | ster Map                                                                                                                                                     | 406 |

|        | 8.3.1   | Coding Palette (Palette Registers) Map                                                                                                                       | 406 |

| 8.4    | Regis   | ster Description                                                                                                                                             | 407 |

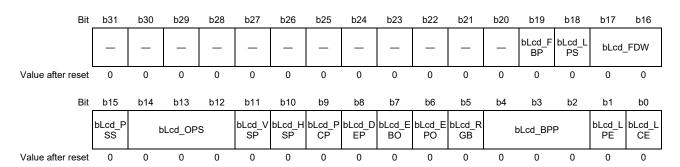

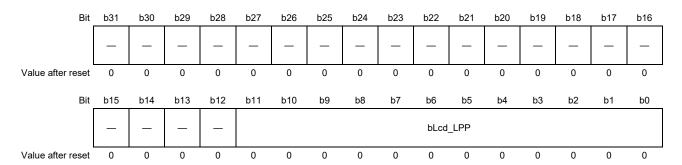

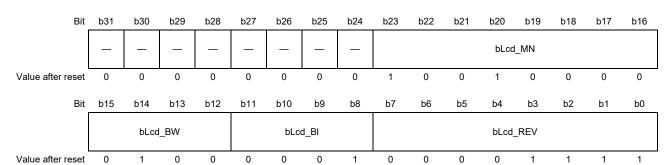

|        | 8.4.1   | rLcd_CR1 — Control Register 1                                                                                                                                | 407 |

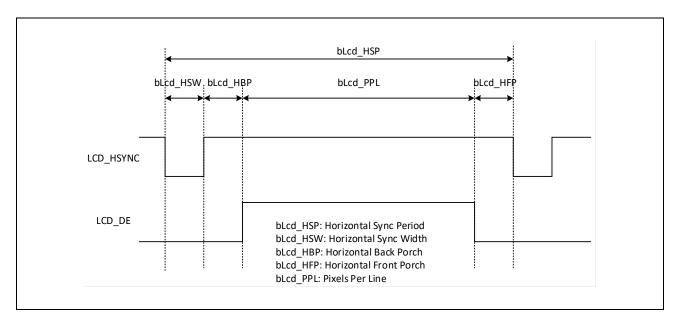

|        | 8.4.2   | rLcd_HTR — Horizontal Timing Register                                                                                                                        | 410 |

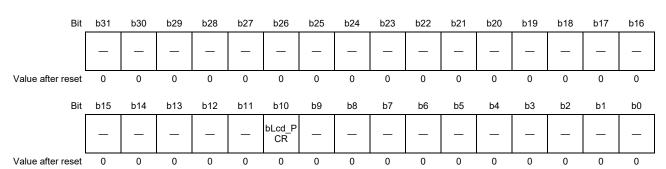

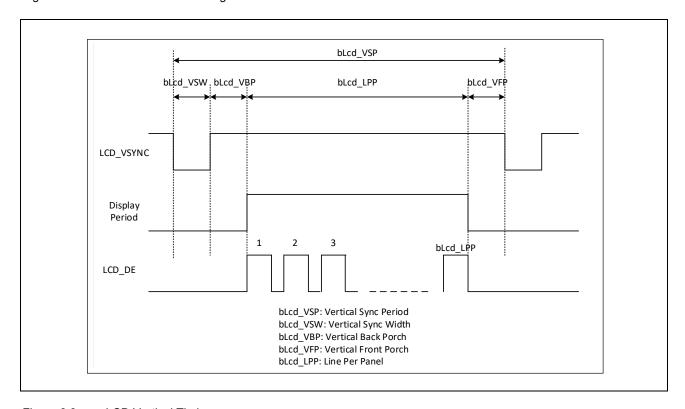

|        | 8.4.3   | rLcd_VTR1 — Vertical1 Timing Register                                                                                                                        | 411 |

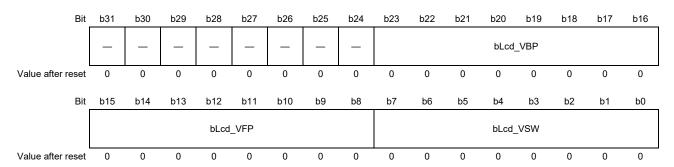

|        | 8.4.4   | rLcd_VTR2 — Vertical2 Timing Register                                                                                                                        | 412 |

|        | 8.4.5   | rLcd_PCTR — Pixel Clock Timing Register                                                                                                                      | 413 |

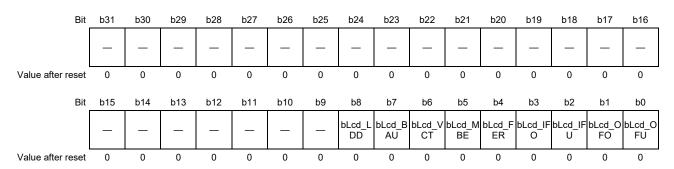

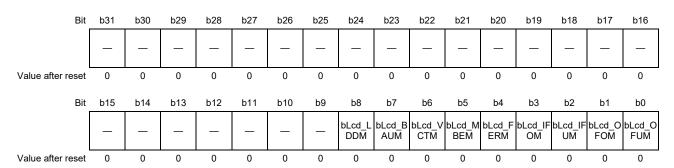

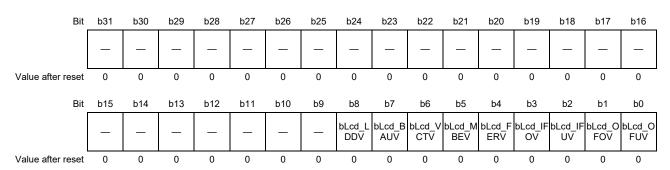

|        | 8.4.6   | rLcd_ISR — Interrupt Status Register Before Masking                                                                                                          | 414 |

|        | 8.4.7   | rLcd_IMR — Interrupt Mask Register                                                                                                                           |     |

|        | 8.4.8   | rLcd_IVR — Interrupt Status Register After Masking                                                                                                           |     |

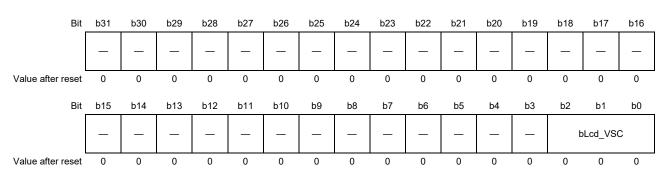

|        | 8.4.9   | rLcd_ISCR — Interrupt Scan Compare Register                                                                                                                  |     |

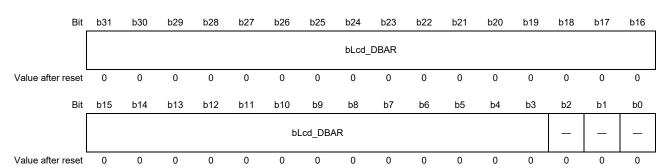

|        | 8.4.10  | rLcd_DBAR — DMA Start Base Address of Frame Buffer Memory                                                                                                    |     |

|        | 8.4.11  | rLcd_DCAR — DMA Current Base Address on Going                                                                                                                |     |

|        | 8.4.12  | rLcd_DEAR — DMA End Address                                                                                                                                  |     |

|        | J.T. 12 | TEG_DEATC DIVIA ETIT AUGUSS                                                                                                                                  | 722 |

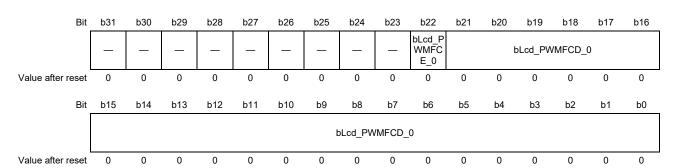

|         | 8.4.13  | rLcd_PWMFR_0 — PWM0 Frequency Register                            | 423 |

|---------|---------|-------------------------------------------------------------------|-----|

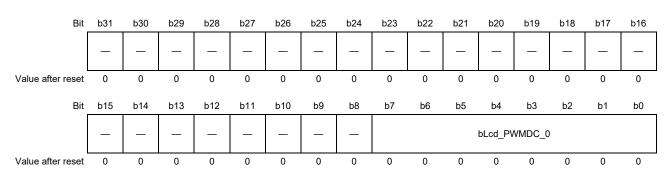

|         | 8.4.14  | rLcd_PWMDCR_0 — PWM0 Duty Cycle Register                          | 424 |

|         | 8.4.15  | rLcd_HVTER — Horizontal and Vertical Timing Extension Register    | 425 |

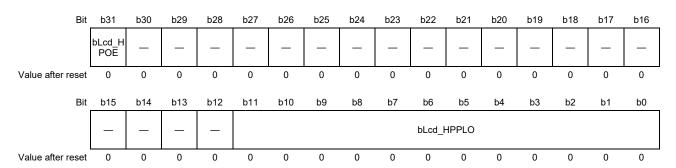

|         | 8.4.16  | rLcd_HPPLOR — Horizontal Pixels-Per-Line Override Control         | 426 |

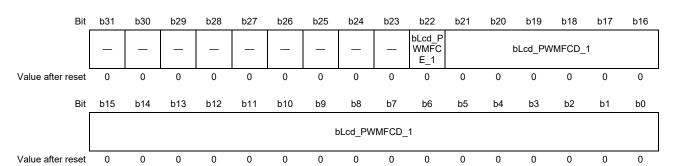

|         | 8.4.17  | rLcd_PWMFR_1 — PWM1 Frequency Register                            | 427 |

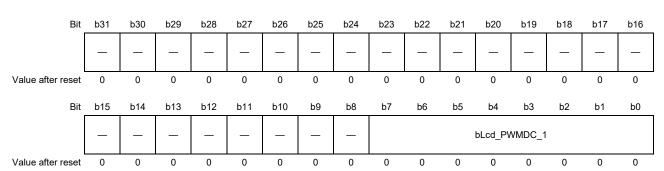

|         | 8.4.18  | rLcd_PWMDCR_1 — PWM1 Duty Cycle Register                          | 428 |

|         | 8.4.19  | rLcd_GPIOR — Blink Control                                        | 429 |

|         | 8.4.20  | rLcd_CIR — Core Identification Register                           | 430 |

|         | 8.4.21  | Coding Palette (Palette registers) Description                    | 431 |

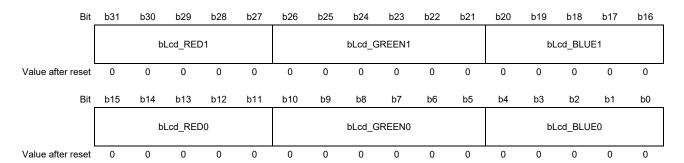

|         |         | .21.1 rLcd_PAL_RGB_555 — Coding Palette when RGB 5:5:5 Mode       |     |

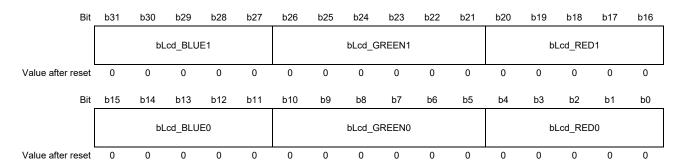

|         |         | .21.2 rLcd_PAL_RGB_565 — Coding Palette when RGB 5:6:5 Mode       |     |

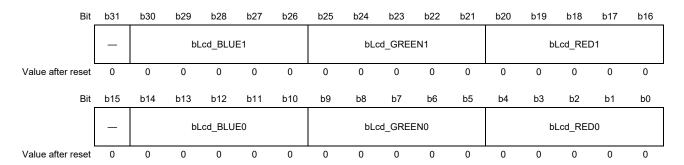

|         |         | .21.4 rLcd_PAL_BGR_565 — Coding Palette when BGR 5:6:5 Mode       |     |

| 8.5     |         | ation                                                             |     |

| 0.0     | 8.5.1   | Main Features Description                                         |     |

|         | 8.5.2   | Bandwidth Limitation                                              |     |

|         | 8.5.3   | Timing and Control                                                |     |

|         | 8.5.4   | DMA Controller and Memory Interface                               |     |

|         | 8.5.5   | Frame Buffer Organization                                         |     |

|         | 8.5.6   | Input FIFO                                                        |     |

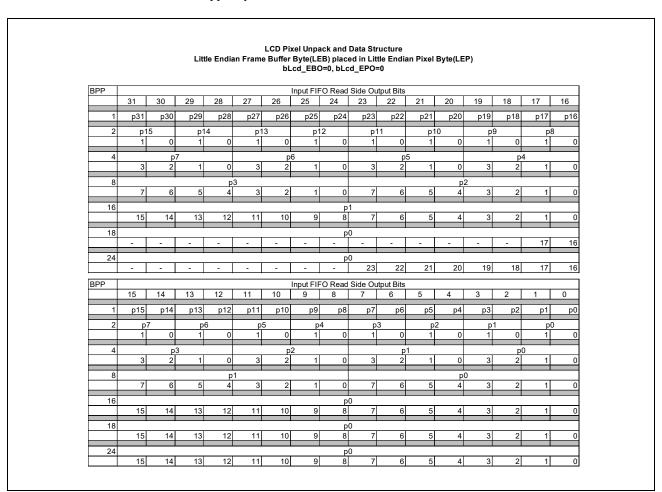

|         | 8.5.7   | Pixel Unpack                                                      |     |

|         | 8.5.8   | Palette Lookup Table                                              |     |

|         | 8.5.9   | Output FIFO and Formatter                                         |     |

|         | 8.5.10  | Initializing Configuration Registers                              | 446 |

|         | 8.5.11  | Interrupts                                                        |     |

|         | 8.5.12  | Power Sequencing                                                  | 447 |

|         | 8.5.13  | Frame Buffer 24 bpp Packed Word                                   | 448 |

|         | 8.5.14  | Pulse Width Modulation                                            | 449 |

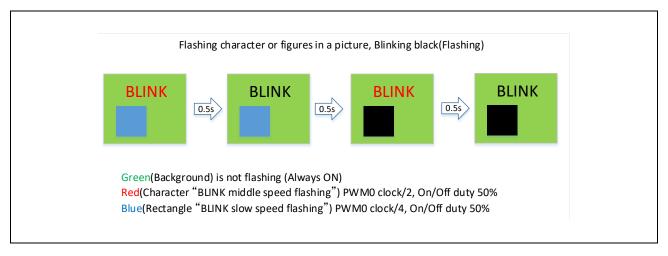

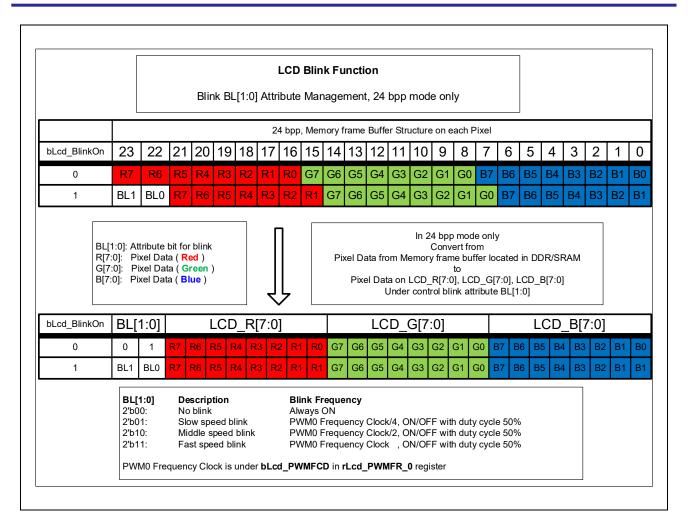

|         | 8.5.15  | Blink Function                                                    | 449 |

|         | 8.5.16  | Limitation                                                        | 451 |

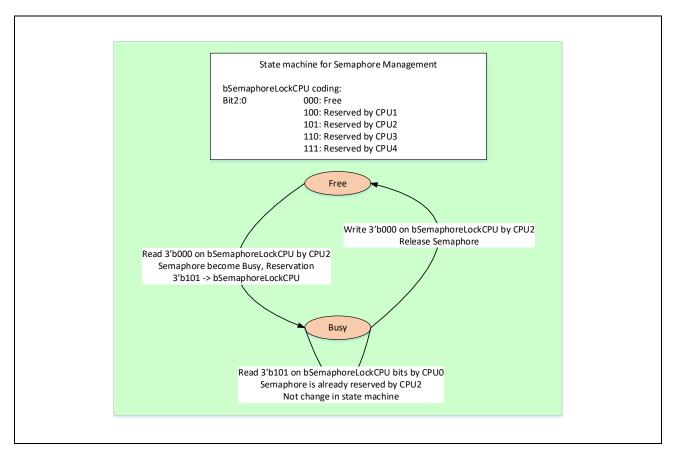

| Section | n 9 Sei | maphore                                                           | 452 |

| 9.1     | Over    | view                                                              | 452 |

| 9.2     | Signa   | al Interfaces                                                     | 452 |

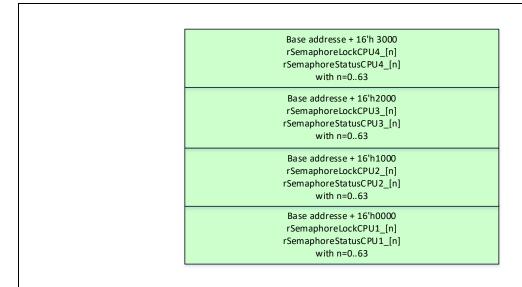

| 9.3     | Regis   | ster Map                                                          | 453 |

| 9.4     | ŭ       | ster Description                                                  |     |

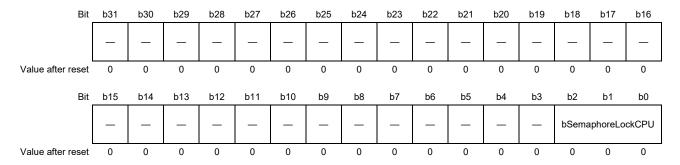

| 0       | 9.4.1   | rSemaphoreLockCPU[m] [n] — Semaphore Lock CPU[m] Register [n]     |     |

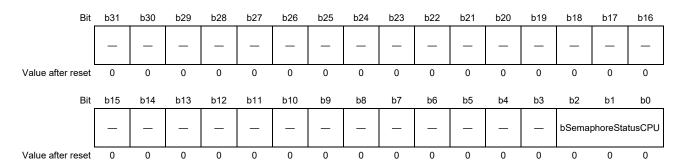

|         | 9.4.2   | rSemaphoreStatusCPU[m] [n] — Semaphore Status CPU[m] Register [n] |     |

| 9.5     |         | ation                                                             |     |

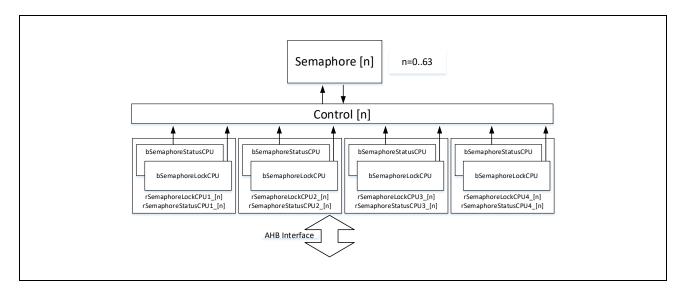

| 0.0     | 9.5.1   | Semaphore [n] (n = 063)                                           |     |

|         | 9.5.2   | CPU Identify and Address Decoding                                 |     |

| 9.6     |         | e Notes                                                           |     |

| 0.0     | 2549    |                                                                   |     |

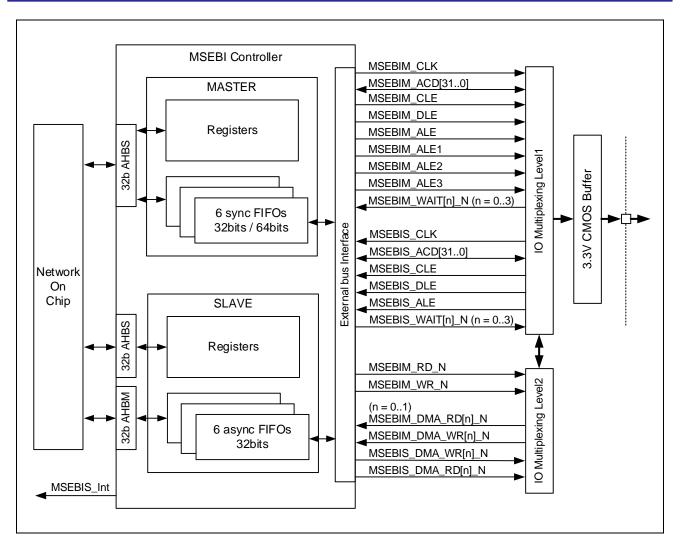

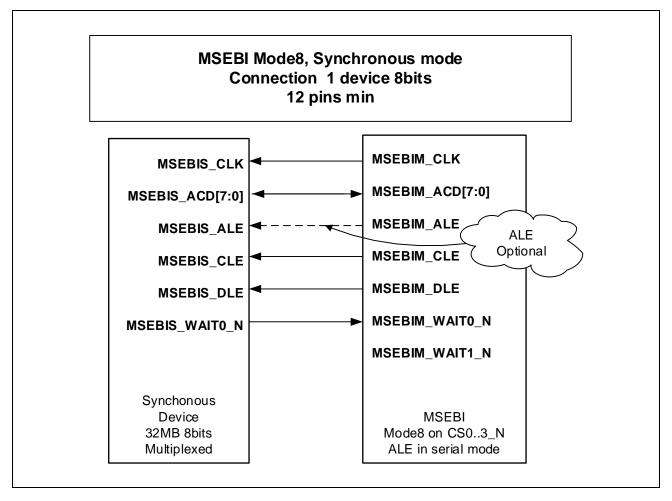

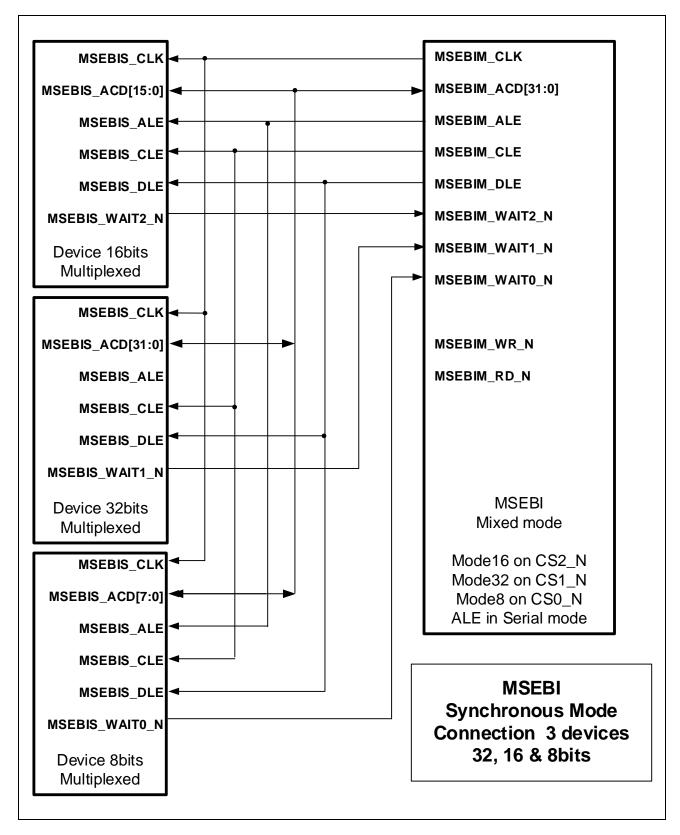

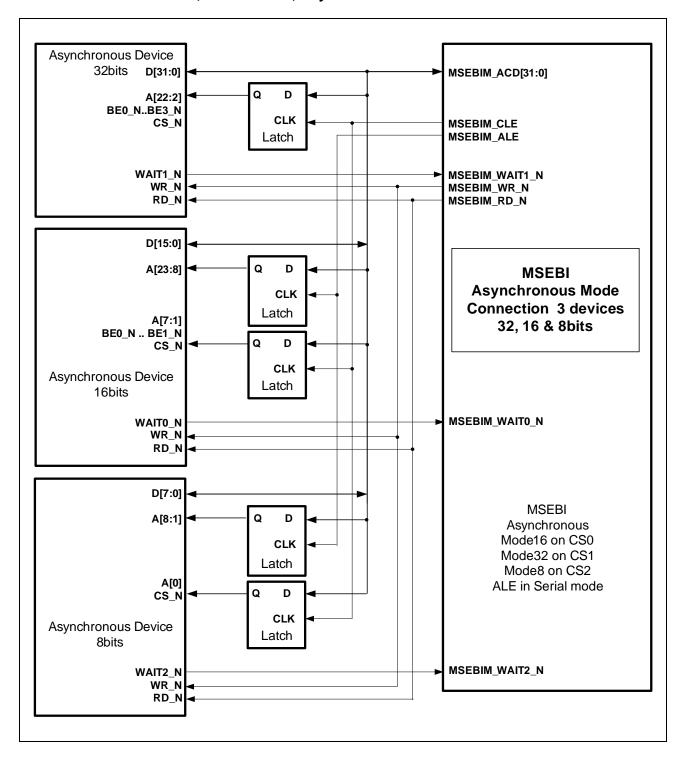

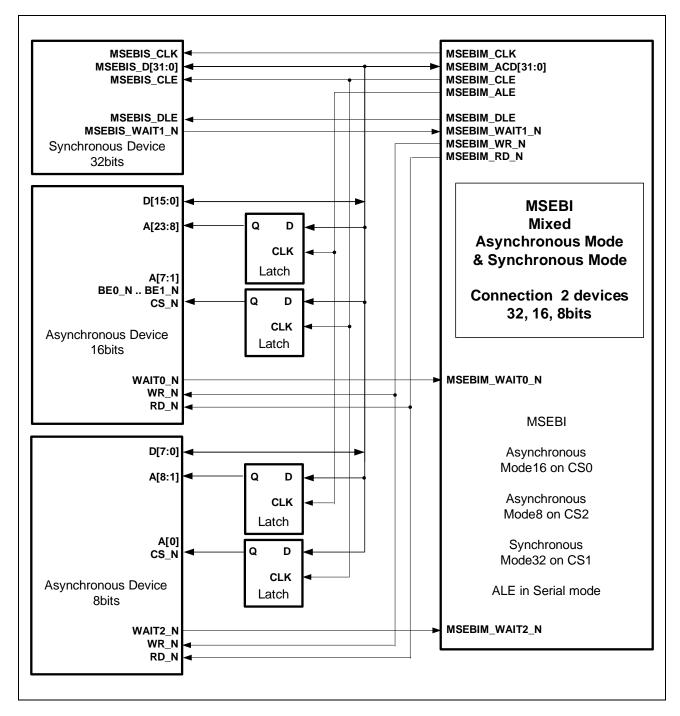

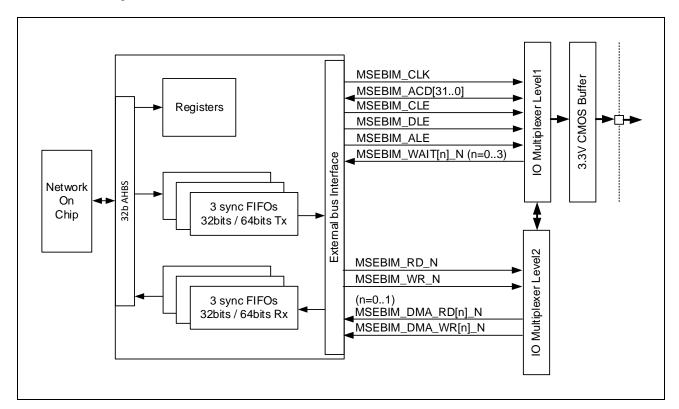

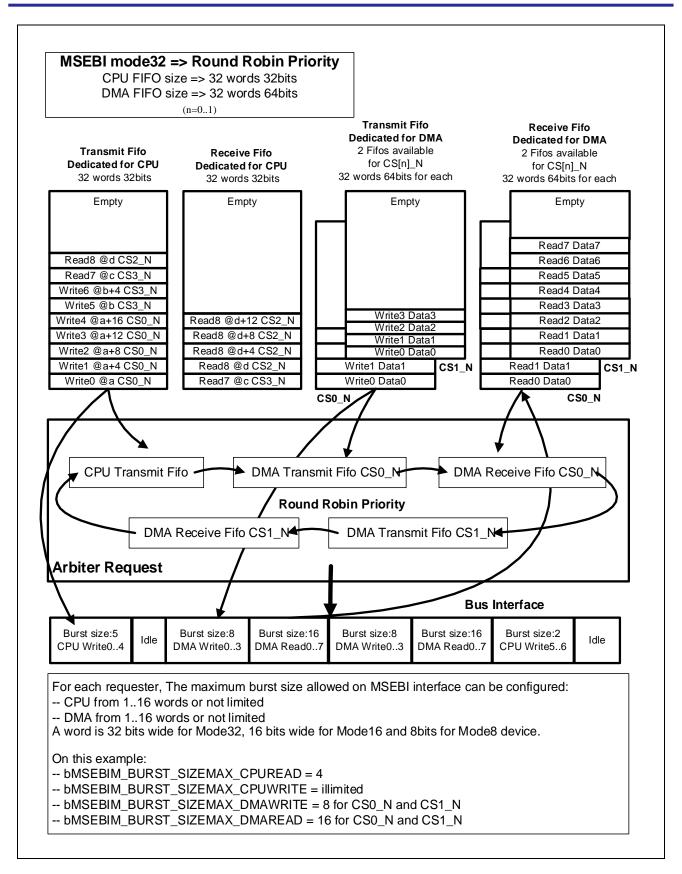

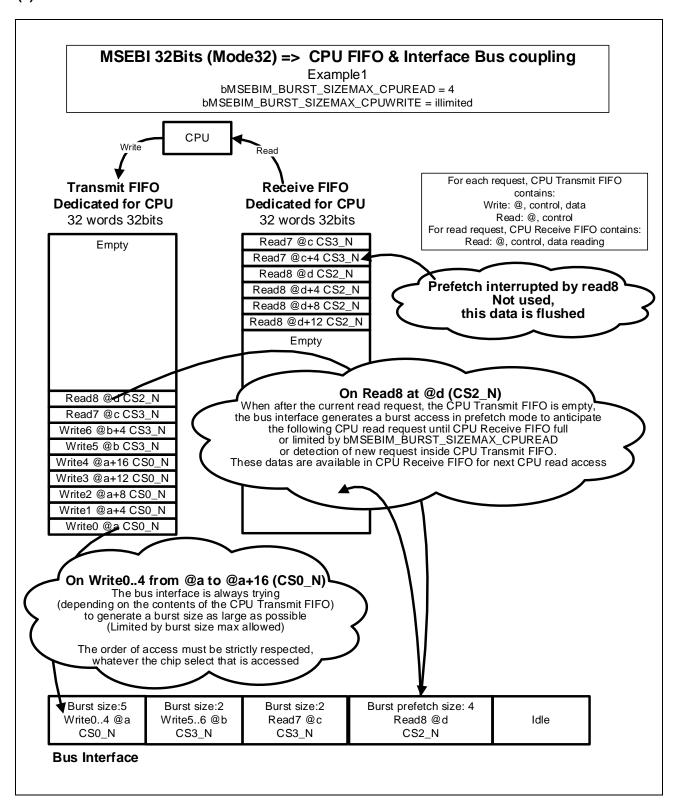

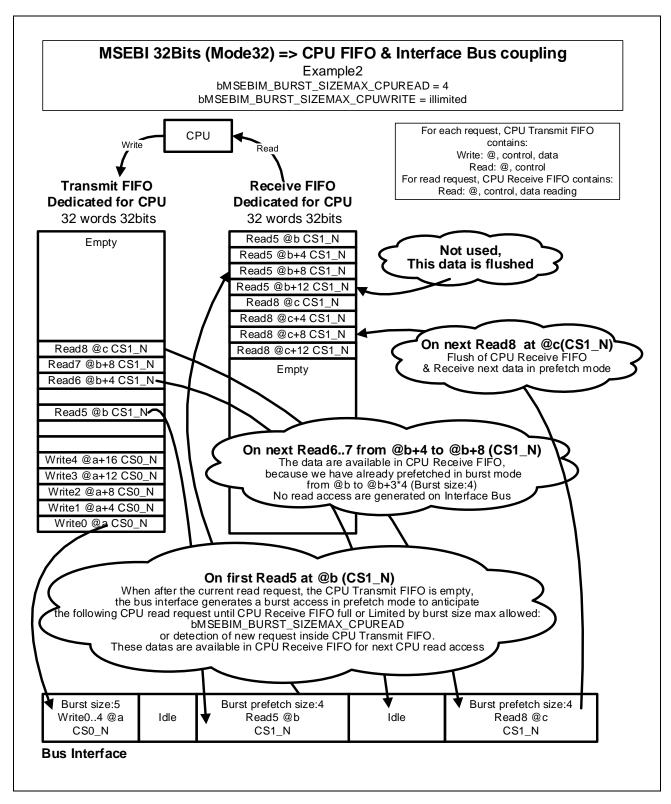

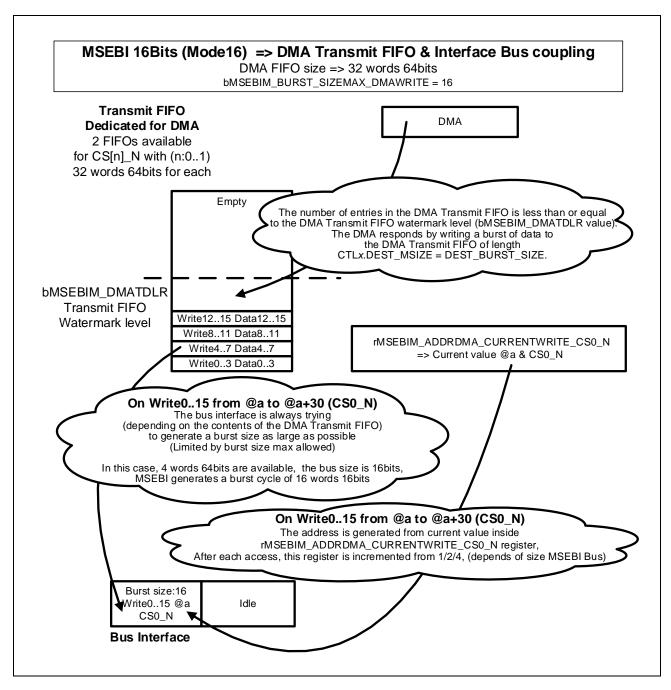

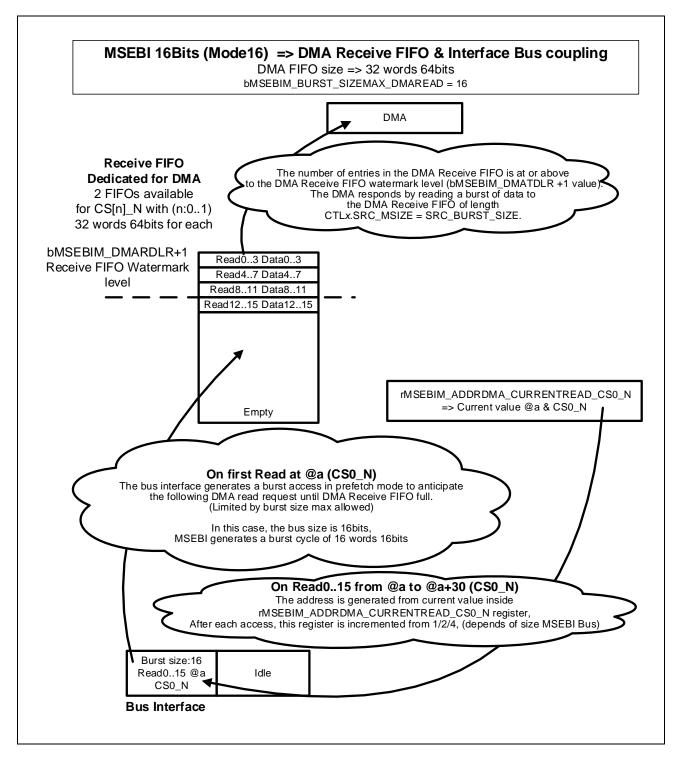

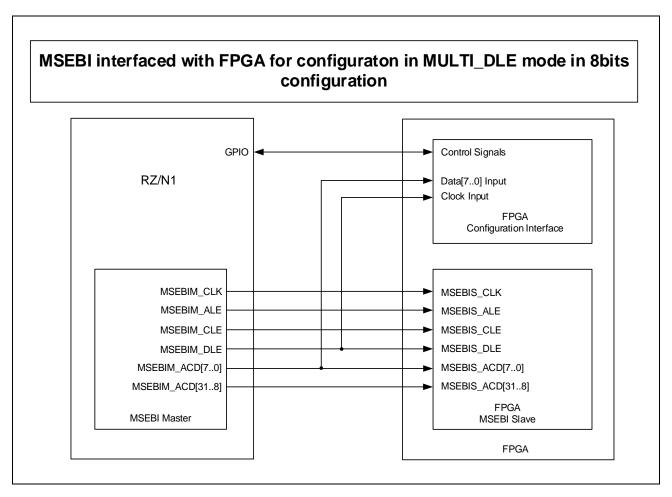

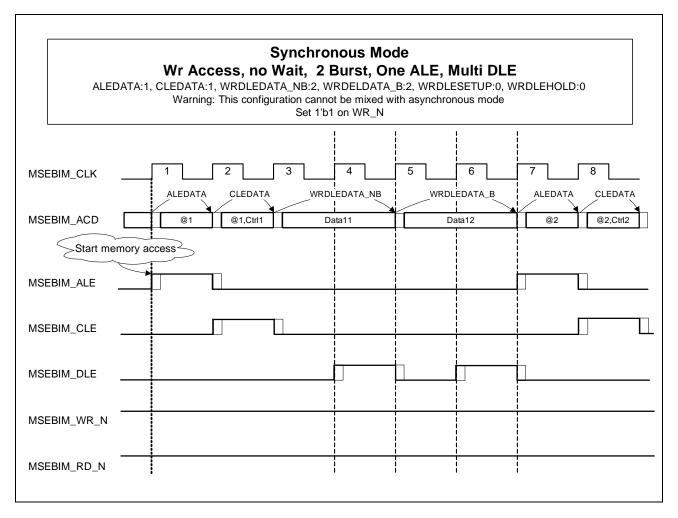

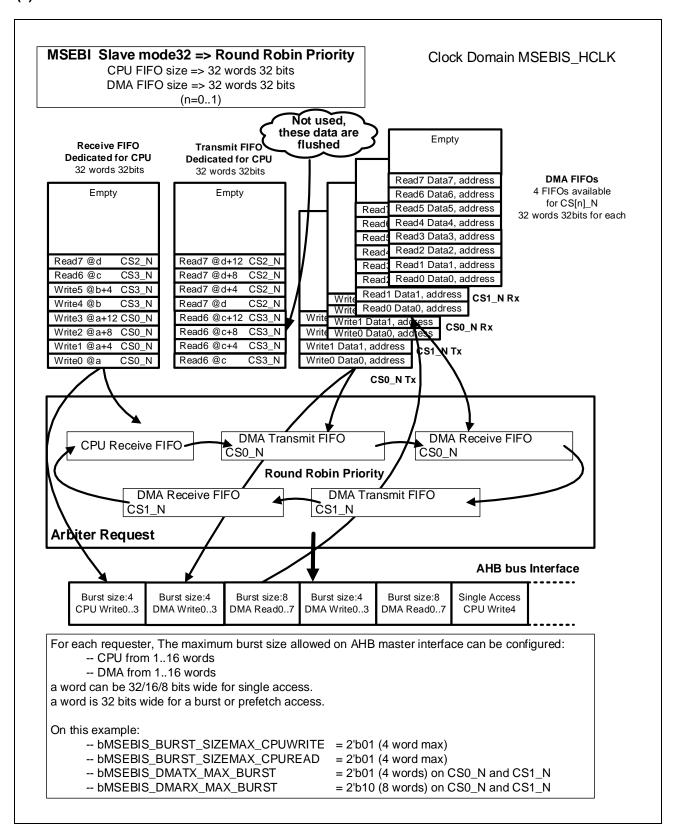

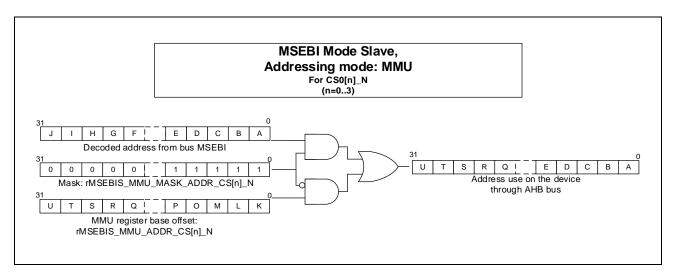

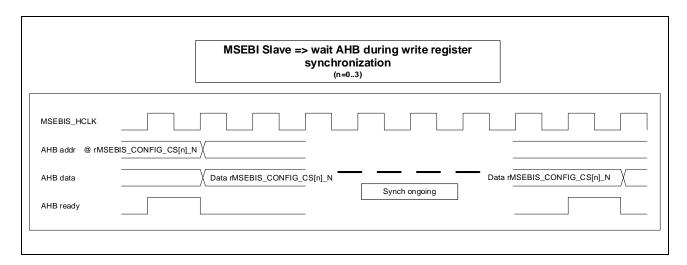

| Section 10 Mediu | um Speed External Bus Interface (MSEBI)                                                         | .459 |

|------------------|-------------------------------------------------------------------------------------------------|------|

| 10.1 Overview    |                                                                                                 | 459  |

| 10.1.1 Signa     | ıl Interfaces                                                                                   | 462  |

| •                | BI Master Address Mapping of CS[n] from CPU                                                     |      |

|                  | blexed Signal Interface                                                                         |      |

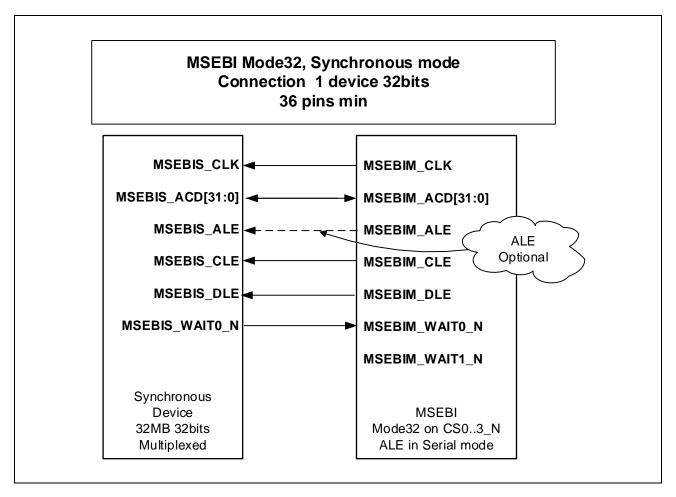

| 10.1.3.1         | Mode32 Multiplexer                                                                              |      |

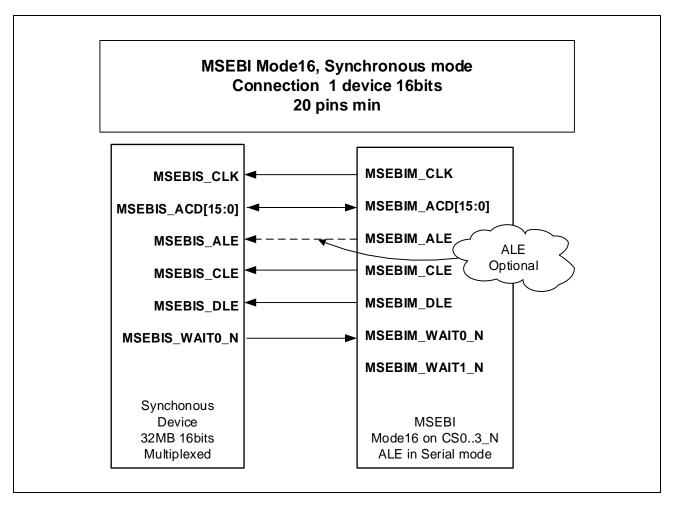

| 10.1.3.2         | Mode16 Multiplexer                                                                              |      |

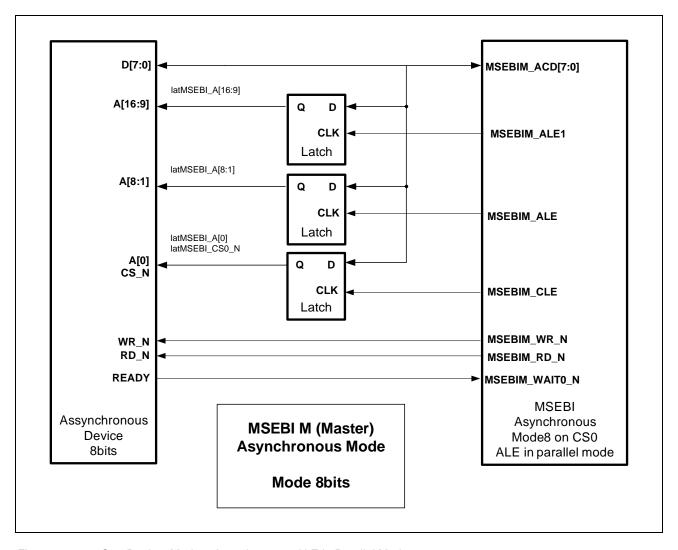

| 10.1.3.3         | Mode8 Multiplexer                                                                               | 469  |

| 10.2 Register Ma | p                                                                                               | 471  |

| 10.2.1 Regis     | ster Map MSEBI Master from CPU                                                                  | 471  |

| 10.2.2 Regis     | ster Map MSEBI Master from DMA                                                                  | 471  |

| 10.2.3 Regis     | ster Map MSEBI Slave from CPU                                                                   | 471  |

| •                | ster Map MSEBI Slave from MSEBI                                                                 |      |

| _                | scription                                                                                       |      |

| J                | ster Description MSEBI Master from CPU                                                          |      |

| 10.3.1 Regis     | rMSEBIM_CYCLESIZE_CS[n]_N — Chip Select CycleSize Register (n = 03)                             |      |

| 10.3.1.2         | rMSEBIM_SETUPHOLD_CS[n]_N — Chip Select SetupHold Register                                      | 770  |

|                  | (n = 03)                                                                                        | 475  |

| 10.3.1.3         | rMSEBIM_TDMACR_CS[n]_N — DMA Transmit Control and Status Register                               |      |

|                  | (n = 01)                                                                                        | 477  |

| 10.3.1.4         | rMSEBIM_RDMACR_CS[n]_N — DMA Receive Control and Status Register                                | 470  |

| 10.3.1.5         | (n = 01)rMSEBIM_ADDRDMA_READ_CS[n]_N — DMA Read Address Register                                | 479  |

| 10.0.1.0         | (n = 0.1)                                                                                       | 481  |

| 10.3.1.6         | rMSEBIM_ADDRDMA_CURRENTREAD_CS[n]_N — DMA Current Read                                          |      |

|                  | Address Register (n = 01)                                                                       | 482  |

| 10.3.1.7         | rMSEBIM_ADDRDMA_WRITE_CS[n]_N — DMA Write Address Register                                      |      |

| 40 2 4 0         | (n = 0.1)                                                                                       | 483  |

| 10.3.1.8         | rMSEBIM_ADDRDMA_CURRENTWRITE_CS[n]_N — DMA Current Write Address Register (n = 01)              | 484  |

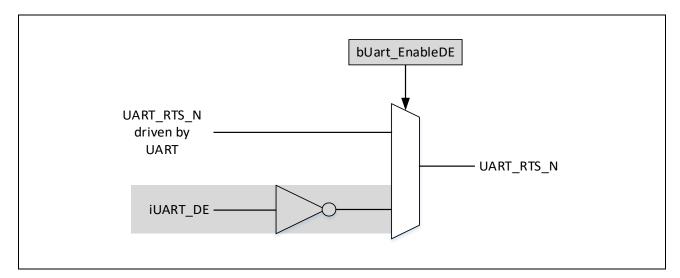

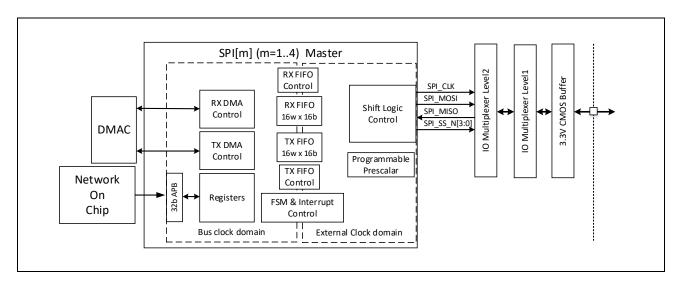

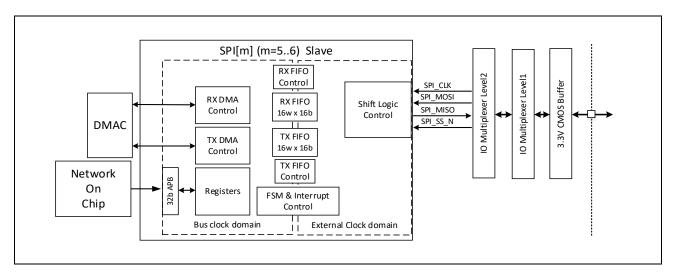

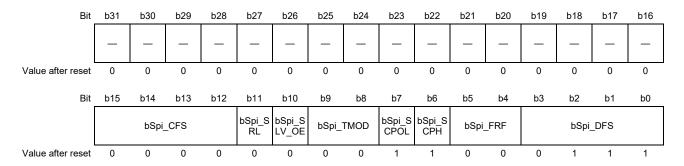

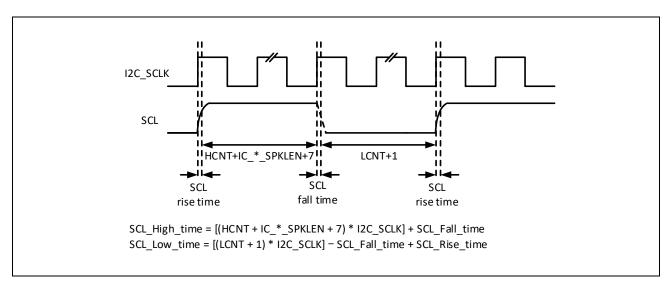

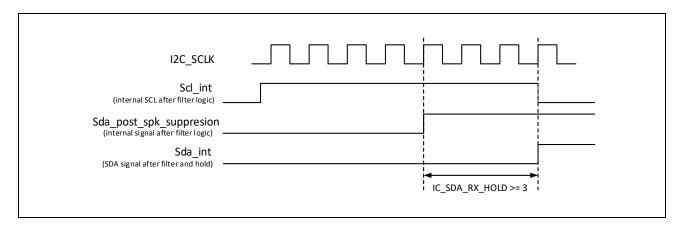

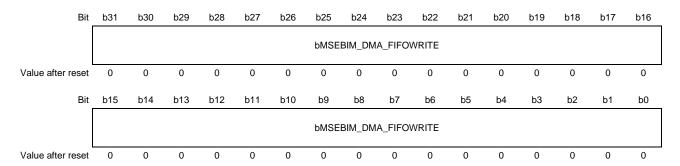

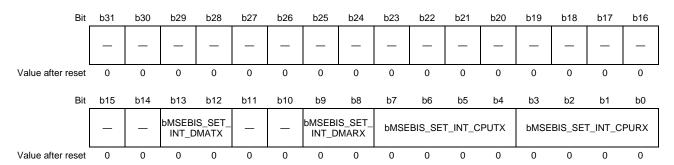

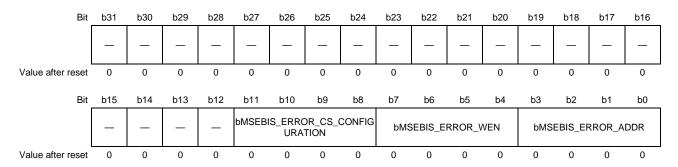

| 10.3.1.9         | rMSEBIM_DMATDLR_CS[n]_N — DMA Transmit Data Level Register                                      |      |