# RX Family RXv1 Instruction Set Architecture

# User's Manual: Software

RENESAS 32-Bit MCU RX Family

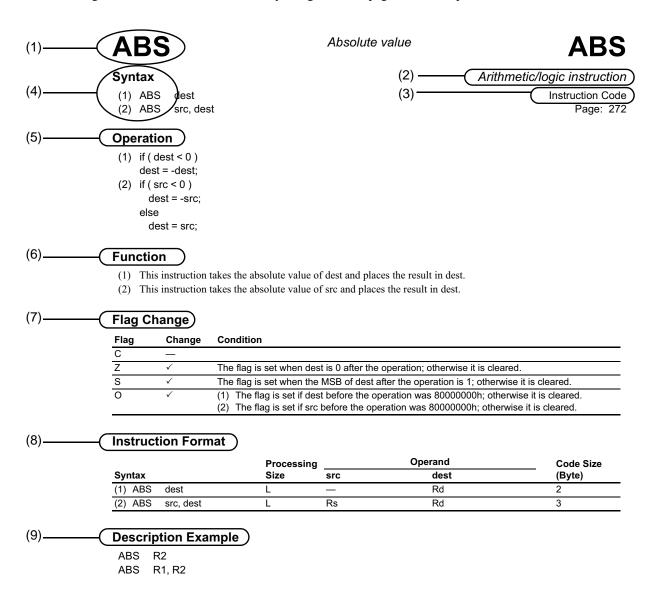

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Renesas Electronics www.renesas.com

Rev.1.30 Dec 2019

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## How to Use This Manual

This manual is designed to provide users with an understanding of RXv1 instruction set architecture (RXv1). The manual contains detailed descriptions of CPU features and instruction sets. The manual is intended for users who are designing application systems using this CPU. Target users are expected to understand the fundamentals of microcomputers.

## **Notation in This Manual**

The following is a list of the elements of the notation used in this manual.

| Classification | Notation                            | Meaning                                                                                                                                                                                                                                                                 |

|----------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbols        | IMM                                 | Immediate value                                                                                                                                                                                                                                                         |

|                | SIMM                                | Immediate value for sign extension according to the processing size                                                                                                                                                                                                     |

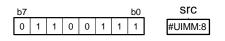

|                | UIMM                                | Immediate value for zero extension according to the processing size                                                                                                                                                                                                     |

|                | src, src2                           | Source of an instruction operand                                                                                                                                                                                                                                        |

|                | dest                                | Destination of an instruction operand                                                                                                                                                                                                                                   |

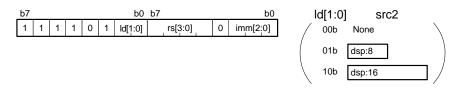

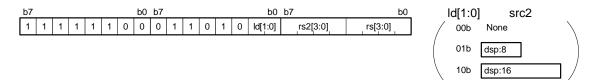

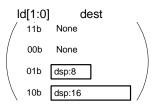

|                | dsp                                 | Displacement of relative addressing                                                                                                                                                                                                                                     |

|                | pcdsp                               | Displacement of relative addressing of the program counter                                                                                                                                                                                                              |

|                | []                                  | Represents indirect addressing                                                                                                                                                                                                                                          |

|                | Rn                                  | General-purpose register. R0 to R15 are specifiable unless stated otherwise.                                                                                                                                                                                            |

|                | Rs                                  | General-purpose register as a source. R0 to R15 are specifiable unless stated otherwise.                                                                                                                                                                                |

|                | Rs2                                 | In the instructions where two general-purpose registers can be specified<br>for operand, the first general-purpose register specified as a source is<br>described as Rs and the second general-purpose register specified as a<br>source is described as Rs2.           |

|                | Rd                                  | General-purpose register as a destination. R0 to R15 are specifiable unless stated otherwise.                                                                                                                                                                           |

|                | Rd2                                 | In the instructions where two general-purpose registers can be specified<br>for operand, the first general-purpose register specified as a destination is<br>described as Rd and the second general-purpose register specified as a<br>destination is described as Rd2. |

|                | Rb                                  | General-purpose register specified as a base register. R0 to R15 are specifiable unless stated otherwise.                                                                                                                                                               |

|                | Ri                                  | General-purpose register as an index register. R0 to R15 are specifiable unless stated otherwise.                                                                                                                                                                       |

|                | Rx                                  | Represents a control register. The PC, ISP, USP, INTB, PSW, BPC, BPSW, FINTV, and FPSW are selectable, although the PC is only selectable as the src operand of MVFC and PUSHC instructions.                                                                            |

|                | flag                                | Represents a bit (U or I) or flag (O, S, Z, or C) in the PSW.                                                                                                                                                                                                           |

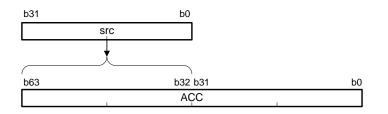

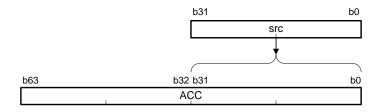

|                | ACC                                 | Accumulator                                                                                                                                                                                                                                                             |

|                | tmp, tmp0, tmp1,<br>tmp2, tmp3 etc. | Temporary registers                                                                                                                                                                                                                                                     |

| Values         | 000 <u>b</u>                        | Binary number                                                                                                                                                                                                                                                           |

|                | 0000 <u>h</u>                       | Hexadecimal number                                                                                                                                                                                                                                                      |

| Bit length     | #IMM <u>:8</u> etc.                 | Represents the effective bit length for the operand symbol.                                                                                                                                                                                                             |

| -              | <u>:1</u>                           | Indicates an effective length of one bit.                                                                                                                                                                                                                               |

|                | <u>:2</u>                           | Indicates an effective length of two bits.                                                                                                                                                                                                                              |

|                | <u>:3</u>                           | Indicates an effective length of three bits.                                                                                                                                                                                                                            |

|                | <u>:4</u>                           | Indicates an effective length of four bits.                                                                                                                                                                                                                             |

|                | <u>.5</u>                           | Indicates an effective length of five bits.                                                                                                                                                                                                                             |

|                | <u>.8</u>                           | Indicates an effective length of eight bits.                                                                                                                                                                                                                            |

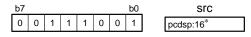

|                | <u></u>                             | Indicates an effective length of 16 bits.                                                                                                                                                                                                                               |

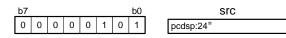

|                | :24                                 | Indicates an effective length of 24 bits.                                                                                                                                                                                                                               |

|                | :32                                 | Indicates an effective length of 32 bits.                                                                                                                                                                                                                               |

| Classification                                                                                | Notation                                                                                                                    | Meaning                                                                                                                                   |  |  |  |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Size specifiers                                                                               | MOV <u>.W</u> etc.                                                                                                          | Indicates the size that an instruction handles.                                                                                           |  |  |  |

| Size specifiers Branch distance specifiers Size extension specifiers added to memory operands | <u>.B</u>                                                                                                                   | Byte (8 bits) is specified.                                                                                                               |  |  |  |

|                                                                                               | <u>.W</u>                                                                                                                   | Word (16 bits) is specified.                                                                                                              |  |  |  |

|                                                                                               | <u>.L</u>                                                                                                                   | Longword (32 bits) is specified.                                                                                                          |  |  |  |

| Branch distance specifiers                                                                    | BRA <u>.A</u> etc.                                                                                                          | Indicates the length of the valid bits to represent the distance to the branch relative destination.                                      |  |  |  |

|                                                                                               | <u>.S</u>                                                                                                                   | 3-bit PC forward relative is specified. The range of valid values is 3 to 10.                                                             |  |  |  |

|                                                                                               | <u>.B</u>                                                                                                                   | 8-bit PC relative is specified. The range of valid values is -128 to 127.                                                                 |  |  |  |

|                                                                                               | <u>.W</u>                                                                                                                   | 16-bit PC relative is specified. The range of valid values is –32768 to 32767.                                                            |  |  |  |

|                                                                                               | <u>.A</u>                                                                                                                   | 24-bit PC relative is specified. The range of valid values is -8388608 to 8388607.                                                        |  |  |  |

|                                                                                               | <u>.L</u>                                                                                                                   | 32-bit PC relative is specified. The range of valid values is -2147483648 to 2147483647.                                                  |  |  |  |

| Size extension specifiers added to                                                            | dsp:16[Rs] <u>.UB</u> etc.                                                                                                  | Indicates the size of a memory operand and the type of extension. If the specifier is omitted, the memory operand is handled as longword. |  |  |  |

| memory operands                                                                               | <u>.B</u>                                                                                                                   | Byte (8 bits) is specified. The extension is sign extension.                                                                              |  |  |  |

|                                                                                               | <u>.UB</u>                                                                                                                  | Byte (8 bits) is specified. The extension is zero extension.                                                                              |  |  |  |

|                                                                                               | <u>.W</u>                                                                                                                   | Word (16 bits) is specified. The extension is sign extension.                                                                             |  |  |  |

|                                                                                               | <u>.UW</u>                                                                                                                  | Word (16 bits) is specified. The extension is zero extension.                                                                             |  |  |  |

|                                                                                               | <u>.L</u>                                                                                                                   | Longword (32 bits) is specified.                                                                                                          |  |  |  |

| Operations                                                                                    | (Operations in this manual are written in accordance with C language syntax. The following is the notation in this manual.) |                                                                                                                                           |  |  |  |

|                                                                                               | =                                                                                                                           | Assignment operator. The value on the right is assigned to the variable on the left.                                                      |  |  |  |

|                                                                                               | -                                                                                                                           | Indicates negation as a unary operator or a "difference" as a binary operator.                                                            |  |  |  |

|                                                                                               | +                                                                                                                           | Indicates "sum" as a binary operator.                                                                                                     |  |  |  |

|                                                                                               | *                                                                                                                           | Indicates a pointer or a "product" as a binary operator.                                                                                  |  |  |  |

|                                                                                               | /                                                                                                                           | Indicates "quotient" as a binary operator.                                                                                                |  |  |  |

|                                                                                               | %                                                                                                                           | Indicates "remainder" as a binary operator.                                                                                               |  |  |  |

|                                                                                               | ~                                                                                                                           | Indicates bit-wise "NOT" as a unary operator.                                                                                             |  |  |  |

|                                                                                               | &                                                                                                                           | Indicates bit-wise "AND" as a binary operator.                                                                                            |  |  |  |

|                                                                                               |                                                                                                                             | Indicates bit-wise "OR" as a binary operator.                                                                                             |  |  |  |

|                                                                                               | ٨                                                                                                                           | Indicates bit-wise "Exclusive OR" as a binary operator.                                                                                   |  |  |  |

|                                                                                               |                                                                                                                             | Indicates the end of a statement.                                                                                                         |  |  |  |

| Classification       | Notation                                                        | Meaning                                                                                                                                                                                                                                          |  |  |  |  |  |

|----------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Operations           | { }                                                             | Indicates the start and end of a complex sentence. Multiple statements can be put in $\{\ \}.$                                                                                                                                                   |  |  |  |  |  |

|                      | if (expression)<br>statement 1 else<br>statement 2              | Indicates an if-statement. The expression is evaluated; statement 1 is executed if the result is true and statement 2 is executed if the result is false.                                                                                        |  |  |  |  |  |

|                      | for (statement 1;<br>expression;<br>statement 2)<br>statement 3 | Indicates a for-statement. After executing statement 1 and then evaluating the expression, statement 3 is executed if the result is true. After statement 3 is executed the first time, the expression is evaluated after executing statement 2. |  |  |  |  |  |

|                      | do statement while (expression);                                | Indicates a do-statement. As long as the expression is true, the statement<br>is executed. Regardless of whether the expression is true or false, the<br>statement is executed at least once.                                                    |  |  |  |  |  |

|                      | while (expression) statement                                    | Indicates a while-statement. As long as the expression is true, the statement is executed.                                                                                                                                                       |  |  |  |  |  |

|                      | ==, !=                                                          | Comparison operators. "==" means "is equal to" and "!=" means "is not equal to".                                                                                                                                                                 |  |  |  |  |  |

|                      | >, <                                                            | Comparison operators. ">" means "greater than" and "<" means "less than".                                                                                                                                                                        |  |  |  |  |  |

|                      | >=, <=                                                          | Comparison operators. The condition includes "==" as well as ">" or "<".                                                                                                                                                                         |  |  |  |  |  |

|                      | &&                                                              | Logical operator. Indicates the "AND" of the conditions to the left and right of the operator.                                                                                                                                                   |  |  |  |  |  |

|                      |                                                                 | Logical operator. Indicates the "OR" of the conditions to the left and right of the operator.                                                                                                                                                    |  |  |  |  |  |

|                      | <<, >>                                                          | Shift operators, respectively indicating leftward and rightward shifts.                                                                                                                                                                          |  |  |  |  |  |

| Floating-point datum | NaN                                                             | Not a number                                                                                                                                                                                                                                     |  |  |  |  |  |

| Floating-point       | SNaN                                                            | Signaling NaN                                                                                                                                                                                                                                    |  |  |  |  |  |

| representation       | QNaN                                                            | Quiet NaN                                                                                                                                                                                                                                        |  |  |  |  |  |

## Contents

| Ho   | ow to U        | se This Manual                                              | 3  |

|------|----------------|-------------------------------------------------------------|----|

| l is | st of RX       | v1 Instruction Set for RX Family                            | 9  |

|      |                | ge Reference in Alphabetical Order                          |    |

|      |                |                                                             |    |

| 1.   |                | J Programming Model                                         |    |

|      | 1.1            | Features                                                    |    |

|      | 1.2            | Register Set of the CPU                                     |    |

|      | 1.2.1<br>1.2.2 |                                                             |    |

|      |                | .2.1 Interrupt Stack Pointer (ISP)/User Stack Pointer (USP) |    |

|      |                | .2.2 Interrupt Table Register (INTB)                        |    |

|      |                | .2.3 Program Counter (PC)                                   |    |

|      |                | .2.4 Processor Status Word (PSW)                            |    |

|      | 1.2            | .2.5 Backup PC (BPC)                                        |    |

|      | 1.2            | .2.6 Backup PSW (BPSW)                                      |    |

|      | 1.2            | .2.7 Fast Interrupt Vector Register (FINTV)                 |    |

|      | 1.2            | .2.8 Floating-Point Status Word (FPSW)                      |    |

|      | 1.2.3          | Accumulator                                                 |    |

|      | 1.3            | Floating-Point Exceptions                                   |    |

|      | 1.3.1          | Overflow                                                    |    |

|      | 1.3.2          | Underflow                                                   |    |

|      | 1.3.3          | Inexact                                                     |    |

|      | 1.3.4          | Division-by-Zero                                            |    |

|      | 1.3.5          | Invalid Operation                                           |    |

|      | 1.3.6          | Unimplemented Processing                                    |    |

|      | 1.4            | Processor Mode                                              |    |

|      | 1.4.1          | Supervisor Mode                                             |    |

|      | 1.4.2          | User Mode                                                   |    |

|      | 1.4.3          | Privileged Instruction                                      |    |

|      | 1.4.4<br>1.5   | Switching Between Processor Modes<br>Data Types             |    |

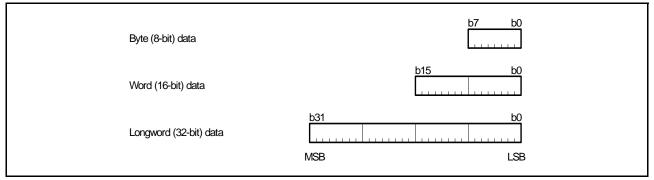

|      | 1.5            | Integer                                                     |    |

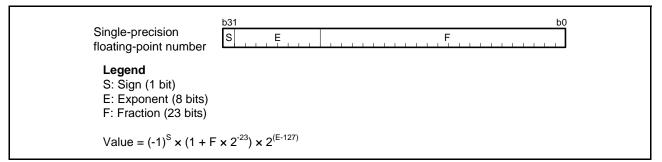

|      | 1.5.1          | Floating-Point Number                                       |    |

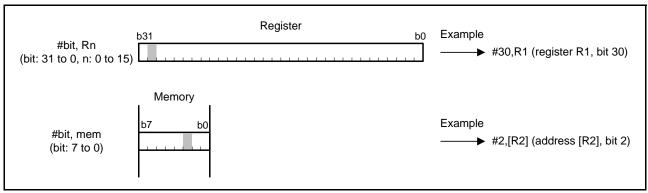

|      | 1.5.2          | Bit                                                         |    |

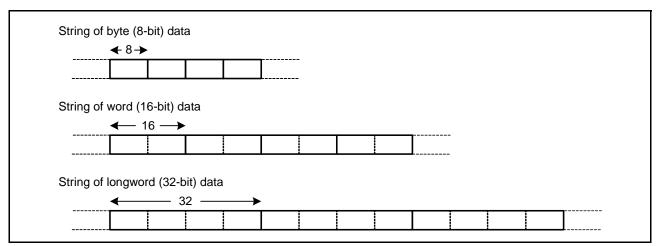

|      | 1.5.4          | String                                                      |    |

|      | 1.6            | Data Arrangement                                            |    |

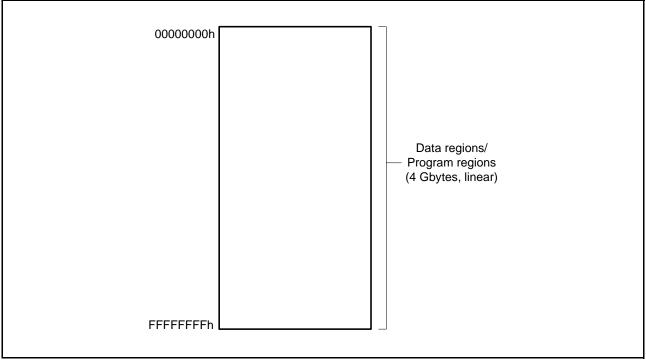

|      | 1.6.1          | Data Arrangement in Registers                               |    |

|      | 1.6.2          | Data Arrangement in Memory                                  |    |

|      | 1.7            | Vector Table                                                |    |

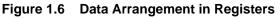

|      | 1.7.1          | Fixed Vector Table                                          |    |

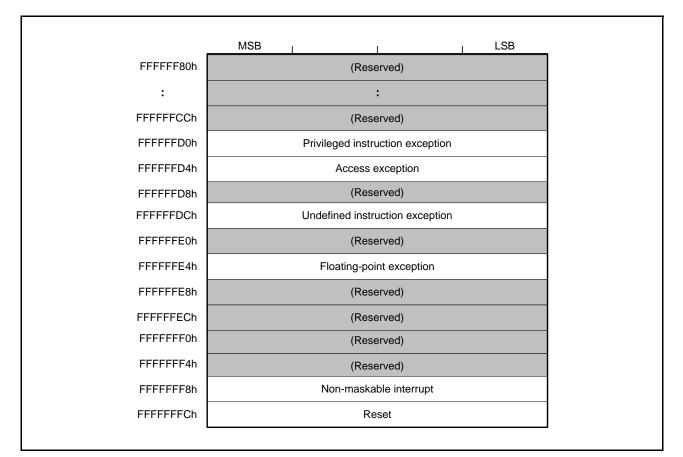

|      | 1.7.2          | Relocatable Vector Table                                    |    |

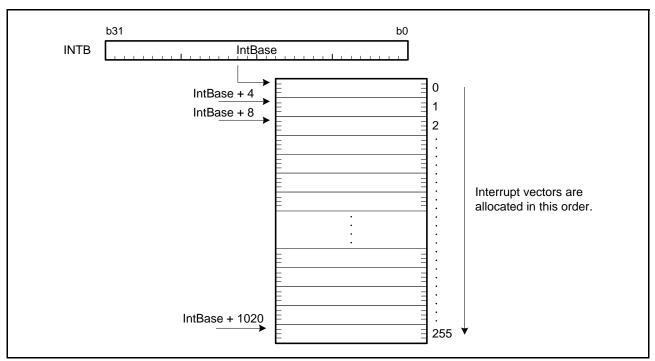

|      | 1.8            | Address Space                                               |    |

| _    |                |                                                             |    |

| 2.   | Add            | ressing Modes                                               |    |

|      | 2.1            | Guide to This Section                                       |    |

|      | 2.2            | Addressing Modes                                            |    |

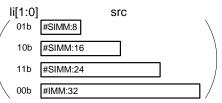

|      | 2.2.1          | Ranges for Immediate Values                                 | 40 |

| 3.   | Inst           | uction Descriptions                                         |    |

|      | 3.1            | Overview of Instruction Set                                 |    |

|      | 3.2            | Guide to This Section                                       |    |

|      | 3.3            | Instructions in Detail                                      |    |

|      |                |                                                             |    |

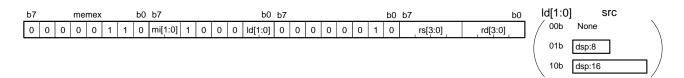

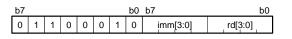

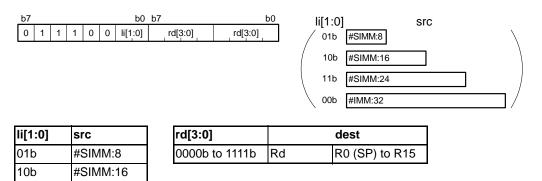

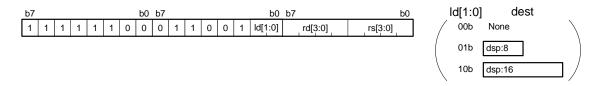

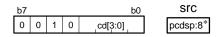

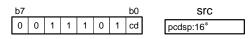

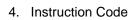

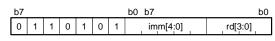

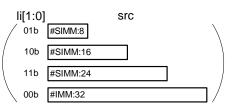

| 4.   |                | uction Code                                                 |    |

|      | 4.1            | Guide to This Section                                       |    |

| 4.2      | Instruction Code Described in Detail                            |     |

|----------|-----------------------------------------------------------------|-----|

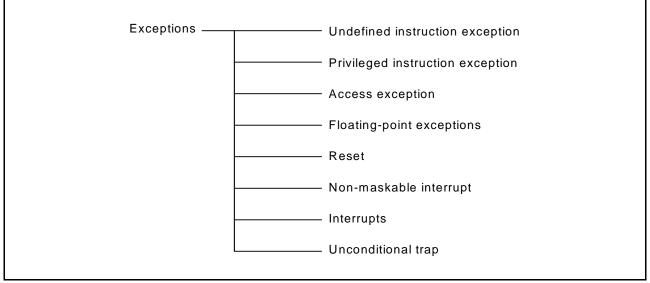

| 5. Exce  | eptions                                                         | 247 |

| 5.1      | Types of Exception                                              |     |

| 5.1.1    | Undefined Instruction Exception                                 |     |

| 5.1.2    | Privileged Instruction Exception                                |     |

| 5.1.3    | Access Exception                                                |     |

| 5.1.4    | Floating-Point Exceptions                                       |     |

| 5.1.5    | Reset                                                           |     |

| 5.1.6    | Non-Maskable Interrupt                                          |     |

| 5.1.7    | Interrupts                                                      |     |

| 5.1.8    | Unconditional Trap                                              |     |

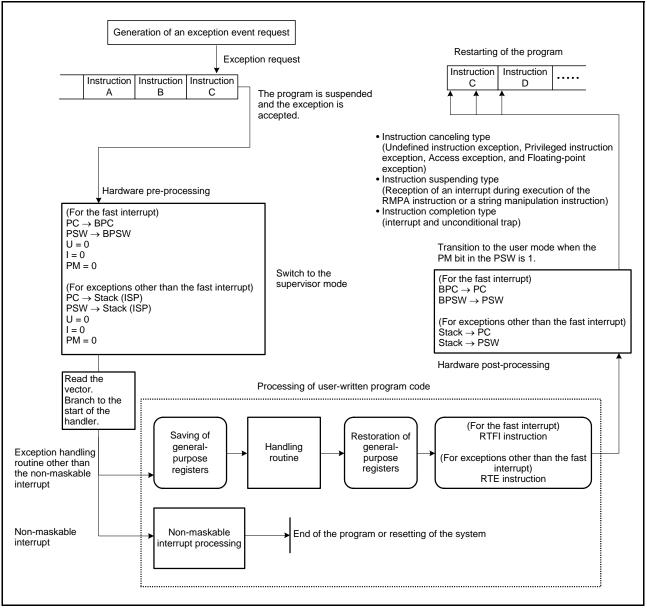

| 5.2      | Exception Handling Procedure                                    |     |

| 5.3      | Acceptance of Exceptions                                        |     |

| 5.3.1    | Timing of Acceptance and Saved PC Value                         |     |

| 5.3.2    | Vector and Site for Preserving the PC and PSW                   |     |

| 5.4      | Hardware Processing for Accepting and Returning from Exceptions |     |

| 5.5      | Hardware Pre-processing                                         |     |

| 5.5.1    | Undefined Instruction Exception                                 |     |

| 5.5.2    | Privileged Instruction Exception                                |     |

| 5.5.3    | Access Exception                                                |     |

| 5.5.4    | Floating-Point Exceptions                                       |     |

| 5.5.5    | Reset                                                           |     |

| 5.5.6    | Non-Maskable Interrupt                                          |     |

| 5.5.7    | Interrupts                                                      |     |

| 5.5.8    | Unconditional Trap                                              |     |

| 5.6      | Return from Exception Handling Routines                         |     |

| 5.7      | Order of Priority for Exceptions                                |     |

| Index    |                                                                 | 257 |

| REVISION | N HISTORY                                                       | 259 |

## List of RXv1 Instruction Set for RX Family

## Quick Page Reference in Alphabetical Order (1 / 4)

| Mnemonic |       | Function                      | Instruction<br>Described<br>in Detail<br>(on Page) | Instruction<br>Code Described<br>in Detail<br>(on Page) |

|----------|-------|-------------------------------|----------------------------------------------------|---------------------------------------------------------|

| ABS      |       | Absolute value                | 51                                                 | 169                                                     |

| ADC      |       | Add with carry                | 52                                                 | 170                                                     |

| ADD      |       | Add without carry             | 53                                                 | 171                                                     |

| AND      |       | Logical AND                   | 55                                                 | 173                                                     |

| BCLR     |       | Clear a bit                   | 57                                                 | 175                                                     |

| BCnd     | BGEU  | Conditional relative branch   | 58                                                 | 177                                                     |

|          | BC    | _                             | 58                                                 | 177                                                     |

|          | BEQ   | —                             | 58                                                 | 177                                                     |

|          | BZ    | —                             | 58                                                 | 177                                                     |

|          | BGTU  | —                             | 58                                                 | 177                                                     |

|          | BPZ   | _                             | 58                                                 | 177                                                     |

|          | BGE   | _                             | 58                                                 | 177                                                     |

|          | BGT   | _                             | 58                                                 | 177                                                     |

|          | BO    | _                             | 58                                                 | 177                                                     |

|          | BLTU  | _                             | 58                                                 | 177                                                     |

|          | BNC   | _                             | 58                                                 | 177                                                     |

|          | BNE   | —                             | 58                                                 | 177                                                     |

|          | BNZ   | —                             | 58                                                 | 177                                                     |

|          | BLEU  | _                             | 58                                                 |                                                         |

|          | BN    | _                             | 58                                                 | 177<br>177                                              |

|          | BLE   | _                             |                                                    | 177                                                     |

|          |       | _                             | 58                                                 |                                                         |

|          | BLT   | _                             | 58                                                 | 177                                                     |

| DMO: d   | BNO   |                               | 58                                                 | 177                                                     |

| BMCnd    | BMGEU | Conditional bit transfer      | 59                                                 | 179                                                     |

|          | BMC   | _                             | 59                                                 | 179                                                     |

|          | BMEQ  | _                             | 59                                                 | 179                                                     |

|          | BMZ   | _                             | 59                                                 | 179                                                     |

|          | BMGTU | _                             | 59                                                 | 179                                                     |

|          | BMPZ  | _                             | 59                                                 | 179                                                     |

|          | BMGE  | _                             | 59                                                 | 179                                                     |

|          | BMGT  | _                             | 59                                                 | 179                                                     |

|          | BMO   | _                             | 59                                                 | 179                                                     |

|          | BMLTU | _                             | 59                                                 | 179                                                     |

|          | BMNC  | _                             | 59                                                 | 179                                                     |

|          | BMNE  | _                             | 59                                                 | 179                                                     |

|          | BMNZ  | _                             | 59                                                 | 179                                                     |

|          | BMLEU |                               | 59                                                 | 179                                                     |

|          | BMN   | _                             | 59                                                 | 179                                                     |

|          | BMLE  | _                             | 59                                                 | 179                                                     |

|          | BMLT  |                               | 59                                                 | 179                                                     |

|          | BMNO  | _                             | 59                                                 | 179                                                     |

| BNOT     |       | Not a bit                     | 61                                                 | 180                                                     |

| BRA      |       | Unconditional relative branch | 62                                                 | 181                                                     |

## Quick Page Reference in Alphabetical Order (2 / 4)

| Mnemonic                                         | Function                                                    | Instruction<br>Described<br>in Detail<br>(on Page) | Instruction<br>Code Described<br>in Detail<br>(on Page) |

|--------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------|

| BRK                                              | Unconditional trap                                          | 63                                                 | 182                                                     |

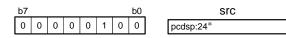

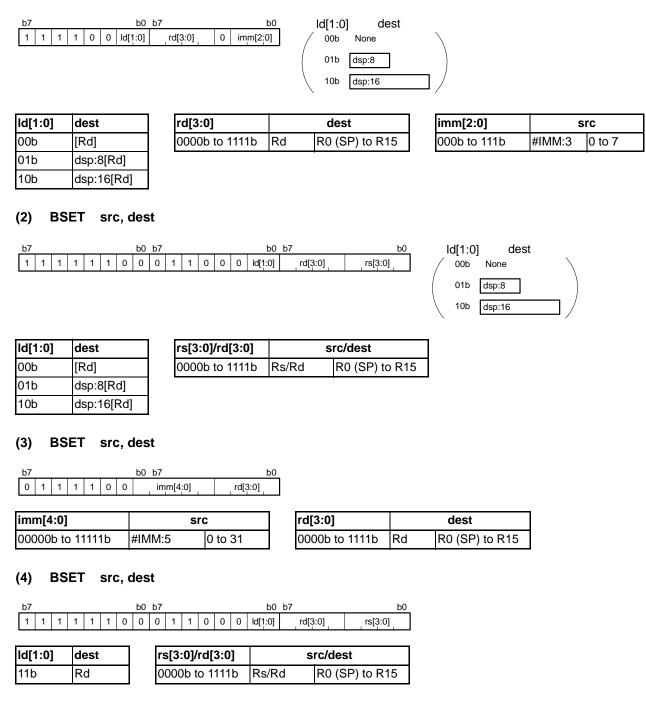

| BSET                                             | Set a bit                                                   | 64                                                 | 182                                                     |

| BSR                                              | Relative branch to subroutine                               | 65                                                 | 184                                                     |

| BTST                                             | Test a bit                                                  | 66                                                 | 185                                                     |

| CLRPSW                                           | Clear a flag or bit in the PSW                              | 67                                                 | 186                                                     |

| CMP                                              | Compare                                                     | 68                                                 | 187                                                     |

| DIV                                              | Divide signed                                               | 69                                                 | 188                                                     |

| DIVU                                             | Divide unsigned                                             | 70                                                 | 190                                                     |

| EMUL                                             | Extended multiply signed                                    | 71                                                 | 191                                                     |

| EMULU                                            | Extended multiply unsigned                                  | 73                                                 | 192                                                     |

| FADD <sup>*1</sup>                               | Add floating-point                                          | 75                                                 | 194                                                     |

| FCMP <sup>*1</sup>                               | Comparefloating-point                                       | 77                                                 | 195                                                     |

| FDIV <sup>*1</sup>                               | Divide floating-point                                       | 79                                                 | 196                                                     |

| FMUL <sup>*1</sup>                               | Multiply floating-point                                     | 81                                                 | 197                                                     |

| FSUB <sup>*1</sup>                               | Subtractfloating-point                                      | 83                                                 | 198                                                     |

| FTOI <sup>*1</sup>                               | Convert floating-point to signed integer                    | 85                                                 | 199                                                     |

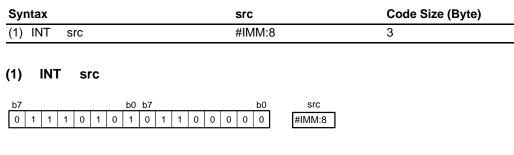

| INT                                              | Software interrupt                                          | 88                                                 | 200                                                     |

| ITOF <sup>*1</sup>                               | Convert signed integer to floating-point                    | 89                                                 | 200                                                     |

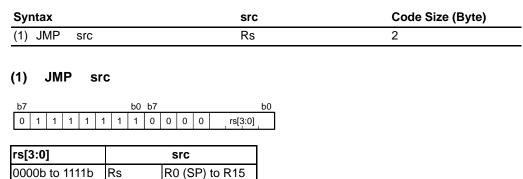

| JMP                                              | Unconditional jump                                          | 91                                                 | 201                                                     |

| JSR                                              | Jump to subroutine                                          | 92                                                 | 201                                                     |

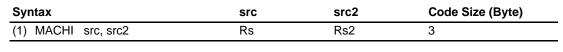

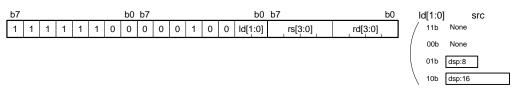

| MACHI                                            | Multiply-Accumulate the upper words                         | 93                                                 | 202                                                     |

| MACLO                                            | Multiply-Accumulate the lower words                         | 94                                                 | 202                                                     |

| MAX                                              | Maximum of two signed integers                              | 95                                                 | 203                                                     |

| MIN                                              | Minimum of two signed integers                              | 96                                                 | 204                                                     |

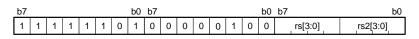

| MOV                                              | Move                                                        | 97                                                 | 205                                                     |

| MOVU                                             | Move unsigned                                               | 100                                                | 210                                                     |

| MUL                                              | Multiply                                                    | 102                                                | 211                                                     |

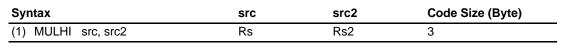

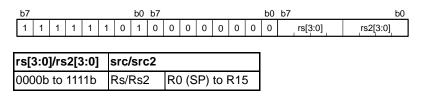

| MULHI                                            | Multiply the upper words                                    | 104                                                | 213                                                     |

| MULLO                                            | Multiply the lower words                                    | 105                                                | 213                                                     |

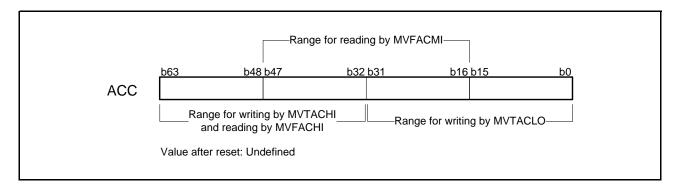

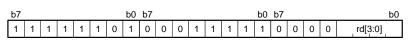

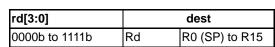

| MVFACHI                                          | Move data from the upper longword of the accumulator        | 106                                                | 213                                                     |

| MVFACMI                                          | Move data from the middle-order longword of the accumulator | 107                                                | 214                                                     |

| MVFC                                             | Move data from a control register                           | 108                                                | 214                                                     |

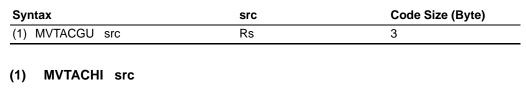

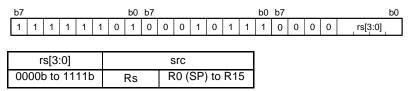

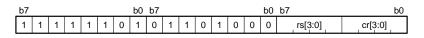

| MVTACHI                                          | Move data to the upper longword of the accumulator          | 109                                                | 215                                                     |

| MVTACLO                                          | Move data to the lower longword of the accumulator          | 110                                                | 215                                                     |

| MVTC                                             | Move data to a control register                             | 111                                                | 216                                                     |

| MVTIPL<br>(privileged instruction) <sup>*2</sup> | Move data to IPL                                            | 112                                                | 217                                                     |

| NEG                                              | Negate (two's complement)                                   | 113                                                | 218                                                     |

| NOP                                              | No operation                                                | 114                                                | 218                                                     |

| NOT                                              | Logical NOT (one's complement)                              | 115                                                | 219                                                     |

| OR                                               | Logical OR                                                  | 116                                                | 220                                                     |

| POP                                              | Pop register from stack                                     | 117                                                | 221                                                     |

| POPC                                             | Pop a control register from stack                           | 118                                                | 222                                                     |

| POPM                                             | Pop multiple registers from stack                           | 119                                                | 222                                                     |

| PUSH                                             | Push register on stack                                      | 120                                                | 223                                                     |

|                                                  |                                                             |                                                    |                                                         |

## Quick Page Reference in Alphabetical Order (3 / 4)

| Mnemonic            |             | Function                                              | Instruction<br>Described<br>in Detail<br>(on Page) | Instruction<br>Code Described<br>in Detail<br>(on Page) |

|---------------------|-------------|-------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------|

| PUSHC               |             | Push a control register on stack                      | 121                                                | 224                                                     |

| PUSHM               |             | Push multiple registers on stack                      | 122                                                | 224                                                     |

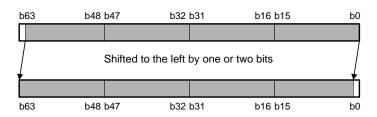

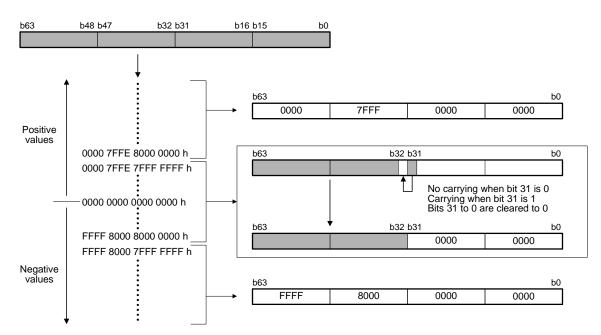

| RACW                |             | Round the accumulator word                            | 123                                                | 225                                                     |

| REVL                |             | Reverse endian within longword                        | 125                                                | 225                                                     |

| REVW                |             | Reverse endian within word                            | 126                                                | 225                                                     |

| RMPA                |             | Repeat multiply-accumulate                            | 127                                                | 226                                                     |

| ROLC                |             | Rotate left with carry                                | 129                                                | 226                                                     |

| RORC                |             | Rotate right with carry                               | 130                                                | 227                                                     |

| ROTL                |             | Rotate left                                           | 131                                                | 227                                                     |

| ROTR                |             | Rotate right                                          | 132                                                | 228                                                     |

| ROUND <sup>*1</sup> |             | Round floating-point to signed integer                | 133                                                | 229                                                     |

| RTE                 |             | Return from exception                                 | 136                                                | 229                                                     |

| (privileged ir      | nstruction) |                                                       |                                                    |                                                         |

| RTFI                |             | Return from fast interrupt                            | 137                                                | 230                                                     |

| (privileged in      | nstruction) |                                                       |                                                    |                                                         |

| RTS                 |             | Return from subroutine                                | 138                                                | 230                                                     |

| RTSD                |             | Return from subroutine after deallocating stack frame | 139                                                | 230                                                     |

| SAT                 |             | Saturate                                              | 141                                                | 231                                                     |

| SATR                |             | Saturate for RMPA                                     | 142                                                | 231                                                     |

| SBB                 |             | Subtract with borrow                                  | 143                                                | 232                                                     |

| SCCnd               | SCGEU       | Store condition                                       | 144                                                | 233                                                     |

|                     | SCC         | _                                                     | 144                                                | 233                                                     |

|                     | SCEQ        | _                                                     | 144                                                | 233                                                     |

|                     | SCZ         | _                                                     | 144                                                | 233                                                     |

|                     | SCGTU       | _                                                     | 144                                                | 233                                                     |

|                     | SCPZ        | _                                                     | 144                                                | 233                                                     |

|                     | SCGE        | _                                                     | 144                                                | 233                                                     |

|                     | SCGT        | _                                                     | 144                                                | 233                                                     |

|                     | SCO         | _                                                     | 144                                                | 233                                                     |

|                     | SCLTU       | _                                                     | 144                                                | 233                                                     |

|                     | SCNC        | _                                                     | 144                                                | 233                                                     |

|                     | SCNE        | _                                                     | 144                                                | 233                                                     |

|                     | SCNZ        | —                                                     | 144                                                | 233                                                     |

|                     | SCLEU       | —                                                     | 144                                                | 233                                                     |

|                     | SCN         | —                                                     | 144                                                | 233                                                     |

|                     | SCLE        | -                                                     | 144                                                | 233                                                     |

|                     | SCLT        | -                                                     | 144                                                | 233                                                     |

|                     | SCNO        | -                                                     | 144                                                | 233                                                     |

| SCMPU               |             | String compare until not equal                        | 145                                                | 233                                                     |

| SETPSW              |             | Set a flag or bit in the PSW                          | 146                                                | 234                                                     |

| SHAR                |             | Arithmetic shift right                                | 147                                                | 235                                                     |

| SHLL                |             | Logical shift left                                    | 148                                                | 236                                                     |

| SHLR                |             | Logical shift right                                   | 149                                                | 237                                                     |

| SMOVB               |             | String move backward                                  | 150                                                | 238                                                     |

| SMOVF               |             | String move forward                                   | 151                                                | 238                                                     |

| SMOVU               |             | String move until zero detected                       | 152                                                | 238                                                     |

|                     |             |                                                       |                                                    |                                                         |

## Quick Page Reference in Alphabetical Order (4 / 4)

| Mnemonic                         | Function                  | Instruction<br>Described<br>in Detail<br>(on Page) | Instruction<br>Code Described<br>in Detail<br>(on Page) |

|----------------------------------|---------------------------|----------------------------------------------------|---------------------------------------------------------|

| SSTR                             | String store              | 153                                                | 239                                                     |

| STNZ                             | Store on not zero         | 154                                                | 239                                                     |

| STZ                              | Store on zero             | 155                                                | 240                                                     |

| SUB                              | Subtract without borrow   | 156                                                | 241                                                     |

| SUNTIL                           | String search until equal | 157                                                | 242                                                     |

| SWHILE                           | String search while equal | 159                                                | 242                                                     |

| TST                              | Test logical              | 161                                                | 243                                                     |

| WAIT<br>(privileged instruction) | Wait                      | 162                                                | 244                                                     |

| XCHG                             | Exchange                  | 163                                                | 244                                                     |

| XOR                              | Logical Exclusive OR      | 164                                                | 245                                                     |

Note: 1. The floating-point arithmetic instructions are optional functions. Whether or not the product has the floating-point arithmetic instructions will depend on the product. For details, refer to the user's manual: hardware for each product.

Note: 2. Products of the RX610 Group do not support the MVTIPL instruction.

## 1. CPU Programming Model

The RXv1 instruction set architecture (RXv1) has the following features.

• Adoption of variable-length instruction format

The RXv1 CPU has short formats for frequently used instructions, facilitating the development of efficient programs that take up less memory.

• Powerful instruction set

The RXv1 supports 90 selected instructions. DSP instructions and floating-point arithmetic instructions realize high-speed arithmetic processing.

• Versatile addressing modes

The RXv1 CPU has 10 versatile addressing modes, with register-register operations, register-memory operations, and bitwise operations included. Data transfer between memory locations is also possible.

## 1.1 Features

•

- Minimum instruction execution rate: One clock cycle

- Address space: 4-Gbyte linear addresses

- Register set of the CPU General purpose: Sixteen 32-bit registers Control: Nine 32-bit registers

Accumulator: One 64-bit register

- Variable-length instruction format (lengths from one to eight bytes)

- 90 instructions/10 addressing modes

- Basic instructions: 73 Floating-point arithmetic instructions: 8 (as an optional function<sup>\*</sup>)

DSP instructions: 9

- Processor modes

Supervisor mode and user mode

- Vector tables

- Fixed vector table and relocatable vector table

- Memory protection unit (as an optional function)

- Data arrangement Selectable as little endian or big endian

- Note: \* The floating-point arithmetic instructions are optional functions. Whether or not the product has the floating-point arithmetic instructions will depend on the product. For details, refer to the user's manual: hardware for each product.

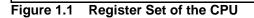

## 1.2 Register Set of the CPU

The RXv1 CPU has sixteen general-purpose registers, nine control registers, and one accumulator used for DSP instructions.

|          | General-purpose register<br>b31 | Control register<br>b0 b31             | b |

|----------|---------------------------------|----------------------------------------|---|

|          |                                 |                                        | D |

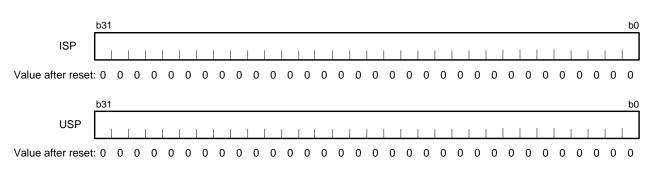

|          | R0 (SP) <sup>*1</sup>           | ISP (Interrupt stack pointer)          |   |

|          | R1                              | USP (User stack pointer)               |   |

|          | R2                              | INTB (Interrupt table register)        |   |

|          | R3                              |                                        |   |

|          | R4                              | PC (Program counter)                   |   |

|          | R5                              |                                        |   |

|          | R6                              | PSW (Processor status word)            |   |

|          | R7                              | BPC (Backup PC)                        |   |

|          | R8                              |                                        |   |

|          | R9                              | BPSW (Backup PSW)                      |   |

|          | R10                             | FINTV (Fast interrupt vector register) |   |

|          | R11                             |                                        |   |

|          | R12                             | FPSW (Floating-point status word)      |   |

|          | R13                             |                                        |   |

|          | R14                             |                                        |   |

|          | R15                             |                                        |   |

|          |                                 |                                        |   |

| DSP inst | ruction register                |                                        |   |

| 563      |                                 |                                        | b |

|          | AC                              | CC (Accumulator)                       |   |

|          |                                 |                                        |   |

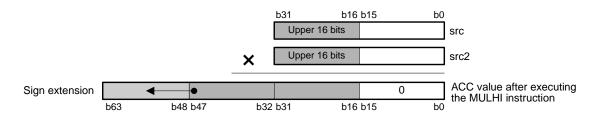

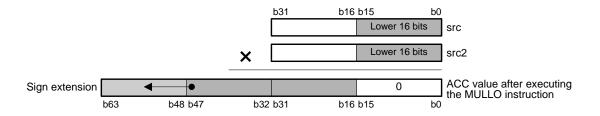

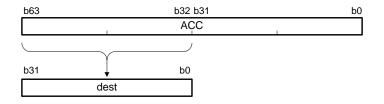

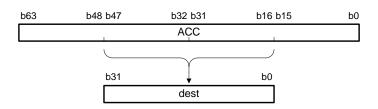

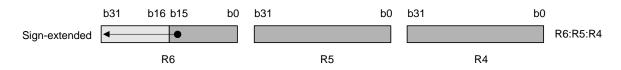

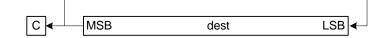

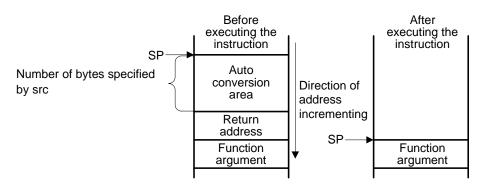

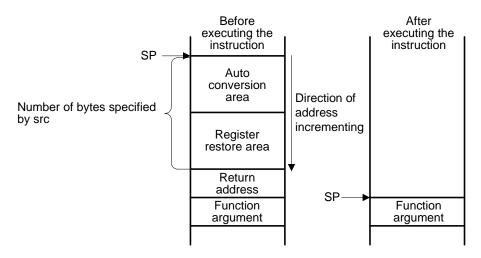

## 1.2.1 General-Purpose Registers (R0 to R15)