# Data Flash Access Library

Type T04 (Pico), European Release

16 Bit Single-chip Microcontroller RL78 Series

Installer: RENESAS\_RL78\_FDL\_T04\_xVxx

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Technology Corp. website (http://www.renesas.com).

Renesas Electronics www.renesas.com R01US0055ED0130, Rev. 1.30 Dec 27, 2023

**User Manual**

## Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

## **Regional Information**

Some information contained in this document may vary from country to country. Before using any Renesas Electronics product in your application, please contact the Renesas Electronics office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

Visit

#### http://www.renesas.com

to get in contact with your regional representatives and distributors.

| Readers           | This manual is intended for users who want to understand the functions of the concerned libraries. |                                                                                                                                                        |  |

|-------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Purpose           | This manual presents the                                                                           | ne software manual for the concerned libraries.                                                                                                        |  |

| Organization      | This document describe                                                                             | es the following sections:                                                                                                                             |  |

|                   | Architecture                                                                                       |                                                                                                                                                        |  |

|                   | Implementation and                                                                                 | d Usage                                                                                                                                                |  |

|                   | • API                                                                                              |                                                                                                                                                        |  |

| Note              | Additional remark or tip                                                                           |                                                                                                                                                        |  |

| Caution           | Item deserving extra attention                                                                     |                                                                                                                                                        |  |

| Numeric notation  | Binary: xxxx or xxxB                                                                               |                                                                                                                                                        |  |

|                   | Decimal:                                                                                           | xxxx                                                                                                                                                   |  |

|                   | Hexadecimal                                                                                        | xxxxH or 0x xxxx                                                                                                                                       |  |

| Numeric prefixes  | representing powers of                                                                             | 2 (address space, memory capacity):                                                                                                                    |  |

|                   | K (kilo):                                                                                          | 2 <sup>10</sup> = 1024                                                                                                                                 |  |

|                   | M (mega):                                                                                          | 2 <sup>20</sup> = 1024 <sup>2</sup> = 1,048,576                                                                                                        |  |

|                   | G (giga):                                                                                          | 2 <sup>30</sup> = 1024 <sup>3</sup> = 1,073,741,824                                                                                                    |  |

| Register contents | X, x = don't care                                                                                  |                                                                                                                                                        |  |

| Diagrams          | functional structure. Tin                                                                          | necessarily show the exact software flow but the<br>ning diagrams are for functional explanation purposes<br>ince to the real hardware implementation. |  |

## Preface

## How to Use This Manual

#### (1) Purpose and Target Readers

This manual is designed to provide the user with an understanding of the library itself and the functionality provided by the library. It is intended for users designing applications using libraries provided by Renesas. A basic knowledge of software systems as well as Renesas microcontrollers is necessary in order to use this manual. The manual comprises an overview of the library, its functionality and its structure, how to use it and restrictions in using the library.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer to the text of the manual for details.

#### (2) List of Abbreviations and Acronyms

| Abbreviation     | Full Form                                                                                                                                                                                                                                                                     |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| API              | Application programming interface                                                                                                                                                                                                                                             |  |

| BGO              | Background operation                                                                                                                                                                                                                                                          |  |

| Flash Area       | Area of Flash consists of several coherent Flash Blocks                                                                                                                                                                                                                       |  |

| Code Flash       | Embedded Flash where the application code or constant data is stored.                                                                                                                                                                                                         |  |

| Data Flash       | Embedded Flash where mainly the data of the EEPROM emulation are stored.                                                                                                                                                                                                      |  |

| Data Set         | Instance of data written to the Flash by the EEPROM Emulation Library (EEL), identified by the Data Set ID                                                                                                                                                                    |  |

| DS               | Data Set                                                                                                                                                                                                                                                                      |  |

| Dual Operation   | Dual operation is the capability to access flash memory<br>during reprogramming another flash memory range.<br>Dual operation is available between Code Flash and<br>Data Flash.<br>Between different Code Flash macros dual operation<br>depends on the device implementatio |  |

| ECC              | Error correction code                                                                                                                                                                                                                                                         |  |

| EEL              | EEPROM Emulation Library                                                                                                                                                                                                                                                      |  |

| EEPROM           | Electrically erasable programmable read-only memory                                                                                                                                                                                                                           |  |

| EEPROM emulation | In distinction to a real EEPROM the EEPROM emulation<br>uses some portion of the flash memory to emulate the<br>EEPROM behavior. To gain a similar behavior some<br>side parameters have to be taken in account.                                                              |  |

| FAL              | Flash Access Library (Flash access layer)                                                                                                                                                                                                                                     |  |

| FCL              | Code Flash Library (Code Flash access layer)                                                                                                                                                                                                                                  |  |

| Abbreviation       | Full Form                                                                                                                                                  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FDL                | Data Flash Library (Data Flash access layer)                                                                                                               |  |

| Firmware           | Firmware is a piece of software that is located in a hidden area of the device, handling the interfacing to the flash.                                     |  |

| Flash              | Electrically erasable and programmable nonvolatile<br>memory. The difference to ROM is, that this type of<br>memory can be re-programmed several times.    |  |

| Flash Block        | A flash block is the smallest erasable unit of the flash memory.                                                                                           |  |

| Flash Macro        | A certain number of Flash blocks is grouped together in a Flash macro.                                                                                     |  |

| FW                 | Firmware                                                                                                                                                   |  |

| ID                 | Identifier of a Data Set instance in the Renesas<br>EEPROM Emulation                                                                                       |  |

| NVM                | Non volatile memory. All memories that hold the value,<br>even when the power is cut off. E.g. Flash memory,<br>EEPROM, MRAM                               |  |

| PFDL               | Pico FDL                                                                                                                                                   |  |

| RAM                | "Random access memory" - volatile memory with<br>random access                                                                                             |  |

| REE                | Renesas Electronics Europe GmbH                                                                                                                            |  |

| REL                | Renesas Electronics Japan                                                                                                                                  |  |

| REN                | Renesas Electronics Corporation                                                                                                                            |  |

| ROM                | "Read only memory" - nonvolatile memory. The content of that memory can not be changed.                                                                    |  |

| Segment / Section  | Segment of Flash is a part of the flash that might consist<br>of several blocks. Important is, that this segment can be<br>protected against manipulation. |  |

| Self-Programming   | Capability to reprogram the embedded flash without<br>external programming tool only via control code running<br>on the microcontroller.                   |  |

| Sequencer          | Dedicated circuit controlling the flash memory (integral part of RL78 device with data flash)                                                              |  |

| Serial programming | The onboard programming mode is used to program the device with an external programmer tool.                                                               |  |

| SPL                | Flash Self-programming Library                                                                                                                             |  |

|                    |                                                                                                                                                            |  |

All trademarks and registered trademarks are the property of their respective owners.

## **Table of Contents**

| Chapter 1      | Overview                                          | 8          |

|----------------|---------------------------------------------------|------------|

| 1.1 lm         | portant Terms                                     | 8          |

| 1.2 Ba         | sic Workflow                                      | 9          |

| 1.2.1          | Library States and Transitions                    | 9          |

| 1.2.2          | Exemplary Flow                                    | 10         |

| Oh an tan 0    |                                                   | 40         |

| Chapter 2      |                                                   |            |

| -              | rdware Environment                                | -          |

| 2.1.1          | Initialization                                    |            |

| 2.1.2          | Blocks                                            |            |

|                | ftware Environment                                | -          |

| 2.2.1          | File Structure                                    |            |

| 2.2.2          | Prohibited RAM Area                               |            |

| 2.2.3          | Register Bank                                     |            |

| 2.2.4          | Stack and Data Buffer                             |            |

| 2.2.5<br>2.2.6 | Data Flash Library<br>Program Area                |            |

| 2.2.8          | Using the PFDL on the R5F10266 device             |            |

|                |                                                   |            |

| 2.5 Ca         | utions on the Programming Environment             | <b>∠</b> I |

| Chapter 3      | Data Flash Library Function                       | 23         |

| 3.1 Ty         | pe of Data Flash Library Functions                | 23         |

|                | gments of Data Flash Library Functions            |            |

|                | ommands                                           |            |

|                | ckground Operation (BGO)                          |            |

|                | st of Data Types, Return Values, and Return Types |            |

|                | scription of Data Flash Library Functions         |            |

| 3.6.1          | PFDL Open                                         |            |

| 3.6.2          | PFDL_Open                                         |            |

| 3.6.3          | PFDL Execute                                      |            |

| 3.6.4          | PFDL Handler                                      |            |

| 3.6.5          | PFDL_GetVersionString                             |            |

| 3.7 De         | scription of Data Flash Library Commands          |            |

| 3.7.1          | PFDL_CMD_READ_BYTES                               |            |

| 3.7.2          | PFDL_CMD_IVERIFY_BYTES                            |            |

| 3.7.3          | PFDL_CMD_BLANKCHECK_BYTES                         |            |

| 3.7.4          | PFDL_CMD_WRITE_BYTES                              |            |

| 3.7.5          | PFDL_CMD_ERASE_BLOCK                              | 46         |

| 3.8 Lik        | orary Timings                                     | 47         |

| 3.8.1          | Maximum Function Execution Times                  | 47         |

| 3.8.2          | Command Execution Times                           | 47         |

## **Chapter 1 Overview**

A Data Flash Library (FDL) is a software library to perform operations on the data flash memory on the RL78 microcontroller.

The library described in this manual (RL78 Data Flash Library Type 04) offers a minimal set of features and aims at very resource critical systems. It is referred to as Pico FDL (PFDL) throughout this document.

Please use this Data Flash Library user's manual together with the user's manual of the target RL78 microcontroller.

## 1.1 Important Terms

The following important terms and definitions are used throughout this manual:

- Data Flash Library (FDL)

Library for data flash memory operations utilizing the features provided by the RL78 microcontroller family.

The library cannot operate on the code flash memory.

- Flash Self-programming Library (SPL) Library for code flash memory operation utilizing the features provided by the RL78 microcontroller.

Operations on the data flash memory cannot be performed.

- *EEPROM Emulation Library* Library that provides functions to store data in the built-in flash memory in an EEPROM-like fashion.

- *Block number* Number that identifies a block of the flash memory. It is the unit of erasure operations in the Data Flash Library Type 04.

- Internal verification

Is used to check if the signal level of the flash memory cell is appropriate

after writing to the flash memory in order to ensure full data retention.

- Sequencer The RL78 microcontroller features a dedicated circuit for controlling the flash memory. In this document, this circuit is called "sequencer."

- Background operation (BGO)

State in which rewriting of the flash memory can be done while operating the user program by letting the sequencer control the flash memory. For a more detailed description, please refer to "2.1 Hardware Environment" and "3.4 Background Operation (BGO)."

- Status check

Using the sequencer in BGO requires to check the state of the sequencer (state of control for the flash memory) within the program controlling the flash memory. In this document, the processing to check the state of the sequencer is called "status checking."

## 1.2 Basic Workflow

In order to perform rewriting of the data flash memory with the PFDL, the initialization process for the library needs to be executed first. Afterwards, the actual accesses to the data flash can be performed by means of dedicated API functions.

The PFDL provides APIs for the C and assembly language of the CA78K0R, IAR V1.xx, IAR V2.xx, GNU, CC-RL and LLVM tool chains.

The PFDL for IAR V2.xx tool chain (except linker sample file) can also be used with the IAR V3.xx or later version tool chains.

## 1.2.1 Library States and Transitions

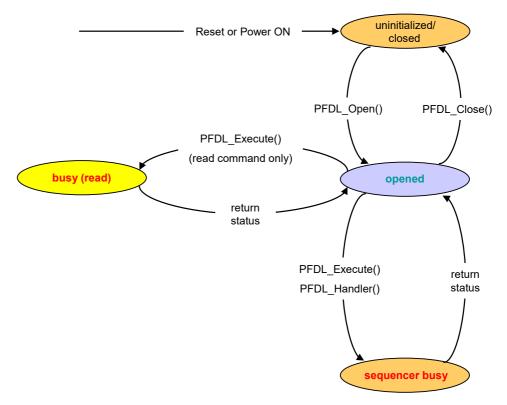

During operation, the PFDL passes through several states as illustrated in the diagram presented in Figure 1-1.

Figure 1-1 State transition diagram of Data Flash Library Type 04

To operate the data flash memory by using the PFDL, the provided functions need to be executed sequentially. Thereby, the library state can be controlled. A detailed description of each state is given below:

1. uninitialized/closed

State at Power ON and Reset. In this state, the Pico FDL is disabled. Please drive the library to this state via PFDL\_Close whenever you want to

- execute the Flash Self-programming Library,

- run an EEPROM Emulation Library,

- use a Data Flash Library other than Type 04 (PFDL), or

- utilize a STOP or HALT command.

Please note that the execution of PFDL\_Close has to be completed before any of these listed actions can be taken.

2. opened

State in which the PFDL\_Open function has been executed from the uninitialized/closed state and the Data Flash Library is operational.

3. busy (read)

State in which the specified processing is being executed directly by the library. The control does not return to the user program until the processing is completed. Please note that the transition to this state is only triggered by the read command in the PFDL.

4. sequencer busy

State in which the specified processing is being executed with the sequencer. The PFDL\_Execute function is used to trigger various commands to be executed on the data flash memory and returns to the user program without waiting for the completion of the sequencer operation. The current status of a running operation in the sequencer can be checked and driven forward with the PFDL\_Handler function.

## 1.2.2 Exemplary Flow

Figure 1-2 shows an example of the data flash memory rewriting flow by using the PFDL. In the following, a more detailed description is given of the illustrated steps:

- <1> Initializing the PFDL The PFDL\_Open function is called to initialize the RAM used for the PFDL and to enable the library.

- <2> Blank checking 1 to 1024 bytes for the specified address (PFDL\_CMD\_BLANKCHECK\_BYTES command) The PFDL\_Execute function (with the PFDL\_CMD\_BLANKCHECK\_BYTES command specified) is called to perform blank checking of 1 to 1024 bytes for the specified address. The processing cannot be executed across blocks.

- <3> Erasing the specified block (1 KB) (PFDL\_CMD\_ERASE\_BLOCK command) The PFDL\_Execute function (with the PFDL\_CMD\_ERASE\_BLOCK command specified) is called to erase the specified block (1 KB).

- <4> Writing 1 to 1024-byte data to the specified address (PFDL\_CMD\_WRITE\_BYTES command) The PFDL\_Execute function (with the PFDL\_CMD\_WRITE\_BYTES command specified) is called to write 1 to 1024 bytes to the specified address. The processing cannot be executed across blocks.

- <5> Internal verification of 1 to 1024 bytes for the specified address (PFDL\_CMD\_IVERIFY\_BYTES command) The PFDL\_Execute function (with the PFDL\_CMD\_IVERIFY\_BYTES command specified) is called to perform internal verification of 1 to 1024 bytes for the specified address. The processing cannot be executed across blocks.

- <6> Reading 1 to 1024 bytes from the specified address (PFDL\_CMD\_READ\_BYTES command) The PFDL\_Execute function (with the PFDL\_CMD\_READ\_BYTES command

The PFDL\_Execute function (with the PFDL\_CMD\_READ\_BYTES command specified) is called to read 1 to 1024 bytes for the specified address. All the processing of reading is executed within the PFDL\_Execute function.

- <7> Ending the PFDL operation The PFDL\_Close function is called to end the operation of the PFDL.

- <8> Status checking

The PFDL\_Handler function is called to perform status checking and drive a running command. Status checking must be performed until the control to the data flash memory by the sequencer is finished.

Note 1 Please note that the presented flow is only an example. It is *not* mandatory to perform a blankcheck before an erase, if you are sure that you want to erase the block in any case. The erase command performs an automatic blankcheck. Please see Section 3.7.5 for details.

For a regular write however, please follow the suggested sequence of blankcheck/write/iverify in order to ensure full data retention.

A detailed description of all PFDL API functions can be found in Section 3.6, while all commands that can be triggered via PFDL\_Execute are explained in Section 3.7.

## **Chapter 2 Programming Environment**

This chapter describes the hardware environment and software environment required to rewrite the data flash memory using the Data Flash Library Type 04 (PFDL).

## 2.1 Hardware Environment

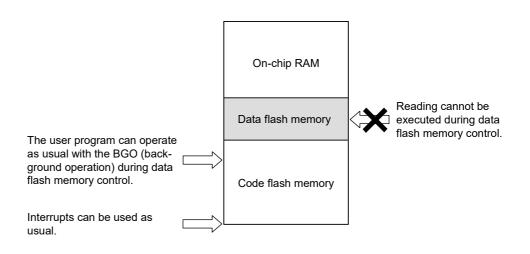

The PFDL for the RL78 microcontroller uses the sequencer to control the Data Flash memory. As the sequencer has the direct control to the data flash memory, the user program can be operated in parallel to the data flash memory control. This is called BGO (background operation).

During rewriting of the data flash memory, the data flash memory is blocked for other accesses. However, the code flash memory can be accessed, so interrupt processing, the user program, and the PFDL can be allocated in the ROM for operation as usual.

The access restrictions during data flash operations are depicted in Figure 2-1.

Figure 2-1 Access restrictions during Data Flash operation

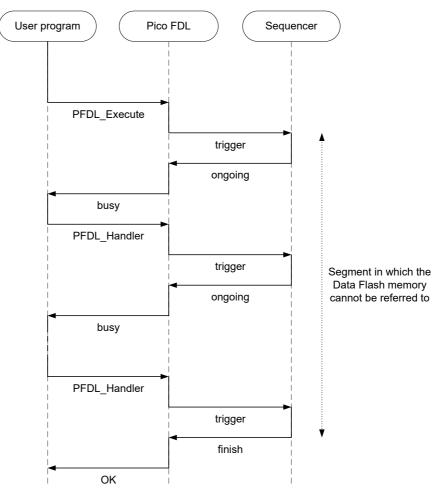

Figure 2-2 shows an example of execution of the Data Flash Library function to perform rewriting of the data flash memory.

After an execution request has been send to the sequencer of the RL78 microcontroller via the PFDL API, the control is immediately returned to the user program. For the current state and result of the issued FDL command, the status check function (PFDL\_Handler function) must be called repeatedly from the user program. Please note that there are commands which require a calling PFDL\_Handler to drive the command execution (see Section 3.4 for details). The actual number of handler calls required to finish a command is not predictable as it depends on the type of command, the parameters and the time interval between the calls.

Figure 2-2 Exemplary sequencer control via PFDL

## 2.1.1 Initialization

Before accessing the Data Flash memory by using the PFDL, the following settings need to be performed:

- 1. Starting the high-speed on-chip oscillator During the usage of the PFDL, keep the high-speed on-chip oscillator running. When the oscillator is stopped, start the oscillator before using the PFDL.

- Setting the CPU operating frequency<sup>Note1</sup>

In order to perform the timing calculation used in the PFDL, set the CPU operating frequency during the initialization. A detailed description of the method that can be used to set the frequency can be found in Section 3.6.1 PFDL\_Open.

- 3. Setting the flash memory programming mode <sup>Note2</sup> In order to specify the flash memory programming mode when writing the data flash memory, select one of the following modes during the initialization.

- Full-speed mode

- Wide voltage mode

A detailed description of the method that can be used to set the flash memory programming mode can be found in Section 3.6.1 PFDL\_Open.

RENESAS

- **Note 1** The CPU operating frequency is used for the parameters of the timing calculation within the PFDL. The actual frequency of the processor core is not changed.

- **Note 2** For the details of the flash memory programming mode, see the target RL78 microcontroller user's manual.

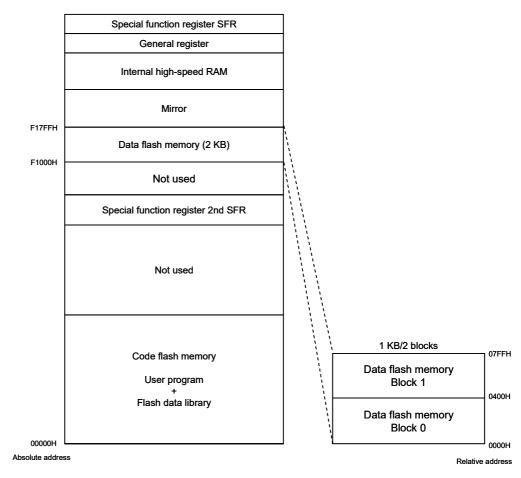

## 2.1.2 Blocks

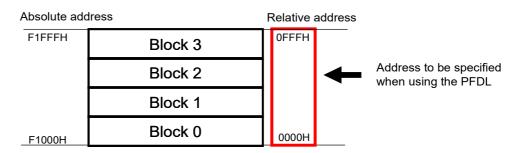

The flash memory of the RL78 microcontroller is divided into 1-KB blocks. In the Data Flash Library, erasure processing is performed for the data flash memory in the units of the blocks.

Reading, writing, blank checking or internal verification are performed on byte granularity and require the specification of start address<sup>Note</sup> and size.

Figure 2-3 shows an example of block positions and block numbers of the data flash memory.

**Note** The address value is used when reading/writing data from/to the flash memory. The address is specified relative to the first element of block 0 of the data flash memory. Note that the specified address is not an absolute address.

Figure 2-3 Blocks of Data Flash Memory (here: RL78/G12 with 2 KB Data Flash)

## 2.2 Software Environment

The PFDL is allocated together with the program in the user area, occupying an area equal to the size of the library. Furthermore, the library itself uses the CPU, the stack, and a data buffer.

Detailed information about the required software resources is listed in Table 2-1.

|                                 | CA78K0R   | IAR V1.xx | IAR V2.xx | GNU       | CC-RL     | LLVM      |

|---------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| Max code size<br>(program area) | 177 bytes | 180 bytes | 168 bytes | 200 bytes | 168 bytes | 168 bytes |

| Constants<br>(program area)     | -         | -         | -         | -         | -         | -         |

| Internal data                   | _Note2    | _Note2    | _Note2    | _Note2    | _Note2    | _Note2    |

| Max. stack<br>consumption       | 46 bytes  | 46 bytes  | 40 bytes  | 50 bytes  | 40 bytes  | 40 bytes  |

Table 2-1 Resource consumption<sup>Note1</sup>

- Note1 All values for resource consumption are based on PFDL version V1.05.

- **Note2** Depending on the used device, the PFDL may use a fraction of the user RAM as working area. Size and location of this area is strictly device dependent, see Section 2.2.2 for more details.

## 2.2.1 File Structure

The actual file structure for the Data Flash Library T04 depends on the utilized tool chain and is listed separately for CA78K0R, IAR V1.xx, IAR V2.xx, GNU, CC-RL and LLVM in Table 2-2, Table 2-3, Table 2-4, Table 2-5, Table 2-6 and Table 2-7 respectively.

Please note that assembler header files for GNU and LLVM use the same extension '.h' as C header files, because the C preprocessor can and should be used for assembler files in the GNU and LLVM tool chains.

| <root></root>                      |                                       |  |

|------------------------------------|---------------------------------------|--|

| Release.txt                        | Library release notes                 |  |

| support.txt                        | Library support information           |  |

| <root>\CA78K0R_xxx\lib</root>      |                                       |  |

| pfdl.h                             | PFDL interface definition (Compiler)  |  |

| pfdl_types.h                       | PFDL types definition (Compiler)      |  |

| pfdl.inc                           | PFDL interface definition (Assembler) |  |

| pfdl.lib                           | Pre-compiled library                  |  |

| <root>\CA78K0R_xxx\Sample\C</root> |                                       |  |

| pfdl_sample_linker_file.dr         | Sample linker file                    |  |

Table 2-2 File structure for CA78K0R tool chain

Table 2-3 File structure for IAR V1.xx tool chain

| <root></root>                  |                                       |  |

|--------------------------------|---------------------------------------|--|

| Release.txt                    | Library release notes                 |  |

| support.txt                    | Library support information           |  |

| <root>\IAR_1xx\lib</root>      |                                       |  |

| pfdl.h                         | PFDL interface definition (Compiler)  |  |

| pfdl_types.h                   | PFDL types definition (Compiler)      |  |

| pfdl.inc                       | PFDL interface definition (Assembler) |  |

| pfdl.r87                       | Pre-compiled library                  |  |

| <root>\IAR_1xx\Sample\C</root> |                                       |  |

| pfdl_sample_linker_file.xcl    | Sample linker file                    |  |

| Table 2-4 File structure | for IAR V2.xx tool chain |

|--------------------------|--------------------------|

|--------------------------|--------------------------|

| <root></root>                  |                                       |

|--------------------------------|---------------------------------------|

| Release.txt                    | Library release notes                 |

| support.txt                    | Library support information           |

| <root>\IAR_2xx\lib</root>      |                                       |

| pfdl.h                         | PFDL interface definition (Compiler)  |

| pfdl_types.h                   | PFDL types definition (Compiler)      |

| pfdl.inc                       | PFDL interface definition (Assembler) |

| pfdl.a                         | Pre-compiled library                  |

| <root>\IAR_2xx\Sample\C</root> |                                       |

| pfdl_sample_linker_file.icf    | Sample linker file                    |

Table 2-5 File structure for GNU tool chain

| <root></root>                   |                                       |  |  |

|---------------------------------|---------------------------------------|--|--|

| Release.txt                     | Library release notes                 |  |  |

| support.txt                     | Library support information           |  |  |

| <root>\GNU_xxxx\lib</root>      |                                       |  |  |

| pfdl.h                          | PFDL interface definition (Compiler)  |  |  |

| pfdl_types.h                    | PFDL types definition (Compiler)      |  |  |

| pfdl_asm.h                      | PFDL interface definition (Assembler) |  |  |

| pfdl.a                          | Pre-compiled library                  |  |  |

| <root>\GNU_xxxx\Sample\C</root> |                                       |  |  |

| pfdl_sample_linker_file.ld      | Sample linker file                    |  |  |

Table 2-6 File structure for CC-RL tool chain

| <root></root>                   |                                       |  |  |

|---------------------------------|---------------------------------------|--|--|

| Release.txt                     | Library release notes                 |  |  |

| support.txt                     | Library support information           |  |  |

| <root>\CCRL_xxx\lib</root>      |                                       |  |  |

| pfdl.h                          | PFDL interface definition (Compiler)  |  |  |

| pfdl_types.h                    | PFDL types definition (Compiler)      |  |  |

| pfdl.inc                        | PFDL interface definition (Assembler) |  |  |

| pfdl.lib                        | Pre-compiled library                  |  |  |

| <root>\CCRL_xxx\Sample\C</root> |                                       |  |  |

| pfdl_sample_linker_file.sub     | Sample linker file                    |  |  |

| Table 2-7 File structure for L | LVM tool chain |

|--------------------------------|----------------|

|--------------------------------|----------------|

| <root></root>                    |                                       |  |  |

|----------------------------------|---------------------------------------|--|--|

| Release.txt                      | Library release notes                 |  |  |

| support.txt                      | Library support information           |  |  |

| <root>\LLVM_xxxx\lib</root>      |                                       |  |  |

| pfdl.h                           | PFDL interface definition (Compiler)  |  |  |

| pfdl_types.h                     | PFDL types definition (Compiler)      |  |  |

| pfdl_asm.h                       | PFDL interface definition (Assembler) |  |  |

| libpfdl.a                        | Pre-compiled library                  |  |  |

| <root>\LLVM_xxxx\Sample\C</root> |                                       |  |  |

| pfdl_sample_linker_file.ld       | Sample linker file                    |  |  |

## 2.2.2 Prohibited RAM Area

The PFDL may use a fraction of the user RAM as working area, referred as prohibited RAM area. The size and position of this area is strictly device dependent (many devices do not even have this area) and vary between the different RL78 products. For details, please refer to the document "User's Manual: Hardware" of your RL78 product.

If a prohibited RAM area is specified for the utilized device, it is not allowed to access this area while the PFDL is active. Whenever PFDL functions are called, the data in the prohibited area may be rewritten.

## 2.2.3 Register Bank

The CA78K0R, IAR V1.xx, IAR V2.xx, CC-RL and LLVM releases of the PFDL use the registers of the currently selected register bank. No implicit register bank switch is performed by the library.

For the GNU release of the PFDL, it is mandatory that register bank 0 is active on function entry. No implicit register bank switch is performed by the library. Return values are placed in register bank 1. For details on GNU calling conventions, please refer to the GNU documentation for RL78 devices.

**Remark** A detailed description of the registers used for parameter passing and return values can be found in Section 3.6 Description of Data Flash Library Functions.

## 2.2.4 Stack and Data Buffer

The PFDL uses the sequencer to write to the data flash memory, but it uses the CPU for pre-setting and control. Therefore, the PFDL also utilizes the stack specified by the user program.

- **Remark** To allocate the stack and data buffer to the user-specified address, the link directive is used.

- Stack

In addition to the stack used by the user program, the stack space required for flash functions must be reserved in advance. It has to be ensured that the stack is allocated so that the RAM used by the user will not be destroyed during stack processing of the PFDL. The stack may not be allocated in the short address range from FFE20H to FFEFFH—and also not in the prohibited RAM area, if it exists in the target device. For the actual stack space required for the Data Flash Library functions, please refer to Table 2-1.

- Data buffer

- The usage of the data buffer is described in following:

- Work area for internal processing of the PFDL

- RAM area in which data is located that is to be written into the data flash

- RAM area in which data is located that is to be obtained from the data flash

The data buffer may not be allocated in the short address range from FFE20H to FFEFFH—and also not in the prohibited RAM area, if it exists in the target device.

Please note that the allocation and usage of the data buffer falls into the responsibility of the user. Especially it has to be ensured that the data buffer is not touched by any other part of the user application while a read or write command accessing this buffer is still running.

## 2.2.5 Data Flash Library

Not all Data Flash Library functions are linked. Only the really utilized Data Flash Library functions are linked  $^{\mbox{Note}}.$

- Memory allocation of the PFDL Segments are assigned to the functions and variables used in the PFDL. The used areas of the PFDL can be mapped to specific locations. For details, refer to 3.2 Segments of Data Flash Library Functions.

- **Note** For the CA78K0R and CC-RL assembler, linking can be reduced to a subset of the Data Flash Library functions by deleting unnecessary functions from the include file.

#### 2.2.6 Program Area

This is the area in which the PFDL and the user program using the PFDL are located.

Utilizing the PFDL for the RL78 microcontroller, the user program can be operated during rewriting of the Data Flash memory, because the Data Flash memory is controlled by the sequencer in the background (background operation).

For details, refer to the sections of Chapter 3 Data Flash Library Function.

#### 2.2.7 Using the PFDL on the R5F10266 device

For the R5F10266 device, RAM is a scarce resource. The device comes with 256 bytes RAM which cannot be used completely by the PFDL. Hence special care has to be taken for a proper RAM usage by a dedicated linking method.

**Note** Due to the limited memory resource—especially for the stack—the usage of interrupts is prohibited for the R5F10266 device when the PFDL is used.

Table 2-8 shows the usage for the different RAM areas on the R5F10266 device when using the PFDL.

| Address<br>range     | Size<br>(byte) | Description                      | Usage and Limitations                                                                                                                                                                          |

|----------------------|----------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0xFFE00 –<br>0xFFE1F | 32             | Free area                        | Please allocate your PFDL function arguments, and data buffers in this area.                                                                                                                   |

| 0xFFE20 –<br>0xFFEA1 | 130            | Short-address<br>area            | Do not allocate any PFDL function argument, data buffer or stack in this area.                                                                                                                 |

| 0xFFEA2 –<br>0xFFEDF | 62             | Stack allocation<br>area         | Please allocate the stack into this area<br>when using R5F10266.<br>Please ensure that the stack does not<br>exceed this area (including library and<br>user application, see also Table 2-1). |

| 0xFFEE0 –<br>0xFFEFF | 32             | General-purpose<br>register area | Do not allocate any PFDL function argument, data buffer or stack in this area.                                                                                                                 |

| Table 2-8 | RAM | usage | for | R5F | 10266 | when | using | PFDL |

|-----------|-----|-------|-----|-----|-------|------|-------|------|

|-----------|-----|-------|-----|-----|-------|------|-------|------|

## 2.3 Cautions on the Programming Environment

- 1. Library code must be located completely in the same 64k flash page.

- 2. The PFDL library initialization by PFDL\_Open must be performed before the execution of PFDL\_Close, PFDL\_Execute, PFDL\_Handler.

- 3. It is not allowed to read the data flash during a command execution of the PFDL.

- 4. It is not possible to modify the Data Flash in parallel to a modification of the Code Flash.

- 5. Do not execute the Flash Self-programming Library, EEPROM Emulation Library, or Data Flash Library other than Type 04 during the execution of the PFDL. When using the Flash Self-programming Library, EEPROM Emulation Library, or Data Flash Library other than Type 04, be sure to execute PFDL\_Close to close the PFDL.

- 6. Do not execute the STOP command mode or HALT command mode during the execution of the PFDL. If the STOP command or HALT command needs to be executed, be sure to execute the PFDL\_Close function to close the PFDL.

- 7. The watchdog timer does not stop during the execution of the PFDL.

- 8. Do not allocate any PFDL function argument, data buffer or stack used by the Data Flash Library to an address over 0xFFE20 or in the prohibited RAM area (if existent for your target device).

- 9. When using the data transfer controller (DTC) during the execution of the PFDL, do not allocate the RAM area used by the DTC to an address over 0xFFE20 or in the prohibited RAM area (if existent for your target device).

- 10. Do not use the RAM area (including the prohibited RAM area) used by the PFDL until the library is closed.

- 11. Do not execute a Data Flash Library function within interrupt processing because the PFDL does not support multiple executions of a Data Flash Library function.

- 12. When executing the PFDL within an operating system, do not execute a Data Flash Library function from multiple tasks, because the PFDL does not support multiple executions of a Data Flash Library function.

- 13. Before initiating any operation with the PFDL, the high-speed on-chip oscillator needs to be started.

- 14. Note the following regarding the operating frequency of the RL78 microcontroller and the operating frequency value set with the initialization function (PFDL\_Open).

- When a frequency below 4 MHz<sup>Note1</sup> is used as the operating frequency of the RL78 microcontroller, 1 MHz, 2 MHz, or 3 MHz can be used (a frequency such as 1.5 MHz that is not an integer value cannot be used). Also, set an integer value such as 1, 2, or 3 as the operating frequency value set with the initialization function.

- When a frequency over 4 MHz<sup>Note1</sup> is used as the operating frequency of the RL78 microcontroller, a frequency with decimal places can be used. However, specify a rounded up integer value as the operating frequency set with the initialization function (PFDL\_Open). Example: For 4.5 MHz, set "5" with the initialization function.

- The operating frequency is not the frequency of the high-speed on-chip oscillator.

- 15. The PFDL does not perform error checking of the parameters set in the argument of a Data Flash Library function. Therefore, make sure to set a correct value to the parameter after checking the specifications of the target RL78 microcontroller. If parameter checking is required to set a correct value, perform it in the user program.

- 16. Please initialize all function arguments (including unused structure elements) at least once before calling a function. Otherwise, a RAM parity error may cause a reset of the device. For details, please refer to the document "User's Manual: Hardware" of your RL78 product.

- 17. Do not write to a data flash cell that is not erased. It is prohibited to rewrite a data flash cell without erasing the corresponding data flash block first. The PFDL does not contain any sanity checks to prevent such a situation. The user is responsible to ensure the compliance of this rule.

- 18. The data flash control register (DFLCTL) should not be operated during the execution of the PFDL. In addition, when the operation of the PFDL is ended, the DFLCTL is set to access inhibit state by the PFDL\_Close function. If accessing the data flash memory is required even after the operation of the PFDL is ended, verify the completion of the PFDL\_Close function, set the DFLCTL to the access permit state and perform the setup<sup>Note2</sup>.

- 19. After the execution of PFDL\_Close, all requested/running commands will be aborted and cannot be resumed. The user has to take care that all running commands are finished before calling PFDL\_Close.

- 20. When using an assembler of the CC-RL compiler from Renesas Electronics, the hexadecimal prefix representation (0x..) cannot be mixed together with the suffix representation (..H). Specify the representation method by editing the symbol definition in pfdl.inc to match the user environment.

- pfdl.inc

When symbol "\_\_PFDL\_INC\_BASE\_NUMBER\_SUFFIX " is not defined (initial state), the prefix representation will be selected.

pfdl.inc

\_\_PFDL\_INC\_BASE\_NUMBER\_SUFFIX .SET 1

When symbol "\_\_PFDL\_INC\_BASE\_NUMBER\_SUFFIX" is defined, the suffix representation will be selected.

- 21. Additional cautions on using the PFDL for IAR V2.xx or LLVM

- The version string provided by the flash library includes the information on the supported compiler. The string indicates that the supported compiler is CC-RL because the library file for IAR V2.xx and LLVM are identical to the one for CC-RL.

- **Note 1** For the range of the operating frequency, see the target RL78 microcontroller user's manual.

- Note 2 For the method of the setup, see the target RL78 microcontroller user's manual.

## Chapter 3 Data Flash Library Function

This chapter describes the details of the Data Flash Library functions.

## 3.1 Type of Data Flash Library Functions

The PFDL provides the following flash functions as listed in Table 3-1.

| Function name         | Description                                                                                                                      |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|

| PFDL_Open             | Initialization of the RAM used by the PFDL, enabling of the Data Flash                                                           |

| PFDL_Close            | Ending the operation of the PFDL, disabling of the Data Flash                                                                    |

| PFDL_Execute          | Triggering and execution of commands on the Data Flash memory                                                                    |

| PFDL_Handler          | Checking of the current status of a running Data Flash<br>operation and driving the command forward<br>(status check processing) |

| PFDL_GetVersionString | Acquisition of the version information of the PFDL                                                                               |

Table 3-1 List of Data Flash Library functions

## 3.2 Segments of Data Flash Library Functions

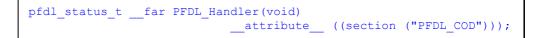

The Data Flash Library functions are located in the following segment:

• PFDL\_COD: Segment of the Data Flash Library functions. It can be allocated to the ROM or RAM.

## 3.3 Commands

All flash operations are issued in the PFDL via the PFDL\_Execute function. The command specified as argument of PFDL\_Execute determines the type of the flash operation. Table 3-2 lists all available commands. For details on the execution method, please refer to Section 3.6.3.

| Definition                | Value | Command name                  |

|---------------------------|-------|-------------------------------|

| PFDL_CMD_READ_BYTES       | 0x00  | Read command                  |

| PFDL_CMD_BLANKCHECK_BYTES | 0x08  | Blank check command           |

| PFDL_CMD_ERASE_BLOCK      | 0x03  | Erasure command               |

| PFDL_CMD_WRITE_BYTES      | 0x04  | Write command                 |

| PFDL_CMD_IVERIFY_BYTES    | 0x06  | Internal verification command |

Table 3-2 List of commands specified for PFDL\_Execute (pfdl\_command\_t)

## 3.4 Background Operation (BGO)

The Data Flash Library functions can be divided into functions that do not use the sequencer and functions that use the sequencer<sup>Note</sup>. For the functions that use the sequencer<sup>Note</sup>, background operation (BGO) can be performed.

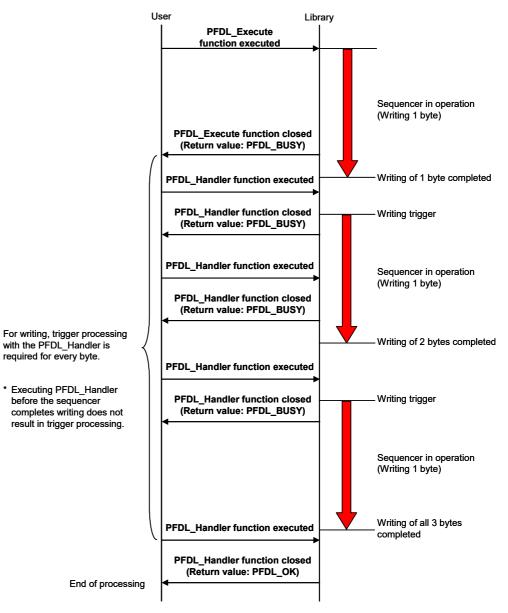

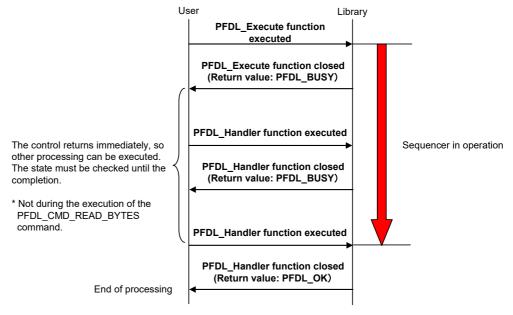

The following Figure 3-1 and Figure 3-2 show examples of operation of the PFDL during BGO. Please note that especially for a write command it is mandatory to call the PFDL\_Handler not only to check the command progress, but also to drive the command.

Table 3-3 shows a list of the API functions with their relation to the sequencer control.

Note Not during the execution of the PFDL\_CMD\_READ\_BYTES command.

Figure 3-1 Background operation example 1 (write: 3 byte)

RENESAS

Figure 3-2 Background operation example 2 (erase, iverify, blankcheck)

Table 3-3 List of interrupt reception and BGO of Data Flash Library functions

| Function name         | Sequencer control /<br>BGO function | Interrupt reception |

|-----------------------|-------------------------------------|---------------------|

| PFDL_Open             | No                                  |                     |

| PFDL_Close            | NO                                  |                     |

| PFDL_Execute          | Yes <sup>Note</sup>                 | Allowed             |

| PFDL_Handler          | restore                             |                     |

| PFDL_GetVersionString | No                                  |                     |

**Note** Not during the execution of the PFDL\_CMD\_READ\_BYTES command.

## 3.5 List of Data Types, Return Values, and Return Types

The data types are listed in Table 3-4. The return types are specified in Table 3-5, while the meaning of each return value is given in Table 3-6.

| Definition        | Data type         | Description                                                                                                    |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------------|

| pfdl_u08          | unsigned char     | 1-byte (8-bit) unsigned integer                                                                                |

| pfdl_u16          | unsigned int      | 2-byte (16-bit) unsigned integer                                                                               |

| pfdl_u32          | unsigned long int | 4-byte (32-bit) unsigned integer                                                                               |

| pfdl_status_t     | enumeration type  | set of 1-byte (8-bit) unsigned integer constants (see also Table 3-6)                                          |

| pfdl_command_t    | enumeration type  | set of 1-byte (8-bit) unsigned integer constants <sup>Note 1</sup> (see also Table 3-2)                        |

| pfdl_request_t    | structure         | structure to specify requests to be<br>executed on the data flash <sup>Note 1</sup> (see<br>also Table 3-7)    |

| pfdl_descriptor_t | structure         | structure to specify the configuration for<br>library initialization <sup>Note 2</sup> (see also Table<br>3-7) |

| Table | 3-4 | List | of | data | types |

|-------|-----|------|----|------|-------|

|-------|-----|------|----|------|-------|

Note 1 A detailed description can be found in Section 3.6.3 PFDL\_Execute.

**Note 2** A detailed description can be found in Section 3.6.1 PFDL\_Open.

|           | Return value  |                          |  |

|-----------|---------------|--------------------------|--|

|           | C language    | Assembly language        |  |

| CAZOKOD   | pfdl_status_t | С                        |  |

| CA78K0R   | far pfdl_u08* | DE:BC                    |  |

|           | pfdl_status_t | A                        |  |

| IAR V1.xx | pfdl_u08far*  | A:HL                     |  |

|           | pfdl_status_t | A                        |  |

| IAR V2.xx | pfdl_u08far * | A:DE                     |  |

| CNU       | pfdl_status_t | R8 (X on bank 1)         |  |

| GNU       | pfdl_u08far*  | R11:R8 (BC:AX on bank 1) |  |

|           | pfdl_status_t | A                        |  |

| CC-RL     | far pfdl_u08* | A:DE                     |  |

|           | pfdl_status_t | A                        |  |

| LLVM      | far pfdl_u08* | A:DE                     |  |

Table 3-5 List of return types

| Definition          | Return<br>value | Description                                                                                                     |

|---------------------|-----------------|-----------------------------------------------------------------------------------------------------------------|

| PFDL_OK             | 0x00            | Normal completion                                                                                               |

| PFDL_ERR_PROTECTION | 0x10            | Reserved for future usage                                                                                       |

| PFDL_ERR_ERASE      | 0x1A            | Erasure error                                                                                                   |

|                     |                 | • Erasure of the target area failed.                                                                            |

| PFDL_ERR_MARGIN     | 0x1B            | Blank check error or Internal verification error                                                                |

|                     |                 | <ul> <li>The target area is not in the blank state.</li> </ul>                                                  |

|                     |                 | <ul> <li>An error occurred during internal<br/>verification processing of the target<br/>area.</li> </ul>       |

| PFDL_ERR_WRITE      | 0x1C            | Writing error                                                                                                   |

|                     |                 | • Writing to the target area failed.                                                                            |

| PFDL_IDLE           | 0x30            | Idle state                                                                                                      |

|                     |                 | <ul> <li>No command is executed in the<br/>PFDL_Execute function.</li> </ul>                                    |

| PFDL_BUSY           | 0xFF            | Execution start of the PFDL_Execute function command, or in execution                                           |

|                     |                 | <ul> <li>The command specified in the<br/>PFDL_Execute function is in<br/>execution.</li> </ul>                 |

| Other than above    | Other           | Other error                                                                                                     |

|                     | than<br>above   | <ul> <li>An abnormal return value. Check<br/>the specified command or resource<br/>allocation again.</li> </ul> |

Table 3-6 List of pfdl\_status\_t values

| Structure         | Member                            | Description                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | pfdl_u16 index_u16                | <ul> <li>Target area</li> <li>Erasure: block number</li> <li>Other: start address of the target area</li> </ul>                                                                                                                                                                                                                                                |

|                   | pfdl_u08* data_pu08<br>(near)     | Pointer to the data buffer for<br>acquisition of data to be written or<br>read. Only used for read/write<br>commands                                                                                                                                                                                                                                           |

| pfdl_request_t    | pfdl_u16 bytecount_u16            | Number of bytes to be transferred<br>starting from the start byte<br>specified in index_u16. The byte<br>count range is from 1 byte to 1024<br>bytes. Please note, that the<br>execution of the<br>read/write/blankcheck/internal<br>verify command across block<br>boundaries is not allowed. This<br>struct member is not required for<br>the erase command. |

|                   | pfdl_command_t<br>command_enu     | Command to be executed                                                                                                                                                                                                                                                                                                                                         |

|                   | pfdl_u08 fx_MHz_u08               | The CPU operating frequency                                                                                                                                                                                                                                                                                                                                    |

| pfdl_descriptor_t | pfdl_u08<br>wide_voltage_mode_u08 | The flash memory programming mode setting                                                                                                                                                                                                                                                                                                                      |

Table 3-7 List of structures

## 3.6 Description of Data Flash Library Functions

The flash functions are described in the following format.

- Outline Describes the purpose of the function.

- Interface Describes the C interfaces and assembler labels required to access the function.

- Arguments Describes the parameters, return values and register usage of the function.

- **Precondition** Describes the conditions that have to be fulfilled before calling the function.

- **Description** Describes the function details and cautions of this function.

## 3.6.1 PFDL\_Open

Outline Initialization of all internal data and activation of the data flash.

#### Interface C interface for CA78K0R compiler

#### C interface for IAR V1.xx compiler

```

__far_func pfdl_status_t PFDL_Open(__near pfdl_descriptor_t

___near* descriptor_pstr);

```

#### C interface for IAR V2.xx compiler

```

__far_func pfdl_status_t PFDL_Open(pfdl_descriptor_t

__near * descriptor_pstr);

```

#### C interface for GNU compiler

#### C interface for CC-RL compiler

C interface for LLVM compiler

## ASM function label for CA78K0R, IAR V1.xx, IAR V2.xx, GNU, CC-RL and LLVM assembler

PFDL\_Open

## Arguments Parameters

| Argument                     | Description                                                                                                                      |    |    |       |    |      |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----|----|-------|----|------|

| descriptor_pstr              | address of the descriptor variable located in the RAM, defines the flash memory programming mode and the CPU operating frequency |    |    |       |    |      |

|                              | Registers                                                                                                                        |    |    |       |    |      |

| Туре                         | CA78K0R IAR V1.xx IAR V2.xx GNU CC-RL LLVM                                                                                       |    |    |       |    | LLVM |

| pfdl_descriptor_t*<br>(near) | AX                                                                                                                               | AX | AX | stack | AX | AX   |

#### Structures

| Structure         | Member                         | Description                               |  |

|-------------------|--------------------------------|-------------------------------------------|--|

| ofdi descriptor t | pfdl_u08 fx_MHz_u08            | The CPU operating<br>frequency            |  |

| pfdl_descriptor_t | pfdl_u08 wide_voltage_mode_u08 | The flash memory programming mode setting |  |

## Return value

| Туре          | Description |                                                       |              |                  |       |      |

|---------------|-------------|-------------------------------------------------------|--------------|------------------|-------|------|

|               |             | Status of operation,<br>PFDL_OK (only possible value) |              |                  |       |      |

|               |             | Registers                                             |              |                  |       |      |

| pfdl_status_t | CA78K0R     | IAR<br>V1.xx                                          | IAR<br>V2.xx | GNU              | CC-RL | LLVM |

|               | С           | А                                                     | А            | R8<br>(X bank 1) | A     | A    |

## **Destructed registers**

| Tool chain | Destructed registers |

|------------|----------------------|

| CA78K0R    | AX                   |

| IAR V1.xx  | Х                    |

| IAR V2.xx  | X, HL, C             |

| GNU        | none                 |

| CC-RL      | X, HL, C             |

| LLVM       | X, HL, C             |

RENESAS

**Preconditions** The following conditions need to be ensured before using PFDL\_Open

- The Flash Self-programming Library, the EEPROM Emulation Library, or any Data Flash Library other than Type 04 are not running or have been closed.

- The high-speed on-chip oscillator is running.

**Description** By calling PFDL\_Open, the Data Flash Library is put into operational state and the data flash of the RL78 device is activated.

PFDL\_Open reserves and initializes the prohibited RAM area<sup>Note 1</sup> used for the PFDL. If a prohibited RAM area<sup>Note 1</sup> exists, do not use it until the PFDL is closed.

For correct operation, the flash memory programming mode<sup>Note 2</sup> of the PFDL needs to be specified in the wide\_voltage\_mode\_u08 structure member of the argument pfdl\_descriptor\_t:

- 00H: Full-speed mode

- 01H: Wide voltage mode

Furthermore, the operating frequency of the CPU needs to be set in the fx\_MHz\_u08 structure member of the argument pfdl\_descriptor\_t. This parameter is used for the calculation of timing data in the PFDL<sup>Note 3</sup>. For the value of the operating frequency of the CPU (fx\_MHz\_u08), note the following:

- When a frequency below 4 MHz<sup>Note 4</sup> is used as the operating frequency of the RL78 microcontroller, only integer frequencies (1 MHz, 2 MHz, or 3 MHz) can be used. Frequencies with decimal fraction (e.g. 1.5 MHz) are not supported. The value of fx\_MHz\_u08 has to match the actual operating frequency of the device.