## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

発行日: 2009 年 03月 09日

# **RENESAS TECHNICAL UPDATE**

〒100-0004 東京都千代田区大手町 2-6-2 日本ビル 株式会社 ルネサス テクノロジ

問合せ窓口 http://japan.renesas.com/inquiry E-mail: csc@renesas.com

|     |              |                                                           | 1      |                                                                   |                  |         |     |

|-----|--------------|-----------------------------------------------------------|--------|-------------------------------------------------------------------|------------------|---------|-----|

| 製品  | 製品分類 MPU&MCU |                                                           | 発行番号   | TN-H8*-A401A/J                                                    |                  | Rev.    | 第1版 |

| 題名  |              | 548、H8SX/1648A、H8SX/1648L、H8SX/16486<br>プハードウェアマニュアルの誤記訂正 | 情報分類   | 技術資料                                                              |                  |         |     |

| 適   |              |                                                           | 対象ロット等 |                                                                   | H8SX/1648, H8SX/ | ′1648A, |     |

| 用製品 |              | 648、 H8SX/1648A 、 H8SX/1648L 、<br>.648G、H8SX/1648H グループ   | 全ロット   | 関連資料   H8SX/1648L,1<br>  H8SX/1648H<br>  グループハー<br>  (RJJ09B0397- |                  | アマニュ    | アル  |

H8SX/1648、H8SX/1648A、H8SX/1648L、H8SX/1648G、H8SX/1648H グループハードウェアマニュアル において 誤記がありましたので、ご案内申し上げます。

#### <誤記訂正内容>

## 1. 概要

(1) 頁 1-8 「表 1.3 製品一覧表」を以下のように訂正します。

〔変更前〕

| 製品グループ          | 製品型名            | ROM 容量    | RAM 容量  | パッケージ     | 備考 |

|-----------------|-----------------|-----------|---------|-----------|----|

| H8SX/1648 グループ  | R5F61648N50FPV  | 1024K バイト | 56K バイト | LQFP-144  | -  |

|                 | R5F61644N50FPV  | 512K バイト  | 40K バイト | LQFP-144  |    |

|                 | R5F61642N50FPV  | 256K バイト  | 24K バイト | LQFP-144  |    |

| H8SX/1648A グループ | R5F61648AN50FPV | 1024K バイト | 56K バイト | LQFP-144  | -  |

|                 | R5F61644AN50FPV | 512K バイト  | 40K バイト | LQFP-144  |    |

|                 | R5F61642AN50FPV | 256K バイト  | 24K バイト | LQFP-144  |    |

| H8SX/1648G グループ | R5F61648GN50BGV | 1024K バイト | 56K バイト | LFBGA-176 | -  |

|                 | R5F61644GN50BGV | 512K バイト  | 40K バイト | LFBGA-176 |    |

|                 | R5F61642GN50BGV | 256K バイト  | 24K バイト | LFBGA-176 |    |

| H8SX/1648L グループ | R5F61648LN50FPV | 1024K バイト | 56K バイト | LQFP-144  | -  |

|                 | R5F61644LN50FPV | 512K バイト  | 40K バイト | LQFP-144  |    |

|                 | R5F61642LN50FPV | 256K バイト  | 24K バイト | LQFP-144  |    |

| H8SX/1648H グループ | R5F61648HN50BGV | 1024K バイト | 56K バイト | LFBGA-176 | -  |

|                 | R5F61644HN50BGV | 512K バイト  | 40K バイト | LFBGA-176 |    |

|                 | R5F61642HN50BGV | 256K バイト  | 24K バイト | LFBGA-176 |    |

## 〔変更後〕

| 製品グループ          | 製品型名            | ROM 容量    | RAM 容量  | パッケージ     | 備考    |

|-----------------|-----------------|-----------|---------|-----------|-------|

| H8SX/1648 グループ  | R5F61648N50FPV  | 1024K バイト | 56K バイト | LQFP-144  | 通常仕様品 |

|                 | R5F61644N50FPV  | 512K バイト  | 40K バイト | LQFP-144  | 1     |

|                 | R5F61642N50FPV  | 256K バイト  | 24K バイト | LQFP-144  | 1     |

|                 | R5F61648D50FPV  | 1024K バイト | 56K バイト | LQFP-144  | 広温度範囲 |

|                 | R5F61644D50FPV  | 512K バイト  | 40K バイト | LQFP-144  | 仕様品   |

|                 | R5F61642D50FPV  | 256K バイト  | 24K バイト | LQFP-144  | 1     |

| H8SX/1648A グループ | R5F61648AN50FPV | 1024K バイト | 56K バイト | LQFP-144  | 通常仕様品 |

|                 | R5F61644AN50FPV | 512K バイト  | 40K バイト | LQFP-144  |       |

|                 | R5F61642AN50FPV | 256K バイト  | 24K バイト | LQFP-144  |       |

|                 | R5F61648AD50FPV | 1024K バイト | 56K バイト | LQFP-144  | 広温度範囲 |

|                 | R5F61644AD50FPV | 512K バイト  | 40K バイト | LQFP-144  | 仕様品   |

|                 | R5F61642AD50FPV | 256K バイト  | 24K バイト | LQFP-144  |       |

| H8SX/1648G グループ | R5F61648GN50BGV | 1024K バイト | 56K バイト | LFBGA-176 | 通常仕様品 |

|                 | R5F61644GN50BGV | 512K バイト  | 40K バイト | LFBGA-176 |       |

|                 | R5F61642GN50BGV | 256K バイト  | 24K バイト | LFBGA-176 |       |

|                 | R5F61648GD50BGV | 1024K バイト | 56K バイト | LFBGA-176 | 広温度範囲 |

|                 | R5F61644GD50BGV | 512K バイト  | 40K バイト | LFBGA-176 | 仕様品   |

|                 | R5F61642GD50BGV | 256K バイト  | 24K バイト | LFBGA-176 |       |

| H8SX/1648L グループ | R5F61648LN50FPV | 1024K バイト | 56K バイト | LQFP-144  | 通常仕樣品 |

|                 | R5F61644LN50FPV | 512K バイト  | 40K バイト | LQFP-144  |       |

|                 | R5F61642LN50FPV | 256K バイト  | 24K バイト | LQFP-144  |       |

|                 | R5F61648LD50FPV | 1024K バイト | 56K バイト | LQFP-144  | 広温度範囲 |

|                 | R5F61644LD50FPV | 512K バイト  | 40K バイト | LQFP-144  | 仕様品   |

|                 | R5F61642LD50FPV | 256K バイト  | 24K バイト | LQFP-144  | 1     |

| H8SX/1648H グループ | R5F61648HN50BGV | 1024K バイト | 56K バイト | LFBGA-176 | 通常仕様品 |

|                 | R5F61644HN50BGV | 512K バイト  | 40K バイト | LFBGA-176 |       |

|                 | R5F61642HN50BGV | 256K バイト  | 24K バイト | LFBGA-176 |       |

|                 | R5F61648HD50BGV | 1024K バイト | 56K バイト | LFBGA-176 | 広温度範囲 |

|                 | R5F61644HD50BGV | 512K バイト  | 40K バイト | LFBGA-176 | 仕様品   |

|                 | R5F61642HD50BGV | 256K バイト  | 24K バイト | LFBGA-176 | 7     |

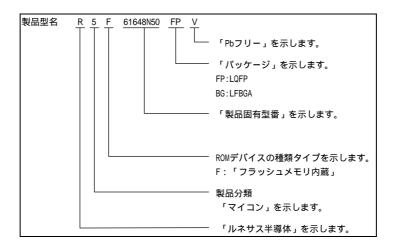

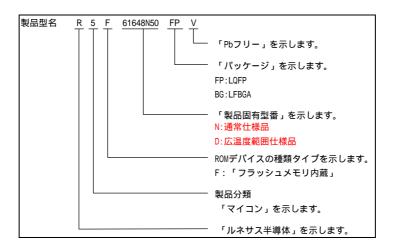

(2) 頁 1-8 「図 1.1 製品型名の読み方」を以下のように訂正します。

〔変更前〕

[変更後]

(3) 頁 1-22 「表 1.5 端子機能」において、16 ビットパルスタイマユニット(TPU)の TIOCA0 ~ TIOCD0 の記述を 以下のように訂正します。

〔変更前〕

| 分類                             | 端子名                                  | 入出力 | 機能                                                       |

|--------------------------------|--------------------------------------|-----|----------------------------------------------------------|

| 16 ビット<br>タイマパルス<br>ユニット (TPU) | TIOCA0<br>TIOCB0<br>TIOCC0<br>TIOCD0 | 入出力 | TGRA_0~TGRD_3 のインプットキャプチャ入力/アウトプットコンペア<br>出力/PWM 出力端子です。 |

[変更後]

| 分類        | 端子名    | 入出力 | 機能                                               |

|-----------|--------|-----|--------------------------------------------------|

| 16 ビット    | TIOCA0 | 入出力 | TGRA_0~ <b>TGRD_0</b> のインプットキャプチャ入力 / アウトプットコンペア |

| タイマパルス    | TIOCB0 |     | 出力/PWM 出力端子です。                                   |

| ユニット(TPU) | TIOCC0 |     |                                                  |

|           | TIOCD0 |     |                                                  |

## 5. 電圧検出回路(LVD)

(1) 頁 5-4 「5.3.2 電圧監視割り込み」において、本文の記述を以下のように訂正します。

〔変更前〕

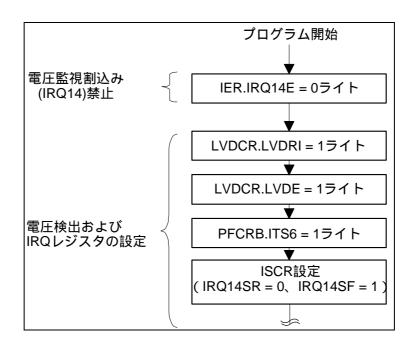

IRQ14 の設定は、PFCRB の ITS6 ビットに 1、IER の IRQ14E ビットに 1、ISCR の IRQ14SR、IRQ14SF に 01 (立ち下がりエッジ割り込み要求) を設定してください。

#### [変更後]

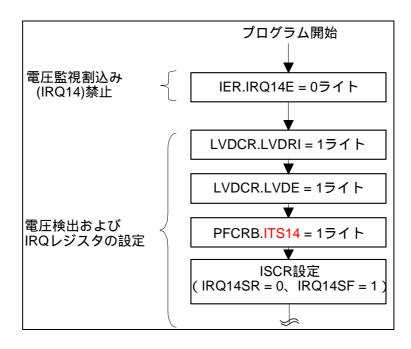

IRQ14 の設定は、PFCRB の ITS14 ビットに 1、IER の IRQ14E ビットに 1、ISCR の IRQ14SR、IRQ14SF に 01 (立ち下がりエッジ割り込み要求) を設定してください。

(2) 頁 5-6 「図 5.4 電圧監視割り込みの設定手順例」において、図の電圧検出および IRQ レジスタの設定手順の記述を以下のように訂正します。

[変更前]

## [変更後]

## 7. 割込みコントローラ

(1) 頁 7-15 ISR のビット 15 の説明を以下のように訂正します。

#### [変更前]

| ビット | ビット名   | 初期値 | R/W      | 説 明                                                                                                                                |

|-----|--------|-----|----------|------------------------------------------------------------------------------------------------------------------------------------|

| 15  | IRQ15F | 入出力 | R/(W)* 1 | IRQ15 として使用する場合: [セット条件] 【省略(修正無し)】 [クリア条件] 【省略(修正無し)】 ・IRQn 割り込みにより DTC が起動され、DTC の MRB の DISELが 0 のとき   TM32K*2:32K0VI として使用する場合 |

|     |        |     |          | 【省略(修正無し)】                                                                                                                         |

#### [変更後]

| ビット | ビット名   | 初期値 | R/W      | 説 明                                        |

|-----|--------|-----|----------|--------------------------------------------|

| 15  | IRQ15F | 入出力 | R/(W)* 1 | IRQ15 として使用する場合:                           |

|     |        |     |          | [ セット条件 ]                                  |

|     |        |     |          | 【省略(修正無し)】                                 |

|     |        |     |          | [ クリア条件 ]                                  |

|     |        |     |          | 【省略(修正無し)】                                 |

|     |        |     |          | ・IRQ15 割り込みにより DTC が起動され、DTC の MRB の DISEL |

|     |        |     |          | が 0 のとき                                    |

|     |        |     |          | TM32K*2:32K0VI として使用する場合                   |

|     |        |     |          | 【省略(修正無し)】                                 |

(2) 頁 7-18 7.4.1 外部割込み要因 (1)NMI 割込み の項目を以下のように訂正します。

#### 〔変更前〕

- ・DTC の DTCCR の ERR ビットを 1 にセット

- ・DMAC の DMDR 0 の ERRF ビットを 1 にセット

- ・EXDMAC\*の DMDR\_0 の ERRF ビットを 1 にセット

- ・DMAC の全チャネルの DMDR の DTE ビットを 0 にクリア、および強制転送終了

- ・EXDMAC\*の全チャネルの DMDR の DTE ビットを 0 にクリア、および強制転送終了

- 【注】\*H8SX/1648G グループ、H8SX/1648H グループのみサポート。

#### [変更後]

- ・DTC の DTCCR の ERR ビットを 1 にセット

- ・DMAC の DMDR\_0 の ERRF ビットを 1 にセット

- ・EXDMAC\*の EDMDR\_0 の ERRF ビットを 1 にセット

- ・DMAC の全チャネルの DMDR の DTE ビットを 0 にクリア、および強制転送終了

- ・EXDMAC\*の全チャネルの EDMDR の DTE ビットを 0 にクリア、および強制転送終了

- 【注】\*H8SX/1648G グループ、H8SX/1648H グループのみサポート。

- (3) 頁 7-33, 頁 7-34「7.6.5 割り込みによる DTC、DMAC の起動」の記述から、DTCERG、DTCERH を削除します。 〔変更前〕

- (1) 割り込み要因の選択

DMAC の各チャネルの起動要因は、DMRSR により選択します。選択した起動要因は、選択回路を経由して DMAC に入力されます。内蔵モジュール割り込みによる転送が有効になるように設定 (DMDR のビット設定: DTF1=1、DTF0=0、DTE=1)、DMDR の DTA ビットが 1 にセットされていると、その DMAC の起動要因になった割り込み要因は DMAC が管理することになり、DTC の起動要因および CPU の割り込み要因になりません。

DMAC に管理されている割り込み以外の割り込み要因は、DTC の DTCERA~DTCERH の DTCE ビットにより、DTC 起動要因とするか、CPU 割り込み要因とするかを選択します。

(省略 ~変更無し~)

(2) 優先順位判定

(省略 ~変更無し~)

(3) 動作順序

(省略 ~変更無し~)

表 7.6 に、DMAC の DMDR の DTA ビット、DTC の DTCERA~DTCERH の DTCE ビット、および MRB の DISEL ビットの設定による割り込み要因の選択と割り込み要因クリア制御を示します。

#### [変更後]

(1) 割り込み要因の選択

DMAC の各チャネルの起動要因は、DMRSR により選択します。選択した起動要因は、選択回路を経由して DMAC に入力されます。内蔵モジュール割り込みによる転送が有効になるように設定(DMDR のビット設定: DTF1=1、DTF0=0、DTE=1)、DMDR の DTA ビットが 1 にセットされていると、その DMAC の起動要因になった割り込み要因は DMAC が管理することになり、DTC の起動要因および CPU の割り込み要因になりません。

DMAC に管理されている割り込み以外の割り込み要因は、DTC の DTCERA~DTCERF の DTCE ビットにより、DTC 起動要因とするか、CPU 割り込み要因とするかを選択します。

(省略 ~変更無し~)

(2) 優先順位判定

(省略 ~変更無し~)

(3) 動作順序

(省略 ~変更なし~)

表 7.6 に、DMAC の DMDR の DTA ビット、DTC の DTCERA~DTCERF の DTCE ビット、および MRB の DISEL ビットの設定による割り込み要因の選択と割り込み要因クリア制御を示します。

<u>13.I/O ポート</u>

(1) 頁 13-9 「表 13.2 各ポートのレジスタ構成」の表と記述を以下のように訂正します。

〔変更前〕

| ポート                                       | 端子数            | レジスタ         |    |      |     |     |     |

|-------------------------------------------|----------------|--------------|----|------|-----|-----|-----|

|                                           |                | DDR          | DR | PORT | ICR | PCR | ODR |

| ポート 1<br>~ ポート 3                          |                | ~説明省略(変更なし)~ |    |      |     |     |     |

| ポート 4                                     | 4              | -            | -  |      |     | -   | -   |

| ポート 5<br>~ ポート B                          | ~ 説明省略(変更なし) ~ |              |    |      |     |     |     |

| ポート C *1                                  | 6              |              |    |      |     | -   | -   |

| ポートD <sup>*2</sup><br>~ポートK <sup>*3</sup> | ~ 説明省略(変更なし) ~ |              |    |      |     |     |     |

| ポート M *4                                  | 5              |              |    |      |     | -   | -   |

| ポートN                                      | 4              |              |    |      |     | -   | -   |

【記号説明】 ○:レジスタあり、-:レジスタなし

- 【注】\*1 ライト時は、初期値をライトしてください。

- \*2 PCJKE=1 のときはアクセスしないでください。

- \*3 PCJKE=0のときはアクセスしないでください。

- \*4 H8SX/1648G グループ、H8SX/1648H グループのみサポート。

〔変更後〕

| ポート                                        | 端子数            | レジスタ |       |                    |     |     |     |

|--------------------------------------------|----------------|------|-------|--------------------|-----|-----|-----|

|                                            |                | DDR  | DR    | PORT               | ICR | PCR | ODR |

| ポート 1<br>~ ポート 3                           |                | ~ [  | 説明省略( | 変更なし) <sup>-</sup> | _   |     |     |

| ポート 4 <sup>*5</sup>                        | 4              | -    | -     |                    |     | -   | -   |

| ポート 5<br>~ ポート B                           | ~ 説明省略(変更なし) ~ |      |       |                    |     |     |     |

| ポート C *1                                   | 6              |      |       |                    |     | -   | -   |

| ポートD <sup>*2</sup><br>~ ポートK <sup>*3</sup> | ~ 説明省略(変更なし) ~ |      |       |                    |     |     |     |

| ポート M *4 *6                                | 5              |      |       |                    |     | -   | -   |

| ポート N *7                                   | 4              |      |       |                    |     | -   | -   |

【記号説明】 ○:レジスタあり、一:レジスタなし

- 【注】\*1 ポート C は、下位 6 ビットが有効で、上位 2 ビットはリザーブビットです。ライト時は、初期値をライトしてください。

- \*2 PCJKE=1 のときはアクセスしないでください。

- \*3 PCJKE=0 のときはアクセスしないでください。

- \*4 H8SX/1648G グループ、H8SX/1648H グループのみサポート。

- \*5 ポート4は、上位4ビットが有効で、下位4ビットはリザーブビットです。ライト時は、初期値をライトしてください。

- \*6 ポートMは、下位5ビットが有効で、上位3ビットはリザーブビットです。ライト時は、初期値をライトしてください。

- \*7 ポートNは、下位4ビットが有効で、上位4ビットはリザーブビットです。ライト時は、初期値をライトしてください。

(2) 頁 13-20 13.2.3 ポート 3 (2) P36/PO14/TIOCA2/EDRAK2 \* の設定に関する記述を、以下のように訂正します。 〔変更前〕

(2) P36/PO14/TIOCA2/EDRAK2 \*

EXDMAC\*、TPU、PPG のレジスタの設定、および P37DDR ビットの組み合わせにより、次のように切り替わります。

| モジュール名  | 端子機能              | 設定         |                     |         |        |  |  |  |  |

|---------|-------------------|------------|---------------------|---------|--------|--|--|--|--|

|         |                   | EXDMAC*    | EXDMAC* TPU PPG I/O |         |        |  |  |  |  |

|         |                   | EDRAK2_OE* | TIOCB2_OE           | PO14_OE | P36DDR |  |  |  |  |

| EXDMAC* | EDRAK2 出力*        | 1          | -                   | -       | -      |  |  |  |  |

| TPU     | TPU TIOCB2 出力 0 1 |            |                     |         |        |  |  |  |  |

|         | ~ 以下省略(変更なし) ~    |            |                     |         |        |  |  |  |  |

## 〔変更後〕

(2) P36/PO14/TIOCA2/EDRAK2 \*

**EXDMAC\***、**TPU**、**PPG** のレジスタの設定、および**P36DDR** ビットの組み合わせにより、次のように切り替わります。

| モジュール名  | 端子機能              | 設定        |                        |         |        |  |  |  |  |

|---------|-------------------|-----------|------------------------|---------|--------|--|--|--|--|

|         |                   | EXDMAC*   | EXDMAC* TPU PPG I/O ポー |         |        |  |  |  |  |

|         |                   | EDRAK2_OE | TIOCA2_OE              | PO14_OE | P36DDR |  |  |  |  |

| EXDMAC* | EDRAK2 出力         | 1         | -                      | -       | -      |  |  |  |  |

| TPU     | TPU TIOCA2 出力 0 1 |           |                        |         |        |  |  |  |  |

|         | ~ 以下省略(変更なし) ~    |           |                        |         |        |  |  |  |  |

(3) 頁 13-24 13.2.5 ポート 6 (1) P67 /IRQ15-B/EDRAK1-B \* の設定に関する記述を、以下のように訂正します。

## 〔変更前〕

- (1) P67 /IRQ15-B/EDRAK1-B \*

- ・H8SX/1648 グループ

| モジュール名         | 端子機能 | 設定      |         |  |  |  |  |  |

|----------------|------|---------|---------|--|--|--|--|--|

|                |      | SCI     | I/O ポート |  |  |  |  |  |

|                |      | SCK6_OE | P6nDDR  |  |  |  |  |  |

| ~ 以下省略(変更なし) ~ |      |         |         |  |  |  |  |  |

・H8SX/1648G グループ、H8SX/1648H グループ

| モジュール名         | 端子機能 | 設定         |         |  |

|----------------|------|------------|---------|--|

|                |      | EXDMAC *   | I/O ポート |  |

|                |      | EDRAK1B_OE | P6nDDR  |  |

| ~ 以下省略(変更なし) ~ |      |            |         |  |

#### [変更後]

- (1) P67 /IRQ15-B/EDRAK1-B \*

- ・H8SX/1648 グループ

| モジュール名         | 端子機能 | 設定             |         |  |  |

|----------------|------|----------------|---------|--|--|

|                |      | SCI            | I/O ポート |  |  |

|                |      | SCK6_OE P67DDR |         |  |  |

| ~ 以下省略(変更なし) ~ |      |                |         |  |  |

・H8SX/1648G グループ、H8SX/1648H グループ

| モジュール名         | 端子機能 | 設定         |         |  |

|----------------|------|------------|---------|--|

|                |      | EXDMAC *   | I/O ポート |  |

|                |      | EDRAK1B_OE | P67DDR  |  |

| ~ 以下省略(変更なし) ~ |      |            |         |  |

(4) 頁 13-25 13.2.4 ポート 6 (2) P66 / $\overline{\text{EDRAK0}}$ -B \* の設定に関する記述を、以下のように訂正します。

〔変更前〕

- (2) P66 /EDRAKO-B \*

- ・H8SX/1648 グループ

| モジュール名         | 端子機能 | 設定             |         |  |  |

|----------------|------|----------------|---------|--|--|

|                |      | SCI            | I/O ポート |  |  |

|                |      | TxD6_OE P6nDDR |         |  |  |

| ~ 以下省略(変更なし) ~ |      |                |         |  |  |

・H8SX/1648G グループ、H8SX/1648H グループ

| モジュール名         | 端子機能 | 設定                 |         |  |

|----------------|------|--------------------|---------|--|

|                |      | EXDMAC *           | I/O ポート |  |

|                |      | EDRAK0B_OE* P6nDDR |         |  |

| ~ 以下省略(変更なし) ~ |      |                    |         |  |

## 〔変更後〕

- (2) P66 /EDRAKO-B \*

- ・H8SX/1648 グループ

| モジュール名         | 端子機能 | 設定             |         |  |  |

|----------------|------|----------------|---------|--|--|

|                |      | SCI            | I/O ポート |  |  |

|                |      | TxD6_OE P66DDR |         |  |  |

| ~ 以下省略(変更なし) ~ |      |                |         |  |  |

・H8SX/1648G グループ、H8SX/1648H グループ

| モジュール名         | 端子機能 | 設定                 |         |  |

|----------------|------|--------------------|---------|--|

|                |      | EXDMAC *           | I/O ポート |  |

|                |      | EDRAKOB_OE* P66DDR |         |  |

| ~ 以下省略(変更なし) ~ |      |                    |         |  |

(5) 頁 13-27 13.2.5 ポート 6 (5) P63/TMRI3/DREQ3/EDREQ1-B\*2/IRQ11-B/TxD6/TMS の説明に関する記述を、 以下のように訂正します。

[変更前]

$(5)\ P63/TMRI3/\overline{DREQ3}/\overline{EDREQ1} - B^{*2}\ /\overline{IRQ11} - B/TxD6/TMS$

動作モード、DSCIのレジスタの設定、およびP63DDRビットの組み合わせにより、次のように切り替わります。

[変更後]

(5)  $P63/TMRI3/\overline{DREQ3}/\overline{EDREQ1}$ - $B^{*2}/\overline{IRQ11}$ -B/TxD6/TMS

動作モード、SCIのレジスタの設定、およびP63DDRビットの組み合わせにより、次のように切り替わります。

(6) 頁 13-33,34 13.2.7 ポート B の PB7、PB4 の記述を、以下のように訂正します。

〔変更前〕

(1) PB7/ $\overline{\text{CS7}}$ -D/SD  $\phi$  \*3

| モジュール名         | 端子機能 | 設定                         |  |  |  |

|----------------|------|----------------------------|--|--|--|

|                |      | MCU 動作モード バスコントローラ I/O ポート |  |  |  |

|                |      | SDRAM CS7D_OE PB7DDR       |  |  |  |

| ~ 以下省略(変更なし) ~ |      |                            |  |  |  |

#### (4) PB4/<del>CS4</del>-B/<del>WE</del>\*2

| モジュール名         | 端子機能 | 設定                        |  |  |  |

|----------------|------|---------------------------|--|--|--|

|                |      | バスコントローラ I/O ポート バスコントローラ |  |  |  |

|                |      | WE_OE                     |  |  |  |

| ~ 以下省略(変更なし) ~ |      |                           |  |  |  |

#### 〔変更後〕

(1) PB7/ $\overline{\text{CS7}}$ -D/SD  $\phi$  \*3

| モジュール名         | 端子機能 | 設定                   |  |  |  |

|----------------|------|----------------------|--|--|--|

|                |      | MCU 動作モード I/O ポート    |  |  |  |

|                |      | SDRAM CS7D_OE PB7DDR |  |  |  |

| ~ 以下省略(変更なし) ~ |      |                      |  |  |  |

## $(4) \quad PB4/\overline{\text{CS4}}\text{-}B/\overline{\text{WE}}^{*2}$

| モジュール名         | 端子機能 | 設定                      |  |  |  |

|----------------|------|-------------------------|--|--|--|

|                |      | バスコントローラ <b>I/O ポート</b> |  |  |  |

|                |      | WE_OE CS4B_OE PB4DDR    |  |  |  |

| ~ 以下省略(変更なし) ~ |      |                         |  |  |  |

(7) 頁 13-69 PFCR9 のビット 7 の説明を以下のように訂正します。

〔変更前〕

13.3.8 ポートファンクションコントロールレジスタ 9 (PFCR9)

| ビット | ビット名   | 初期値 | R/W | 説明                 |

|-----|--------|-----|-----|--------------------|

| 7   | TPUMS5 | 0   | R/W | TPU 入出力端子マルチ機能セレクト |

|     |        |     |     | TIOCS5 の機能を選択します。  |

|     |        |     |     | ~以下説明省略(変更なし)~     |

## 〔変更後〕

13.3.8 ポートファンクションコントロールレジスタ 9 (PFCR9)

| ビット | ビット名   | 初期値 | R/W | 説明                 |  |  |  |  |  |

|-----|--------|-----|-----|--------------------|--|--|--|--|--|

| 7   | TPUMS5 | 0   | R/W | TPU 入出力端子マルチ機能セレクト |  |  |  |  |  |

|     |        |     |     | TIOCA5 の機能を選択します。  |  |  |  |  |  |

|     |        |     |     | ~以下説明省略(変更なし)~     |  |  |  |  |  |

発行日: 2009年03月09日

(8) 頁 13-71 PFCRA のビット 0 の説明を以下のように訂正します。

〔変更前〕

13.3.9 ポートファンクションコントロールレジスタ A (PFCRA)

| ビット | ビット名    | 初期値 | R/W | 説明           |

|-----|---------|-----|-----|--------------|

| 1   | TPUMS6A | 0   | R/W | ~説明省略(変更なし)~ |

| 0   | TPUMS6A | 0   | R/W | ~説明省略(変更なし)~ |

[変更後]

13.3.9 ポートファンクションコントロールレジスタ A (PFCRA)

| ビット | ビット名    | 初期値 | R/W | 説明           |

|-----|---------|-----|-----|--------------|

| 1   | TPUMS6A | 0   | R/W | ~説明省略(変更なし)~ |

| 0   | TPUMS6B | 0   | R/W | ~説明省略(変更なし)~ |

#### 14. 16 ビットタイマパルスユニット(TPU)

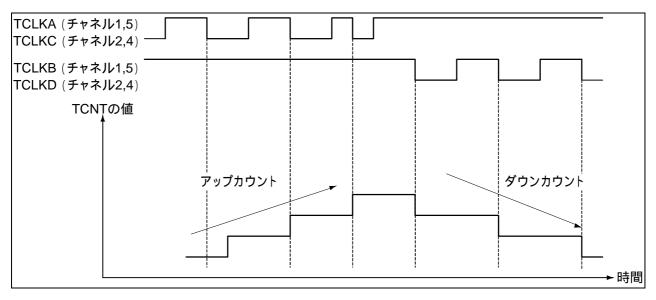

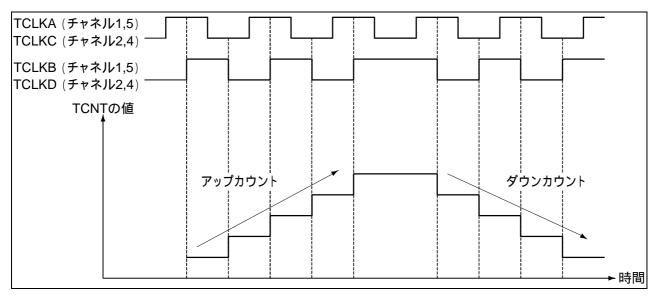

(1) 頁 14-65 「図 14.29 位相計数モード 4 の動作例」を、以下のように訂正します。

〔変更前〕

#### [変更後]

#### 15. プログラマブルパルスジェネレータ(PPG)

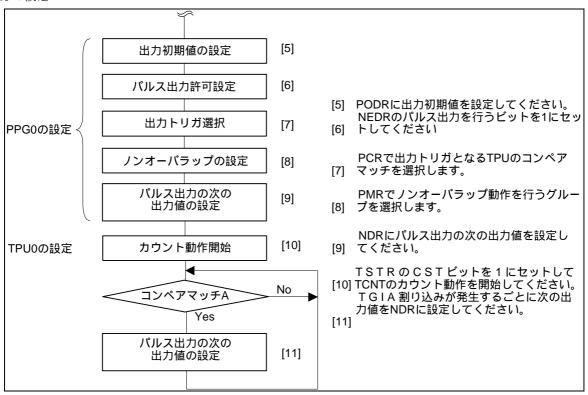

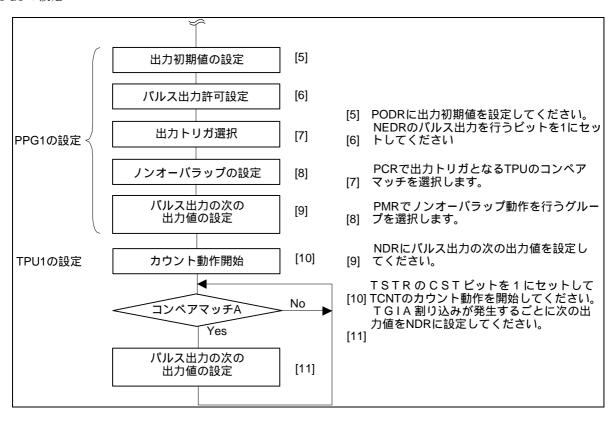

- (1) 頁 15-25 「図 15.10 パルス出力ノンオーバラップ動作の設定手順例 ( PPG0 の設定 )」を、以下のように訂正します。 〔変更前〕

- ・PPG0 の設定

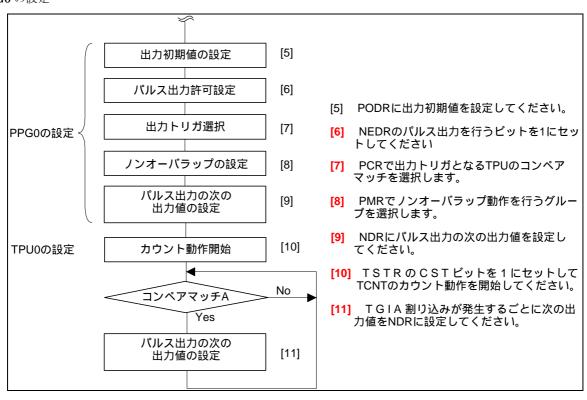

#### [変更後]

・PPG0 の設定

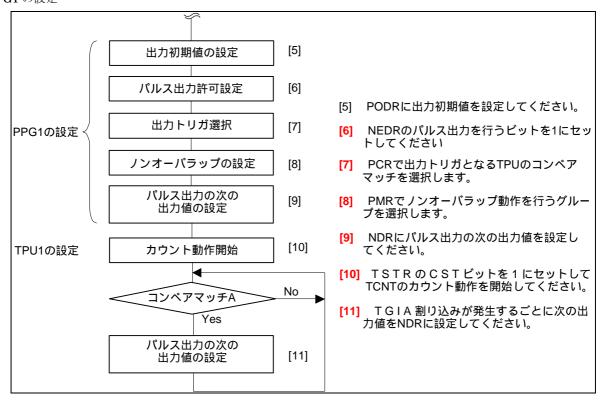

- (2) 頁 15-26 「図 15.11 パルス出力ノンオーバラップ動作の設定手順例 ( PPG1 の設定 )」を、以下のように訂正します。

- ・PPG1 の設定

〔変更前〕

#### [変更後]

・PPG1 の設定

## 21. A/D変換器

(1) 頁 21-14 ADCR\_0 のビット 3,2 の説明を以下のように訂正します。

〔変更前〕

・21.3.5 A/D コントロールレジスタ(ADCR\_0) ユニット 0

| ビット | ビット名 | 初期値 | R/W | 説明                                     |  |  |  |  |  |

|-----|------|-----|-----|----------------------------------------|--|--|--|--|--|

| 3   | CKS1 | 0   | R/W | クロックセレクト 1、0                           |  |  |  |  |  |

| 2   | CKS0 | 0   | R/W | ~説明省略(変更なし)~                           |  |  |  |  |  |

|     |      |     |     | CKS1 CKS0                              |  |  |  |  |  |

|     |      |     |     | 00:変換時間 = 530 ステート*3 (max)             |  |  |  |  |  |

|     |      |     |     | 01∶変換時間 = 266 ステート <sup>*3</sup> (max) |  |  |  |  |  |

|     |      |     |     | 10∶変換時間 = 134 ステート <sup>*3</sup> (max) |  |  |  |  |  |

|     |      |     |     | 11∶変換時間 = 68 ステート <sup>*3</sup> (max)  |  |  |  |  |  |

#### 〔変更後〕

・21.3.5 A/D コントロールレジスタ(ADCR\_0) ユニット 0

| ビット | ビット名 | 初期値 | R/W | 説明                                                  |

|-----|------|-----|-----|-----------------------------------------------------|

| 3   | CKS1 | 0   | R/W | クロックセレクト1、0                                         |

| 2   | CKS0 | 0   | R/W | ~説明省略(変更なし)~                                        |

|     |      |     |     | CKS1 CKS0                                           |

|     |      |     |     | 00∶変換時間 = <b>528</b> ステート <sup>*3</sup> (max)       |

|     |      |     |     | 01∶変換時間 = <mark>268</mark> ステート <sup>*3</sup> (max) |

|     |      |     |     | 10∶変換時間 = <b>138</b> ステート <sup>*3</sup> (max)       |

|     |      |     |     | 11∶変換時間 = <b>73</b> ステート <sup>*3</sup> (max)        |

(2) 頁 21-16 ADCR\_1 のビット 3,2 の説明を以下のように訂正します。

[変更前]

・21.3.6 A/D コントロールレジスタ(ADCR\_1) ユニット1

| ビット | ビット名         | 初期値 | R/W        | 説明                                                                                                                                                   |

|-----|--------------|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 2 | CKS1<br>CKS0 | 0 0 | R/W<br>R/W | クロックセレクト 1、0<br>~説明省略(変更なし)~<br>EXCKS CKS1 CKS0<br>000:変換時間 = 530 ステート*3 (max)<br>001:変換時間 = 266 ステート*3 (max)<br>010:変換時間 = 134 ステート*3 (max)         |

|     |              |     |            | 011:変換時間 = 68 ステート*3 (max)<br>100:変換時間 = 332 ステート*3 (max)<br>101:変換時間 = 168 ステート*3 (max)<br>110:変換時間 = 87 ステート*3 (max)<br>111:変換時間 = 46 ステート*3 (max) |

#### [変更後]

・21.3.6 A/D コントロールレジスタ(ADCR\_1) ユニット1

| ビット | ビット名 | 初期値 | R/W | 説明                                                   |

|-----|------|-----|-----|------------------------------------------------------|

| 3   | CKS1 | 0   | R/W | クロックセレクト 1、0                                         |

| 2   | CKS0 | 0   | R/W | ~説明省略(変更なし)~                                         |

|     |      |     |     | EXCKS CKS1 CKS0                                      |

|     |      |     |     | 000∶変換時間 = <mark>528</mark> ステート <sup>*3</sup> (max) |

|     |      |     |     | 001∶変換時間 = <mark>268</mark> ステート <sup>*3</sup> (max) |

|     |      |     |     | 010∶変換時間 = <b>138</b> ステート <sup>*3</sup> (max)       |

|     |      |     |     | 011∶変換時間 = <b>73</b> ステート <sup>*3</sup> (max)        |

|     |      |     |     | 100∶変換時間 = <b>336</b> ステート <sup>*3</sup> (max)       |

|     |      |     |     | 101∶変換時間 = <b>172</b> ステート <sup>*3</sup> (max)       |

|     |      |     |     | 110∶変換時間 = <mark>90</mark> ステート <sup>*3</sup> (max)  |

|     |      |     |     | 111∶変換時間 = <b>49</b> ステート <sup>*3</sup> (max)        |

(3) 頁 21-18 ADCR\_2 のビット 3,2 の説明を以下のように訂正します。

〔変更前〕

・21.3.7 A/D コントロールレジスタ(ADCR\_2) ユニット2

| ビット | ビット名 | 初期値 | R/W | 説明                                      |

|-----|------|-----|-----|-----------------------------------------|

| 3   | CKS1 | 0   | R/W | クロックセレクト 1、0                            |

| 2   | CKS0 | 0   | R/W | ~説明省略(変更なし)~                            |

|     |      |     |     | EXCKS CKS1 CKS0                         |

|     |      |     |     | 000∶変換時間 = 530 ステート <sup>*2</sup> (max) |

|     |      |     |     | 001:変換時間 = 266 ステート <sup>*2</sup> (max) |

|     |      |     |     | 010∶変換時間 = 134 ステート <sup>*3</sup> (max) |

|     |      |     |     | 011∶変換時間 = 68 ステート <sup>*3</sup> (max)  |

|     |      |     |     | 100∶変換時間 = 332 ステート <sup>*3</sup> (max) |

|     |      |     |     | 101∶変換時間 = 168 ステート <sup>*3</sup> (max) |

|     |      |     |     | 110∶変換時間 = 87 ステート <sup>*3</sup> (max)  |

|     |      |     |     | 111∶変換時間 = 46 ステート <sup>*3</sup> (max)  |

#### [変更後]

・21.3.7 A/D コントロールレジスタ(ADCR\_2) ユニット2

| ビット | ビット名 | 初期値 | R/W | 説明                                                   |

|-----|------|-----|-----|------------------------------------------------------|

| 3   | CKS1 | 0   | R/W | クロックセレクト 1、0                                         |

| 2   | CKS0 | 0   | R/W | ~説明省略(変更なし)~                                         |

|     |      |     |     | EXCKS CKS1 CKS0                                      |

|     |      |     |     | 000∶変換時間 = <b>528</b> ステート <sup>*3</sup> (max)       |

|     |      |     |     | 001∶変換時間 = <mark>268</mark> ステート <sup>*3</sup> (max) |

|     |      |     |     | 010∶変換時間 = <b>138</b> ステート <sup>*3</sup> (max)       |

|     |      |     |     | 011∶変換時間 = <b>73</b> ステート <sup>*3</sup> (max)        |

|     |      |     |     | 100∶変換時間 = <b>336</b> ステート <sup>*3</sup> (max)       |

|     |      |     |     | 101∶変換時間 = <mark>172</mark> ステート <sup>*3</sup> (max) |

|     |      |     |     | 110∶変換時間 = <mark>90</mark> ステート <sup>*3</sup> (max)  |

|     |      |     |     | 111∶変換時間 = <b>49</b> ステート <sup>*3</sup> (max)        |

(4) 頁 21-24「表 21.3 A/D 変換特性(EXCKS=0 時)」、「表 21.4 A/D 変換特性(EXCKS=1 時)(ユニット 1、ユニット 2)」を、以下のように訂正します。

〔変更前〕

表 21.3 A/D 変換特性(EXCKS=0 時)

| 項目           | 記号                | CKS1=0 |     |     |        |     |     | CKS1=1 |     |     |        |     |     |

|--------------|-------------------|--------|-----|-----|--------|-----|-----|--------|-----|-----|--------|-----|-----|

|              |                   | CKS0=0 |     |     | CKS0=1 |     |     | CKS0=0 |     |     | CKS0=1 |     |     |

|              |                   | min    | typ | max |

| A/D 変換開始遅延時間 | t <sub>D</sub>    | 18     | -   | 33  | 10     | -   | 17  | 6      | -   | 9   | 4      | -   | 5   |

| 入力サンプリング時間   | t <sub>SPL</sub>  | -      | 319 | -   | -      | 159 | -   | -      | 79  | -   | -      | 29  | -   |

| A/D 変換時間     | t <sub>CONV</sub> | 515    | -   | 530 | 259    | -   | 266 | 131    | -   | 134 | 67     | -   | 68  |

## 表 21.4 A/D 変換特性(EXCKS=1 時) (ユニット 1、ユニット 2)

| 項目           | 記号                | CKS1=0 |     |     |        |     |     | CKS1=1 |     |     |        |     |     |

|--------------|-------------------|--------|-----|-----|--------|-----|-----|--------|-----|-----|--------|-----|-----|

|              |                   | CKS0=0 |     |     | CKS0=1 |     |     | CKS0=0 |     |     | CKS0=1 |     |     |

|              |                   | min    | typ | max |

| A/D 変換開始遅延時間 | t <sub>D</sub>    | 3      | -   | 10  | 3      | -   | 6   | 3      | -   | 5   | 3      | -   | 4   |

| 入力サンプリング時間   | t <sub>SPL</sub>  | -      | 120 | -   | -      | 60  | -   | -      | 30  | -   | -      | 15  | -   |

| A/D 変換時間     | t <sub>CONV</sub> | 325    | -   | 332 | 165    | -   | 168 | 85     | -   | 87  | 45     | •   | 46  |

#### [変更後]

## 表 21.3 A/D 変換特性(ユニット 0)

| 項目           | 記号                | CKS1=0 |     |     |        |     |     | CKS1=1 |     |     |        |     |     |

|--------------|-------------------|--------|-----|-----|--------|-----|-----|--------|-----|-----|--------|-----|-----|

|              |                   | CKS0=0 |     |     | CKS0=1 |     |     | CKS0=0 |     |     | CKS0=1 |     |     |

|              |                   | min    | typ | max |

| A/D 変換開始遅延時間 | t <sub>D</sub>    | 3      | -   | 14  | 3      | -   | 10  | 3      | -   | 8   | 3      | -   | 7   |

| 入力サンプリング時間   | t <sub>SPL</sub>  | -      | 312 | -   | -      | 156 | -   | -      | 78  | -   | -      | 39  | -   |

| A/D 変換時間     | t <sub>CONV</sub> | 517    | -   | 528 | 261    | -   | 268 | 133    | -   | 138 | 69     | -   | 73  |

## 表 21.4.1 A/D 変換特性(ユニット 1、ユニット 2: EXCKS=0 時)

| 項目           | 記号                | CKS1=0 |        |     |     |        |     |     | CKS    | 1=1 |        |     |     |

|--------------|-------------------|--------|--------|-----|-----|--------|-----|-----|--------|-----|--------|-----|-----|

|              |                   | C      | CKS0=0 |     |     | CKS0=1 |     | (   | CKS0=0 | )   | CKS0=1 |     |     |

|              |                   | min    | typ    | max | min | typ    | max | min | typ    | max | min    | typ | max |

| A/D 変換開始遅延時間 | t <sub>D</sub>    | 4      | -      | 14  | 4   | -      | 10  | 4   | -      | 8   | 4      | -   | 7   |

| 入力サンプリング時間   | t <sub>SPL</sub>  | -      | 312    | -   | -   | 156    | -   | -   | 78     | -   | -      | 39  | -   |

| A/D 変換時間     | t <sub>CONV</sub> | 518    | -      | 528 | 262 | -      | 268 | 134 | -      | 138 | 70     | -   | 73  |

## 表 21.4.2 A/D 変換特性(ユニット 1、ユニット 2: EXCKS=1 時)

| 項目           | 記号                | CKS1=0 |        |     |     |        |     |     | CKS    | 1=1 |     |        |     |

|--------------|-------------------|--------|--------|-----|-----|--------|-----|-----|--------|-----|-----|--------|-----|

|              |                   | C      | CKS0=0 |     | (   | CKS0=1 |     |     | CKS0=0 | )   |     | CKS0=1 |     |

|              |                   | min    | typ    | max | min | typ    | max | min | typ    | max | min | typ    | max |

| A/D 変換開始遅延時間 | t <sub>D</sub>    | 4      | -      | 14  | 4   | -      | 10  | 4   | -      | 8   | 4   | -      | 7   |

| 入力サンプリング時間   | t <sub>SPL</sub>  | -      | 120    | -   | -   | 60     | -   | -   | 30     | -   | -   | 15     | -   |

| A/D 変換時間     | t <sub>CONV</sub> | 326    | -      | 336 | 166 | -      | 172 | 86  | -      | 90  | 46  | -      | 49  |

## 24. フラッシュメモリ

(1) 頁 24-29 「表 24.5 オンボードプログラミングモードの設定方法」のモード設定の記述を以下のように訂正します。

〔変更前〕

| モード設定         | EMLE | MD2 | MD1 | MD0 |

|---------------|------|-----|-----|-----|

| ユーザブートモード     | 0    | 0   | 0   | 1   |

| ブートモード        | 0    | 0   | 1   | 0   |

| ユーザプログラミングモード | 0    | 1   | 1   | 0   |

|               | 0    | 1   | 1   | 1   |

[変更後]

| モード設定       | EMLE | MD2 | MD1 | MD0 |

|-------------|------|-----|-----|-----|

| ユーザブートモード   | 0    | 0   | 0   | 1   |

| プートモード      | 0    | 0   | 1   | 0   |

| ユーザプログラムモード | 0    | 1   | 1   | 0   |

|             | 0    | 1   | 1   | 1   |

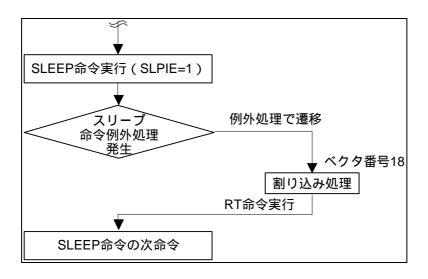

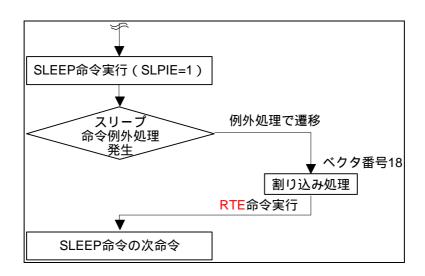

#### 27. 低消費電力

(1) 頁 27-45 「図 27.12 SLEEP 命令実行直前に解除要因割り込みが発生した場合(スリープ命令例外処理が発生する場合)」を、以下のように訂正します。

〔変更前〕

[変更後]

## 28. レジスタ一覧

(1) 頁 28-58 「28.3 各動作モードにおけるレジスタの状態」 の SYSTEM モジュールの記述を以下のように訂正します。

## 〔変更前〕

| レジスタ<br>略称     | リセット  | モジュール<br>ストップ<br>状態 | スリープ<br>モード | 全モジュール<br>クロック<br>ストップ<br>モード | ソフトウェア<br>スタンバイ<br>モード | ディープ<br>ソフトウェア<br>スタンバイ<br>モード | ハードウェア<br>スタンバイ<br>モード | モジュール  |  |

|----------------|-------|---------------------|-------------|-------------------------------|------------------------|--------------------------------|------------------------|--------|--|

| ~ 説明省略(変更なU) ~ |       |                     |             |                               |                        |                                |                        |        |  |

| DPSBYCR        | 初期化   | _                   | _           | _                             | _                      | 初期化*1                          | 初期化                    | SYSTEM |  |

| DPSWCR         | 初期化   | _                   | -           | -                             | _                      | 初期化*1                          | 初期化                    | _      |  |

| DPSIER         | 初期化   | _                   | -           | -                             | _                      | 初期化*1                          | 初期化                    | _      |  |

| DPSIFR         | 初期化   | _                   | -           | -                             | _                      | 初期化*1                          | 初期化                    | _      |  |

| DPSIEGR        | 初期化   | _                   | _           | _                             | _                      | 初期化*1                          | 初期化                    | -      |  |

| RSTSR          | 初期化   | _                   | _           | -                             | _                      | 初期化*1                          | 初期化                    | -      |  |

| LVDCR *3       | 初期化*4 | -                   | -           | _                             | _                      | _                              | 初期化                    | -      |  |

| ~ 説明省略(変更なし) ~ |       |                     |             |                               |                        |                                |                        |        |  |

## [変更後]

| レジスタ<br>略称     | リセット  | モジュール<br>ストップ<br>状態 | スリープ<br>モード | 全モジュール<br>クロック<br>ストップ<br>モード | ソフトウェア<br>スタンバイ<br>モード | ディープ<br>ソフトウェア<br>スタンバイ<br>モード | ハードウェア<br>スタンバイ<br>モード | モジュール        |  |

|----------------|-------|---------------------|-------------|-------------------------------|------------------------|--------------------------------|------------------------|--------------|--|

| ~ 説明省略(変更なし) ~ |       |                     |             |                               |                        |                                |                        |              |  |

| DPSBYCR        | 初期化   | _                   | _           | _                             | _                      |                                | 初期化                    | SYSTEM       |  |

| DPSWCR         | 初期化   | -                   | _           | -                             | _                      |                                | 初期化                    | -            |  |

| DPSIER         | 初期化   | -                   | _           | -                             | _                      |                                | 初期化                    | _            |  |

| DPSIFR         | 初期化   | -                   | -           | _                             | _                      |                                | 初期化                    | <del>-</del> |  |

| DPSIEGR        | 初期化   | -                   | -           | _                             | _                      |                                | 初期化                    | <del>-</del> |  |

| RSTSR          | 初期化   | -                   | -           | _                             | _                      |                                | 初期化                    | -            |  |

| LVDCR *3       | 初期化*4 | _                   | _           | _                             | _                      | _                              | 初期化                    | -            |  |

| ~ 説明省略(変更なし) ~ |       |                     |             |                               |                        |                                |                        |              |  |

## 29. 電気的特性

(1) 頁 29-2 「表 29.2 DC 特性(1)」の入力 High レベル電圧(シュミットトリガ入力端子を除く) の項目を以下のように訂正します。

〔変更前〕

29.2 DC 特性 H8SX/1648 グループ、H8SX/1648A グループ、H8SX/1648G グループ

|       | 項目                          | 記号              | Min                          | typ | Max                    | 単位 | 測定条件 |

|-------|-----------------------------|-----------------|------------------------------|-----|------------------------|----|------|

|       | MD 端子、RES、<br>STBY、EMLE、NMI | V <sub>IH</sub> | V <sub>cc</sub> <b>x</b> 0.9 |     | V <sub>cc</sub> + 0.3  | V  |      |

| トトリガ入 |                             |                 | V <sub>cc</sub> × 0.7        |     | V <sub>cc</sub> + 0.3  |    |      |

| <)    | ポート 4、ポート 5                 |                 | AV <sub>cc</sub> × 0.7       |     | AV <sub>cc</sub> + 0.3 |    |      |

#### [変更後]

29.2 DC 特性 H8SX/1648 グループ、H8SX/1648A グループ、H8SX/1648G グループ

|       | 項目                          | 記号              | min                           | typ | max                    | 単位 | 測定条件 |

|-------|-----------------------------|-----------------|-------------------------------|-----|------------------------|----|------|

|       | MD 端子、RES、<br>STBY、EMLE、NMI | V <sub>IH</sub> | V <sub>cc</sub> × 0.9         |     | V <sub>cc</sub> + 0.3  | V  |      |

| トトリガ入 |                             |                 | V <sub>cc</sub> × 0.7         |     | V <sub>cc</sub> + 0.3  |    |      |

| <)    | ポート N                       |                 | $V_{cc} \times 0.7$           |     | 5.5                    |    |      |

|       | ポート 4、ポート 5                 |                 | AV <sub>cc</sub> <b>×</b> 0.7 |     | AV <sub>cc</sub> + 0.3 |    |      |

(2) 頁 29-5 「表 29.4 DC 特性(1)」の入力 High レベル電圧(シュミットトリガ入力端子を除く) の項目を以下のように訂正します。

〔変更前〕

29.3 DC 特性 H8SX/1648L グループ、H8SX/1648H グループ

|                                        | 項目                          | 記号       | min                          | typ | Max                    | 単位 | 測定条件 |

|----------------------------------------|-----------------------------|----------|------------------------------|-----|------------------------|----|------|

|                                        | MD 端子、RES、<br>STBY、EMLE、NMI | $V_{IH}$ | V <sub>cc</sub> × 0.9        |     | V <sub>cc</sub> + 0.3  | V  |      |

| <ul><li>(シュミットトリガ入<br/>力端子を除</li></ul> |                             |          | V <sub>cc</sub> <b>×</b> 0.7 |     | V <sub>cc</sub> + 0.3  |    |      |

| <)                                     | ポート 4、ポート 5                 |          | $AV_{cc} \times 0.7$         |     | AV <sub>cc</sub> + 0.3 |    |      |

## [変更後]

29.3 DC 特性 H8SX/1648L グループ、H8SX/1648H グループ

|       | 項目                | 記号              | min                   | typ | max                   | 単位 | 測定条件 |

|-------|-------------------|-----------------|-----------------------|-----|-----------------------|----|------|

|       | MD 端子、RES、        | V <sub>IH</sub> | V <sub>cc</sub> × 0.9 |     | V <sub>cc</sub> + 0.3 | V  |      |

|       | STBY, EMLE, NMI   |                 |                       |     |                       |    |      |

| (シュミッ |                   |                 | \/O.7                 |     | V <sub>cc</sub> + 0.3 |    |      |

| トトリガ入 | ENTAL<br>スの他の入力地で |                 | $V_{cc} \times 0.7$   |     | V <sub>CC</sub> + 0.3 |    |      |

| 力端子を除 | その他の入力端子          |                 |                       |     |                       |    |      |

| <)    | ポートN              |                 | $V_{cc} \times 0.7$   |     | 5.5                   |    |      |

|       | ポート 4、ポート 5       |                 | $AV_{cc} \times 0.7$  |     | $AV_{cc} + 0.3$       |    |      |