# **USB IP Core**

# USB3.1 Gen1 xHCl Host Controller IP Core

## Overview

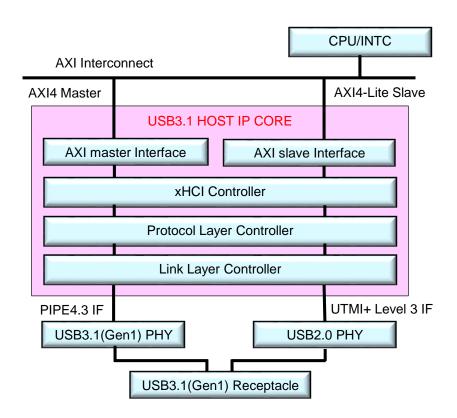

The Renesas USB3.1 xHCl Host Controller IP is compliant with the Universal Serial Bus (USB) 3.1 Specification.

This IP AXI uses AXI interconnection, which is a system interface that is based on the AMBA® AXI4, and AXI4-Lite Protocol Specification.

In addition, this IP has interfaces with USB3.1 PHY which is compliant with PHY Interface for the PCI Express, SATA, and USB 3.1 Architectures Version 4.3 (PIPE4.3), and with USB2.0 PHY which is compliant with USB2.0 Transceiver Macrocell Interface Plus (UTMI+) Specification Level 3.

This IP supports USB3.1 bus-speeds: Super Speed (5 Gbps), High Speed (480 Mbps), Full Speed (12Mbps), and Low Speed (1.5Mbps).

This IP is also compliant with the Battery Charging Specification Revision 1.2, and is based on the eXtensible Host Controller Interface for the Universal Serial Bus (xHCI) Specification as a Host Controller Interface.

# **Key Features**

## General

- ✓ Compliant with the Universal Serial Bus (USB) 3.1 Specification Revision 1.0.

- ✓ Compliant with the Universal Serial Bus Specification Revision 2.0.

- ✓ Compliant with the Battery Charging Specification Revision 1.2.

- ✓ Compliant with the PHY Interface for the PCI Express, SATA, and USB3.1 (PIPE) Version 4.3.

- ✓ Compliant with the eXtensible Host Controller Interface for the Universal Serial Bus Specification Revision 1.1.

- ✓ Compliant with the USB2.0 Transceiver Macrocell Interface Plus (UTMI+) Specification Revision 1.0 Level 3.

- ✓ Compliant with AMBA® AXI4, and AXI4-Lite Protocol Specification.

# **USB** function

- Supports 1 downstream USB receptacle.

- ➤ Number of SS ports : 1

- Number of HS,FS,LS ports: 1

- Supports USB bus-speeds: Super Speed (5 Gbps), High Speed (480 Mbps), Full Speed (12 Mbps), and Low Speed (1.5 Mbps).

- Supports all transfer-types: Control, Bulk, Interrupt, Isochronous, and these split-transactions.

- Supports Power Control and Over Current Detection.

## **Battery Charging Functions**

- Supports the following charging port device's modes.

- > Standard Downstream Port (SDP) Mode

- ➤ Charging Downstream Port (CDP) Mode

- Dedicated Charging Port (DCP) Mode

# **Key Features (Cont'd)**

# xHCI Capabilities

xHCl Host Capability

Number of Device Slots (MaxSlots) : 32Number of Total Endpoints : 64

➤ Number of Event Ring Segment Tables

(ERST Max) : 2(1)

➤ Supported Page Size : 4K bytes

➤ Context Size (CSZ) : 64 bytes(1)

➤ Number of Interrupter (MaxIntrs) : 1

➤ Number of Stream IDs (MaxPSASize) : 65536(15)

Supports Primary Stream Array.Supports the USB Legacy Support.

#### PIPE4.3 interface

Data Bus width and Frequency:

> Gen1: 32 bits @125 MHz

#### **UTMI+** interface

• Supported Level: Level 3

Data Bus with : 8 bits @60MHzData Bus mode : Unidirectional

#### **AXI4 Master interface**

Address Bus width : 32 bits (64bits optional)

Data Bus width : 128 bits

ID width : 4 bits

Maximum Burst Length : 16 bursts

Incremental BurstLittle Endian bus

## **AXI4-Lite Slave interface**

Address Bus width : 32 bits (64 bits optional)

Data Bus width : 32 bits

ID width : 32 bits

Maximum burst Length : 1 burst

· Little Endian bus

# **Product Details**

#### **IP Core**

The Renesas USB3.1 Host controller is the xHCI-compliant IP which implements Link Layer Controller, Protocol Layer Controller, xHCI Controller and AXI bus Interface. Link Layer Controller frames the USB packet, treats link command and controls LTSSM (Link Training Sequence State Machine). Protocol Layer Controller buffers the transaction data, constructs/deconstructs the packets and controls the transaction. The xHCI Controller contains xHCI registers, schedules the transfer and interfaces to xHCI Driver. This IP supports Super Speed (5 Gbps), High Speed (480 Mbps), Full Speed (12Mbps), and Low Speed (1.5Mbps).

This IP has three interfaces: AXI, PIPE, and UTMI+.

#### **AXI** interface

This IP has AXI4 Master interface and AXI4-Lite Slave interface. The master interface is for transaction data handling, and the slave interface is for register interface.

#### PIPE interface

This IP supports PIPE4.3 interface for USB Super Speed.

#### **UTMI+** interface

This IP supports UTMI+ Level 3 interface for USB High Speed, Full Speed, and Low Speed.