# RX ファミリ、RL78 ファミリ、78K0R/Kx3-L

R01AN1439JJ0104 Rev.1.04

Micron Technology 社製 P5Q Serial Phase Change Memory 制御ソフトウェア 2016.03.31

#### 要旨

本アプリケーションノートでは、ルネサス エレクトロニクス製 RX ファミリ、RL78 ファミリ、78K0R/Kx3-L を使用した Micron Technology, Inc.社製 P5Q Serial Phase Change Memory 制御方法とサンプルコードの使用方法を説明します。

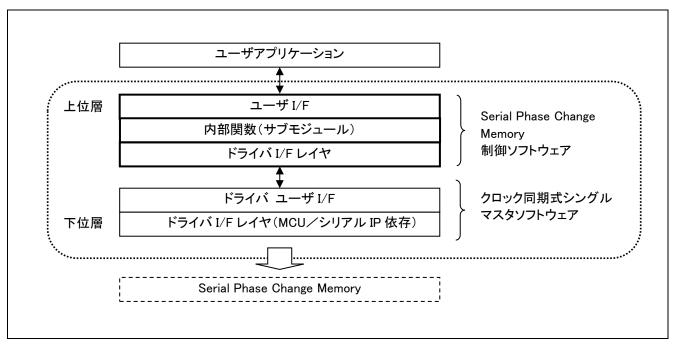

なお、本サンプルコードは、スレーブデバイスとしての Serial Phase Change Memory を制御するための上位層に位置するソフトウェアです。

別途、マスタデバイスとしての各 MCU 個別の SPI モードを制御するための下位層に位置するソフトウェア (クロック同期式シングルマスタ制御ソフトウェア) を用意していますので、以下から入手してください。なお、クロック同期式シングルマスタ制御ソフトウェアにおいて、新規 MCU が対応可能になった場合でも、本アプリケーションノートの更新が間に合わないことがあります。最新のサポート MCU とその制御ソフトウェアの情報は、以下の URL のページに記載されている「クロック同期式シングルマスタドライバ(下位層ソフトウェア)」を参照してください。

SPI/QSPI シリアルフラッシュメモリ制御、QSPI シリアル相変化メモリ制御 http://japan.renesas.com/driver/spi\_serial\_flash

#### 動作確認デバイス

Serial Phase Change Memory Micron Technology, Inc.社製 P5Q Serial Phase Change Memory

なお、P5Q Serial Phase Change Memory の製品入手につきましては、Micron Technology, Inc.社にご確認ください。

動作確認に使用した MCU

RX600 シリーズ : RX63N (RSPI を使用) RX100 シリーズ : RX111 (SCI を使用)

: RX111 (RSPI を使用)

RL78/G1x : RL78/G14, RL78/G1C (SAU を使用)

RL78/L1x : RL78/L12, RL78/L13, RL78/L1C (SAU を使用)

上記以外の対象マイコンについては、「3.関連アプリケーションノート」を参照ください。

本アプリケーションノートを他のマイコンへ適用する場合、そのマイコンの仕様にあわせて変更し、十分評価してください。

なお、本アプリケーションノートでは、以下の略称を使用します。

Single-SPI (Single SPI mode による通信)

Dual-SPI (Dual SPI mode による通信)

Quad-SPI (Quad SPI mode による通信)

# 目次

| 1. 仕   | 策                                     | 4        |

|--------|---------------------------------------|----------|

| 2. 動作  | 作確認条件                                 | <b>-</b> |

|        | F唯応未件<br> RX ファミリ                     |          |

|        |                                       |          |

| 2.2 F  | RL78 ファミリ、78K0R/Kx3-L                 | /        |

| 3. 関   | 連アプリケーションノート                          | 13       |

| 3.1 F  | RX ファミリ 関連アプリケーションノートー覧               | 13       |

| 3.2 F  | RL78 ファミリ、78K0R ファミリ 関連アプリケーションノートー覧  | 13       |

| 4. /\- | ードウェア説明                               | 14       |

|        | ハードウェア構成例                             |          |

| 4.1.1  |                                       |          |

| 4.1.2  |                                       |          |

| 4.1.3  |                                       |          |

| 4.1.4  |                                       |          |

| 4.1.5  |                                       |          |

| 4.1.6  |                                       |          |

| 7.1.0  |                                       |          |

| 5. ソ   | フトウェア説明                               | 17       |

| 5.1    | 動作概要                                  | 17       |

| 5.1.1  | Ⅰ データバッファと送信/受信データの関係                 | 17       |

| 5.1.2  | 2 クロック同期式モードで発生させるタイミング               | 18       |

| 5.1.3  | 3 Serial Phase Change Memory の S#端子制御 | 20       |

| 5.1.4  | 4 Serial Phase Change Memory の命令コード   | 21       |

| 5.2    | ソフトウェア構成                              | 22       |

|        | 込要メモリサイズ                              |          |

| 5.3.1  | I RX ファミリ                             | 23       |

| 5.3.2  | 2 RL78 ファミリ、78K0R/Kx3-L               | 25       |

| 5.4    | ファイル構成                                | 28       |

|        | 定数一覧                                  |          |

| 5.5.1  | I 戻り値                                 | 29       |

| 5.5.2  | 2 コマンド定義                              | 29       |

| 5.5.3  | 3 各種定義                                | 30       |

|        | 構造体/共用体一覧                             |          |

|        | 変数一覧                                  |          |

| 5.8    | <b>對数一</b> 覧                          | 34       |

| 5.9    | 男数仕様                                  | 35       |

|        | ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・  |          |

|        | 2 ステータスレジスタ読み出し処理                     |          |

|        | - ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・   |          |

|        | 4 WRDIコマンド発行処理                        |          |

|        | 5 データ読み出し処理                           |          |

|        | -                                     |          |

# RX ファミリ、RL78 ファミリ、78K0R/Kx3-L

# Micron Technology 社製 P5Q Serial Phase Change Memory 制御ソフトウェア

|    | 5.9.7  | データ書き込み処理(1Page 書き込み用)                | 44 |

|----|--------|---------------------------------------|----|

|    | 5.9.8  | 消去処理                                  | 47 |

|    | 5.9.9  | ID 読み出し処理                             |    |

|    | 5.9.10 | )ビジーウェイト処理                            | 51 |

| 6. | 応用     | ]例                                    | 53 |

| 6  |        | erial Phase Change Memory 制御ソフトウェアの設定 |    |

|    | 6.1.1  | r_qspi_pcm_p5q.h                      |    |

|    | 6.1.2  | r_qspi_pcm_p5q_sfr.h                  | 56 |

|    | 6.1.3  | r_qspi_pcm_p5q_sub.h                  | 59 |

|    | 6.1.4  | r_qspi_pcm_p5q_sub.c                  | 60 |

|    | 6.1.5  | r_qspi_pcm_p5q_drvif.c                | 62 |

|    | 6.1.6  | r_qspi_pcm_p5q_sfr_rl78.c             | 65 |

| 7. | 使用     | 上の注意事項                                | 66 |

| 7  | '.1 組  | み込み時の注意事項                             | 66 |

| 7  | '.2 +  | ·ャッシュ搭載の MCU を使用する場合                  | 66 |

| 7  |        | 容量に対応する場合                             |    |

| 7  | '.4 他  | スレーブデバイスを使用する場合                       | 66 |

| 7  |        | 源投入後の電圧安定待ち時間について                     |    |

| 7  | '.6 Se | erial Phase Change Memory の使用制限について   | 67 |

#### 1. 仕様

ルネサス エレクトロニクス製 MCU を使用し、Micron Technology, Inc.社製 P5Q Serial Phase Change Memory を制御します。

別途、MCU 個別のクロック同期式シングルマスタ制御ソフトウェアが必要です。

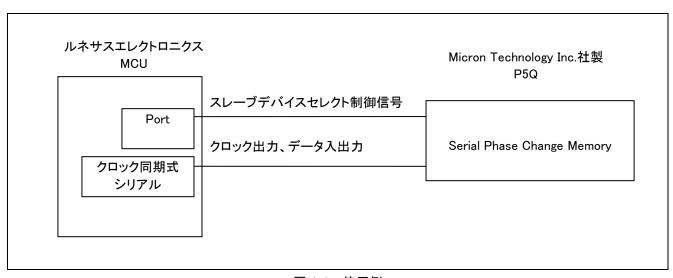

表 1-1 に使用する周辺機能と用途を、図 1-1 に使用例を示します。

以下に、機能概略を示します。

- マスタデバイスをルネサス エレクトロニクス製 MCU、スレーブデバイスを Micron Technology, Inc.社製 P5Q Serial Phase Change Memory としたデバイスドライバです。

- MCU 内蔵のシリアル通信機能(クロック同期式モード)を使用し、Single-SPI、Dual-SPI、Quad-SPI により制御します。

- ユーザ設定したシリアル通信機能1チャネルの使用が可能です。複数チャネルの使用はできません。

- 同一型名、かつ最大 2 個の Serial Phase Change Memory の制御が可能です。

- 通信速度レートは、ユーザ設定可能です。

- ビッグエンディアン/リトルエンディアンでの動作が可能です。(使用 MCU 依存)

| 周辺機能            | 用途                      |

|-----------------|-------------------------|

| MCU 内蔵のシリアル通信機能 | シリアル通信機能(クロック同期式モード)による |

| (クロック同期式モード)    | SPI スレーブデバイスとの通信        |

|                 | 1ch(必須)                 |

| Port            | SPI スレーブデバイスセレクト制御信号用   |

|                 | 使用デバイス数分のポートが必要(必須)     |

表 1-1 使用する周辺機能と用途

図 1-1 使用例

### 2. 動作確認条件

本アプリケーションノートのサンプルコードは、下記の条件で動作を確認しています。

### 2.1 RX ファミリ

#### (1) RX63N RSPI の場合

表 2-1 動作確認条件

| 項目            | 内容                                                       |

|---------------|----------------------------------------------------------|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory |

| 評価に使用したマイコン   | RX63N グループ(プログラム ROM 1MB/RAM 128KB)                      |

| 動作周波数         | ICLK: 96MHz、PCLK: 48MHz                                  |

| 動作電圧          | 3.3V                                                     |

| 統合開発環境        | ルネサス エレクトロニクス製                                           |

|               | High-performance embedded Workshop Version 4.09.01.007   |

| Cコンパイラ        | ルネサス エレクトロニクス製                                           |

|               | RX ファミリ用 C/C++コンパイラパッケージ (ツールチェーン 1.2.1.0)               |

|               | コンパイルオプション                                               |

|               | 統合開発環境のデフォルト設定を使用しています。                                  |

| エンディアン        | ビッグエンディアン/リトルエンディアン                                      |

| サンプルコードのバージョン | Ver.2.20                                                 |

| 評価に使用したソフトウェア | RX63N 用 RSPI を使ったクロック同期式シングルマスタ制御ソフトウェア                  |

|               | Ver.2.04                                                 |

| 評価に使用した使用ボード  | Renesas Starter Kit for RX63N                            |

#### (2) RX111 RSPI の場合

表 2-2 動作確認条件

| 項目            | 内容                                                       |

|---------------|----------------------------------------------------------|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory |

| 評価に使用したマイコン   | RX111 グループ(プログラム ROM 128KB RAM 16KB)                     |

| 動作周波数         | ICLK: 32MHz、PCLK: 32MHz                                  |

| 動作電圧          | 3.3V                                                     |

| 統合開発環境        | ルネサス エレクトロニクス製                                           |

|               | CubeSuite+ V2.01.00                                      |

| Cコンパイラ        | ルネサス エレクトロニクス製                                           |

|               | RX ファミリ用 C/C++コンパイラケッケージ (ツールチェーン 2.01.00)               |

|               | コンパイルオプション                                               |

|               | 総合開発環境のデフォルト設定(※1)を使用しています。                              |

|               | ※1:最適化レベル"2"、最適化方法"サイズ優先"                                |

| エンディアン        | ビッグエンディアン/リトルエンディアン                                      |

| サンプルコードのバージョン | Ver.2.21 R01                                             |

| 評価に使用したソフトウェア | RX210, RX21A, RX220, RX63N, RX63T, RX111 グループ RSPI を使った  |

|               | クロック同期式シングルマスタ制御ソフトウェア(R01AN1196JJ) Ver.2.04             |

|               | R04                                                      |

| 評価に使用した使用ボード  | Renesas Starter Kit for RX111                            |

#### (3) RX111 SCI の場合

表 2-3 動作確認条件

| 項目            | 内容                                                       |

|---------------|----------------------------------------------------------|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory |

| 評価に使用したマイコン   | RX111 グループ(プログラム ROM 128KB RAM 16KB)                     |

| 動作周波数         | ICLK: 32MHz、PCLK: 32MHz                                  |

| 動作電圧          | 3.3V                                                     |

| 統合開発環境        | ルネサス エレクトロニクス製                                           |

|               | CubeSuite+ V2.01.00                                      |

| Cコンパイラ        | ルネサス エレクトロニクス製                                           |

|               | RX ファミリ用 C/C++コンパイラケッケージ (ツールチェーン 2.01.00)               |

|               | コンパイルオプション                                               |

|               | 総合開発環境のデフォルト設定(※1)を使用しています。                              |

|               | ※1:最適化レベル"2"、最適化方法"サイズ優先"                                |

| エンディアン        | ビッグエンディアン/リトルエンディアン                                      |

| サンプルコードのバージョン | Ver.2.21 R01                                             |

| 評価に使用したソフトウェア | RX210, RX21A, RX220, RX63N, RX63T, RX111 グループ SCI を使った   |

|               | クロック同期式シングルマスタ制御ソフトウェア(R01AN1229JJ) Ver.2.01             |

|               | R05                                                      |

| 評価に使用した使用ボード  | Renesas Starter Kit for RX111                            |

## 2.2 RL78 ファミリ、78K0R/Kx3-L

(1) RL78/G14 SAU 統合開発環境 CS+ for CA,CX の場合(コンパイラ:CA78K0R)

表 2-4 動作確認条件

| 項目            | 内容                                                       |

|---------------|----------------------------------------------------------|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory |

| 評価に使用したマイコン   | RL78/G14(プログラム ROM 256KB/RAM 24KB)                       |

| 動作周波数         | メイン・システム・クロック: 24MHz                                     |

|               | CPU/周辺ハードウェア・クロック: 24MHz                                 |

|               | シリアル・クロック:6MHz                                           |

| 動作電圧          | 3.3V                                                     |

| 統合開発環境        | ルネサス エレクトロニクス製 CS+ for CA,CX V3.01.00                    |

| Cコンパイラ        | ルネサス エレクトロニクス製                                           |

|               | RL78,78K0R コンパイラ CA78K0R V1.71                           |

|               | コンパイルオプション                                               |

|               | 統合開発環境のデフォルト設定("-qx2")を使用しています。                          |

| サンプルコードのバージョン | Ver.2.22                                                 |

| 評価に使用したソフトウェア | RL78/G14、RL78/G1C、RL78/L12、RL78/L13、RL78/L1C グループ シリ     |

|               | アル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマ                     |

|               | スタ制御ソフトウェア(R01AN1195JJ) Ver.2.05                         |

| 評価に使用した使用ボード  | Renesas Starter Kit for RL78/G14                         |

#### (2) RL78/G14 SAU 統合開発環境 CS+ for CC の場合 (コンパイラ: CC-RL)

表 2-5 動作確認条件

| 項目            | 内容                                                       |

|---------------|----------------------------------------------------------|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory |

| 評価に使用したマイコン   | RL78/G14(プログラム ROM 256KB/RAM 24KB)                       |

| 動作周波数         | メイン・システム・クロック: 24MHz                                     |

|               | CPU/周辺ハードウェア・クロック: 24MHz                                 |

|               | シリアル・クロック:6MHz                                           |

| 動作電圧          | 3.3V                                                     |

| 統合開発環境        | ルネサス エレクトロニクス製 CS+ for CC V3.03.00                       |

| Cコンパイラ        | ルネサス エレクトロニクス製 RL78 コンパイラ CC-RL V1.02.00                 |

|               | コンパイルオプション                                               |

|               | 統合開発環境のデフォルト設定 (既定の最適化を行う(なし)) を使用してい                    |

|               | ます。                                                      |

| サンプルコードのバージョン | Ver.2.22                                                 |

| 評価に使用したソフトウェア | RL78/G14、RL78/G1C、RL78/L12、RL78/L13、RL78/L1C グループ シリ     |

|               | アル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマ                     |

|               | スタ制御ソフトウェア(R01AN1195JJ) Ver.2.05                         |

| 評価に使用した使用ボード  | Renesas Starter Kit for RL78/G14                         |

#### (3) RL78/G14 SAU 統合開発環境 IAR Embedded Workbench の場合

表 2-6 動作確認条件

| 項目            | 内容                                                       |

|---------------|----------------------------------------------------------|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory |

| 評価に使用したマイコン   | RL78/G14(プログラム ROM 256KB/RAM 24KB)                       |

| 動作周波数         | メイン・システム・クロック: 24MHz                                     |

|               | CPU/周辺ハードウェア・クロック: 24MHz                                 |

|               | シリアル・クロック:6MHz                                           |

| 動作電圧          | 3.3V                                                     |

| 統合開発環境        | IAR Systems 製                                            |

|               | IAR Embedded Workbench for Renesas RL78 (Ver.1.30.2)     |

| Cコンパイラ        | IAR Systems 製                                            |

|               | IAR Assembler for Renesas RL78 (Ver.1.30.2.50666)        |

|               | IAR C/C++ Compiler for Renesas RL78 (Ver.1.30.2.50666)   |

|               | コンパイルオプション                                               |

|               | 統合開発環境のデフォルト設定("レベル 低")を使用しています。                         |

| サンプルコードのバージョン | Ver.2.21                                                 |

| 評価に使用したソフトウェア | シリアル・アレイ・ユニットの CSI モードを使ったクロック同期式シング                     |

|               | ルマスタ制御ソフトウェア Ver.2.03                                    |

| 評価に使用した使用ボード  | Renesas Starter Kit for RL78/G14                         |

#### (4) RL78/G1C SAU 統合開発環境 CubeSuite+の場合

表 2-7 動作確認条件

| 項目            | 内容                                                        |

|---------------|-----------------------------------------------------------|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory  |

| 評価に使用したマイコン   | RL78/G1C(プログラム ROM 32KB/RAM 5.5KB)                        |

| 動作周波数         | メイン・システム・クロック: 24MHz                                      |

|               | CPU/周辺ハードウェア・クロック: 24MHz                                  |

|               | シリアル・クロック: 12MHz                                          |

| 動作電圧          | 3.3V                                                      |

| 統合開発環境        | ルネサス エレクトロニクス製 CubeSuite+ V2.01.00                        |

| Cコンパイラ        | ルネサス エレクトロニクス製                                            |

|               | CubeSuite+ RL78,78K0R コンパイラ CA78K0R V1.70                 |

|               | コンパイルオプション                                                |

|               | 統合開発環境のデフォルト設定("-qx2")を使用しています。                           |

| サンプルコードのバージョン | Ver.2.21 R01                                              |

| 評価に使用したソフトウェア | RL78/G14, RL78/G1C, RL78/L12, RL78/L13, RL78/L1C グループ シリア |

|               | ル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマス                      |

|               | タ制御ソフトウェア(R01AN1195JJ0103) Ver.2.03                       |

| 評価に使用した使用ボード  | Renesas RL78/G1C ターゲット・ボード QB-R5F10JGC-TB                 |

### (5) RL78/G1C SAU 統合開発環境 IAR Embedded Workbench の場合

表 2-8 動作確認条件

| 項目            | 内容                                                        |

|---------------|-----------------------------------------------------------|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory  |

| 評価に使用したマイコン   | RL78/G1C(プログラム ROM 32KB/RAM 5.5KB)                        |

| 動作周波数         | メイン・システム・クロック: 24MHz                                      |

|               | CPU/周辺ハードウェア・クロック: 24MHz                                  |

|               | シリアル・クロック:12MHz                                           |

| 動作電圧          | 3.3V                                                      |

| 統合開発環境        | IAR Systems 製                                             |

|               | IAR Embedded Workbench for Renesas RL78 (Ver.1.30.5)      |

| Cコンパイラ        | IAR Systems 製                                             |

|               | IAR Assembler for Renesas RL78 (Ver.1.30.4.50715)         |

|               | IAR C/C++ Compiler for Renesas RL78 (Ver.1.30.5.50715)    |

|               | コンパイルオプション                                                |

|               | 統合開発環境のデフォルト設定("レベル 低")を使用しています。                          |

| サンプルコードのバージョン | Ver.2.21 R01                                              |

| 評価に使用したソフトウェア | RL78/G14, RL78/G1C, RL78/L12, RL78/L13, RL78/L1C グループ シリア |

|               | ル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマス                      |

|               | タ制御ソフトウェア(R01AN1195JJ0103) Ver.2.03                       |

| 評価に使用した使用ボード  | Renesas RL78/G1C ターゲット・ボード QB-R5F10JGC-TB                 |

#### (6) RL78/L12 SAU 統合開発環境 CubeSuite+の場合

表 2-9 動作確認条件

| 項目            | 内容                                                        |

|---------------|-----------------------------------------------------------|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory  |

| 評価に使用したマイコン   | RL78/L12(プログラム ROM 32KB / RAM 1.5KB)                      |

| 動作周波数         | メイン・システム・クロック: 24MHz                                      |

|               | CPU/周辺ハードウェア・クロック: 24MHz                                  |

|               | シリアル・クロック:6MHz                                            |

| 動作電圧          | 3.3V                                                      |

| 統合開発環境        | ルネサス エレクトロニクス製 CubeSuite+ V2.01.00                        |

| Cコンパイラ        | ルネサス エレクトロニクス製                                            |

|               | CubeSuite+ RL78,78K0R コンパイラ CA78K0R V1.70                 |

|               | コンパイルオプション                                                |

|               | 統合開発環境のデフォルト設定("-qx2")を使用しています。                           |

| サンプルコードのバージョン | Ver.2.21 R01                                              |

| 評価に使用したソフトウェア | RL78/G14, RL78/G1C, RL78/L12, RL78/L13, RL78/L1C グループ シリア |

|               | ル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマス                      |

|               | タ制御ソフトウェア(R01AN1195JJ0103) Ver.2.03                       |

| 評価に使用した使用ボード  | Renesas Starter Kit for RL78/L12                          |

### (7) RL78/L12 SAU 統合開発環境 IAR Embedded Workbench の場合

表 2-10 動作確認条件

| 項目            | 内容                                                        |  |  |

|---------------|-----------------------------------------------------------|--|--|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory  |  |  |

| 評価に使用したマイコン   | RL78/L12(プログラム ROM 32KB / RAM 1.5KB)                      |  |  |

| 動作周波数         | メイン・システム・クロック: 24MHz                                      |  |  |

|               | CPU/周辺ハードウェア・クロック: 24MHz                                  |  |  |

|               | シリアル・クロック:6MHz                                            |  |  |

| 動作電圧          | 3.3V                                                      |  |  |

| 統合開発環境        | IAR Systems 製                                             |  |  |

|               | IAR Embedded Workbench for Renesas RL78 (Ver.1.30.5)      |  |  |

| Cコンパイラ        | IAR Systems 製                                             |  |  |

|               | IAR Assembler for Renesas RL78 (Ver.1.30.4.50715)         |  |  |

|               | IAR C/C++ Compiler for Renesas RL78 (Ver.1.30.5.50715)    |  |  |

|               | コンパイルオプション                                                |  |  |

|               | 統合開発環境のデフォルト設定("レベル 低")を使用しています。                          |  |  |

| サンプルコードのバージョン | Ver.2.21 R01                                              |  |  |

| 評価に使用したソフトウェア | RL78/G14, RL78/G1C, RL78/L12, RL78/L13, RL78/L1C グループ シリア |  |  |

|               | ル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマス                      |  |  |

|               | タ制御ソフトウェア(R01AN1195JJ0103) Ver.2.03                       |  |  |

| 評価に使用した使用ボード  | Renesas Starter Kit for RL78/L12                          |  |  |

#### (8) RL78/L13 SAU 統合開発環境 CubeSuite+の場合

表 2-11 動作確認条件

| 項目            | 内容                                                        |  |  |

|---------------|-----------------------------------------------------------|--|--|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory  |  |  |

| 評価に使用したマイコン   | RL78/L13(プログラム ROM 128KB / RAM 8KB)                       |  |  |

| 動作周波数         | メイン・システム・クロック: 24MHz                                      |  |  |

|               | CPU/周辺ハードウェア・クロック: 24MHz                                  |  |  |

|               | シリアル・クロック:6MHz                                            |  |  |

| 動作電圧          | 3.3V                                                      |  |  |

| 統合開発環境        | ルネサス エレクトロニクス製 CubeSuite+ V2.01.00                        |  |  |

| Cコンパイラ        | ルネサス エレクトロニクス製                                            |  |  |

|               | CubeSuite+ RL78,78K0R コンパイラ CA78K0R V1.70                 |  |  |

|               | コンパイルオプション                                                |  |  |

|               | 統合開発環境のデフォルト設定("-qx2")を使用しています。                           |  |  |

| サンプルコードのバージョン | Ver.2.21 R01                                              |  |  |

| 評価に使用したソフトウェア | RL78/G14, RL78/G1C, RL78/L12, RL78/L13, RL78/L1C グループ シリア |  |  |

|               | ル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマス                      |  |  |

|               | タ制御ソフトウェア(R01AN1195JJ0103) Ver.2.03                       |  |  |

| 評価に使用した使用ボード  | Renesas Starter Kit for RL78/L13                          |  |  |

### (9) RL78/L13 SAU 統合開発環境 IAR Embedded Workbench の場合

表 2-12 動作確認条件

| 項目            | 内容                                                        |  |  |

|---------------|-----------------------------------------------------------|--|--|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory  |  |  |

| 評価に使用したマイコン   | RL78/L13(プログラム ROM 128KB / RAM 8KB)                       |  |  |

| 動作周波数         | メイン・システム・クロック: 24MHz                                      |  |  |

|               | CPU/周辺ハードウェア・クロック: 24MHz                                  |  |  |

|               | シリアル・クロック:6MHz                                            |  |  |

| 動作電圧          | 3.3V                                                      |  |  |

| 統合開発環境        | IAR Systems 製                                             |  |  |

|               | IAR Embedded Workbench for Renesas RL78 (Ver.1.30.5)      |  |  |

| Cコンパイラ        | IAR Systems 製                                             |  |  |

|               | IAR Assembler for Renesas RL78 (Ver.1.30.4.50715)         |  |  |

|               | IAR C/C++ Compiler for Renesas RL78 (Ver.1.30.5.50715)    |  |  |

|               | コンパイルオプション                                                |  |  |

|               | 統合開発環境のデフォルト設定("レベル 低")を使用しています。                          |  |  |

| サンプルコードのバージョン | Ver.2.21 R01                                              |  |  |

| 評価に使用したソフトウェア | RL78/G14, RL78/G1C, RL78/L12, RL78/L13, RL78/L1C グループ シリア |  |  |

|               | ル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマス                      |  |  |

|               | タ制御ソフトウェア(R01AN1195JJ0103) Ver.2.03                       |  |  |

| 評価に使用した使用ボード  | Renesas Starter Kit for RL78/L13                          |  |  |

#### (10) RL78/L1C SAU 統合開発環境 CubeSuite+の場合

表 2-13 動作確認条件

| 項目            | 内容                                                        |  |  |

|---------------|-----------------------------------------------------------|--|--|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory  |  |  |

| 評価に使用したマイコン   | RL78/L1C(プログラム ROM 256KB / RAM 16KB)                      |  |  |

| 動作周波数         | メイン・システム・クロック: 24MHz                                      |  |  |

|               | CPU/周辺ハードウェア・クロック: 24MHz                                  |  |  |

|               | シリアル・クロック:6MHz                                            |  |  |

| 動作電圧          | 3.3V                                                      |  |  |

| 統合開発環境        | ルネサス エレクトロニクス製 CubeSuite+ V2.01.00                        |  |  |

| Cコンパイラ        | ルネサス エレクトロニクス製                                            |  |  |

|               | CubeSuite+ RL78,78K0R コンパイラ CA78K0R V1.70                 |  |  |

|               | コンパイルオプション                                                |  |  |

|               | 統合開発環境のデフォルト設定("-qx2")を使用しています。                           |  |  |

| サンプルコードのバージョン | Ver.2.21 R01                                              |  |  |

| 評価に使用したソフトウェア | RL78/G14, RL78/G1C, RL78/L12, RL78/L13, RL78/L1C グループ シリア |  |  |

|               | ル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマス                      |  |  |

|               | タ制御ソフトウェア(R01AN1195JJ0103) Ver.2.03                       |  |  |

| 評価に使用した使用ボード  | Renesas Starter Kit for RL78/L1C                          |  |  |

### (11) RL78/L1C SAU 統合開発環境 IAR Embedded Workbench の場合

表 2-14 動作確認条件

| 項目            | 内容                                                        |  |  |  |

|---------------|-----------------------------------------------------------|--|--|--|

| 評価に使用したメモリ    | Micron Technology, Inc.社製 P5Q Serial Phase Change Memory  |  |  |  |

| 評価に使用したマイコン   | RL78/L1C(プログラム ROM 256KB / RAM 16KB)                      |  |  |  |

| 動作周波数         | メイン・システム・クロック: 24MHz                                      |  |  |  |

|               | CPU/周辺ハードウェア・クロック: 24MHz                                  |  |  |  |

|               | シリアル・クロック:6MHz                                            |  |  |  |

| 動作電圧          | 3.3V                                                      |  |  |  |

| 統合開発環境        | IAR Systems 製                                             |  |  |  |

|               | IAR Embedded Workbench for Renesas RL78 (Ver.1.30.5)      |  |  |  |

| Cコンパイラ        | IAR Systems 製                                             |  |  |  |

|               | IAR Assembler for Renesas RL78 (Ver.1.30.4.50715)         |  |  |  |

|               | IAR C/C++ Compiler for Renesas RL78 (Ver.1.30.5.50715)    |  |  |  |

|               | コンパイルオプション                                                |  |  |  |

|               | 統合開発環境のデフォルト設定("レベル 低")を使用しています。                          |  |  |  |

| サンプルコードのバージョン | Ver.2.21 R01                                              |  |  |  |

| 評価に使用したソフトウェア | RL78/G14, RL78/G1C, RL78/L12, RL78/L13, RL78/L1C グループ シリア |  |  |  |

|               | ル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマス                      |  |  |  |

|               | タ制御ソフトウェア(R01AN1195JJ0103) Ver.2.03                       |  |  |  |

| 評価に使用した使用ボード  | Renesas Starter Kit for RL78/L1C                          |  |  |  |

#### 3. 関連アプリケーションノート

本アプリケーションノートに関連するアプリケーションノートを以下に示します。併せて参照してください。

なお、以下の関連アプリケーションノートのうち、動作確認済の MCU については、表紙の"対象デバイス" をご参照ください。

#### 3.1 RX ファミリ 関連アプリケーションノート一覧

- RX610 グループ SCI を使ったクロック同期式シングルマスタ制御ソフトウェア (R01AN0534JJ)

- RX62N グループ RSPI を使ったクロック同期式シングルマスタ制御ソフトウェア (R01AN0323JJ)

- RX62N グループ SCI を使ったクロック同期式シングルマスタ制御ソフトウェア (R01AN1088JJ)

- RX210,RX21A,RX220,RX63N,RX63T,RX111 グループ RSPI を使ったクロック同期式シングルマスタ制御 ソフトウェア (R01AN1196JJ)

- RX210,RX21A,RX220,RX63N,RX63T,RX111 グループ SCI を使ったクロック同期式シングルマスタ制御 ソフトウェア (R01AN1229JJ)

#### 3.2 RL78 ファミリ、78K0R ファミリ 関連アプリケーションノート一覧

- 78K0R/Kx3-L シリアル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマスタ制御 ソフトウェア (R01AN0708JJ)

- RL78/G14, RL78/G1C, RL78/L12, RL78/L13, RL78/L1C グループ シリアル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマスタ制御ソフトウェア (R01AN1195JJ)

#### 4. ハードウェア説明

### 4.1 ハードウェア構成例

以下にハードウェア構成例を示します。

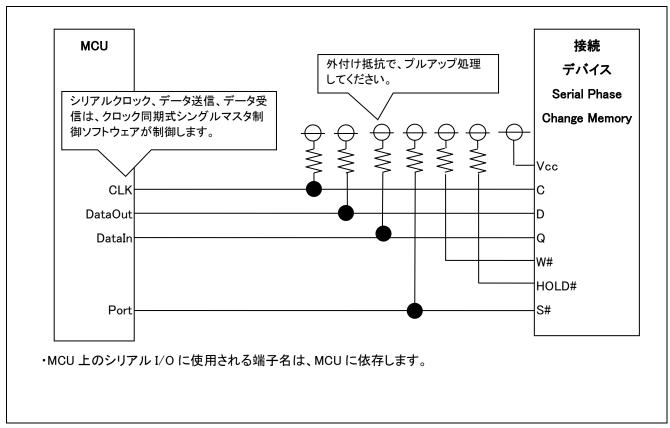

#### 4.1.1 Single-SPI 使用時の端子一覧

表 4-1 に MCU 側の Single-SPI 使用端子と機能を示します。

表 4-1 Single-SPI 使用端子と機能

| MCU 端子名   | 入出力 | 内容             |

|-----------|-----|----------------|

| CLK       | 出力  | クロック出力         |

| DataOut   | 出力  | マスタデータ出力       |

| DataIn    | 入力  | マスタデータ入力       |

| Port(CS#) | 出力  | スレーブデバイスセレクト出力 |

#### 4.1.2 Single-SPI 使用時の接続例

以下に Single-SPI 使用時の接続例を示します。

図 4-1 Single-SPI 使用時の MCU と SPI スレーブデバイスの接続例

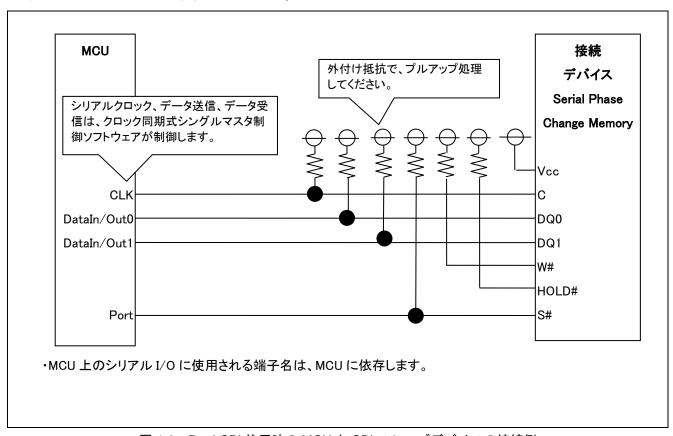

#### 4.1.3 Dual-SPI 使用時の端子一覧

表 4-2 に MCU 側の Dual-SPI 使用端子と機能を示します。

なお、Dual-SPI を使用するためには、対象 MCU にクワッドシリアルペリフェラルインターフェース機能が搭載されている必要があります。

| MCU 端子名     | 入出力 | 内容             |

|-------------|-----|----------------|

| CLK         | 出力  | クロック出力         |

| DataIn/Out0 | 入出力 | マスタデータ入出力 0    |

| DataIn/Out1 | 入出力 | マスタデータ入出力1     |

| Port(CS#)   | 出力  | スレーブデバイスセレクト出力 |

表 4-2 Dual-SPI 使用端子と機能

#### 4.1.4 Dual-SPI 使用時の接続例

以下に Dual-SPI 使用時の接続例を示します。

図 4-2 Dual-SPI 使用時の MCU と SPI スレーブデバイスの接続例

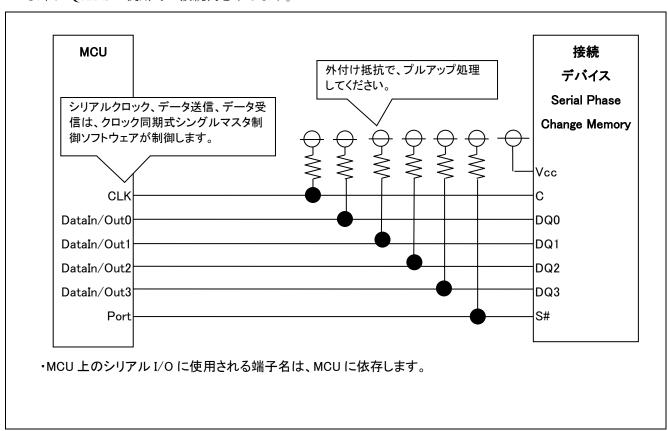

#### 4.1.5 Quad-SPI 使用時の端子一覧

表 4-3 に MCU 側の Quad-SPI 使用端子と機能を示します。

なお、Quad-SPI を使用するためには、対象 MCU にクワッドシリアルペリフェラルインターフェース機能が搭載されている必要があります。

| MCU 端子名     | 入出力 | 内容             |

|-------------|-----|----------------|

| CLK         | 出力  | クロック出力         |

| DataIn/Out0 | 入出力 | マスタデータ入出力0     |

| DataIn/Out1 | 入出力 | マスタデータ入出力1     |

| DataIn/Out2 | 入出力 | マスタデータ入出力2     |

| DataIn/Out3 | 入出力 | マスタデータ入出力3     |

| Port(CS#)   | 出力  | スレーブデバイスセレクト出力 |

表 4-3 Quad-SPI 使用端子と機能

#### 4.1.6 Quad-SPI 使用時の接続例

以下に Quad-SPI 使用時の接続例を示します。

図 4-3 Quad-SPI 使用時の MCU と SPI スレーブデバイスの接続例

#### 5. ソフトウェア説明

#### 5.1 動作概要

MCU のクロック同期式シリアル通信機能を使って、Serial Phase Change Memory 制御を実現します。 本サンプルコードでは、以下の制御を行っています。

- SPI スレーブデバイスの S#端子を MCU の Port に接続し、MCU 汎用ポート出力で、制御する。(本サンプルコードで制御する。)

- データの入出力を、クロック同期式モード(内部クロック使用)で、制御する。(本サンプルコードが、MCU 個別のクロック同期式シングルマスタ制御ソフトウェアを使用する。)

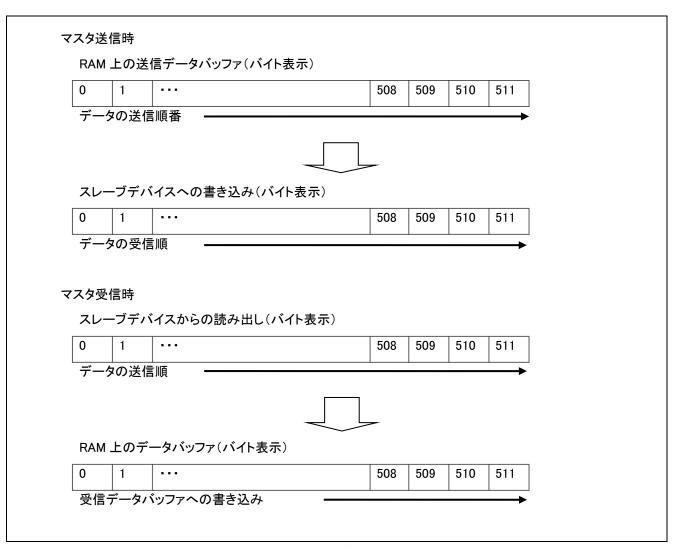

#### 5.1.1 データバッファと送信/受信データの関係

本サンプルコードは、ブロック型デバイスドライバであり、送信/受信データポインタを引数として設定します。RAM上のデータバッファのデータ並びと送信/受信順番の関係は、以下のとおりで、エンディアンや使用するシリアル通信機能に関係なく、送信データバッファの並びの順に送信し、また、受信の順に受信データバッファに書き込みます。

図 5-1 に転送データの格納を示します。

図 5-1 転送データの格納

#### 5.1.2 クロック同期式モードで発生させるタイミング

以下にクロック同期式モードで発生させるタイミングについて示します。

なお、使用可能なシリアルクロック周波数は、MCUと SPI デバイスの各データシートを参照し、設定してください。

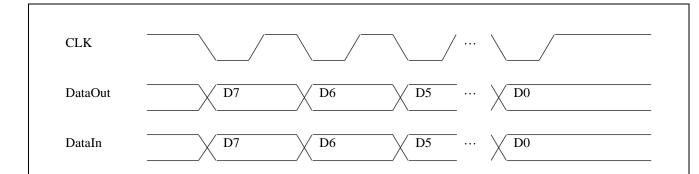

#### (1) Single-SPI 使用時

Serial Phase Change Memory 制御のため、図 5-2 に示す SPI モード 3(CPOL=1、CPHA=1)のタイミングを発生させます。

- ・MCU->Serial Phase Change Memory の送信時: 転送クロックの立ち下がりで送信データ出力開始

- Serial Phase Change Memory->MCU の受信時:転送クロックの立ち上がりで受信データの入力取り込み

- ・MSB ファーストでの転送

転送を行っていないときのCLK 端子のレベルは、"H"です。

図 5-2 Single-SPI 時のクロック同期式モード タイミング設定

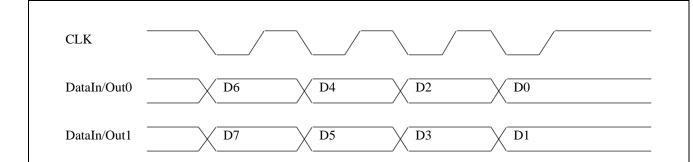

#### (2) Dual-SPI 使用時

Serial Phase Change Memory 制御のため、図 5-3 に示す SPI モード 3(CPOL=1、CPHA=1)のタイミングを発生させます。

- MCU->Serial Phase Change Memory の送信時:転送クロックの立ち下がりで送信データ出力開始

- Serial Phase Change Memory->MCU の受信時:転送クロックの立ち上がりで受信データの入力取り込み

- ・MSB ファーストでの転送

転送を行っていないときのCLK 端子のレベルは、"H"です。

図 5-3 Dual-SPI 時のクロック同期式モード タイミング設定

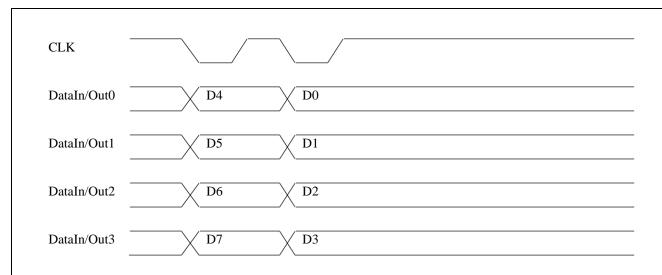

#### (3) Quad-SPI 使用時

Serial Phase Change Memory 制御のため、図 5-4 に示す SPI モード 3(CPOL=1、CPHA=1)のタイミングを発生させます。

- ・MCU->Serial Phase Change Memory の送信時:転送クロックの立ち下がりで送信データ出力開始

- Serial Phase Change Memory->MCU の受信時:転送クロックの立ち上がりで受信データの入力取り込み

- ・MSB ファーストでの転送

転送を行っていないときの CLK 端子のレベルは、"H"です。

#### 図 5-4 Quad-SPI 時のクロック同期式モード タイミング設定

#### 5.1.3 Serial Phase Change Memory の S#端子制御

Serial Phase Change Memory の S#端子を MCU の Port に接続し、MCU 汎用ポート出力で、制御します。

Serial Phase Change Memory の S# (MCU の Port(CS#)) 信号の立ち下がりから、Serial Phase Change Memory の C (MCU の CLK) 信号の立ち下がりまでの時間は、Serial Phase Change Memory の S#セットアップ時間待ちのために、ソフトウェア・ウェイトで制御しています。

Serial Phase Change Memory の C (MCU の CLK) 信号の立ち上がりから、Serial Phase Change Memory の S# (MCU の Port(CS#)) 信号の立ち上がりまでの時間は、Serial Phase Change Memory の S#ホールド時間待ちのために、ソフトウェア・ウェイトで制御しています。

Serial Phase Change Memory のデータシートを確認して、システムに応じたソフトウェア・ウェイト時間を 設定してください。

# 5.1.4 Serial Phase Change Memory の命令コード

Serial Phase Change Memory 制御のための以下の命令(Instruction)コードがあり、このコードを使って、コマンド制御を行います。

表 5-1 Instruction Set

| Instruction | Description                                   | Instruction format |

|-------------|-----------------------------------------------|--------------------|

| WREN        | Write Enable                                  | 0000 0110 (06 h)   |

| WRDI        | Write Disable                                 | 0000 0100 (04 h)   |

| RDSR        | Read Status-Register                          | 0000 0101 (05 h)   |

| WRSR        | Write Status-Register                         | 0000 0001 (01 h)   |

| FAST READ   | Read Data Bytes at Higher Speed               | 0000 1011 (0b h)   |

| READ        | Read Data Bytes                               | 0000 0011 (03 h)   |

| DOFR        | Dual output fast read                         | 0011 1011 (3b h)   |

| QOFR        | Quad output fast read                         | 0110 1011 (6b h)   |

| PP          | Page Program (legacy program)                 | 0000 0010 (02 h)   |

|             | Page Program (bit-alterable write)            | 0010 0010 (22 h)   |

|             | Page Program (on all 1s)                      | 1101 0001 (d1 h)   |

| DIFP        | Dual Input fast program (legacy program)      | 1010 0010 (a2 h)   |

|             | Dual Input fast program (bit-alterable write) | 1011 0011 (d3 h)   |

|             | Dual Input fast program (on all 1s)           | 1101 0101 (d5 h)   |

| QIFP        | Quad Input fast program (legacy program)      | 0011 0010 (32 h)   |

|             | Quad Input fast program (bit-alterable write) | 1101 0111 (d7 h)   |

|             | Quad Input fast program (on all 1s)           | 1101 1001 (d9 h)   |

| SE          | Sector Erase                                  | 1101 1000 (d8 h)   |

| BE          | Bulk Erase                                    | 1100 0111 (c7 h)   |

| RDID        | Read Identification                           | 1001 1111 (9f h)   |

#### 5.2 ソフトウェア構成

本サンプルコードは、Serial Phase Change Memory 制御のための上位層に位置する制御ソフトウェア (図 5-5 の Serial Phase Change Memory 制御ソフトウェア) です。

図 5-5 ソフトウェア構成

以下に制御手順を示します。

- ①Port(CS#)信号の立ち下げ

- ②ソフトウェア・ウェイト

- ③クロック同期式シングルマスタソフトウェアを使ったコマンド/データ送受信

- ④ソフトウェア・ウェイト

- ⑤Port(CS#)信号の立ち上げ

#### 5.3 必要メモリサイズ

以下に必要メモリサイズを示します。

#### 5.3.1 RX ファミリ

環境は、「2.動作確認条件」を参照してください。

#### (1) RX63N RSPI の場合

表 5-2 必要メモリサイズ

| 使用メモリ        | サイズ         | 備考                     |

|--------------|-------------|------------------------|

| ROM          | 2,901 バイト   | r_qspi_pcm_p5q_usr.c   |

|              | (リトルエンディアン) | r_qspi_pcm_p5q_sub.c   |

|              |             | r_qspi_pcm_p5q_drvif.c |

| RAM          | 5バイト        | r_qspi_pcm_p5q_usr.c   |

|              | (リトルエンディアン) | r_qspi_pcm_p5q_sub.c   |

|              |             | r_qspi_pcm_p5q_drvif.c |

| 最大使用ユーザスタック  | 136 バイト     |                        |

| 最大使用割り込みスタック | _           | 割り込み未使用                |

【注】 必要メモリサイズは C コンパイラのバージョンやコンパイルオプションにより異なります。

ROM/RAM サイズは下位層のクロック同期式シングルマスタソフトウェアに使用されるメモリサイズを含みません。

使用する MCU により、上記メモリサイズは異なります。

#### (2) RX111 RSPI の場合

表 5-3 必要メモリサイズ

| 使用メモリ        | サイズ         | 備考                     |

|--------------|-------------|------------------------|

| ROM          | 2,850 バイト   | r_qspi_pcm_p5q_usr.c   |

|              | (リトルエンディアン) | r_qspi_pcm_p5q_sub.c   |

|              |             | r_qspi_pcm_p5q_drvif.c |

| RAM          | 5バイト        | r_qspi_pcm_p5q_usr.c   |

|              | (リトルエンディアン) | r_qspi_pcm_p5q_sub.c   |

|              |             | r_qspi_pcm_p5q_drvif.c |

| 最大使用ユーザスタック  | 152 バイト     |                        |

| 最大使用割り込みスタック | _           | 割り込み未使用                |

【注】 必要メモリサイズは C コンパイラのバージョンやコンパイルオプションにより異なります。

ROM/RAM サイズは下位層のクロック同期式シングルマスタソフトウェアに使用されるメモリサイズを含みません。

使用する MCU により、上記メモリサイズは異なります。

最大使用ユーザスタックサイズは、下位層のクロック同期式シングルマスタソフトウェアのスタックサイズも含みます。

#### (3) RX111 SCI の場合

表 5-4 必要メモリサイズ

| 使用メモリ        | サイズ         | 備考                     |

|--------------|-------------|------------------------|

| ROM          | 2,850 バイト   | r_qspi_pcm_p5q_usr.c   |

|              | (リトルエンディアン) | r_qspi_pcm_p5q_sub.c   |

|              |             | r_qspi_pcm_p5q_drvif.c |

| RAM          | 5バイト        | r_qspi_pcm_p5q_usr.c   |

|              | (リトルエンディアン) | r_qspi_pcm_p5q_sub.c   |

|              |             | r_qspi_pcm_p5q_drvif.c |

| 最大使用ユーザスタック  | 148 バイト     |                        |

| 最大使用割り込みスタック | _           | 割り込み未使用                |

【注】 必要メモリサイズは C コンパイラのバージョンやコンパイルオプションにより異なります。

ROM/RAM サイズは下位層のクロック同期式シングルマスタソフトウェアに使用されるメモリサイズを含みません。

使用する MCU により、上記メモリサイズは異なります。

#### 5.3.2 RL78 ファミリ、78K0R/Kx3-L

命令の異なる MCU 毎にメモリサイズを示します。使用 MCU の命令を調査し参考にしてください。 環境は、「2.動作確認条件」を参照してください。

(1) RL78/G14 SAU 統合開発環境 CS+ for CA,CX の場合 (コンパイラ: CA78K0R)

表 5-5 必要メモリサイズ

| 使用メモリ        | サイズ       | 備考                        |

|--------------|-----------|---------------------------|

| ROM          | 5,291 バイト | r_qspi_pcm_p5q_usr.c      |

|              |           | r_qspi_pcm_p5q_sub.c      |

|              |           | r_qspi_pcm_p5q_drvif.c    |

|              |           | r_qspi_pcm_p5q_sfr_rl78.c |

| RAM          | 6バイト      | r_qspi_pcm_p5q_usr.c      |

|              |           | r_qspi_pcm_p5q_sub.c      |

|              |           | r_qspi_pcm_p5q_drvif.c    |

|              |           | r_qspi_pcm_p5q_sfr_rl78.c |

| 最大使用ユーザスタック  | 110 バイト   |                           |

| 最大使用割り込みスタック | _         | 割り込み未使用                   |

【注】 必要メモリサイズは C コンパイラのバージョンやコンパイルオプションにより異なります。

ROM/RAM サイズは下位層のクロック同期式シングルマスタソフトウェアに使用されるメモリサイズを含みません。

使用する MCU により、上記メモリサイズは異なります。

最大使用ユーザスタックサイズは、下位層のクロック同期式シングルマスタソフトウェアのスタックサイズも含みます。

(2) RL78/G14 SAU 統合開発環境 CS+ for CC の場合 (コンパイラ: CC-RL)

表 5-6 必要メモリサイズ

| 使用メモリ        | サイズ       | 備考                        |

|--------------|-----------|---------------------------|

| ROM          | 3,867 バイト | r_qspi_pcm_p5q_usr.c      |

|              |           | r_qspi_pcm_p5q_sub.c      |

|              |           | r_qspi_pcm_p5q_drvif.c    |

|              |           | r_qspi_pcm_p5q_sfr_rl78.c |

| RAM          | 6バイト      | r_qspi_pcm_p5q_usr.c      |

|              |           | r_qspi_pcm_p5q_sub.c      |

|              |           | r_qspi_pcm_p5q_drvif.c    |

|              |           | r_qspi_pcm_p5q_sfr_rl78.c |

| 最大使用ユーザスタック  | 80 バイト    |                           |

| 最大使用割り込みスタック | _         | 割り込み未使用                   |

【注】 必要メモリサイズは C コンパイラのバージョンやコンパイルオプションにより異なります。

ROM/RAM サイズは下位層のクロック同期式シングルマスタソフトウェアに使用されるメモリサイズを含みません。

使用する MCU により、上記メモリサイズは異なります。

#### (3) RL78/G14 SAU 統合開発環境 IAR Embedded Workbench の場合

表 5-7 必要メモリサイズ

| 使用メモリ        | サイズ       | 備考                        |

|--------------|-----------|---------------------------|

| ROM          | 5,534 バイト | r_qspi_pcm_p5q_usr.c      |

|              |           | r_qspi_pcm_p5q_sub.c      |

|              |           | r_qspi_pcm_p5q_drvif.c    |

|              |           | r_qspi_pcm_p5q_sfr_rl78.c |

| RAM          | 6バイト      | r_qspi_pcm_p5q_usr.c      |

|              |           | r_qspi_pcm_p5q_sub.c      |

|              |           | r_qspi_pcm_p5q_drvif.c    |

|              |           | r_qspi_pcm_p5q_sfr_rl78.c |

| 最大使用ユーザスタック  | 154 バイト   |                           |

| 最大使用割り込みスタック | _         | 割り込み未使用                   |

【注】 必要メモリサイズは C コンパイラのバージョンやコンパイルオプションにより異なります。

ROM/RAM サイズは下位層のクロック同期式シングルマスタソフトウェアに使用されるメモリサイズを含みません。

使用する MCU により、上記メモリサイズは異なります。

最大使用ユーザスタックサイズは、プロジェクト全体のスタックサイズです。下位層のクロック同期 式シングルマスタソフトウェアのスタックサイズも含みます。

#### (4) RL78/L13 SAU 統合開発環境 CubeSuite+の場合

表 5-8 必要メモリサイズ

| 使用メモリ        | サイズ       | 備考                        |

|--------------|-----------|---------------------------|

| ROM          | 4,801 バイト | r_qspi_pcm_p5q_usr.c      |

|              |           | r_qspi_pcm_p5q_sub.c      |

|              |           | r_qspi_pcm_p5q_drvif.c    |

|              |           | r_qspi_pcm_p5q_sfr_rl78.c |

| RAM          | 6バイト      | r_qspi_pcm_p5q_usr.c      |

|              |           | r_qspi_pcm_p5q_sub.c      |

|              |           | r_qspi_pcm_p5q_drvif.c    |

|              |           | r_qspi_pcm_p5q_sfr_rl78.c |

| 最大使用ユーザスタック  | 102 バイト   |                           |

| 最大使用割り込みスタック | _         | 割り込み未使用                   |

【注】 必要メモリサイズは C コンパイラのバージョンやコンパイルオプションにより異なります。

ROM/RAM サイズは下位層のクロック同期式シングルマスタソフトウェアに使用されるメモリサイズを含みません。

使用する MCU により、上記メモリサイズは異なります。

#### (5) RL78/L13 SAU 統合開発環境 IAR Embedded Workbench の場合

表 5-9 必要メモリサイズ

| 使用メモリ        | サイズ       | 備考                        |

|--------------|-----------|---------------------------|

| ROM          | 4,058 バイト | r_qspi_pcm_p5q_usr.c      |

|              |           | r_qspi_pcm_p5q_sub.c      |

|              |           | r_qspi_pcm_p5q_drvif.c    |

|              |           | r_qspi_pcm_p5q_sfr_rl78.c |

| RAM          | 6バイト      | r_qspi_pcm_p5q_usr.c      |

|              |           | r_qspi_pcm_p5q_sub.c      |

|              |           | r_qspi_pcm_p5q_drvif.c    |

|              |           | r_qspi_pcm_p5q_sfr_rl78.c |

| 最大使用ユーザスタック  | 120 バイト   |                           |

| 最大使用割り込みスタック | _         | 割り込み未使用                   |

【注】 必要メモリサイズは C コンパイラのバージョンやコンパイルオプションにより異なります。

ROM/RAM サイズは下位層のクロック同期式シングルマスタソフトウェアに使用されるメモリサイズを含みません。

使用する MCU により、上記メモリサイズは異なります。

最大使用ユーザスタックサイズは、プロジェクト全体のスタックサイズです。下位層のクロック同期 式シングルマスタソフトウェアのスタックサイズも含みます。

## 5.4 ファイル構成

表 5-10 に、サンプルコードで使用するファイルを示します。なお、統合開発環境で自動生成するファイルを除きます。

表 5-10 ファイル構成

| r01an1439jj0104_mcu_serial <dir></dir> |                                          |

|----------------------------------------|------------------------------------------|

| r01an1439jj0104_mcu.pdf                | アプリケーションノート                              |

| ¥source <dir></dir>                    | プログラム格納用フォルダ                             |

| ¥r_qspi_pcm_p5q <dir></dir>            | Serial Phase Change Memory 制御ソフトウェア用フォルダ |

| r_qspi_pcm_p5q.h                       | ヘッダファイル                                  |

| r_qspi_pcm_p5q_drvif.c                 | ドライバ I/F ソースファイル                         |

| r_qspi_pcm_p5q_drvif.h                 | ドライバ I/F ヘッダファイル                         |

| r_qspi_pcm_p5q_sfr.h.rl78g14           | レジスタ用共通定義(RL78/G14 用)                    |

| r_qspi_pcm_p5q_sfr.h.rl78g1c           | レジスタ用共通定義(RL78/G1C 用)                    |

| r_qspi_pcm_p5q_sfr.h.rl78l1c           | レジスタ用共通定義(RL78/L1C 用)                    |

| r_qspi_pcm_p5q_sfr.h.rl78l12           | レジスタ用共通定義(RL78/L12 用)                    |

| r_qspi_pcm_p5q_sfr.h.rl78l13           | レジスタ用共通定義(RL78/L13 用)                    |

| r_qspi_pcm_p5q_sfr.h.rx63n             | レジスタ用共通定義(RX63N 用)                       |

| r_qspi_pcm_p5q_sfr.h.rx111             | レジスタ用共通定義(RX111 用)                       |

| r_qspi_pcm_p5q_sfr_rl78g14.c           | レジスタ用共通定義ソースファイル(RL78/G14 用)             |

| r_qspi_pcm_p5q_sfr_rl78g1c.c           | レジスタ用共通定義ソースファイル(RL78/G1C 用)             |

| r_qspi_pcm_p5q_sfr_rl78l1c.c           | レジスタ用共通定義ソースファイル(RL78/G1C 用)             |

| r_qspi_pcm_p5q_sfr_rl78l12.c           | レジスタ用共通定義ソースファイル(RL78/G12 用)             |

| r_qspi_pcm_p5q_sfr_rl78l13.c           | レジスタ用共通定義ソースファイル(RL78/G13 用)             |

| r_qspi_pcm_p5q_sub.c                   | 内部関数ソースファイル                              |

| r_qspi_pcm_p5q_sub.h                   | 内部関数ヘッダファイル                              |

| r_qspi_pcm_p5q_usr.c                   | ユーザ I/F ソースファイル                          |

| ¥sample <dir></dir>                    | 動作確認プログラム格納用フォルダ                         |

| testmain.c                             | 動作確認用のサンプルソースファイル                        |

【注】 別途、MCU 個別のクロック同期式シングルマスタ制御ソフトウェアが必要です。

## 5.5 定数一覧

### 5.5.1 戻り値

表 5-11 にサンプルコードで使用する戻り値を示します。

表 5-11 戻り値

| 定数名             | 設定値           | 内容                   |

|-----------------|---------------|----------------------|

| PCM_OK          | (error_t)( 0) | Successful operation |

| PCM_ERR_PARAM   | (error_t)(-1) | Parameter error      |

| PCM_ERR_HARD    | (error_t)(-2) | Hardware error       |

| PCM_ERR_TIMEOUT | (error_t)(-6) | Time out error       |

| PCM_ERR_OTHER   | (error_t)(-7) | Other error          |

### 5.5.2 コマンド定義

表 5-12 にサンプルコードで使用するコマンド定義を示します。

表 5-12 コマンド定義(r\_qspi\_pcm\_p5q\_sub.c 参照)

| 定数名             | 設定値             | 内容                                            |

|-----------------|-----------------|-----------------------------------------------|

| PCM_CMD_WREN    | (uint8_t)(0x06) | Write Enable                                  |

| PCM_CMD_WRDI    | (uint8_t)(0x04) | Write Disable                                 |

| PCM_CMD_RDSR    | (uint8_t)(0x05) | Read Status Register                          |

| PCM_CMD_WRSR    | (uint8_t)(0x01) | Write Status Register                         |

| PCM_CMD_FREAD   | (uint8_t)(0x0b) | Read for Memory Array at Higher Speed         |

| PCM_CMD_READ    | (uint8_t)(0x03) | Read for Memory Array                         |

| PCM_CMD_DOFR    | (uint8_t)(0x3b) | Dual Output Fast Read                         |

| PCM_CMD_QOFR    | (uint8_t)(0x6b) | Quad Output Fast Read                         |

| PCM_CMD_PP_L    | (uint8_t)(0x02) | Page Program (Legacy Program)                 |

| PCM_CMD_PP_BA   | (uint8_t)(0x22) | Page Program (Bit-alterable Write)            |

| PCM_CMD_PP_OA   | (uint8_t)(0xd1) | Page Program (on all 1s)                      |

| PCM_CMD_DIFP_L  | (uint8_t)(0xa2) | Dual Input Fast Program (Legacy Program)      |

| PCM_CMD_DIFP_BA | (uint8_t)(0xd3) | Dual Input Fast Program (Bit-alterable Write) |

| PCM_CMD_DIFP_OA | (uint8_t)(0xd5) | Dual Input Fast Program (on all 1s)           |

| PCM_CMD_QIFP_L  | (uint8_t)(0x32) | Quad Input Fast Program (Legacy Program)      |

| PCM_CMD_QIFP_BA | (uint8_t)(0xd7) | Quad Input Fast Program (Bit-alterable Write) |

| PCM_CMD_QIFP_OA | (uint8_t)(0xd9) | Quad Input Fast Program (on all 1s)           |

| PCM_CMD_SE      | (uint8_t)(0xd8) | Sector Erase for Memory Array                 |

| PCM_CMD_BE      | (uint8_t)(0xc7) | Bulk Erase for Memory Array                   |

| PCM_CMD_RDID    | (uint8_t)(0x9f) | Read Identification                           |

### 5.5.3 各種定義

以下にサンプルコードで使用する各種定義した値を示します。

表 5-13 r\_qspi\_pcm\_p5q.h の各種定義値

| 定数名                           | 設定値                    | 内容                                            |

|-------------------------------|------------------------|-----------------------------------------------|

| PCM_DEV_NUM                   | (1)                    | 接続するデバイスの数                                    |

| PCM_DEV0                      | (0)                    | デバイス番号 0                                      |

| PCM_DEV1                      | (1)                    | デバイス番号 1                                      |

| PCM_DELAY_TASK                | (uint8_t)(1)           | ディレイタスクのウェイト時間[単位:ms](※1)                     |

| PCM_LOG_ERR                   | (1)                    | Log Type : Error                              |

| PCM_TRUE                      | (uint8_t)(0x01)        | Flag "ON"                                     |

| PCM_FALSE                     | (uint8_t)(0x00)        | Flag "OFF"                                    |

| PCM_MODE_PP_LEGACY            | (uint8_t)(1)           | Page Program Type : Legacy                    |

| PCM_MODE_PP_BIT_ALTE<br>RABLE | (uint8_t)(2)           | Page Program Type : Bit-alterable             |

| PCM_MODE_ON_ALL_1S            | (uint8_t)(3)           | Page Program Type : on all 1s (preset writes) |

| PCM_B_ERASE                   | (uint8_t)(1)           | Erasure Type : Bulk Erase                     |

| PCM_S_ERASE                   | (uint8_t)(2)           | Erasure Type : Sector Erase                   |

| PCM_MEM_SIZE                  | (uint32_t)(16777216)   | メモリサイズ(バイト単位)                                 |

|                               |                        | 左記は 128Mbit の場合の値です。                          |

| PCM_SECT_ADDR                 | (uint32_t)(0xfffe0000) | セクタ消去時のセクタアドレスマスク値                            |

|                               |                        | 左記は 128Mbit の場合の値です。                          |

| PCM_PAGE_SIZE                 | (uint32_t)(64)         | ページサイズ(バイト単位)                                 |

|                               |                        | 左記は、128Mbit の場合の値です。                          |

| PCM_ADDR_SIZE                 | (uint8_t)(3)           | アドレスサイズ(バイト単位)                                |

|                               |                        | 左記は 128Mbit の場合の値です。                          |

| PCM_WP_WHOLE_MEM              | (uint8_t)(0x1f)        | チップ全体のライトプロテクト                                |

※1: OS 制御時のディレイタスクです。本サンプルコードの OS 制御は、μITRON4.0 を想定しています。

| ā | 表 5-14 | r_qspi_pcm_p5q_sfr.h.rx63n の各種定義値 |    |

|---|--------|-----------------------------------|----|

|   |        | 設定値                               | 内容 |

| 定数名               | 設定値               | 内容                           |

|-------------------|-------------------|------------------------------|

| PCM_DR_CS0        | PORTA.PODR.BIT.B0 | デバイス番号 0 ポート出力データレジスタ SFR 定義 |

| PCM_DDR_CS        | PORTA.PDR.BIT.B0  | デバイス番号 0 ポート方向レジスタ SFR 定義    |

| PCM_DR_CS1        | -                 | デバイス番号 1 ポート出力データレジスタ SFR 定義 |

|                   |                   | (2 デバイス制御する場合は設定してください。)     |

| PCM_DDR_CS1       | -                 | デバイス番号 1 ポート方向レジスタ SFR 定義    |

|                   |                   | (2 デバイス制御する場合は設定してください。)     |

| PCM_HI            | (uint8_t)(0x01)   | Port "H"                     |

| PCM_LOW           | (uint8_t)(0x00)   | Port "L"                     |

| PCM_OUT           | (uint8_t)(0x01)   | Port Output Setting          |

| PCM_IN            | (uint8_t)(0x00)   | Port Input Setting           |

| PCM_BR            | (uint8_t)(0x01)   | コマンド送信時の転送レート ※1             |

| PCM_BR_WRITE_DATA | (uint8_t)(0x01)   | データ送信時の転送レート ※1              |

| PCM_BR_READ_DATA  | (uint8_t)(0x01)   | データ受信時の転送レート ※1              |

※ 1: RSPI を使ったクロック同期式シングルマスタ制御ソフトウェアを使用した場合、RSPI ビットレート レジスタ SPBR に設定される値です。周辺モジュールクロックを 48[MHz]とし、転送レートを 12[MHz] に設定する場合の値です。

SCI を使ったクロック同期式シングルマスタ制御ソフトウェアを使用した場合、ビットレートレジスタ BRR に設定される値です。周辺モジュールクロックを 48[MHz]とし、転送レートを 6[MHz]に設定する場合の値です。

| 定数名               | 設定値             | 内容                           |

|-------------------|-----------------|------------------------------|

| PCM_DR_CS0        | P8.0            | デバイス番号 0 ポート・レジスタ SFR 定義     |

| PCM_DDR_CS        | PM8.0           | デバイス番号 0 ポート・モード・レジスタ SFR 定義 |

| PCM_DR_CS1        | -               | デバイス番号 1 ポート・レジスタ SFR 定義     |

|                   |                 | (2 デバイス制御する場合は設定してください。)     |

| PCM_DDR_CS1       | -               | デバイス番号 1 ポート・モード・レジスタ SFR 定義 |

|                   |                 | (2 デバイス制御する場合は設定してください。)     |

| PCM_HI            | (uint8_t)(0x01) | Port "H"                     |

| PCM_LOW           | (uint8_t)(0x00) | Port "L"                     |

| PCM_OUT           | (uint8_t)(0x00) | Port Output Setting          |

| PCM_IN            | (uint8_t)(0x01) | Port Input Setting           |

| PCM_BR            | (uint8_t)(0x01) | コマンド送信時の転送レート ※1             |

| PCM_BR_WRITE_DATA | (uint8_t)(0x01) | データ送信時の転送レート ※1              |

| PCM_BR_READ_DATA  | (uint8_t)(0x01) | データ受信時の転送レート ※1              |

表 5-15 r\_qspi\_pcm\_p5q\_sfr.h.rl78 の各種定義値

※1:シリアル・アレイ・ユニットの CSI モードを使ったクロック同期式シングルマスタ制御ソフトウェア を使用した場合、シリアル・データ・レジスタ SDR のビット 15-9 に設定される値です。本サンプル コードでは、動作クロックを 24[MHz]とし、転送レートを 6[MHz]に設定する場合の値です。

## 表 5-16 r\_qspi\_pcm\_p5q\_sub.c の各種定義値

| 定数名            | 設定値                    | 内容                                |

|----------------|------------------------|-----------------------------------|

| PCM_SHORT_SIZE | (uint32_t)(0x00008000) | 下位関数での最大転送サイズの設定<br>(最大:32KBytes) |

#### 表 5-17 r\_qspi\_pcm\_p5q\_sub.h の各種定義値

| 定数名              | 設定値                 | 内容                            |

|------------------|---------------------|-------------------------------|

| PCM_BE_BUSY_WAIT | (uint32_t)(100000)  | Bulk Erase Busy Timeout       |

|                  |                     | 100000 × 1ms = 100s           |

| PCM_SE_BUSY_WAIT | (uint32_t)(800)     | Sector Erase Busy Timeout     |

|                  |                     | 800 × 1ms = 800ms             |

| PCM_WBUSY_WAIT   | (uint32_t)(400)     | Write Ready Timeout           |

|                  |                     | 400 × 1us = 400us             |

| PCM_T_WBUSY_WAIT | (uint16_t)MTL_T_1US | Write Busy Polling Time       |

| PCM_T_EBUSY_WAIT | (uint16_t)MTL_T_1MS | Erase Busy Polling Time       |

| PCM_T_CS_HOLD    | (uint16_t)MTL_T_1US | CS Stability Waiting Time     |

| PCM_T_R_ACCESS   | (uint16_t)MTL_T_1US | Reading Start Waiting Time    |

| PCM_REG_SRWD     | (uint8_t)(0x80)     | Status Register Write Disable |

| PCM_REG_BP3      | (uint8_t)(0x40)     | Block Protection Bit3         |

| PCM_REG_TB       | (uint8_t)(0x20)     | Top/Bottom Bit                |

| PCM_REG_BP2      | (uint8_t)(0x10)     | Block Protection Bit2         |

| PCM_REG_BP1      | (uint8_t)(0x08)     | Block Protection Bit1         |

| PCM_REG_BP0      | (uint8_t)(0x04)     | Block Protection Bit0         |

| PCM_REG_WEL      | (uint8_t)(0x02)     | Write Enable Latch Bit        |

| PCM_REG_WIP      | (uint8_t)(0x01)     | Write In Progress Bit         |

| PCM_REG          | (uint8_t)(0xfc)     | Write status fixed data       |

#### 5.6 構造体/共用体一覧

図 5-6、図 5-7 にサンプルコードで使用する構造体/共用体を示します。

```

typedef union {

uint32_t ul;

uint8_t uc[4];

} PCM_EXCHG_LONG;

/* total 4bytes

*/

```

図 5-6 サンプルコードで使用する共用体 (r\_qspi\_pcm\_p5q\_sub.c 参照)

```

typedef struct

Addr;

/* Address to issue a command

uint32 t

/* Number of bytes to be read/written

uint32_t

Cnt;

*/

DataCnt;

/* Temporary counter or Number of bytes to be written in a page

*/

uint16_t

/* Reserved

*/

uint8_t

rsv[2];

*/

uint8_t FAR*

pData;

/* Data storage buffer pointer

} r_qspi_pcm_info_t;

```

図 5-7 サンプルコードで使用する構造体(r\_qspi\_pcm\_p5q.h 参照)

| 表   | 5-18 | 構造体 | "r | aspi   | ncm  | info  | t" | の説明    |

|-----|------|-----|----|--------|------|-------|----|--------|

| 200 | 0 10 |     | '- | _4301_ | POIL | 11110 | ٠. | マノロルワ」 |

| 構造体     | 設定可能範囲                    | 説明                                                                                                               |

|---------|---------------------------|------------------------------------------------------------------------------------------------------------------|

| メンバ     |                           |                                                                                                                  |

| Addr    | 0000 0000h~<br>FFFF FFFFh | 書き込み/読み出しを開始するアドレス                                                                                               |

| Cnt     | 0000 0000h~<br>FFFF FFFFh | 書き込み/読み出しのデータカウンタ(バイト単位)                                                                                         |

| DataCnt | (設定禁止)                    | 書き込み時:書き込みデータカウンタ Temp.(最大 1Page)<br>読み出し時:読み出しデータカウンタ Temp.(最大 32KBytes)                                        |

| rsv[2]  | (設定無効)                    | アライメント調整用                                                                                                        |

| pData   | _                         | データ格納バッファポインタ<br>書き込み時:Serial Phase Change Memory へ書き込むデータの格納元<br>読み出し時:Serial Phase Change Memory から読み出すデータの格納先 |

#### 5.7 変数一覧

表 5-19 に static 型変数を示します。

表 5-19 static 型変数 (r\_qspi\_flash\_p5q\_sub.c 参照)

| 型              | 変数名             | 内容        | 使用関数                                      |

|----------------|-----------------|-----------|-------------------------------------------|

| STATIC uint8_t | g_pcm_cmdbuf[5] | コマンド用バッファ | r_qspi_pcm_send_cmd<br>r_qspi_pcm_set_cmd |

#### 5.8 関数一覧

表 5-20 に関数を示します。

表 5-20 関数

| 関数名                            | 概要                     |

|--------------------------------|------------------------|

| R_QSPI_PCM_Init_Driver()       | ドライバ初期化処理              |

| R_QSPI_PCM_Read_Status()       | ステータスレジスタ読み出し処理        |

| R_QSPI_PCM_Set_Write_Protect() | ライトプロテクト設定処理           |

| R_QSPI_PCM_Write_Di()          | WRDI コマンド発行処理          |

| R_QSPI_PCM_Read_Data()         | データ読み出し処理              |

| R_QSPI_PCM_Write_Data()        | データ書き込み処理              |

| R_QSPI_PCM_Write_Data_Page()   | データ書き込み処理(1Page 書き込み用) |

| R_QSPI_PCM_Erase()             | 消去処理                   |

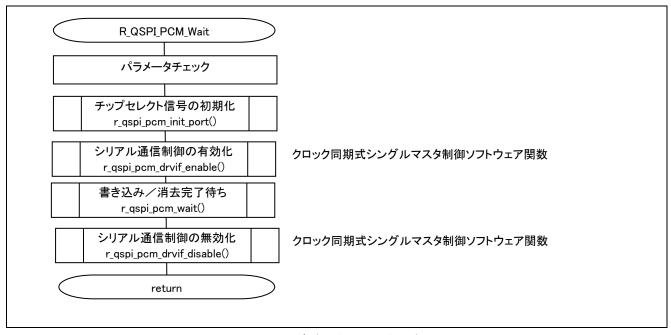

| R_QSPI_PCM_Read_ID()           | ID 読み出し処理              |

| R_QSPI_PCM_Wait()              | ビジーウェイト処理              |

キャッシュ搭載の MCU を使用する場合、読み出し/書き込み用データ格納バッファは、非キャッシュ領域を指定してください。

読み出し/書き込み用データ格納バッファアドレスは、下位層の MCU 個別のクロック同期式シングルマスタ制御ソフトウェアに依存し、4 バイト境界アドレスを指定する必要がある場合があります。 MCU 個別のクロック同期式シングルマスタ制御ソフトウェアのアプリケーションノートを参照してください。

### 5.9 関数仕様

サンプルコードの関数仕様を示します。

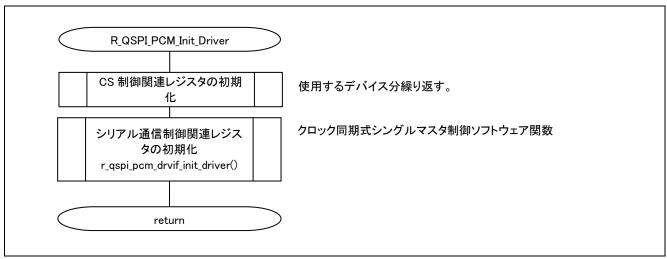

#### 5.9.1 ドライバ初期化処理

# R\_QSPI\_PCM\_Init\_Driver

概 要 ドライバ初期化処理

ィッダ r\_qspi\_pcm\_p5q.h, r\_qspi\_pcm\_p5q\_sub.h, r\_qspi\_pcm\_sfr.h, r\_qspi\_pcm\_drvif.h

宣言 error\_t R\_QSPI\_PCM\_Init\_Driver(void)

説 明 ・R\_QSPI\_PCM\_Init\_Port()関数をコールし、CS#端子の初期化を行います。

・クロック同期式シングルマスタ制御ソフトウェアの初期化関数をコールし、I/O ポートの初期化を行います。

・システム起動時に一度だけ呼び出してください。

引数 な

リターン値・初期化結果を返します。

PCM OK ; Successful operation

PCM\_ERR\_OTHER ; Other error

図 5-8 ドライバ初期化処理概要

PCM\_ERR\_OTHER

# Micron Technology 社製 P5Q Serial Phase Change Memory 制御ソフトウェア

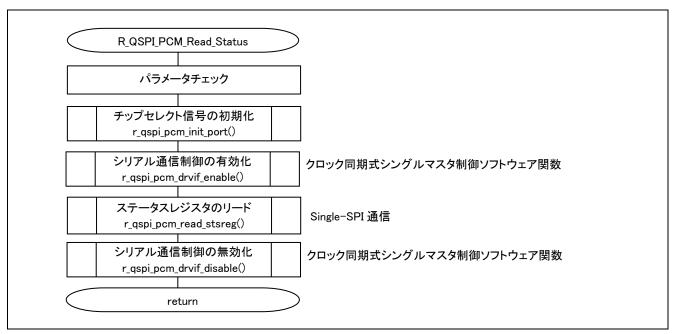

# 5.9.2 ステータスレジスタ読み出し処理

| R_QSPI_PCM_Rea | d_Status                                                                     |  |  |  |

|----------------|------------------------------------------------------------------------------|--|--|--|

| 概 要            | ステータスレジスタ読み出し処理                                                              |  |  |  |

| ヘッダ            | r_qspi_pcm_p5q.h, r_qspi_pcm_p5q_sub.h, r_qspi_pcm_sfr.h, r_qspi_pcm_drvif.h |  |  |  |

| 宣言             | error_t R_QSPI_PCM_Read_Status(uint8_t DevNo, uint8_t FAR* pStatus)          |  |  |  |

| 説明             | ・ステータスレジスタを読み出し、pStatus に格納します。                                              |  |  |  |

|                | 読み出しバッファとして、1 バイトを設定してください。                                                  |  |  |  |

|                | ・読み出しステータス格納バッファ(pStatus)には下記情報が格納されます。                                      |  |  |  |

|                | Bit 7:SRWD                                                                   |  |  |  |

|                | 1: TB, BP3, BP2, BP1, BP0 are read-only bits                                 |  |  |  |

|                | 0: TB, BP3, BP2, BP1, BP0 are read/writable                                  |  |  |  |

|                | Bits 6 to 2: BP3, TB, BP2, BP1, BP0                                          |  |  |  |

|                | Bit 1:WEL                                                                    |  |  |  |

|                | 1: Internal Write Enable Latch is set                                        |  |  |  |

|                | 0: Internal Write Enable Latch is reset                                      |  |  |  |

|                | Bit 0:WIP                                                                    |  |  |  |

|                | 1: Program or Erase cycle is in progress                                     |  |  |  |

|                | 0: No Program or Erase cycle is in progress                                  |  |  |  |

|                | ・プロテクト領域とプロテクトビットの関係は、使用する Serial Phase Change Me                            |  |  |  |

|                | mory のデータシートを参照してください。BP ビットが割り当てられていない可能<br>性があります。                         |  |  |  |

| 引数             | uint8_t DevNo ; デバイス番号                                                       |  |  |  |

|                | uint8_t FAR* pStatus ; 読み出しステータス格納バッファポインタ                                   |  |  |  |

| リターン値          | ・ステータスレジスタ取得結果を返します。                                                         |  |  |  |

|                | PCM_OK ; Successful operation                                                |  |  |  |

|                | PCM_ERR_PARAM ; Parameter error                                              |  |  |  |

|                | PCM_ERR_HARD ; Hardware error                                                |  |  |  |

; Other error

図 5-9 ステータスレジスタ読み出し処理概要

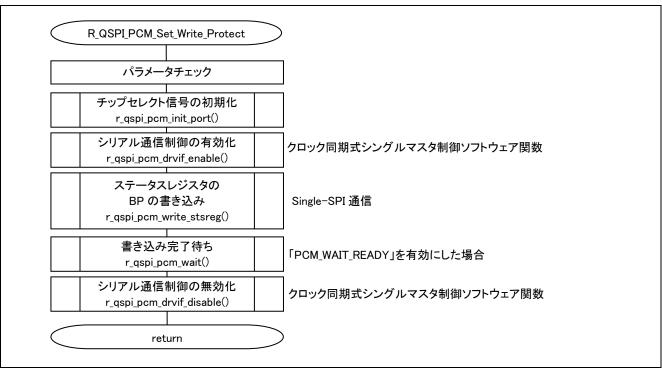

# 5.9.3 ライトプロテクト設定処理

#### R\_QSPI\_PCM\_Set\_Write\_Protect

概要

ライトプロテクト設定処理

ヘッダ

宣言説明

r\_qspi\_pcm\_p5q.h, r\_qspi\_pcm\_p5q\_sub.h, r\_qspi\_pcm\_sfr.h, r\_qspi\_pcm\_drvif.h error\_t R\_QSPI\_PCM\_Set\_Write\_Protect(uint8\_t DevNo, uint8\_t WpSts)

- ・32Mb/64Mb/128Mb Serial Phase Change Memory の使用制限(※ 1)により、 ライトプロテクトビットに 1 をセットすることができません。本ユーザ API をご使 用される際は、最新の Serial Phase Change Memory のデータシートから製品情 報をご確認ください。

- (※1:以下の使用制限情報を参照。32Mb/64Mb P5Q Serial Phase Change Me mory Errata Rev.A、128Mb P5Q Serial Phase Change Memory Errata Rev.D)

- ・ライトプロテクトの設定を行います。

- ・ライトプロテクト設定データ(WpSts)は下記のように設定してください。

| WpSts       | BP3 | TB1 | BP2 | BP1 | BP0 | Protected Area                |

|-------------|-----|-----|-----|-----|-----|-------------------------------|

| 0x00        | 0   | 0   | 0   | 0   | 0   | None                          |

| 0x01        | 0   | 0   | 0   | 0   | 1   | Upper 32nd (sector 31)        |

| 0x02        | 0   | 0   | 0   | 1   | 0   | Upper 16th (sectors 30 to 31) |

| 0x03        | 0   | 0   | 0   | 1   | 1   | Upper 8th (sectors 28 to 31)  |

| 0x04        | 0   | 0   | 1   | 0   | 0   | Upper 4th (sectors 24 to 31)  |

| 0x05        | 0   | 0   | 1   | 0   | 1   | Upper half (sectors 16 to 31) |

| 0x06        | 0   | 0   | 1   | 1   | 0   | All sectors (sectors 0 to 31) |

| 0x07        | 0   | 0   | 1   | 1   | 1   | All sectors (sectors 0 to 31) |

| 0x10 - 0x16 | 1   | 0   | 0/1 | 0/1 | 0/1 | 本ユーザ API では設定禁止               |

| 0x17        | 1   | 0   | 1   | 1   | 1   | All sectors (sectors 0 to 31) |

| 0x08        | 0   | 1   | 0   | 0   | 0   | None                          |

| 0x09        | 0   | 1   | 0   | 0   | 1   | Lower 32nd (sector 0)         |

| 0x0a        | 0   | 1   | 0   | 1   | 0   | Lower 16th (sectors 0 to 1)   |

| 0x0b        | 0   | 1   | 0   | 1   | 1   | Lower 8th (sectors 0 to 3)    |

| 0x0c        | 0   | 1   | 1   | 0   | 0   | Lower 4th (sectors 0 to 7)    |

| 0x0d        | 0   | 1   | 1   | 0   | 1   | Lower half (sectors 0 to 15)  |

| 0x0e        | 0   | 1   | 1   | 1   | 0   | All sectors (sectors 0 to 31) |

| 0x0f        | 0   | 1   | 1   | 1   | 1   | All sectors (sectors 0 to 31) |

| 0x18-0x1e   | 1   | 1   | 0/1 | 0/1 | 0/1 | 本ユーザ API では設定禁止               |

| 0x1f        | 1   | 1   | 1   | 1   | 1   | All sectors (sectors 0 to 31) |

- SRWD は、0 に設定されます。

- ・プロテクト領域とプロテクトビットの関係は、使用する Serial Phase Change Me mory のデータシートを参照してください。BP ビットが割り当てられていない可能性があります。

- ・書き込み完了待ちの方法は二種類あります。以降にその方法を示します。なお、次の処理(書き込み/読み出し/消去等)は、書き込み完了を確認した後、実行してください。

- ・本ユーザ API で完了待ちを行う場合、r\_qspi\_pcm\_p5q.h の「PCM\_WAIT\_READY」を有効にしてください。

- ・本ユーザ API で完了待ちを行わない場合、r\_qspi\_pcm\_p5q.h の「PCM\_WAIT\_RE ADY」を無効にし、本ユーザ API の処理が完了した後、R\_QSPI\_PCM\_Wait()をコールしてください。この処理方法では、ユーザの任意のタイミングで書き込み完了待

ちを確認することができます。使用方法は図 5-11 を参照してください。

引数 uint8\_t DevNo ; デバイス番号

uint8\_t WpSts : ライトプロテクト設定データ

リターン値・ライトプロテクト設定結果を返します。

PCM\_OK ; Successful operation PCM\_ERR\_PARAM ; Parameter error PCM\_ERR\_HARD ; Hardware error

PCM\_ERR\_TIMEOUT ; Time out error (「PCM\_WAIT\_READY」有効時)

PCM\_ERR\_OTHER ; Other error

図 5-10 ライトプロテクト設定処理概要

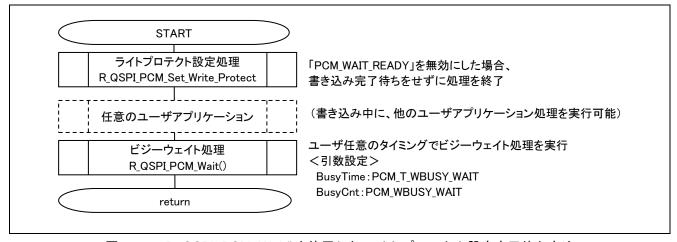

図 5-11 R\_QSPI\_PCM\_Wait()を使用したライトプロテクト設定完了待ち方法

## 5.9.4 WRDI コマンド発行処理

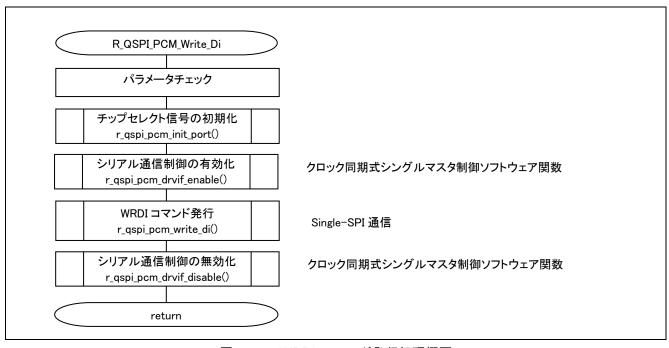

#### R\_QSPI\_PCM\_Write\_Di 概要 WRDI コマンド発行処理 ヘッダ $r\_qspi\_pcm\_p5q.h, r\_qspi\_pcm\_p5q\_sub.h, r\_qspi\_pcm\_p5q\_sfr.h,$ r\_qspi\_pcm\_p5q\_drvif.h 宣 言 error t R QSPI PCM Write Di(uint8 t DevNo) 説明 ・ステータスレジスタの WEL ビットをクリアします。 ・プログラムエラー、消去エラーと判断される場合は、本関数をコールして WEL ビッ トをクリアする必要があります。 引 数 uint8 t DevNo ; デバイス番号 リターン値 クリア結果を返します。 ; Successful operation PCM\_OK PCM \_ERR\_PARAM ; Parameter error ; Hardware error PCM ERR HARD ; Other error PCM \_ERR\_OTHER

図 5-12 WRDIコマンド発行処理概要

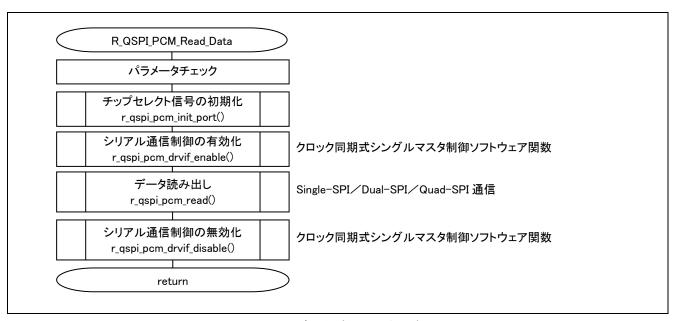

#### 5.9.5 データ読み出し処理

#### R\_QSPI\_PCM\_Read\_Data \_\_\_\_ データ読み出し処理 概要 ヘッダ r\_qspi\_pcm\_p5q.h, r\_qspi\_pcm\_p5q\_sub.h, r\_qspi\_pcm\_sfr.h, r\_qspi\_pcm\_drvif.h error tR QSPI PCM Read Data(uint8 t DevNo, r qspi pcm info t FAR\* 宣 言

pPcm\_Info)

説明 · Serial Phase Change Memory 上の指定アドレスから指定バイト数分、データを読 み出し、pData に格納します。

・最終読み出しアドレスは、Serial Phase Change Memory 容量-1 です。

・ロールオーバーによる読み出しはできません。最終アドレスの読み出し後、一度処 理を完了させて、再度アドレスを設定し直してから、本ユーザ API をコールしてく ださい。なお、32Mb/64Mb Serial Phase Change Memory の使用制限(※1)によ り、最終アドレスを読み出した後、次の読み出しではアドレスがロールオーバーし ないため、続けて先頭アドレスの読み出しを行うことはできません。

(※1:以下の使用制限情報を参照。32Mb/64Mb P5Q Serial Phase Change Memory Errata Rev.A)

; デバイス番号 引 数 uint8 t DevNo

> r\_qspi\_pcm\_info\_t FAR\* pPcm\_Info ; PCM 通信情報構造体 Addr uint32\_t : 読み出し開始アドレス uint32 t Cnt ; 読み出しバイト数

uint16 t DataCnt ; 読み出しバイト Temp. (設定禁止) uint8\_t FAR\* pData ; 読み出しデータ格納バッファポインタ

リターン値 読み出し結果を返します。

> PCM OK ; Successful operation PCM\_ERR\_PARAM ; Parameter error PCM\_ERR\_HARD Hardware error PCM ERR OTHER ; Other error

図 5-13 データ読み出し処理概要

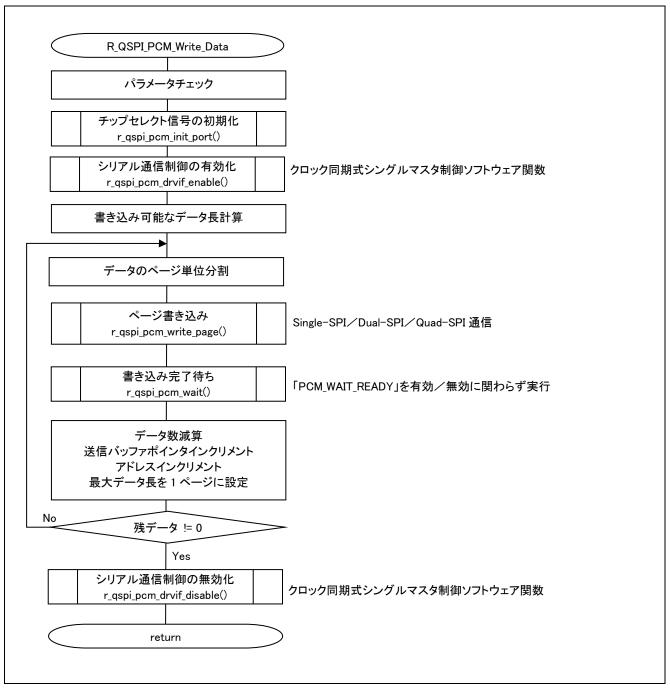

# 5.9.6 データ書き込み処理

| e_Data                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| データ書き込み処理                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                         |

| error_t R_QSPI_PCM_Write_Data(uint                                                                                                                                                                                                                                         | ub.h, r_qspi_pcm_sfr.h, r_qspi_pcm_drvif.h<br>8_t DevNo, r_qspi_pcm_info_t FAR*                                                                                                                                                                                         |

| <ul> <li>・pData のデータを Serial Phase Chan 数分書き込みます。</li> <li>・ Mode の設定により、legacy program みを実行します。</li> <li>・ Serial Phase Change Memory への書能です。プロテクトされた領域への記せん。WEL ビットは、セット状態で・プログラムエラーが発生した場合、式態です。</li> <li>・ 最終書き込みアドレスは、Serial Pha・書き込みバイト数(Cnt)に設定でき容量の値です。</li> </ul> | エラーを返しません。WEL ビットは、セット<br>ase Change Memory 容量-1 です。<br>る最大値は、Serial Phase Change Memory<br>J.h の「PCM_WAIT_READY」の設定有無に関                                                                                                                                                |

| uint8_t DevNo r_qspi_pcm_info_t FAR* pPcm_Info uint32_t Addr uint32_t Cnt uint16_t DataCnt uint8_t FAR* pData uint8_t Mode                                                                                                                                                 | <ul> <li>デバイス番号</li> <li>PCM 通信情報構造体</li> <li>書き込み開始アドレス</li> <li>書き込みバイト数</li> <li>書き込みバイト Temp. (設定禁止)</li> <li>書き込みデータ格納バッファポインタ</li> <li>書き込みモード(以下より1つ選択)</li> <li>PCM_MODE_PP_LEGACY</li> <li>PCM_MODE_PP_BIT_ALTERABLE</li> <li>PCM_MODE_PP_ON_ALL_1S</li> </ul> |

|                                                                                                                                                                                                                                                                            | データ書き込み処理 r_qspi_pcm_p5q.h, r_qspi_pcm_p5q_s error_t R_QSPI_PCM_Write_Data(uinta pPcm_Info, uint8_t Mode)                                                                                                                                                               |

リターン値

読み出し結果を返します。

PCM\_OK ; Successful operation

PCM\_ERR\_PARAM ; Parameter error

PCM\_ERR\_HARD ; Hardware error

PCM\_ERR\_TIMEOUT ; Time out error

PCM\_ERR\_OTHER ; Other error

図 5-14 データ書き込み処理概要

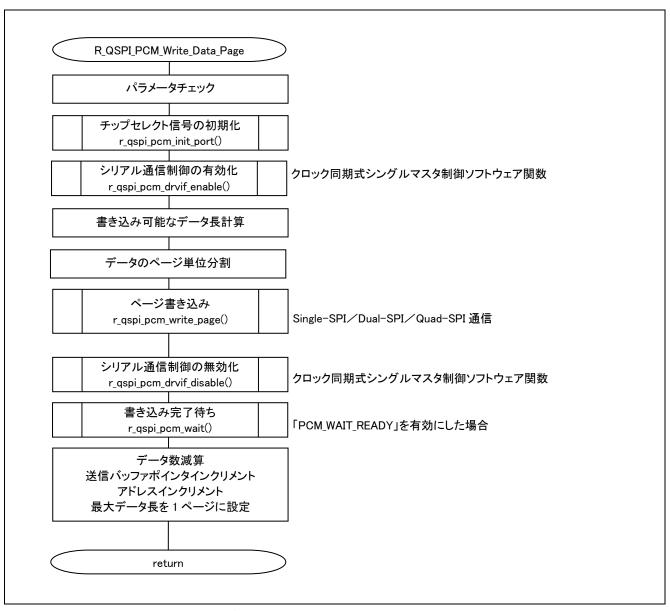

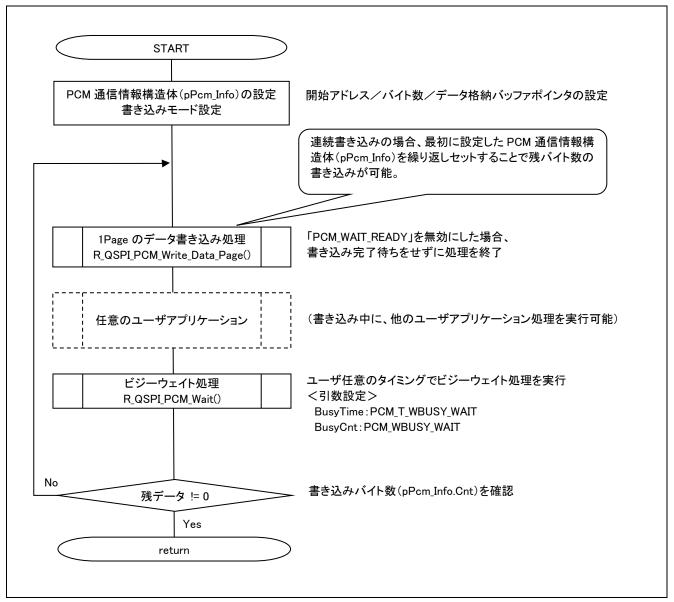

#### 5.9.7 データ書き込み処理(1Page 書き込み用)

#### R\_QSPI\_PCM\_Write\_Data\_Page

概要デー

データ書き込み処理(1Page 書き込み用)

ヘッダ

宣言

r\_qspi\_pcm\_p5q.h, r\_qspi\_pcm\_p5q\_sub.h, r\_qspi\_pcm\_sfr.h, r\_qspi\_pcm\_drvif.h error\_t R\_QSPI\_PCM\_Write\_Data\_Page(uint8\_t DevNo, r\_qspi\_pcm\_info\_t FAR\* pPcm\_Info, uint8\_t Mode)

説明

- pData のデータを Serial Phase Change Memory 上の指定アドレスから指定バイト 数分(最大: 1Page) 書き込みます。

- Mode の設定により、legacy program、bit-alterable write、on all 1s による書き込みを実行します。

- ・大容量のデータ書き込みの際、Page 単位に通信を分割するため、通信中に他の処理ができなくなることを防ぐことができます。

- ・Serial Phase Change Memory への書き込みは、ライトプロテクト解除領域のみ可能です。プロテクトされた領域への書き込みはできません。また、エラーを返しません。WEL ビットは、セット状態です。

- ・プログラムエラーが発生した場合、エラーを返しません。WEL ビットは、セット 状態です。

- ・最終書き込みアドレスは、Serial Phase Change Memory 容量-1 です。

- ・書き込みバイト数(Cnt)に設定できる最大値は、Serial Phase Change Memory 容量の値です。

- ・1Page を超えるバイト数が設定されている場合でも、1Page 書き込み処理完了後、 残バイト数と次アドレス情報が PCM 通信情報構造体(pPcm\_Info)に残ります。 未変更のまま再びその pPcm\_Info をセットすることで残バイト数の書き込みが可 能です。

- ・書き込み完了待ちの方法は二種類あります。以降にその方法を示します。なお、次の処理(書き込み/読み出し/消去等)は、書き込み完了を確認した後、実行してください

- ・本ユーザ API で完了待ちを行う場合、r\_qspi\_pcm\_p5q.h の「PCM\_WAIT\_READY」を有効にしてください。

- ・本ユーザ API で完了待ちを行わない場合、r\_qspi\_pcm\_p5q.h の「PCM\_WAIT\_READY」を無効にし、本ユーザ API の処理が完了した後、R\_QSPI\_PCM\_Wait()をコールしてください。この処理方法では、ユーザの任意のタイミングで書き込み完了待ちを確認することができます。使用方法は図 5-16 を参照してください。

引 数

uint8\_t DevNo ; デバイス番号

r\_qspi\_pcm\_info\_t FAR\* pPcm\_Info ; PCM 通信情報構造体 uint32\_t Addr ; 書き込み開始アドレス uint32\_t Cnt ; 書き込みバイト数

uint16\_tDataCnt;書き込みバイト Temp. (設定禁止)uint8\_t FAR\*pData;書き込みデータ格納バッファポインタuint8\_tMode:書き込みモード(以下より1つ選択)

PCM\_MODE\_PP\_LEGACY

; PCM\_MODE\_PP\_BIT\_ALTERABLE ; PCM\_MODE\_PP\_ON\_ALL\_1S

リターン値

読み出し結果を返します。

PCM\_OK ; Successful operation

PCM\_ERR\_PARAM ; Parameter error

PCM\_ERR\_HARD ; Hardware error

PCM\_ERR\_TIMEOUT ; Time out error (「PCM\_WAIT\_READY」有効時)

PCM\_ERR\_OTHER ; Other error

図 5-15 データ書き込み処理 (1Page 書き込み用) 概要

図 5-16 R\_QSPI\_PCM\_Wait()を使用したデータ書き込み処理(1Page 書き込み用)の完了待ち方法

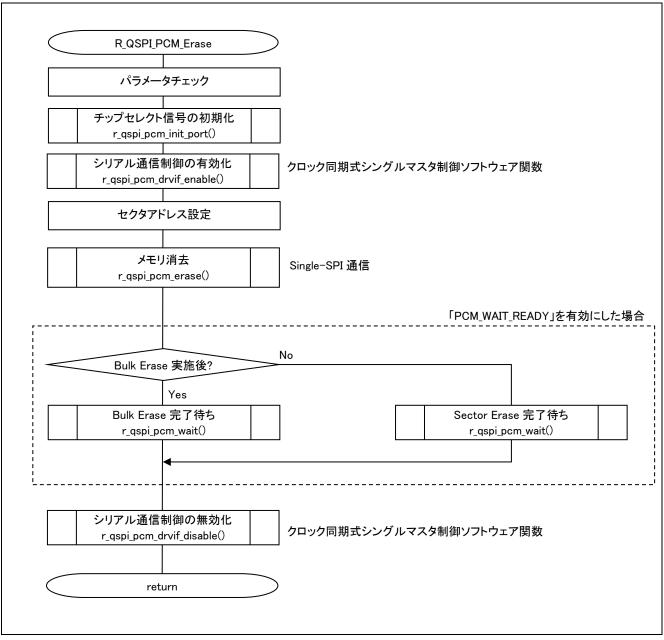

#### 5.9.8 消去処理

## R\_QSPI\_PCM\_Erase

概要

消去処理

ヘッダ

r\_qspi\_pcm\_p5q.h, r\_qspi\_pcm\_p5q\_sub.h, r\_qspi\_pcm\_sfr.h, r\_qspi\_pcm\_drvif.h error\_t R\_QSPI\_PCM\_Erase(uint8\_t DevNo, uint32\_t Addr, uint8\_t Mode)

宣言説明

- ・メモリの全データ消去 (Bulk Erase)、または指定されたセクタの全データ消去 (Sector Erase) を行います。

- ・Mode の設定により、Bulk Erase または Sector Erase を実行します。

- ・Bulk Erase の場合、Addr には 0x00000000 を設定してください。

- Serial Phase Change Memory の消去は、ライトプロテクト解除領域のみ可能です。 プロテクトされている領域は、消去はできません。また、エラーは返りません。 WEL ビットは、セット状態です。

- ・消去エラーが発生した場合、エラーを返しません。WEL ビットは、セット状態です。

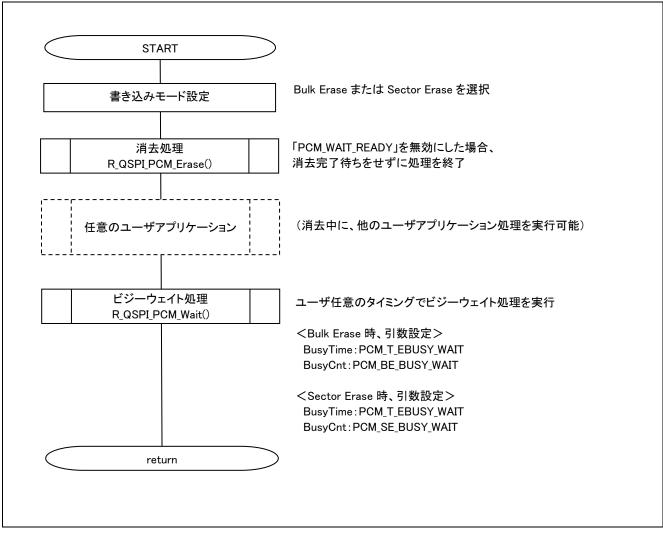

- ・消去完了待ちの方法は二種類あります。以降にその方法を示します。なお、次の処理(書き込み/読み出し/消去等)は、消去完了を確認した後、実行してください。

- ・本ユーザ API で完了待ちを行う場合、r\_qspi\_pcm\_p5q.h の「PCM\_WAIT\_READY」を有効にしてください。

- ・本ユーザ API で完了待ちを行わない場合、r\_qspi\_pcm\_p5q.h の「PCM\_WAIT\_READY」を無効にし、本ユーザ API の処理が完了した後、R\_QSPI\_PCM\_Wait()をコールしてください。この処理方法では、ユーザの任意のタイミングで書き込み完了待ちを確認することができます。使用方法は図 5-18 を参照してください。

- Bulk Erase と Sector Erase では、R\_QSPI\_PCM\_Wait()をコールする際の引数 BusyCnt の設定が異なります。

Bulk Erase 時 : BusyCnt = PCM\_BE\_BUSY\_WAIT Sector Erase 時 : BusyCnt = PCM\_SE\_BUSY\_WAIT

引 数

uint8\_t

DevNo ; デバイス番号

uint32\_t

Addr ; 消去アドレス

uint8\_t

Mode ; 消去モード (下記より1つ選択)

; PCM\_MODE\_B\_ERASE

; PCM MODE S ERASE

リターン値

・消去結果を返します。

PCM\_OK ; Successful operation PCM\_ERR\_PARAM ; Parameter error

PCM\_ERR\_HARD ; Hardware error

PCM\_ERR\_TIMEOUT ; Time out error (「PCM\_WAIT\_READY」有効時)

PCM\_ERR\_OTHER ; Other error

図 5-17 消去処理概要

図 5-18 R\_QSPI\_PCM\_Wait()を使用した消去処理の完了待ち方法

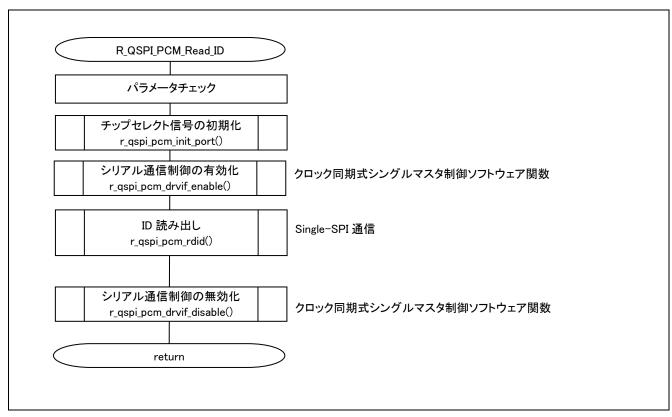

## 5.9.9 ID 読み出し処理

| R_QSPI_PCM_Read | _ID                                                                                                                                                                                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 概 要             | ID 読み出し処理                                                                                                                                                                                                                                             |