## IS-2100ARH, IS-2100AEH

Radiation Hardened High Frequency Half Bridge Drivers

FN9037 Rev 3.00 May 10, 2016

The radiation hardened IS-2100ARH, IS-2100AEH are high frequency, 130V half bridge N-Channel MOSFET driver ICs, which are functionally similar to industry standard 2110 types. The low-side and high-side gate drivers are independently controlled. This gives the user maximum flexibility in dead time selection and driver protocol.

In addition, the devices have on-chip error detection and correction circuitry, which monitors the state of the high-side latch and compares it to the HIN signal. If they disagree, a set or reset pulse is generated to correct the high-side latch. This feature protects the high-side latch from single event upsets (SEUs).

## **Applications**

- · High frequency switch-mode power supplies

- · Drivers for inductive loads

- · DC motor drivers

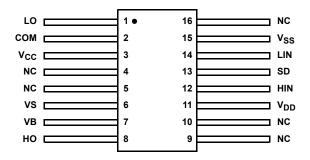

## Pin Configuration

IS-2100ARH, IS-2100AEH FLATPACK (CDFP4-F16) **TOP VIEW**

## **Features**

- Electrically screened to DLA SMD # 5962-99536

- · QML qualified per MIL-PRF-38535 requirements

- · Radiation environment

- DI RSG process provides latch-up immunity

- SEU rating ...... 82MeV/mg/cm<sup>2</sup>

- Vertical device architecture reduces sensitivity to low dose rates

- Bootstrap supply maximum voltage to 150V

- Drives 1000pF load at 1MHz with rise and fall times of 30ns (typical)

- · 1.5A (typical) peak output current

- · Independent inputs for non-half bridge topologies

- Low DC power consumption . . . . . . . . . . 60mW (typical)

- Operates with V<sub>DD</sub> = V<sub>CC</sub> over 12V to 20V range

- · Low-side supply undervoltage protection

# **Ordering Information**

| ORDERING SMD NUMBER<br>(Note 2) | PART NUMBER<br>(Note 1) | TEMP RANGE (°C) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG.# |

|---------------------------------|-------------------------|-----------------|-----------------------------|---------------|

| 5962F9953602V9A                 | ISO-2100ARH-Q           | -55 to +125     | Die                         |               |

| 5962F9953602VXC                 | IS9-2100ARH-Q           | -55 to +125     | 16 Ld Flatpack              | K16.A         |

| 5962F9953602QXC                 | IS9-2100ARH-8           | -55 to +125     | 16 Ld Flatpack              | K16.A         |

| N/A                             | IS9-2100ARH/Proto       | -55 to +125     | 16 Ld Flatpack              | K16.A         |

| 5962F9953603VXC                 | IS9-2100AEH-Q           | -55 to +125     | 16 Ld Flatpack              | K16.A         |

| 5962F9953603V9A                 | ISO-2100AEH-Q           | -55 to +125     | Die                         |               |

#### NOTES:

- 1. These Intersil Pb-free Hermetic packaged products employ 100% Au plate e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

- 2. Specifications for Rad Hard QML devices are controlled by the Defense Logistics Agency Land and Maritime (DLA). The SMD numbers listed in the "Ordering Information" table must be used when ordering.

## **Die Characteristics**

#### **DIE DIMENSIONS:**

4820 $\mu$ m x 3300 $\mu$ m (190 mils x 130 mils) Thickness: 483 $\mu$ m  $\pm$ 25.4 $\mu$ m (19 mils  $\pm$ 1 mil)

### **INTERFACE MATERIALS:**

### **Glassivation:**

Type: PSG (Phosphorous Silicon Glass) Thickness:  $8.0k\mathring{A} \pm 1.0k\mathring{A}$

### **Top Metallization:**

Type: ALSiCu

Thickness: 16.0kÅ ±2kÅ

#### Substrate:

Radiation Hardened Silicon Gate, Dielectric Isolation

#### **Backside Finish:**

Silicon

#### **ASSEMBLY RELATED INFORMATION:**

#### **Substrate Potential:**

Unbiased (DI)

### **ADDITIONAL INFORMATION:**

### **Worst Case Current Density:**

$< 2.0 \times 10^5 \text{ A/cm}^2$

### **Transistor Count:**

542

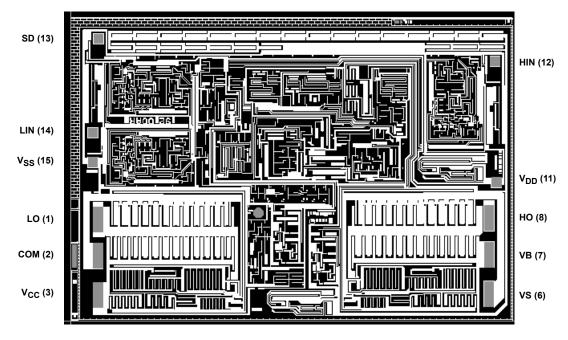

## **Metallization Mask Layout**

#### IS-2100ARH, IS-2100AEH

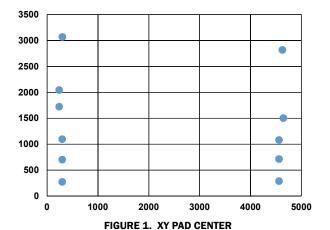

TABLE 1. IS-2100ARH, ISL-2100AEH DIE LAYOUT X-Y COORDINATES

| PAD NUMBER | PAD NAME | PAD CENTER |           | PAD SIZE   |            |

|------------|----------|------------|-----------|------------|------------|

|            |          | X<br>(μm)  | Υ<br>(μm) | DX<br>(μm) | DY<br>(μm) |

| 3          | vcc      | 296.5      | 270       | 109        | 280        |

| 6          | VS       | 4561       | 284.5     | 109        | 280        |

| 7          | VB       | 4561       | 711       | 109        | 280        |

| 8          | но       | 4561       | 1079      | 109        | 280        |

| 11         | VDD      | 4645.5     | 1500      | 109        | 109        |

| 12         | HIN      | 4627.5     | 2817      | 109        | 109        |

| 13         | SD       | 302        | 3064.5    | 109        | 109        |

| 14         | LIN      | 237.5      | 2040      | 109        | 109        |

| 15         | VSS      | 239        | 1719      | 109        | 109        |

| 1          | LO       | 296.5      | 1095      | 109        | 280        |

| 2          | СОМ      | 296.5      | 697       | 109        | 280        |

NOTE: Origin of coordinates is the lower left corner of the die.

**Revision History** The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE         | REVISION | CHANGE                                                                                                                                                 |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 10, 2016 | FN9037.3 | Updated Ordering information table by applying new standards and adding Notes 1 and 2.  Added Table 1 on page 4.  Added Package Outline Drawing K16.A. |

## **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <a href="https://www.intersil.com">www.intersil.com</a>.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support.

© Copyright Intersil Americas LLC 2001-2016. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

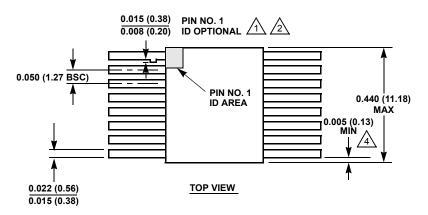

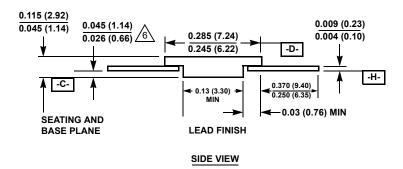

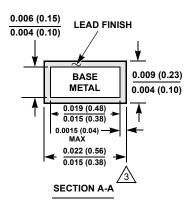

# **Package Outline Drawing**

#### K16.A

16 LEAD CERAMIC METAL SEAL FLATPACK PACKAGE

Rev 2, 1/10

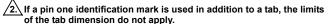

#### NOTES:

1. Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark. Alternately, a tab may be used to identify pin one.

1/3. The maximum limits of lead dimensions (section A-A) shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

4. Measure dimension at all four corners.

5. For bottom-brazed lead packages, no organic or polymeric materials shall be molded to the bottom of the package to cover the leads.

6. Dimension shall be measured at the point of exit (beyond the meniscus) of the lead from the body. Dimension minimum shall be reduced by 0.0015 inch (0.038mm) maximum when solder dip lead finish is applied.

- 7. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 8. Controlling dimension: INCH.