-

-

-

設計リソース

- 設計・開発

- 注目の設計ツール

- パートナー

- コンテンツ&トレーニング

-

サポート

-

サンプル&ご購入

-

ルネサスサイトからの直接購入

便利なルネサスからの直接購入を選択できるようになりました。

- 購入関連情報

-

ルネサスサイトからの直接購入

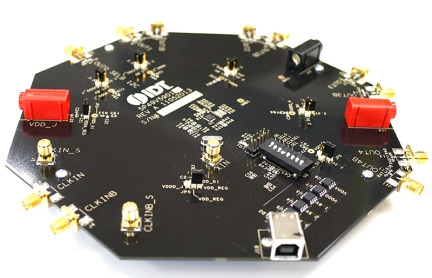

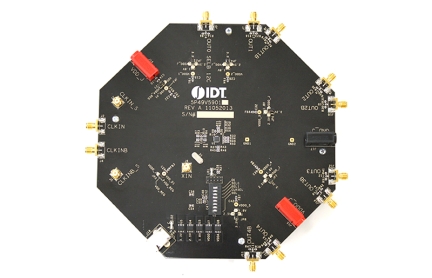

EVKVC5-5901

circleアクティブEvaluation Board for 5P49V5901 VersaClock® 5

Alternative replacement for the EVKVC5-5901ALL

概要

説明

This is the evaluation board for the Renesas 5P49V59xx VersaClock 5 family of programmable clock generators. With RMS phase jitter less than 0.7 picoseconds over the full 12 kHz to 20 MHz integration range, the device meets the stringent jitter requirements of PCI ExpressR Gen 1/2/3, USB 3.0, and 1G/10G Ethernet. VersaClock 5 ideal for high-performance consumer, networking, industrial, computing, and data-communications applications.

Note that the evaluation board for the VersaClock 5 family is based around the 5P49V5901, which contains a superset of functionality for the other family members.

特長

- 4 Differential Outputs capable of generating any output frequency using Renesas Timing CommanderTM software

- SMA connectors for outputs

- When the board is connected to a PC running Renesas Timing Commander Software through USB, the device can be configured and programmed to generate frequencies with best-in-class performance

- The 25MHz crystal installed on the board can source a reference frequency to the device when CLKIN/CLKINB is not used.

アプリケーション

関連製品

ドキュメント

|

|

|

|

|---|---|---|

| 分類 | タイトル | 日時 |

| マニュアル-ハードウェア | PDF 725 KB | |

| マニュアル-ソフトウェア | PDF 2.04 MB | |

| 回路図 | PDF 844 KB | |

3 items

|

||

製品選択

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product

ビデオ&トレーニング

This video will show you how to program VersaClock® 5 Low Power Programmable Clock Generator.

How to Program VersaClock - 5 Programmable Clock Generator by IDT

This video will show you how to program VersaClock® 5 Low Power Programmable Clock Generator.

This video will show you how to program VersaClock® 5 Low Power Programmable Clock Generator.