# RENESAS

#### Choosing the Correct Crystal or XO for FemtoClock™3

This application note highlights the characteristics that are to be considered when choosing a crystal or XO for FemtoClock<sup>™</sup>3 (FC3) devices. This document also contains a list of recommended crystals to be used with FemtoClock3.

#### Contents

| 1.  | Introduction                             | 1 |

|-----|------------------------------------------|---|

| 2.  | Frequency                                | 2 |

| 3.  | Load Capacitance                         | 5 |

| 4.  | Equivalent Series Resistance             | 5 |

| 5.  | Drive Level                              | 5 |

| 6.  | Using a Crystal Oscillator (XO) with FC3 | 6 |

| 7.  | Operating Temperature                    | 6 |

| 8.  | Frequency Tolerance                      | 7 |

| 9.  | Aging                                    | 7 |

| 10. | Recommended Crystals (XTAL)              | 7 |

| 11. | Revision History                         | 8 |

#### 1. Introduction

The FemtoClock3 (FC3) family of devices uses a crystal (or XO) as a reference for the analog PLL (APLL). All FC3 outputs are synthesized from the APLL. When choosing the crystal or XO for an FC3 device, several characteristics must be considered to ensure optimal performance and minimized output jitter. The following sections highlight these crystal or XO characteristics so that the correct crystal is chosen for a given project.

| Symbol           | Parameter                             | Condition Minimum Typical Maximum                        |             |   |     |     |  |  |

|------------------|---------------------------------------|----------------------------------------------------------|-------------|---|-----|-----|--|--|

| -                | Mode of Oscillation                   | -                                                        | Fundamental |   |     |     |  |  |

|                  |                                       | Using a crystal, APLL in Integer mode <sup>[1]</sup>     | 25          | - | 80  | MHz |  |  |

| _                |                                       | Using an XO, APLL in integer mode.                       | 25          | - | 150 | MHz |  |  |

| F <sub>IN</sub>  | Input Frequency                       | Using a crystal, APLL not in Integer mode <sup>[2]</sup> | 25          | - | 73  | MHz |  |  |

|                  |                                       | Using an XO, APLL not in Integer mode <sup>[2]</sup>     | 25          | - | 63  | MHz |  |  |

| f <sub>vco</sub> | Analog PLL VCO Operating<br>Frequency | - 9.7 - 10.7                                             |             |   |     |     |  |  |

#### Table 1. FemtoClock3 XIN Input Parameters

#### Choosing the Correct Crystal or XO for FemtoClock™3

| Symbol                          | Parameter                    | Condition                  | Minimum | Typical | Maximum | Unit |

|---------------------------------|------------------------------|----------------------------|---------|---------|---------|------|

| Requirem                        | ents for Crystals            |                            |         |         |         |      |

| ESR                             | Equivalent Series Resistance | $8pF \le C_L \le 10pF$     | -       | -       | 50      | Ω    |

| Co                              | Shunt Capacitance            | -                          | -       | -       | 4       | pF   |

| $C_{L}$                         | Load Capacitance             | -                          | -       | -       | 10      | pF   |

|                                 | Drive Level                  | C <sub>L</sub> = 8pF       | -       | 160     | -       | μW   |

| Drive                           |                              | C <sub>L</sub> = 10pF      | -       | 225     | -       | μW   |

| F <sub>TOL</sub> <sup>[3]</sup> | Frequency Tolerance          | -                          | -       | -       | -       | PPM  |

| Requirem                        | ents for XOs                 |                            |         |         |         |      |

| VBIAS                           | Bias Point for XIN           | Over-driving crystal input | -       | 0.6     | -       | V    |

| VIVS                            | Input Voltage Swing for XIN  | Over-driving crystal input | 0.6     | -       | 1.2     | V    |

| Vslew <sup>[4]</sup>            | Input Slew Rate for XIN      | Over-driving crystal input | 0.6     | -       | -       | V/ns |

1. APLL configured with integer\_mode =1, apll\_fb\_div\_frac = 0, and the DPLL configured with dpll\_mode = 0 (Freerun). Note that this configuration does not permit the APLL to be steered by the DPLL/DCO.

2. APLL configured with integer\_mode = 0, apll\_fb\_div\_frac  $\neq$  0.

3. These parameters are customer/application dependent. Common maximum values are  $F_{TOL} = \pm 20$  ppm,  $F_{STAB} = \pm 20$  ppm, and Aging =  $\pm 5$  ppm/10years. The customer is free to adjust these parameters to their particular requirements.

4. The slew rate is calculated by measuring at the midpoint of the rising waveform using a window of ±50mV.

#### 2. Frequency

For synthesizer applications (APLL in Integer mode), FC3 supports crystals with frequencies in the range of 25MHz to 80MHz. Crystal oscillators with frequencies in the range of 25MHz to 150MHz may be used by overdriving the crystal input. Best performance is obtained by selecting a frequency that is an integer multiple of the VCO frequency to allow all dividers to run in integer mode.

For jitter attenuator applications (APLL not in Integer mode), the maximum frequency is 73MHz when using a crystal and 63MHz when over-driving the crystal input. Best performance is obtained by selecting a crystal that is not an integer of the VCO or the output frequency to reduce the likelihood of boundary spurs. Attention should also be paid to the harmonic frequencies of the crystal and outputs to avoid boundary spurs. Boundary spurs are produced when the phase-locked loop (PLL) feedback loop fractional divider ratio is programmed to a value that is close to an integer. Boundary spurs occur because the harmonics of the phase and frequency detector (PFD) frequency mix with the VCO (or its harmonics) and the resultant intermodulation frequency components fall within the loop bandwidth. Ideally, the ratio of an output frequency or its harmonics to the crystal frequency (or the crystal frequencies harmonics) should not have a fractional component close to .0 or 0.5, with the best cases being a fractional component of 0.25 or 0.75. For a detailed explanation of boundary spurs, please see the application note: Integer Boundary Spurs in Fractional Feedback Phase-Locked Loops (PLLs).

Table 2 shows several recommended crystal frequencies for common output frequencies. The recommended crystal frequencies differ depending on whether synthesizer mode or jitter attenuator mode is being used. For 100MHz, 125MHz, 156.25 MHz, and 312.5MHz synthesizer applications, Renesas recommends that 62.5MHz be selected as the primary option, 50MHz be used as a secondary option, and 10GHz be used for a VCO frequency. For 106.25MHz, 212.5MHz, and 425MHz synthesizer applications, Renesas recommends that 68MHz be selected as the primary option, 50MHz be used as a secondary option, and 10.2GHz be used for a VCO frequency. These crystal frequency/VCO frequency combinations ensure that there is an integer relationship between the crystal frequency and the VCO, as well as between the VCO and the output frequency. These integer relationships decrease the likelihood of fractional spurs.

| Mode              | Output Frequencies (MHz)         | Recommended Crystal<br>Frequencies (MHz) | Recommended VCO<br>Frequency |

|-------------------|----------------------------------|------------------------------------------|------------------------------|

| Cumthooizor       | 100, 125, 156.25, 312.5          | 78.125, 62.5, 50                         | 10GHz                        |

| Synthesizer       | 106.25, 212.5, 425               | 68, 63.75, 50                            | 10.2GHz                      |

|                   | 100, 106.25, 125, 156.25, 212.5, | 68, 54, 49.152                           | 10GHz                        |

| Jitter Attenuator | 312.5, 425                       | 73, 60, 48                               | 10.625GHz                    |

Table 2. Recommended Output Frequency / Crystal Frequency Pairs

For jitter attenuator applications using output frequencies of 100MHz, 106.25MHz, 125MHz, 156.25MHz, 212.5MHz, 312.5MHz, and 425MHz, Renesas recommends that 54MHz be selected as the primary option with a VCO frequency of 10GHz; 73MHz can be selected as a secondary option with a VCO frequency of 10.625GHz. This ensures that the APLL is not operating in integer and reduces the likelihood of integer boundary spurs.

For jitter attenuator applications, the RMS jitter of outputs can be improved by selecting a crystal that is slightly offset from the goal crystal input frequency. A crystal's frequency will naturally vary as the temperature of the crystal changes. A crystal's frequency stability expresses the degree to which the frequency will vary over a crystal's operational temperature range. Additionally, a crystal's tolerance indicates the difference between the actual frequency of the crystal from the nominal frequency value at 25°C.

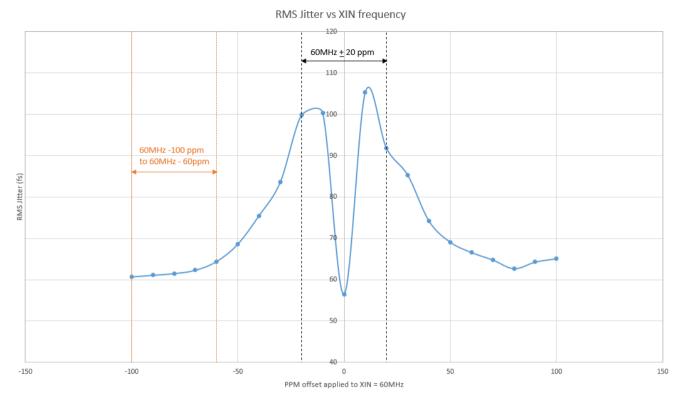

Figure 1 shows RMS jitter data for an FC3 output as the crystal input frequency varies over a range of 60MHz  $\pm$ 100ppm while the goal of the crystal input frequency programmed on the device remains at 60MHz. Frequency variations from the crystal can cause significant changes in performance. Smaller frequency offsets from the goal frequency yield larger increases in jitter. As the offsets applied to the crystal input become larger, the RMS jitter of the output decreases and eventually begins to level out. This is significant as many crystals have a stability rating <=  $\pm$ 30ppm and a tolerance rating <=  $\pm$ 20ppm, meaning that they will operate within  $\pm$ 50ppm of the nominal frequency (the region with the worst performance). Using a crystal with nominal frequency that is slightly offset from the goal frequency can improve performance by ensuring that the crystal input frequency remains in the frequency range that performs best. The RMS jitter improves with larger offsets from the goal frequency as the walking spurs caused by the crystal frequency variation can be better filtered by the DPLL loop, compared to the walking spurs created by smaller offsets.

**Example**: Using an arbitrary crystal with a frequency of 59.9952MHz (60MHz - 80ppm), with a stability of ±15ppm and a tolerance of ±5ppm, the frequency of the crystal will be somewhere in the range of 60MHz - 100ppm to 60MHz - 60ppm. This means the RMS jitter of the output will be between 60.7fs and 64.4fs based on the data in Table 3. If an arbitrary crystal with nominal frequency of 60MHz is used instead with the same stability and tolerance, the frequency range will be  $60MHz \pm 20ppm$ , and the RMS jitter of the output will be between 56.5fs and 105.3fs, based on the data in Table 3.

Figure 1: RMS Jitter Plot of a 156.25MHz FC3 Output in Jitter Attenuator Mode as the XIN Frequency Varies over 60MHz ±100ppm

| Offset of XIN from 60MHz (ppm) | RMS Jitter (fs) |

|--------------------------------|-----------------|

| -100                           | 60.7            |

| -90                            | 61.1            |

| -80                            | 61.5            |

| -70                            | 62.3            |

| -60                            | 64.4            |

| -50                            | 68.6            |

| -40                            | 75.5            |

| -30                            | 83.6            |

| -20                            | 99.8            |

| -10                            | 100.3           |

| 0                              | 56.5            |

| 10                             | 105.3           |

| 20                             | 91.8            |

| 30                             | 85.3            |

| 40                             | 74.2            |

| 50                             | 69.1            |

| 60                             | 66.6            |

| 70                             | 64.8            |

Table 3. RMS Jitter of a 156.25MHz FC3 Output in Jitter Attenuator Mode as the XIN Frequency Varies over 60MHz±100ppm

| Offset of XIN from 60MHz (ppm) | RMS Jitter (fs) |

|--------------------------------|-----------------|

| 80                             | 62.7            |

| 90                             | 64.3            |

| 100                            | 65.1            |

#### 3. Load Capacitance

For FC3, Renesas recommends to using a crystal that has a nominal load capacitance between 8pF and 10pF. FC3 does not utilize physical tuning capacitors, but instead uses an internal, adjustable load capacitance. The internal load capacitance can be adjusted in the programmed configuration file or via register writes to the device.

#### 4. Equivalent Series Resistance

Equivalent series resistance (ESR) is the effective resistance component in series with the LC model of the crystal itself. ESR is determined by the crystal size, cut, frequency and mode of vibration. An AT-cut crystal with a fundamental mode 50MHz resonance frequency in a 3225 package will have an ESR of around  $50\Omega$ , due to the size of crystal that easily fits into this package size. ESR subtracts from the negative resistance in the oscillator. A very small package with a very small crystal may have too high an ESR for the driver, making it harder to start and sustain oscillation. A large package can fit a larger crystal (at the same cut, mode, and frequency) and will have a lower ESR.

ESR is proportional to the motional resistance ( $R_M$ ) of the crystal and the shunt capacitance ( $C_O$ ). It is also inversely proportional to the load capacitance ( $C_L$ ). The ESR can be calculated as follows:

$$ESR = R_M \left(1 + \frac{C_O}{C_L}\right)^2$$

ESR is commonly expressed as a maximum value in ohms and is significant for two reasons.

- 1. The loop gain needed for an oscillator to start up and maintain oscillation is proportional to the ESR.

- 2. The drive level of an oscillator is proportional to the ESR. Therefore, if the ESR is too large, the crystal can have trouble oscillating or it can lead to a drive level which exceeds the rating which accelerates aging.

For FC3 devices, the maximum ESR value that is recommended is  $50\Omega$ .

### 5. Drive Level

Confirm that the crystal maximum specified drive level will accommodate the drive level of the FC3 product. For FC3 products, the typical drive strength is  $160\mu$ W for a load capacitance of 8pF and  $225\mu$ W for a load capacitance of 10pF. To prevent exceeding the drive level of the crystal, a series-damping resistor (R<sub>S</sub>) may be added, but this series resistor will decrease the negative resistance and loop gain will increase phase noise. It is preferred to select a crystal that can tolerate the required drive strength. Adding an R<sub>S</sub>, populated with a 0-ohm shunt, allows the use of a series resistance if a suitable crystal cannot be sourced.

Exceeding the drive level on the crystal accelerates aging. Renesas recommends measuring the power dissipated in the crystal to ensure it is below the crystal maximum specification. For more information, see the <u>Quartz Crystal Drive Level Application Note</u>.

Rs should be a small surface mounted part (example 0201 or 0402) to minimize stray capacitance.

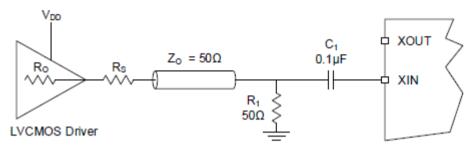

### 6. Using a Crystal Oscillator (XO) with FC3

A crystal oscillator (XO) may be used in place of a crystal with FC3. To use a XO with FC3, the crystal interface must be overdriven. When overdriving the crystal interface, the XOUT pin should be floated with no trace attached and the XIN input overdriven by an AC coupled LVCMOS driver, or, by one side of an AC coupled differential driver. The XIN pin is internally biased to 0.6V. The voltage swing on XIN should be between 0.6V peak-to-peak and 1.2V peak-to-peak; the slew rate should not be less than 0.6V/ns. The slew rate is calculated by measuring at the midpoint of the rising waveform using a window of ±50mV.

Note: The maximum allowable voltage on the XIN pin is 1.32V. Exceeding this voltage may damage the pin.

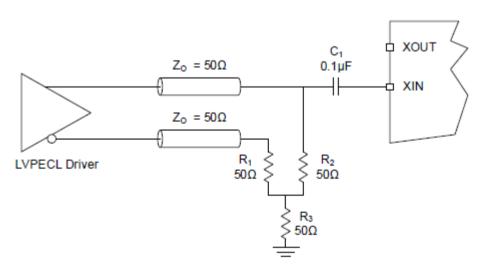

Figure 2 shows a 1.8V or 2.5V LVCMOS driver overdriving the XIN pin. For VDD = 1.8V, considering the output impedance of the driver (Ro), the values of the series resistance (Rs) and R1 should be chosen so that the voltage swing on XIN will be below 1.2V peak-to-peak. For VDD = 2.5V, the sum of the output impedance of the driver (Ro) and the series resistance (Rs) can be made higher than R1 so that the voltage swing on XIN will be below 1.2V peak-to-peak. For VDD = 2.5V, the sum of the output impedance of the driver (Ro) and the series resistance (Rs) can be made higher than R1 so that the voltage swing on XIN will be below 1.2V peak-to-peak. For VDD = 2.5V, the sum of the output impedance of the driver (Ro) and the series resistance (Rs) can be made higher than R1 so that the voltage swing on XIN will be below 1.2V peak-to-peak. Figure 3 shows one side of an LVPECL driver overdriving the XIN pin.

Figure 2. LVCMOS Driver to Crystal Input Interface

Figure 3. LVPECL Driver to Crystal Input Interface

### 7. Operating Temperature

Operating a crystal outside of its specified operating temperature range may prematurely age the crystal (increased ppm frequency change over time) or may damage the housing. A crystal operating outside of its temperature range can result in higher jitter frequency offset caused by the temperature. Crystal performance is typically not guaranteed beyond its specified temperature range. The recommended operating temperature range for FC3 devices is -40°C to 85°C.

#### 8. Frequency Tolerance

Select a manufacturing tolerance (maximum deviation from the specified resonant frequency at room temperature) and frequency shift over the operating temperature range (often called frequency stability) that is acceptable for the application. When tight frequency tolerances (< 10ppm) over the operating temperature range are a requirement, it may be necessary to use a TCXO (temperature compensated crystal oscillator) or OCXO (oven-controlled crystal oscillator) instead.

*Note*: for FC3 products, the crystal or crystal oscillator at XIN is the jitter reference. The preference is to use a crystal for low jitter instead of a generated clock signal.

## 9. Aging

Confirm that the crystal aging tolerance (ppm per year) meets the application requirement. Exceeding the drive level on the crystal, as well as shock, vibration and operating the crystal outside of its specified temperature range, accelerates aging. If the crystal will experience shock or vibration in its application, consider an oven-controlled SC-cut crystal which is more tolerant of vibration.

# 10. Recommended Crystals (XTAL)

Table 4 provides a list of acceptable crystals for applications using a FC3 device.

| Manufacturer | Туре | Part Number             | Product<br>Size (mm) | Frequency<br>(MHz) | ESR<br>(Ω) | CL<br>(pF) | Typical<br>Drive Level<br>(µW) | Freq.<br>Tolerance<br>(ppm) | Freq.<br>Stability<br>(ppm) | Aging<br>(ppm/year<br>at 25°C) | Temp.<br>Range (ºC) |

|--------------|------|-------------------------|----------------------|--------------------|------------|------------|--------------------------------|-----------------------------|-----------------------------|--------------------------------|---------------------|

| NDK          | XTAL | NX2016SA-50M            | 2.0 × 1.6            | 50                 | 50         | 8          | 200                            | ±15                         | ±15                         | ±3                             | -40 to 125          |

| KYOCERA      | XTAL | CX2016SA50000           | 3.2 × 2.5            | 50                 | 50         | 8          | 200                            | ±15                         | ±50                         | ±1                             | -40 to 125          |

| ECS          | XTAL | ECS-500-8-37-<br>AGN-TR | 2.0 × 1.6            | 50                 | 50         | 8          | 100                            | ±25                         | ±30                         | ±5                             | -40 to 85           |

| TXC          | XTAL | 7M54072002              | 3.2 × 2.5            | 54                 | 50         | 8          | 100                            | ±12                         | ±15                         | ±3                             | -40 to 85           |

| KYOCERA      | XTAL | CX3225SB54000           | 3.2 × 2.5            | 54                 | 50         | 8          | 100                            | ±10                         | ±15                         | ±1                             | -30 to 85           |

| TXC          | XTAL | 8Y60072005              | 2.0 × 1.6            | 60                 | 40         | 8          | 100                            | -5 to 12                    | -15 to 12                   | ±1                             | -40 to 85           |

| NDK          | XTAL | EXS00A-<br>CS15287      | 2.0 × 1.6            | 60                 | 30         | 9          | 200                            | ±25                         | -                           | -                              | -40 to 85           |

| TXC          | XTAL | 8Y62572002              | 2.0 × 1.6            | 62.5               | 40         | 8          | 100                            | -5 to 12                    | -15 to 12                   | ±1                             | -40 to 85           |

| TXC          | XTAL | 8Z62572001              | 2.5 × 2.0            | 62.5               | 40         | 8          | 100                            | -5 to 12                    | -15 to 12                   | ±1                             | -40 to 85           |

| NDK          | XTAL | EXS00A-<br>CS15295      | 2.0 × 1.6            | 62.5               | 35         | 9          | 200                            | ±30                         | -                           | -                              | -40 to 85           |

| TXC          | XTAL | 8Y68072001              | 2.0 × 1.6            | 68                 | 40         | 8          | 100                            | -5 to 12                    | -15 to 12                   | ±1                             | -40 to 85           |

| NDK          | XTAL | EXS00A-<br>CS15306      | 2.0 × 1.6            | 68                 | 50         | 9          | 200                            | ±30                         | -                           | -                              | -40 to 85           |

| TXC          | XTAL | 8Y73072002              | 2.0 × 1.6            | 73                 | 40         | 8          | 100                            | -5 to 12                    | -15 to 12                   | ±1                             | -40 to 85           |

| NDK          | XTAL | EXS00A-<br>CS15308      | 2.0 × 1.6            | 73                 | 50         | 9          | 200                            | ±30                         | -                           | -                              | -40 to 85           |

| TXC          | XTAL | 8Y78172001              | 2.0 × 1.6            | 78.125             | 40         | 8          | 100                            | -5 to 12                    | -15 to 12                   | ±1                             | -40 to 105          |

Table 4. Recommended Crystals for FC3 Applications

| Manufacturer | Туре | Part Number        | Product<br>Size (mm) | Frequency<br>(MHz) | ESR<br>(Ω) | CL<br>(pF) | Typical<br>Drive Level<br>(µW) | Freq.<br>Tolerance<br>(ppm) | Freq.<br>Stability<br>(ppm) | Aging<br>(ppm/year<br>at 25°C) | Temp.<br>Range (ºC) |

|--------------|------|--------------------|----------------------|--------------------|------------|------------|--------------------------------|-----------------------------|-----------------------------|--------------------------------|---------------------|

| TXC          | XTAL | 8Y78172002         | 2.0 × 1.6            | 78.125             | 40         | 8          | 100                            | -5 to 12                    | -15 to 12                   | ±1                             | -40 to 85           |

| NDK          | XTAL | EXS00A-<br>CS15310 | 2.0 × 1.6            | 78.125             | 50         | 9          | 200                            | ±30                         | -                           | -                              | -40 to 85           |

# **11. Revision History**

| Revision | Date         | Description      |

|----------|--------------|------------------|

| 1.00     | Nov 17, 2023 | Initial release. |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.