# ClockMatrix Combo Mode Filter

This application note explains how to configure the Combo Mode Filter when using the Combo bus of ClockMatrix devices.

# Contents

| 1. | Introd | Introduction                     |   |  |  |  |  |

|----|--------|----------------------------------|---|--|--|--|--|

| 2. | Filter | Configuration Steps with Example | 2 |  |  |  |  |

|    | 2.1    | Step 1                           | 2 |  |  |  |  |

|    | 2.2    | Step 2                           | 4 |  |  |  |  |

|    | 2.3    | Step 3                           | 5 |  |  |  |  |

| 3. | Revis  | sion History                     | 6 |  |  |  |  |

# 1. Introduction

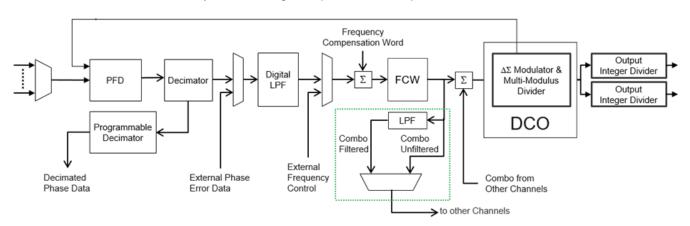

The ClockMatrix architecture allows the option for the Master Combo channel to filter the frequency information before it is transferred to the Slave Combo channel. Figure 1 shows a filter between the Combo Mode master and the Combo Mode slave. This low pass filter provides a lower bandwidth than what is used in the regular loop filter, without affecting the DPLL's output clock. The filter feature was included in the ClockMatrix device with the anticipation that the ITU standards committee would recommend such a filter in the future to filter syncE phase transients. However, enhanced syncE has a tighter specification for phase transients.

The filtered output provides an additional low-pass filter that can filter some of the Combo Master SyncE noise before the frequency information is passed to the Combo Slave. For example, if the combo filter is set to attenuate down to 1100mHz before it passes the frequency information to the Slave Time (PTP) PLL Channel, then it will eliminate noise from 1100mHz on the output of the master combo SyncE PLL. The combo low pass filter is in addition to the regular DPLL loop filter.

# 2. Filter Configuration Steps with Example

# 2.1 Step 1

The input to the combo filter type can be selected by setting the

DPLL\_CTRL\_{x}.DPLL\_COMBO\_MASTER\_CFG bit, where "x" is the DPLL channel. It can be selected between the integrator value or the sum of the proportional and the integrator values. The integrator value is the frequency offset (holdover value), as it is integrated over time. The sum of the proportional and the integrator value is the loop filter output value of the DPLL. An excerpt from the *8A3xxx Family Programming Guide* is shown in Figure 2. By default, the "integrator value only" is selected, with a bandwidth setting of 0, which means the filter is bypassed.

### DPLL\_CTRL\_0.DPLL\_COMBO\_MASTER\_CFG

DPLL combo master configuration.

### Table 274: DPLL\_CTRL\_0.DPLL\_COMBO\_MASTER\_CFG Bit Field Locations and Descriptions

| Offset<br>Address |    | D                                                | PLL_CTRL_0.D | PLL_COMBO_M | ASTER_CFG Bi | t Field Location | s  |    |

|-------------------|----|--------------------------------------------------|--------------|-------------|--------------|------------------|----|----|

| (Hex)             | D7 | D6                                               | D5           | D4          | D3           | D2               | D1 | D0 |

| 03Ah              |    | RESERVED[7:2] FILTER_IN_ HOLD_EN[0]<br>SELECT[1] |              |             |              |                  |    |    |

| DPLL_CTRL_0.DPLL_COMBO_MASTER_CFG Bit Field Descriptions |                           |   |                                                                                                                   |  |  |  |

|----------------------------------------------------------|---------------------------|---|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit Field Name Field Type Default Value                  |                           |   | Description                                                                                                       |  |  |  |

| RESERVED N/A -                                           |                           | - | This field must not be modified from the read value                                                               |  |  |  |

| FILTER_IN_SELECT[1]                                      | FILTER_IN_SELECT[1] R/W 0 |   | Select filtered DCO value as combo source.<br>0 = integrator value only<br>1 = sum of proportional and integrator |  |  |  |

Figure 2. Register Description for the Combo Master Configuration

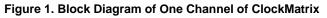

Figure 3 is the DPLL configuration window in Timing Commander, showing Channel 4 as the Master SyncE Channel.

Figure 3. Channel 4 as the Combo Master Showing the Location of the Combo Master Settings in the GUI

The SyncE loop filter bandwidth is 10Hz (G.8262 EEC Option 1) in this example. The combo filter must be smaller than the Master DPLL loop filter bandwidth. In this example, the combo filter bandwidth is 1100mHz.

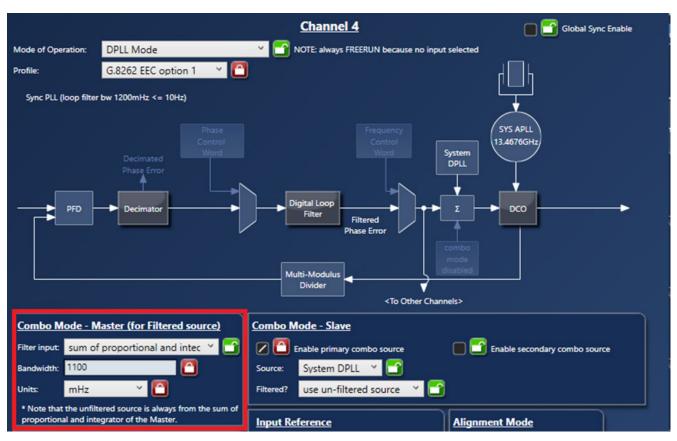

In the GUI, select the input to the filter as shown in Figure 4.

Figure 4. Filter Input Combo Master Settings as Shown in the GUI

## 2.2 Step 2

Set the Filter bandwidth using the DPLL\_CTRL\_{x}.DPLL\_COMBO\_MASTER\_BW and the DPLL\_CTRL\_{x}.BW\_UNIT settings as shown in Figure 5.

### Table 273: DPLL\_CTRL\_0.DPLL\_COMBO\_MASTER\_BW Bit Field Locations and Descriptions

| Offset<br>Address | DPLL_CTRL_0.DPLL_COMBO_MASTER_BW Bit Field Locations |                           |    |    |    |    |    |    |  |

|-------------------|------------------------------------------------------|---------------------------|----|----|----|----|----|----|--|

| (Hex)             | D7                                                   | D6                        | D5 | D4 | D3 | D2 | D1 | D0 |  |

| 038h              |                                                      | DPLL_COMBO_MASTER_BW[7:0] |    |    |    |    |    |    |  |

| 039h              | BW_UNIT[15:14] DPLL_COMBO_MASTER_BW[13:8]            |                           |    |    |    |    |    |    |  |

|                                | DPLL_CTRL_0.DPLL_COMBO_MASTER_BW Bit Field Descriptions |   |                                                                         |  |  |  |  |

|--------------------------------|---------------------------------------------------------|---|-------------------------------------------------------------------------|--|--|--|--|

| Bit Field Name                 | Bit Field Name Field Type Default Value                 |   | Description                                                             |  |  |  |  |

| BW_UNIT[15:14]                 | R/W                                                     | 0 | Combo filter bandwidth unit.<br>0 = uHz<br>1 = mHz<br>2 = Hz<br>3 = kHz |  |  |  |  |

| DPLL_COMBO_MASTER_<br>BW[13:0] | R/W                                                     | 0 | Unsigned 14-bit Combo filter bandwidth value.                           |  |  |  |  |

### Figure 5. Register Description for the Combo Master Filter Bandwidth

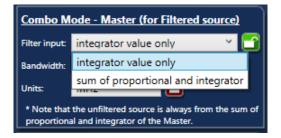

These are the settings in the GUI as shown in Figure 6.

| Combo Mode - Master (for Filtered source)                                                              |                                   |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|--|

| Filter input:                                                                                          | sum of proportional and intec 🍸 🎦 |  |  |  |  |  |  |

| Bandwidth:                                                                                             | 1100                              |  |  |  |  |  |  |

| Units:                                                                                                 | mHz 🖌 🎦                           |  |  |  |  |  |  |

| * Note that the unfiltered source is always from the sum of proportional and integrator of the Master. |                                   |  |  |  |  |  |  |

Figure 6. Filter Bandwidth Combo Master Settings as shown in the GUI

# 2.3 Step 3

The Combo mode slave primary source configuration can be set through the  $DPLL_{x}.DPLL_COMBO_SLAVE_CFG_{x}$  register, where "x" is the DPLL channel as shown in Figure 7.

## DPLL\_0.DPLL\_COMBO\_SLAVE\_CFG\_0

Combo mode slave primary source configuration.

### Table 215: DPLL\_0.DPLL\_COMBO\_SLAVE\_CFG\_0 Bit Field Locations and Descriptions

| Offset<br>Address |       |          |                         |                                            |    |           |              |    |

|-------------------|-------|----------|-------------------------|--------------------------------------------|----|-----------|--------------|----|

| (Hex)             | D7    | D6       | D5                      | D4                                         | D3 | D2        | D1           | D0 |

| 032h              | RESER | /ED[7:6] | PRI_COMBO<br>_SRC_EN[5] | PRI_COMBO<br>_SRC_FILTE<br>RED_CNFG[<br>4] |    | PRI_COMBO | _SRC_ID[3:0] |    |

|                                         | DPLL_0.DPLL_COMBO_SLAVE_CFG_0 Bit Field Descriptions |               |                                                                               |  |  |  |  |

|-----------------------------------------|------------------------------------------------------|---------------|-------------------------------------------------------------------------------|--|--|--|--|

| Bit Field Name Field Type Default Value |                                                      | Default Value | Description                                                                   |  |  |  |  |

| RESERVED                                | N/A                                                  | -             | This field must not be modified from the read value                           |  |  |  |  |

| PRI_COMBO_SRC_EN[5]                     | R/W                                                  | 0             | Enable this source.<br>0 = disabled<br>1 = enabled                            |  |  |  |  |

| PRI_COMBO_SRC_FILTE<br>RED_CNFG[4]      | R/W                                                  | 0             | Use filtered source.<br>0 = use un-filtered source<br>1 = use filtered source |  |  |  |  |

| PRI_COMBO_SRC_ID[3:0<br>]               | R/W                                                  | 0             | Primary combo source DPLL index.                                              |  |  |  |  |

### Figure 7. Register Description for the Combo Slave Configuration

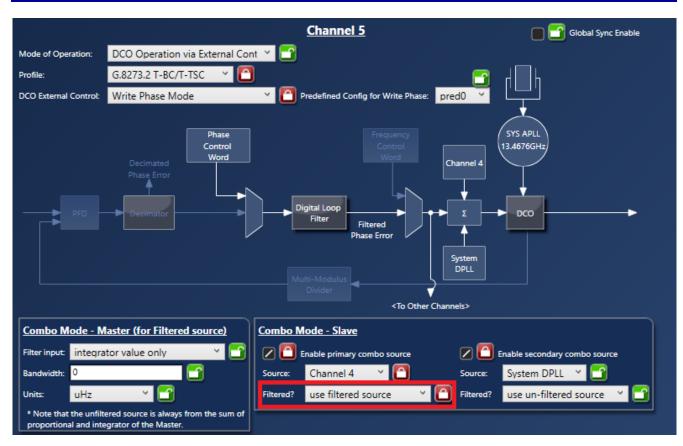

Figure 8 shows the DPLL configuration window in Timing Commander, with Channel 5 displayed as the Slave Time (PTP) PLL Channel. Notice how the filtered source is used, which means the 1100mHz combo filter is used as defined in Channel 4 above. If an unfiltered source is used, the combo filter is bypassed.

## ClockMatrix Combo Mode Filter Application Note

Figure 8. Filter Selection Combo Slave Settings as Shown in the GUI

# 3. Revision History

| Revision | Date         | Description      |

|----------|--------------|------------------|

| 1.0      | Jul 21, 2021 | Initial release. |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.