#### ISL73141SEH

#### Radiation Hardened 14-Bit 1MSPS SAR ADC

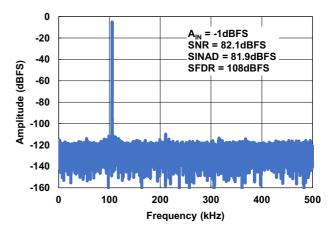

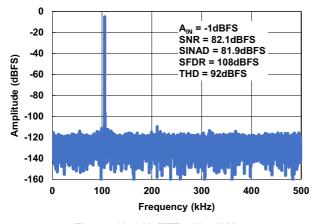

The <u>ISL73141SEH</u> is a radiation hardened high precision 14-bit, 1Msps SAR Analog-to-Digital Converter (ADC) that features SNR of 82.1dBFS and dissipates only 60mW when operating from a 5V supply. With a 3.3V supply, the ISL73141SEH operates at 750ksps with a power consumption of 28mW.

The product features 1Msps throughput with no data latency and features excellent linearity and dynamic accuracy. The ISL73141SEH provides a high-speed SPI-compatible serial interface that supports logic ranging from 2.2V to 3.6V using a separate digital I/O supply pin.

The ISL73141SEH provides a separate power-down pin that reduces power dissipation to <50µW. The analog input signal range is determined by an external reference.

The ISL73141SEH operates across the military temperature range from -55°C to +125°C and is available in a 14 Ld hermetically sealed Ceramic Dual Flat-Pack (CDFP) package.

### **Applications**

- · Precision signal processing in satellite payloads

- · Satellite telemetry systems

- · Satellite propulsion and orbit control

- · Attitude control of satellites

- · High-end industrial

- · Down-hole drilling

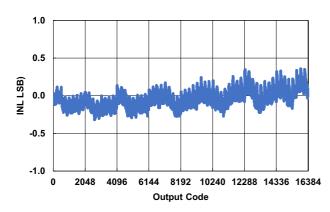

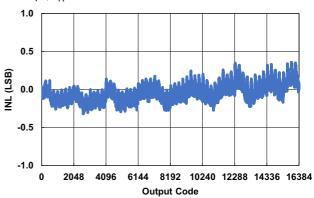

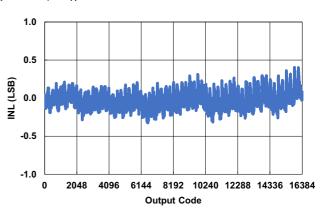

Figure 1. INL vs Output Code

#### **Features**

- 1Msps throughput rate with no data latency

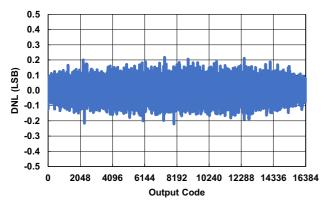

- Excellent linearity: ±0.2 LSB DNL, ±0.5 LSB INL

- · No missing codes

- Low noise: 82.1dB SNR

- 3.3V or 5V AV<sub>CC</sub> supply options

- · Separate 2.2V to 3.6V digital I/O supply

- · Low power: 60mW at 1Msps

- $\circ$  AV<sub>CC</sub> = 5V, DV<sub>CC</sub> = 2.5V

- Power-down mode with <50µW power consumption

- High speed SPI-compatible serial I/O

- · Full military temperature range operation

- $\circ$  T<sub>A</sub> = -55°C to +125°C

- · Radiation acceptance testing

- LDR (0.01rad(Si)/s): 75krad(Si)

- · SEE hardness (see SEE report for details)

- $\circ$  No SEB/SEL LET<sub>TH</sub> (AV<sub>CC</sub> = 6.3V): 86MeV•cm<sup>2</sup>/mg

- No SEFIs at LET 86MeV•cm<sup>2</sup>/mg

- Qualified to Renesas Rad Hard QML-V Equivalent Screening and QCI flow (R34TB0001EU)

- All screening and QCI is in accordance with MIL-PRF- 38535L Class-V

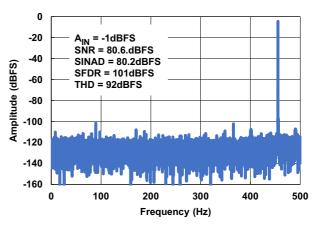

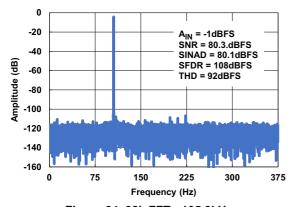

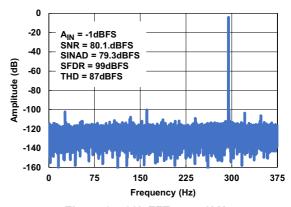

Figure 2. 32k FFT - 105.3kHz

#### ISL73141SEH

## **Contents**

| 1.   | Overview 3                          |

|------|-------------------------------------|

| 1.1  | Typical Application Schematic       |

| 1.2  | Functional Block Diagram            |

| 1.3  | Ordering Information                |

| 2.   | Pin In formation                    |

| 2.1  | Pin Assignments                     |

| 2.2  | Pin Descriptions                    |

| 3.   | Specifications                      |

| 3.1  | Absolute Maximum Ratings            |

| 3.2  | Thermal Information                 |

| 3.3  | Recommended Operating Conditions    |

| 3.4  | Electrical Specifications           |

| 3.5  | Timing Specifications               |

| 3.6  | Timing Diagrams                     |

| 4.   | Typical Performance Curves          |

| 4.1  | 5.0V Curves                         |

| 4.2  | 3.3V Curves                         |

| 5.   | Applications Information            |

| 5.1  | Overview                            |

| 5.2  | Serial Interface and BUSY           |

| 5.3  | Operational Phases and Timing       |

| 5.4  | Convert Start ( <del>CS</del> ) Pin |

| 5.5  | Power Down (PD) Pin                 |

| 5.6  | Reference Input (REF) Pin           |

| 5.7  | ISL73141 Transfer Function          |

| 5.8  | Power Supply Sequencing             |

| 5.9  | Analog Input (AIN) Pin              |

| 5.10 | Package                             |

| 6.   | Die and Assembly Characteristics    |

| 7.   | Revision History                    |

| 8.   | Package Outline Drawing             |

ISL73141SEH 1. Overview

### 1. Overview

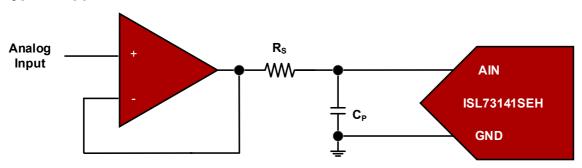

## 1.1 Typical Application Schematic

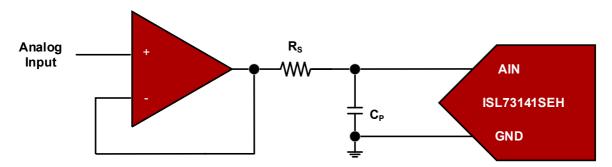

Figure 3. Typical Application Example Circuit

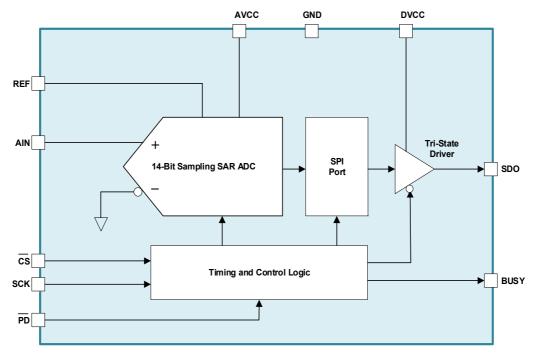

## 1.2 Functional Block Diagram

Figure 4. ISL73141SEH Block Diagram

ISL73141SEH 2. Pin In formation

### 1.3 Ordering Information

| Part Number (Note 1)       | AV <sub>CC</sub> Supply<br>Voltage | Radiation Hardness<br>(Total Ionizing Dose)   | Package Description (RoHS Compliant) | Package<br>Drawing | Carrier<br>Type | Temp<br>Range |  |

|----------------------------|------------------------------------|-----------------------------------------------|--------------------------------------|--------------------|-----------------|---------------|--|

| ISL73141SEHMFN             | 3.3V                               | LDR to 75krad(Si)                             | ` '                                  | K14.A              | Tray            | -55 to +125°C |  |

| ISL73141SEHMF7             | 5V                                 |                                               | Device (QML-V Level Screening)       |                    |                 |               |  |

| ISL73141SEHFN/PROTO Note 2 | 3.3V                               | N/A                                           | 14 Ld CDFP Packaged                  |                    |                 |               |  |

| ISL73141SEHF7/PROTO Note 2 | 5V                                 |                                               | Device                               |                    |                 |               |  |

| ISL73141SEHFNEV1Z Note 3   | Single IC Evalu                    | Single IC Evaluation Board for ISL73141SEHMFN |                                      |                    |                 |               |  |

| ISL73141SEHF7EV1Z Note 3   | Single IC Evalu                    | uation Board for ISL731                       | 41SEHMF7                             |                    |                 |               |  |

#### Notes:

- 1. These Pb-free Hermetic packaged products employ 100% Au plate e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

- 2. The /PROTO is not rated or certified for Total Ionizing Dose (TID) or Single Event Effect (SEE) immunity. These parts are intended for engineering evaluation purposes only. The /PROTO parts meet the electrical limits and conditions across the temperature range specified in this datasheet. These part types do not come with a Certificate of Conformance.

- 3. Evaluation board uses the /PROTO parts and /PROTO parts are not rated or certified for Total Ionizing Dose (TID) or Single Event Effect (SEE) immunity

### 2. Pin In formation

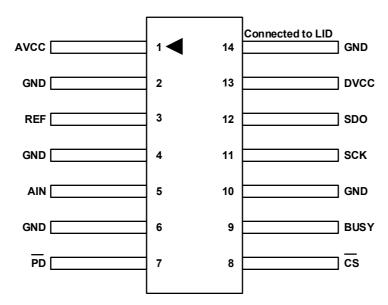

### 2.1 Pin Assignments

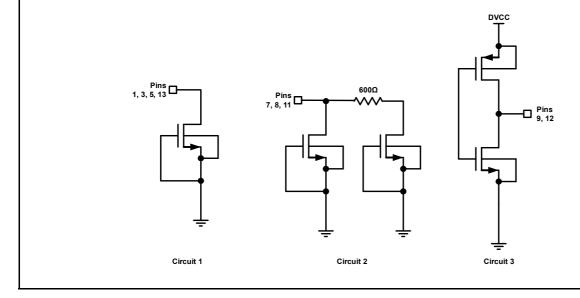

Note: The ESD triangular mark is indicative of Pin #1. It is a part of the device marking and is placed on the lid in the quadrant where Pin #1 is located.

Top View

### 2.2 Pin Descriptions

| Pin Number      | Pin Name | ESD<br>Circuit | Description                                                                                                                                                      |

|-----------------|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | AVCC     | 1              | Analog supply. The supply range is 3V to 3.6V (ISL73141SEHMFN) or 4.5V to 5.5V (ISL73141SEHMF7). Bypass this pin to GND with a 10µF ceramic capacitor.           |

| 2, 4, 6, 10, 14 | GND      | -              | Analog and digital supply ground. Connect these pins directly to the PCB GND plane. Pin 14 (GND pin) is electrically connected to the package seal ring and lid. |

ISL73141SEH 2. Pin In formation

| Pin Number | Pin Name | ESD<br>Circuit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3          | REF      | 1              | Reference input. The input range of REF is 1.95V to AV $_{\rm CC}$ for the ISL73141SEHMFN and 3.9V to 4.2V for the ISL73141SEHMF7. The voltage at the REF pin (V $_{\rm REF}$ ) defines the input range of the analog input as 0V to V $_{\rm REF}$ . Bypass REF to GND with a low ESR 10 $\mu$ F ceramic capacitor.                                                                                                                                                                                                                                  |

| 5          | AIN      | 1              | Analog input. AIN supports an input voltage range of 0V to V <sub>REF</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8          | CS       | 2              | Convert Start Low input. A falling edge on this input starts a new conversion. The conversion is timed using an internal oscillator. The device automatically powers down following the conversion process. The logic state of the $\overline{CS}$ pin controls the state of the SDO pin. A logic high on the $\overline{CS}$ pin disables the SDO pin driver and the SDO pin impedance is Hi-Z. A logic low on the $\overline{CS}$ pin enables the SDO driver (unless $\overline{PD}$ is low) and allows data to be read out following a conversion. |

| 7          | PD       | 2              | Power-down low input. When this pin is brought low the ADC enters power-down mode. If this occurs during a conversion, the conversion is halted and the SDO pin is placed in Hi-Z. Logic levels are determined by DV <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                  |

| 9          | BUSY     | 3              | Busy output. A logic high indicates a conversion is in progress. The BUSY indicator returns low following the completion of a conversion. Logic levels are determined by DV <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                           |

| 11         | SCK      | 2              | Serial data clock input. When $\overline{CS}$ is low and the BUSY indicator is low, the conversion result is shifted out on SDO on the rising edges of SCK, Most Significant Bit (MSB) first to Least Significant Bit (LSB) last. Logic levels are determined by DV <sub>CC</sub> . SCK should be held low when it is not being asserted.                                                                                                                                                                                                             |

| 12         | SDO      | 3              | Serial data output. The current conversion result is serially shifted out on this pin on the rising edges of SCK, MSB first to LSB last. The data stream is composed of 14 bits of conversion data followed by trailing zeros. Logic Levels are determined by DV <sub>CC</sub> .                                                                                                                                                                                                                                                                      |

| 13         | DVCC     | 1              | Digital I/O supply. Voltage range on this pin is 2.2V to 3.6V. DV $_{CC}$ is nominally set to the same supply voltage as the host interface (2.5V or 3.3V). Bypass DVCC to GND with 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                            |

| LID        | N/A      | N/A            | Package Lid is internally connected to GND through Pin 14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## 3. Specifications

## 3.1 Absolute Maximum Ratings

| Parameter                                             | Min  | Max                    | Unit |

|-------------------------------------------------------|------|------------------------|------|

| Supply Voltage (AV <sub>CC</sub> , DV <sub>CC</sub> ) | -0.3 | 6.4                    | V    |

| Supply Voltage (AV <sub>CC</sub> ) (Note 5)           | -0.3 | 6.3                    | V    |

| Supply Voltage (DV <sub>CC</sub> ) ( <u>Note 5</u> )  | -0.3 | 4.6                    | V    |

| A <sub>IN</sub> , REF (Note 4)                        | -0.3 | AV <sub>CC</sub> + 0.3 | V    |

| A <sub>IN</sub> , REF ( <u>Notes 4, 5</u> )           | -0.3 | 5.1                    | V    |

| Digital Input Voltage (PD, CS, SCK)                   | -0.3 | DV <sub>CC</sub> + 0.3 | V    |

| Digital Output Voltage (BUSY, SDO)                    | -0.3 | DV <sub>CC</sub> + 0.3 | V    |

| ESD Rating                                            | V    | /alue                  | Unit |

| Human Body Model (Tested per MIL-STD-883 TM3015.7)    |      | 2.5                    | kV   |

| Charged Device Model (Tested per JS-002-2014)         |      | 600                    | V    |

**CAUTION:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

- 4. AIN voltage should not exceed REF voltage by more than 300mV or device damage can occur.

- 5. Tested in a heavy ion environment at LET = 86MeV•cm<sup>2</sup>/mg at 125°C.

#### 3.2 Thermal Information

| Thermal Resistance (Typical)    | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|---------------------------------|------------------------|------------------------|

| CDFP Package K14.A (Notes 6, 7) | 34                     | 6                      |

#### Notes:

- 6.  $\theta_{JA}$  is measured in free air with the component on high-effective thermal conductivity test board with direct attach features. See <u>TB379</u>.

- 7. For  $\theta_{\text{JC}},$  the case temperature location is the center of the package underside.

| Parameter                    | Min | Max  | Unit |

|------------------------------|-----|------|------|

| Maximum Junction Temperature | -   | +150 | °C   |

| Storage Temperature Range    | -65 | +150 | °C   |

## 3.3 Recommended Operating Conditions

| Parameter                                                  | Min  | Max              | Unit |

|------------------------------------------------------------|------|------------------|------|

| Temperature                                                | -55  | +125             | °C   |

| Analog Supply Voltage, A <sub>VCC</sub> (ISL73141SEHMFN)   | 3.0  | 3.6              | V    |

| Analog Supply Voltage, A <sub>VCC</sub> (ISL73141SEHMF7)   | 4.5  | 5.5              | V    |

| Digital Supply Voltage, D <sub>VCC</sub>                   | 2.2  | 3.6              | V    |

| Reference Input Voltage, V <sub>REF</sub> (ISL73141SEHMFN) | 1.95 | 3.6              | V    |

| Reference Input Voltage, V <sub>REF</sub> (ISL73141SEHMF7) | 3.9  | 4.2              | V    |

| Analog Input Voltage, A <sub>IN</sub>                      | 0    | V <sub>REF</sub> | V    |

## 3.4 Electrical Specifications

## 3.4.1 ISL73141SEHMF7 - 5V Operation

$AV_{CC} = 5.0V; DV_{CC} = 2.5V, REF = 4.096V, GND = 0V, f_{SAMP} = 1 \\ Msps, A_{IN} = -1 \\ dBFS; T_A = -55 \\ ^{\circ}C \text{ to } +125 \\ ^{\circ}C, unless \text{ otherwise noted.}$

| Parameter                             | Symbol               | Test Conditions                                         | Min<br>( <u>Notes 9, 10</u> ) | Typ<br>(Note 8) | Max<br>( <u>Notes 9, 10</u> ) | Unit               |

|---------------------------------------|----------------------|---------------------------------------------------------|-------------------------------|-----------------|-------------------------------|--------------------|

| Converter Characteristics             |                      |                                                         |                               |                 |                               |                    |

| Resolution                            |                      |                                                         | 14                            |                 |                               | bits               |

| No Missing Codes                      |                      |                                                         | 14                            |                 |                               | bits               |

| Transition Noise                      |                      | RMS noise, 14-bit LSB                                   |                               | 0.3             |                               | LSB <sub>RMS</sub> |

| Integral Non-Linearity                | INL                  | Measured with full scale input signal.                  | -1.0                          | ±0.4            | 1.0                           | LSB                |

| Differential Non-Linearity            | DNL                  | Measured with full scale input signal.                  | -0.5                          | ±0.2            | 0.5                           | LSB                |

| Zero Scale Error                      | VOFF                 | Measured with input grounded.                           | -5                            | 0               | 5                             | LSB                |

| Zero Scale Error Drift                | VOFFD                | Measured with input grounded.                           |                               | ±0.006          |                               | LSB/°C             |

| Full Scale Error                      | FSE                  | Measured with input connected to VREF                   | -7                            | ±1              | 7                             | LSB                |

| Full Scale Error Drift                | FSED                 | Measured with input connected to VREF                   |                               | ±0.004          |                               | LSB/°C             |

| Dynamic Accuracy                      |                      |                                                         | l                             |                 |                               | 1                  |

| Signal to Noise Ratio                 | SNR                  | F <sub>IN</sub> = 105kHz                                | 80                            | 82.1            |                               | dBFS               |

| Signal to Noise + Distortion<br>Ratio | SINAD                | F <sub>IN</sub> = 105kHz                                | 79                            | 81.9            |                               | dBFS               |

| Effective Number of Bits              | ENOB                 | F <sub>IN</sub> = 105kHz                                | 12.5                          | 13.3            |                               | bits               |

| Total Harmonic Distortion             | THD                  | F <sub>IN</sub> = 105kHz, first five harmonics          | 85                            | 92              |                               | dBFS               |

| Spurious Free Dynamic Range           | SFDR                 | F <sub>IN</sub> = 105kHz, first five harmonics excluded | 90                            | 108             |                               | dBFS               |

| Input Bandwidth G                     |                      | Source impedance = 25Ω, -3dB point                      |                               | 50              |                               | MHz                |

| Aperture Delay                        | t <sub>AD</sub>      | CS falling edge to sample edge                          |                               | 2.5             |                               | ns                 |

| Aperture Jitter                       | t <sub>AJITTER</sub> |                                                         |                               | 1               |                               | ps <sub>RMS</sub>  |

| Analog Input Characteristics (        | A <sub>IN</sub> )    |                                                         | l                             |                 |                               | 1                  |

| Input Voltage Range, A <sub>IN</sub>  | A <sub>IN</sub>      | Recommended operating condition                         | 0                             |                 | $V_{REF}$                     | V                  |

| Absolute Input Range, A <sub>IN</sub> |                      |                                                         | -0.1                          |                 | AV <sub>CC</sub> + 0.1        | V                  |

| Input Leakage Current                 | IA <sub>IN</sub>     |                                                         | -1                            |                 | 1                             | μΑ                 |

| Input Capacitance                     |                      | Sample Mode                                             |                               | 15              |                               | pF                 |

|                                       |                      | Hold Mode                                               |                               | 3               |                               | pF                 |

| Reference Input Characteristic        | s (REF)              |                                                         | I                             | I.              |                               | I                  |

| REF Input Voltage Range               | $V_{REF}$            |                                                         | 3.9                           |                 | 4.2                           | V                  |

| REF Input Current                     | I <sub>REF</sub>     |                                                         |                               | 135             | 200                           | μΑ                 |

| Power Supply Characteristics          | (AVCC, D\            | /cc)                                                    |                               |                 |                               | 1                  |

| Analog Supply Voltage                 | AV <sub>CC</sub>     |                                                         | 4.5                           |                 | 5.5                           | V                  |

| Analog Supply Current - Active        | I <sub>AVCC</sub>    | Active, f <sub>SAMP</sub> = 1Msps                       |                               | 12              | 14.5                          | mA                 |

| Analog Supply Current - Static        | I <sub>Static</sub>  | CS held High                                            |                               | 4.3             | 7                             | mA                 |

| Analog Supply Current - Sleep         | I <sub>SLAVCC</sub>  | PD held Low                                             |                               | 4.8             | 12                            | μA                 |

| Digital Supply Voltage                | DV <sub>CC</sub>     |                                                         | 2.2                           |                 | 3.6                           | V                  |

| Digital Supply Current - Active       | I <sub>DVCC</sub>    | f <sub>SCK</sub> = 50MHz                                |                               | 72              | 90                            | μA                 |

| Digital Supply Current - Static       | I <sub>STDVCC</sub>  | CS held High                                            |                               | 26.4            | 35                            | μA                 |

| Digital Supply Current - Sleep        | I <sub>SLDVCC</sub>  | PD held Low                                             |                               | 6               | 8                             | μA                 |

$AV_{CC} = 5.0V; DV_{CC} = 2.5V, REF = 4.096V, GND = 0V, f_{SAMP} = 1 \\ Msps, A_{IN} = -1 \\ dBFS; T_A = -55 \\ ^{\circ}C \text{ to } +125 \\ ^{\circ}C, \text{ unless otherwise noted.}$

| Parameter                      | Symbol              | Test Conditions                                    | Min<br>( <u>Notes 9, 10</u> ) | Typ<br>(Note 8) | Max<br>( <u>Notes 9, 10</u> ) | Unit |

|--------------------------------|---------------------|----------------------------------------------------|-------------------------------|-----------------|-------------------------------|------|

| $P_{D}$                        | P <sub>ACTIVE</sub> | Sample rate = 1Msps                                |                               | 60              | 72.8                          | mW   |

|                                | P <sub>STATIC</sub> | CS held High                                       |                               | 21.6            | 35.1                          | mW   |

|                                | P <sub>SLEEP</sub>  | PD held Low                                        |                               | 39              | 80                            | μW   |

| Digital Inputs and Outputs (PD | , cs, sck,          | BUSY, SDO)                                         |                               |                 |                               |      |

| High Level Input               | $V_{IH}$            |                                                    | 0.8*DV <sub>CC</sub>          |                 |                               | V    |

| Low Level Input                | V <sub>IL</sub>     |                                                    |                               |                 | 0.2*DV <sub>CC</sub>          | V    |

| Input Current (CS, SCK)        | I <sub>IN</sub>     | V <sub>IN</sub> = 0V to DV <sub>CC</sub>           | -1                            |                 | 1                             | μA   |

| Input Capacitance              | C <sub>IN</sub>     |                                                    |                               | 5               |                               | pF   |

| High Level Output              | V <sub>OH</sub>     | DV <sub>CC</sub> - Output, I <sub>O</sub> = -500μA | DV <sub>CC</sub> - 0.2        |                 |                               | V    |

| Low Level Output               | V <sub>OL</sub>     | I <sub>O</sub> = 500μA                             |                               |                 | 0.2                           | V    |

| Output Source Current          | I <sub>SRC</sub>    | V <sub>OUT</sub> = 0V to DV <sub>CC</sub>          |                               | -10             |                               | mA   |

| Output Sink Current            | I <sub>SNK</sub>    | V <sub>OUT</sub> = 0V to DV <sub>CC</sub>          |                               | 10              |                               | mA   |

| Hi-Z Output Leakage Current    | I <sub>OZ</sub>     | V <sub>OUT</sub> = 0V to DV <sub>CC</sub>          | -1                            |                 | 1                             | μA   |

| PD Input Resistance            | R <sub>INPDL</sub>  | Internal pull-up resistance to D <sub>VCC</sub>    | 400                           | 500             | 600                           | kΩ   |

# 3.4.2 ISL73141SEHMFN - 3.3V Operation

$AV_{CC} = 3.3V; \ DV_{CC} = 2.5V, \ REF = 3.0V, \ GND = 0V, \ f_{SAMP} = 750ksps, \ A_{IN} = -1dBFS; \ T_A = -55^{\circ}C \ to \ +125^{\circ}C, \ unless \ otherwise \ noted.$

| Parameter                          | Symbol               | Test Conditions                                         | Min<br>( <u>Notes 9,</u> <u>10</u> ) | Typ<br>( <u>Note 8</u> ) | Max<br>( <u>Notes 9</u> , <u>10</u> ) | Unit               |

|------------------------------------|----------------------|---------------------------------------------------------|--------------------------------------|--------------------------|---------------------------------------|--------------------|

| Converter Characteristics          | •                    |                                                         |                                      | •                        |                                       | •                  |

| Resolution                         |                      |                                                         | 14                                   |                          |                                       | bits               |

| No Missing Codes                   |                      |                                                         | 14                                   |                          |                                       | bits               |

| Transition Noise                   |                      | RMS noise, 14-bit LSB                                   |                                      | 0.4                      |                                       | LSB <sub>RMS</sub> |

| Integral Non-Linearity             | INL                  | Measured with full scale input signal                   | -1.5                                 | ±0.5                     | 1.5                                   | LSB                |

| Differential Non-Linearity         | DNL                  | Measured with full scale input signal                   | -0.5                                 | ±0.25                    | 0.5                                   | LSB                |

| Zero Scale Error                   | VOFF                 | Measured with input grounded                            | -5                                   | 0                        | 5                                     | LSB                |

| Zero Scale Error Drift,            | VOFFD                | Measured with input grounded                            |                                      | ±0.01                    |                                       | LSB/°C             |

| Full Scale Error                   | FSE                  | Measured with input connected to VREF                   | -7                                   | ±1                       | 7                                     | LSB                |

| Full Scale Error Drift             | FSED                 | Measured with input connected to VREF                   | -                                    | ±0.02                    | -                                     | LSB/°C             |

| Dynamic Accuracy                   |                      |                                                         |                                      | I .                      |                                       | I                  |

| Signal to Noise Ratio              | SNR                  | F <sub>IN</sub> = 105kHz                                | 77                                   | 80.3                     |                                       | dB                 |

| Signal to Noise + Distortion Ratio | SINAD                | F <sub>IN</sub> = 105kHz                                | 76                                   | 80.1                     |                                       | dB                 |

| Effective Number of Bits           | ENOB                 | F <sub>IN</sub> = 105kHz                                | 12.3                                 | 12.8                     |                                       | bits               |

| Total Harmonic Distortion          | THD                  | F <sub>IN</sub> = 105kHz, first five harmonics          | 85                                   | 92                       |                                       | dB                 |

| Spurious Free Dynamic Range        | SFDR                 | F <sub>IN</sub> = 105kHz, first five harmonics excluded | 90                                   | 108                      |                                       | dB                 |

| Input Bandwidth                    |                      | Source impedance = $25\Omega$ , -3dB point              |                                      | 50                       |                                       | MHz                |

| Aperture Delay                     | t <sub>AD</sub>      | CS falling edge to sample edge                          |                                      | 4                        |                                       | ns                 |

| Aperture Jitter                    | t <sub>AJITTER</sub> |                                                         |                                      | 1                        |                                       | ps <sub>RMS</sub>  |

$AV_{CC}$  = 3.3V;  $DV_{CC}$  = 2.5V, REF = 3.0V, GND = 0V,  $f_{SAMP}$  = 750ksps,  $A_{IN}$  = -1dBFS;  $T_A$  = -55°C to +125°C, unless otherwise noted. (Cont.)

| Parameter                             | Symbol                              | Test Conditions                                 | Min<br>( <u>Notes 9, 10</u> ) | Typ<br>( <u>Note 8</u> ) | Max<br>( <u>Notes 9, 10</u> ) | Unit |

|---------------------------------------|-------------------------------------|-------------------------------------------------|-------------------------------|--------------------------|-------------------------------|------|

| Analog Input Characteristics (A       | IN)                                 |                                                 |                               |                          |                               |      |

| Input Voltage Range, A <sub>IN</sub>  | A <sub>IN</sub>                     | Recommended operating condition                 | 0                             |                          | $V_{REF}$                     | V    |

| Absolute Input Range, A <sub>IN</sub> |                                     |                                                 | -0.1                          |                          | AV <sub>CC</sub> + 0.1        | V    |

| Input Leakage Current                 | IA <sub>IN</sub>                    |                                                 | -1                            |                          | 1                             | μΑ   |

| Input Capacitance                     |                                     | Sample Mode                                     |                               | 15                       |                               | pF   |

|                                       |                                     | Hold Mode                                       |                               | 3                        |                               | pF   |

| Reference Input Characteristics       | (REF)                               |                                                 | •                             |                          |                               |      |

| REF Input Voltage Range               | V <sub>REF</sub>                    |                                                 | 1.95                          |                          | AV <sub>CC</sub>              | V    |

| REF Input Current                     | I <sub>REF</sub>                    |                                                 |                               | 82                       | 150                           | μA   |

| Power Supply Characteristics (A       | AV <sub>CC</sub> , DV <sub>CC</sub> | <u>,</u> )                                      | •                             | •                        |                               |      |

| Analog Supply Voltage                 | AV <sub>CC</sub>                    |                                                 | 3                             |                          | 3.6                           | V    |

| Analog Supply Current - Active        | I <sub>AVCC</sub>                   | Active, f <sub>SAMP</sub> = 750ksps             |                               | 8.5                      | 10.5                          | mA   |

| Analog Supply Current - Static        | I <sub>Static</sub>                 | CS held High                                    |                               | 3.7                      | 6.5                           | mA   |

| Analog Supply Current - Sleep         | I <sub>SLAVCC</sub>                 | PD held Low                                     |                               | 4.6                      | 10                            | μA   |

| Digital Supply Voltage                | DV <sub>CC</sub>                    |                                                 | 2.2                           |                          | 3.6                           | V    |

| Digital Supply Current - Active       | I <sub>DVCC</sub>                   | f <sub>SCK</sub> = 33MHz, 10pF load             |                               | 70                       | 90                            | μΑ   |

| Digital Supply Current - Static       | I <sub>STDVCC</sub>                 | CS held High                                    |                               | 27                       | 35                            | μΑ   |

| Digital Supply Current - Sleep        | I <sub>SLDVCC</sub>                 | PD held Low                                     |                               | 6                        | 8                             | μA   |

| P <sub>D</sub>                        | P <sub>ACTIVE</sub>                 | Sample rate = 750ksps                           |                               | 28                       | 33.9                          | mW   |

|                                       | P <sub>STATIC</sub>                 | CS held High                                    |                               | 12.3                     | 21.6                          | mW   |

|                                       | P <sub>SLEEP</sub>                  | PD held Low                                     |                               | 30.2                     | 53                            | μW   |

| Digital Inputs and Outputs (PD,       | CS, SCK, E                          | BUSY, SDO)                                      | •                             | •                        |                               |      |

| High Level Input                      | V <sub>IH</sub>                     |                                                 | 0.8*DV <sub>CC</sub>          |                          |                               | V    |

| Low Level Input                       | V <sub>IL</sub>                     |                                                 |                               |                          | 0.2*DV <sub>CC</sub>          | V    |

| Input Current (CS, SCK)               | I <sub>IN</sub>                     | V <sub>IN</sub> = 0V to DV <sub>CC</sub>        | -1                            |                          | 1                             | μA   |

| Input Capacitance                     | C <sub>IN</sub>                     |                                                 |                               | 5                        |                               | pF   |

| High Level Output                     | V <sub>OH</sub>                     | $DV_{CC}$ - Output, $I_{O}$ = -500 $\mu$ A      | DV <sub>CC</sub> - 0.2        |                          |                               | V    |

| Low Level Output                      | V <sub>OL</sub>                     | I <sub>O</sub> = 500μA                          |                               |                          | 0.2                           | V    |

| Output Source Current                 | I <sub>SRC</sub>                    | V <sub>OUT</sub> = 0V to DV <sub>CC</sub>       |                               | -10                      |                               | mA   |

| Output Sink Current                   | I <sub>SNK</sub>                    | V <sub>OUT</sub> = 0V to DV <sub>CC</sub>       |                               | 10                       |                               | mA   |

| Hi-Z Output Leakage Current           | I <sub>OZ</sub>                     | V <sub>OUT</sub> = 0V to DV <sub>CC</sub>       | -1                            |                          | 1                             | μA   |

| PD Input Resistance                   | R <sub>INPDL</sub>                  | Internal pull-up resistance to D <sub>VCC</sub> | 400                           | 500                      | 600                           | kΩ   |

#### Notes:

- 8. Typical values shown are not guaranteed. Values derived from +25°C median data.

- 9. Parameters with MIN and/or MAX limits are 100% tested at -55°C, +25°C, and +125°C, unless otherwise specified.

- 10. Limits valid post radiation test with LDR [0.01rad(Si)/s] at 75krad(Si).

### 3.4.3 ISL73141SEHMF7 - 5.0V Operation Burn-In Deltas

$AV_{CC} = 5.0V; \ DV_{CC} = 2.5V, \ REF = 4.096V, \ GND = 0V, \ f_{SAMP} = 1000ksps, A_{IN} = -1dBFS; \ T_A = +25^{\circ}C; \ unless \ otherwise \ noted.$

| Parameter                | Symbol | Test Conditions                       | Min   | Max  | Unit |

|--------------------------|--------|---------------------------------------|-------|------|------|

| Integral Non-Linearity   | INL    | Measured with full scale input signal | -0.35 | 0.35 | LSB  |

| Signal to Noise Ratio    | SNR    | F <sub>IN</sub> = 105kHz              | -1    | 1    | dBFS |

| Effective Number of Bits | ENOB   | F <sub>IN</sub> = 105kHz              | -0.2  | 0.2  | bits |

### 3.4.4 ISL73141SEHMFN - 3.3V Operation Burn-In Deltas

$AV_{CC} = 3.3V$ ;  $DV_{CC} = 2.5V$ , REF = 3.0V, GND = 0V,  $f_{SAMP} = 750ksps$ ,  $A_{IN} = -1dBFS$ ;  $T_A = +25^{\circ}C$ ;unless otherwise noted.

| Parameter                | Symbol | Test Conditions                       | Min  | Max | Unit |

|--------------------------|--------|---------------------------------------|------|-----|------|

| Integral Non-Linearity   | INL    | Measured with full scale input signal | -0.5 | 0.5 | LSB  |

| Signal to Noise Ratio    | SNR    | F <sub>IN</sub> = 105kHz              | -1   | 1   | dBFS |

| Effective Number of Bits | ENOB   | F <sub>IN</sub> = 105kHz              | -0.2 | 0.2 | bits |

## 3.5 Timing Specifications

# 3.5.1 5V Operation

$AV_{CC}$  = 4.5V to 5.5V;  $DV_{CC}$  = 2.2V to 3.6V, REF = 4.096V, GND = 0V,  $f_{SAMP}$  = 1Msps,  $A_{IN}$  = -1dBFS;  $T_A$  = -55°C to +125°C, unless otherwise noted

| Parameter                          | Symbol                  | Test Conditions                        | Min<br>( <u>Notes 9, 10</u> ) | Typ<br>( <u>Note 8</u> ) | Max<br>( <u>Notes 9, 10</u> ) | Unit |

|------------------------------------|-------------------------|----------------------------------------|-------------------------------|--------------------------|-------------------------------|------|

| Timing Characteristics             | !                       |                                        | •                             | •                        |                               |      |

| Maximum Sampling Frequency         | f <sub>SAMP</sub>       |                                        |                               |                          | 1                             | MHz  |

| Conversion Time                    | t <sub>CONV</sub>       | BUSY Output High Time                  |                               | 595                      | 665                           | ns   |

| CS High Time                       | t <sub>CSH</sub>        |                                        | 40                            |                          |                               | ns   |

| SCK Held Low to CS↓                | t <sub>QUIET</sub>      |                                        | 40                            |                          |                               | ns   |

| CS Falling Edge to BUSY↑           | t <sub>BUSYLH</sub>     | C <sub>L</sub> = 10pF                  |                               | 17                       | 25                            | ns   |

| SCK Period                         | t <sub>SCK</sub>        |                                        | 20                            |                          |                               | ns   |

| SCK High Time                      | t <sub>SCKH</sub>       |                                        | 8                             |                          |                               | ns   |

| SCK Low Time                       | t <sub>SCKL</sub>       |                                        | 8                             |                          |                               | ns   |

| SDO Data Valid Delay from BUSY↓    | t <sub>DBUSYLSDOV</sub> | C <sub>L</sub> = 10pF                  |                               | -2.6                     | 0                             | ns   |

| SDO Data Valid Delay from SCK↑     | t <sub>DSCKSDOV</sub>   | C <sub>L</sub> = 10pF                  |                               |                          | 18.5                          | ns   |

| SDO Data Valid Hold Time from SCK↑ | t <sub>HSDOV</sub>      | C <sub>L</sub> = 10pF                  | 8                             | 13                       |                               | ns   |

| SDO Bus Acquisition Time from CS↓  | t <sub>DCSLSDOL</sub>   | C <sub>L</sub> = 10pF                  |                               | 11                       | 20                            | ns   |

| SDO Bus Relinquish Time after CS↑  | t <sub>DCSHSDOZ</sub>   | C <sub>L</sub> = 10pF                  |                               | 12                       | 20                            | ns   |

| Wake-Up time from Power-Down Mode  | t <sub>WAKE</sub>       | Time to wait after PD↑ to first sample |                               | 20                       |                               | μs   |

####

$AV_{CC}$  = 3.0V to 3.6V;  $DV_{CC}$  = 2.2V to 3.6V, REF = 3.0V, GND = 0V,  $f_{SAMP}$  = 750ksps,  $A_{IN}$  = -1dBFS;  $T_A$  = -55°C to +125°C, unless otherwise noted.

| Parameter                                     | Symbol                  | Test Conditions                        | Min<br>( <u>Notes 9, 10</u> ) | Typ<br>( <u>Note 8</u> ) | Max<br>( <u>Notes 9, 10</u> ) | Unit |

|-----------------------------------------------|-------------------------|----------------------------------------|-------------------------------|--------------------------|-------------------------------|------|

| Timing Characteristics                        |                         |                                        |                               |                          |                               |      |

| Maximum Sampling Frequency                    | f <sub>SAMP</sub>       |                                        |                               |                          | 750                           | kHz  |

| Conversion Time                               | t <sub>CONV</sub>       | BUSY Output High Time                  |                               | 760                      | 850                           | ns   |

| CS High Time                                  | t <sub>CSH</sub>        |                                        | 50                            |                          |                               | ns   |

| SCK Held Low to CS↓                           | t <sub>QUIET</sub>      |                                        | 50                            |                          |                               | ns   |

| CS Falling Edge to BUSY↑                      | t <sub>BUSYLH</sub>     | C <sub>L</sub> = 10pF                  |                               | 21                       | 40                            | ns   |

| SCK Period                                    | t <sub>SCK</sub>        |                                        | 30                            |                          |                               | ns   |

| SCK High Time                                 | t <sub>SCKH</sub>       |                                        | 12                            |                          |                               | ns   |

| SCK Low Time                                  | t <sub>SCKL</sub>       |                                        | 12                            |                          |                               | ns   |

| SDO Data Valid Delay from BUSY↓               | t <sub>DBUSYLSDOV</sub> | C <sub>L</sub> = 10pF                  |                               | -5                       | 0                             | ns   |

| SDO Data Valid Delay from SCK↑                | t <sub>DSCKSDOV</sub>   | C <sub>L</sub> = 10pF                  |                               |                          | 25                            | ns   |

| SDO Data Valid Hold Time from SCK↑            | t <sub>HSDOV</sub>      | C <sub>L</sub> = 10pF                  | 8                             | 16                       |                               | ns   |

| SDO Bus Acquisition Time from CS↓             | t <sub>DCSLSDOL</sub>   | C <sub>L</sub> = 10pF                  |                               | 12                       | 30                            | ns   |

| SDO Bus Relinquish Time after <del>CS</del> ↑ | t <sub>DCSHSDOZ</sub>   | C <sub>L</sub> = 10pF                  |                               | 14                       | 30                            | ns   |

| Wake-Up time from Power-Down<br>Mode          | t <sub>WAKE</sub>       | Time to wait after PD↑ to first sample |                               | 20                       |                               | μs   |

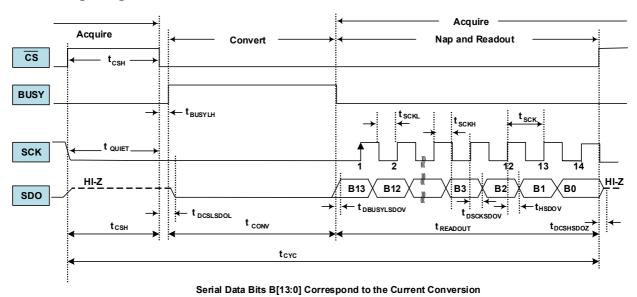

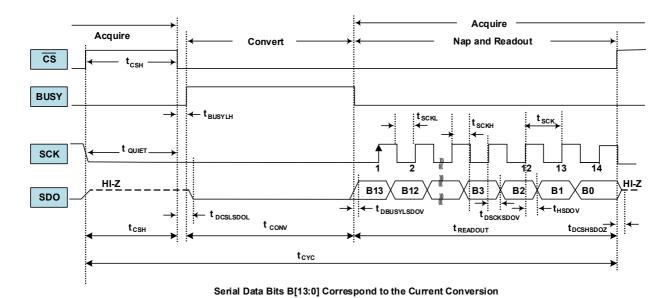

## 3.6 Timing Diagrams

Figure 5. ISL73141SEH Operational Timing Diagram

## 4. Typical Performance Curves

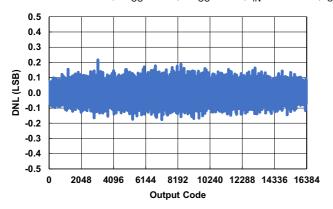

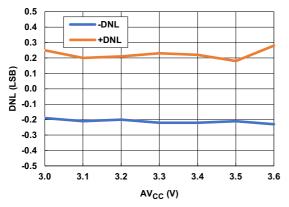

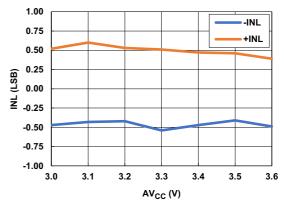

### 4.1 5.0V Curves

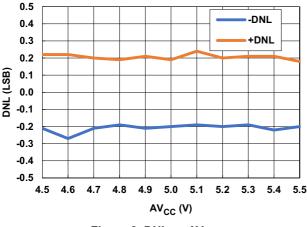

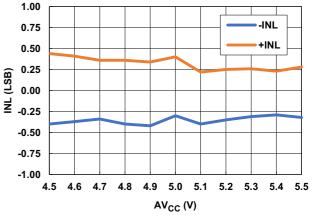

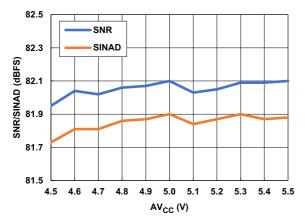

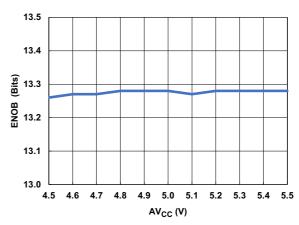

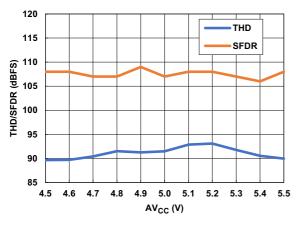

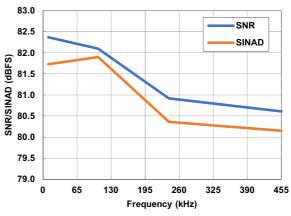

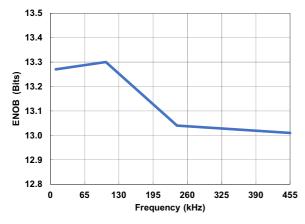

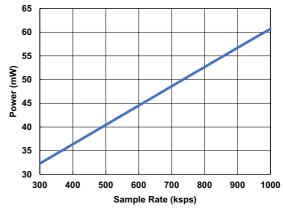

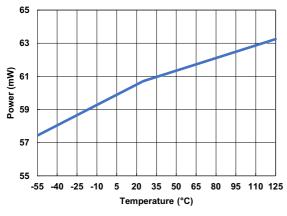

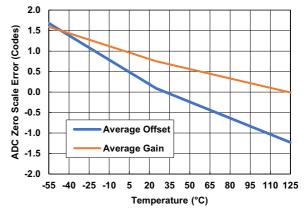

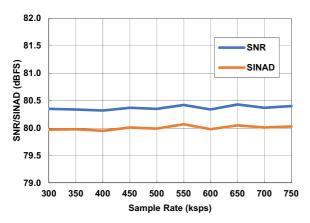

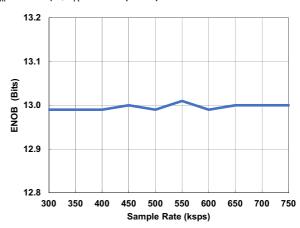

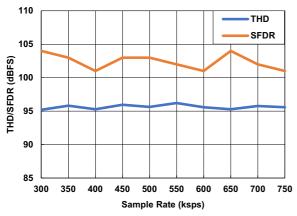

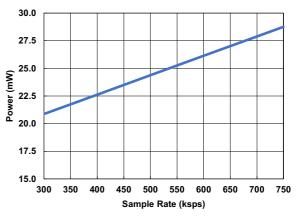

Unless otherwise noted, AV $_{CC}$  = 5.0V; DV $_{CC}$  = 2.5V;  $f_{IN}$  = 105.3kHz;  $f_{SAMP}$  = 1Msps;  $T_A$  = +25°C

Figure 6. Differential Non-Linearity (DNL)

Figure 7. Integral Non-Linearity (INL)

Figure 8. DNL vs AV<sub>CC</sub>

Figure 9. INL vs AV<sub>CC</sub>

Figure 10. 32k FFT - 105.3kHz

Figure 11. 32k FFT - 455.3kHz

Unless otherwise noted, AV $_{CC}$  = 5.0V; DV $_{CC}$  = 2.5V;  $f_{IN}$  = 105.3kHz;  $f_{SAMP}$  = 1Msps;  $T_A$  = +25°C (Cont.)

Figure 12. SNR and SINAD vs  $AV_{CC}$

Figure 13. ENOB vs AVCC

Figure 14. THD and SFDR vs AV<sub>CC</sub>

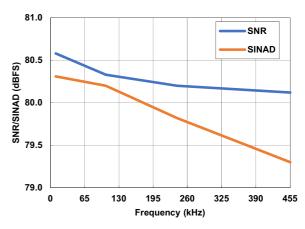

Figure 15. SNR and SINAD vs Frequency

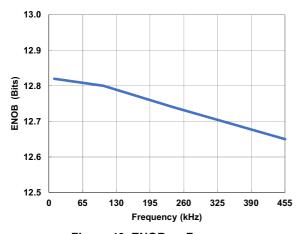

Figure 16. ENOB vs Frequency

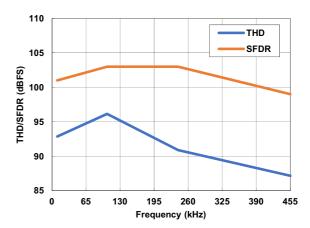

Figure 17. THD and SFDR vs Frequency

Unless otherwise noted, AV $_{CC}$  = 5.0V; DV $_{CC}$  = 2.5V;  $f_{IN}$  = 105.3kHz;  $f_{SAMP}$  = 1Msps;  $T_A$  = +25°C (Cont.)

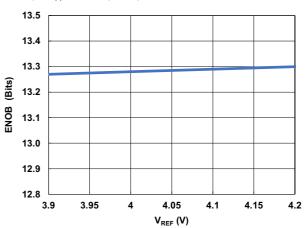

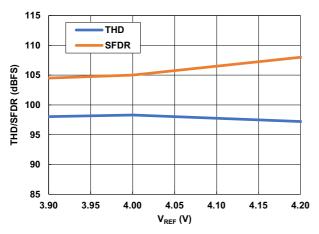

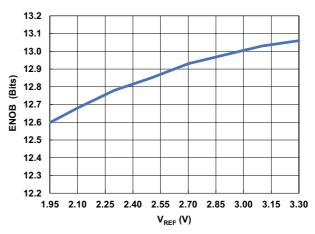

Figure 18. SNR and SINAD vs  $V_{\text{REF}}$

Figure 19. ENOB vs  $V_{\text{REF}}$

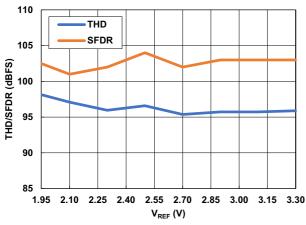

Figure 20. THD and SFDR vs  $\mathbf{V}_{\text{REF}}$

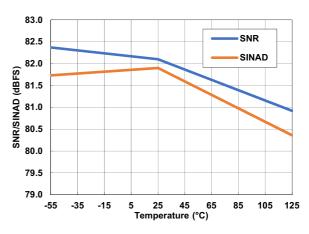

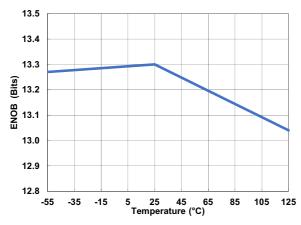

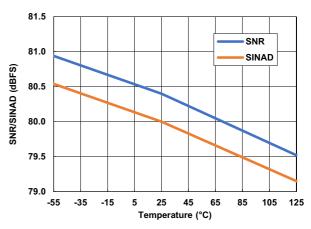

Figure 21. SNR and SINAD vs Temperature

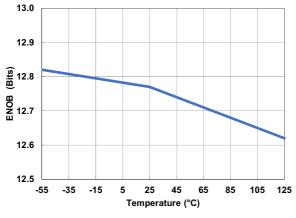

Figure 22. ENOB vs Temperature

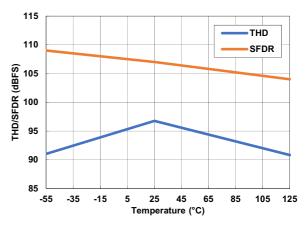

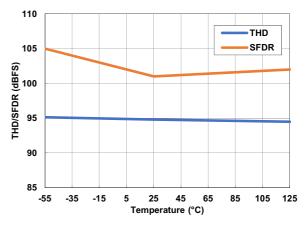

Figure 23. THD and SFDR vs Temperature

Unless otherwise noted, AV $_{CC}$  = 5.0V; DV $_{CC}$  = 2.5V;  $f_{IN}$  = 105.3kHz;  $f_{SAMP}$  = 1Msps;  $T_A$  = +25°C (Cont.)

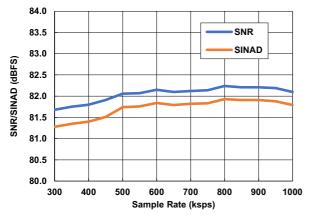

Figure 24. SNR and SINAD vs Sample Rate

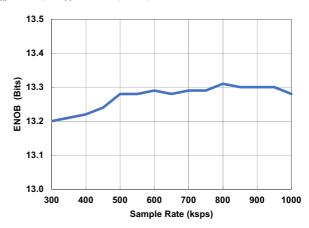

Figure 25. ENOB vs Sample Rate

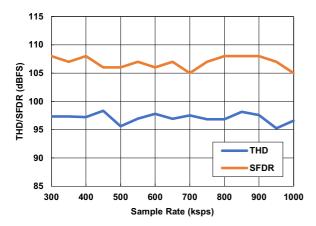

Figure 26. THD and SFDR vs Sample Rate

Figure 27. Power vs Sample Rate

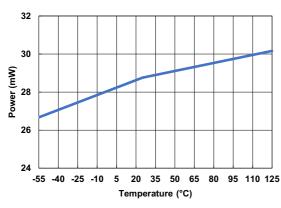

Figure 28. Power vs Temperature

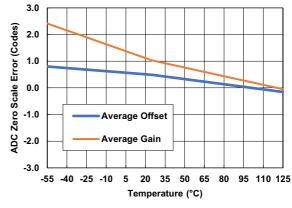

Figure 29. Zero and Full Scale Error vs Temperature

### 4.2 3.3V Curves

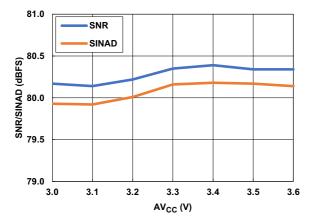

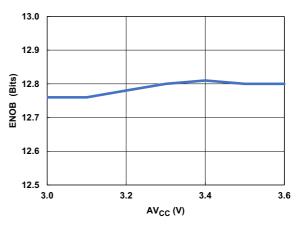

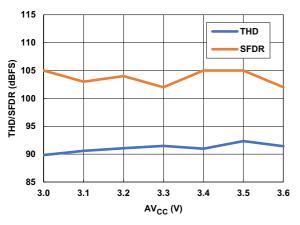

Unless otherwise noted, AV<sub>CC</sub> = 3.3V; DV<sub>CC</sub> = 2.5V;  $f_{IN}$  = 105.3kHz;  $f_{SAMP}$  = 750ksps;  $T_A$  = +25°C

Figure 30. Differential Non-Linearity (DNL)

Figure 31. Integral Non-Linearity (INL)

Figure 32. DNL vs  $AV_{CC}$

Figure 33. INL vs  $AV_{CC}$

Figure 34. 32k FFT - 105.3kHz

Figure 35. 32k FFT - 455.3kHz

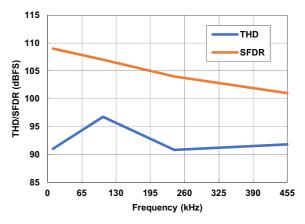

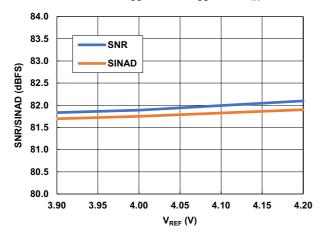

Unless otherwise noted, AV $_{CC}$  = 3.3V; DV $_{CC}$  = 2.5V;  $f_{IN}$  = 105.3kHz;  $f_{SAMP}$  = 750ksps;  $T_A$  = +25°C (Cont.)

Figure 36. SNR and SINAD vs  $AV_{CC}$

Figure 37. ENOB vs AV<sub>CC</sub>

Figure 38. THD and SFDR vs  $AV_{CC}$

Figure 39. SNR and SINAD vs Frequency

Figure 40. ENOB vs Frequency

Figure 41. THD and SFDR vs Frequency

Unless otherwise noted, AV $_{CC}$  = 3.3V; DV $_{CC}$  = 2.5V;  $f_{IN}$  = 105.3kHz;  $f_{SAMP}$  = 750ksps;  $T_A$  = +25°C (Cont.)

Figure 42. SNR and SINAD vs  $V_{REF}$

Figure 43. ENOB vs V<sub>REF</sub>

Figure 44. THD and SFDR vs  $V_{REF}$

Figure 45. SNR and SINAD vs Temperature

Figure 46. ENOB vs Temperature

Figure 47. THD and SFDR vs Temperature

Unless otherwise noted, AV<sub>CC</sub> = 3.3V; DV<sub>CC</sub> = 2.5V;  $f_{IN}$  = 105.3kHz;  $f_{SAMP}$  = 750ksps;  $T_A$  = +25°C (Cont.)

Figure 48. SNR and SINAD vs Sample Rate

Figure 49. ENOB vs Sample Rate

Figure 50. THD and SFDR vs Sample Rate

Figure 51. Power vs Sample Rate

Figure 52. Power vs Temperature

Figure 53. Zero and Full Scale Error vs Temperature

### 5. Applications Information

#### 5.1 Overview

The ISL73141SEH is a radiation hardened, high precision, low noise, 14-bit Successive Approximation Register (SAR) ADC. The device operates from an analog supply voltage range of 3V to 3.6V or 4.5V to 5.5V, a digital supply voltage range of 2.2V to 3.6V, and has a dedicated reference input (REF). The ISL73141SEH supports sample rates up to 1Msps with an analog supply voltage range of 4.5V to 5.5V. It also supports sample rates up to 750ksps with an analog supply voltage range of 3V to 3.6V, which allows you to optimize your system based on the range of the analog signal being sampled. The ISL73141SEH samples at a rate of 1Msps and achieves excellent dynamic performance (82.1dB SNR, 100dB THD) and linearity (INL  $\pm$ 1LSB, DNL  $\pm$ 0.5 LSB) while still maintaining a low power consumption of 60mW from a 5V supply. Additionally, the device offers a Sleep mode that minimizes power consumption to <50 $\mu$ W during idle operation.

The IS73141SEH offers a high-speed serial interface with an independent digital supply ( $DV_{CC}$ ) range of 2.2V to 3.6V, making it ideal to interface to 2.5V or 3.3V systems. The conversion data is output on the SDO pin with no latency. The ISL73141SEH supports up to a 50MHz serial data read clock on the SCK input.

The single-ended analog input voltage ( $A_{IN}$ ) is sampled on the falling edge of  $\overline{CS}$ . The input range of the ISL73141SEH is determined by the REF pin voltage to GND. The ISL73141SEH supports excellent THD and SFDR sampling input signal frequencies up to and beyond Nyquist (such as  $f_{IN} \ge 500 \text{kHz}$  with  $f_{SAMP} = 1 \text{Msps}$ ). The ISL73141SEH uses the external reference input (REF) as the positive reference and the GND pin of the device as the negative reference.

#### 5.2 Serial Interface and BUSY

The ISL73141SEH uses a 3-wire serial port interface to communicate with other devices such as microcontrollers and other external circuitry. A falling edge on  $\overline{\text{CS}}$  initiates conversion in the ISL73141SEH. Renesas requires holding  $\overline{\text{CS}}$  high for at least 40ns before initiating the conversion. The conversion is timed by an internal oscillator. During the conversion process, the BUSY signal is asserted high. When the conversion is complete, BUSY is de-asserted. Renesas requires holding SCK low during  $t_{\text{CONV}}$ . When BUSY is de-asserted, the MSB is immediately available on the SDO pin. Each subsequent rising edge of SCK serially outputs data on SDO from the MSB-1 to the LSB. The input logic level of  $\overline{\text{CS}}$  and SCK is determined by the DV<sub>CC</sub> supply voltage that operates across a range of 2.2V up to 3.6V. Similarly, the output voltage level of BUSY is also determined by the DV<sub>CC</sub> supply voltage.

#### 5.3 Operational Phases and Timing

The conversion result MSB is available for serial readout at the SDO pin immediately following a completed conversion. The BUSY indicator flag is high during conversion, and transitions low following completion of the conversion. When the BUSY indicator flag goes LOW after a conversion, the MSB of the conversion result (B13) is immediately available at the SDO pin. Subsequent rising edges of SCK shift bits MSB-1 (B12) through the LSB (B0) to SDO for readout. The output voltage level of SDO is determined by the DV<sub>CC</sub> supply voltage which operates across a range of 2.2V up to 3.6V. Figure 54 shows the basic timing of the ISL73141SEH in a conversion cycle.

Figure 54. ISL73141SEH Timing Diagram

The following are the three phases of operation in the ISL73141SEH that are shown in Figure 54.

- · Acquisition

- Conversion

- Readout

The Acquisition phase begins immediately following the completion of the conversion. During CS high, the SDO pin is held in high impedance (high-Z). The falling edge of  $\overline{\text{CS}}$  defines the sampling instant of the ISL73141SEH, initiates a conversion, and also enables the SDO output to a low state. The conversion cycle is internally timed through an internal oscillator and takes an ensured maximum time of  $t_{\text{CONV}}$  to complete. Following conversion, several internal blocks are powered down to reduce power consumption. This phase of power-down is referred to as NAP mode. The ISL73141SEH stays in NAP mode until the next rising edge of  $\overline{\text{CS}}$  where the ISL73141SEH is fully powered up.

The following is an example of timing calculation in an application operating the ISL73141SEHMF7 at 1Msps. When deriving timing it is imperative to use the appropriate maximum and minimum specifications. The  $\overline{\text{CS}}$  input must be held high for 40ns ( $t_{\text{CSH}}$ ). The time between the falling edge of  $\overline{\text{CS}}$  and the rising edge of BUSY is a maximum of 30ns ( $t_{\text{BUSYLH}}$ ). The conversion time ( $t_{\text{CONV}}$ ) is a maximum of 660ns. To clock the data out of the ADC there must be 14 rising edges of SCK ( $t_{\text{READOUT}}$ ). The 14th SCK falling edge must be coincident with the rising edge of  $\overline{\text{CS}}$  for the subsequent sample. Using the maximum SCK frequency of 50MHz yields:

$$13 \times 20$$

ns +  $10$ ns =  $270$ ns

**Note:** The 14th SCK edge is coincident with the rising edge of  $\overline{\text{CS}}$  so there is only a 1/2 period for the 14th SCK. To calculate and validate the sample timing use <u>Equation 1</u>:

(EQ. 1)

$$t_{CYC} = t_{CSH} + t_{BUSYLH} + t_{CONV} + t_{READOUT}$$

For a sample rate of 1Msps using the timing calculates to:

$$t_{CYC} = 40 ns + 30 ns + 660 ns + 270 ns = 1000 ns$$

## 5.4 Convert Start (CS) Pin

The convert start input  $(\overline{CS})$  initiates a conversion in the ISL73141SEH. The input logic level of  $\overline{CS}$  is determined by the DV<sub>CC</sub> supply voltage, which operates across a range of 2.2V up to 3.6V. A falling edge on this input starts a new conversion. The conversion is timed using an internal oscillator. The logic state of the  $\overline{CS}$  pin controls the state of the SDO pin. A logic high on the  $\overline{CS}$  pin disables the SDO pin driver resulting in a high-impedance state on the SDO pin. A logic low on the  $\overline{CS}$  pin enables the SDO driver (unless  $\overline{PD}$  is low) and allows data to be read out following a conversion.

## 5.5 Power Down (PD) Pin

The ISL73141SEH has a power down pin that is active low  $(\overline{PD})$ . When this pin is asserted the ISL73141SEH is powered down to  $\leq 50 \mu W$  of total power dissipation. If  $\overline{PD}$  is asserted during a conversion, the conversion is halted and the SDO pin is held in high impedance (high-Z). The input logic level of  $\overline{PD}$  is determined by the DV<sub>CC</sub> supply voltage, which operates across a range of 2.2V up to 3.6V. There is an internal  $500 k\Omega$  pull-up resistor connected to DV<sub>CC</sub> on this pin.

### 5.6 Reference Input (REF) Pin

The ISL73141SEH has a voltage reference input that determines the full scale input range. The input voltage range of this pin is from 1.95V to 3.6V (ISL73141SEHMFN) or 3.9V to 4.2V (ISL73141SEHMF7). Decouple this pin to ground with a high quality, low ESR 10µF ceramic capacitor. Renesas recommends using a capacitor with a voltage rating of 10V or greater and to place the capacitor as close as possible to the REF pin.

Use a low noise, low temperature drift reference to drive this pin. Input noise from the input reference directly impacts the noise performance of the device. Temperature drift of the external reference affects the full scale error for the over-temperature of the device.

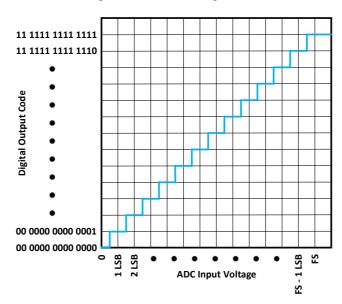

#### 5.7 ISL73141 Transfer Function

<u>Figure 55</u> gives the transfer function of the device. Code transitions in the digital outputs bits of the device occur at midway points between successive integer LSB values that range from 0.5 LSB, 1.5 LSB, 2.5 LSB, 3.5 LSB... and FS - 3.5 LSB, FS - 2.5 LSB, FS - 1.5 LSB, FS - 0.5 LSB. The device is a 14-bit ADC with an output code range in decimal from 0 to  $2^{N}$ -1 where N = 14, making the total code range 0 to 16383 inclusive.

Figure 55. ISL73141SEH Transfer Function

### 5.8 Power Supply Sequencing

The ISL73141SEH does not have any specific power sequencing requirements when increasing the supply voltages. **IMPORTANT:** You must follow the guidelines in the recommended operating conditions and take care in observing the maximum supply voltage conditions outlined in the Absolute Maximum Ratings section.

### 5.9 Analog Input (AIN) Pin

The ISL73141SEH supports single-ended input drive only. **IMPORTANT**: Ensure that proper grounding techniques and supply decoupling are used in circuit board layout to achieve optimum performance. The ISL73141SEH evaluation board can be used as a guide for proper circuit optimization. The analog input is a high-impedance input that exhibits a capacitive load of approximately 15pF during sample mode and 3pF during hold mode. Due to the high bandwidth (50MHz) of the analog input, Renesas recommends using an Anti-Alias Filter (AAF) appropriate for the desired application. It is not required to operate the ISL73141SEH with an input amplifier, but it can improve performance and/or provide gain in certain applications. An example topology is given in Figure 56, which uses a driver amplifier and an RC input filter. Care must be taken to choose an amplifier with low noise and distortion because the ADC performance is directly impacted. It is also important to choose feedback resistance values that are less than  $1k\Omega$  (typically,  $100\Omega$  to  $200\Omega$ ) to minimize the impact of resistor thermal noise. The noise of the resistor is directly related to its value by Equation 2.

(EQ. 2) Power Spectral Density (PSD) =

$$4kTR (V^2/Hz)$$

#### where

- k = Boltzmans constant (1.38 x 10<sup>-23</sup>)

- T = Temperature in Kelvin (room temperature = 27°C = 300K)

- R = Resistance value

At the input to the ADC, a simple RC filter should be sufficient for most applications. Choose the RC circuit values appropriately for the application. A low-value resistor ( $R_S \le 50$ ) is recommended for low noise performance. Add a high-quality shunt capacitor ( $C_P$ ) as close as possible to the AIN pin to shunt charge kickback from the ADC during sampling and to limit the input bandwidth to the ADC. The recommended values for the  $C_P$  range is from 220pF to 680pF. Larger values for  $C_P$  can be used for slower conversion rates.

Figure 56. ISL73141SEH Analog Input Amplifier Example Circuit

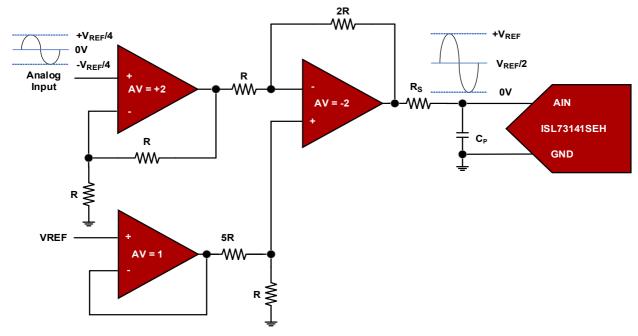

Due to the switched capacitance of the analog input, Renesas recommends limiting series inductance in the analog input path, particularly the inductance near the analog input pins of the device. Renesas also recommends using a high quality ceramic capacitor  $(C_P)$  in shunt on the analog input that is at an appropriate value for the required application. Choose the series resistance in the analog input circuit based on the output impedance of the driver amplifier and the application requirements. An example topology is given in Figure 57, which converts a 0V input common-mode voltage to the ADC input common-mode voltage of  $V_{REF}/2$ . This circuit is employed on the ISL73141SEH evaluation board to allow the ADC to be driven from various types of signal generators.

Figure 57. ISL73141SEH Common-Mode Conversion Amplifier Example Circuit

It is important to understand the settling time associated with the analog input of the ISL73141SEH and the impacts of  $R_S$  and  $C_P$ . To allow the ISL73141SEH to accurately resolve the input signal, it is important that the input signal is settled completely before the signal is sampled by the ISL73141SEH. To meet the datasheet specifications, the settling time must be met for the input signals on the analog input of the ISL73141SEH. To accurately resolve to 1 LSB, the settling time is defined by Equation 3:

(EQ. 3)

$$\frac{1}{2^N} = e^{-t/\tau}$$

Simplifying this results in Equation 4:

(EQ. 4)

$$ln(2^N) = -\frac{t}{\tau}$$

Solving for t results in:

$$t = -\tau \times ln(2^N) \text{, which can be written as } \ t = N \times \tau \times ln(2) \text{] and further simplified to } \ t = 0.693 \times N \times \tau \text{.}$$

Settling time is t,  $R_S \times C_P$  is  $\tau$ , and the resolution of the ADC is N.

The ISL73141SEH is a 14-bit ADC, which means the settling time to attain 1 LSB accuracy is  $9.7 \times \tau$ . For example, the ISL73141SEHEV1Z evaluation board employs a  $24\Omega$  resistor for  $R_S$  and a 470pF capacitor for  $C_P$ , which means that the required settling time would be  $t = 0.693 \times 14 \times 24\Omega \times 470$ pF = 109.4ns. If different  $R_S$  and  $C_P$  values are used, calculate the settling time for those conditions. These calculations assume the settling time of the input network  $R_S$  and  $C_P$  are much larger than the settling time of any amplifier driving the ISL73141SEH analog input. If this is not the case, the settling time of the input network must be root-sum-squared with the settling time of the amplifier to determine the required settling time using Equation 5:

(EQ. 5)

$$t = \sqrt{(t_{\Delta MP})^2 + (t_{RC})^2}$$

#### 5.10 Package

The ISL73141SEH is available in a 14 Ld hermetically sealed Ceramic Dual Flatpack (CDFP) package (see <a href="Package Outline Drawing">Package Outline Drawing</a>). Pin 14 (GND) is connected to the package seal ring and the package lid.

# 6. Die and Assembly Characteristics

## Table 1. Die and Assembly Related Information

| Die Information           |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| Dimensions                | 2410µm x 3910µm (95 mils x 154 mils)<br>Thickness: 483µm ±25µm (19 mils ±1 mil) |

| Interface Materials       |                                                                                 |

| Passivation               | Oxide/Nitride Total Thickness 24.5 kÅ                                           |

| Top Metallization         | Top metal/Bond Pad Composition<br>99.5% Al, 0.5%Cu                              |

| Process                   | 0.25um CMOS                                                                     |

| Assembly Information      | ·                                                                               |

| Substrate Potential       | GND                                                                             |

| Additional Information    |                                                                                 |

| Transistor Count          | 37700                                                                           |

| Weight of Packaged Device | 0.572 grams (typical) - K14.A package                                           |

| Lid Characteristics       | Finish: Gold<br>Lid Potential: Connected to package Pin 14 (DGND)               |

ISL73141SEH 7. Revision History

# 7. Revision History

| Rev. | Date         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2  | Feb 23, 2023 | Added Feature bullet. Removed Related Literature. Updated Ordering information table package descriptions.                                                                                                                                                                                                                                                                                                                                                                           |

| 4.1  | Jun 24, 2021 | Added the Die and Assembly Characteristics section.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.0  | May 14, 2021 | Updated Ordering information table formatting. Updated the SDO Data Valid Delay from SCK↑ specs changed 5V operation maximum from 16ns to 18.5ns and changed 3.3V operation maximum from 24ns to 25n. Updated Figures 5 and 54.                                                                                                                                                                                                                                                      |

| 3.1  | Jan 28, 2021 | Added ESD circuits to the pin description table.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.0  | Dec 9, 2020  | Corrected typo in the REF pin description by changing the capacitor value from 10F to 10µF.  Updated the Effective Number of Bits minimum value on page 7 from 12.8 to 12.5 for 5V specification table.  Updated the Analog Supply Current - Active test condition changed from 1MSPS to 750ksps in the 3.3V specification table.                                                                                                                                                    |

| 2.0  | Oct 21, 2020 | Changed Radiation Tolerant to Radiation Hardened in Title and throughout datasheet.  Updated 3rd paragraph of description on page 1.  Pin Description table: updated pin 3/REF input range.  Recommended Operating Conditions and Electrical Spec tables: updated Reference Input Voltage, VREF from 1.5V to: 1.95 for ISL73141SEHMFN) and 3.9V for ISL73141SEHMF7)  Updated Figures 18, 19, 20, 42, 43, 44  Reference Input (REF) Pin section, page 22: updated input voltage range |

| 1.0  | Sep 1, 2020  | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

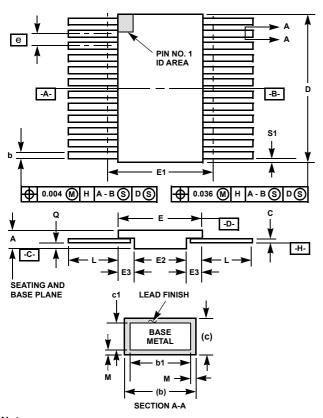

### 8. Package Outline Drawing

For the most recent package outline drawing, see K14.A.

### Notes:

- Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark. Alternately, a tab (dimension k) may be used to identify pin one.

- 2. If a pin one identification mark is used in addition to a tab, the limits of dimension k do not apply.

- 3. This dimension allows for off-center lid, meniscus, and glass overrun

- 4. Dimensions b1 and c1 apply to lead base metal only. Dimension M applies to lead plating and finish thickness. The maximum limits of lead dimensions b and c or M shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- 5. N is the maximum number of terminal positions.

- 6. Measure dimension S1 at all four corners.

- For bottom-brazed lead packages, no organic or polymeric materials shall be molded to the bottom of the package to cover the leads.

- Dimension Q shall be measured at the point of exit (beyond the meniscus) of the lead from the body. Dimension Q minimum shall be reduced by 0.0015 inch (0.038mm) maximum when solder dip lead finish is applied.

- 9. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 10. Controlling dimension: INCH.

K14.A MIL-STD-1835 CDFP3-F14 (F-2A, Configuration B) 14 Lead Ceramic Metal Seal Flatpack Package (CDFP)

|        | INCHES MILLIME |        |          |      |       |

|--------|----------------|--------|----------|------|-------|

|        |                |        |          |      |       |

| SYMBOL | MIN            | MAX    | MIN      | MAX  | NOTES |

| Α      | 0.045          | 0.115  | 1.14     | 2.92 | -     |

| b      | 0.015          | 0.022  | 0.38     | 0.56 | -     |

| b1     | 0.015          | 0.019  | 0.38     | 0.48 | -     |

| С      | 0.004          | 0.009  | 0.10     | 0.23 | -     |

| c1     | 0.004          | 0.006  | 0.10     | 0.15 | -     |

| D      | -              | 0.390  | -        | 9.91 | 3     |

| Е      | 0.235          | 0.260  | 5.97     | 6.60 | -     |

| E1     | -              | 0.290  | -        | 7.11 | 3     |

| E2     | 0.125          | -      | 3.18     | -    | -     |

| E3     | 0.030          | -      | 0.76     | -    | 7     |

| е      | 0.050          | BSC    | 1.27 BSC |      | -     |