# **RAJ306102**

**General Purpose Motor Control IC**

Rev.1.00 Oct 5, 2023

## 1 Description

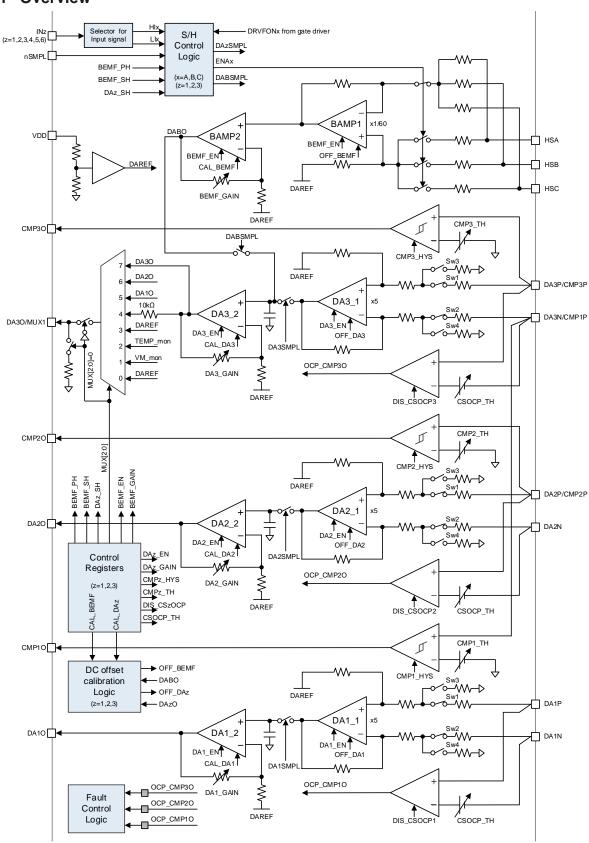

The RAJ306102 is a general-purpose motor control IC for 3-phase brushless DC (BLDC) motor applications. RAJ306102 combines a smart gate driver and MCU (RL78/G1F) in a single package.

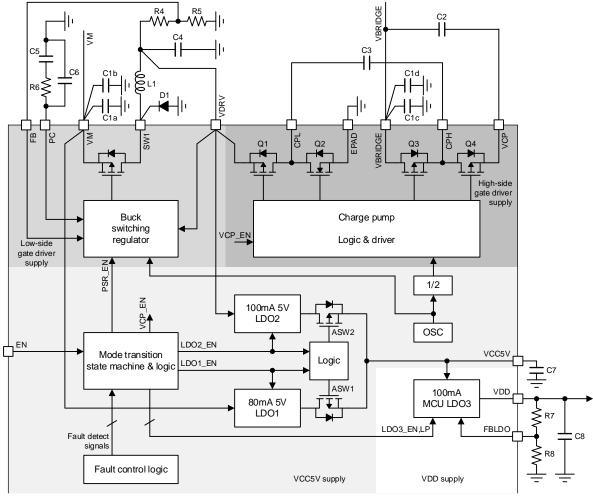

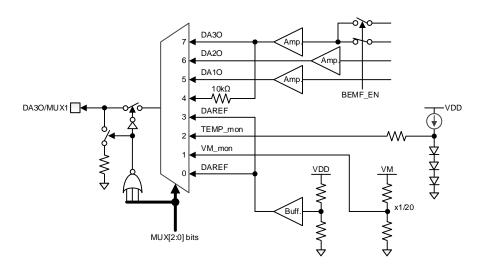

The smart gate driver includes three half-bridge gate drivers, a buck switching regulator and a charge pump for the gate drive voltage, two LDOs for the internal analog and logic circuitry and MCU, three accurate differential amplifiers, a BEMF sense amplifier, three general purpose comparators, and extensive protection functions.

The three half-bridge gate drivers are capable of driving up to three N-channel MOSFET bridges and support bridge voltages from 6V to 65V. Each gate driver supports up to 0.64A source and 1.28A sink peak drive current with adjustable drive strength control. Adaptive and adjustable dead-times are implemented to ensure robustness and flexibility. The active gate holding mechanism prevents miller effect induced cross-conduction and further enhances robustness.

Three accurate differential amplifiers with adjustable gain support ground-side shunt current sensing for each bridge. The device can also support both BLDC sensor/sensorless motor drive by the three general purpose comparators or a BEMF sense amplifier.

The protection functions include supply voltage OV/UV protection, buck regulator OV/UV/OC protection, charge pump UV protection, MOSFET VDS OC protection, current sense OC protection, MOSFET VGS fault, thermal warning, and thermal shutdown.

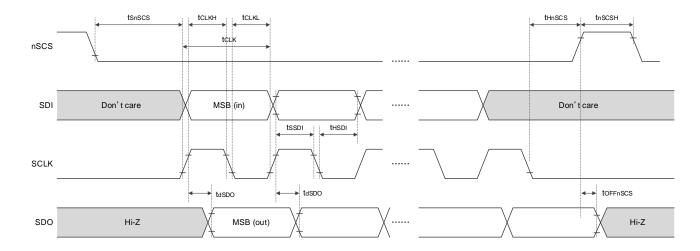

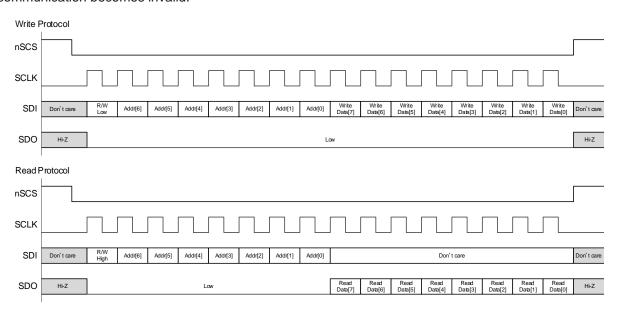

The smart gate driver can be configured to use SPI interface by the internal connection with MCU. All the parameters can be set through the SPI interface, and allows better monitoring. Fault conditions are reported on the nFAULT signal and each status bit in the Fault Status registers.

MCU supports H/W of the safe standard of IEC60730 and IEC61508. The development tools of the RL78 family are available.

## 2 Features

- · Operating power supply voltage:

- VBRIDGE: 6V to 65V (78V abs max)

- VM: 6V to 60V (65V abs max)

- Operating ambient temperature: -40°C to 105°C

- · Supply current:

- MCU, VDD current: (HS mode, fiH=32MHz: 5.2mA)

- Smart gate driver, VM current:

Operating Mode: 2mA, Sleep Mode: 28µA

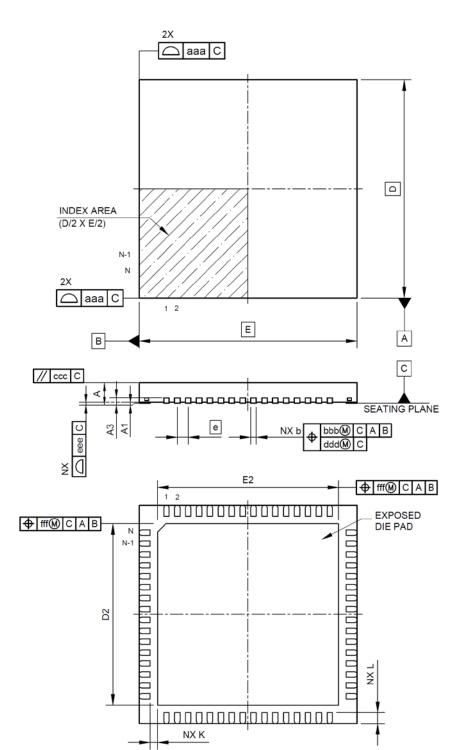

- 8mm×8mm 64 Ld QFN package (0.4mm pitch)

#### **Smart Gate Driver function**

- 3-Phase drive for BLDC application

- Peak 0.64A/1.28A source/sink current with 16 adjustable drive strength through SPI interface

- Adaptive and adjustable dead time

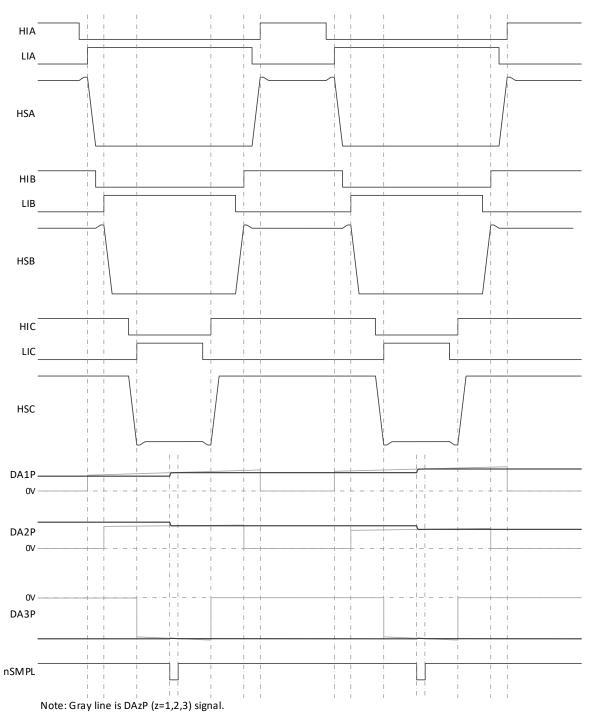

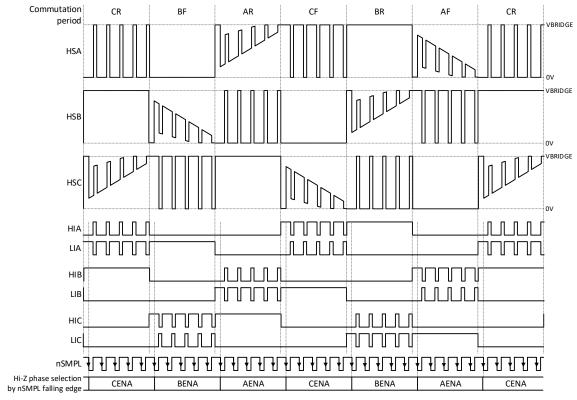

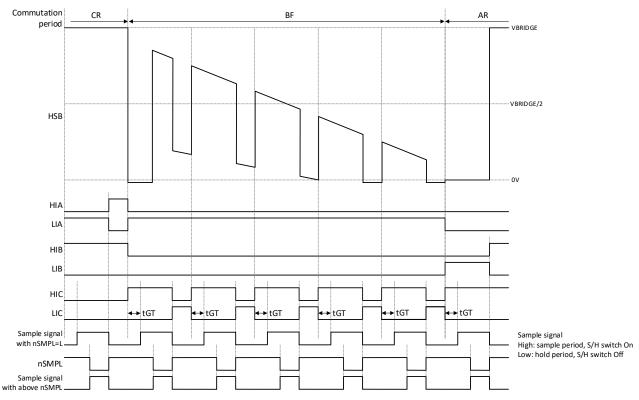

- 3-phase HI/LI mode and 3-phase PWM mode

- Input control signal configuration

- · Fully integrated power supply architecture

- Two 5V LDOs allow for Sleep Mode low IQ

- 500mA buck switching regulator for the gate drive voltage (5V to 15V adjustable)

- 100mA adjustable output LDO for MCU supplies

- Three differential amplifiers with configurable gain for current sensing (5, 10, 20, 40V/V)

- · BEMF sense amplifier for sensorless motor drive

- · Three comparators for hall sensor motor drive

- · Extensive protection functions

#### MCU (RL78/G1F) function

- CPU: 16bit CISC CPU

- Code flash: 64KB, Data flash: 4KB, RAM: 5.5KB

- Serial array unit: 2 units (CSI:2ch, UART:1ch, I<sup>2</sup>C:2ch)

- GPIO: 29 channels: I/O: 27ch, Input: 2ch

- Timer: Timer array unit: 1unit: 16bit, 4ch

- Timer RJ/RG: 16bit, 1ch/1ch

- Timer RD for motor control: 16bit, 2ch

- Timer RX: 16bit, 1ch

- 10-bit resolution A/D converter input: 11ch

- External interrupt input: 10ch

# 3 Applications

- Power tools and Garden tools

- Vacuum cleaners, Fans, Pumps, and Robotics

- 1. Please refer to not only this datasheet but also "RAJ306102 User's Manual: Hardware (R18UZ0082EJ)" to understand this IC.

- 2. About detail specifications of RL78/G1F, please see "RL78/G1F User's Manual: Hardware (R01UH0516EJ)".

- This product has some restrictions on function.

Please check them on "CHAPTER2 MCU: RL78/G1F" in "RAJ306102 User's Manual: Hardware (R18UZ0082EJ)".

- 4. About the electrical characteristics of RL78/G1F, please substitute EVDD0/VDD condition to 3.135V<=EVDD0/VDD<=5.25V.

## 4 Overview

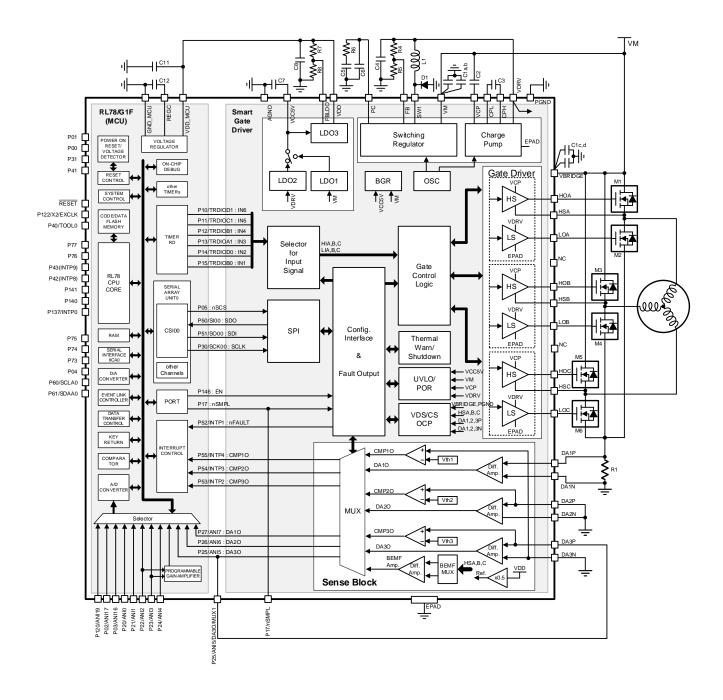

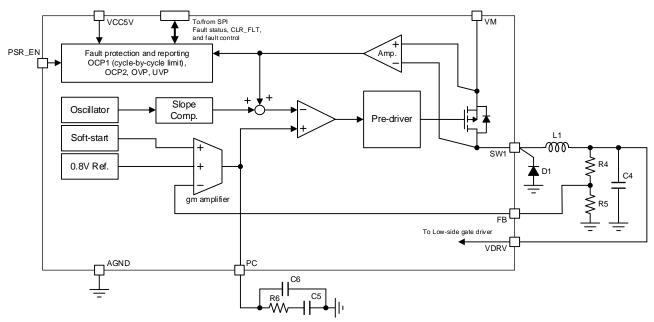

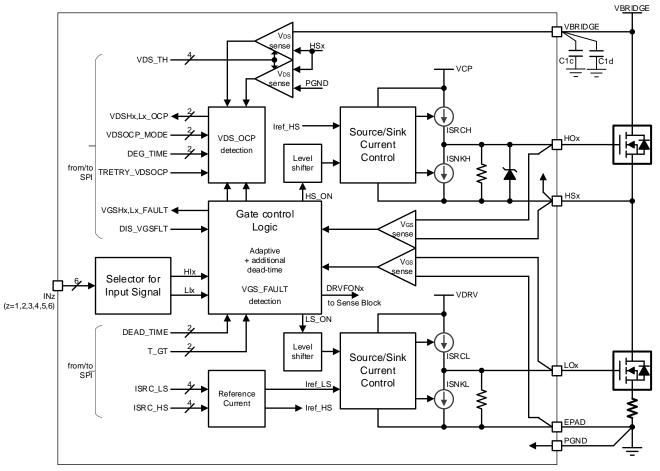

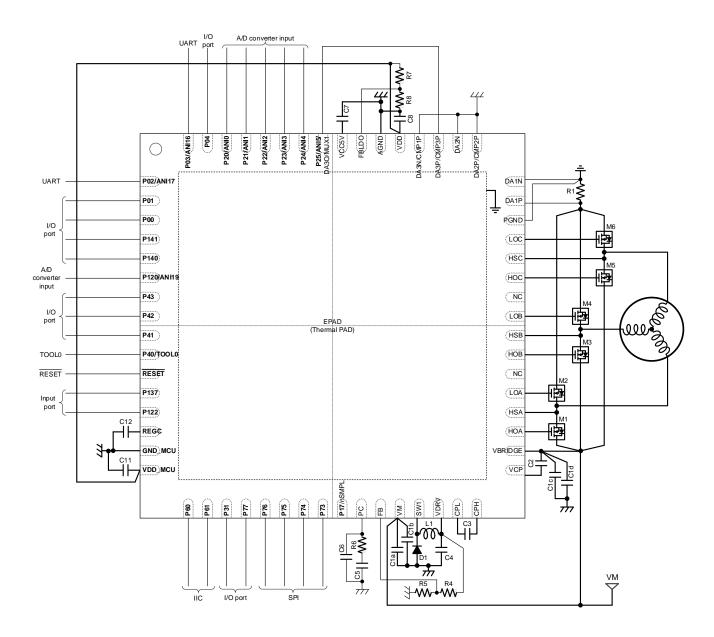

## 4.1 Typical Application Circuits

Figure 4.1-1 Simplified Block Diagram and Application – Sensorless Motor Drive by BEMF Sensing Comparator

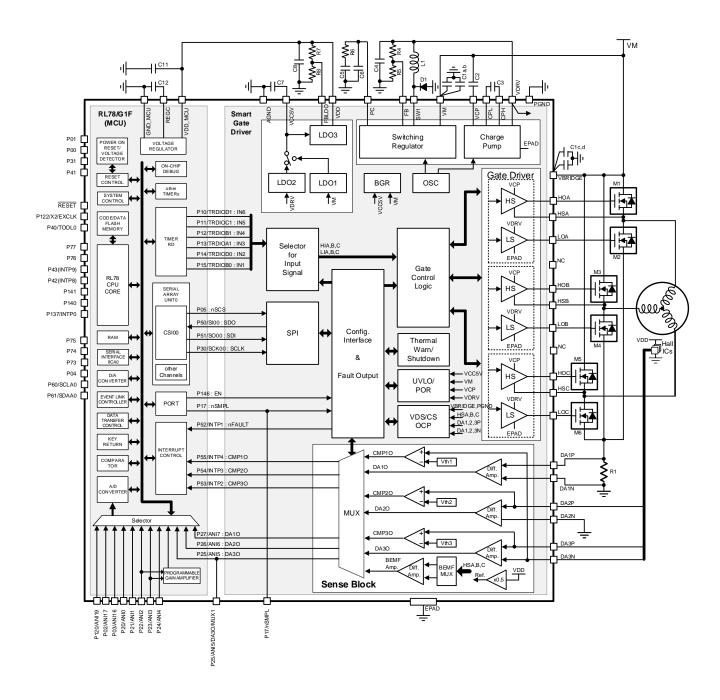

# 4.1 Typical Application Circuits (continued)

Figure 4.1-2 Simplified Block Diagram and Application - Hall Sensor Motor Drive by Using 3 Comparators

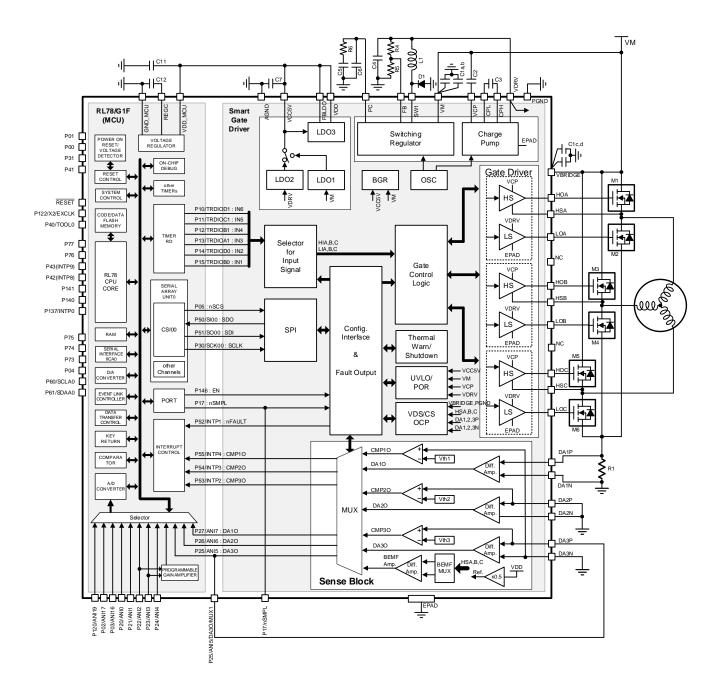

## 4.1 Typical Application Circuits (continued)

Figure 4.1-3 Simplified Block Diagram and Application – Sensorless Motor Drive by BEMF Sensing Comparator with 5V MCU Supply

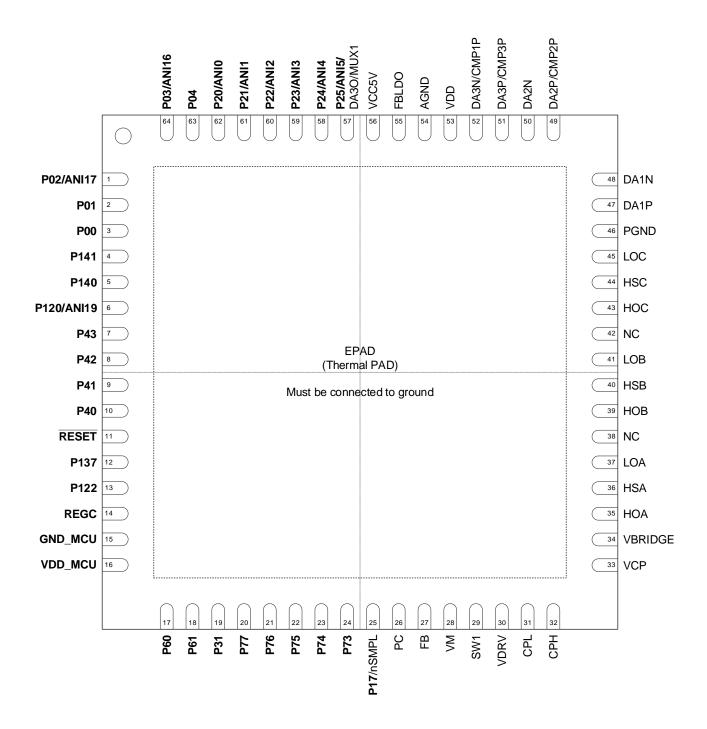

## 4.2 Pin Configurations

Figure 4.2-1 Pin Configuration Diagram Top View

# 4.3 Pin Descriptions

Table 4.3-1 Pin Descriptions

|        | PIN     | Alternate                                   |       | I/O    |         |                                                                                                                                                                |      |

|--------|---------|---------------------------------------------|-------|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Number | Name    | Function                                    | level | type   | Initial | Function                                                                                                                                                       | Note |

| 1      | P02     | ANI17/SO10/<br>TxD1/IVCMP10                 | VDD   | IN/OUT | ANALOG  | Digital input/output / ADC analog input / Serial data output of CSI10 / Serial data output of UART / Comparator 1 analog voltage input/reference voltage input | 1    |

| 2      | P01     | TO00/TRGCLKB/<br>TRJIO0/(INTP10)            | VDD   | IN/OUT | IN      | Digital input/output / Timer 00 output / Timer RG external clock input / Timer RJ input/output / (INTP10 interrupt request input)                              | 1    |

| 3      | P00     | TI00/TRGCLKA/<br>(TRJO0)/(INTP8)            | VDD   | IN/OUT | IN      | Digital input/output / Timer 00 input / Timer RG external clock input / (Timer RJ output) / (INTP8 interrupt request input)                                    | 1    |

| 4      | P141    | PCLBUZ1/<br>INTP7                           | VDD   | IN/OUT | IN      | Digital input/output / Programmable clock output/Buzzer output / INTP7 interrupt request input                                                                 | 1    |

| 5      | P140    | PCLBUZ0/<br>INTP6                           | VDD   | IN/OUT | IN      | Digital input/output / Programmable clock output/Buzzer output / INTP6 interrupt request input                                                                 | 1    |

| 6      | P120    | ANI19/VCOUT0                                | VDD   | IN/OUT | ANALOG  | Digital input/output / ADC analog input / Comparator 0 output                                                                                                  | 1    |

| 7      | P43     | INTP9                                       | VDD   | IN/OUT | IN      | Digital input/output / INTP9 interrupt request input                                                                                                           | 1    |

| 8      | P42     | INTP8                                       | VDD   | IN/OUT | IN      | Digital input/output / INTP8 interrupt request input                                                                                                           | 1    |

| 9      | P41     | (TRJIO0)                                    | VDD   | IN/OUT | IN      | Digital input/output / (Timer RJ input/output)                                                                                                                 | 1    |

| 10     | P40     | TOOL0                                       | VDD   | IN/OUT | IN      | Digital input/output / Data I/O for flash memory programmer/debugger                                                                                           | 1    |

| 11     | /RESET  | -                                           | VDD   | IN     | -       | The active-low system reset input for RL78/G1F                                                                                                                 | 1    |

| 12     | P137    | INTP0                                       | VDD   | IN     | IN      | Digital input / INTP0 interrupt request input                                                                                                                  | 1    |

| 13     | P122    | EXCLK                                       | VDD   | IN     | IN      | Digital input / External clock input for main system clock                                                                                                     | 1    |

| 14     | REGC    | -                                           | VDD   | -      | -       | Connect regulator output stabilization capacitor between REGC and GND_MCU for internal operation of RL78/G1F.                                                  | 1    |

| 15     | GND_MCU | -                                           | VDD   | GND    | -       | Ground for RL78/G1F                                                                                                                                            | 1    |

| 16     | VDD_MCU | -                                           | VDD   | POWER  | -       | Positive power supply input for RL78/G1F Connect to bypass capacitors between VDD_MCU and GND_MCU.                                                             | 1    |

| 17     | P60     | SCLA0                                       | VDD   | IN/OUT | IN      | Digital input/output / Serial clock I/O of serial interface IICA0                                                                                              | 1    |

| 18     | P61     | SDAA0                                       | VDD   | IN/OUT | IN      | Digital input/output / Serial data I/O of serial interface IICA0                                                                                               | 1    |

| 19     | P31     | TI03/TO03/<br>(PCLBUZ0)/<br>(TRJIO0)/VCOUT1 | VDD   | IN/OUT | IN      | Digital input/output / Timer 03 input / Timer 03 output / (Programmable clock output/Buzzer output) / (Timer RJ output) / Comparator 1 output                  | 1    |

| 20     | P77     | KR7/INTP11                                  | VDD   | IN/OUT | IN      | Digital input/output / KR7 key interrupt input / INTP11 interrupt request input                                                                                | 1    |

| 21     | P76     | KR6/INTP10                                  | VDD   | IN/OUT | IN      | Digital input/output / KR6 key interrupt input / INTP10 interrupt request input                                                                                | 1    |

| 22     | P75     | KR5/SCK01/<br>SCL01                         | VDD   | IN/OUT | IN      | Digital input/output / KR5 key interrupt input / Serial clock I/O of CSI01 / Serial clock output of IIC01                                                      | 1    |

| 23     | P74     | KR4/SI01/<br>SDA01                          | VDD   | IN/OUT | IN      | Digital input/output / KR4 key interrupt input / Serial data input of CSI01 / Serial data I/O of IIC01                                                         | 1    |

| 24     | P73     | KR3/S001                                    | VDD   | IN/OUT | IN      | Digital input/output / KR3 key interrupt input / Serial data output of CSI01                                                                                   | 1    |

| 25     | P17     | TI02/TO02/<br>nSMPL                         | VDD   | IN/OUT | IN      | Digital input/output / Timer 02 input / Timer 02 output / Sample and Hold control input for smart gate driver                                                  | 1,2  |

| 26     | PC      | -                                           | VCC5V | ОИТ    | ОИТ     | gm amplifier output for phase compensation of buck switching regulator.                                                                                        |      |

| 27     | FB      | -                                           | VCC5V | IN     | IN      | Voltage feedback input of buck switching regulator (Ref.=0.8V).                                                                                                |      |

| 28     | VM      | -                                           | VM    | POWER  | -       | Power supply input. Connect bypass capacitors between VM and analog ground.                                                                                    |      |

| 29     | SW1     | -                                           | VM    | OUT    | OUT     | Switch node of buck switching regulator.                                                                                                                       |      |

| 30     | VDRV    | -                                           | VDRV  | POWER  | -       | Output of buck switching regulator, Low-side gate driver supply.  Connect to bypass capacitors between VDRV and analog ground.                                 |      |

| 31     | CPL     | -                                           | VDRV  | OUT    | OUT     | Charge pump low-side switch node. Connect a flying capacitor between CPH and CPL pins.                                                                         |      |

| 32     | СРН     | -                                           | VCP   | ОИТ    | ОИТ     | Charge pump high-side switch node. Connect a flying capacitor between CPH and CPL pins.                                                                        |      |

Note1: RL78/G1F terminal. Please refer to "RL78/G1F User's Manual: Hardware" (R01UH0516EJ) about port functions of RL78/G1F.

Note2: When this pin is used as P17(Digital input/output), T102, or TO02 function, the S/H function of the differential amplifier in the smart gate driver is not available.

Please set all of BEMF\_SH, DA1\_SH, DA2\_SH, and DA3\_SH bit in SNSCTL2 register of the smart gate driver to "0".

Please refer to the control register information on section 6.7.15, Sense Block Control 2 register.

# 4.3 Pin Descriptions (continued)

Table 4.3-2 Pin Descriptions (continued)

|        | PIN                   | Alternate                         |         | I/O    |         |                                                                                                                                                                                         |      |

|--------|-----------------------|-----------------------------------|---------|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Number | Name                  | Function                          | level   | type   | Initial | Function                                                                                                                                                                                | Note |

| 33     | VCP                   | -                                 | VCP     | POWER  | -       | Charge pump output. Connect a bypass capacitor between VCP and VBRIDGE pins.                                                                                                            |      |

| 34     | VBRIDGE               | -                                 | VBRIDGE | IN     | IN      | Charge pump output reference and high-side MOSFET drain sense Input. Connect a bypass capacitor between VBRIDGE pin and power ground.                                                   |      |

| 35     | HOA                   | -                                 | VCP     | ОИТ    | OUT     | Phase A high-side gate driver output. Connect to the high-side MOSFET gate.                                                                                                             |      |

| 36     | HSA                   | -                                 | VBRIDGE | IN     | IN      | Phase A high-side source sense input. Connect to the high-side MOSFET source.                                                                                                           |      |

| 37     | LOA                   | -                                 | VDRV    | OUT    | OUT     | Phase A low-side gate driver output. Connect to the low-side MOSFET gate.                                                                                                               |      |

| 38     | NC                    | -                                 | -       | -      | -       | No connection (Keep open state)                                                                                                                                                         |      |

| 39     | HOB                   | -                                 | VCP     | OUT    | OUT     | Phase B high-side gate driver output. Connect to the high-side MOSFET gate.                                                                                                             |      |

| 40     | HSB                   | -                                 | VBRIDGE | IN     | IN      | Phase B high-side source sense input. Connect to the high-side MOSFET source.                                                                                                           |      |

| 41     | LOB                   | -                                 | VDRV    | OUT    | OUT     | Phase B low-side gate driver output. Connect to the low-side MOSFET gate.                                                                                                               |      |

| 42     | NC                    | -                                 | -       | -      | -       | No connection (Keep open state)                                                                                                                                                         |      |

| 43     | HOC                   | -                                 | VCP     | OUT    | OUT     | Phase C high-side gate driver output. Connect to the high-side MOSFET gate.                                                                                                             |      |

| 44     | HSC                   | -                                 | VBRIDGE | IN     | IN      | Phase C high-side source sense input. Connect to the high-side MOSFET source.                                                                                                           |      |

| 45     | LOC                   | -                                 | VDRV    | ОИТ    | OUT     | Phase C low-side gate driver output. Connect to the low-side MOSFET gate.                                                                                                               |      |

| 46     | PGND                  | -                                 | GND     | GND    | -       | Ground sense input of external power stage.                                                                                                                                             |      |

| 47     | DA1P                  | -                                 | VDD     | IN     | IN      | Positive input of differential amplifier 1.                                                                                                                                             |      |

| 48     | DA1N                  | -                                 | VDD     | IN     | IN      | Negative input of differential amplifier 1.                                                                                                                                             |      |

| 49     | DA2P                  | CMP2P                             | VDD     | IN     | IN      | Positive input of differential amplifier 2 and positive input of comparator 2.                                                                                                          |      |

| 50     | DA2N                  | -                                 | VDD     | IN     | IN      | Negative input of differential amplifier 2.                                                                                                                                             |      |

| 51     | DA3P                  | CMP3P                             | VDD     | IN     | IN      | Positive input of differential amplifier 3 and positive input of comparator 3.                                                                                                          |      |

| 52     | DA3N                  | CMP1P                             | VDD     | IN     | IN      | Negative input of differential amplifier 3 and positive input of comparator 1.                                                                                                          |      |

| 53     | VDD                   | -                                 | VDD     | POWER  | -       | Internal series regulator output and power supply of output buffers.  Connect to a bypass capacitor between VDD and AGND.                                                               |      |

| 54     | AGND                  | -                                 | GND     | GND    | -       | Device analog ground.                                                                                                                                                                   |      |

| 55     | FBLDO                 | -                                 | VCC5V   | IN     | IN      | Voltage feedback input of internal series regulator (Ref.=1.2V).                                                                                                                        |      |

| 56     | VCC5V                 | -                                 | VCC5V   | POWER  | -       | Internal series regulator output(5V). Connect to a bypass capacitor between VCC5V and AGND.                                                                                             |      |

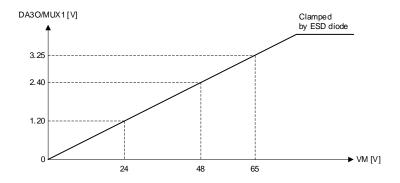

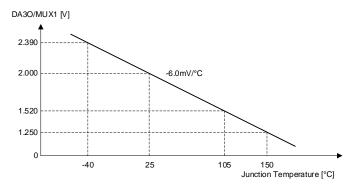

| 57     | P25                   | ANI5/DA3O/MUX1                    | VDD     | IN/OUT | ANALOG  | Digital input/output / ADC analog input / Output of differential amplifier 3, BEMF sense amplifier, and multiplexer.                                                                    | 1,3  |

| 58     | P24                   | ANI4                              | VDD     | IN/OUT | ANALOG  | Digital input/output / ADC analog input                                                                                                                                                 | 1    |

| 59     | P23                   | ANI3/ANO1/<br>PGAGND              | VDD     | IN/OUT | ANALOG  | Digital input/output / ADC analog input / DAC output / PGA reference voltage input                                                                                                      | 1    |

| 60     | P22                   | ANI2/ANO0/<br>PGAI/IVCMP0         | VDD     | IN/OUT | ANALOG  | Digital input/output / ADC analog input / DAC output / PGA voltage input / Comparator 0 analog voltage input                                                                            | 1    |

| 61     | P21                   | ANI1/AVREFM/<br>IVCMP13           | VDD     | IN/OUT | ANALOG  | Digital input/output / ADC analog input / ADC reference(- side) input                                                                                                                   | 1    |

| 62     | P20                   | ANIO/AVREFP/<br>IVCMP12/(INTP11)  | VDD     | IN/OUT | ANALOG  | Digital input/output / ADC analog input / ADC reference (+ side) input / Comparator 1 analog voltage input/reference voltage input / (External interrupt request input)                 | 1    |

| 63     | P04                   | SCK10/SCL10                       | VDD     | IN/OUT | ANALOG  | Digital input/output / Serial clock I/O of CSI10 /<br>Serial clock output of IIC10                                                                                                      | 1    |

| 64     | P03                   | ANI16/SI10/RxD1/<br>SDA10/IVCMP11 | VDD     | IN/OUT | ANALOG  | Digital input/output / ADC analog input / Serial data input of CSI10 / Serial data input of UART / Serial data I/O of IIC10 / Comparator 1 analog voltage input/reference voltage input | 1    |

| -      | EPAD<br>(Thermal PAD) | -                                 | GND     | GND    | -       | Power ground for gate driver and charge pump.  Must be connected to power ground.                                                                                                       |      |

Note1: RL78/G1F terminal. Please refer to "RL78/G1F User's Manual: Hardware" (R01UH0516EJ) about port functions of RL78/G1F.

Note3: When this pin is used as P25 or ANI5 pin, please set MUX bits in SNSCTL5 register of the smart gate driver to "000b".

This pin has 330kohm pulldown resistance. Please refer to the control register information on section 6.5.5, MUX1 Output Control, and section 6.7.18, Sense Block Control 5 register.

# 5 Specifications

## 5.1 Absolute Maximum Ratings

Table 5.1-1 Absolute Maximum Ratings Note1

|                              | Item                                                                                                       | Symbol           | Minimum | Maximum                             | unit |  |

|------------------------------|------------------------------------------------------------------------------------------------------------|------------------|---------|-------------------------------------|------|--|

| VBRIDGE to GND Note2         | VBRIDGE to GND Note2                                                                                       |                  | -0.3    | 78                                  | V    |  |

| VM to GND Note2              |                                                                                                            | VMabs            | -0.3    | 65                                  | V    |  |

| Voltage difference between g | round pins (AGND, PGND, EPAD)                                                                              | DGNDabs          | -0.3    | 0.3                                 | V    |  |

| VCP to GND, CPH to GND, \    | /CP to HSx, VCP to HOx (x=A,B,C)                                                                           | VCPabs           | -0.3    | VBRIDGE + 15 Note3                  | V    |  |

| CPL to GND                   |                                                                                                            | VCPLabs          | -0.3    | VDRV + 0.3                          | V    |  |

| Continuous HOx (x=A,B,C) to  | o GND                                                                                                      | VHOxabs          | -5      | VCP + 0.5                           | V    |  |

| Transient 200ns HOx (x=A,B   | ,C) to GND                                                                                                 | VHOxtran         | -7      | VCP + 0.5                           | V    |  |

| HOx to HSx (x=A,B,C)         |                                                                                                            | VGSHxabs         | -0.3    | 15                                  | V    |  |

| Continuous HSx (x=A,B,C) to  | GND                                                                                                        | VHSxabs          | -5      | VBRIDGE + 5 Note4                   | V    |  |

| Transient 200ns HSx (x=A,B   | ,C) to GND                                                                                                 | VHSxtran         | -7      | VBRIDGE + 7 Note4                   | V    |  |

| VDRV to AGND                 |                                                                                                            | VDRVabs          | -0.3    | 17                                  | V    |  |

| Continuous LOx (x=A,B,C) to  | GND                                                                                                        | VLOabs           | -1      | VDRV + 0.5                          | V    |  |

| SW1 to GND                   |                                                                                                            | VSWabs           | -1      | VM + 0.5                            | V    |  |

| VCC5V to GND                 |                                                                                                            | VCCabs           | -0.3    | -0.3 5.5                            |      |  |

| FB, PC, FBLDO to GND         |                                                                                                            | VFBabs           | -0.3    | VCC5V + 0.3                         | V    |  |

| DAzP (z=1,2,3) to GND, DAz   | zN (z=1,2,3) to GND                                                                                        | VDAINabs         | -1      | VDD + 0.6                           | V    |  |

| VDD, VDD_MCU to GND          |                                                                                                            | VDDabs           | -0.3    | 5.5                                 | V    |  |

| REGC input voltage to GND    |                                                                                                            | Virego           | -0.3    | 2.8 Note5                           | V    |  |

| Digital input voltage        | P00 to P04, P17, P20 to P25, P31,<br>P40 to P43, P73 to P77, P120, P122,<br>P137, P140, P141, /RESET, TEST | Voi1             | -0.3    | VDD + 0.3                           | V    |  |

|                              | P60, P61 (Nch open-drain)                                                                                  | V <sub>DI2</sub> | -0.3    | 6.5                                 | V    |  |

| Output voltage               | P00 to P04, P17, P20 to P25, P31,<br>P40 to P43, P60, P61, P73 to P77,<br>P120, P140, P141, DA3O           | Vouт             | -0.3    | VDD + 0.3                           | V    |  |

| Analog input voltage         | ANI0 to ANI5, ANI16, ANI17, ANI19                                                                          | Vai1             | -0.3    | VDD + 0.3 and<br>AVREFP + 0.3 Note6 | V    |  |

Note1: Not subject to production test, specified at Ta=25°C by design

Note2: Power supply can be applied to VBRIDGE and VM pin independently.

Note3: VCP pin voltage with respect to HOx and HSx pins should be limited to 86V maximum.

This will limit the maximum VCPabs, minimum VHOxabs, VHSxabs, and maximum VGSHxabs when VBRIDGE is greater than 66V. For example, when VBRIDGE=78V, VCPabs=84V, and VHOxabs=VHSxabs=-2V, VGSHxabs should be limited to (84V - 78V) = 6V. In this example, VDRV pin voltage will be also limited to about 7V in consideration of the step-up voltage of the charge pump.

Note4: In case of VDRV<=7V, the maximum VHSxabs is limited to VBRIDGE + (VDRV-2V).

The maximum VHSxtran is also limited to VBRIDGE + VDRV.

Note5: Connect the REGC pin to GND\_MCU via a capacitor (0.47 to 1µF). This value regulates the absolute maximum rating of REGC pin. Do not use this pin with voltage applied to it.

Note6: Do not exceed AVREFP + 0.3V in case of A/D conversion target pin.

Caution: Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter

That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage,

and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

Remark1: Unless specified otherwise, the characteristics of alternate-function pins are same as those of the port pins.

$\label{lem:Remark2: AVREFP: positive side reference voltage of the A/D converter.}$

Remark3: The GND pin of each block is the followings.

Gate driver block: EPAD, Charge pump: EPAD, Analog blocks: AGND, MCU: GND\_MCU

# 5.1 Absolute Maximum Ratings (continued)

Table 5.1-2 Absolute Maximum Ratings (continued) Note1

|                          | ltem                                     | Symbol         | Minimum | Maximum | unit     |

|--------------------------|------------------------------------------|----------------|---------|---------|----------|

|                          | P00 to P04, P40 to P43, P120, P140, P141 | IDOH1          | -40     | -       | mA/pin   |

|                          |                                          | IDOH1A         | -70     | -       | mA total |

| Output current, high     | P17, P31, P73 to P77                     | IDOH2          | -40     | -       | mA/pin   |

|                          |                                          | IDOH2A         | -100    | -       | mA total |

|                          | P20 to P25                               | Іронз          | -0.5    | -       | mA/pin   |

|                          |                                          | Іронза         | -2      | -       | mA total |

|                          | P00 to P04, P40 to P43, P120, P140, P141 | IDOL1          | -       | 40      | mA/pin   |

|                          |                                          | IDOL1A         | -       | 70      | mA total |

| Output current, low      | P17, P31, P73 to P77                     | IDOL2          | -       | 40      | mA/pin   |

|                          |                                          | IDOL2A         | -       | 100     | mA total |

|                          | P20 to P25                               | lDOL3          | -       | 1       | mA/pin   |

|                          |                                          | <b>I</b> DOL3A | -       | 5       | mA total |

| Ambient temperature      |                                          | TA             | -40     | 105     | °C       |

| Junction temperature for | smart gate driver (RAA306012)            | TJ             | -40     | 150     | °C       |

| Storage temperature      |                                          | Tstg           | -65     | 150     | °C       |

Note1: Not subject to production test, specified at Ta=25°C by design

Caution: Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter

That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage,

and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

Remark1: Unless specified otherwise, the characteristics of alternate-function pins are same as those of the port pins.

Remark2: AVREFP: positive side reference voltage of the A/D converter.

Remark3: The GND pin of each block is the followings.

Gate driver block: EPAD, Charge pump: EPAD, Analog blocks: AGND, MCU: GND\_MCU

#### 5.2 Thermal Information

Table 5.2-1 Thermal Information

| Thermal resistance (Typical)       | θ <sub>JA</sub> [°C/W] | Ψ <sub>JT</sub> [°C/W] |

|------------------------------------|------------------------|------------------------|

| 8mm x 8mm 64Ld QFN Package Note1,2 | 21.4                   | 1.69                   |

Note1:  $\theta_{JA}$  is measured in free air with the component mounted on a high-effective thermal conductivity test board with "direct attach" features. See <u>TB379</u>.

Note2: For  $\Psi_{JT}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

## 5.3 Recommended Operating Conditions

Table 5.3-1 Recommended Operating Conditions

|                           | Item                                  | Symbol        | Minimum | Maximum             | unit |

|---------------------------|---------------------------------------|---------------|---------|---------------------|------|

| VBRIDGE to GND            |                                       | VBRIDGEope    | 6       | 65                  | V    |

| VM to GND                 |                                       | VMope         | 6       | 60                  | V    |

| VCC5V to GND              |                                       | VCCope        | 4.75    | 5.25                | V    |

| VDRV to GND               |                                       | VDRVope Note4 | 5       | 16                  | V    |

| VDD to GND                |                                       | VDDope        | 3.135   | 5.25                | V    |

| VDD_MCU to GND            | supplied from VCC5V                   | VMCUope1      | 4.75    | 5.25                | V    |

|                           | supplied from VDD                     | VMCUope2      | 3.135   | 3.465               | V    |

| External load current (VI | DD & VCC5V), Sleep Mode               | Ivdd0         | 0       | 50 Note3            | mA   |

| External load current (VI | DD & VCC5V), during start-up, LDO1=On | Ivdd1_0       | 0       | 70 <sup>Note3</sup> | mA   |

| External load current (VI | DD & VCC5V), Operating Mode           | Ivdd1_1       | 0       | 90 Note3            | mA   |

| Operating junction temper | erature                               | Tjope         | -40     | 125                 | °C   |

Note3: Power dissipation and thermal limits must be observed.

External load current is defined as the total of VCC5V and VDD load current including MCU supply current.

Note4: VDRV voltage must be set so that VCC5V voltage doesn't deviate from the recommended operating condition.

## 5.4 Electrical Characteristics

Regarding the electrical characteristics of the function implemented in RL78/G1F, please refer to "RL78/G1F User's Manual: Hardware" (R01UH0516EJ).

Note: All specifications are for Ta=25°C, VM=48V unless otherwise noted.

| <u> </u>                                 |           | 0 88                                                                   |       | Rated level |       | I bela |

|------------------------------------------|-----------|------------------------------------------------------------------------|-------|-------------|-------|--------|

| Parameter                                | Symbol    | Condition                                                              | MIN   | TYP         | MAX   | Unit   |

| Power supply (VM)                        | •         |                                                                        |       | ,           |       |        |

| VM Sleep Mode current                    | I∨MO      | HOx/LOx=Low/Low, No load on VDD                                        | -     | 28          | 44    | μA     |

| VM, VBRIDGE operating current (combined) | I∨м1      | Operating Mode, HOx/LOx=Low/Low, excluding MCU supply current          | -     | 2           | -     | mA     |

| VDRV operating current                   | Ivdrv1    | Operating Mode, HOx/LOx=Low/Low                                        | -     | 3.8         | -     | mA     |

| Sleep Mode entry time delay              | tsleep    | From internal EN trigger to Sleep Mode                                 | -     | 0.55        | 0.85  | ms     |

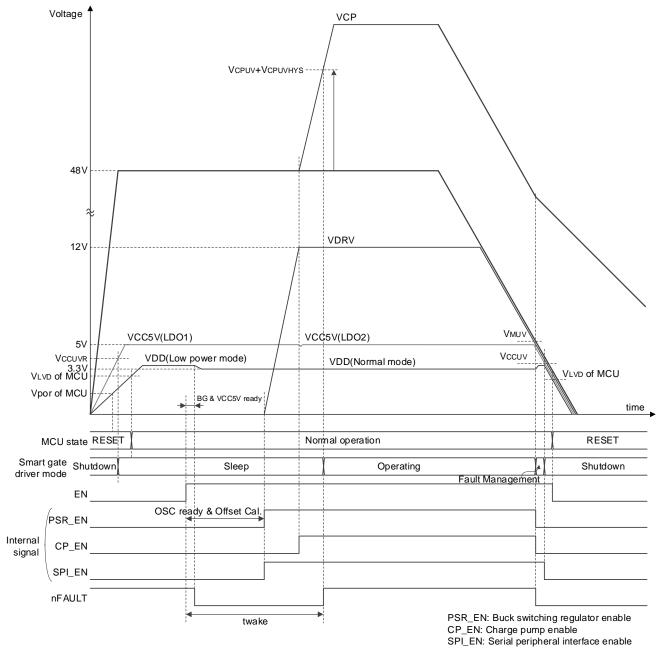

| Wake-up time delay                       | twake     | From internal EN trigger to All power rails ready, C2=2.2µF, C3=0.22µF | -     | 6.5         | -     | ms     |

| Power supply (VCC5V)                     |           |                                                                        |       |             |       |        |

| Output voltage                           | Vvcc0_1   | VM=60V, Sleep Mode, load=0mA                                           | -     | 5           | -     | V      |

|                                          | Vvcc0_2   | VM=36V, Sleep Mode, load=10mA                                          | -     | 5           | -     | V      |

|                                          | Vvcc0_3   | VM=6V, Sleep Mode, load=50mA                                           | 4.75  | 5           | -     | V      |

|                                          | Vvcc1_1   | VDRV=15V, Operating Mode, load=0.1mA                                   | -     | 5           | -     | V      |

|                                          | Vvcc1_2   | VDRV=12V, Operating Mode, load=40mA                                    | 4.85  | 5           | 5.15  | V      |

|                                          | Vvcc1_3   | VDRV=8V, Operating Mode, load=100mA                                    | -     | 5           | -     | V      |

| Current limit                            | Іьмтсс0_0 | VM=6V, Sleep Mode                                                      | 50    | 80          | -     | mA     |

|                                          | Іьмтсс0_1 | VM=36V, during start up, LDO1=On                                       | 80    | 130         | -     | mA     |

|                                          | Іьмтос1   | VDRV=12V, Operating Mode                                               | 100   | 160         | -     | mA     |

| Power supply (VDD)                       |           |                                                                        |       |             |       |        |

| Output voltage Note2                     | Vvdd0_1   | VM=60V, Sleep Mode, load=0mA                                           | -     | 3.3         | -     | V      |

|                                          | Vvdd0_2   | VM=36V, Sleep Mode, load=10mA                                          | -     | 3.3         | -     | V      |

|                                          | Vvdd0_3   | VM=6V, Sleep Mode, load=50mA                                           | 3.0   | 3.3         | -     | V      |

|                                          | Vvdd1_1   | VDRV=15V, Operating Mode, load=0.1mA                                   | -     | 3.3         | -     | V      |

|                                          | VvDd1_2   | VDRV=12V, Operating Mode, load=40mA                                    | 3.201 | 3.3         | 3.399 | V      |

|                                          | VvDd1_3   | VDRV=8V, Operating Mode, load=100mA                                    | -     | 3.3         | -     | V      |

| Current limit Note3                      | ILMTDD0   | VM=6V, Sleep Mode                                                      | 50    | 80          | -     | mA     |

|                                          | ILMTDD1_0 | VM=36V, during start-up, LDO1=On                                       | 80    | 130         | -     | mA     |

|                                          | ILMTDD1_1 | VDRV=12V, Operating Mode                                               | 100   | 160         | -     | mA     |

Note2: VDD specification does not apply when VDD LDO is not used by connecting FBLDO to VCC5V or VDD pin.

Note3: VDD current is limited by VCC5V current limit. These items are not tested.

# 5.4 Electrical Characteristics (continued)

Note: All specifications are for Ta=25°C, VM=48V unless otherwise noted.

| Parameter                                   | Symbol    | Condition                                          | MIN   | TYP   | MAX   | Unit          |

|---------------------------------------------|-----------|----------------------------------------------------|-------|-------|-------|---------------|

| Buck switching regulator (VDRV)             |           |                                                    |       |       |       |               |

| Output voltage adjustment range Note1       | Vdrv      |                                                    | 5     | -     | 15    | V             |

| Reference voltage                           | VREF_SR   |                                                    | 0.776 | 0.8   | 0.824 | V             |

| gm amplifier gain                           | gm_sr     |                                                    | -     | 200   | -     | μ <b>A</b> /V |

| gm amplifier output capability              | IgmSRC_SR |                                                    | -     | 18    | -     | μΑ            |

|                                             | IgmSNK_SR |                                                    | -     | -18   | -     | μA            |

| gm amplifier maximum output voltage         | VgmH_SR   | FB=0V                                              | -     | 3.95  | -     | V             |

| gm amplifier minimum output voltage         | VgmL_SR   | FB=1V                                              | -     | 0.02  | -     | V             |

| Ramp offset voltage                         | Vramp_SR  |                                                    | -     | 870   | -     | mV            |

| Oscillator frequency                        | fsw_sr    |                                                    | 400   | 500   | 575   | kHz           |

| Soft-start time                             | tss_sr    | Time to FB=0.8V                                    | -     | 2.2   | -     | ms            |

| Cycle-by-cycle current limit Note1          | IOC1_SR   |                                                    | -     | 1.2   | -     | А             |

| Hiccup current limit threshold Note1        | loc2_sr   |                                                    | -     | 1.4   | -     | А             |

| Charge pump (VCP)                           | •         |                                                    | •     |       |       |               |

| Output voltage with respect to VBRIDGE      | Vvcp_1    | VM=60V, VDRV=12V, load=15mA                        | -     | 11    | -     | V             |

|                                             | Vvcp_2    | VM=36V, VDRV=12V, load=15mA                        | -     | 11    | -     | V             |

|                                             | Vvcp_3    | VM=6V, VDRV=6V, load=15mA                          | 5.0   | 5.3   | -     | V             |

| Oscillator frequency                        | fsw_cp    |                                                    | -     | 250   | -     | kHz           |

| Maximum load current Note1                  | load_CP   |                                                    | 28    | -     | -     | mA            |

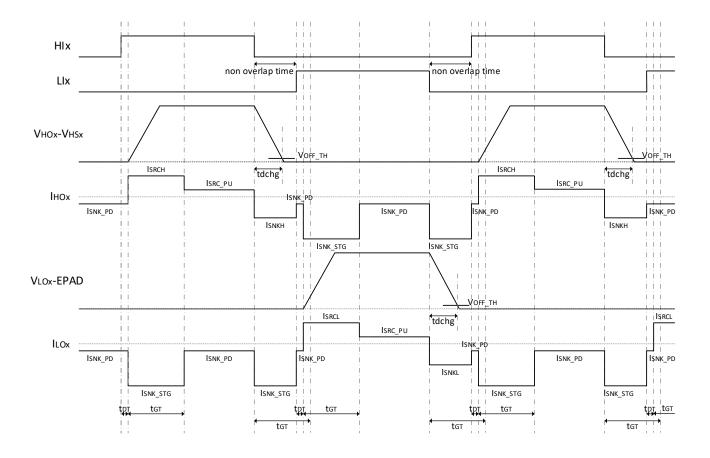

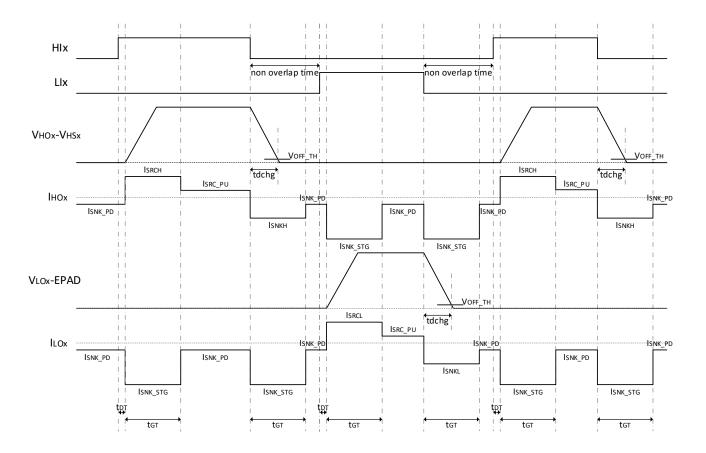

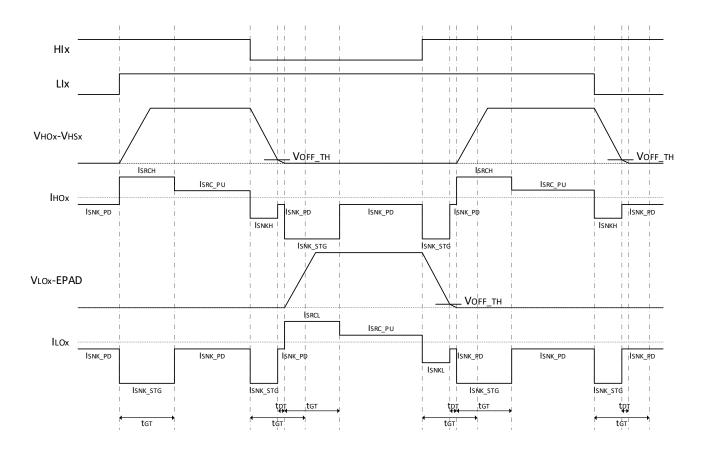

| Gate driver block (HOx, LOx (x=A,B,C))      | •         |                                                    | •     |       |       |               |

| High-side gate driver Output high voltage   | Vgshh     | Io=1mA, VDRV=12V, VM=HSx=24V, with respect to HSx  | -     | 11.45 | -     | V             |

| High-side gate driver<br>Output low voltage | VGSHL     | Io=-1mA, VDRV=12V, VM=HSx=24V, with respect to HSx | -     | 0.05  | -     | V             |

| Low-side gate driver<br>Output high voltage | Vgslh     | Io=1mA, VDRV=12V, VM=HSx=24V, with respect to GND  | -     | 11.95 | -     | V             |

| Low-side gate driver<br>Output low voltage  | VGSLL     | Io=-1mA, VDRV=12V, VM=HSx=24V, with respect to GND | -     | 0.05  | -     | V             |

| High-side gate clamp voltage Note1          | VCLMP     | Io=-1mA, with respect to HSx                       | 16.0  | 17.2  | 18.4  | V             |

| Gate pulldown resistance                    | Rpd       |                                                    | -     | 200   | -     | kΩ            |

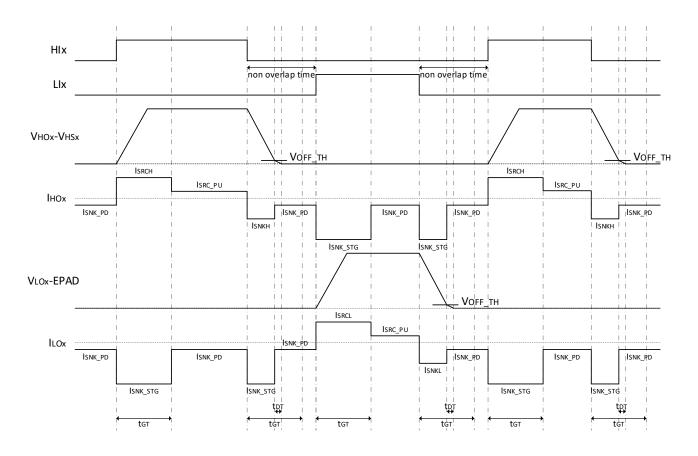

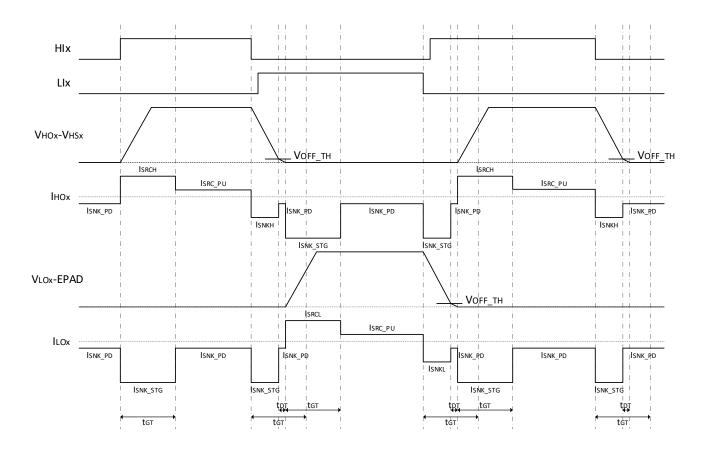

| Strong sink current Note1                   | ISNK_STG  |                                                    | -     | 1280  | -     | mA            |

| Pullup source current                       | Isrc_pu   |                                                    | -     | 50    | -     | mA            |

| Pulldown sink current                       | ISNK_PD   |                                                    | -     | 100   | -     | mA            |

$\label{lem:note1:this specification is not tested in production. Only functional test.}$

# 5.4 Electrical Characteristics (continued)

Note: All specifications are for Ta=25°C, VM=48V unless otherwise noted.

| _                                   |         |                 |     | Rated level |     |      |

|-------------------------------------|---------|-----------------|-----|-------------|-----|------|

| Parameter                           | Symbol  | Condition       | MIN | TYP         | MAX | Unit |

| Gate driver block (HOx (x=A,B,C))   |         |                 |     |             |     |      |

| High-side peak source current Note1 | Isrcho  | ISRC_HS[3:0]=0h | -   | 50          | -   | mA   |

|                                     | IsrcH1  | ISRC_HS[3:0]=1h | -   | 60          | -   | mA   |

|                                     | Isrch2  | ISRC_HS[3:0]=2h | -   | 70          | -   | mA   |

|                                     | IsrcH3  | ISRC_HS[3:0]=3h | -   | 80          | -   | mA   |

|                                     | ISRCH4  | ISRC_HS[3:0]=4h | -   | 100         | -   | mA   |

|                                     | Isrch5  | ISRC_HS[3:0]=5h | -   | 120         | -   | mA   |

|                                     | Isrch6  | ISRC_HS[3:0]=6h | -   | 140         | -   | mA   |

|                                     | Isrch7  | ISRC_HS[3:0]=7h | -   | 160         | -   | mA   |

|                                     | Isrch8  | ISRC_HS[3:0]=8h | -   | 200         | -   | mA   |

|                                     | IsrcH9  | ISRC_HS[3:0]=9h | -   | 240         | -   | mA   |

|                                     | IsrcH10 | ISRC_HS[3:0]=Ah | -   | 280         | -   | mA   |

|                                     | IsrcH11 | ISRC_HS[3:0]=Bh | -   | 320         | -   | mA   |

|                                     | ISRCH12 | ISRC_HS[3:0]=Ch | -   | 400         | -   | mA   |

|                                     | ISRCH13 | ISRC_HS[3:0]=Dh | -   | 480         | -   | mA   |

|                                     | ISRCH14 | ISRC_HS[3:0]=Eh | -   | 560         | -   | mA   |

|                                     | ISRCH15 | ISRC_HS[3:0]=Fh | -   | 640         | -   | mA   |

| High-side peak sink current Note1   | Isnkho  | ISRC_HS[3:0]=0h | -   | 100         | -   | mA   |

|                                     | IsnkH1  | ISRC_HS[3:0]=1h | -   | 120         | -   | mA   |

|                                     | Isnkh2  | ISRC_HS[3:0]=2h | -   | 140         | -   | mA   |

|                                     | IsnkH3  | ISRC_HS[3:0]=3h | -   | 160         | -   | mA   |

|                                     | IsnkH4  | ISRC_HS[3:0]=4h | -   | 200         | -   | mA   |

|                                     | Isnkh5  | ISRC_HS[3:0]=5h | -   | 240         | -   | mA   |

|                                     | IsnkH6  | ISRC_HS[3:0]=6h | -   | 280         | -   | mA   |

|                                     | Isnkh7  | ISRC_HS[3:0]=7h | -   | 320         | -   | mA   |

|                                     | Isnkh8  | ISRC_HS[3:0]=8h | -   | 400         | -   | mA   |

|                                     | IsnkH9  | ISRC_HS[3:0]=9h | -   | 480         | -   | mA   |

|                                     | IsnkH10 | ISRC_HS[3:0]=Ah | -   | 560         | -   | mA   |

|                                     | IsnkH11 | ISRC_HS[3:0]=Bh | -   | 640         | -   | mA   |

|                                     | ISNKH12 | ISRC_HS[3:0]=Ch | -   | 800         | -   | mA   |

|                                     | IsnkH13 | ISRC_HS[3:0]=Dh | -   | 960         | -   | mA   |

|                                     | IsnkH14 | ISRC_HS[3:0]=Eh | -   | 1120        | -   | mA   |

|                                     | ISNKH15 | ISRC_HS[3:0]=Fh | -   | 1280        | -   | mA   |

$\label{lem:note1:note2} \textbf{Note1: This specification is not tested in production. Only functional test.}$

# 5.4 Electrical Characteristics (continued)

Note: All specifications are for Ta=25°C, VM=48V unless otherwise noted.

| <u> </u>                           |         | 0 111           |     | Rated level |     |      |

|------------------------------------|---------|-----------------|-----|-------------|-----|------|

| Parameter                          | Symbol  | Condition       | MIN | TYP         | MAX | Unit |

| Gate driver block (LOx (x=A,B,C))  |         |                 |     |             |     |      |

| Low-side peak source current Note1 | ISRCL0  | ISRC_LS[3:0]=0h | -   | 50          | -   | mA   |

|                                    | ISRCL1  | ISRC_LS[3:0]=1h | -   | 60          | -   | mA   |

|                                    | ISRCL2  | ISRC_LS[3:0]=2h | -   | 70          | -   | mA   |

|                                    | ISRCL3  | ISRC_LS[3:0]=3h | -   | 80          | -   | mA   |

|                                    | ISRCL4  | ISRC_LS[3:0]=4h | -   | 100         | -   | mA   |

|                                    | ISRCL5  | ISRC_LS[3:0]=5h | -   | 120         | -   | mA   |

|                                    | ISRCL6  | ISRC_LS[3:0]=6h | -   | 140         | -   | mA   |

|                                    | ISRCL7  | ISRC_LS[3:0]=7h | -   | 160         | -   | mA   |

|                                    | ISRCL8  | ISRC_LS[3:0]=8h | -   | 200         | -   | mA   |

|                                    | ISRCL9  | ISRC_LS[3:0]=9h | -   | 240         | -   | mA   |

|                                    | ISRCL10 | ISRC_LS[3:0]=Ah | -   | 280         | -   | mA   |

|                                    | ISRCL11 | ISRC_LS[3:0]=Bh | -   | 320         | -   | mA   |

|                                    | ISRCL12 | ISRC_LS[3:0]=Ch | -   | 400         | -   | mA   |

|                                    | ISRCL13 | ISRC_LS[3:0]=Dh | -   | 480         | -   | mA   |

|                                    | ISRCL14 | ISRC_LS[3:0]=Eh | -   | 560         | -   | mA   |

|                                    | ISRCL15 | ISRC_LS[3:0]=Fh | -   | 640         | -   | mA   |

| Low-side peak sink current Note1   | Isnklo  | ISRC_LS[3:0]=0h | -   | 100         | -   | mA   |

|                                    | ISNKL1  | ISRC_LS[3:0]=1h | -   | 120         | -   | mA   |

|                                    | ISNKL2  | ISRC_LS[3:0]=2h | -   | 140         | -   | mA   |

|                                    | Isnkl3  | ISRC_LS[3:0]=3h | -   | 160         | -   | mA   |

|                                    | ISNKL4  | ISRC_LS[3:0]=4h | -   | 200         | -   | mA   |

|                                    | ISNKL5  | ISRC_LS[3:0]=5h | -   | 240         | -   | mA   |

|                                    | ISNKL6  | ISRC_LS[3:0]=6h | -   | 280         | -   | mA   |

|                                    | Isnkl7  | ISRC_LS[3:0]=7h | -   | 320         | -   | mA   |

|                                    | ISNKL8  | ISRC_LS[3:0]=8h | -   | 400         | -   | mA   |

|                                    | Isnkl9  | ISRC_LS[3:0]=9h | -   | 480         | -   | mA   |

|                                    | ISNKL10 | ISRC_LS[3:0]=Ah | -   | 560         | -   | mA   |

|                                    | ISNKL11 | ISRC_LS[3:0]=Bh | -   | 640         | -   | mA   |

|                                    | ISNKL12 | ISRC_LS[3:0]=Ch | -   | 800         | -   | mA   |

|                                    | ISNKL13 | ISRC_LS[3:0]=Dh | -   | 960         | -   | mA   |

|                                    | ISNKL14 | ISRC_LS[3:0]=Eh | -   | 1120        | -   | mA   |

|                                    | ISNKL15 | ISRC_LS[3:0]=Fh | -   | 1280        | -   | mA   |

$\label{lem:note1:note2} \textbf{Note1: This specification is not tested in production. Only functional test.}$

# 5.4 Electrical Characteristics (continued)

Note: All specifications are for Ta=25°C, VM=48V unless otherwise noted.

|                                                                 |                  | 0 151                                                    |      | Rated level |         | - Unit |

|-----------------------------------------------------------------|------------------|----------------------------------------------------------|------|-------------|---------|--------|

| Parameter                                                       | Symbol           | Condition                                                | MIN  | TYP         | MAX     |        |

| Gate driver block (HOx, LOx (x=A,B,C))                          | ļ                |                                                          |      |             |         |        |

| Adaptive dead time<br>VGs falling threshold <sup>Note1</sup>    | VTH_VGS          |                                                          | -    | 1           | -       | V      |

| Adaptive dead time<br>VGs threshold hysteresis <sup>Note1</sup> | VHYS_VGS         |                                                          | -    | 2           | -       | V      |

| Gate drive dead time                                            | t <sub>DT0</sub> | DEAD_TIME[1:0]=0h<br>from VTH_VGS to other-side ON       | -    | 50          | -       | ns     |

|                                                                 | t <sub>DT1</sub> | DEAD_TIME[1:0]=1h<br>from VTH_VGS to other-side ON       | -    | 100         | -       | ns     |

|                                                                 | tDT2             | DEAD_TIME[1:0]=2h<br>from VTH_VGS to other-side ON       | -    | 200         | -       | ns     |

|                                                                 | t <sub>DT3</sub> | DEAD_TIME[1:0]=3h<br>from VTH_VGS to other-side ON       | -    | 400         | -       | ns     |

| Maximum gate transition time                                    | tgT0             | T_GT[1:0]=0h from Source/Sink start to Pullup/down start | -    | 500         | -       | ns     |

|                                                                 | tgT1             | T_GT[1:0]=1h from Source/Sink start to Pullup/down start | -    | 1000        | -       | ns     |

|                                                                 | tgT2             | T_GT[1:0]=2h from Source/Sink start to Pullup/down start | -    | 2000        | -       | ns     |

|                                                                 | tgT3             | T_GT[1:0]=3h from Source/Sink start to Pullup/down start | -    | 4000        | -       | ns     |

| Propagation delay Note1                                         | tprop            | from PWM input trigger to HOx/LOx start                  | -    | 40          | -       | ns     |

| Differential amplifier (DAzP, DAzN, DAzO (                      | z=1,2,3))        |                                                          |      |             |         |        |

| Common mode input voltage range                                 | VIC_CSA          | DAzP, DAzN pin                                           | -0.5 | -           | 2.8     | V      |

| Differential mode input voltage range                           | VID_CSA          | DAzP - DAzN                                              | -0.5 | -           | 0.5     | V      |

| Input offset voltage                                            | VIO_CSA          | CAL_CONN=1                                               | -5   | -           | 5       | mV     |

| Output voltage linear range Note1                               | Vo_csa           |                                                          | 0.4  | -           | VDD-0.4 | V      |

| Amplifier gain                                                  | Gcsa0            | DAz_GAIN[1:0]=0h                                         | 4.85 | 5           | 5.15    | V/V    |

|                                                                 | GCSA1            | DAz_GAIN[1:0]=1h                                         | 9.7  | 10          | 10.3    | V/V    |

|                                                                 | GCSA2            | DAz_GAIN[1:0]=2h                                         | 19.4 | 20          | 20.6    | V/V    |

|                                                                 | GCSA3            | DAz_GAIN[1:0]=3h                                         | 38.8 | 40          | 41.2    | V/V    |

| Settling time to +/-1% Note1                                    | tset_csao        | DAz_GAIN[1:0]=0h                                         | -    | 250         | -       | ns     |

|                                                                 | tset_csa1        | DAz_GAIN[1:0]=1h                                         | -    | 300         | -       | ns     |

|                                                                 | tset_csa2        | DAz_GAIN[1:0]=2h                                         | -    | 400         | -       | ns     |

|                                                                 | <u> </u>         |                                                          |      |             |         |        |

Note1: This specification is not tested in production. Only functional test.

# 5.4 Electrical Characteristics (continued)

Note: All specifications are for Ta=25°C, VM=48V unless otherwise noted.

| BEMF sense amplifier (HSA, HSB, HSC, DA3O)  Common mode input voltage range Vic_  Differential mode input voltage range0 Vid_t  Differential mode input voltage range3 Vid_t  Output offset voltage0 Vid_t  Amplifier output voltage bias VREF  BEMF sense amplifier gain Gen | EMF  | Condition  HSA, HSB, HSC pin  HSA, HSB, HSC pin - VBRIDGE/2 | -2.5   | TYP   | MAX    | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------|--------|-------|--------|------|

| Common mode input voltage range VIC_ Differential mode input voltage range0 VID_I Differential mode input voltage range3 VID_I Output offset voltage0 VIO_I Output offset voltage3 VIO_I Amplifier output voltage bias VREF BEMF sense amplifier gain GER                     |      |                                                             | -2.5   |       |        |      |

| Differential mode input voltage range0 VID_t  Differential mode input voltage range3 VID_t  Output offset voltage0 VIO_t  Output offset voltage3 VIO_t  Amplifier output voltage bias VREF  BEMF sense amplifier gain GEN                                                     |      |                                                             | -2.5   |       |        |      |

| Differential mode input voltage range3  VID_1  Output offset voltage0  Vio_1  Output offset voltage3  Amplifier output voltage bias  VREF  BEMF sense amplifier gain  Gen                                                                                                     | MF0  | HSA, HSB, HSC pin - VBRIDGE/2                               |        | -     | VM+2.5 | V    |

| Output offset voltage0 Vio_t  Output offset voltage3 Vio_t  Amplifier output voltage bias VREF  BEMF sense amplifier gain GER                                                                                                                                                 |      | BEMF_GAIN[1:0]=0h                                           | -24    | -     | 24     | V    |

| Output offset voltage3  Amplifier output voltage bias  BEMF sense amplifier gain  Gen                                                                                                                                                                                         | EMF3 | HSA, HSB, HSC pin - VBRIDGE/2<br>BEMF_GAIN[1:0]=3h          | -1.2   | -     | 1.2    | V    |

| Amplifier output voltage bias VREF BEMF sense amplifier gain GE                                                                                                                                                                                                               | EMF0 | DA3O pin with respect to VDD/2<br>BEMF_GAIN[1:0]=0h         | -0.2   | -     | 0.2    | V    |

| BEMF sense amplifier gain GEN                                                                                                                                                                                                                                                 | EMF3 | DA3O pin with respect to VDD/2<br>BEMF_GAIN[1:0]=3h         | -0.3   | -     | 0.3    | V    |

|                                                                                                                                                                                                                                                                               | _EMF |                                                             | -      | VDD/2 | -      | V    |

|                                                                                                                                                                                                                                                                               | MF0  | BEMF_GAIN[1:0]=0h                                           | 0.0475 | 0.05  | 0.0525 | V/V  |

| Ger                                                                                                                                                                                                                                                                           | /IF1 | BEMF_GAIN[1:0]=1h                                           | 0.095  | 0.1   | 0.105  | V/V  |

| Gen                                                                                                                                                                                                                                                                           | /IF2 | BEMF_GAIN[1:0]=2h                                           | 0.475  | 0.5   | 0.525  | V/V  |

| Gen                                                                                                                                                                                                                                                                           | MF3  | BEMF_GAIN[1:0]=3h                                           | 0.95   | 1     | 1.05   | V/V  |

| Settling time to +/-1% Note1 tset_                                                                                                                                                                                                                                            | EMF0 | BEMF_GAIN[1:0]=0h                                           | -      | 350   | -      | ns   |

| tset_                                                                                                                                                                                                                                                                         | EMF1 | BEMF_GAIN[1:0]=1h                                           | -      | 400   | -      | ns   |

| tset_                                                                                                                                                                                                                                                                         | EMF2 | BEMF_GAIN[1:0]=2h                                           | -      | 500   | -      | ns   |

| tset_                                                                                                                                                                                                                                                                         | EMF3 | BEMF_GAIN[1:0]=3h                                           | -      | 1000  | -      | ns   |

| Comparator (CMPzO (z=1,2,3))                                                                                                                                                                                                                                                  |      | <u>'</u>                                                    |        |       |        |      |

| VTH_                                                                                                                                                                                                                                                                          | CMP1 | CMPz_VTH[3:0] =1h                                           | 0.173  | 0.206 | 0.221  | V    |

| VTH_                                                                                                                                                                                                                                                                          | CMP2 | CMPz_VTH[3:0] =2h                                           | 0.380  | 0.413 | 0.433  | V    |

| V <sub>TH</sub> _                                                                                                                                                                                                                                                             | CMP3 | CMPz_VTH[3:0] =3h                                           | 0.589  | 0.619 | 0.650  | V    |

| Threshold voltage V <sub>TH_0</sub>                                                                                                                                                                                                                                           | CMP4 | CMPz_VTH[3:0] =4h                                           | 0.784  | 0.825 | 0.866  | V    |

| for VDD=3.3V setting VTH_                                                                                                                                                                                                                                                     | CMP5 | CMPz_VTH[3:0] =5h                                           | 0.980  | 1.031 | 1.083  | V    |

| V <sub>TH</sub> _                                                                                                                                                                                                                                                             | CMP6 | CMPz_VTH[3:0] =6h                                           | 1.176  | 1.238 | 1.299  | V    |

| V <sub>TH</sub> _                                                                                                                                                                                                                                                             | CMP7 | CMPz_VTH[3:0] =7h                                           | 1.372  | 1.444 | 1.516  | V    |

| V <sub>TH_</sub>                                                                                                                                                                                                                                                              | CMP8 | CMPz_VTH[3:0] =8h                                           | 1.568  | 1.650 | 1.733  | V    |

| V <sub>TH</sub> _                                                                                                                                                                                                                                                             | CMP9 | CMPz_VTH[3:0] =9h                                           | 1.763  | 1.856 | 1.949  | V    |

| V <sub>TH_C</sub>                                                                                                                                                                                                                                                             | MP10 | CMPz_VTH[3:0] =Ah                                           | 1.959  | 2.063 | 2.166  | V    |

| V <sub>TH_C</sub>                                                                                                                                                                                                                                                             | MP11 | CMPz_VTH[3:0] =Bh                                           | 2.155  | 2.269 | 2.382  | V    |

| V <sub>TH_C</sub>                                                                                                                                                                                                                                                             | MP12 | CMPz_VTH[3:0] =Ch                                           | 2.351  | 2.475 | 2.599  | V    |

| V <sub>TH_</sub> C                                                                                                                                                                                                                                                            | MP13 | CMPz_VTH[3:0] =Dh                                           | 2.547  | 2.681 | 2.815  | V    |

| V <sub>TH_C</sub>                                                                                                                                                                                                                                                             | MP14 | CMPz_VTH[3:0] =Eh                                           | 2.743  | 2.888 | 3.032  | V    |

| V <sub>TH_C</sub>                                                                                                                                                                                                                                                             | MP15 | CMPz_VTH[3:0] =Fh                                           | 2.939  | 3.094 | 3.248  | V    |

| Hysteresis VHYS_                                                                                                                                                                                                                                                              |      | CMPz_HYS=0                                                  | -      | +/-44 | -      | mV   |

| VHYS                                                                                                                                                                                                                                                                          | CMP1 | CMPz_HYS=1                                                  | -      | 0     | -      | mV   |

| Comparator delay toly_                                                                                                                                                                                                                                                        | CMP  |                                                             | _      |       | 1      | μs   |

Note1: This specification is not tested in production. Only functional test.

#### **Electrical Characteristics (continued)** 5.4

Note: All specifications are for Ta=25°C, VM=48V unless otherwise noted.

| Dovometer                           | C) (mah a) | Condition                          |      | Rated level |      |      |

|-------------------------------------|------------|------------------------------------|------|-------------|------|------|

| Parameter                           | Symbol     | Symbol Condition                   |      | TYP         | MAX  | Unit |

| Fault management                    |            |                                    |      |             |      |      |

| VCC5V power-on-reset rising         | Vccuvr     |                                    | -    | 4.00        | -    | V    |

| VCC5V power-on-reset falling        | Vccuv      |                                    | -    | 3.63        | -    | V    |

| VM under voltage rising0            | Vvmuvr0    | VMUV_TH=0                          | 5.2  | 5.5         | 5.8  | V    |

| VM under voltage falling0           | Vvmuv0     | VMUV_TH=0                          | 5.0  | 5.3         | 5.6  | V    |

| VM under voltage rising1            | Vvmuvr1    | VMUV_TH=1                          | 7.38 | 7.78        | 8.18 | V    |

| VM under voltage falling1           | Vvmu∨1     | VMUV_TH=1                          | 7.1  | 7.5         | 7.9  | V    |

| VM over voltage rising              | Vvmov      |                                    | -    | 63          | -    | V    |

| VM over voltage falling             | Vvmovr     |                                    | -    | 60          | -    | V    |

| VDRV under voltage fault rising     | Vdrvuvr    |                                    | 4.2  | 4.4         | 4.6  | V    |