## RC32312, RC32308

FemtoClock®3 Jitter Attenuator and Multi-Frequency Clock Synthesizer

The RC32312/RC32308 is an ultra-low phase noise jitter attenuator, multi-frequency synthesizer, synchronous Ethernet synchronizer, and digitally controlled oscillator (DCO). This flexible, low-power device outputs clocks with 25fs RMS jitter supporting 112Gbps and 224Gbps SerDes.

This document provides programming information for software engineers to use the RC32312/RC32308.

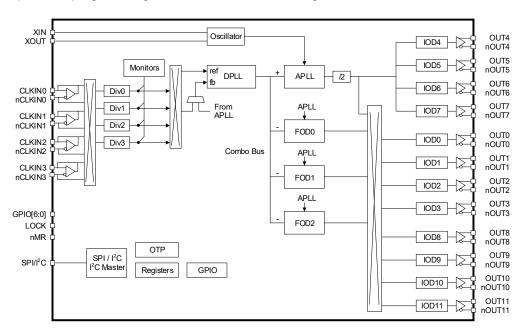

Figure 1. RC32312 Block Diagram

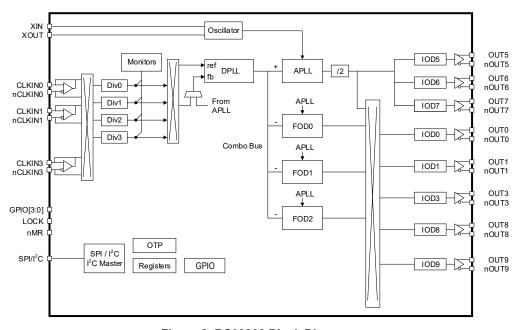

Figure 2. RC32308 Block Diagram

Note: Device specifications and ordering information are available in the RC32312/RC32308 Datasheet.

## **Contents**

| ۱. | Func  | tional De  | escription                                      | 8    |

|----|-------|------------|-------------------------------------------------|------|

|    | 1.1   | Overvie    | w                                               | 8    |

|    | 1.2   | Device l   | Frequency Reference                             | 8    |

|    | 1.3   | Analog     | PLL                                             | 9    |

|    | 1.4   | Fraction   | nal Output Dividers                             | 9    |

|    |       | 1.4.1      | FOD Synthesizer Mode                            | . 10 |

|    |       | 1.4.2      | FOD Digitally Controlled Oscillator Mode        | . 10 |

|    |       | 1.4.3      | FOD Synchronous Mode                            | . 10 |

|    | 1.5   | Divider    | Synchronization                                 | . 10 |

|    | 1.6   | DPLL R     | Reference Selection                             | . 11 |

|    |       | 1.6.1      | Manual Reference selection                      | . 11 |

|    |       | 1.6.2      | Automatic Reference Selection                   | . 11 |

|    |       | 1.6.3      | Aligned DPLL Reference Switching                | . 11 |

|    |       | 1.6.4      | Hitless DPLL Reference Switching                | . 11 |

|    |       | 1.6.5      | DPLL External Feedback                          | . 12 |

|    | 1.7   | Referen    | nce and Crystal Monitors                        | . 12 |

|    | 1.8   | Digital F  | PLL                                             | . 12 |

|    |       | 1.8.1      | Holdover Handler                                | . 13 |

|    |       | 1.8.2      | DPLL State Machine                              | . 14 |

|    |       | 1.8.3      | Freerun State                                   | . 14 |

|    |       | 1.8.4      | Normal State                                    | . 14 |

|    |       | 1.8.5      | Write Phase Mode                                | . 15 |

|    |       | 1.8.6      | Holdover State                                  | . 15 |

|    |       | 1.8.7      | Write Frequency State                           | . 16 |

|    |       | 1.8.8      | Acquire State                                   | . 16 |

|    |       | 1.8.9      | Hitless Switch State                            | . 17 |

|    | 1.9   | Clock O    | Output Paths                                    | . 17 |

|    |       | 1.9.1      | Integer Output Dividers                         |      |

|    |       | 1.9.2      | Clock Output Path for OUT[7:4]                  | . 18 |

|    |       | 1.9.3      | Output Clock Path for OUT[3:0] and OUT[11:8]    | . 18 |

|    |       | 1.9.4      | Clock Output Buffers                            | . 18 |

|    | 1.10  | Status a   | and Control                                     | . 19 |

|    | 1.11  | Power-0    | On Reset and Reset Controller                   | . 19 |

|    |       | 1.11.1     | Master Reset Sequence                           |      |

|    |       | 1.11.2     | Soft Reset Sequence                             | . 20 |

| 2. | Seria | l Interfac | ces                                             | . 22 |

|    | 2.1   |            |                                                 |      |

|    | 2.2   | 0 0        | ve                                              |      |

|    |       | 2.2.1      | I <sup>2</sup> C 1-byte (1B) Addressing Example |      |

|    |       | 2.2.2      | I <sup>2</sup> C 2-byte (2B) Addressing Example |      |

|    | 2.3   |            | ve                                              |      |

|    | -     | 2.3.1      | SPI 1-byte (1B) Addressing Example              |      |

|    |       | 2.3.2      | SPI 2-byte (2B) Addressing Example              |      |

| 3. | Post  |            |                                                 |      |

| ). | Regis |            |                                                 |      |

|    | 3.1   |            | L                                               |      |

|    |       | 3.1.1      | VENDOR ID                                       | . 28 |

|      | 3.1.2  | DEVICE_ID                             | 28 |

|------|--------|---------------------------------------|----|

|      | 3.1.3  | DEVICE_REV                            | 29 |

|      | 3.1.4  | DEVICE_PGM                            | 29 |

|      | 3.1.5  | DEVICE_CNFG                           | 29 |

|      | 3.1.6  | MISC_CNFG                             | 30 |

|      | 3.1.7  | SCRATCH_CNFG                          |    |

|      | 3.1.8  | MISC CTRL                             |    |

|      | 3.1.9  | STARTUP STS                           |    |

|      | 3.1.10 | DEVICE STS                            |    |

| 3.2  |        | · · · · · · · · · · · · · · · · · · · |    |

|      | 3.2.1  | INT_EN_CTRL                           |    |

|      | 3.2.2  | INT_STS                               |    |

| 3.3  |        |                                       |    |

| 0.0  | 3.3.1  | I2C_FLTR_CNFG                         |    |

|      | 3.3.2  | I2C_TIMING_CNFG.                      |    |

|      | 3.3.3  | I2C ADDR CNFG                         |    |

|      | 3.3.4  | SPI_CNFG                              |    |

|      | 3.3.5  | SSI GLOBAL CNFG.                      |    |

|      | 3.3.6  | SCL SCLK PAD CNFG                     |    |

|      | 3.3.7  |                                       |    |

|      |        | SDA_SDIO_PAD_CNFGSDO A1 PAD CNFG      |    |

|      | 3.3.8  |                                       |    |

|      | 3.3.9  | NCS_A0_PAD_CNFG                       |    |

|      | 3.3.10 | I2C_EVENT                             |    |

| 0.4  | 3.3.11 | I2C_CRC_ERR_CNT_EVENT                 |    |

| 3.4  |        |                                       |    |

|      | 3.4.1  | <del>-</del>                          |    |

| 3.5  |        | UF                                    |    |

|      | 3.5.1  | INPUT_CNFG                            |    |

| 3.6  |        | 1UX                                   |    |

|      | 3.6.1  | REF_SEL_CNFG                          |    |

| 3.7  |        | NV                                    |    |

|      | 3.7.1  | INPUT_DIV_CNFG                        |    |

| 3.8  | SYSDIV | ′                                     |    |

|      | 3.8.1  | SYS_DIV_INT_CNFG                      |    |

|      | 3.8.2  | COUNTER_1US_CNFG                      |    |

|      | 3.8.3  | SYS_DIV_EN_CTRL                       | 47 |

| 3.9  | GPIO . |                                       |    |

|      | 3.9.1  | GPIO_CNFG                             | 47 |

|      | 3.9.2  | GPIO_DEGLITCH_CNFG                    | 51 |

|      | 3.9.3  | GPIO_PAD_CNFG                         |    |

|      | 3.9.4  | GPIO_STS                              | 52 |

| 3.10 | OUTBU  | F                                     | 52 |

|      | 3.10.1 | OUT_CNFG                              | 52 |

|      | 3.10.2 | OUT_MODE_CNFG                         | 53 |

|      | 3.10.3 | OUT_HCSL_CMOS_CNFG                    |    |

|      | 3.10.4 | OUT_LVDS_CNFG                         |    |

|      | 3.10.5 | OUT_EN_CTRL                           |    |

|      | 3.10.6 | OUT SPARE                             |    |

| 3.11 |        | LL                                    |    |

|      |        |                                       |    |

|      | 3.11.1 | TDC_FB_DIV_INT_CNFG         | 56 |

|------|--------|-----------------------------|----|

|      | 3.11.2 | TDC_REF_DIV_CNFG            | 56 |

|      | 3.11.3 | TDC_ENABLE_CTRL             | 56 |

| 3.12 | XTALM  | ON                          | 57 |

|      | 3.12.1 | XTALMON_NOMINAL_MARGIN_CNFG | 57 |

|      | 3.12.2 | XTALMON_WINDOW_CNFG         | 57 |

|      | 3.12.3 | XTALMON_QUAL_CNFG           | 58 |

|      | 3.12.4 | XTALMON_CTRL                | 58 |

|      | 3.12.5 | XTALMON_EVENT               | 59 |

|      | 3.12.6 | XTALMON_CNT_EVENT           | 59 |

|      | 3.12.7 | XTALMON_STS                 | 59 |

| 3.13 | LOSMO  | N                           | 60 |

|      | 3.13.1 | LOSMON_NOMINAL_MARGIN_CNFG  | 60 |

|      | 3.13.2 | LOSMON_WINDOW_CNFG          | 60 |

|      | 3.13.3 | LOSMON_QUAL_CNFG            | 61 |

|      | 3.13.4 | LOSMON_CTRL                 | 61 |

|      | 3.13.5 | LOSMON_EVENT                | 62 |

|      | 3.13.6 | LOSMON_CNT_EVENT            | 62 |

|      | 3.13.7 | LOSMON_STS                  | 62 |

| 3.14 | FREQM  | ON                          | 63 |

|      | 3.14.1 | FREQMON_WINDOW_CNFG         | 63 |

|      | 3.14.2 | FREQMON_NOMINAL_CNFG        |    |

|      | 3.14.3 | FREQMON_MARGIN_CNFG         | 64 |

|      | 3.14.4 | FREQMON_CTRL                | 64 |

|      | 3.14.5 | FREQMON_EVENT               |    |

|      | 3.14.6 | FREQMON_STS                 | 65 |

| 3.15 | APLL   |                             |    |

|      | 3.15.1 | APLL_DCD_SDM_CNFG           |    |

|      | 3.15.2 | APLL_FB_DIV_FRAC_CNFG       |    |

|      | 3.15.3 | APLL_FB_DIV_INT_CNFG        |    |

|      | 3.15.4 | APLL_DCD_CAL_CNFG           |    |

| 3.16 |        |                             |    |

|      | 3.16.1 | IOD_DIV_CNFG                |    |

|      | 3.16.2 | IOD_PHASE_CNFG              |    |

|      | 3.16.3 | IOD_CNFG                    |    |

|      | 3.16.4 | IOD_EN_CTRL                 |    |

|      | 3.16.5 | IOD_PHASE_EN_CTRL           |    |

| 3.17 |        |                             |    |

|      | 3.17.1 | FOD_CNFG                    |    |

|      | 3.17.2 | FOD_PHASE_CNFG              |    |

|      | 3.17.3 | FOD_NUM_CNFG                |    |

|      | 3.17.4 | FOD_DEN_CNFG                |    |

|      | 3.17.5 | FOD_DIV_CNFG                |    |

|      | 3.17.6 | FOD_EN_CTRL                 |    |

|      | 3.17.7 | FOD_PHASE_EN_CTRL           |    |

|      | 3.17.8 | FOD_WRITE_FREQ_CTRL         |    |

| 3.18 |        |                             |    |

|      | 3.18.1 | DPLL_REF_FB_CNFG            |    |

|      | 3.18.2 | DPLL_REF_PRIORITY_CNFG      | 74 |

|    |       | 3.18.3    | DPLL_MODE_CNFG                | 76 |

|----|-------|-----------|-------------------------------|----|

|    |       | 3.18.4    | DPLL_XTAL_OFFSET_CNFG         | 77 |

|    |       | 3.18.5    | DPLL_DECIMATOR_CNFG           | 77 |

|    |       | 3.18.6    | DPLL_BANDWIDTH_CNFG           | 78 |

|    |       | 3.18.7    | DPLL_DAMPING_CNFG             | 78 |

|    |       | 3.18.8    | DPLL_PHASE_SLOPE_LIMIT_CNFG   | 79 |

|    |       | 3.18.9    | DPLL_HOLDOVER_CNFG            | 79 |

|    |       | 3.18.10   | DPLL_INTEGRATOR_LIMIT_CNFG    | 79 |

|    |       | 3.18.11   | DPLL_HS_CNFG                  | 80 |

|    |       | 3.18.12   | DPLL_WR_FREQ_PHASE_TIMER_CNFG | 80 |

|    |       | 3.18.13   | DPLL_PHASE_OFFSET_CNFG        | 81 |

|    |       | 3.18.14   | DPLL_FB_DIV_NUM_CNFG          | 82 |

|    |       | 3.18.15   | DPLL_FB_DIV_DEN_CNFG          | 82 |

|    |       | 3.18.16   | DPLL_FB_DIV_INT_CNFG          | 82 |

|    |       | 3.18.17   | DPLL_FB_CORR_CNFG             | 83 |

|    |       | 3.18.18   | DPLL_LOCK_CNFG                | 83 |

|    |       | 3.18.19   | DPLL_CTRL                     | 84 |

|    |       | 3.18.20   | DPLL_HOLDOVER_CTRL            | 84 |

|    |       | 3.18.21   | DPLL_HS_CTRL                  | 84 |

|    |       | 3.18.22   | DPLL_FILTER_DIS_CTRL          | 85 |

|    |       | 3.18.23   | DPLL_WR_PHASE_CTRL            | 85 |

|    |       |           | DPLL_WR_FREQ_CTRL             |    |

|    |       |           | DPLL_TIMED_WR_FREQ_CTRL       |    |

|    |       | 3.18.26   | DPLL_EVENT                    | 86 |

|    |       | 3.18.27   | DPLL_STS                      | 86 |

|    |       | 3.18.28   | DPLL_LOL_CNT_STS              | 87 |

|    |       | 3.18.29   | DPLL_WR_FREQ_PHASE_TIMER_STS  | 87 |

|    |       | 3.18.30   | DPLL_FILTER_STS               | 87 |

|    |       | 3.18.31   | DPLL_PHASE_STS                | 88 |

|    | 3.19  | EEPROI    | М                             | 88 |

|    |       | 3.19.1    | EEPROM_CNFG                   | 88 |

|    |       | 3.19.2    | EEPROM_ADDR_CNFG              | 90 |

|    |       | 3.19.3    | EEPROM_EVENT                  | 90 |

|    |       | 3.19.4    | EEPROM_ERR_CNT_EVENT          | 90 |

| 1. | Revis | sion Hist | ory                           | 91 |

|    |       |           |                               |    |

# **Figures**

| Figure 1. RC32312 Block Diagram                                       | 1    |

|-----------------------------------------------------------------------|------|

| Figure 2. RC32308 Block Diagram                                       | 1    |

| Figure 3. RC32312 Functional Block Diagram                            | 8    |

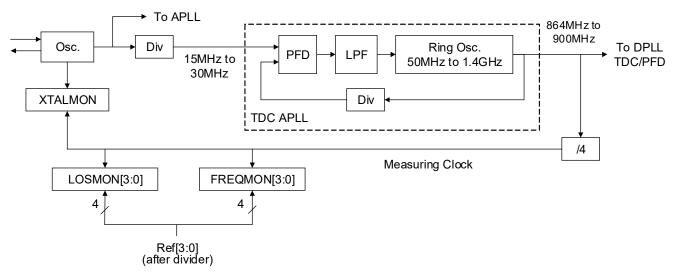

| Figure 4. Clock Monitors and TDC APLL                                 | . 12 |

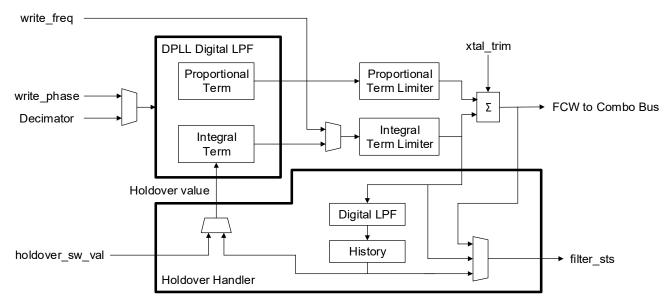

| Figure 5. DPLL Digital Low-pass Filter, Limiters and Holdover Handler | . 13 |

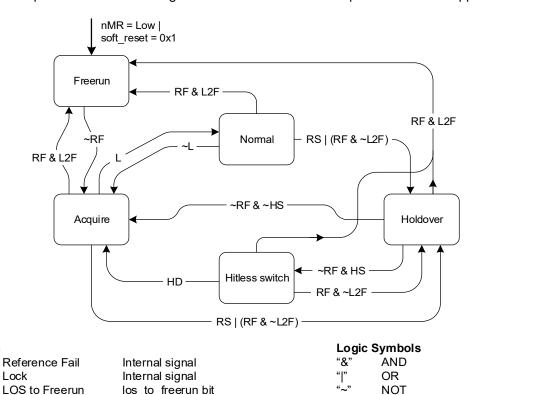

| Figure 6. DPLL State Machine in Automatic Mode                        | . 15 |

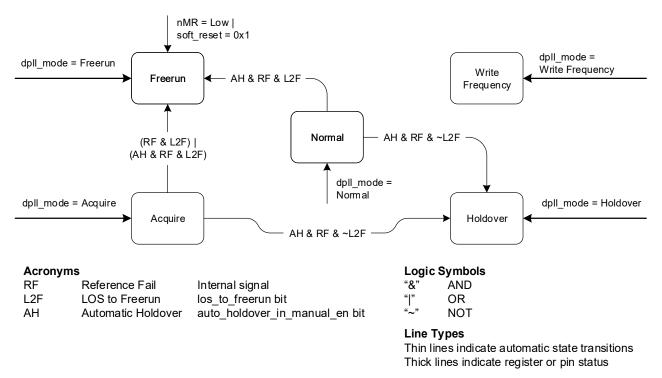

| Figure 7. DPLL State Machine in Manual Mode                           | . 16 |

| Figure 8. Clock Path for OUT[7:4]                                     | . 18 |

| Figure 9. Clock Path for OUT[3:0] and OUT[11:8]                       | . 18 |

| Figure 10. Master Reset Sequence Initiation                           | . 19 |

| Figure 11. Register Addressing Modes Using Serial Port                | . 22 |

| Figure 12. I2C Slave Sequencing                                       | . 23 |

| Figure 13. SPI Sequencing                                             | . 24 |

# **Tables**

| Table 1. FOD Modes and Division Types | 9  |

|---------------------------------------|----|

| Table 2. Reference Selection by Pin   | 11 |

| Table 3. DPLL States and Modes        | 14 |

| Table 4. Register Index               | 26 |

| Table 5. GLOBAL Register Index        | 28 |

| Table 6. INT Register Index           | 33 |

| Table 7. SSI Register Index           | 37 |

| Table 8. XO Register Index            | 42 |

| Table 9. INPUTBUF Register Index      | 42 |

| Table 10. INPUTMUX Register Index     | 43 |

| Table 11. INPUTDIV Register Index     | 45 |

| Table 12. SYSDIV Register Index       | 46 |

| Table 13. GPIO Register Index         | 47 |

| Table 14. OUTBUF Register Index       | 52 |

| Table 15. TDCAPLL Register Index      | 56 |

| Table 16. XTALMON Register Index      | 57 |

| Table 17. LOSMON Register Index       | 60 |

| Table 18. FREQMON Register Index      | 63 |

| Table 19. APLL Register Index         | 65 |

| Table 20. IOD Register Index          | 67 |

| Table 21. FOD Register Index          | 69 |

| Table 22. DPLL Register Index         | 72 |

| Table 23. EEPROM Register Index       | 88 |

## 1. Functional Description

### 1.1 Overview

The RC32312/RC32308 is an ultra-low phase noise jitter attenuator, multi-frequency synthesizer, synchronous Ethernet synchronizer, and digitally controlled oscillator (DCO). This flexible, low-power device outputs clocks with 25fs RMS jitter supporting 112Gbps and 224Gbps SerDes.

The RC32312 has four differential clock inputs (CLKINx) and 12 differential clock outputs (OUTx). The RC32308 has three differential clock inputs (CLKINx) and eight differential clock outputs. Both devices provide a digital PLL (DPLL), an ultra-low phase noise synthesizer based on an analog PLL (APLL), and three low-phase noise synthesizers based on fractional output dividers (FOD). See Figure 1 for a block diagram of the RC32312, and see Figure 2 for a block diagram of the RC32308.

Each CLKINx can be configured as two single-ended inputs (CLKINx and nCLKINx). The clock inputs can operate at frequencies up to 1GHz when differential, and up to 250MHz when single-ended. Each OUTx can be configured as LVDS or HCSL outputs that can operate at frequencies up to 1GHz. Each OUTx can be configured as two LVCMOS outputs (OUTx and nOUTx) that can operate at frequencies up to 250MHz. When configured for LVCMOS, the OUTx and nOUTx pins can operate in-phase or 180° out-of-phase.

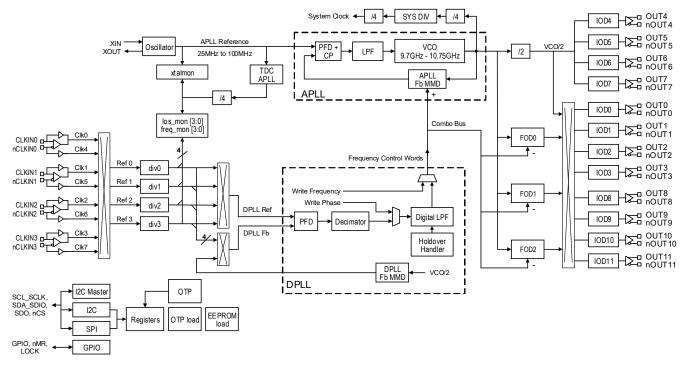

Figure 3 shows a detailed functional block diagram of RC32312. This diagram is also representative of the RC32308's architecture.

Figure 3. RC32312 Functional Block Diagram

### 1.2 Device Frequency Reference

The RC32312/RC32308 requires a frequency reference. The frequency reference can be implemented with an external crystal resonator and the device oscillator circuitry; or with an external oscillator. If a crystal resonator is used it must be connected between the XIN and XOUT pins. If an external oscillator is used it must be connected to the XIN pin so that it overdrives the device oscillator circuitry. For more information, see the tables titled "Crystal Oscillator Input and APLL AC/DC Electrical Characteristics" and "Recommended Crystal Characteristics" in the RC32312/RC32308 Datasheet.

The device frequency reference must support the phase noise, frequency accuracy, and frequency stability requirements of the intended application. The phase noise of the frequency reference affects the phase noise of clocks output by the device.

For DPLL applications, the accuracy of the frequency reference determines the frequency accuracy of the reference monitors and freerun clocks. The stability of the frequency reference determines the holdover stability of the DPLL and it affects the lowest filtering bandwidth the DPLL can support.

For DCO applications, the accuracy of the frequency reference determines the frequency accuracy of the freerun clocks. The stability of the frequency reference determines the stability of the DCO clocks when a source of synchronization is not available, and it affects the lowest filtering bandwidth the system can support.

### 1.3 Analog PLL

The APLL is configured using registers in the APLL section.

The internal APLL locks to the device frequency reference and generates an ultra-low phase noise clock of virtually any frequency between 9.70GHz and 10.75GHz. The voltage controlled oscillator (VCO) is the synthesizer for the APLL and it outputs a frequency equal to the APLL reference frequency multiplied by the APLL feedback divide ratio. The APLL feedback divide ratio is programmed as indicated in the following equation using the following register fields: apll fb div int and apll fb div frac.

$$APLL \ feedback \ divide \ ratio = \left(apII\_fb\_div\_int[9:0] + \frac{apII\_fb\_div\_frac[37:0]}{2^{38}}\right)$$

The APLL is the source of the DPLL feedback clock (VCO/2), and the DPLL steers the FFO of the APLL using frequency control words (FCW) as shown in the following equation (see also Figure 3). When the DPLL is in the Write Frequency State, the FCW is controlled by the write\_freq register field. When the DPLL is in the Write Phase Mode, the FCW is the result of the values written to the write\_phase register field after filtering by the DPLL low-pass filter.

$$APLL \ feedback \ divide \ ratio = \bigg(apII\_fb\_div\_int[9:0] + \frac{apII\_fb\_div\_frac[37:0]}{2^{38}}\bigg)x\bigg(1 + \frac{FCW}{2^{44}}\bigg)$$

The VCO clock is pre-divided by 2 and is available as an input to the integer output dividers (IOD). The pre-divided VCO clock is available directly to IOD[7:4], it is also available, via cross connect, to IOD[3:0] and IOD[11:8]. The undivided VCO clock is supplied to FOD[3:0].

## 1.4 Fractional Output Dividers

The FODs are configured using registers in the FOD section.

The FODs synthesize low-phase noise clocks with programmable frequencies by dividing the VCO clock using integer and fractional division. The FOD output clocks are available, via cross connect, to IOD[3:0] and IOD[11:8].

The FODs have the following three modes of operation: synthesizer mode, DCO mode, and synchronous mode. All three FOD modes divide the VCO clock, the three modes differ in their intended applications, how the divide ratios are specified and how the FOD follows frequency steering applied to the VCO. The FOD mode is selected using the fod sync mode and fod integer mode register bits as indicated in Table 1.

FOD Mode

Division Type

fod\_sync\_mode

fod\_integer\_mode

Synthesizer / DCO

Fractional

0x0

0x0

Synchronous

Fractional

0x1

0x0

Integer

X

0x1

Table 1. FOD Modes and Division Types

### 1.4.1 FOD Synthesizer Mode

In synthesizer mode, an FOD divides the VCO frequency by a static value comprised of an integer plus a fraction. In this mode an FOD can translate the VCO frequency to virtually any frequency within the FOD frequency range with 0.9 parts per trillion (PPT) FFO vs the VCO frequency. In synthesizer mode the FOD divide ratio is programmed using the fod div integer, and fod div fraction register fields as indicated in the following equation.

FOD divide ratio =

$$\left( \text{fod\_div\_integer}[48:40] + \frac{\text{fod\_div\_fraction}[39:0]}{2^{40}} \right)$$

An FOD in synthesizer mode will counteract digital frequency steering applied to the VCO by the DPLL, or by external software via the write\_phase or write\_freq register field. In this way an FOD based synthesizer is virtually unaffected by digital frequency steering applied to the VCO.

### 1.4.2 FOD Digitally Controlled Oscillator Mode

In DCO mode, an FOD synthesizes a nominal frequency in the same way as the synthesizer mode, and it allows external software to dynamically steer the nominal frequency with 44-bit (0.05 PPT) resolution over a range of ±244 PPM. In DCO mode the nominal FOD divide ratio is programmed using the fod\_div\_integer, and fod\_div\_fraction register fields, and the divide ratio is dynamically steered using the fod\_write\_freq register field, see the following equation.

$$FOD \ divide \ ratio = \left(fod\_div\_integer[48:40] + \frac{fod\_div\_fraction[39:0]}{2^{40}}\right) \times \left(1 + \frac{fod\_write\_freq[32:0]}{2^{44}}\right) = \left(1 + \frac{fod\_write\_freq[32:0]}{2^{44}}\right) + \frac{fod\_div\_fraction[39:0]}{2^{44}} + \frac{fod\_div\_fraction[39:0]}{2^{44}} + \frac{fod\_write\_freq[32:0]}{2^{44}} + \frac{fod\_write\_freq[32:0]}{2^{44}} + \frac{fod\_div\_fraction[39:0]}{2^{44}} + \frac{fod\_write\_freq[32:0]}{2^{44}} + \frac{fod\_write\_freq[32:0]}{2^{44}$$

An FOD in DCO mode will counteract digital frequency steering applied to the VCO by the DPLL, or by external software via the write\_phase or write\_freq register field. In this way an FOD based DCO is virtually unaffected by digital frequency steering applied to the VCO.

### 1.4.3 FOD Synchronous Mode

In synchronous mode, the FOD divides the VCO frequency by a static value comprised of an integer plus a fraction. The synchronous mode is capable of translating many common VCO frequencies to many common FOD frequencies with zero PPT FFO vs the VCO frequency. The FOD divide ratio in synchronous mode is programmed using the fod\_div\_integer, fod\_div\_fraction, fod\_div\_numerator, and fod\_div\_denominator register fields as indicated in the following equation.

$$FOD \ divide \ ratio = \left( fod\_div\_integer[48:40] + \frac{fod\_div\_fraction[15:0] + \left( \frac{(fod\_div\_numerator[39:0])}{(fod\_div\_denominator[39:0])} \right)}{2^{16}} \right) = \frac{10^{-10}}{2^{16}}$$

The synchronous mode has an integer sub-mode that is optimized for lowest phase noise integer division. An FOD can be configured for synchronous integer division by writing setting fod\_integer\_mode = 0x1 (see Table 1). In this mode the FOD divide ratio is programmed using the fod\_div\_integer register field as indicated in the following equation.

An FOD in synchronous mode will faithfully follow frequency steering applied to the VCO by the DPLL, or by external software via the write\_phase or write\_freq register field, or by steering the device frequency reference (e.g., a VCXO overdriving the XIN pin).

## 1.5 Divider Synchronization

The IODs, FODs, and DPLL feedback divider are automatically synchronized after the device is configured on startup, and can be manually synchronized by setting divider\_sync = 0x1; or by setting apll\_reinit = 0x1 (for more information, see Soft Reset Sequence). Re-synchronizing the dividers ensures a deterministic input to output phase relationship for DPLL mode.

### 1.6 DPLL Reference Selection

The DPLL can lock to any of the clock input references Ref 0, Ref 1, Ref 2, or Ref 3. The reference selection can be manual or automatic as determined the dpll ref sel mode register field.

#### 1.6.1 Manual Reference selection

For manual reference selection, the reference is selected by register or by pin as determined by the dpll ref sel mode register field.

In the case of selection by register, the reference is selected using the dpll\_ref\_sel register field.

In the case of selection by pin, the reference is selected according to Table 2 using the two pins assigned as DPLL REFIN\_SEL[0] and DPLL REFIN\_SEL[1] in the gpio\_func register field. If DPLL REFIN\_SEL[0] or DPLL REFIN\_SEL[1] is not assigned to a pin then is given a value of 0.

| REFIN_SEL[0] | REFIN_SEL[1] | Selected Reference |

|--------------|--------------|--------------------|

| 0            | 0            | Ref 0              |

| 0            | 1            | Ref 1              |

| 1            | 0            | Ref 2              |

| 1            | 1            | Ref 3              |

Table 2. Reference Selection by Pin

#### 1.6.2 Automatic Reference Selection

For automatic reference selection, the reference is selected based on clock quality status and priority. The quality status is provided by the clock monitors. The priorities can be re-programmed in the <a href="mailto:DPLL\_REF\_PRIORITY\_CNFG">DPLL\_REF\_PRIORITY\_CNFG</a> register fields. If two clock inputs are programmed to the same priority, the one with the lower index number takes precedence (e.g., Ref0 takes precedence over Ref1).

Automatic reference selection can be revertive or non-revertive as determined by the <a href="mailto:dpll\_revertive\_en">dpll\_revertive\_en</a> register field.

In revertive mode, the qualified reference with the highest priority is always selected. If a reference of higher priority than the currently selected reference becomes qualified, the DPLL will switch to that reference. If a reference clock of equal or lower priority than the currently selected one becomes qualified, the DPLL will continue with the current reference.

In non-revertive mode, when a reference with higher priority than the current reference changes status from disqualified to qualified the DPLL will continue with current reference unless the current reference becomes disqualified. If the current reference becomes disqualified then the DPLL will select the highest priority qualified reference available.

### 1.6.3 Aligned DPLL Reference Switching

Aligned reference switching is the natural behavior of a DPLL. The DPLL will act to close a phase offset between the selected reference and the feedback clock. A step change in the phase difference can occur when a new reference is selected while the DPLL is in the Acquire State or the Normal State, or when the DPLL exits the Holdover State and enters the Acquire State. The resulting phase transient is filtered by the DPLL loop filter and the phase slope limiter, and there will not be any sudden phase steps or glitches on the device outputs.

Aligned reference switching should be used for applications that require a known phase relationship between the DPLL reference and the output clocks.

#### 1.6.4 Hitless DPLL Reference Switching

Hitless reference switching causes the DPLL to ignore the initial phase offset between a newly selected reference and the DPLL feedback clock so that the DPLL can lock to the new reference with a minimal phase transient.

Hitless reference switching is enabled by setting dpll\_hitless\_en = 0x1. Hitless reference switching requires the Hitless Switch State which is available only when the DPLL state machine is in the automatic mode (see Table 3).

A hitless reference switch event begins when the DPLL is in the Holdover State; the event is triggered according to the logic shown in Figure 6. The DPLL measures the phase offset between the selected reference and the DPLL feedback clock. The measured hitless switching phase offset is stored and is subtracted from later phase offsets measured by the DPLL phase detector (for more information, see the Hitless Switch State). The hitless switching phase offset can be cleared by setting hs offset clr b = 0x0.

If there is an FFO between the newly selected reference and the DPLL holdover frequency then a phase transient will occur while the DPLL is in the Acquire State regardless of the hitless reference switching process.

When hitless switching is enabled, the DPLL\_PHASE\_OFFSET\_CNFG register fields are ignored by the DPLL and only the hitless switching phase offset affects the input-output phase offset. When hitless switching is disabled (dpll hitless en = 0x0), the hitless switching phase offset is set to zero.

Hitless reference switching does not allow a known phase relationship to exist between the DPLL reference and its output clocks. Hitless reference switching should not be enabled for applications that require a known phase relationship between the DPLL reference and the output clocks.

#### 1.6.5 DPLL External Feedback

In some applications it is useful to use an external feedback path for the DPLL. The dpll\_fb\_sel register field can be used to select one of the input clock references as the DPLL feedback clock. When external feedback is used, the feedback clock must have the same frequency as the selected DPLL reference.

When external feedback is used, power consumption can be reduced by setting dpll\_fb\_div\_dis = 0x1 to disable the DPLL feedback divider.

## 1.7 Reference and Crystal Monitors

The reference monitors are configured using the XTALMON, LOSMON, and FREQMON registers.

Figure 4. Clock Monitors and TDC APLL

### 1.8 Digital PLL

The DPLL is configured using registers in the DPLL section.

Up to four of the clock inputs can be selected as inputs for the reference monitors and the DPLL reference selection multiplexer. The DPLL can lock to reference frequencies from 1kHz to 33MHz; clock inputs with frequencies above 33MHz must be divided using the internal reference dividers. The DPLL steers the APLL using digital frequency control words (FCW) via the Combo Bus.

The DPLL FCWs are relative to the device frequency reference; when the FCW is zero the VCO FFO vs. the frequency reference is zero. The FCW is the sum of the proportional term and the integral term output by the DPLL digital low-pass filter and the xtal\_trim register field (see Figure 5). The integral term represents a time average of the VCO FFO. The proportional term represents the short-term changes of the VCO FFO due to tracking jitter and phase transients on the selected clock input reference.

The DPLL implements a programmable limiter for the magnitude of the proportional term (see <a href="phase\_slope\_limit">phase\_slope\_limit</a>). This limiter can be used to control the rate of phase change when the DPLL switches between two references with the same FFO. The DPLL also implements a limiter for the magnitude of the integral term (see <a href="integrator\_limit">integrator\_limit</a>). This limiter can be used to prevent the holdover value from being pulled outside specified limits during a locking transient. Both limiters are shown in <a href="Figure 5">Figure 5</a>.

The xtal\_trim register field allows host software to apply an FFO to the device frequency reference. The xtal\_trim field can be used to improve the frequency accuracy in the Freerun State by compensating for a known FFO of the frequency reference; note that the reference monitors are not affected by this compensation.

Figure 5. DPLL Digital Low-pass Filter, Limiters and Holdover Handler

#### 1.8.1 Holdover Handler

The Holdover Handler processes the DPLL integral term and determines the holdover value that is restored to the DPLL integrator when the DPLL enters the Holdover State (see Figure 5).

The Holdover Handler filters the DPLL integrator term with a bypassable digital low-pass filter. The bandwidth of the holdover filter is determined by the holdover\_bw\_shift and holdover\_bw\_mult register fields. The holdover filter does not affect the DPLL transfer function.

The holdover filter can be cleared by writing 0x1 to the holdover\_filter\_rst bit; this will cause it to be loaded with the current integrator term. Writing 0x0 to the holdover\_filter\_rst bit will cause the holdover filter to resume filtering.

The Holdover Handler stores the filtered value in two holdover history registers, alternating between them. The update interval for the holdover history registers is defined by the holdover\_history register field. When the DPLL enters the Holdover State, the oldest history register value is selected to be restored to the DPLL integrator.

The holdover history can be cleared by writing 0x1 to the holdover\_filter\_rst bit. This can only be done when the DPLL is not already in the Holdover State.

Host software can override the holdover value processed by the Holdover Handler by writing a holdover value in the holdover sw val register field and setting the manual holdover bit.

The Holdover Handler makes the following values available to host software via the filter\_sts register field: the current integral term, the current sum of the proportional and integral terms, and the oldest holdover history value. The value selected is determined by the filter status sel register field.

#### 1.8.2 DPLL State Machine

The DPLL can operate in any of six states: Freerun State, Normal State, Holdover State, Write Frequency State, Acquire State, and Hitless Switch State; while in the Normal state or the Acquire state it can also operate in the Write Phase Mode. The state or mode of the DPLL is controlled by the dpll\_en register bit and the dpll\_mode register field as shown in Table 3. The Hitless Switch State is part of the automatic state machine; the DPLL cannot be specifically forced into this state by host software.

The current DPLL state is indicated by the dpll\_state\_sts register field. DPLL state changes can be monitored using the dpll\_state\_ch\_int\_sts interrupt status bit.

| Manual State Machine or Automatic State Machine | Forced State or Mode | dpll_en | dpll_mode               |

|-------------------------------------------------|----------------------|---------|-------------------------|

|                                                 | Freerun              | 0x0     | 0x0, 0x6                |

|                                                 | Reserved             | 0.00    | 0x2, 0x3, 0x4, 0x5, 0x7 |

|                                                 | Reserved             |         | 0x5, 0x7                |

| Manual                                          | Freerun              |         | 0x0                     |

| See Figure 7                                    | Normal               |         | 0x1                     |

|                                                 | Holdover             | 0x1     | 0x2                     |

|                                                 | Write Frequency      | OX1     | 0x3                     |

|                                                 | Acquire              |         | 0x4                     |

| Automatic<br>See Figure 6                       | Automatic Mode       |         | 0x6                     |

Table 3. DPLL States and Modes

#### 1.8.3 Freerun State

In the Freerun state, the integral and proportional terms output by the DPLL are held at zero. In this state, the FFO of the APLL is determined by the FFO of the device frequency reference, plus xtal\_trim if used. During the Master Reset Sequence or the Soft Reset Sequence the DPLL will be in the Freerun state (see Figure 6 and Figure 7). There are three combinations of the dpll\_en register bit and the dpll\_mode register field that will force the DPLL into the Freerun state (see Table 3).

The DPLL can automatically enter the Freerun state; the conditions for entering this state depend on the operating mode of the DPLL state machine. When the DPLL state machine is in the manual mode it will automatically enter the Freerun state according to the logic shown in Figure 7. When the DPLL state machine is in the automatic mode, the DPLL will automatically enter the Freerun state according to the logic shown in Figure 6. See Table 3 to configure the operating mode of the DPLL state machine.

#### 1.8.4 Normal State

The Normal state supports DPLL operation, the DPLL control loop is active and it steers the APLL. While the DPLL is locked, OUTx clocks sourced from the VCO or from FODs in the Synchronous mode track the selected reference according to the configured DPLL bandwidth, damping factor, FFO limit, and phase slope limit. The DPLL is placed in the Normal state by the following settings: dpll\_en = 0x1 and dpll\_mode = 0x1 (see Table 3).

When the DPLL state machine is in the automatic mode, the DPLL will automatically enter the Normal state according to the logic shown in Figure 6. See Table 3 to configure the operating mode of the DPLL state machine.

In the Normal state the DPLL bandwidth and damping are configured using the normal\_bw\_shift and normal\_bw\_mult; and normal\_damping\_shift and normal\_damping\_mult register fields respectively. The FFO limit and the phase slope limit are configured using the integrator\_limit and phase\_slope\_limit register fields, respectively.

The Normal state is intended for normal operation when the DPLL is locked. The DPLL bandwidth, damping, FFO limit and phase slope limit should be configured to meet the standard requirements of the application.

Figure 6. DPLL State Machine in Automatic Mode

Line Types

Thin lines indicate automatic state transitions

Thick lines indicate register or pin status

dpll hitless en bit

Internal signal

Internal signal

#### 1.8.5 Write Phase Mode

Hitless Switch

Hitless Switch Done

Reference Switch

Acronyms

RF

HS

HD

RS

L L2F

The Write Phase mode supports DCO operation. It allows host software to steer the FFO of the APLL using the write\_phase register field. The Write Phase mode is enabled when the DPLL is in the Normal State or the Acquire State and phase source sel = 0x1.

In the Write Phase mode the output of the PFD, via the decimator, is replaced by values from the write\_phase register field (see Figure 3 and Figure 5).

#### 1.8.6 Holdover State

The Holdover state supports continued generation of accurate clock frequencies during short-term interruptions of the synchronization reference. The DPLL can be forced into the Holdover state by the following settings: dpll\_en = 0x1 and dpll\_mode = 0x2 (see Table 3).

The DPLL can automatically enter the Holdover state. The conditions for entering this state depend on the operating mode of the DPLL state machine. When the DPLL state machine is in the manual mode it will automatically enter the Holdover state according to the logic shown in Figure 7. When the DPLL state machine is in the automatic mode, the DPLL will automatically enter the Holdover state according to the logic shown in Figure 6. See Table 3 to configure the operating mode of the DPLL state machine.

In the Holdover state the integral term from the low-pass filter output is replaced by a holdover value from holdover handler and the proportional term is held at zero, see Figure 5.

### 1.8.7 Write Frequency State

The Write Frequency state supports DCO operation, it allows host software to steer the FFO of the APLL using the write\_freq register field. The DPLL can be forced into the Write Frequency state by the following settings: dpll en = 0x1and dpll mode = 0x3 (see Table 3).

In the Write Frequency state the integral term from the low-pass filter output is replaced by values from the write freq register field and the proportional term is held at zero (see Figure 5).

Figure 7. DPLL State Machine in Manual Mode

#### 1.8.8 Acquire State

The Acquire state supports DPLL operation, the DPLL control loop is active and it steers the APLL. The Acquire state is the same as the Normal State except that it supports independent DPLL bandwidth and damping settings and it supports different automatic state transitions (see Figure 6 and Figure 7). The DPLL can be forced into the Acquire state by the following settings: dpll\_en = 0x1and dpll\_mode = 0x4 (see Table 3).

When the DPLL state machine is in the automatic mode, the DPLL will automatically enter the Acquire state according to the logic shown in Figure 6. See Table 3 to configure the operating mode of the DPLL state machine.

In the Acquire state the DPLL bandwidth and damping are configured using the acquire\_bw\_shift and acquire\_bw\_mult; and acquire\_damping\_shift and acquire\_damping\_mult register fields respectively. The FFO limit and the phase slope limit are configured using the integrator\_limit and phase\_slope\_limit register fields respectively.

The Acquire state is intended to accelerate the DPLL locking process with relaxed DPLL bandwidth and damping versus the Normal state. To further accelerate the locking process, host software can also relax the phase slope limit while the DPLL is in the acquire state by configuring the phase\_slope\_limit register field. After the DPLL reports lock, host software can restore the normal phase slope limit.

#### 1.8.9 Hitless Switch State

The Hitless Switch state manages the process of switching the DPLL from the Holdover State to the Acquire State without causing a phase transient on the OUTx clocks (see Hitless DPLL Reference Switching). The Hitless state is accessible when the DPLL is in the Holdover State and the DPLL state machine is in the automatic mode. The Hitless state cannot be directly accessed using the dpll mode register field.

When the DPLL state machine is in the automatic mode, the DPLL will automatically enter the Hitless Switch state according to the logic shown in Figure 6. See Table 3 to configure the operating mode of the DPLL state machine.

The hitless switching phase offset is measured over the number of reference clock cycles programmed in the <a href="hs\_counter\_limit">hs\_counter\_limit</a> register field. The phase offset measurements are averaged by the decimator using the bandwidth for hitless switching defined by the dec\_hitless\_bw\_shift register field. When the phase measurement is complete the DPLL enters the Acquire State (see Figure 6).

For applications where the DPLL state machine is used in the manual mode the Hitless Switch state is accessible as follows: after the DPLL has entered the Holdover State according to the logic in Figure 7, set the DPLL state machine to automatic mode by setting dpll\_mode = 0x6. When the selected reference is valid the DPLL will transition from the Holdover State to the Hitless Switch state and then to the Acquire State (see Figure 6). Host software can monitor the automatic state machine using the dpll\_state\_sts register field and the dpll\_state\_ch\_int\_sts interrupt status bit and return to the manual mode as desired.

### 1.9 Clock Output Paths

The RC32312/RC32308 has two types of clock output path. The paths for OUT[7:4] have access to the VCO/2 clock only. The paths for OUT[3:0] and OUT[11:8] have access to the VCO/2 clock and the FOD[2:0] clocks. Each clock output path includes one IOD and one clock output buffer.

### 1.9.1 Integer Output Dividers

The IODs are configured using registers in the IOD section.

The 21-bit integer divide ratio for each IOD is programmed using the respective iod\_divider register field. Programming an IOD with a value of 0x0 or 0x1 causes the divider to be bypassed. When reprogramming an IOD divider value after startup, writing the entire iod\_divider value as a single burst will ensure the divider is updated atomically; this prevents unintended intermediate divider values from being latched by the divider. After reprogramming an IOD, a divider synchronization is recommended as described below.

The IODs, FODs, and DPLL feedback divider can be manually synchronized by setting the divider\_sync register bit to 0x1, or by setting the apll\_reinit register bit to 0x1 (for more information, see Soft Reset Sequence). IOD output clocks will be interrupted during divider synchronization, but will resume after synchronization and no runt pulses will be generated.

#### 1.9.1.1 IOD Phase Adjustment

The phase of each IOD output clock can be independently adjusted using the signed 16-bit iod\_phase\_config register field. IOD phase adjustments are specified in periods of the IOD input clock.

IOD phase adjustments are applied by temporarily modulating the high phase of the IOD output clock. Positive phase adjustments will extend the duration of the high phase and negative phase adjustments will reduce the duration of the high phase. The entire phase adjustment in the <a href="mailto:iod\_phase\_config">iod\_phase\_config</a> register field will be applied regardless of whether it spans multiple cycles of the IOD output clock. The IOD will apply the phase adjustment in a single step or multiple steps, depending on the divide ratio in the <a href="mailto:iod\_divider">iod\_divider</a> register field. In some cases, the IOD will apply a phase adjustment in multiple steps of one period of the IOD input clock.

IOD phase adjustments are triggered by writing the iod\_ph\_adj\_now trigger bit to 0x1. The iod\_ph\_adj\_now bit will remain high until the phase adjustment is completed then it will be automatically cleared. An IOD can be configured to automatically apply an IOD phase adjustment after a divider synchronization event by writing the iod\_ph\_adj\_post\_sync bit to 0x1.

The pulse width high during phase adjustments will not be less than two periods of the IOD input clock. Negative phase adjustments are not possible if  $iod\_divider \le 0x5$ . IOD phase adjustments are not possible if the IOD is bypassed (e.g.,  $iod\_divider$  is set to 0x0 or 0x1).

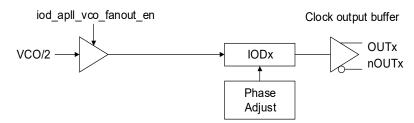

### 1.9.2 Clock Output Path for OUT[7:4]

The clock source selection for OUT[7:4] is illustrated in Figure 8.

Unused clock paths can be powered down by configuring the respective register fields as follows: iod\_apll\_vco\_fanout\_en = 0x0; iod\_enable = 0x0; out\_en\_bias = 0x0; out\_dis\_state = 0x3; and out\_driver\_en = 0x0.

Figure 8. Clock Path for OUT[7:4]

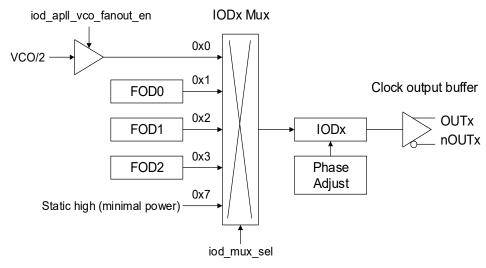

### 1.9.3 Output Clock Path for OUT[3:0] and OUT[11:8]

The clock source selection for OUT[3:0] and OUT[11:8] is illustrated in Figure 9.

When VCO/2 is not the selected source for an IOD then the respective iod\_apll\_vco\_fanout\_en bit should be set to 0x0 to minimize power consumption.

Unused output clock paths can be powered down by configuring the respective register fields as follows: iod\_apll\_vco\_fanout\_en = 0x0; iod\_mux\_sel = 0x7; iod\_enable = 0x0; out\_en\_bias = 0x0; out\_dis\_state = 0x3; and out\_driver\_en = 0x0.

Figure 9. Clock Path for OUT[3:0] and OUT[11:8]

#### 1.9.4 Clock Output Buffers

The clock output buffers are configured using registers in the OUTBUF section.

Unused clock output buffers can be powered down by configuring the respective register fields as follows: out\_en\_bias = 0x0; out\_dis\_state = 0x3; and out\_driver\_en = 0x0.

The HCSL output voltage swing, LVDS output voltage swing, and LVDS common mode voltage are controlled using the out\_cnf\_hcsl\_swing, out\_cnf\_lvds\_amp, and out\_lvds\_cm\_voltage register fields, respectively. The

descriptions for these register fields provide nominal voltage values. For the actual range of voltages associated with each setting, see the device datasheet.

For HCSL outputs (out\_mode = 0x0), a boost mode can be enabled for outputs that are configured for 950mV amplitude swing (out\_cnf\_hcsl\_swing = 0xF) by setting the respective out\_spare register bit to 0x1. Boost mode increases the HCSL amplitude swing by approximately 10%.

#### 1.10 Status and Control

All control and status registers (CSR) are accessed through a 1MHz I<sup>2</sup>C or 20MHz SPI slave microprocessor interface. The device can automatically load a configuration from internal one time programmable (OTP) memory. Alternatively, the I<sup>2</sup>C master interface can automatically load a configuration from an external EEPROM after reset.

#### 1.11 Power-On Reset and Reset Controller

There are no power supply sequencing requirements; however, if  $V_{DDOx}$  or  $V_{DD\_CLK}$  reach 90% of  $V_{DD}$  nominal after the later of  $V_{DD\_VCO}$  or  $V_{DDD33\_DIA}$  then a soft reset or a master reset must be initiated to ensure the input dividers and output dividers are synchronized. A soft reset can be initiated by setting the self clearing soft\_reset register bit to 0x1; a master reset can be initiated as described in the following paragraphs.

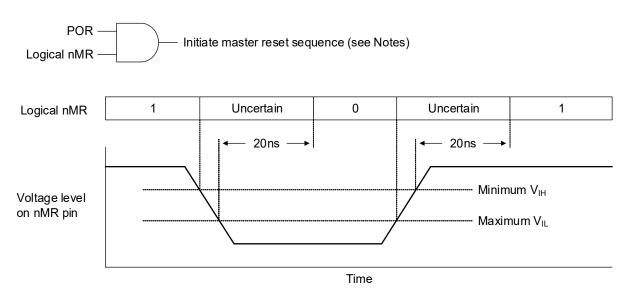

Upon power-up, an internal power-on reset (POR) signal is asserted 5ms after both the  $V_{DDXO\_DCD}$  and  $V_{DDD33\_DIA}$  supplies reach 90% of  $V_{DD}$  nominal. The first master reset sequence is initiated when POR is asserted and the voltage level on the nMR pin is high.

After the first master reset sequence is initiated, another master reset sequence can be initiated by taking the voltage level on the nMR pin low and then high while POR remains asserted (see Figure 10). To ensure a master reset sequence is initiated, the voltage level on the nMR pin must be held low for at least 20ns before transitioning high. To ensure deterministic behavior, voltage level transitions on the nMR pin must be monotonic between minimum  $V_{IH}$  and maximum  $V_{II}$ .

#### Notes:

- Requires 1 from logical nMR for the first master reset sequence

- Requires 0 to 1 transition from logical nMR after the first master reset sequence has been initiated

Figure 10. Master Reset Sequence Initiation

The nMR pin has an internal pull-up that can be left to float, or it can optionally be externally pulled high or low. If nMR is high when the internal POR is asserted, the reset controller will initiate a master reset sequence. If nMR is

low when the internal POR is asserted, the reset controller will not initiate a master reset sequence until nMR is taken high.

During the master reset sequence all clock outputs are optionally disabled, depending on the value of the out\_startup register field. Disabled outputs behave according to the associated out\_dis\_state register field.

The serial ports are accessible when the device\_ready\_sts register bit is set to 0x1. Any GPIO can be configured to indicate the state of the device\_ready\_sts register bit by setting the associated gpio\_func register field to 0x18. When a reset sequence completes the rst\_done\_sts register bit is set to 0x1.

When a configuration is loaded from EEPROM, the voltage level on the nMR pin must be held high from the time a master reset sequence is initiated until after the EEPROM transactions have completed, as indicated when the device ready sts register bit is set to 0x1.

#### 1.11.1 Master Reset Sequence

The device can be configured by the config\_sel register field to select an OTP configuration using the voltage levels latched at start-up on the GPIO, nCS\_A0, SDO\_A1, SDA\_SDIO, and SCL\_SCLK pins. In addition, the device can be configured by the i2c\_addr\_sel register field to select the I<sup>2</sup>C address using the voltage levels latched at start-up on the GPIO, nCS\_A0, and SDO\_A1 pins. For pins used in this way, the voltage levels externally applied must not change from the time a master reset is initiated until after the configurations have been loaded (i.e., device ready sts = 0x1).

The master reset sequence executes the following steps (in the order listed):

- 1. Latch the levels on the following pins: GPIOs, nCS\_A0, SDO\_A1, SDA\_SDO, and SCL\_SCLK.

- 2. Load the defaults or configurations from OTP memory and/or EEPROM (if present).

- a. Set device\_ready\_sts to 0x1.

- 3. Calibrate the VCO.

- 4. Lock the APLL.

- 5. Calibrate the digitally controlled delays (DCD).

- 6. Synchronize all dividers.

- 7. Start the DPLL state machine (see DPLL State Machine and Table 3).

- 8. Set rst done sts to 0x1.

### 1.11.2 Soft Reset Sequence

After the device is ready (i.e., device\_ready\_sts = 0x1), a soft reset sequence can be initiated by writing 0x1 to the self clearing soft\_reset register bit. A soft reset will clear any status bits that are interrupt sources.

The relatch\_inputs register bit can be configured to update the I<sup>2</sup>C address during the soft reset sequence by relatching the voltage levels as described under Master Reset Sequence. For pins used to update the I<sup>2</sup>C address, the voltage levels externally applied must not change from the time a soft reset is initiated until after the soft reset sequence is completed as indicated by rst\_done\_sts = 0x1.

The soft reset sequence executes the following steps (in the order listed):

- 1. Set rst\_done\_sts 0x0.

- If relatch\_inputs = 0x1.

- a. Latch the levels on the following pins: GPIOs, nCS A0, SDO A1, SDA SDO, and SCL SCLK.

- 3. If soft reset sel = 0x1.

- a. Synchronize all dividers.

- b. Start the DPLL state machine (see DPLL State Machine and Table 3).

- c. Set rst\_done\_sts to 0x1.

- 4. If  $soft_reset_sel = 0x0$ .

- a. Calibrate the VCO.

- b. Lock the APLL.

- c. Calibrate the digitally controlled delays (DCD).

- d. Synchronize all dividers.

- e. Start the DPLL state machine (see DPLL State Machine and Table 3).

- f. Set rst done sts to 0x1.

The soft reset sequence can be executed starting at Step 4a (Calibrate the VCO) without initiating a soft reset by writing 0x1 to the apll\_reinit register bit. The reset sequence can also be executed starting at Step 4d (Synchronize all dividers) without initiating a soft reset by writing 0x1 to the divider\_sync register bit. In both of these cases the soft\_reset\_sel register bit is ignored.

### 2. Serial Interfaces

I<sup>2</sup>C or SPI operation is selected by the ssi\_enable register field, which defaults to I<sup>2</sup>C mode. The serial interfaces are inactive until the OTP load completes during the power-up sequence.

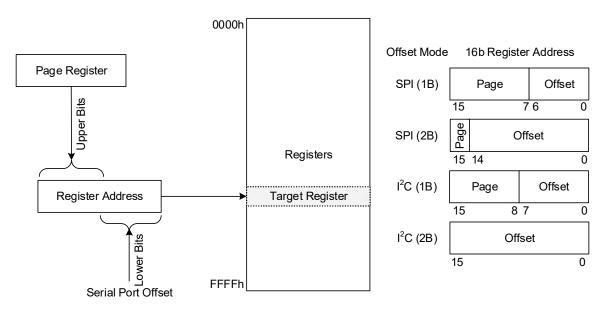

## 2.1 Paging

You can choose to operate the serial port providing the full offset address within each burst, or to operate in a paged mode where part of the address offset is provided in each transaction and another part comes from an internal page register in each serial port. Figure 11 shows how page register and offset bytes from each serial transaction interact to address a register within the RC32312, RC32308.

Figure 11. Register Addressing Modes Using Serial Port

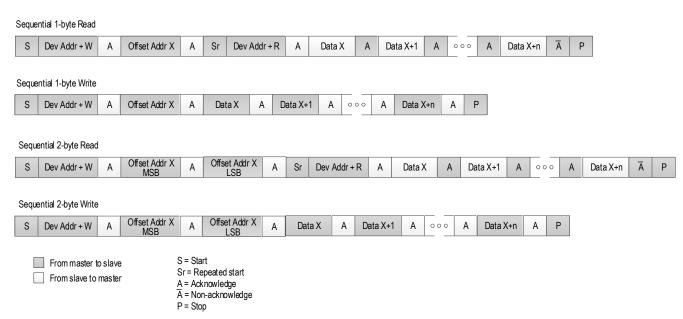

### 2.2 I<sup>2</sup>C Slave

The  $I^2C$  slave protocol of the RC32312, RC32308 complies with the  $I^2C$  specification, version UM10204 Rev.6 – 4 April 2014. In the following description, serial clock line (SCL) refers to the SCL\_SCLK pin and serial data line (SDA) refers to the SDA SDIO pin.

Figure 12 shows the sequence of states on the I<sup>2</sup>C SDA signal for the supported modes of operation.

Figure 12. I<sup>2</sup>C Slave Sequencing

The Dev Addr shown in the figure represents the I<sup>2</sup>C bus address of the device. This 7-bit value in the i2c\_addr register field defaults to 0x09 if not programmed using the OTP load, or controlled through the nCS\_A0, SDO\_A1 or GPIO pins.

The selection of 1-byte (1B) or 2-byte (2B) offset addressing must also be configured using the ssi\_addr\_size register field. These offsets are used in conjunction with the page register to access registers internal to the device (see Figure 11). Because the I<sup>2</sup>C protocol already includes a read/write bit with the Dev Addr, all bits of the 1B or 2B offset field can be used to address internal registers.

- In 1B mode, the lower 8 bits of the register offset address come from the Offset Addr byte and the upper 8 bits come from the page register. The page register can be accessed at any time using an offset byte value of 0xFC. This 4-byte register must be written in a single-burst write transaction.

- In 2B mode, the full 16-bit register address can be obtained from the Offset Addr bytes.

*Note*: I<sup>2</sup>C burst mode operation is recommended to ensure data integrity of multi-byte registers. When accessing a multi-byte register, all data bytes must be written or read in a single I<sup>2</sup>C burst access. Bursts can be of greater length if required but must not extend beyond the end of the register page (Offset Addr 0xFF in 1B mode). An internal address pointer is incremented automatically as each data byte is written or read.

I<sup>2</sup>C interface timing is shown in the RC32312, RC32308 datasheet.100kHz (Standard mode), 400kHz (Fast mode), and 1MHz (Fast mode plus) operation are supported. The output slew rate is set according to the speed selected by the pad\_scl\_sclk\_drv register field.

The I<sup>2</sup>C interface operating at 1MHz supports a DCO update rate of approximately 16k updates per second.

### 2.2.1 I<sup>2</sup>C 1-byte (1B) Addressing Example

RC32312, RC32308 I<sup>2</sup>C 7-bit I<sup>2</sup>C address is 0x09 with LSB = R/W

Example write 0x8003 to register 0x20:

```

12* FC 00 00 00 00 #Set Page Register, *I2C Address is left-shifted one bit.

12 20 03 80 #Write data 0x8003 to 0x20

```

#### Example read from register 0x168

```

12* FC 00 01 00 00  #Set Page Register, *I2C Address is left-shifted one bit.

12 68  #Set I2C pointer to 0x168, I2C instruction should use "No Stop".

13 <read back data>  #Send address with Read bit set.

```

### 2.2.2 I<sup>2</sup>C 2-byte (2B) Addressing Example

RC32312, RC32308 I<sup>2</sup>C 7-bit I<sup>2</sup>C address is 0x09 with LSB = R/W.

Example write 0x8003 to register 0x20:

```

12 00 20 03 80 #Write data 0x8003 to 0x0020

```

Example read from register 0x168:

```

#Set I2C pointer to 0x0168, * I2C instruction should use "No Stop".

13 <read back data> #Send address with Read bit set.

```

### 2.3 SPI Slave

In the following description, nCS refers to the nCS\_A0 pin, SCLK refers to the SCL\_SCLK pin, SDI SDIO refers to the SDA SDIO pin, and SDO refers to the SDO A1 pin.

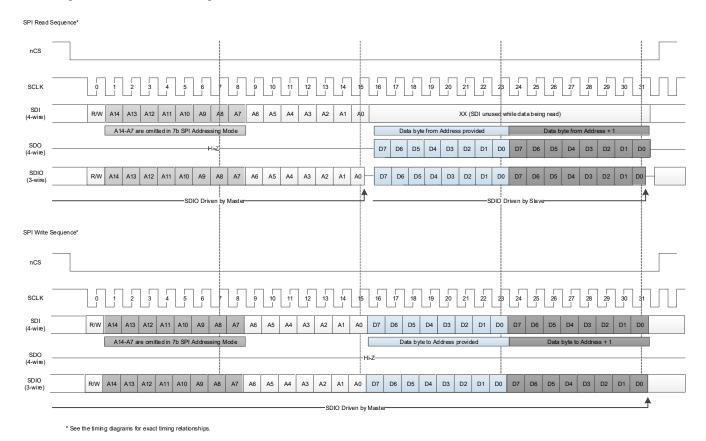

The RC32312, RC32308 supports 4-wire or 3-wire SPI operation as a selectable protocol on the serial port. The 3-wire or 4-wire mode is selected by the spi\_3wire register bit. In 4-wire mode, there are separate data in (to the RC32312, RC32308) and data out signals (SDI and SDO respectively). In 3-wire mode, the SDIO signal is used as a single, bidirectional data signal.

Figure 13. SPI Sequencing

Figure 13 shows the sequencing of address and data on the serial port in both 3-wire and 4-wire SPI mode. 4-wire SPI mode is the default. The R/W bit is high for read cycles and low for write cycles.

SPI operation can be configured for the following settings through register fields:

1-byte (1B) or 2-byte (2B) offset addressing (ssi\_addr\_size) (see Figure 11)

- In 1B operation, the 16-bit register address is formed by using the 7 bits of address supplied in the SPI access

and taking the upper 9 bits from the page register. The page register is accessed using an Offset Address of

0x7C with a 4-byte burst access.

- In 2B operation, the 16-bit register address is formed by using the 15 bits of address supplied in the SPI access and the upper 1-bit is fixed to b'0.

- Data sampling on falling or rising edge of SCLK (spi\_clk\_sel).

- Output (read) data positioning relative to active SCLK edge (spi\_del\_out).

*Note*: SPI burst mode operation is recommended to ensure data integrity of multi-byte registers. When accessing a multi-byte register, all data bytes must be written or read in a single SPI burst access. Bursts can be of greater length if desired but must not extend beyond the end of the register page. An internal address pointer is incremented automatically as each data byte is written or read.

SPI timing is shown in the RC32312, RC32308 Datasheet.

The SPI interface operating at 20MHz supports a DCO update rate of approximately 400k updates per second.

### 2.3.1 SPI 1-byte (1B) Addressing Example

Example write to "50" to register 0xE4:

7C 80 00 00 00 #Set Page register

64\* 50 #\*MSB is 0 for write transactions

Example read from 0x24:

7C 00 00 00 00 #Set Page register

A4\* 00 #\*MSB is set, so this is a read command

### 2.3.2 SPI 2-byte (2B) Addressing Example

Example write to "50" to register 0xCBE4

4B E4\* 50 #\*MSB is 0 for write transactions

Example read from 0xC024:

CO\* 24 00 #\*MSB is set, so this is a read command

# 3. Registers

Table 4. Register Index

| Module Base<br>Address (Hex) |             | Module Description                                                                            | Link     |  |

|------------------------------|-------------|-----------------------------------------------------------------------------------------------|----------|--|

| 0x0                          | GLOBAL      | Global Control and Status Registers                                                           | GLOBAL   |  |

| 0x40                         | INT         | Interrupt Registers                                                                           | INT      |  |

| 0x50                         | SSI         | Slave Serial Interface Registers                                                              | SSI      |  |

| 0x60                         | хо          | Crystal Oscillator, Input Buffer and Reference Select Registers                               | XO       |  |

| 0x70                         | INPUTBUF[0] | Input Buffer Registers                                                                        | INPUTBUF |  |

| 0x72                         | INPUTBUF[1] | Same as INPUTBUF[0]                                                                           | INPUTBUF |  |

| 0x74                         | INPUTBUF[2] | Same as INPUTBUF[0]                                                                           | INPUTBUF |  |

| 0x76                         | INPUTBUF[3] | Same as INPUTBUF[0]                                                                           | INPUTBUF |  |

| 0x80                         | INPUTMUX    | Input Mux Registers                                                                           | INPUTMUX |  |

| 0x84                         | INPUTDIV[0] | Input Buffer Registers                                                                        | INPUTDIV |  |

| 0x88                         | INPUTDIV[1] | Same as INPUTDIV[0]                                                                           | INPUTDIV |  |

| 0x8C                         | INPUTDIV[2] | Same as INPUTDIV[0]                                                                           | INPUTDIV |  |

| 0x90                         | INPUTDIV[3] | Same as INPUTDIV[0]                                                                           | INPUTDIV |  |

| 0x94                         | SYSDIV      | System Clock Divider Registers                                                                | SYSDIV   |  |

| 0xA0                         | GPIO[0]     | General Purpose IO Registers Instances 0-7 apply to GPIO0 to GPIO9 Instance 8 applies to LOCK | GPIO     |  |

| 0xA8                         | GPIO[1]     | Same as GPIO[0]                                                                               | GPIO     |  |

| 0xB0                         | GPIO[2]     | Same as GPIO[0]                                                                               | GPIO     |  |

| 0xB8                         | GPIO[3]     | Same as GPIO[0]                                                                               | GPIO     |  |

| 0xC0                         | GPIO[4]     | Same as GPIO[0]                                                                               | GPIO     |  |

| 0xC8                         | GPIO[5]     | Same as GPIO[0]                                                                               | GPIO     |  |

| 0xD0                         | GPIO[6]     | Same as GPIO[0]                                                                               | GPIO     |  |

| 0xD8                         | GPIO[7]     | Same as GPIO[0]                                                                               | GPIO     |  |

| 0xE0                         | GPIO[8]     | Same as GPIO[0]                                                                               | GPIO     |  |

| 0x100                        | OUTBUF[0]   | Output Buffer Registers                                                                       | OUTBUF   |  |

| 0x108                        | OUTBUF[1]   | Same as OUTBUF[0]                                                                             | OUTBUF   |  |

| 0x110                        | OUTBUF[2]   | Same as OUTBUF[0]                                                                             | OUTBUF   |  |

| 0x118                        | OUTBUF[3]   | Same as OUTBUF[0]                                                                             | OUTBUF   |  |

| 0x120                        | OUTBUF[4]   | Same as OUTBUF[0]                                                                             | OUTBUF   |  |

| 0x128                        | OUTBUF[5]   | Same as OUTBUF[0]                                                                             | OUTBUF   |  |

| 0x130                        | OUTBUF[6]   | Same as OUTBUF[0]                                                                             | OUTBUF   |  |

| 0x138                        | OUTBUF[7]   | Same as OUTBUF[0]                                                                             | OUTBUF   |  |

| 0x140                        | OUTBUF[8]   | Same as OUTBUF[0]                                                                             | OUTBUF   |  |

| 0x148                        | OUTBUF[9]   | Same as OUTBUF[0]                                                                             | OUTBUF   |  |

| 0x150                        | OUTBUF[10]  | Same as OUTBUF[0]                                                                             | OUTBUF   |  |

Table 4. Register Index

| Module Base<br>Address (Hex) |            | Module Description                                         | Link    |

|------------------------------|------------|------------------------------------------------------------|---------|

| 0x158                        | OUTBUF[11] | Same as OUTBUF[0]                                          | OUTBUF  |

| 0x160                        | TDCAPLL    | TDC APLL Registers                                         | TDCAPLL |

| 0x170                        | XTALMON    | XTAL Monitor Registers (xtalmon[0] = XIN, xtalmon[1]=REF4) | XTALMON |

| 0x180                        | LOSMON[0]  | LOS Monitor Registers                                      | LOSMON  |

| 0x190                        | LOSMON[1]  | Same as LOSMON[0]                                          | LOSMON  |

| 0x1A0                        | LOSMON[2]  | Same as LOSMON[0]                                          | LOSMON  |

| 0x1B0                        | LOSMON[3]  | Same as LOSMON[0]                                          | LOSMON  |

| 0x1C0                        | FREQMON[0] | Frequency Monitor Registers                                | FREQMON |

| 0x1E0                        | FREQMON[1] | Same as FREQMON[0]                                         | FREQMON |

| 0x200                        | FREQMON[2] | Same as FREQMON[0]                                         | FREQMON |

| 0x220                        | FREQMON[3] | Same as FREQMON[0]                                         | FREQMON |

| 0x240                        | APLL       | APLL Registers                                             | APLL    |

| 0x2A0                        | IOD[0]     | Integer Output Divider Registers                           | IOD     |

| 0x2B0                        | IOD[1]     | Same as IOD[0]                                             | IOD     |

| 0x2C0                        | IOD[2]     | Same as IOD[0]                                             | IOD     |

| 0x2D0                        | IOD[3]     | Same as IOD[0]                                             | IOD     |

| 0x2E0                        | IOD[4]     | Same as IOD[0]                                             | IOD     |

| 0x2F0                        | IOD[5]     | Same as IOD[0]                                             | IOD     |

| 0x300                        | IOD[6]     | Same as IOD[0]                                             | IOD     |

| 0x310                        | IOD[7]     | Same as IOD[0]                                             | IOD     |

| 0x320                        | IOD[8]     | Same as IOD[0]                                             | IOD     |

| 0x330                        | IOD[9]     | Same as IOD[0]                                             | IOD     |

| 0x340                        | IOD[10]    | Same as IOD[0]                                             | IOD     |

| 0x350                        | IOD[11]    | Same as IOD[0]                                             | IOD     |

| 0x400                        | FOD[0]     | Fractional Output Divider Registers                        | FOD     |

| 0x440                        | FOD[1]     | Same as FOD[0]                                             | FOD     |

| 0x480                        | FOD[2]     | Same as FOD[0]                                             | FOD     |

| 0x500                        | DPLL       | DPLL Registers                                             | DPLL    |

| 0x600                        | EEPROM     | EEPROM Registers                                           | EEPROM  |

## 3.1 GLOBAL

Global Control and Status Registers.

Table 5. GLOBAL Register Index

| Offcot (Hox) | Register Module Base Address: 0x0 |                              |  |  |

|--------------|-----------------------------------|------------------------------|--|--|

| Offset (Hex) | Register Name                     | Register Description         |  |  |

| 0x0          | VENDOR_ID                         | Vendor ID and Device Type    |  |  |

| 0x2          | DEVICE_ID                         | Device ID                    |  |  |

| 0x4          | DEVICE_REV                        | Device Revisions and Font ID |  |  |

| 0x6          | DEVICE_PGM                        | Device Dash Code             |  |  |

| 0x8          | DEVICE_CNFG                       | Device Configuration         |  |  |

| 0xC          | MISC_CNFG                         | Reset Configuration          |  |  |

| 0x10         | SCRATCH_CNFG                      | Scratch register             |  |  |

| 0x14         | MISC_CTRL                         | Reset Control                |  |  |

| 0x20         | STARTUP_STS                       | Startup status               |  |  |

| 0x24         | DEVICE_STS                        | Device status                |  |  |

## 3.1.1 VENDOR\_ID

Vendor ID and Device Type.

|              | VENDOR_ID Bit Field Descriptions |               |                  |                                                                                                                                                                                                |  |  |

|--------------|----------------------------------|---------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit<br>Field | Field Name                       | Field<br>Type | Default<br>Value | Description                                                                                                                                                                                    |  |  |

| 15:12        | dev_id_type                      | RO            | 0x1              | Device ID Block Type. A value of 0x1 indicates that this register is followed by a 16-bit Device ID register and an 16-bit Device Revision register, and a 16-bit Device Programming register. |  |  |

| 11           | reserved                         | RO            | 0x0              | Reserved                                                                                                                                                                                       |  |  |

| 10:0         | vendor_id                        | RO            | 0x33             | Vendor ID. IDT JEDEC ID.                                                                                                                                                                       |  |  |

## 3.1.2 DEVICE\_ID

Device ID.

|              | DEVICE_ID Bit Field Descriptions |               |                  |                                                                                                                          |  |  |

|--------------|----------------------------------|---------------|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit<br>Field | Field Name                       | Field<br>Type | Default<br>Value | Description                                                                                                              |  |  |

| 15:0         | device_id                        | RW            | 0x0              | Device ID. For default value refer to Product Identification. This field is write-able so it may be configured from OTP. |  |  |

## 3.1.3 DEVICE\_REV

Device Revisions and Font ID.

|              | DEVICE_REV Bit Field Descriptions |               |                  |                                                                                                                                        |  |  |  |

|--------------|-----------------------------------|---------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit<br>Field | Field Name                        | Field<br>Type | Default<br>Value | Description                                                                                                                            |  |  |  |

| 15:13        | reserved                          | RO            | 0x0              | Reserved                                                                                                                               |  |  |  |

| 12:8         | font_id                           | RO            | 0x5              | Font ID. Font ID to distinguish die variants. Decode as follows:  0x0 = Font 0  0x2 = Font 1  0x3 = Font 2  0x4 = Font 3  0x5 = Font 4 |  |  |  |

| 7:0          | reserved                          | RO            | 0x53             | Reserved                                                                                                                               |  |  |  |

## 3.1.4 DEVICE\_PGM

Device Dash Code.

|              | DEVICE_PGM Bit Field Descriptions |               |                  |                                                                                                                                                                                                                                                                                   |  |  |