# **Product Advisory (PA)**

**Subject:** Changes to the Power-up / Power-down Sequencing and Recovery from Brown-out Condition **Publication Date:** 2/24/2023 **Effective Date:** 2/24/2023

#### **Revision Description:**

Initial Release

#### **Description of Change:**

This notice is to inform you that the High-Performance Serial MRAM Memory datasheet has been updated as follows:

- Wording changes in Chapter 3 Table 2 (Signal Description)

- Chapter 7 (Device Initialization) has been revised. The proper (and required) device initialization is now described in more detail.

- Some parameters in Chapter 7 Table 6 and Table 7 (Power Up/Down Timing) have been updated, to reflect the new requirements for proper power-up/down sequencing.

Changes are as reflected in Appendix A of the notice.

The test program was revised to the new specification on 11/15/22. All the material shipped after 01/01/23 has been screened to the revised test program.

### Affected Product List:

Please refer to Appendix B

#### Reason for Change:

Update power supply sequencing and DC tables to provide proper power up and power down guidelines for the MRAM family of devices. These updates address gaps in the datasheet and provide additional guidance to the customer.

#### Impact on Fit, Form, Function, Quality & Reliability:

There is no change to form, fit, function, quality and reliability of the device.

**Product Identification:** Parts shipped after 01/01/23 are screened to the new specification. For more information please contact Renesas.

Qualification Status: Not Applicable Sample Availability Date: Not Applicable Device Material Declaration: Available upon request

Questions or requests pertaining to this change notice, including additional data or samples, must be sent to Renesas within 30 days of the publication date.

For additional information regarding this notice, please contact idt-pcn@lm.renesas.com

Appendix A - Description of Change The highlighted texts and graphs below show the datasheet updates.

# 1. Chapter 3 - Signal Description and Assignment Table 2: Signal Description

| Signal      | Туре                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CS#         | Input                       | <b>Chip Select:</b> When CS# is driven High, the device will enter standby mode. All other input pins are ignored and the output pin is tri-stated. Driving CS# Low enables the device, placing it in the active mode. After power-up, a falling edge on CS# is required prior to the start of any instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| WP# / IO[2] | Input<br>/<br>Bidirectional | <ul> <li>Write Protect (SPI): Write protects the status register in conjunction with the enable/disable bit of the status register. This is important since other write protection features are controlled through the Status Register. When the enable/disable bit of the status register is set to 1 and the WP# signal is driven Low, the status register becomes read-only and the WRITE STATUS REGISTER operation will not execute. This signal does not have internal pullups, it cannot be left floating and must be driven. WP# is valid only in Single SPI mode. This pin can be tied to Vcc if not used.</li> <li>Bidirectional Data 2 (DPI/QPI): The bidirectional I/O transfers data into and out of the device in Dual and Quad SPI modes.</li> </ul>                                                         |  |  |

| CLK         | Input                       | <ul> <li>Clock: Provides the timing for the serial interface. Depending on the mode selected, either single (rising or falling) edge or both edges of the clock are utilized for information transfer.</li> <li>In Single Data Rate mode (SDR) command, address and data inputs are latched on the rising edge of the clock. Data is output on the falling edge of the clock.</li> <li>In Double Data Rate mode (DDR) command is latched on the rising edge of the clock.</li> <li>In Double Data Rate mode (DDR) command is latched on the rising edge of the clock. Address and Data inputs are latched on both edges of the clock.</li> <li>Similarly, Data is output on both edges of the clock.</li> <li>SPI Mode 0 (CPOL = 0, CPHA = 0) – SDR and DDR</li> <li>SPI Mode 3 (CPOL = 1, CPHA = 1) – SDR only</li> </ul> |  |  |

| IO[3]       | Bidirectional               | <b>Bidirectional Data 3 (DPI/QPI):</b> The bidirectional I/O transfers data into and out of the device in Dual and Quad SPI modes. This pin can be tied to Vcc if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| SI / IO[0]  | Input<br>/<br>Bidirectional | Serial Data Input (SPI): The unidirectional I/O transfers data into the device<br>on the rising edge of the clock in Single SPI mode.<br>Bidirectional Data 0 (DPI/QPI): The bidirectional I/O transfers data into and<br>out of the device in Dual and Quad SPI modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

#### 2. Chapter 7 - Device Initialization

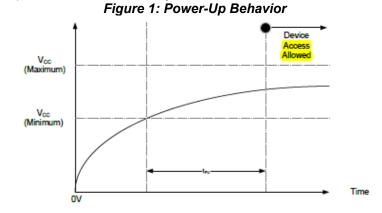

When powering up, the following procedure is required to initialize the device correctly:

- Ramp up Vcc (trvr)

- CS# must follow V<sub>CC</sub> during power-up (a 10KΩ pull-up Resistor to V<sub>CC</sub> is recommended)

- It is recommended that no instructions are sent to the device when  $V_{CC}$  is below  $V_{CC}$  (minimum)

- During initial Power-up, recovering from power loss or brownout, a delay of t<sub>PU</sub> is required before normal operation commences

- Upon Power-up, the device is in Standby mode

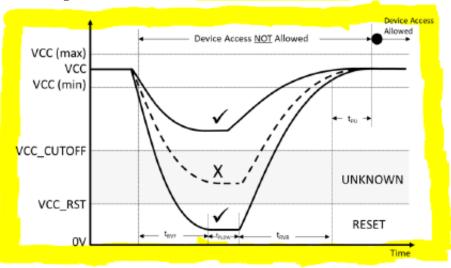

When powering down or in case of brown-out, the following procedure is required to turn off the device correctly:

- Ramp down Vcc below Vcc\_Rst level

- CS# must follow V<sub>CC</sub> during power-down (a 10KΩ pull-up Resistor to V<sub>CC</sub> is recommended)

- The device must not be selected and that no instructions are sent to the device when V<sub>CC</sub> is below V<sub>CC</sub> (minimum)

- The Power-up timing and device initialization needs to be observed after V<sub>CC</sub> ramps up above V<sub>CC</sub> (minimum)

- To stabilize the V<sub>CC</sub> level, suitable decoupling capacitors close to package V<sub>CC</sub> pin is recommended

- Chip functionality not guaranteed if Vcc ramps down between Vcc\_cutoff and Vcc\_Rst and then ramps up to Vcc

#### Figure 7: Power-Down and Brown-out Behavior

## 3. Chapter 7

# Table 6: Power Up/Down Timing - 3.0V

| Parameter                                                         | Symbol                       | Test Conditions | 3.0V              |         |                   |                 |

|-------------------------------------------------------------------|------------------------------|-----------------|-------------------|---------|-------------------|-----------------|

| Farameter                                                         |                              |                 | Minimum           | Typical | Maximum           | Units           |

| Vcc Range                                                         | Vcc                          | All operating   | 2.7               | -       | 3.6               | V               |

| Vcc Ramp Up Time <mark>to Vcc (min)</mark>                        | t <sub>rvr</sub>             |                 | 30                | -       | <mark>1500</mark> | <mark>μs</mark> |

| V <sub>cc</sub> Ramp Down Time <mark>to V<sub>cc_Rst</sub></mark> | <mark>t<sub>RVF</sub></mark> |                 | 20                | -       | -                 | <mark>μs</mark> |

| Vcc Power Up to First Instruction                                 | t <sub>PU</sub>              |                 | 250               | -       | -                 | μs              |

| Vcc Cutoff – Must Initialize Device                               | VCC_CUTOFF                   |                 | 1.6               | -       | -                 | V               |

| V <sub>cc</sub> Reset                                             | V <sub>CC_RST</sub>          | voltages and    | <mark>0</mark>    | -       | <mark>0.3</mark>  | V               |

| Vcc Power Down Low Time                                           | t <sub>PLOW</sub>            | temperatures    | <mark>1000</mark> | -       | -                 | <mark>μs</mark> |

| Time to Enter Deep Power Down                                     | tedpd                        | -               | -                 | -       | 3                 | μs              |

| Time to Exit Deep Power Down                                      | t <sub>EXDPD</sub>           |                 | -                 | -       | 400               | μs              |

| Time to Enter Hibernate                                           | tenthib                      |                 | -                 | -       | 3                 | μs              |

| Time to Exit Hibernate                                            | t <sub>ЕХНІВ</sub>           |                 | -                 | -       | 450               | μs              |

| CS# Pulse Width                                                   | t <sub>CSDPD</sub>           |                 | 50                | -       | -                 | ns              |

# 4. Chapter 7

# Table 7: Power Up/Down Timing - 1.8V

| Parameter                                     | Symbol              | Test Conditions              | 1.8V              |         |                   |                 |

|-----------------------------------------------|---------------------|------------------------------|-------------------|---------|-------------------|-----------------|

| Parameter                                     |                     |                              | Minimum           | Typical | Maximum           | Units           |

| V <sub>cc</sub> Range                         | Vcc                 |                              | 1.71              | -       | 2.0               | V               |

| Vcc Ramp Up Time <mark>to Vcc (min)</mark>    | t <sub>rvr</sub>    | -                            | 30                | -       | <mark>1000</mark> | <mark>µs</mark> |

| Vcc Ramp Down Time to Vcc_rst                 | <mark>t</mark> r∨F  |                              | 20                | -       | -                 | <mark>µs</mark> |

| V <sub>cc</sub> Power Up to First Instruction | t <sub>PU</sub>     |                              | 250               | -       | -                 | μs              |

| Vcc Cutoff – Must Initialize Device           | Vcc_cutoff          |                              | 1.6               | -       | -                 | V               |

| Vcc Reset                                     | Vcc_rst             | All operating                | <mark>0</mark>    | -       | <mark>0.2</mark>  | V               |

| V <sub>cc</sub> Power Down Low Time           | t <sub>PLOW</sub>   | voltages and<br>temperatures | <mark>1000</mark> | -       | -                 | <mark>µs</mark> |

| Time to Enter Deep Power Down                 | tedpd               |                              | -                 | -       | 3                 | μs              |

| Time to Exit Deep Power Down                  | <b>t</b> EXDPD      |                              | -                 | -       | 400               | μs              |

| Time to Enter Hibernate                       | t <sub>ENTHIB</sub> |                              | -                 | -       | 3                 | μs              |

| Time to Exit Hibernate                        | t <sub>ЕХНІВ</sub>  |                              | -                 | -       | 450               | μs              |

| CS# Pulse Width                               | tcsdpd              |                              | 50                | -       | -                 | ns              |

# Appendix B – Affected Product List

| Part Numbers       |                    |                    |  |  |

|--------------------|--------------------|--------------------|--|--|

| M10042040108X0IWAR | M10162040108X0IWAR | M10082040054X0IWAR |  |  |

| M10042040108X0IWAY | M10162040108X0IWAY | M10082040054X0IWAY |  |  |

| M10042040108X0ISAR | M10162040108X0ISAR | M10082040054X0ISAR |  |  |

| M10042040108X0ISAY | M10162040108X0ISAY | M10082040054X0ISAY |  |  |

| M10042040108X0PWAR | M10162040108X0PWAR | M10082040054X0PWAR |  |  |

| M10042040108X0PWAY | M10162040108X0PWAY | M10082040054X0PWAY |  |  |

| M10042040108X0PSAR | M10162040108X0PSAR | M10082040054X0PSAR |  |  |

| M10042040108X0PSAY | M10162040108X0PSAY | M10082040054X0PSAY |  |  |

| M30042040108X0IWAR | M30162040108X0IWAR | M30082040054X0IWAR |  |  |

| M30042040108X0IWAY | M30162040108X0IWAY | M30082040054X0IWAY |  |  |

| M30042040108X0ISAR | M30162040108X0ISAR | M30082040054X0ISAR |  |  |

| M30042040108X0ISAY | M30162040108X0ISAY | M30082040054X0ISAY |  |  |

| M30042040108X0PWAR | M30162040108X0PWAR | M30082040054X0PWAR |  |  |

| M30042040108X0PWAY | M30162040108X0PWAY | M30082040054X0PWAY |  |  |

| M30042040108X0PSAR | M30162040108X0PSAR | M30082040054X0PSAR |  |  |

| M30042040108X0PSAY | M30162040108X0PSAY | M30082040054X0PSAY |  |  |

| M10082040108X0IWAR | M10042040054X0IWAR | M10162040054X0IWAR |  |  |

| M10082040108X0IWAY | M10042040054X0IWAY | M10162040054X0IWAY |  |  |

| M10082040108X0ISAR | M10042040054X0ISAR | M10162040054X0ISAR |  |  |

| M10082040108X0ISAY | M10042040054X0ISAY | M10162040054X0ISAY |  |  |

| M10082040108X0PWAR | M10042040054X0PWAR | M10162040054X0PWAR |  |  |

| M10082040108X0PWAY | M10042040054X0PWAY | M10162040054X0PWAY |  |  |

| M10082040108X0PSAR | M10042040054X0PSAR | M10162040054X0PSAR |  |  |

| M10082040108X0PSAY | M10042040054X0PSAY | M10162040054X0PSAY |  |  |

| M30082040108X0IWAR | M30042040054X0IWAR | M30162040054X0IWAR |  |  |

| M30082040108X0IWAY | M30042040054X0IWAY | M30162040054X0IWAY |  |  |

| M30082040108X0ISAR | M30042040054X0ISAR | M30162040054X0ISAR |  |  |

| M30082040108X0ISAY | M30042040054X0ISAY | M30162040054X0ISAY |  |  |

| M30082040108X0PWAR | M30042040054X0PWAR | M30162040054X0PWAR |  |  |

| M30082040108X0PWAY | M30042040054X0PWAY | M30162040054X0PWAY |  |  |

| M30082040108X0PSAR | M30042040054X0PSAR | M30162040054X0PSAR |  |  |

| M30082040108X0PSAY | M30042040054X0PSAY | M30162040054X0PSAY |  |  |