-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

RMLV1616A-U

circleActive16Mbit LPSRAM (1M word × 16bit / 2M word x 8bit)

Jump to Page Section:

arrow_drop_down

Overview

Description

The RMLV1616A-U Series is a family of 16-Mbit asynchronous SRAMs organized 1,048,576-word × 16-bit.

The RMLV1616A-U Series has realized higher soft error immunity compared to typical SRAMs with on-chip ECC, archived by Renesas’s unique Advanced LPSRAM technologies. Therefore, it is suitable for battery backup systems.

It is offered in 48pin TSOP (I) or 48-ball fine pitch ball grid array.

Features

- Ultra-low standby current consumption:

- ~25°C: 0.5μA (typ.)/3μA (max.)

- ~85°C: 4.5μA (typ.)/8μA (max.) - High speed access time: 45ns/55ns (max.)

- Higher soft error immunity (< 0.04 FIT/Mb)*1 compared to typical SRAMs with on-chip ECC

- Single 3V supply: 2.7V to 3.6V

- Organized 1,048,576-word × 16-bit (48pin TSOP (I) also configurable as 2,097,152-word × 8bit)

- Easy memory expansion by CS1# and CS2

- No clocks, No refresh

- Common data input and output

- Three state output - Directly TTL compatible

- All inputs and outputs - Battery backup operation

- Available in Pb-free and RoHS applicable package

Note *1. Based on an accelerated test that complies with JEDEC standard JESD89A. Contact us for details.

Comparison

Applications

Documentation

= Featured Documentation

Log in required to subscribe

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 331 KB 日本語 | |

| Guide | PDF 2.00 MB 日本語 | |

| Guide | PDF 182 KB 日本語 | |

| Guide | PDF 471 KB 日本語 | |

| Product Reliability Report | PDF 197 KB | |

| Guide | PDF 1.27 MB 日本語 | |

| Package Outline Drawing | PDF 60 KB | |

7 items

|

||

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Please log in or register to buy

Log in to order

Processing table

PLP |

Pkg. Type |

Carrier Type |

Moisture Sensitivity Level (MSL) |

Buy / Sample |

|

|---|---|---|---|---|---|

| Part Number | |||||

| TBD | FBGA(48) | Tray | 3 | ||

| TBD | FBGA(48) | Embossed Tape | 3 | ||

| TBD | FBGA(48) | Tray | 3 | ||

| TBD | FBGA(48) | Embossed Tape | 3 | ||

| TBD | TSOP(48) | Tray | 3 | ||

| TBD | TSOP(48) | Embossed Tape | 3 | ||

| TBD | TSOP(48) | Tray | 3 | ||

| TBD | TSOP(48) | Embossed Tape | 3 |

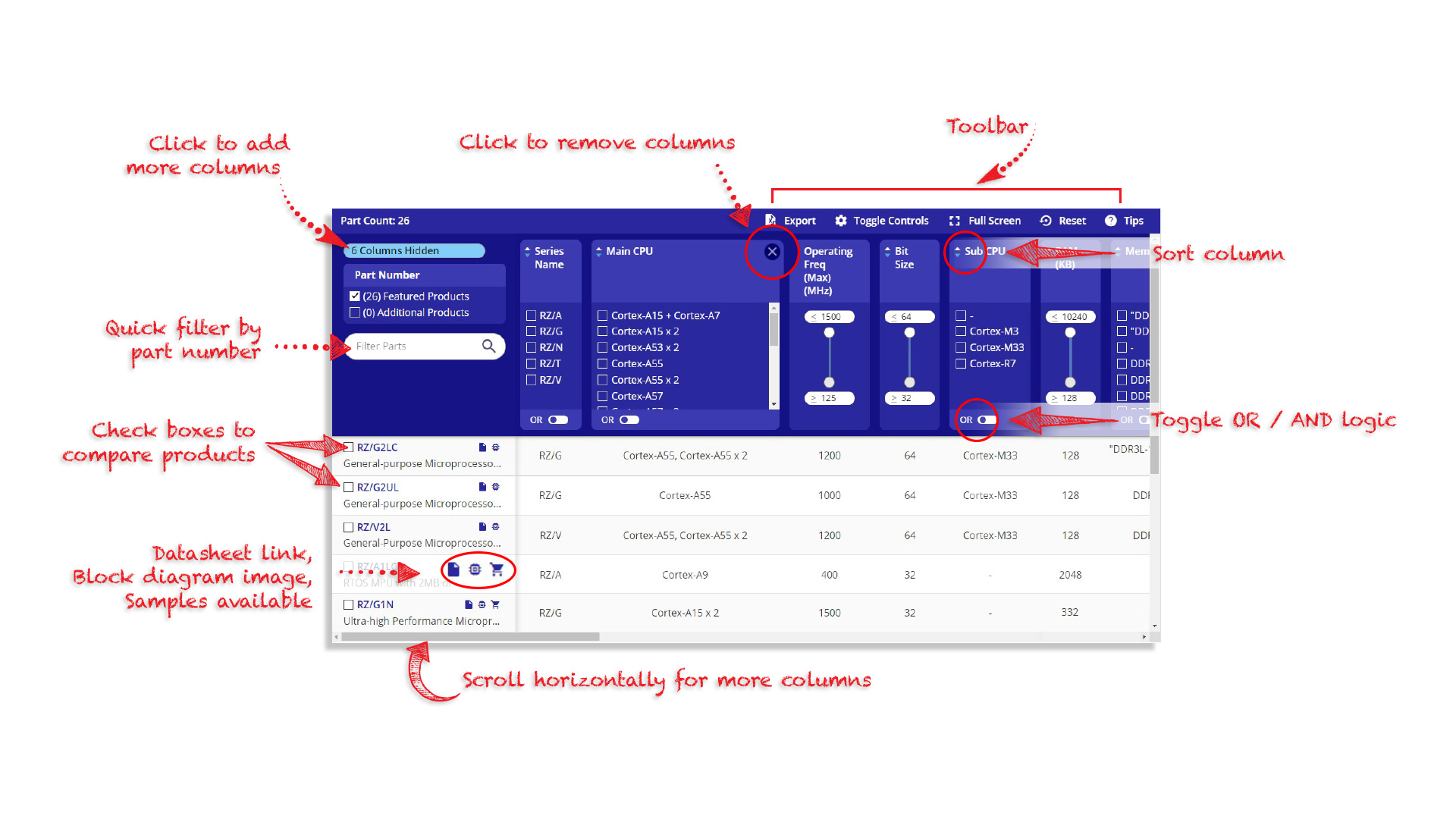

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product