## Introduction

This application note provides some basic guidelines when selecting the proper crystal (XTAL) to work with IDT's family of Synchronization WAN-PLLs™ with low jitter, VCXO-based APPLs. A list of recommended XTAL vendors and parts numbers are provided, and have been categorized based on applicable industry standards.

## VCXO Overview and Definitions

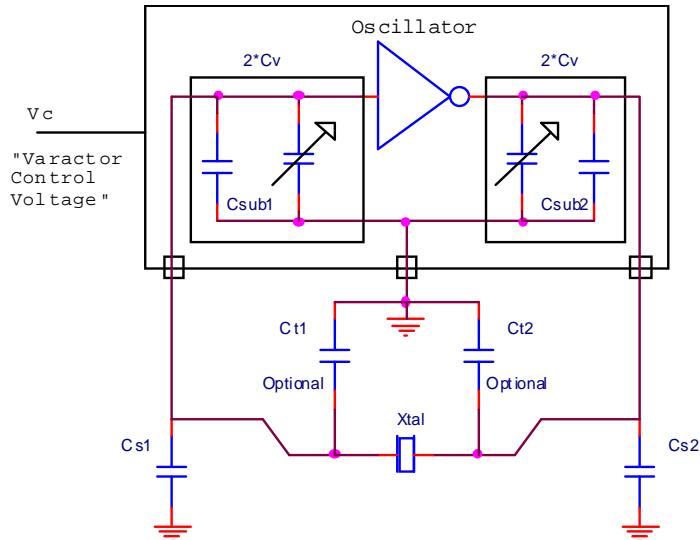

The VCXO consists of four basic components which can be identified in [Figure 1](#) below.

- The crystal.

- The IC oscillator with internal voltage variable capacitors and internal wiring capacities.

- The stray wiring capacity between the IC oscillator and the crystal, including the pads for the IC, crystal and tuning capacitors.

- Optional discrete tuning capacitors to decrease the VCXO center frequency to match the specified crystal frequency

**Figure 1. VCXO Oscillator Circuit**

Where

- Vc = Control voltage to change the VCXO frequency.

- Csub = Internal VCXO parasitic wiring capacity to the IC substrate.

- 2\*Cv = Varactor Capacity and Csub in parallel on oscillator input and output.

- Ct = Tuning capacitors to center the VCXO center frequency.

- Cs = Stray capacities of crystal and tuning capacitor pads and wiring.

The frequency of a parallel resonant fundamental mode crystal, such as used in IDT VCXOs, is specified by crystal frequency at a specified CL, which is the total loading capacity across the two terminals of the crystal. However the various capacitors associated with the wiring and the IC oscillators are all referenced to ground as seen in the figure below. Conversion of these grounded capacitors to equivalent capacitors across the terminals of the crystal is required to ensure that the sum of all the VCXO capacitors does not exceed the CL of the crystal.

The IC inverter forces the currents flowing in parallel combination of the grounded capacitors on the inverter input to be 180 degrees out of phase with the current flowing in the parallel combination of the grounded capacitors at the inverter output. Since the currents are the same, the input and output capacities are effectively in series. Using the varactor capacities as an example, the input and output capacities are  $2*Cv$ . The series capacity is half that of each grounded capacitor, or  $Cv$  and appears equivalently across the crystal terminals. Similarly for the stray and tuning capacitors,  $Cs$  and  $Ct$  respectively.

## Key Crystal Parameters

### Frequency Tolerance

Frequency tolerance, also known as calibration accuracy, is the amount of frequency deviation from a specified center frequency at ambient temperature (referenced at 25°C). It is specified in units of parts-per-million (ppm).

### Frequency Stability

Frequency stability is the amount of frequency deviation from the ambient temperature frequency over the operating temperature range. This deviation is associated with a set of operating conditions including: Operating Temperature Range, Load Capacitance, and Drive Level.

This parameter is specified with a maximum and minimum frequency deviation, expressed in percent (%) or parts per million (ppm). The frequency stability is determined by the following primary factors: Type of quartz cut and angle of the quartz cut. Some of the secondary factors include: mode of operation, drive level, load capacitance, and mechanical design.

### Aging

Aging is the systematic change in frequency with time due to internal changes in the crystal which is related to the crystal contamination and drive level. Over time, particles drop off or fall onto the quartz surface, hence slightly changing the resonant frequency.

Aging is often expressed as a maximum value in parts per million per year [ppm/year]. The rate of aging is typically greatest during the first 30 to 60 days after which time the aging rate decreases. The following factors effect crystal aging: adsorption and desorption of contamination on the surfaces of the quartz, stress relief of the mounting and bonding structures, material outgassing, and seal integrity.

### Hold-In

The hold-in, or frequency accuracy, is a measure of the worst-case offset, in parts-per-million (ppm), one can expect from the nominal frequency over a period of time. This specification is the sum of the maximum static system offset plus the dynamic tracking offset forced upon a PLL by output phase slope limiting system requirements when phase transients are present in the PLL input reference.

For GR-253 Core Issue 5, see Figure 5-18 on page 5-78. The worst case MTIE is required to be equal to  $(7.6+885^*S)nS$  when  $S = 0.14$  for an offset of 0.94 ppm. The dynamic offset is rounded up to 1ppm.

For G.813 Option 1 and G.8262 Option 1, see G.6262 Opt 1 Section 11.4.1, EEC-Option 1. The 7.5 ppm requirement is stated explicitly. This sum of the static and dynamic is rounded up to 13ppm.

| Specifications                                                                       | Maximum Clock Frequency Offset (ppm) | Phase Slope Limiting Offset (ppm) | PLL Tracking Offset (ppm) |

|--------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------|---------------------------|

| 1. GR-253-Core SONET Minimum Clock<br>2. SONET/SDH<br>3. G.813 Option 2              | 20                                   | 0.94                              | 21                        |

| 1. G.813 Option 1<br>2. G.8262 Option 1                                              | 4.6                                  | 7.5                               | 13                        |

| 1. GR1244-Core<br>2. GR-253-Core Stratum 3<br>3. G.812 Type IV<br>4. G.8262 Option 2 | 4.6                                  | 0.94                              | 6                         |

### Pull

Crystals in an HC-49S (low profile) package generally don't have as much pulling range as would a crystal in an HC-49U (high profile) package; crystals in a ceramic package generally have even less. Pullability is usually a function of the size of the termination electrode connected to the crystal blank. A bigger crystal blank, of course, can accommodate a larger electrode. Due to its low profile, an HC-49S crystal has a smaller electrode than an HC-49U, thus a reduced pullability.

## Cs Requirement

Of the three components of the VCXO shown in [Figure 1](#) above, only the stray wiring capacity is not guaranteed by a component vendor. A maximum stray wiring capacity that appears in parallel with the crystal terminals is specified in [Table 1](#) below. This is the series equivalent capacity of Cs1 and Cs2 as shown in [Figure 1](#).

This maximum capacity will guarantee that the pull range of the VCXO will be symmetric about the nominal center frequency under the condition of the CL and Cv capacities specified in [Table 1](#). It is the responsibility of the board designer to ensure that this maximum is not exceeded. It is preferable that the wiring capacity is less than the maximum, allowing tuning caps to be installed to make a fine adjustment of the VCXO center frequency.

**Table 1: WAN-PLL VCXO-based APLL Capacitance Requirements**

| Symbol  | Parameter                                                      | Typical (pF) | Max (pF) |

|---------|----------------------------------------------------------------|--------------|----------|

| Cs      | Equivalent Parallel Stray capacity                             |              | 1.9      |

| CL      | Crystal Parallel Load Capacity at the nominal center frequency | 10           |          |

| Cv_LOW  | Low Varactor Capacitance                                       | 5.4          |          |

| Cv_HIGH | High Varactor Capacitance                                      | 12.7         |          |

CL = 10pF is set for the best match between the varactor capacities and stray capacitances achievable on a printed wiring board. The maximum stray capacitance requirement is determined by the crystal load curve. The interested reader is pointed to [IDT AN-841](#) for the stray capacity limit and to [AN-831](#) for the crystal load curve.

## Determination of VCXO Margin Against the Application APR

The application's Absolute Pull Range requirement (APR), is the guaranteed pull range of the VCXO after all crystal tolerances have been accounted for. The accounting begins with the pull range of a properly tuned VCXO and subtracts all the known tolerances as well as the application APR. The remainder is the Margin against APR and must be greater than zero.

### Example: Calculating a VCXO's APR Margin Budget

[Table 2](#) shows an example of an HC49S crystal electrical specification. Most manufacturers have similar values and variables. For such a crystal and a VCXO with the capacities shown in [Table 1](#) above, the pull range of the VCXO is  $\pm 120$  ppm. Since all tolerances and APR are symmetric, it suffices to use only positive values.

**Table 2: Example of an HC49S Crystal Electrical Specification**

| Symbol         | Parameter                    | Test Conditions | Minimum | Typical     | Maximum                                       | Units |

|----------------|------------------------------|-----------------|---------|-------------|-----------------------------------------------|-------|

|                | Mode of Oscillation          |                 |         | Fundamental |                                               |       |

| f <sub>N</sub> | Frequency                    |                 |         | 25          |                                               | MHz   |

| f <sub>T</sub> | Frequency Tolerance          | @ 25°C          |         |             | $\pm 20$                                      | ppm   |

| f <sub>S</sub> | Frequency Stability          | -40°C to +85°C  |         |             | $\pm 20$                                      | ppm   |

|                | Operating Temperature Range  |                 | -40     |             | 85                                            | °C    |

| C <sub>L</sub> | Load Capacitance             |                 |         | 10          |                                               | pF    |

| C <sub>O</sub> | Shunt Capacitance            |                 |         | 3.3         |                                               | pF    |

| C <sub>1</sub> | Motional Capacitance         |                 |         | 12.7        |                                               | fF    |

| ESR            | Equivalent Series Resistance |                 |         |             | 40                                            | Ω     |

|                | Drive Level                  |                 |         | 100         | 200                                           | μW    |

|                | Aging @ 25°C                 |                 |         |             | $\pm 5$ over 1 year<br>$\pm 20$ over 20 years | ppm   |

Using the crystal tolerances from the HC49S crystal above in [Table 2](#), the margin against APR is calculated as shown in [Table 3](#) and [Table 4](#) below.

**Table 3: HC49S Margin Against APR**

|                   | <b>SynchE</b> | <b>SONET/SDH</b> | <b>Units</b> |

|-------------------|---------------|------------------|--------------|

| VCXO Pull Range   | 120           | 120              | ppm          |

| Crystal Tolerance | -20           | -20              | ppm          |

| Crystal Stability | -20           | -20              | ppm          |

| Aging (20 yrs)    | -20           | -20              | ppm          |

| APR               | -13           | -21              | ppm          |

| <b>Margin</b>     | <b>47</b>     | <b>39</b>        | <b>ppm</b>   |

In the same manner, the margin against APR can be calculated for a 5032 crystal with the same capacities as [Table 1](#), but with  $C_0 = 2.2\text{pF}$  and  $C_1 = 8.4\text{fF}$ . The pull range is  $\pm 95\text{ ppm}$ .

**Table 4: 5032 Margin Against APR**

|                   | <b>SynchE</b> | <b>SONET/SDH</b> | <b>Units</b> |

|-------------------|---------------|------------------|--------------|

| VCXO Pull Range   | 95            | 95               | ppm          |

| Crystal Tolerance | -20           | -20              | ppm          |

| Crystal Stability | -20           | -20              | ppm          |

| Aging (20 yrs)    | -20           | -20              | ppm          |

| APR               | -13           | -21              | ppm          |

| <b>Margin</b>     | <b>22</b>     | <b>14</b>        | <b>ppm</b>   |

## XTAL Layout Considerations

The objective is to avoid adding any noise to the clock between the crystal and XTALn\_IN/OUT pins. Below are some guidelines when co-locating the crystal with the PLL.

1. Place tuning capacitors symmetrically across the crystal terminals. Connect the ground terminals together and tie with a single via to the IC ground. See [Figure 1](#) for schematic representation.

2. Keep the crystal bond pads and trace width to the XTALn\_IN/OUT pins as small as possible. Routing should be done on top layer with no vias.

3. Clocks and frequently switched signals should not be routed close to the crystals.

4. Digital signals should not be routed directly under the crystal or XTALn\_IN/OUT pins.

5. All metal layers in the PCB are recommended to be removed under the XTALn\_OUT ball, crystal pad and associated trace.

6. It is recommended to protect crystal traces with ground traces and guard rings.

For ceramic packages, provide an option for load tuning capacitors, in case fine tuning is needed or for centering the nominal frequency.

## Example Crystal Layouts

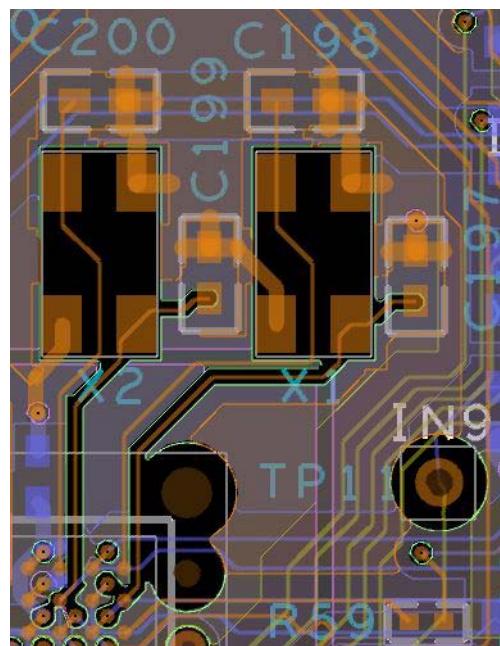

**Figure 2. HC49S Layout**

**Figure 3. 5032 Layout (with load tuning caps)**

## Target Standards and Recommended Crystals

The following tables categorize recommended crystal vendors and parts numbers based on applicable industry standards. This is not meant to be an exhaustive list, but does highlight parts that have proven to be suitable with IDT's synchronization WAN-PLLs in meeting applicable industry standards.

### GR-253-Core SONET Minimum Clock / G.813 Option 2 / SONET/SDH Line Card

Frequency Accuracy/Hold-In (20 years<sup>1</sup>):  $\pm 21\text{ppm}$

| XTAL Vendor                                                         | Part Order Number<br>(XTAL Family) | Pkg           | Temperature Range | Notes |

|---------------------------------------------------------------------|------------------------------------|---------------|-------------------|-------|

| <b>24.8832 MHz (SONET)</b>                                          |                                    |               |                   |       |

| Fox<br>( <a href="http://www.foxonline.com">www.foxonline.com</a> ) | 278LF-24.8832-3<br>(HC49SDLF)      | HC-49S<br>SMD | -40°C to +85°C    | 1     |

| <b>25 MHz (ETH)</b>                                                 |                                    |               |                   |       |

| Fox<br>( <a href="http://www.foxonline.com">www.foxonline.com</a> ) | 278LF-25-336<br>(HC49SDLF)         | HC-49S<br>SMD | -40°C to +85°C    | 1     |

| <b>25.78125 MHz (ETH LAN)</b>                                       |                                    |               |                   |       |

| Fox<br>( <a href="http://www.foxonline.com">www.foxonline.com</a> ) | 278LF-25.78125-1<br>(HC49SDLF)     | HC-49S<br>SMD | -40°C to +85°C    | 1     |

| 1. Tested in the lab by IDT                                         |                                    |               |                   |       |

**G.813 Option 1 / G.8262 Option 1 / SyncE Line Card**Frequency Accuracy/Hold-In (1 year):  $\pm 13\text{ppm}$

| XTAL Vendor                                                           | Part Order Number<br>(XTAL Family) | Pkg         | Temperature Range | Notes |

|-----------------------------------------------------------------------|------------------------------------|-------------|-------------------|-------|

| <b>NOTE: All XTALs listed in previous table(s) are also suitable.</b> |                                    |             |                   |       |

| <b>24.8832 MHz (SONET)</b>                                            |                                    |             |                   |       |

| Fox<br>(www.foxonline.com)                                            | 495-24.8832-2<br>(FX532B)          | 5032<br>SMD | -40°C to +85°C    |       |

| MtronPTI<br>(www.mtronpti.com)                                        | M1325S141<br>(M1325)               | 5032<br>SMD | -40°C to +85°C    | 1     |

| Rakon<br>(www.rakon.com)                                              | 513810<br>(IFF10RSX-5)             | 5032<br>SMD | -40°C to +85°C    |       |

| <b>25 MHz (ETH)</b>                                                   |                                    |             |                   |       |

| Fox<br>(www.foxonline.com)                                            | 495-25-141<br>(FX532B)             | 5032<br>SMD | -40°C to +85°C    |       |

| MtronPTI<br>(www.mtronpti.com)                                        | M1325S139<br>(M1325)               | 5032<br>SMD | -40°C to +85°C    |       |

| Rakon<br>(www.rakon.com)                                              | 512839<br>(IFF10RSX-5)             | 5032<br>SMD | -40°C to +85°C    | 1     |

| <b>25.78125 MHz (ETH LAN)</b>                                         |                                    |             |                   |       |

| Fox<br>(www.foxonline.com)                                            | 495-25.78125-2<br>(FX532B)         | 5032<br>SMD | -40°C to +85°C    |       |

| MtronPTI<br>(www.mtronpti.com)                                        | M1325S142<br>(M1325)               | 5032<br>SMD | -40°C to +85°C    | 1     |

| Rakon<br>(www.rakon.com)                                              | 513805<br>(IFF10RSX-5)             | 5032<br>SMD | -40°C to +85°C    |       |

| <b>24.576 MHz (CPRI)</b>                                              |                                    |             |                   |       |

| Rakon<br>(www.rakon.com)                                              | 513809<br>(IFF10RSX-5)             | 5032<br>SMD | -40°C to +85°C    |       |

| 1. Tested in the lab by IDT                                           |                                    |             |                   |       |

**GR1244-Core / GR-253-Core Stratum 3 / G.812 Type IV / G.8262 Option 2**Frequency Accuracy/Hold-In (20 years<sup>2</sup>):  $\pm 6\text{ppm}$

| XTAL Vendor                                                           | Part Order Number<br>(XTAL Family) | Pkg | Temperature Range | Notes |

|-----------------------------------------------------------------------|------------------------------------|-----|-------------------|-------|

| <b>NOTE: All XTALs listed in previous table(s) are also suitable.</b> |                                    |     |                   |       |

2. Per Telcordia GR-1244-CORE; ITU-T specifies 1 year

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).