# **Application Note** Class-D Audio Amplifier

# AN-CM-216

# Abstract

This application note shows how to create a Class-D Audio Amplifier using GreenPAK<sup>™</sup> SLG46140V. This application note comes complete with design files which can be found in the References section.

# Contents

| Ab  | stract                   | 1  |

|-----|--------------------------|----|

| Со  | ntents                   | 2  |

| Fig | jures                    | 2  |

| 1   | Terms and Definitions    | 3  |

| 2   | References               | 3  |

| 3   | Introduction             | 4  |

| 4   | Input and Output Signals | 4  |

| 5   | GreenPAK Design          | 6  |

| 6   | Results                  | 9  |

| 7   | Conclusion               | 11 |

| Re  | vision History           | 12 |

# **Figures**

| Figure 1: Timing Diagrams for the Different Stages of the Class D Audio Amplifier | . 4 |

|-----------------------------------------------------------------------------------|-----|

| Figure 2: Circuit Diagram                                                         | . 5 |

| Figure 3: GreenPAK Design                                                         |     |

| Figure 4: VREF Properties                                                         | . 6 |

| Figure 5: ACMP0 Properties                                                        | . 7 |

| Figure 6: PWM Output Relative to ADC Value                                        | . 7 |

| Figure 7: Break-Before-Make Outputs                                               | . 8 |

| Figure 8: pFET0 and nFET1 are ON                                                  | . 8 |

| Figure 9: pFET1 and nFET0 are ON                                                  | . 9 |

| Figure 10: System Input is a 262 Hz Sine Wave (middle C)                          | . 9 |

| Figure 11: 70% Output Duty Cycle, ANALOG_IN ≈ 700 mV                              | 10  |

| Figure 12: 50% Output Duty Cycle, ANALOG_IN ≈ 550 mV                              | 10  |

| Figure 13: 30% Output Duty Cycle, ANALOG_IN ≈ 400 mV                              | 11  |

| Figure 14: Amplified Output                                                       | 11  |

# **1** Terms and Definitions

| ACMP | Analog comparator module    |

|------|-----------------------------|

| ADC  | Analog to digital converter |

| CNT  | Counter                     |

| DLY  | Delay                       |

| LC   | Inductor and capacitor      |

| PWM  | Pulse-width modulation      |

| VREF | Voltage-reference           |

# 2 References

For related documents and software, please visit:

#### GreenPAK<sup>™</sup> Programmable Mixed-Signal Products | Renesas

Download our free GreenPAK Designer software [1] to open the .gp files [2] and view the proposed circuit design. Use the GreenPAK development tools [3] to freeze the design into your own customized IC in a matter of minutes. Renesas Electronics provides a complete library of application notes [4] featuring design examples as well as explanations of features and blocks within the IC.

- [1] GreenPAK Designer Software, Software Download and User Guide, Renesas Electronics

- [2] AN-CM-216 Class-D Audio Amplifier.gp, GreenPAK Design File, Renesas Electronics

- [3] GreenPAK Development Tools, GreenPAK Development Tools Webpage, Renesas Electronics

- [4] GreenPAK Application Notes, GreenPAK Application Notes Webpage, Renesas Electronics

- [5] SLG46140V, Datasheet, Renesas Electronics

# 3 Introduction

In this app note, we will use a GreenPAK<sup>™</sup> SLG46140V to create a Class-D Audio Amplifier. A Class-D amplifier takes an analog audio signal, converts it into a digital PWM signal, and then filters the PWM signal to recapture the analog signal with a greater amplitude for greater volume.

# 4 Input and Output Signals

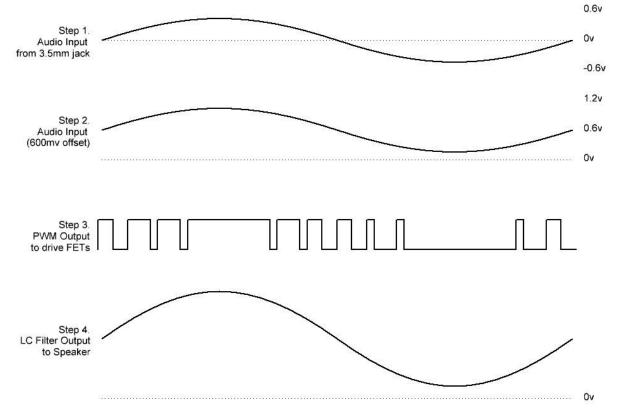

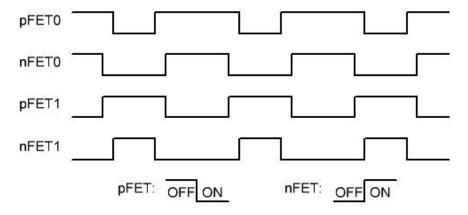

Figure 1 shows the input and output signals used in this app note. The analog waves that come out of an iPhone headphone jack are centered around 0 v and have an amplitude of between 1-2 v. We need to process that analog signal through our GreenPAK's ADC (analog to digital converter), but the GreenPAK ADC can only convert positive values from 50 mv to 1200 mv. This means that the first thing we need to do is add a 600 mv DC offset to the input signal. The amplitude of the input signal remains the same, but it is now centered around 600 mv as shown in Step 2 of Figure 1.

Figure 1: Timing Diagrams for the Different Stages of the Class D Audio Amplifier

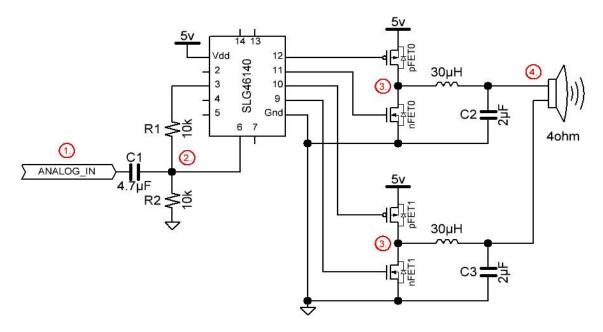

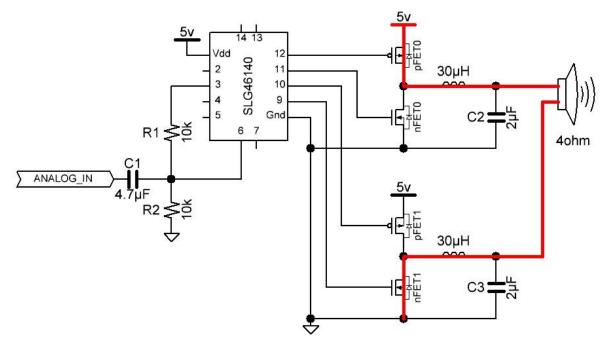

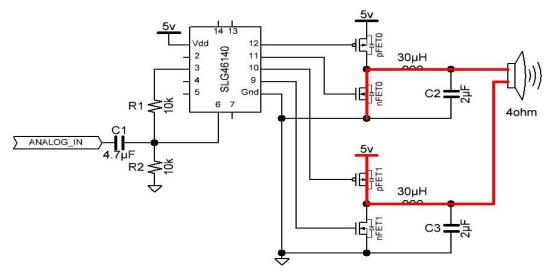

We can do that by adding a series capacitor and a resistive divider to our circuit, as shown in Step 2 of Figure 2. The voltage coming out of the GreenPAK's Pin3 is 1.2 v, which means that the waveform that enters Pin6 will be centered around 0.6 v. We'll discuss how to create that 1.2 v rail in the GreenPAK Design section.

The GreenPAK takes the voltage that it receives at Pin6 and converts it into several different PWM signals which are output on Pins 9-12. Those signals are used to control the gates of 4 MOSFETs which are configured as an H-Bridge. In order to maximize the voltage potential across the speaker, pFET0 and nFET1 are turned on at the same time, and pFET1 and nFET0 are turned on at the same time.

| Application Note | Revision 1.0 | 24-Nov-2017 |

|------------------|--------------|-------------|

|                  |              |             |

To recreate our analog input signal, we added a pair of LC filters to both sides of the H-Bridge. The outputs of both filters are connected to the speaker terminals.

#### Figure 2: Circuit Diagram

We desired a cutoff frequency of 20kHz, since that is the upper range of human hearing. We measured the speaker impedance at  $4\Omega$ , and used those values to calculate the capacitance and inductance needed for our LC filters.

$$L = \frac{Z}{2\pi f_c} = \frac{4}{2\pi * 20000} = 31.8\mu H \approx 30\mu H$$

$$C = \frac{1}{2\pi f_c Z} = \frac{1}{2\pi * 20000 * 4} = 1.989\mu F \approx 2\mu F$$

# 5 GreenPAK Design

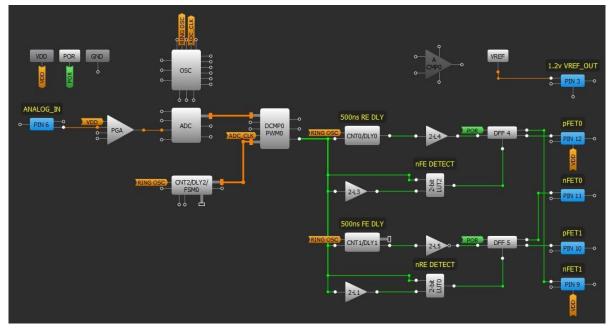

#### Figure 3: GreenPAK Design

The first thing we needed to do in the GreenPAK design was to create a 1.2 v rail to help add the 600 mV offset to our input signal. We accomplished this by configuring the VREF block so that it outputs the ACMP0 threshold to Pin3. We set ACMP0's threshold to 1200 mV as shown in Figure 5.

| Properties                  |                | × |

|-----------------------------|----------------|---|

|                             | VREF           |   |

| Chopper clock<br>frequency: | 2 MHz          | • |

| Opamp offset<br>chopper:    | Enable         |   |

| Source selector:            | ACMP0 IN-      | • |

| A CMP0<br>reference volt.   | 1200 mV        | * |

| A CMP1<br>reference volt.   | 50 mV          | * |

| Con                         | nections       |   |

| Output                      | PIN 3          | v |

| Power                       | ctrl. settings |   |

**Figure 4: VREF Properties**

**Application Note**

**Revision 1.0**

| Properties                     |           | × |  |

|--------------------------------|-----------|---|--|

| A                              | CMP0      |   |  |

| Hysteresis:                    | Disable   | • |  |

| Low bandwidth:                 | Disable   | • |  |

| Input 100uA<br>current source: | Disable   | • |  |

| IN+ gain:                      | Disable   | • |  |

| Cor                            | inections |   |  |

| IN+ source:                    | PIN 10    | • |  |

| IN- source:                    | 1200 mV   | • |  |

**Figure 5: ACMP0 Properties**

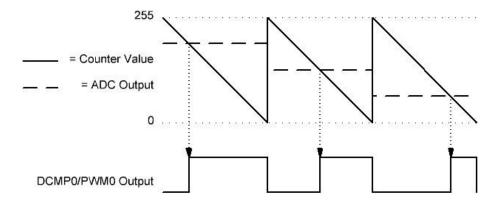

Pin6 receives the analog input signal with the 600 mV offset. The signal is passed through the PGA with a gain of x1, and then is converted into an 8-bit value by the ADC. Meanwhile, CNT2/DLY2 is configured as an 8-bit ripple counter and its clock line is connected to the GreenPAK's 25 MHz RING oscillator. CNT2's count value starts at 255, and every time it is clocked the count value is decremented. When CNT2 has counted 255 clocks, it rolls over to 255 and continues to count down. The DCMP0/PWM0 block is used to generate a PWM output so that when the ADC value is greater than the CNT2 value, the DCP0/PWM0 block outputs HIGH, as shown in Figure 6. This means that when the Analog voltage at Pin6 is higher, the ADC will output a bigger 8-bit number, and the DCMP's output pulse length will be longer.

Figure 6: PWM Output Relative to ADC Value

The output of the DCMP0/PWM0 block is sent through some break-before-make circuitry to ensure that our external H-bridge works properly. We want to make sure that pFET0 and nFET0 are never turned on at the same time, which would short our power supply to ground. Likewise, we never want pFET1 and nFET1 to be turned on at the same time.

We used delay blocks, DFFs, and edge detectors to create the break-before-make circuitry. When the output of DCMP0 goes HIGH, the rising edge detector composed of 2-bit LUT1 and 2-bit LUT0 is used to reset DFF5, which turns off both nFET0 and pFET1. 500 ns later, DLY0 clocks POR through DFF4, which will turn on nFET1 and pFET0. The same timing occurs in the inverse when there is a falling edge on the output of DCMP0.

| Application Note | Revision 1.0 | 24-Nov-2017 |

|------------------|--------------|-------------|

|                  |              |             |

Figure 7: Break-Before-Make Outputs

When opposite sides of the H-Bridge are ON at the same time, the full power supply voltage can be delivered to the speaker.

Figure 8: pFET0 and nFET1 are ON

Figure 9: pFET1 and nFET0 are ON

The LC filters smooth out the outputs to create a less choppy signal, thus recreating the original audio waveform.

# 6 Results

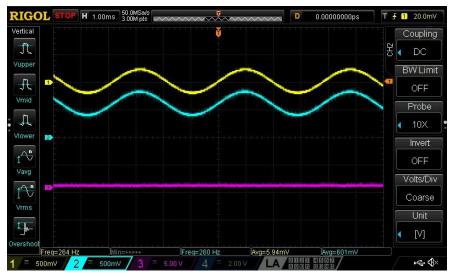

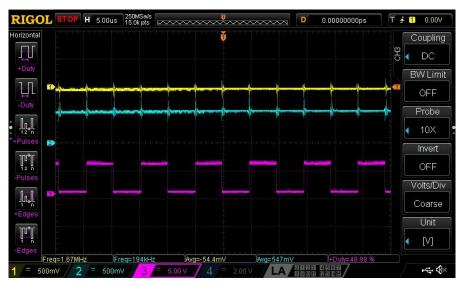

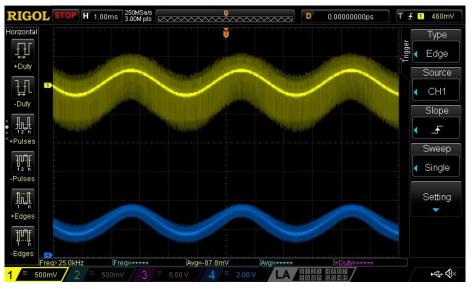

In the following oscilloscope waveforms, the channels were connected to the following signals:

Channel 1 (yellow) – Output from 3.5 mm audio jack

Channel 2 (blue) - Pin6 (ANALOG\_IN)

Channel 3 (pink) – Pin9 (nFET1)

Channel 4 (dark blue) - Output of top LC filter

We tested our circuit with a 262 Hz sinewave, which corresponds to the note "Middle C." As you can see in Figure 10, the ANALOG\_IN signal has a 600 mV DC offset from the audio jack output. In Figure 10, we disconnected the GreenPAK's Pins 9-12 to reduce switching noise.

Figure 10: System Input is a 262 Hz Sine Wave (middle C)

**Application Note**

**Revision 1.0**

24-Nov-2017

If we enable Pins 9-12 and zoom in, we can see the duty cycle of Pin9 change at different points in the sinewave. We also encounter some switching noise. This is shown in Figure 11, Figure 12, and Figure 13.

Figure 11: 70% Output Duty Cycle, ANALOG\_IN ≈ 700 mV

Figure 12: 50% Output Duty Cycle, ANALOG\_IN ≈ 550 mV

Figure 13: 30% Output Duty Cycle, ANALOG\_IN ≈ 400 mV

In Figure 14, when we zoom back out you can see that the input waveform has been amplified by our circuit and the output is the same frequency as the input. To hear the amplifier in action, watch the video connected to this app note.

Figure 14: Amplified Output

# 7 Conclusion

In this app note we created a Class-D amplifier with a GreenPAK SLG46140V and a few passive external components. We created a DC offset to prepare the input signal to be processed by the GreenPAK's ADC and used an H-Bridge with a pair of LC filters on the output to recreate the input signal.

Since this design only uses about half of the digital logic resources inside the SLG46140V, a designer could use the rest of the logic blocks to add more functionality to the design.

| <b>Application No</b> | to l |

|-----------------------|------|

| ADDIICATION NO        | Le   |

**Revision 1.0**

# **Revision History**

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.0      | 24-Nov-2017 | Initial Version |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.