# RENESAS

Daisy-Chain SPI Using Quad SLG47011 SLG47011V

This application note describes the design for daisy-chaining SPI signals across four SLG47011 ICs.

# Contents

| Terr | ns and Definitions                                                     | 1  |

|------|------------------------------------------------------------------------|----|

| Refe | erences                                                                | 1  |

| 1.   | Introduction                                                           | 2  |

| 2.   | Design Principle                                                       | 3  |

| 3.   | GreenPAK Design Internal Block Configuration                           | 7  |

| 4.   | Simulation Results                                                     | 16 |

| 5.   | Design Verification Using Hardware Prototype                           | 17 |

|      | 5.1 Inspection: Reading Data from DLY/CNT, [h0139, h013A]              | 17 |

|      | 5.2 Capturing ADC Data: Reading Channel_0 from Buffer0, [h2202, h2203] | 18 |

| 6.   | Conclusion                                                             | 18 |

| 7.   | Revision History                                                       | 19 |

### **Terms and Definitions**

| ADC     | Analog to Digital Converter |

|---------|-----------------------------|

| AFE     | Analog Front-End            |

| CMD     | Command                     |

| CNT/DLY | Counter and Delay           |

| LUT     | Look Up Table               |

| PGA     | Programmable Gain Amplifier |

| SHR     | Shifter Register            |

| SPI     | Serial Peripheral interface |

# References

For related documents and software, please visit: AnalogPAK | Renesas

Download our free Go Configure Software Hub [1] to open the .aap file [2] and view the proposed circuit design. Use the AnalogPAK development tools [3] to freeze the design into your own customized IC in a matter of minutes. Renesas Electronics provides a complete library of application notes [4] featuring design examples, as well as explanations of features and blocks within the Renesas IC.

[1] GreenPAK Go Configure Software Hub, Software Download and User Guide, Renesas Electronics

[2] AN-CM-414 Daisy-Chain SPI Using Quad SLG47011, AnalogPAK Design File, Renesas Electronics

- [3] <u>GreenPAK Development Tools</u>, AnalogPAK Development Tools Webpage, Renesas Electronics

- [4] GreenPAK Application Notes, GreenPAK Application Notes Webpage, Renesas Electronics

Author: Paul Yeh, Sr. Application Engineer, Renesas Electronics

### 1. Introduction

This application note presents a daisy-chained SPI design for four SLG47011 chips. SPI is a high-speed protocol (>1 MHz) that transfers data between an MCU and multiple peripherals using Chip-Select (CS), Serial Clock (SCLK), Master-Out-Slave-In (MOSI), and optionally, Master-In-Slave-Out (MISO) signals.

There are two ways to connect multiple devices:

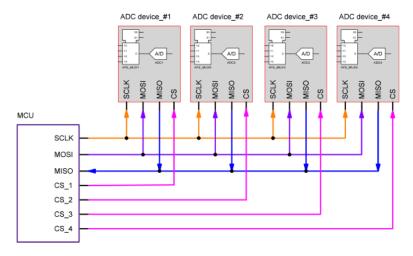

- In Figure 1, an MCU provides multiple Chip-Select (CS) signals to corresponding peripheral ADC devices. Each Chip-Select signal is independently connected to a peripheral device. This method of SPI connection requires complicated PCB layout/subnodes and additional GPIO utilization. In addition, the MCU cannot capture ADC data from the ADC devices synchronously.

- Daisy-Chain SPI, as shown in Figure 2, is developed to simplify subnodes using only one Chip-Select (CS) signal. The MCU provides a single Chip-Select (CS) signal that is sent to all peripheral ADC devices. Meanwhile, MOSI and MISO signals are integrated using a daisy-chain configuration. While the CS signal activates all peripheral ADC devices, each ADC device can transfer its own data in sequence to the MCU. Therefore, the MCU can capture multiple instances of ADC data simultaneously.

Figure 1: General SPI Connection Diagram

Figure 2: Daisy-Chain SPI Connection Diagram

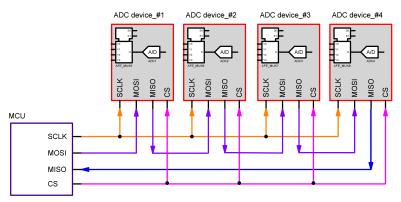

The SLG47011 is comprised of a diverse collection of digital and analog marcocells for AFE applications. One 14-bit SAR ADC and one 4-channel PGA (shown in the Block Diagram of the SLG47011 in Figure 3 are used to perform Analog Front-End signal capturing. The PGA is capable of operating in different configurations including

single-ended mode and differential mode. Additionally, the reference voltages used by the PGA and ADC can be configured independently as needed. The ADC supports resolutions ranging from 8 bits to 14 bits. Moreover, the SLG47011 offers four Buffer blocks in which averaging and over-sampling functions are used to process ADC data.

Figure 3: SLG47011 Block Diagram

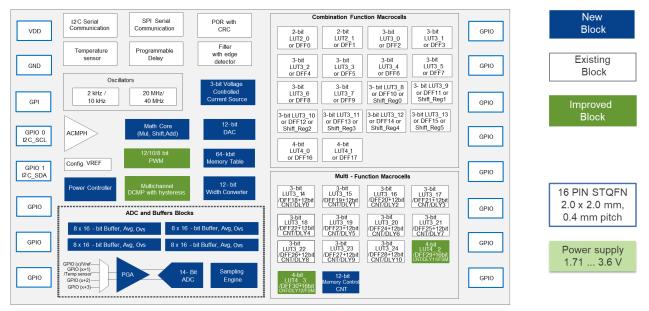

# 2. Design Principle

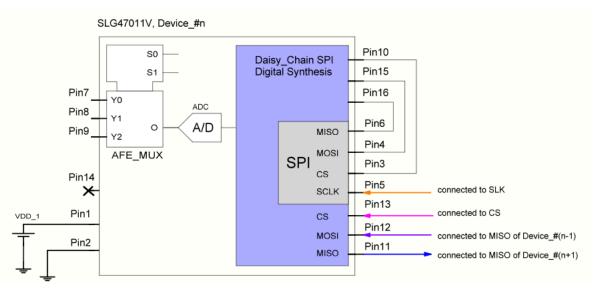

Figure 4 shows the system diagram of a Daisy chain SPI connection. Each SLG47011 provides 3 external AFE inputs (Pin7, Pin8, and Pin9). The SPI interface I/O inherited from the SLG47011 provides the CS(PIN3), SCLK (PIN5), MOSI (PIN4) and MISO (PIN6) connections. To create Daisy-chain SPI based on inherited SPI, we use the internal digital blocks of the SLG47011 and utilize GPIO Pins to synthesize the required function. Pin16, Pin15, and Pin10 are assigned to connect the inherited SPI interface I/O directly. Compared to an Inherited SPI interface I/O, the Daisy Chain SPI interface I/O represented by CS (Pin13), SCLK (PIN5), MOSI (PIN12), and MISO (PIN11). Therefore, MCU would read the data via Daisy Chain SPI interface I/O. Figure 5 shows the Pin connections of a single chip as a reference. Since the inherited SPI macrocell in the SLG47011V cannot support an internal connection using Matirix I/O, GPIO Pins are used to carry out the design. Since the propagation delay of the GPIO Pins is greater than that of the Matrix I/O, it is estimated that the SPI baud rate frequency (SCLK) should be limited to be less than 3.4 MHz.

Figure 4: System Diagram of using Quad-Chips in a Daisy-Chain SPI Connection

Figure 5: Pin Assignment for a Single-Chip Implemented in a Daisy-Chain SPI Design

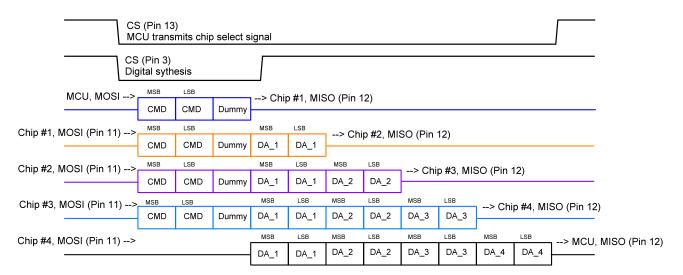

A diagram of the SPI signal sequence of Daisy chain SPI is shown in Figure 6. The master MCU device sends one SPI command to collect required data from all peripheral devices (chip\_1~4). Once an individual peripheral device receives a command, it will transfer internal data via the inherited SPI macrocell. To manipulate the internal data in sequence, the digital synthesis subcircuit, in Figure 5, needs to initiate the serial-in/serial-out process. Since the CMD signal or Data signals will be propagated through a string of peripheral devices, Pin 10 and Pin 15 are regarded as the main subnodes and must succeed to transfer data and receive the CMD signal, separately. SCLK can be used to allocate the Data sequence transfer and interconnection period.

Figure 6: SPI Signal Sequence Diagram of Daisy Chain SPI

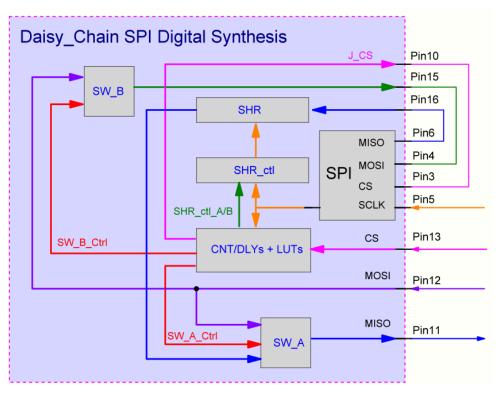

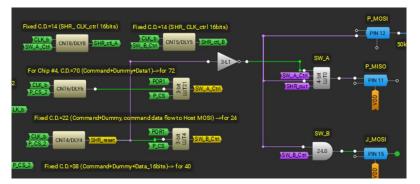

In Figure 7, the block diagram illustrates the basic digital synthesis design. SW\_A and SW\_B are the switches used for sending CMD and Data. The CNT/DLYs + LUTs block provides the CS signal to the inherited SPI block. The Inherited SPI block transfers the corresponding data associated with the unique CMD in all chips. The SHR shifts the data from the inherited SPI block using its specific register lengths setting. Therefore, data from each individual chip is arranged in order. We utilize the macrocells of the SLG47011V to fulfill this required functionality.

Figure 7: Block Diagram of the Daisy Chain SPI Digital Synthesis

# 3. GreenPAK Design Internal Block Configuration

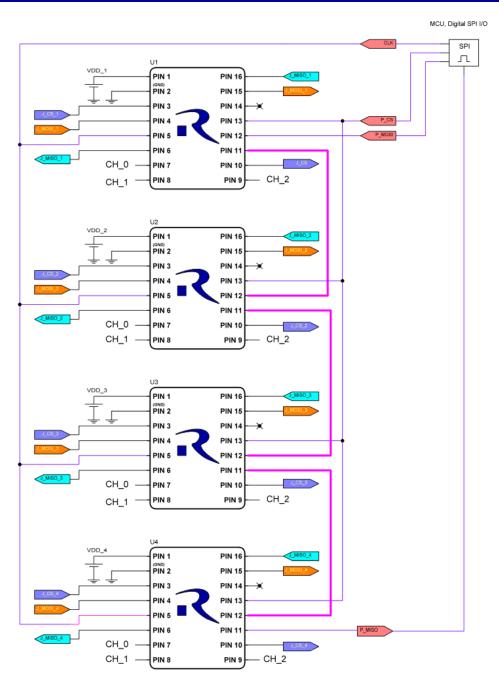

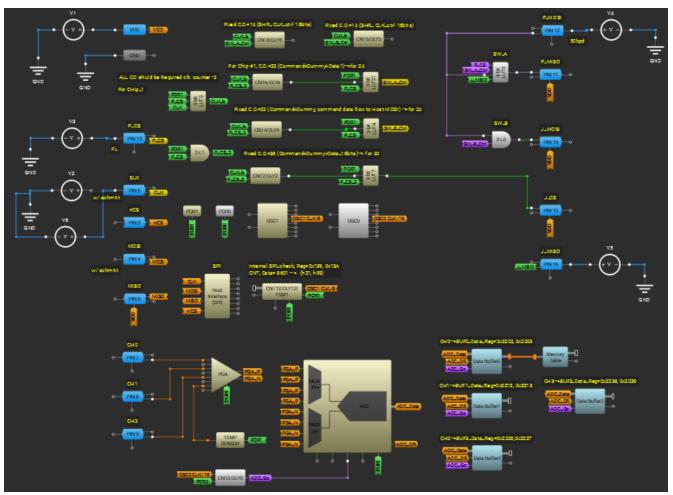

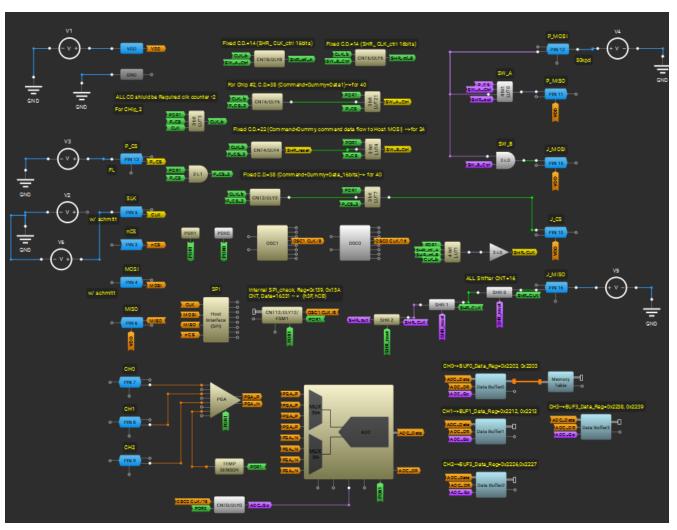

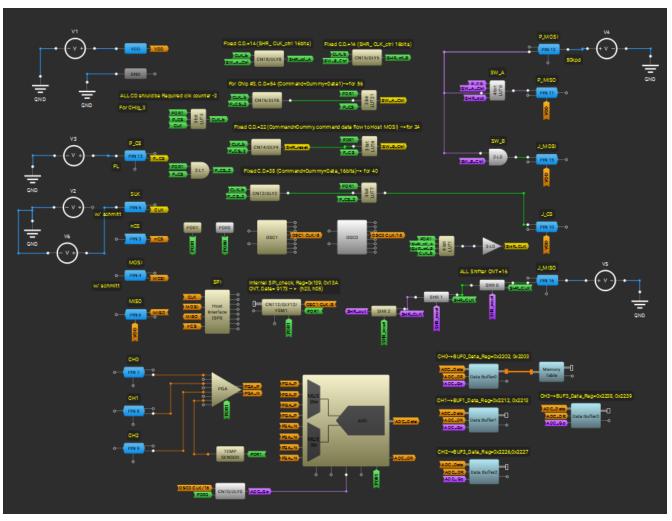

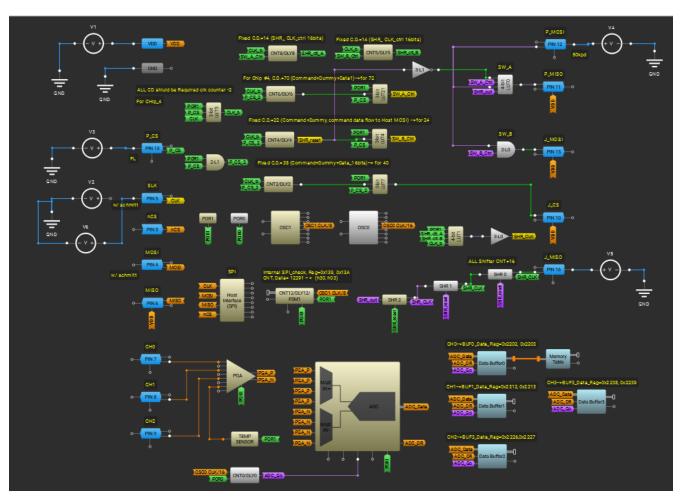

All GreenPAK Designs shown in the Go Configure Software are presented in Figure 8 - Figure 11. The configuration descriptions follow.

Figure 8: GreenPAK Designer Schematic (Daisychain\_SPI\_CHIP\_1.aap)

#### Daisy-Chain SPI Using Quad SLG47011

Figure 9: GreenPAK Designer Schematic (Daisychain\_SPI\_CHIP\_2.aap)

#### Daisy-Chain SPI Using Quad SLG47011

Figure 10: GreenPAK Designer Schematic (Daisychain\_SPI\_CHIP\_3.aap)

#### Daisy-Chain SPI Using Quad SLG47011

Figure 11: GreenPAK Designer Schematic (Daisychain\_SPI\_CHIP\_4.aap)

As shown in Figure 7, SW\_A and SW\_B functions are accomplished by using LUT macrocells. The logic configuration of these macrocells is shown in Figure 12.

Figure 12: LUT Configuration for SW\_A and SW\_B

Also shown in Figure 7, the SHR (Shifter register) processes the data from the inherited SPI block. In order to ensure the data sequence is integrated into the final MOSI bus of chip\_4, we have to use three SHR macrocells to output data in sequence. In our design, chip\_1 is not equipped with a SHR block due to data first-in-first-out principles, as shown in Figure 8. The total register length settings of the SHR blocks are set to 18. This configuration is shown in Figure 13.

| ALL Shifter ONT-16 J_MISO | Properties<br>3-bit LUT10/DF   | F/LATCH12/Shift F | Regi | Properties<br>3-bit LUT9/DFF/  | LATCH11/Shift Reg | 🔀<br>gist | Properties<br>3-bit LUT8/DFF/  | LATCH10/Shift Reg | gist |

|---------------------------|--------------------------------|-------------------|------|--------------------------------|-------------------|-----------|--------------------------------|-------------------|------|

| + SHI COCK                | Туре:                          | Shift Register    | •    | Туре:                          | Shift Register    | •         | Туре:                          | Shift Register    | •    |

| SPRONT BHR2 EXECUT        | Register length:               | 2                 | •    | Register length:               | 8                 | \$        | Register length:               | 8                 | ¢    |

|                           | Initial<br>value [1:0]:        | 00                | ٢    | Initial<br>value [7:0]:        | 00000000          | \$        | Initial<br>value [7:0]:        | 00000000          | \$   |

|                           | SET/RESET<br>option:           | RESET             | •    | SET/RESET<br>option:           | RESET             | *         | SET/RESET<br>option:           | RESET             | *    |

|                           | Active level for<br>SET/RESET: | Low level         | *    | Active level for<br>SET/RESET: | Low level         | •         | Active level for<br>SET/RESET: | Low level         | *    |

|                           | Q output<br>polarity:          | Non-inverted (Q)  | *    | Q output<br>polarity:          | Non-inverted (Q)  | •         | Q output<br>polarity:          | Non-inverted (Q)  | *    |

Figure 13: Configuration for the SHR Block

Referring back to Figure 7 and the schematics in the GP file, this design uses multiple combination blocks for five control signals: *SW\_A\_Ctrl*, *SW\_B\_Ctrl*, *J\_CS*, *SHR\_ctl\_A*, and *SHR\_ctl\_B*

The first combination block (*SW\_A\_Ctrl*) consists of CNT6 and LUT21. Output is assigned to control SW\_A.

For Chip 1: CNT6 Counter data = 22.

For Chip 2: CNT6 Counter data = 38.

For Chip 3: CNT6 Counter data = 54.

For Chip 4: CNT6 Counter data = **70**.

|                         |                    |      |                    | 3         |       |       |        |

|-------------------------|--------------------|------|--------------------|-----------|-------|-------|--------|

| 12-bit CN               | T6/DLY6 (MF6)      |      |                    | 3-bit     | LUT21 | (MF7) |        |

| Multi-function<br>mode: | CNT/DLY            | •    | Multi-fur<br>mode: | nction    | LUT   |       |        |

| Mode:                   | Delay              | •    | IN3                | IN2       | IN1   | INO   | OUT    |

|                         |                    |      | 0                  | 0         | 0     | 0     | 0      |

| Counter data:           | 70                 | \$   | 0                  | 0         | 0     | 1     | 0      |

| counter data.           |                    | •    | 0                  | 0         | 1     | 0     | 0      |

| Delay time              | (Range: 1 - 4095)  |      | 0                  | 0         | 1     | 1     | 0      |

| (typical):              | N/D Form           | nula | 0                  | 1         | 0     | 0     | 0      |

| Edge mode               | Falling            | -    | 0                  | 1         | 0     | 1     | 0      |

| select:                 |                    | =    | 0                  | 1         | 1     | 0     | 1      |

| DLY IN init. value:     | Bypass the initial | •    | 0                  | 1         | 1     | 1     | 0      |

|                         |                    |      | 1                  | 0         | 0     | 0     | 0      |

| Output polarity:        | Non-inverted (OUT  | -    | 1                  | 0         | 0     | 1     | 0      |

|                         |                    |      | 1                  | 0         | 1     | 0     | 0      |

| Up signal SYNC:         | None               | Ŧ    | 1                  | 0         | 1     | 1     | 0      |

| Keep signal             |                    |      | 1                  | 1         | 0     | 0     | 0      |

| SYNC:                   | None               | ×    | 1                  | 1         | 0     | 1     | 0      |

| Mode signal<br>SYNC:    | Bypass             | -    | 1                  | 1         | 1     | 0     | 0      |

|                         |                    |      | 1                  | 1         | 1     | 1     | 0      |

| Cor                     | inections          |      | Standard           | l gates   |       | A     | l to 0 |

| Clock source:           | Ext. Clk. (From ma | -    | Define             | d by use  | r v   | A     | l to 1 |

| Clock divider:          | N/D                |      | Reg                | gular sha | pe    |       | nvert  |

| Clock frequency:        | N/D                |      |                    |           |       |       |        |

Figure 14: Configuration for the first Combination Block

The second combination block (SW\_B\_Ctrl) consists of CNT4 and LUT4. Output is assigned to control SW\_B. All macrocells are given the same configuration. For chip\_1~4: CNT4 Counter data = 22.

| Properties              |                          | ×    | Properties      | 5        |        |                              |        |  |

|-------------------------|--------------------------|------|-----------------|----------|--------|------------------------------|--------|--|

| 12-bit CN               | IT4/DLY4 (MF4)           |      |                 | 3-bit LU | T4/DFF | LATCH                        | 5      |  |

| Multi-function<br>mode: | CNT/DLY                  | •    | Туре:           |          | LUT    |                              |        |  |

| Mode:                   | Delay                    | -    | IN3             | IN2      | IN1    | INO                          | OUT    |  |

|                         |                          |      | 0               | 0        | 0      | 0                            | 0      |  |

| Counter data:           | 22                       | \$   | 0               | 0        | 0      | 1                            | 0      |  |

| oounter data.           | (Range: 1 - 4095)        | •    | 0               | 0        | 1      | 0                            | 0      |  |

| Delay time              |                          |      | 0               | 0        | 1      | 1                            | 0      |  |

| (typical):              | N/D For                  | mula | 0               | 1        | 0      | 0                            | 1      |  |

| Edge mode<br>select:    | Falling                  | -    | 0               | 1        | 0      | 1                            | 0      |  |

|                         |                          | =    | 0               | 1        | 1      | 0                            | 0      |  |

| DLY IN init. value:     | Bypass the initial       | •    | 0               | 1        | 1      | 1                            | 0      |  |

|                         |                          |      | 1               | 0        | 0      | 0                            | 0      |  |

| Output polarity:        | Inverted (nOUT)          | -    | 1               | 0        | 0      | 1                            | 0      |  |

|                         |                          |      | 1               | 0        | 1      | 0                            | 0      |  |

| Up signal SYNC:         | None                     | -    | 1               | 0        | 1      | 1                            | 0      |  |

| Keep signal             | Need                     |      | 1               | 1        | 0      | 0                            | 0      |  |

| SYNC:                   | None                     | _    | 1               | 1        | 0      | 1                            | 0      |  |

| Mode signal<br>SYNC:    | Bypass                   | -    | 1               | 1        | 1      | 0                            | 0      |  |

|                         | nections                 |      | 1               | 1        | 1      | 1                            | 0      |  |

| Cor                     | mecdons                  |      | Standard        | l gates  |        | A                            | l to 0 |  |

| Clock source:           | e: Ext. Clk. (From mar 🔻 |      | Defined by user |          |        | <ul> <li>All to 1</li> </ul> |        |  |

| Clock divider:          | N/D                      |      | Reg             |          | Invert |                              |        |  |

| Clock frequency:        | N/D                      |      |                 |          |        |                              |        |  |

Figure 15: Configuration for second Combination Block

The third combination block (J\_CS) consists of CNT3, CNT4, LUT1, and LUT17. Output is assigned to generate a variant CS signal forward to Pin10. All macrocells are given the same configuration. For chip\_ 1~4: CNT2 Counter data = 38.

| Properties              | 2                     | Properties | s        |         |       | (      |

|-------------------------|-----------------------|------------|----------|---------|-------|--------|

| 12-bit CN               | IT2/DLY2 (MF2)        |            | 3-bit LU | T7/DFF/ | LATCH | 9      |

| Multi-function<br>mode: | CNT/DLY -             | Туре:      |          | LUT     |       | Ŧ      |

| Mode:                   | Delay 👻               | IN3        | IN2      | IN1     | INO   | OUT    |

|                         |                       | 0          | 0        | 0       | 0     | 0      |

| Counter data:           | 38                    | 0          | 0        | 0       | 1     | 0      |

|                         | (Range: 1 - 4095)     | 0          | 0        | 1       | 0     | 0      |

| Delay time              | N/D Formula           | 0          | 0        | 1       | 1     | 0      |

| (typical):              | N/D Formula           | 0          | 1        | 0       | 0     | 1      |

| Edge mode<br>select:    | Falling 👻             | 0          | 1        | 0       | 1     | 0      |

|                         |                       | 0          | 1        | 1       | 0     | 0      |

| DLY IN init. value:     | Bypass the initial 🔻  | 0          | 1        | 1       | 1     | 1      |

|                         |                       | 1          | 0        | 0       | 0     | 0      |

| Output polarity:        | Non-inverted (OUT     | 1          | 0        | 0       | 1     | 0      |

|                         |                       | 1          | 0        | 1       | 0     | 0      |

| Up signal SYNC:         | None 👻                | 1          | 0        | 1       | 1     | 0      |

| Keep signal             | None 👻                | 1          | 1        | 0       | 0     | 0      |

| SYNC:                   | THORE                 | 1          | 1        | 0       | 1     | 0      |

| Mode signal<br>SYNC:    | Bypass 💌              | 1          | 1        | 1       | 0     | 0      |

| Cor                     | nections              | 1          | 1        | 1       | 1     | 0      |

| CO                      | meetions              | Standard   | gates    |         | Δ     | l to 0 |

| Clock source:           | Ext. Clk. (From mar 🔻 | Define     | d by use | r •     |       | l to 1 |

| Clock divider:          | N/D                   |            | ular sha |         |       | nvert  |

|                         |                       |            |          | 5 EX    |       | ivert  |

| Clock frequency:        | N/D                   |            |          |         |       |        |

4. The fourth and fifth combination blocks (*SHR\_ctl\_A* and *SHR\_ctl\_B*) are used to arrange the data transfer sequences. For chip\_1~4: CNT5 and CNT8 Counter data = **14**.

|                           | _ctl_A                               | ×    | Properties              | R_ctl_B                              |

|---------------------------|--------------------------------------|------|-------------------------|--------------------------------------|

| 12-bit CN                 | IT8/DLY8 (MF8)                       |      | 12-bit CN               | IT5/DLY5 (MF5)                       |

| Multi-function<br>mode:   | CNT/DLY                              | -    | Multi-function<br>mode: | CNT/DLY                              |

| Mode:                     | One shot                             | -    | Mode:                   | One shot                             |

| Counter data:             | 14                                   | \$   | Counter data:           | 14                                   |

| Pulse width<br>(typical): | (Range: 1 - 4095)<br>N/D <u>Form</u> | nula | Pulse width (typical):  | (Range: 1 - 4095)<br>N/D <u>Form</u> |

| Edge mode<br>select:      | Falling                              | •    | Edge mode<br>select:    | Falling                              |

| DLY IN init. value:       | Bypass the initial                   | •    | DLY IN init. value:     | Bypass the initial                   |

| Output polarity:          | Non-inverted (OUT                    | •    | Output polarity:        | Non-inverted (OUT                    |

| Up signal SYNC:           | None                                 | -    | Up signal SYNC:         | None                                 |

| Keep signal<br>SYNC:      | None                                 | -    | Keep signal<br>SYNC:    | None                                 |

| Mode signal<br>SYNC:      | Bypass                               | -    | Mode signal<br>SYNC:    | Bypass                               |

| Cor                       | nnections                            |      | Cor                     | nnections                            |

| Clock source:             | Ext. Clk. (From mar                  | -    | Clock source:           | Ext. Clk. (From ma                   |

| Clock divider:            | N/D                                  |      | Clock divider:          | N/D                                  |

| Clock frequency:          | <u>N/D</u>                           |      | Clock frequency:        | <u>N/D</u>                           |

Figure 17: Configuration for the fourth and fifth Combination Blocks

As shown in Figure 6, the MISO bus of Chip 4 transmits data forward to the MCU. In Figure 18 it is shown that SHR\_reset is used to blank the CMD transfer in SW\_A of Chip 4.

#### Figure 18: CMD Blank Block

For inspecting the sequence of data transfer in Daisy Chain SPI, we assign the FSM1 macrocell to store a specific counter data. The design and configuration is shown in Figure 19.

| 8,601 (h21, h99)               | For Chip 2:                    | Counter                      | data = 16,331 (h3F, hCB)             |

|--------------------------------|--------------------------------|------------------------------|--------------------------------------|

| 9,173 (h23, hD5)               | For Chip 4:                    | Counter                      | data = 12,291 (h30, h03)             |

|                                | Properties<br>16-bit CNT12/    | DLY12/FSM1 (MF1              | I2) *                                |

| CNT12/DLY12/     FSM1     POR1 | K/8<br>Multi-function<br>mode: | CNT/DLY                      | •                                    |

|                                | Mode:                          | Delay                        | •                                    |

|                                | Counter data:                  | 9173                         | 6                                    |

|                                | Delay time<br>(typical):       |                              | rmul                                 |

|                                | Edge mode<br>select:           | Rising                       | •                                    |

|                                | DLY IN init. value:            | Initial O                    | •                                    |

|                                | Output polarity:               | Non-inverted (OU             | r. •                                 |

|                                | Up signal SYNC:                | Bypass                       | •                                    |

|                                | SYNC:                          | Bypass                       | *                                    |

|                                | • FSM1 POR1                    | 9,173 (h23, hD5) For Chip 4: | 9,173 (h23, hD5) For Chip 4: Counter |

Figure 19: Configuration for Specific Data Inspection

SYNC:

Set to date

The prototypical Daisy chain SPI is eventually completed. Next, we add the ADC block for multiple AFE applications. As shown in Figure 20, we create four AFE channels associated with the ADC block. Three external AFE channels are assigned to Pin 7, Pin 8, and Pin 9, respectively. The PGA macrocell is configured in single-ended mode for the AFE channels. Additionally, the internal AFE channel is used to monitor the temperature sensor.

Figure 20: Three External AFE Channels associated with ADC

Figure 21 shows the configuration for the reference design. The ADC macrocell is configured with 14-bit resolution and channel sampling period of 400  $\mu$ s. ADC data is configured in Buffer Mode to transfer data to the Buffer macrocells, and the Buffer data can be read via SPI protocol directly.

| Properties                  |                                 | ×     | Properties                  |                   | ×   | Properties                     |                    | ×   | Properties                                   |                | ×      |

|-----------------------------|---------------------------------|-------|-----------------------------|-------------------|-----|--------------------------------|--------------------|-----|----------------------------------------------|----------------|--------|

|                             | PGA                             |       |                             | PGA               |     |                                | PGA                |     |                                              | ADC            | -      |

| Out+ to PIN 13<br>(GPI09)   | Disable                         | •     | Out+ to PIN 13<br>(GPI09)   | Disable           | •   | Out+ to PIN 13<br>(GPIO9)      | Disable            | •   | Clock selection:                             | OSC1           | -      |

| Out- to PIN 14<br>(GPI010)  | Disable                         | •     | Out- to PIN 14<br>(GPIO10)  | Disable           | •   | Out- to PIN 14<br>(GPIO10)     | Disable            | •   | Vref selection:                              | 1.62V internal | Vref 👻 |

| PGA/ADC manual mode enable: | Disable                         | •     | PGA/ADC manual mode enable: | Disable           | *   | PGA/ADC manual<br>mode enable: | Disable            | •   | AVDD divider:                                | (1/8)AVDD      |        |

| Manual channel selection:   | Channel 0                       | •     | Manual channel selection:   | Channel 0         | •   | Manual channel<br>selection:   | Channel 0          | •   | Resolution:                                  | 14-bit         | -      |

| с                           | hannels                         |       | C                           | hannels           |     | C                              | hannels            |     | Sample per                                   | 1              |        |

| 0 1 2                       | 3                               |       | 0 1 2                       | 3                 |     | 0 1 2                          | 3                  |     | channel:<br>Channel 0 system<br>calibration: | Disable        | *      |

| Input mode:                 | Single ended input              | -     | Input mode:                 | Single ended inpu | t • | Input mode:                    | Single ended input | n • | Channel 2 system<br>calibration:             | Disable        | -      |

| Mode:                       | (6) Buffer                      | •     | Mode:                       | (6) Buffer        | •   | Mode:                          | (6) Buffer         | *   | Clock divider:                               | /4 divider     | -      |

| Gain:                       | 1x                              | +     | Gain:                       | 1x                | Ψ.  | Gain:                          | 1x                 | *   | Sampling rate                                |                |        |

| IN+ source:                 | PIN 7 (GPIO3)                   | *     | IN+ source:                 | PIN 8 (GPIO4)     | •   | IN+ source:                    | PIN 9 (GPI05)      | •   | (single channel):<br>Delay between           | 125.000 ksps   | Formul |

| IN- source:                 | AGND                            | *     | IN- source:                 | AGND              | *   | IN- source:                    | AGND               |     | channels:                                    | 500            | \$     |

| Properties                  | ASNO                            | ×     |                             |                   |     |                                |                    |     | Delay between<br>channels                    | 1              | *      |

|                             | T0/DLY0 (MF0)                   |       |                             |                   |     |                                |                    |     | predivider:                                  |                |        |

|                             | 10/0210 (MPO)                   |       |                             |                   |     |                                |                    |     | Delay:                                       | 100 us         |        |

| Multi-function<br>mode:     | CNT/DLY                         | •     |                             |                   |     |                                |                    |     | Data aligment:                               | MSB            | -      |

| Mode:                       | Delay                           | •     |                             |                   |     |                                |                    | -   |                                              |                |        |

|                             |                                 |       | Properties                  |                   | ×   | Properties                     | D. Mark            | ×   | Properties                                   |                | ×      |

| Counter data:               | 3                               | \$    | Da                          | ta Buffer0        |     | Dat                            | a Buffer1          |     | Data                                         | Buffer2        |        |

| Delay time                  | (Range: 1 - 4095)<br>32 ms Form | de la | Mode:                       | Storage           | •   | Mode:                          | Storage            | •   | Mode:                                        | Storage        | -      |

| (typical):<br>Edge mode     | Contraction of the second       | 5     | Length:                     | 1 word            | *   | Length:                        | 1 word             | •   | Length:                                      | 1 word         | •      |

| select:                     | Rising                          | 31    | Initial data:               | 0000h             | *   | Initial data:                  | 0000h              | •   | Initial data:                                | 0000h          | •      |

| DLY IN init. value:         | Bypass the initial              |       | Input source:               | ADC               | •   | Input source:                  | ADC                | •   | Input source:                                | ADC            | *      |

| Output polarity:            | Non-inverted (OUT               | •     | Load source:                | ADC ready 0       | •   | Load source:                   | ADC ready 1        | •   | Load source:                                 | ADC ready 2    | -      |

| Up signal SYNC:             | None                            |       | Load en sync:               | ADC clk           | •   | Load en sync:                  | ADC clk            | •   | Load en sync:                                | ADC clk        | •      |

| Keep signal                 | None                            |       | OUT source:                 | Data              | *   | OUT source:                    | Data               | •   | OUT source:                                  | Data           | •      |

| SYNC:<br>Mode signal        |                                 |       | Buffer ready:               | 1                 | •   | Buffer ready:                  | 1                  | •   | Buffer ready:                                | 1              | •      |

| SYNC:                       | Bypass                          |       | (march 1)                   |                   |     |                                |                    |     |                                              |                |        |

Figure 21: Configuration of Multiple AFE Channel Block

### 4. Simulation Results

The simulation of Chip 2 is shown in Figure 22.

The CS signal transmitted by the MCU can be reshaped to trigger the inherited SPI to prepare Chip 2 data.

CMD is received and forwarded to MISO.

The SHR block works to propagate the Chip data in turn.

The MISO signal from Chip 2 outputs CMD and the Data of Chip 1 and the Data of Chip 2.

This single chip simulation also applies to the behavior of the other Chips as well.

| 42.8 ms                              | +0.2 ms | +0.4 ms | +0.6 ms           | +0.8 ms  | +1ms            | +1.2 ms            |

|--------------------------------------|---------|---------|-------------------|----------|-----------------|--------------------|

| GreenPAK -> PIN 14 -> OUT            |         |         |                   |          |                 | 0. 40. 40. 40.<br> |

| MCU: CS                              |         |         |                   |          |                 |                    |

| GreenPAK → 3-L2 → OUT                |         |         |                   |          |                 |                    |

| Variant CS to Pi                     | n3      |         |                   |          |                 |                    |

| GreenPAK → PIN 5 → OUT [CLK]         |         |         |                   |          |                 |                    |

| SCLK (Pin 5)                         |         |         |                   |          |                 |                    |

| GreenPAK -> PIN 16 -> OUT            | Comman  | d Dummy |                   |          |                 |                    |

| High<br>MOSI (Pin 12)                |         | yv/ E   | Data #1           |          |                 |                    |

| GreenPAK → PIN 10 → OUT              |         | / CI    | hip #2 outputs Da | ata_#2   |                 |                    |

| Inherited SPI_M<br>(Pin 6_of Chip #: |         |         |                   |          |                 |                    |

| GreenPAX → SHR 5 → Q                 |         | X       | $\mathbf{h}$      | 1994     |                 |                    |

| High<br>SHR output forv<br>to Pin11  | vard    |         |                   |          |                 |                    |

| GreenPAK → 3-bit LUT0 → OUT          |         |         | Data #2           |          |                 |                    |

| MISO (Pin 11)                        |         | w/ D    | Data #1           | Transfer | to next chip MC | SI                 |

Figure 22: Simulation Results

### 5. Design Verification Using Hardware Prototype

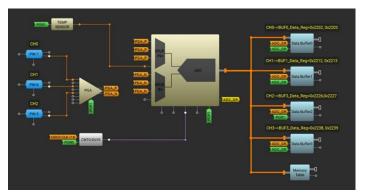

After programming the NVM on each chip, we can prepare four SLG47011V daughterboards and carry out the wire connection, as shown in Figure 23. A Digilent <sup>®</sup> ADP3450 Portable oscilloscope is set up to provide the required SPI send/receive test-pattern and protocol analyzer.

Figure 23: Hardware Prototype and Bench

Basic Testing conditions:  $V_{DD}$  = 3.3 V to the four chips; SPI SCLK frequency = 3.4 MHz (provided by the ADP3450)

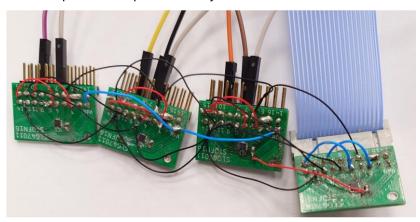

### 5.1 Inspection: Reading Data from DLY/CNT, [h0139, h013A]

To inspect the SPI communication and data sequence, the quad SLG47011V prototype is equipped with specific data, independently. The specific data are regarded as check-code allocated to each individual chip's **FSM1** macrocell. From the validation results, the SPI MISO data sequence indicates the data permutations in arrangement. The protocol **analyzer** collects all specific data by sending an SPI command [hA2, h26]. Every chip reflects its individual data including **[h01, h39]** (FSM1\_Data\_MSB) and **[h01, h3A]** (FSM1\_Data\_LSB).

Chip 1: specific counter data in FSM1 macrocell is given h2199.

Chip 2: specific counter data in FSM1 macrocell is given h3FCB.

Chip 3: specific counter data in FSM1 macrocell is given h23D5.

Chip 4: specific counter data in FSM1 macrocell is given h3003.

Figure 24: Sequence Inspection for Daisy Chain SPI

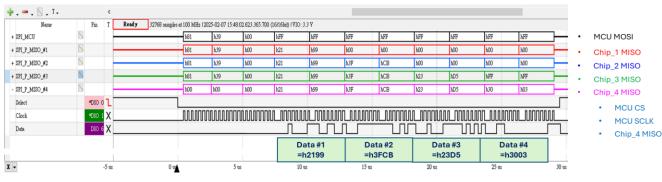

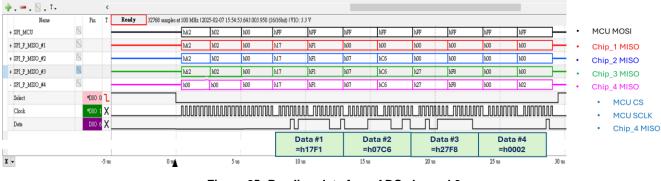

### 5.2 Capturing ADC Data: Reading Channel\_0 from Buffer0, [h2202, h2203]

This validation shows that the **protocol analyzer** collects every chip's channel\_0 data by sending an SPI command **[h22, h02]**. Every chip reflects its individual data including **[h22, h02]** (BUFFER0\_Data\_MSB) and **[h22, h03]** (BUFFER0\_Data\_LSB). BUFFER0\_Data collects the data from ADC channel\_0.

- Chip 1: Channel 0 is given 0.6 V, Buffer0 return ADC data= h17F1 for 0.6061 V

- Chip 2: Channel 0 is given 0.2 V, Buffer0 return ADC data= h07C6 for 0.1968 V

- Chip 3: Channel 0 is given 1.0 V, Buffer0 return ADC data= h27F8 for 1.0118 V

Chip 4: Channel 0 is given 0.0 V, Buffer0 return ADC data= h0002 for 0.0002 V

Figure 25: Reading data from ADC channel 0

# 6. Conclusion

Quad SLG47011V chips with Daisy chain SPI can be utilized to simplify the PCB layout and/or reduce the number of required subnodes. A maximum baud rate frequency of 3.4 MHz for the SCLK is supported. Every SPI command can force all SLG47011V chips to transfer individual ADC data synchronously. The validation result shows the Daisy Chain SPI functionality collects the ADC data corresponding to each individual ADC channel. To ensure ADC accuracy and reduce noise coupling, we recommended that fully PCB layout is necessary.

# 7. Revision History

| Revision | Date           | Description     |

|----------|----------------|-----------------|

| 1.00     | April 30, 2025 | Initial release |