# Application Note DA9080 PCB Layout Recommendations

**AN-PM-179**

# **Abstract**

This application note provides recommendations on how to place and route DA9080 device. It also gives guidance on the passive components needed for proper functioning of the system. This document is a guideline only; target applications may have different requirements.

# **Contents**

| Αb  | strac   | t      |                                                          | <i>'</i> |

|-----|---------|--------|----------------------------------------------------------|----------|

| Сс  | ntent   | s      |                                                          |          |

| Fiç | gures.  |        |                                                          |          |

| Ta  | bles    |        |                                                          |          |

| 1   |         |        | Definitions                                              |          |

| 2   |         |        |                                                          |          |

| 3   |         |        |                                                          |          |

|     |         |        |                                                          |          |

| 4   | •       |        | ommendations                                             |          |

|     | 4.1     |        | 0 Package Information                                    |          |

|     |         | 4.1.1  | Pinout                                                   |          |

|     | 4.0     | 4.1.2  | Package Information                                      |          |

|     | 4.2     |        | Converter and LDO                                        |          |

|     |         | 4.2.1  | Input Decoupling                                         |          |

|     |         | 4.2.2  | Ground Connections                                       |          |

|     |         | 4.2.3  | LX Routing                                               |          |

|     |         | 4.2.4  | Buck and LDO                                             |          |

|     | 4.3     | 4.2.5  | Feedback Linesunication Interface (I <sup>2</sup> C)     |          |

| _   |         |        | y                                                        |          |

| Fi  | gure    | es     |                                                          |          |

| Fic | ure 1:  | DA9080 | O Recommended Components and Connections                 |          |

| Fiç | jure 2: | DA9080 | FCQFN Pinout Diagram (Top View)                          | 6        |

|     |         |        | I5x5 Package Outline Diagrammsms                         |          |

|     |         |        | erminals Connection                                      |          |

|     |         |        | ut on Layer 2                                            |          |

|     |         |        | e Pattern on DA9080 Evaluation Board                     |          |

| Fiç | gure 8: | Output | Voltage Feedback Line Routing on DA9080 Evaluation Board | 12       |

|     |         |        |                                                          |          |

| Ta  | able    | S      |                                                          |          |

| та  | hla 1·  | DVOUSU | Pacammanded Components                                   | ı        |

# 1 Terms and Definitions

IC Channel

FCQFN Flip chip quad flat-pack no-lead (package)

GND Ground

IC Integrated circuit LDO Low drop out

PCB Printed circuit board

# 2 References

[1] DA9080\_Datasheet, Renesas Electronics.

Note 1 References are for the latest published version, unless otherwise indicated.

# 3 Introduction

DA9080 is a five-channel advanced, configurable, system power management IC (PMIC) with four buck regulators and one LDO. Along with several other features, the DA9080 offers dynamic voltage control (DVC), robust protection features, and a dedicated I2C interface. These features coupled with the high-efficiency, fast transient response, and small footprint of the DA9080 lends itself to become the preferred power solution for a host of complex, high-performance applications. The DA9080 is offered in a FCQFN package. For more information, please see the DA9080 Datasheet [1].

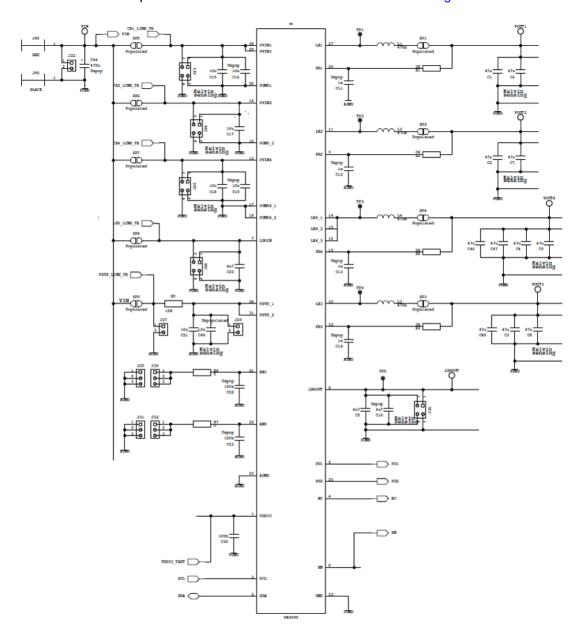

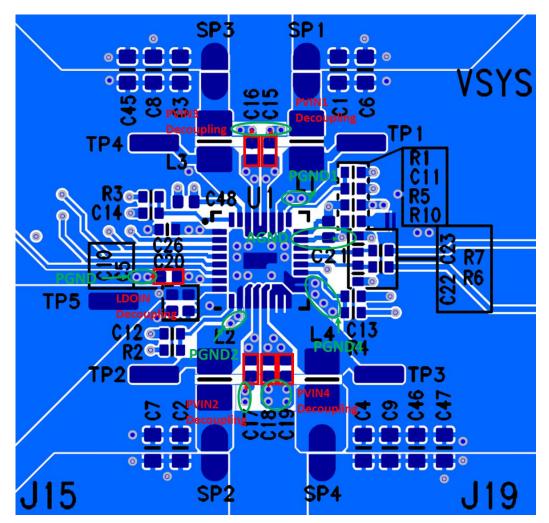

The recommended components and connections for DA9080 is shown in Figure 1.

Figure 1: DA9080 Recommended Components and Connections

**Table 1: DA9080 Recommended Components**

| Application                             | Part<br>Reference               | Value  | Temp.<br>Char.   | Voltage Rating | ISAT and ITEMP              |

|-----------------------------------------|---------------------------------|--------|------------------|----------------|-----------------------------|

| CVSYS                                   | C21                             | 10 μF  | X5R or<br>better | 10 V or above  | N/A                         |

| CPVIN1,<br>CPVIN2,<br>CPVIN3,<br>CPVIN4 | C15,<br>C16(UNPOP),<br>C17, C18 | 10 μF  | X5R or better    | 10 V or above  | N/A                         |

| CVOUT1,<br>CVOUT2,<br>CVOUT3,<br>CVOUT4 | C1~4, C6~9,<br>C45~47           | 47 μF  | X5R or better    | 6.3 V or above | N/A                         |

| CLDOIN                                  | C20                             | 4.7 µF | X5R or<br>better | 10 V or above  | N/A                         |

| CLDOOUT                                 | C5                              | 4.7 µF | X5R or<br>better | 10 V or above  | N/A                         |

| CVDDIO                                  | C26                             | 0.1 μF | X5R or<br>better | 10 V or above  | N/A                         |

| LOUT1,<br>LOUT2,<br>LOUT3, LOUT4        | L1~4                            | 470 nH | N/A              | N/A            | 5.6 A ISAT typical or above |

# 4 Layout Recommendations

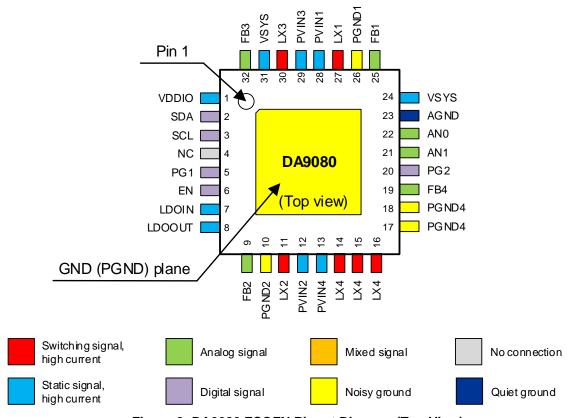

DA9080 comes in a 5.0 x 5.0 mm 32-pin FCQFN package with a 0.5 mm pitch.

Although the PCB layout recommendations described in this application note is with reference to the Renesas Electronics' DA9080 Evaluation Board, a six-layer PCB, the required number of routing layers and other PCB parameters are also determined by the other devices in the system.

# 4.1 DA9080 Package Information

#### **4.1.1 Pinout**

Figure 2: DA9080 FCQFN Pinout Diagram (Top View)

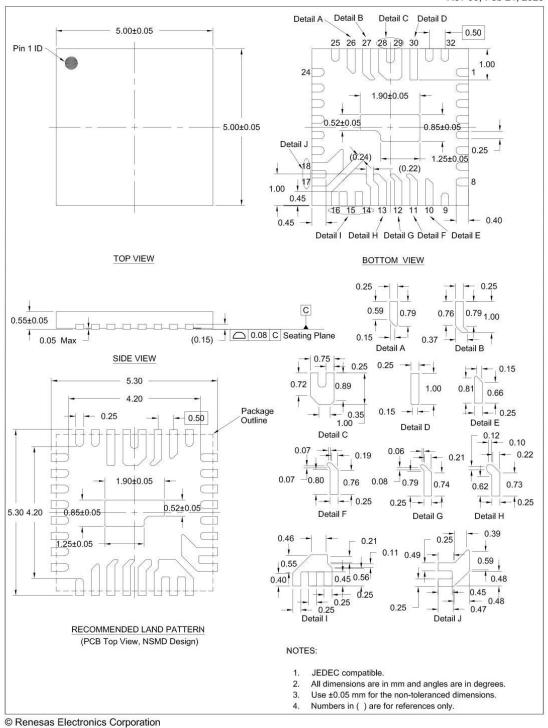

## 4.1.2 Package Information

# RENESAS

## **Package Outline Drawing**

PSC-5139-01 FQ0032AA 32-FCQFN 5.0 x 5.0 x 0.55 mm Body, 0.5 mm Pitch Rev 00, Feb 21, 2025

Figure 3: FCQFN5x5 Package Outline Diagram

## 4.2 Buck Converter and LDO

## 4.2.1 Input Decoupling

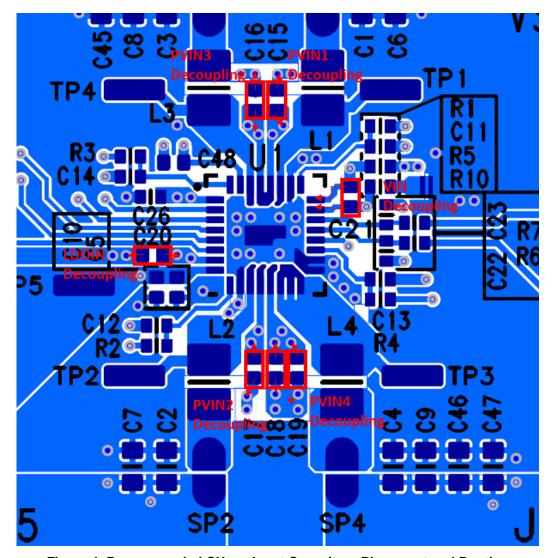

In a buck converter layout, the input capacitor location is critical. Locate the input capacitor as close as possible to the device's input and power GND pins to minimize the parasitic inductance.

In the DA9080 layout design, the input capacitor for each CH<x> should be placed as close as possible to the PVIN<x> and PGND<x> pins, and on the same layer as the DA9080 device.

If multiple layers are used, it is recommended to use as many as possible microvias (or through-hole vias) to minimize line resistance.

Figure 4 shows the input capacitor placement and routing recommendation.

Figure 4: Recommended CH<x> Input Capacitors Placement and Routing

The LDO input capacitor should be placed as close as possible to the LDOIN and PGND pins.

Trace impedances to the LDO input connection should be minimized to reduce drop-out and effects on load regulation.

## 4.2.2 Ground Connections

Special care should be taken with ground connections because of the high current capability of DA9080 and because of the device's high-performance requirements.

The power PGND terminals (PGND<x>) of the DA9080 are placed conveniently to allow the placement of the PVIN decoupling capacitors as close as possible to the device.

It is best practice to isolate quiet analog GND (AGND) from noisy power GND terminals (PGND<x>).

On the Renesas Electronics' DA9080 Evaluation Board, AGND is isolated from the power GND terminals (PGND<x>) at the top layer (component layer) and connected at a single point (C21). AGND and power GND (PGND<x>) are connected together with R10 (0R), which is located in a quiet area of the PCB.

Layer 2 can be used as a return power GND plane, where the device's power GND pins (for CH<x>) and output capacitor GND can be connected. It is recommended to minimize the line impedance of the power GND pins and output capacitor GND connections by using as many vias as possible. This will also improve the heat dissipation.

#### **NOTE**

It is always recommended to use copper plugged vias to achieve the minimum parasitic via impedance and best thermal performance.

Example of GND terminals connection is illustrated in Figure 5.

Figure 5: GND Terminals Connection

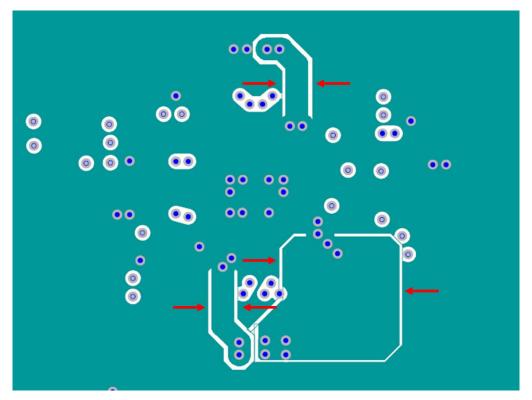

To minimize ground-bounce effects from the bucks affecting the LDO or between bucks, it is recommended that GND 'cuts' are applied between each buck. Figure 6 illustrates the power ground with cuts (highlighted by red arrows) implemented on the Renesas Electronics' DA9080 Evaluation Board.?

Figure 6: GND Cut on Layer 2

## 4.2.3 LX Routing

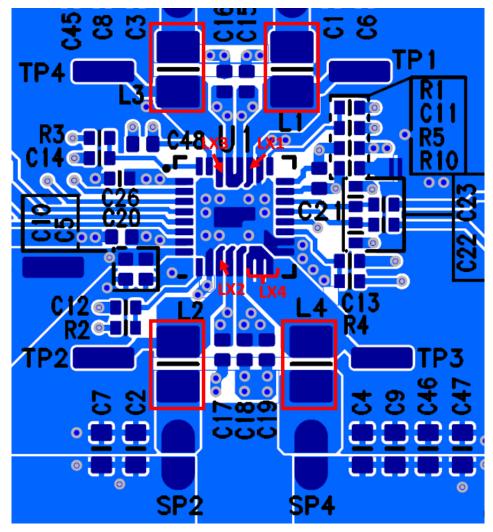

Switch node/LX node traces (traces between LX pins and output inductors) need to be kept as short as possible since this node generates switching noise, which can interfere with buck converters stability. Very high current will flow through these traces and so the minimum width of trace used for this LX node must be considered. Also, if used, ensure that there are enough vias to deliver the current.

The LX node patterns on the Renesas Electronics' DA9080 Evaluation Board are shown in Figure 7. The LX nodes are routed out on layer 1.

## Layer 1:

Figure 7: LX Node Pattern on DA9080 Evaluation Board

## 4.2.4 Buck and LDO

Output capacitors should be placed locally close to the output inductors to avoid any effects to the stability of the buck converters.

Minimizing the distance (which minimizes the line impedance) from the output inductors to the output capacitors is very important since it directly affects the efficiency and load transient response performance of the buck converter. Care must be taken with the size of the output traces to accommodate the high output current that DA9080 needs to support.

It is best practice to transfer the output current at the top layer directly without using any vias. This will give the best performance in terms of efficiency and load transient response performance.

The output capacitors for the LDO should be placed near the device. Trace impedances to the LDO output connection should be minimized to reduce drop-out and effects on load regulation.

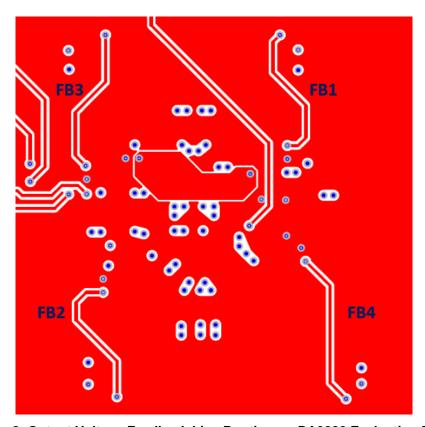

#### 4.2.5 Feedback Lines

Feedback lines must be routed far from any noise source (for example, output inductors, LX node, and so on). It is strongly recommended to place an UNPOP bypass capacitor (typically 1 nF) on the feedback. The bypass capacitor should be placed as close as possible to the IC. It is useful for filtering noise which may be injected to the feedback lines due to a layout limitation (for example, a long feedback pattern or noise from other devices in the system).

Also, ensure that the feedback lines are not overlapping any noisy node traces (for example, the LX node trace) without an insulation plane in between.

#### **NOTE**

The feedback lines must be routed directly from the load point in order to achieve the best voltage accuracy and stability.

Examples of output-voltage feedback-line routing, on the Renesas Electronics' DA9080 Evaluation Board, is shown in Figure 8.

## Layer 6:

Figure 8: Output Voltage Feedback Line Routing on DA9080 Evaluation Board

## 4.3 Communication Interface (I<sup>2</sup>C)

It is recommended to route the communication interface far from any noise source.

Care must also be taken regarding the noise produced by the interface signal in order to avoid coupling to the sensitive analog references and feedbacks. The routing layer is not critical, but it is recommended to use the bottom or top layer.

# **Revision History**

| Revision | Date        | Description                             |

|----------|-------------|-----------------------------------------|

| 1        | 22-Nov-2023 | Initial version.                        |

| 2        | 04-Apr-2025 | Watermark removed and Figure 3 updated. |

## **Status Definitions**

| Status               | Definition                                                                                                                   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED or unmarked | The content of this document has been approved for publication.                                                              |

# **RoHS Compliance**

Renesas Electronics' suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

#### **Important Notice and Disclaimer**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

© 2025 Renesas Electronics Corporation. All rights reserved.

(Rev.1.0 Mar 2020)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu

Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

https://www.renesas.com/contact/

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

Application Note Revision 2 04-Apr-2025