# DA9168BC APPLICATION NOTE

FEB 2022 RENESAS ELECTRONICS CORPORATION

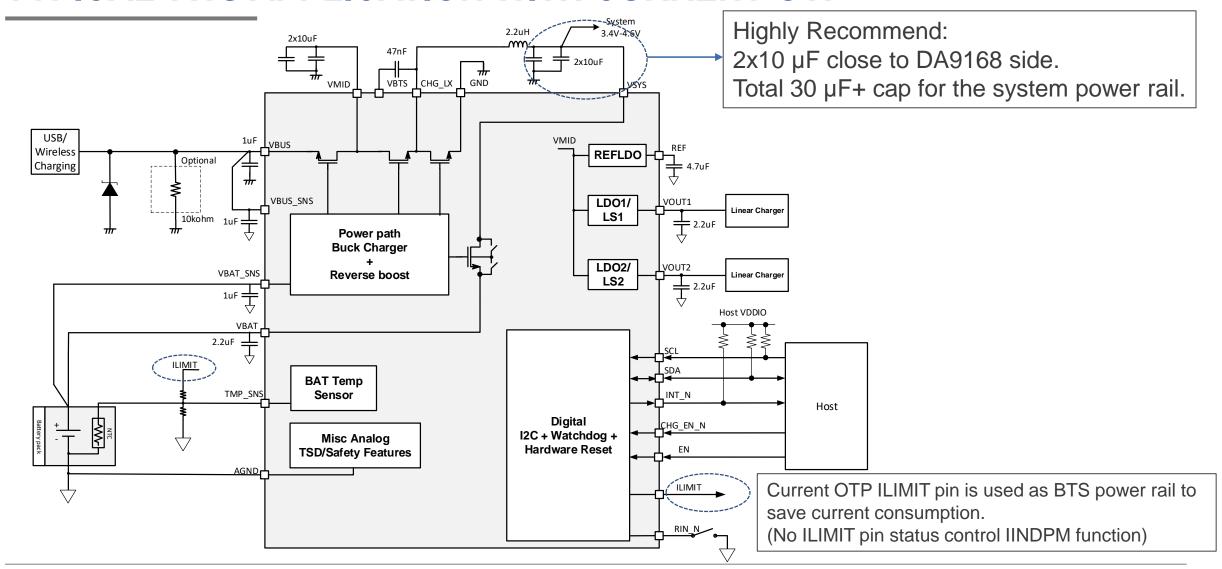

# TYPICAL TWS APPLICATION WITH CURRENT OTP

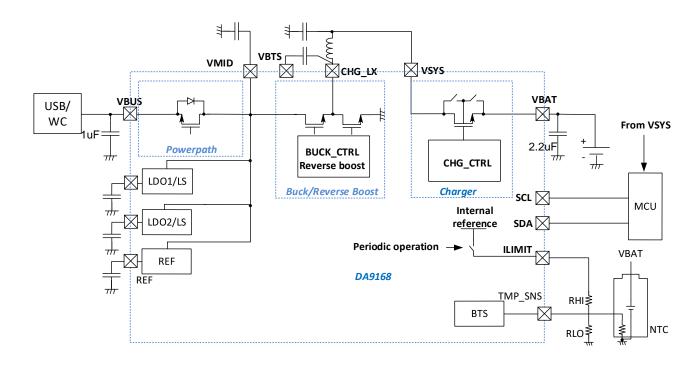

# DA9168 BTS WITH ILIMT PIN

# BTS WITH ILIMIT - VBUS IQ

Using ILIMIT pin (instead of REF) for BTS has large  $I_Q$  savings

| BTS Reference | втѕ      | Condition                               | I <sub>Q</sub> from VBAT (μA) | Savings (µA) |

|---------------|----------|-----------------------------------------|-------------------------------|--------------|

| REF           | Disabled | Reverse boost + REFLDO                  | 377                           | -            |

| REF           | Enabled  | Reverse boost + REFLDO + BTS (50msec)   | 380                           | -            |

| REF           | Enabled  | Reverse boost + REFLDO + BTS (2 sec)    | 377                           | -            |

| ILIMIT        | Disabled | Standby (boost disable)                 | 10 I <sub>Q</sub> increase    | 367          |

| ILIMIT        | Enabled  | Standby (boost disable) + BTS (50 msec) | 41 from BTS                   | 339          |

| ILIMIT        | Enabled  | Standby (boost disable) + BTS (2 sec)   | 11 just ~1 μA                 | 366          |

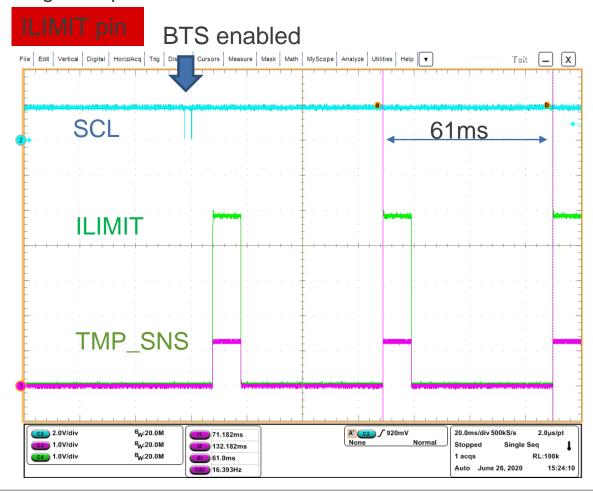

# **BTS WITH ILIMIT - PERIODIC OPERATION**

✓ BTS periodic operation working as expected.

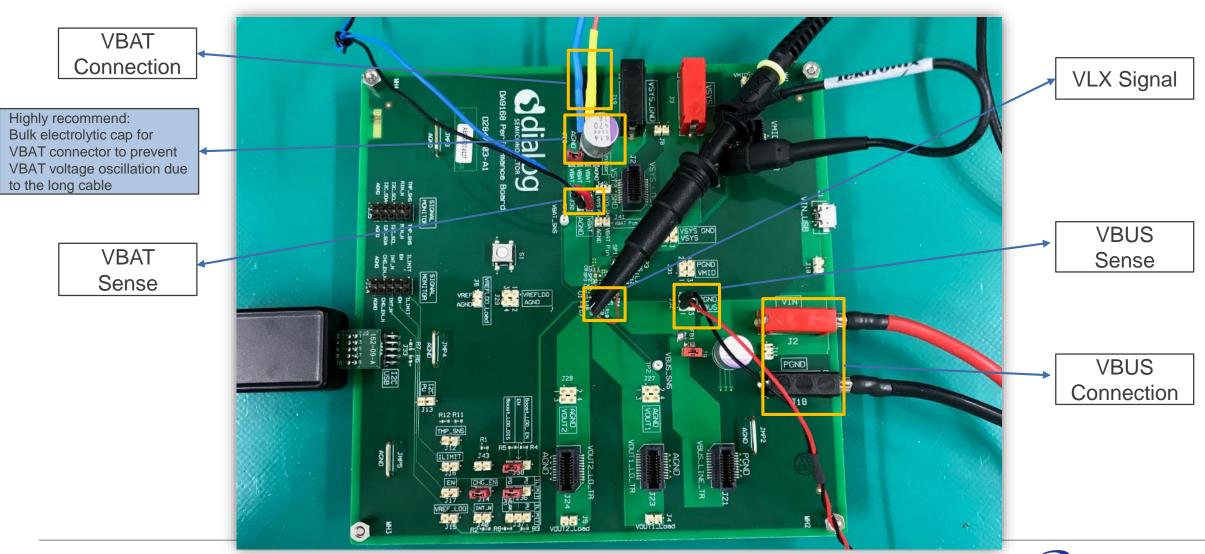

# DA9168 PERFORMANCE BOARD

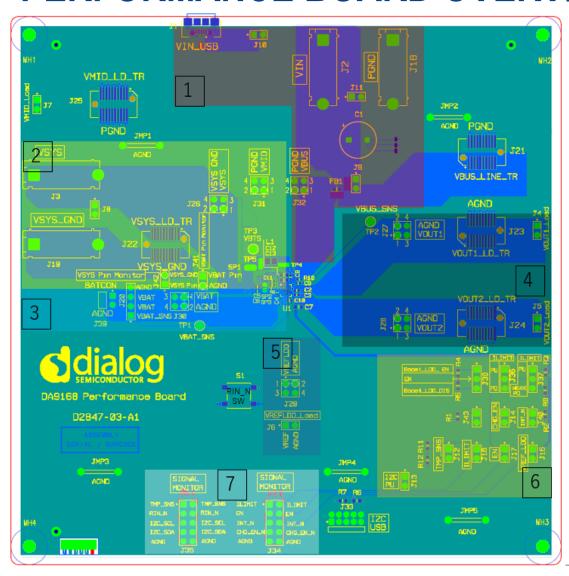

# PERFORMANCE BOARD OVERVIEW

#### **CAUTION**

Apply high current to J26, J27, J28, J29, J30, J31, J32, J41 and J42 headers pin 1 and 2 may causes the voltage sensing traces burn out.

- 1. VBUS input section: Power supply and USB power supply connectors.

- 2. VSYS output section.

- 3. VBAT input/output section.

- 4. VOUT1 and VOUT2 outputs section.

- 5. REFLDO output section.

- 6. GPIOs network section.

- 7. GPIOs signal monitors section.

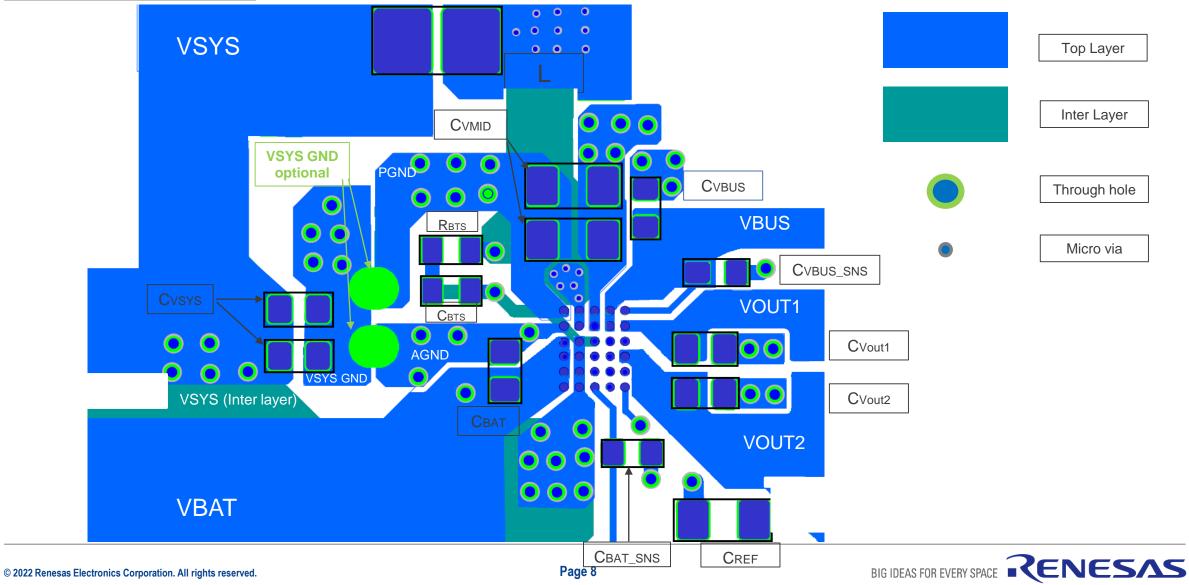

# DA9168 PERFORMANCE BOARD LAYOUT CONCEPT

# LAYOUT GUIDELINES

- Minimize high frequency current path loop (VMID CHG\_LX VSYS GND and CHG\_LX VSYS GND) to reduce EMI.

- 2. The two VMID capacitors (2x10 μF) need to be placed as close as possible to the device DA9168.

- 3. The inductor input pin connected to GHG\_LX pin should be as short as possible to reduce switching noise.

- 4. Make sure decoupling capacitors trace to the device pins as short as possible.

- 5. Split AGND (analog ground) and GND (power ground), and tie the analog ground and power ground with single ground connection.

- 6. For high current paths, ensure that the vias number and copper area is enough to support the operation current.

#### Note:

- 1. Currently, there are two options for VSYS GND connection. Based on device evaluation results, recommend VSYS GND connect to AGND.

- 2. VBAT\_SNS Capacitor can be removed if the battery connection is short enough.

# PERFORMANCE BOARD EXTERNAL COMPONENTS LIST

#### Inductors

| Manufacturers | Part #            | Size<br>(mm)                      | Inductance<br>(μΗ) | Rdc<br>(mΩ) |     | Heat Rating<br>Current (A) |     | Saturation<br>Current (A) |     |

|---------------|-------------------|-----------------------------------|--------------------|-------------|-----|----------------------------|-----|---------------------------|-----|

|               |                   |                                   |                    | Тур         | Max | Тур                        | Max | Тур                       | Max |

| Cyntec        | HTEH20160H-1R0MSR | L = 2.0; $W = 1.6T = 0.8  (max)$  | 1.0                | 29          | 35  | 4.4                        | 4.0 | 4.0                       | 3.6 |

| Cyntec        | HTEH20160H-2R2MSR | L = 2.0; W = 1.6<br>T = 0.8 (max) | 2.2                | 75          | 90  | 2.6                        | 2.3 | 2.9                       | 2.7 |

# PERFORMANCE BOARD EXTERNAL COMPONENTS LIST

#### MLCC

| Manufacturers | Part #             | Size<br>(mm) | Height<br>(mm) | Capacitance<br>(µF) | Rated<br>voltage | Temp<br>characteristics | ESR<br>@1 MHz<br>(Ω) | Position                        |

|---------------|--------------------|--------------|----------------|---------------------|------------------|-------------------------|----------------------|---------------------------------|

| Murata        | GRM155R6YA105KE11  | 1005         | 0.5 ±0.1       | 1.0 ±10%            | 35 V             | X5R                     | 0.01                 | VBUS<br>VBUS_SNS<br>(*VBAT_SNS) |

| Murata        | GRM155R61A106ME11  | 1005         | $0.5 \pm 0.2$  | 10.0 ±20%           | 10 V             | X5R                     | -                    | VSYS(2x)                        |

| Murata        | GRM188R61E106MA73D | 1608         | $0.8 \pm 0.2$  | 10.0 ±20%           | 25 V             | X5R                     | -                    | VMID (2x)                       |

| Taiyo Yuden   | TMK105BJ473KV-F    | 1005         | 0.55<br>(Max)  | 0.047±10%           | 25 V             | X5R                     | 0.1                  | VBTS                            |

| Murata        | GRM155R61C225KE11  | 1005         | 0.5 ±0.2       | 2.2 ±10%            | 16 V             | X5R                     | 0.008                | VBAT<br>VOUT1<br>VOUT2          |

| Murata        | GRM155R61C105KA12  | 1005         | $0.5 \pm 0.05$ | 1.0 ±10%            | 16 V             | X5R                     | 0.02                 | VBAT_SNS                        |

| Murata        | GRM185R61C475KE11  | 1608         | $0.5 \pm 0.05$ | 4.7 ±10%            | 16 V             | X5R                     | 0.006                | VREF                            |

# **DA9168 GUI**

For GUI Install and Setup, please refer to document: "UM\_PM\_051\_DA9168\_Performance\_Board\_User\_Manual"

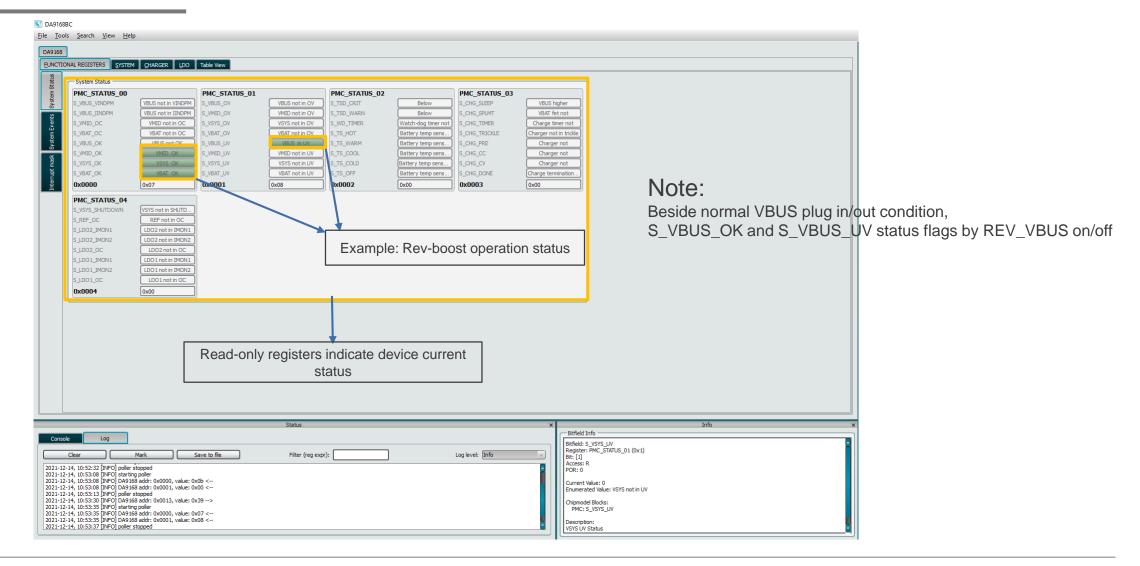

# **SYSTEM STATUS REGISTERS**

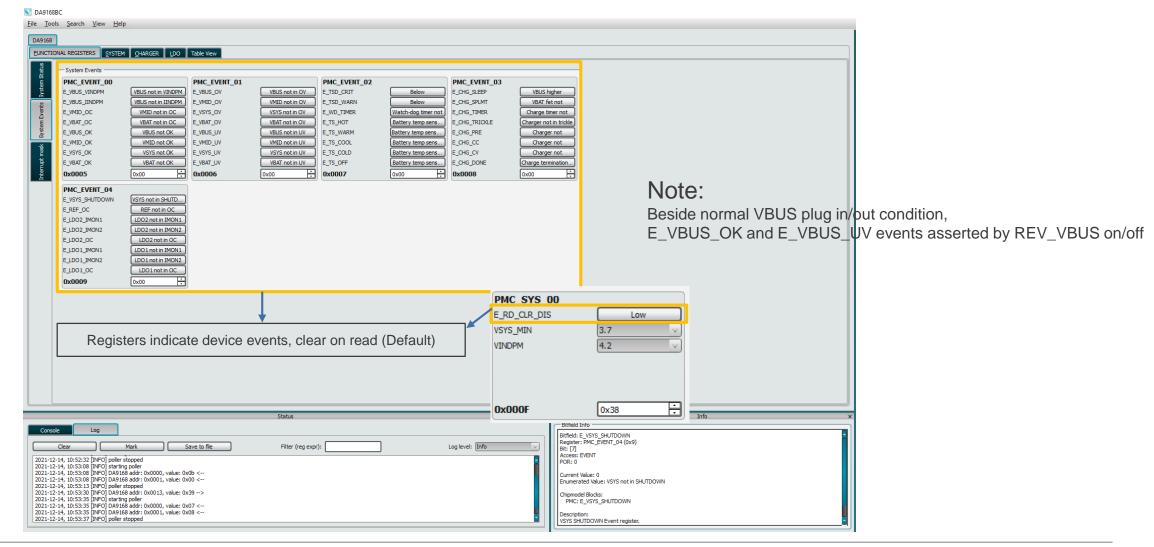

#### **SYSTEM EVENTS REGISTERS**

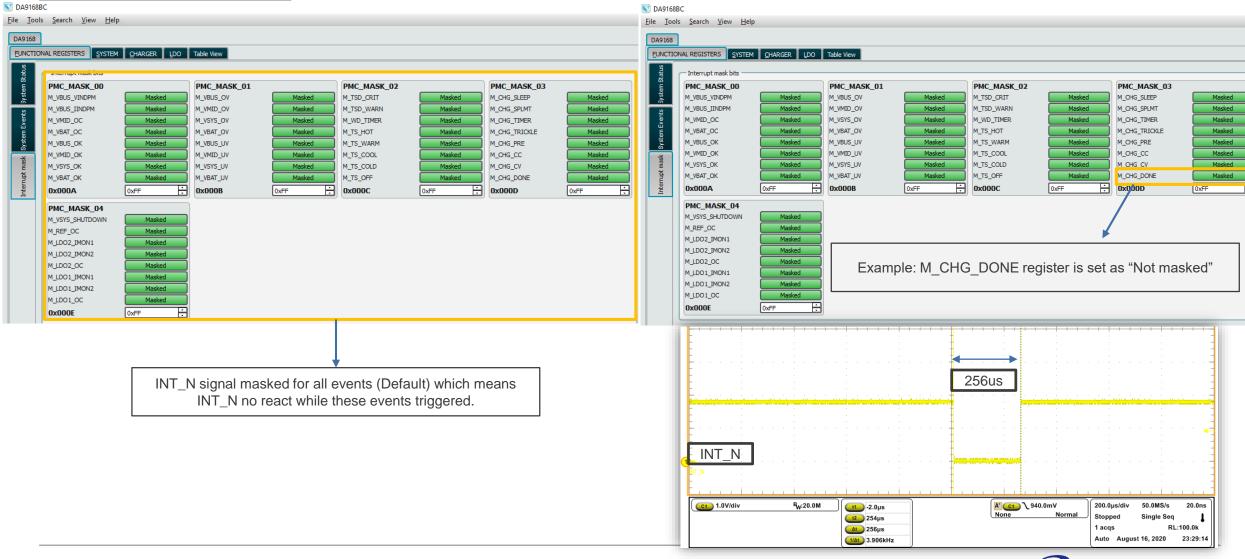

# **INTERRUPT MASK REGISTERS**

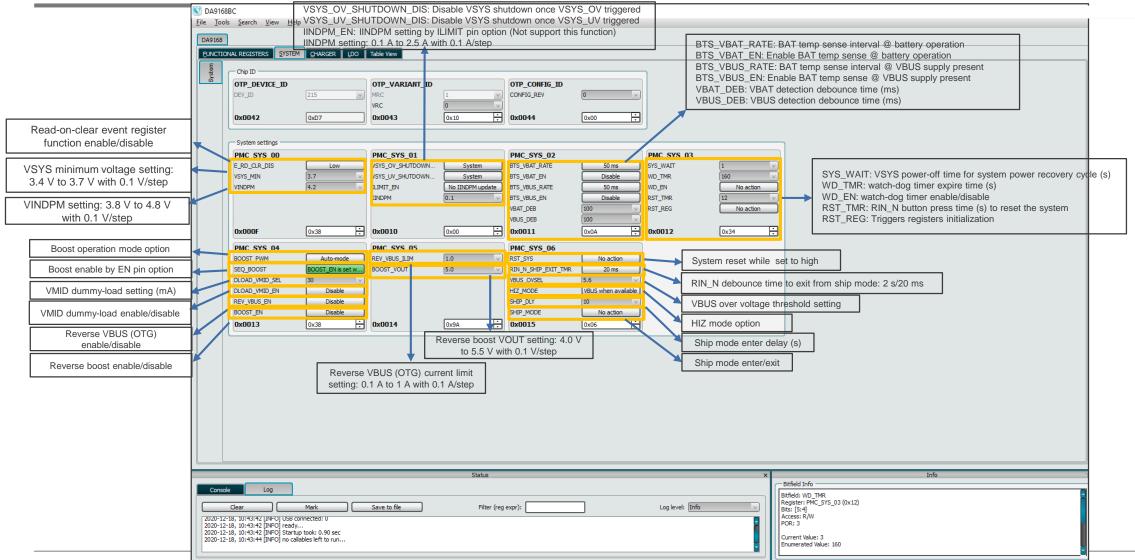

# **SYSTEM REGISTERS**

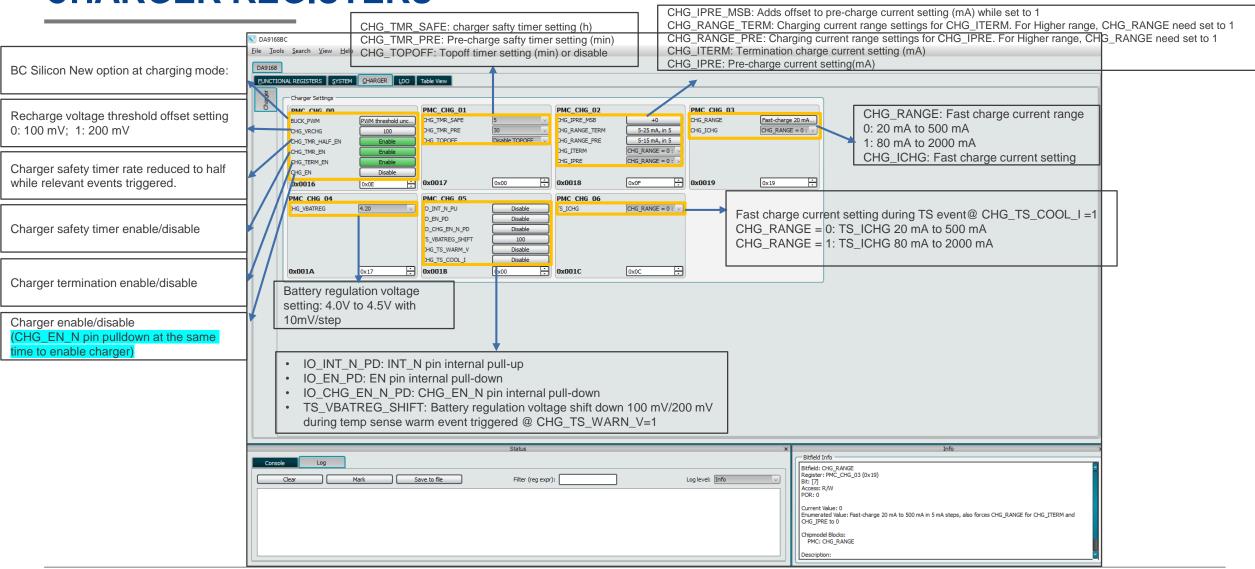

# **CHARGER REGISTERS**

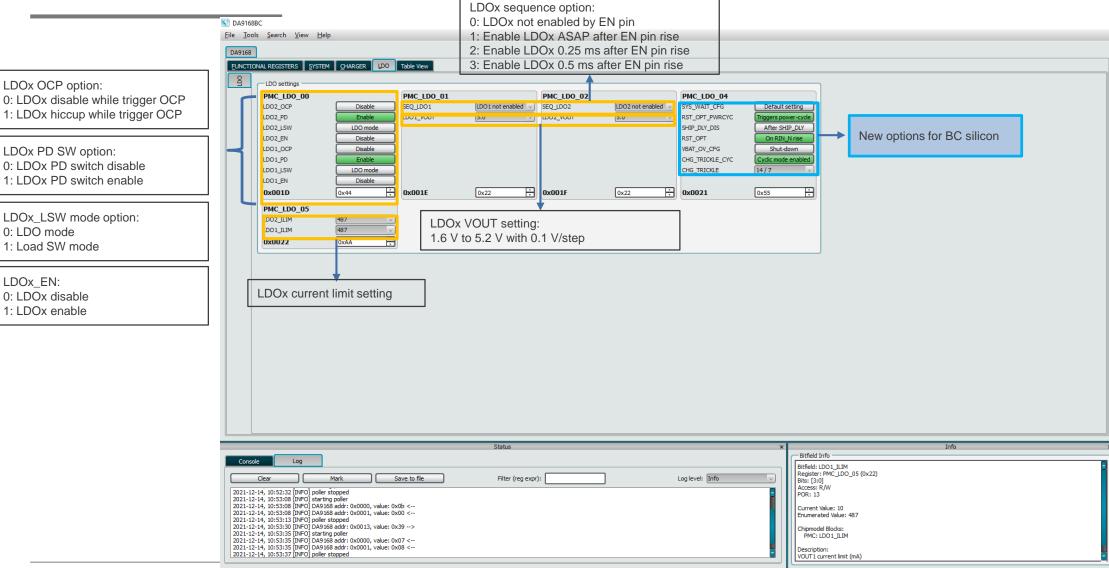

LDOS/LSWS REGISTERS

LDOx OCP option:

LDOx PD SW option:

0: LDOx PD switch disable

1: LDOx PD switch enable

LDOx LSW mode option:

0: LDO mode

LDOx EN:

1: Load SW mode

0: LDOx disable 1: LDOx enable

# TEST BENCH SETUP

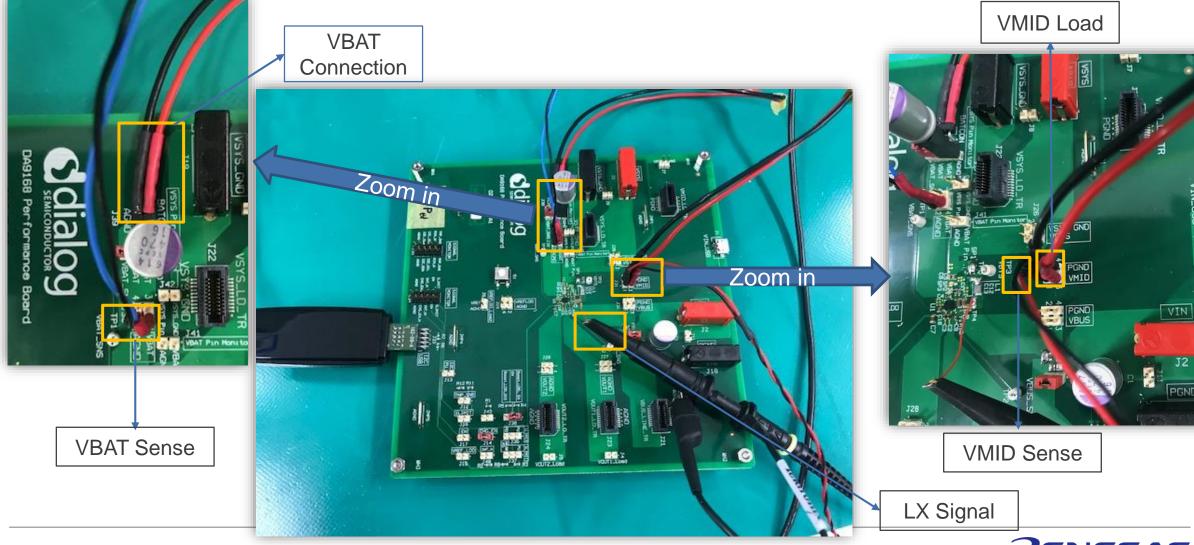

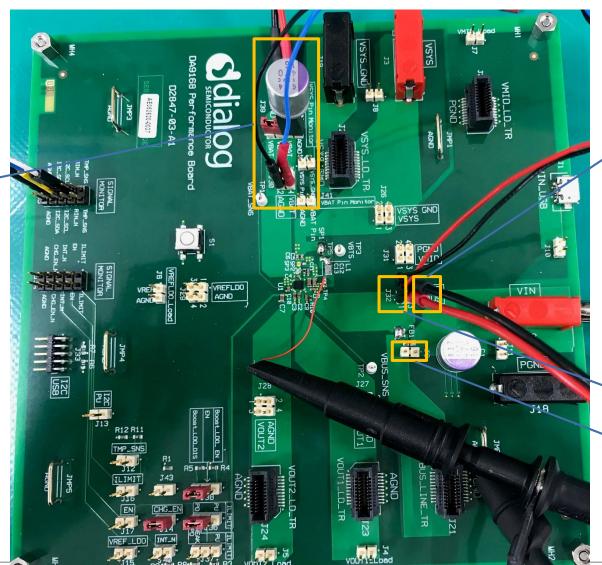

# **CHARGE MODE BOARD SETUP**

# CHARGE MODE TEST BENCH SETUP

# **REV-BOOST MODE BOARD SETUP**

# **REV-BOOST MODE TEST BENCH SETUP**

# **REV-VBUS (OTG) BOARD SETUP**

VBAT and VBAT sense connections are same with Rev\_boost setup

Rev-VBUS Load

> Rev-VBUS Sense

Remove jumper J9

# **REV-VBUS (OTG) TEST BENCH SETUP**

Renesas.com