# **RL78 Family**

R01AN7508EJ0101 Rev.1.01 Oct.20.25

# IEC 60730/60335 Self Test Library for RL78 MCU (Class-C)

#### Introduction

Today, as automatic electronic controls systems continue to expand into many diverse applications, the requirement of reliability and safety are becoming an ever increasing factor in system design.

For example, the introduction of the IEC60730 safety standard for household appliances requires manufactures to design automatic electronic controls that ensure safe and reliable operation of their products.

The IEC60730 standard covers all aspects of product design but Annex H is of key importance for design of Microcontroller based control systems. This provides three software classifications for automatic electronic controls:

- 1. Class A: Control functions, which are not intended to be relied upon for the safety of the equipment. Examples: Room thermostats, humidity controls, lighting controls, timers, and switches.

- 2. Class B: Control functions, which are intended to prevent unsafe operation of the controlled equipment. Examples: Thermal cut-offs and door locks for laundry equipment.

- 3. Class C: Control functions, which are intended to prevent special hazards Examples: Automatic burner controls and thermal cut-outs for closed.

This Application Note provides guidelines on how to use flexible sample software routines to assist with compliance with IEC60730 class C safety standards. These routines have been certified by VDE Test and Certification Institute GmbH and a copy of the Test Certificate is available in the download package for this Application Note.

The software routines provided are to be used after reset and also during the program execution. This document and the accompanying sample code provide an example of how to do this.

## **Target Device**

RL78/G23 MCU RL78/G14 MCU RL78/F24 MCU

# Contents

| 1.    | Overview of Self-test Library              | 4   |

|-------|--------------------------------------------|-----|

| 2.    | Self-test Library Functions                | 6   |

| 2.1   | Instruction Decoding Test                  | 6   |

| 2.1.1 | 1 CPU Instruction Test – Software API      | 8   |

| 2.2   | CPU Register Test                          | 10  |

| 2.2.1 | 1 CPU Register Test – Software API         | 12  |

| 2.3   | Invariable Memory Test – Flash ROM         | 18  |

| 2.3.1 | 1 CRC 16-CCITT algorithm                   | 18  |

| 2.3.2 | 2 Hardware CRC – Software API              | 19  |

| 2.4   | Variable Memory Test – SRAM                | 22  |

| 2.4.1 | 1 Algorithm                                | 22  |

| 2.4.2 | 2 Variable Memory Test – Software API      | 23  |

| 2.5   | System Clock Test                          | 26  |

| 2.5.1 | 1 Hardware Measurement                     | 26  |

| 2.6   | Watchdog                                   | 30  |

| 2.6.1 | 1 Monitoring by built-in WDT               | 30  |

| 2.7   | MCU Anomaly Detection                      | 31  |

| ^     | Francis Users                              | 0.0 |

| 3.    | Example Usage                              |     |

| 3.1   | CPU                                        |     |

| 3.1.1 |                                            |     |

| 3.1.2 |                                            |     |

| 3.2   | Flash ROM                                  |     |

| 3.2.1 |                                            |     |

| 3.2.2 |                                            |     |

| 3.3   | RAM                                        |     |

|       | 1 Power-on Tests                           |     |

| 3.3.2 |                                            |     |

| 3.4   | System Clock                               |     |

| 3.4.1 |                                            |     |

| 3.4.2 | 2 Periodic                                 | 36  |

| 4.    | Development Environment                    | 37  |

| 4.1   | CS+ Settings                               | 38  |

| 4.1.1 | 1 Common Options                           | 38  |

| 4.1.2 | 2 Link Options                             | 38  |

| 4.1.3 | 3 Hex Output Options                       | 39  |

| 4.1.4 | Download file for Debug Tool Configuration | 40  |

| 4.1.5 | 5 Code Generation (Design Tool)            | 40  |

| 4.2   | e <sup>2</sup> stuido Settings             | 43  |

|       |                                            |     |

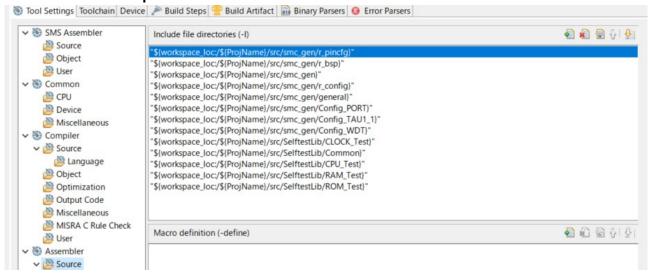

| 4.2.1 | Complier Options         | 43 |

|-------|--------------------------|----|

|       | Assembler Options        |    |

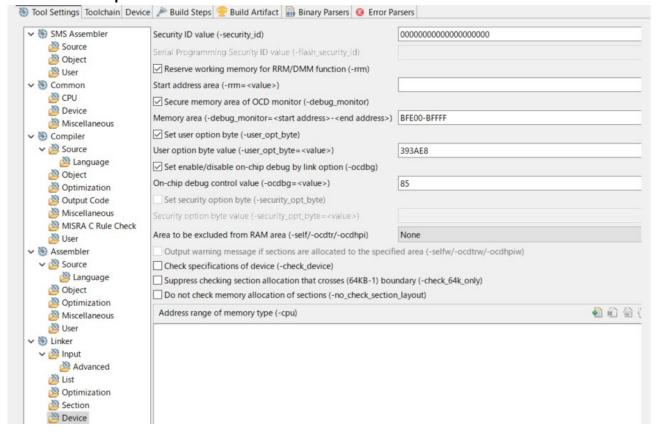

| 4.2.3 | Linker Options           | 44 |

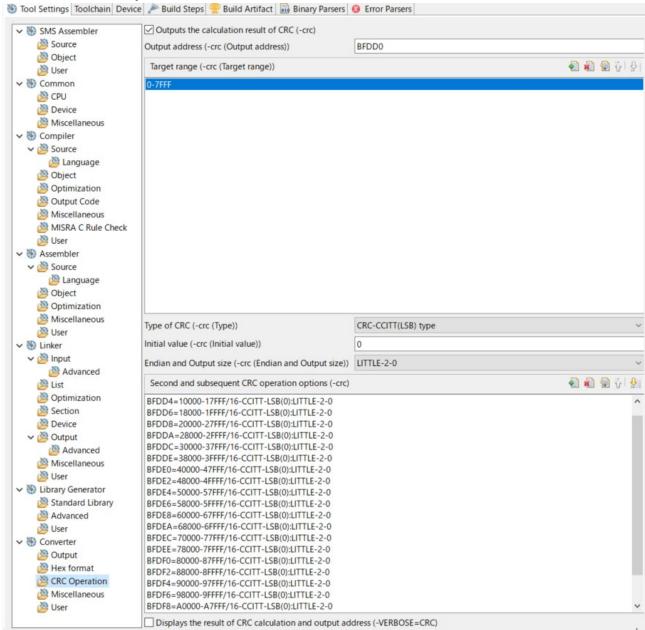

| 4.2.4 | Converter Options        | 45 |

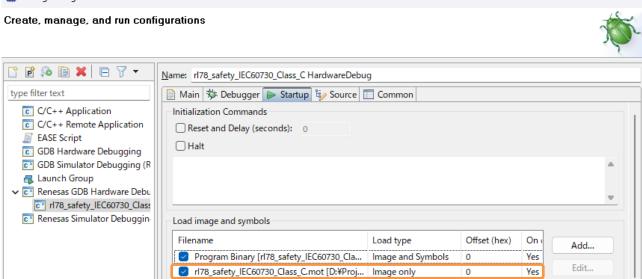

| 4.2.5 | Debug Configurations     | 46 |

| 5. E  | Benchmark Test results   | 47 |

| 6. F  | Related Application Note | 48 |

| Home  | page and Support Contact | 48 |

| Revis | sion History             | 49 |

## 1. Overview of Self-test Library

The self-test library (STL) consists of self-test functions targeting instruction decode, CPU registers, internal memory, watchdog timer and system clock. As described below, the test harness provides an application program interface (API) for each module that monitors. Each function is used according to its purpose. The test harness uses the automatic generation function of the integrated development environment.

The self-test library functions are divided by module according to IEC60730 Class-C. In the test harness, each test function can be selected in turn and executed standalone.

The system hardware required at least two independent clock sources (e.g., crystal/ceramic oscillator and an independent operating oscillator or external input source). It is needed to provide an independent clock reference for monitoring the system clock. RL78 can use the High speed and Low speed internal oscillators which are independent of each other.

The self-test library is intended for implementation in a safety MCU. By integrating the safety section MCU into the system, risk reduction can be achieved from failures and other anomalies.

RL78 self-test library includes the following self-test functions:

#### Instruction decoding

Verifies that combinations of all addressing mode work correctly for all instructions of RL78 MCU Refer to "IEC 60730-1:2013+A1:2015+A2:2020 Annex H - H2.18.5 equivalence class test."

#### CPU register

Test the following CPU registers.

All CPU general-purpose registers in all 4 register banks, Stack Pointer (SP), Program Status Word (PSW), and extended register (CS and ES)

The internal data path is verified during the normal operation test of the above registers

Refer to "IEC 60730-1:2013+A1:2015+A2:2020 Annex H - Table H.11.12.7 1.CPU"

Note: ABRAHAM algorithm is used for memory areas mapped as general-purpose registers.

#### Invariable memory

Test internal Flash memory of the MCU.

Refer to "IEC 60730-1:2013+A1:2015+A2:2020 Annex H - H2.19.4.1 CRC - Single Word"

## Variable memory

Test internal SRAM of the MCU

Refer to "IEC 60730-1:2013+A1:2015+A2:2020 Annex H - H.2.19.1 Abraham test"

## System clock

Test using TAU's input capture feature against the system clock (this test requires an internal or external independent reference clock).

Refer to "IEC Reference - IEC 60730-1:2013+A1:2015+A2:2020 Annex H - H2.18.10.1 Frequency monitoring"

### • CPU/ Program Counter (PC)

To confirm that the program is executing the sequence within the specified time, it is confirmed using the built-in watchdog timer that operates with a clock independent of the CPU. A process is implemented in the test harness to monitor whether the program is executing the expected sequence order.

Refer to "IEC 60730-1:2013+A1:2015+A2:2020 Annex H - H2.18.10.3 time-slot and logical monitoring"

## 2. Self-test Library Functions

#### 2.1 Instruction Decoding Test

This test verifies that all instructions of RL78/G23 core in all addressing mode perform correctly. There are 2 types of execution: one with function calls from test harness process, and one without function calls from test harness process. The test startup without function calls from test harness process verifies all instructions before initializing "C" environment with a modified "startup.asm" module. If any anomaly is detected, stl\_RL78\_InstructionTest\_Fail is called.

The target addressing mode and instructions are as follows.

For detail of addressing mode instructions, please refer to "RL78 Family User's Manual: Software" (R01US0015).

#### (1) Instruction Address Addressing

There are 4 types of instruction address addressing as follows:

- Relative addressing

- Immediate addressing

- Table indirect addressing

- Register direct addressing

- (2) Addressing for Processing Data address

There are 9 types of addressing for processing data address as follows:

- Implied addressing

- Register addressing

- Direct addressing

- Short direct addressing

- SFR addressing

- Register indirect addressing

- Based addressing

- Based indexed addressing

- Stack addressing

- (3) RL78/G23 Instructions

RL78-S3 core has 81 types of instructions as follows:

[8-bit Data Transfer Instructions]

MOV XCH **ONEB CLRB MOVS**

[16-bit Data Transfer Instructions]

MOVW XCHGW **ONEW**

[8-bit Operation Instructions]

**CMPS** ADD ADDC **SUB** SUBC AND OR XOR CMP CMP0

[16-bit Operation Instructions]

SUBW ADDW **CMPW**  [Multiply/Divide/Multiply & Accumulate Instructions]

MULU MULUH MULH DIVHU DIVWU MACHU MACH

[Increment/Decrement Instructions]

INC DEC INCW DECW

[Shift Instructions]

SHR SHRW SHL SHLW SAR SARW

[Rotate Instructions]

ROR ROL RORC ROLC ROLWC

**(Bit Manipulation Instructions)**

MOV1 AND1 OR1 XOR1 SET1 CLR1 NOT1

[Call Return Instructions]

CALL CALLT BRK RET RETI RETB

[Stack Manipulation Instructions]

PUSH POP

MOVW SP,src

MOVW AX,SP

ADDW SP,#Byte

SUBW SP,#byte

[Unconditional Branch Instructions]

BR

[Conditional Branch Instructions]

BC BNC BZ BNZ BH BNH BT BF BTCLR

[Conditional Skip Instructions]

SKC SKNC SKZ SKNZ SKH SKNH

**[CPU Control Instructions]**

SEL RBn NOP EI DI HALT STOP

Note: BRK, RETB, RETI, HALT, STOP are excluded from the instruction test.

## 2.1.1 CPU Instruction Test - Software API

Table 2-1 Source File: Periodic CPU instruction test

| STL File name                | Header File |

|------------------------------|-------------|

| stl_RL78_InstructionTest.asm | stl.h       |

| Test Harness File Name       | Header File |

| main.c                       |             |

**Syntax**

unsigned char stl\_RL78\_InstructionTest (void)

Description

Test RL78 instructions other than the ones listed below

EI DI

The instructions listed above are tested in initial processing.

The call function should not generate an interrupt during the test. Also, the test should start with register bank0 selected

Test harness control file (main.c) calls stl\_RL78\_InstructionTest\_Fail when an error is detected.

| Input Parameters  |                                    |  |

|-------------------|------------------------------------|--|

| None              | N/A                                |  |

| Output Parameters |                                    |  |

| None              | N/A                                |  |

| Return Values     |                                    |  |

|                   | Test result                        |  |

| unsigned char     | 0 = Test passed                    |  |

|                   | 1 = Test or parameter check failed |  |

## Table 2-2 Source File: Initial CPU instruction test

| STL File                     | Header File                  |

|------------------------------|------------------------------|

| stl_RL78_InstructionTest.asm | stl_RL78_InstructionTest.inc |

| Test Harness File Names      | Header File                  |

| startup.asm                  |                              |

| Syntax                                                           |                                                                                                   |  |  |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| stl_RL78_InitialInstruction                                      | stl_RL78_InitialInstructionTest                                                                   |  |  |

| Description                                                      |                                                                                                   |  |  |

| Test all RL78 instruction                                        | S                                                                                                 |  |  |

| This module is executed                                          | This module is executed before the application system is initialized. No function calls are used. |  |  |

| When it finishes normally                                        | When it finishes normally, jump to stl_RL78_InstructionTest_Pass                                  |  |  |

| When an error is detected, jump to stl_RL78_InstructionTest_Fail |                                                                                                   |  |  |

| Input Parameters                                                 |                                                                                                   |  |  |

| None                                                             | N/A                                                                                               |  |  |

| Output Parameters                                                |                                                                                                   |  |  |

| None                                                             | N/A                                                                                               |  |  |

| Return Vales                                                     |                                                                                                   |  |  |

| None                                                             | N/A                                                                                               |  |  |

#### 2.2 **CPU Register Test**

This chapter describes each routine of the CPU register test. The test harness control file "main.c" contains API samples written in C language for each C register test.

These modules test the basic operation of CPU. Each API function informs the test result by return values.

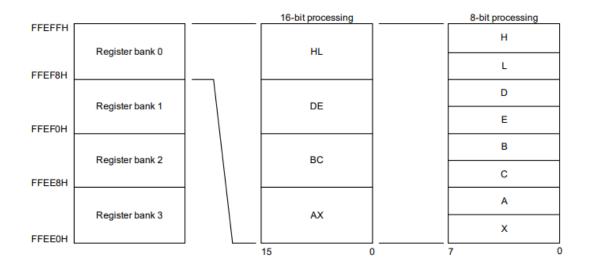

The target CPU registers are as follows:

General-Purpose Register: AX、HL、DE、BC of Register bank 0~3

Figure 2-1 Configuration of General-Purpose Registers

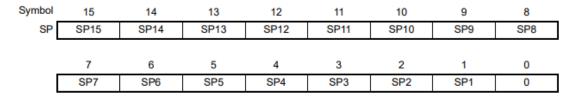

Stack Pointer (SP)

Figure 2-2 Format of Stack Pointer

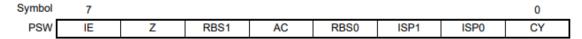

Program Status Word (PSW)

Oct.20.25

Figure 2-3 Format of Program Status Word

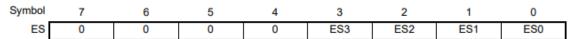

· CS register

Figure 2-4 Configuration of ES

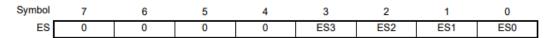

· ES register

Figure 2-5 Configuration of ES

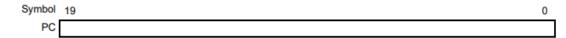

Program Counter (PC)

Figure 2-6 Format of Program Counter

## 2.2.1 CPU Register Test - Software API

Table 2-3 Source file: CPU general-purpose register test

| STL File Name             | Header File |

|---------------------------|-------------|

| stl_RL78_RegisterTest.asm | stl.h       |

| Test Harness File Name    | Header File |

| main.c                    |             |

## Syntax

unsigned char stl\_RL78\_RegisterTest(unsigned char Bank)

## Description

Test RL78 general-purpose registers.

Register AX, HL, DE, BC in specified register bank (Bank 0, 1, 2, 3)

ABRAHAM algorithm is performed on memory areas mapped as registers.

It is the calling function's responsibility to ensure no interrupts occur during this test. In addition, Register Bank 0 must be selected when this test starts.

The original register contents are restored on completion of the test.

| Input Parameters   |                                    |  |

|--------------------|------------------------------------|--|

| unsigned char Bank | Target register bank (0~3)         |  |

| Output Parameters  |                                    |  |

| None               | N/A                                |  |

| Return Values      |                                    |  |

|                    | Test result                        |  |

| unsigned char      | 0 = Test passed                    |  |

|                    | 1 = Test or parameter check failed |  |

Table 2-4 Source file: CPU register test - PSW

| STL File Name                          | Header File |

|----------------------------------------|-------------|

| stl_RL78_registertest_psw.asm          | stl.h       |

| Anomality Monitoring Process File Name | Header File |

| r_main.c                               |             |

unsigned char stl\_RL78\_registertest\_psw(void)

## Description

Test 8-bit Program Status Word (PSW) register

The following tests are performed:

- 1. Write h'55 to the register

- 2. Read out the register and check that it is equal to the written value

- 3. Write h'AA to the register

- 4. Read out the register and check that it is equal to the written value

It is the calling function's responsibility to ensure no interrupts occur during this test.

The original register content is restored on completion of the test

| Input Parameters  |                                     |  |

|-------------------|-------------------------------------|--|

| None              | N/A                                 |  |

| Output Parameters |                                     |  |

| None              | N/A                                 |  |

| Return Values     |                                     |  |

|                   | Test result                         |  |

| unsigned char     | 0 = Test passed                     |  |

|                   | 1 = Test or parameter check failed. |  |

Table 2-5 Source file: CPU register test - SP

| STL File Name                          | Header File |

|----------------------------------------|-------------|

| stl_RL78_registertest_stack.asm        | stl.h       |

| Anomality Monitoring Process File Name | Header File |

| r_main.c                               |             |

unsigned char stl\_RL78\_registertest\_stack(void)

## Description

Test 16-bit Stack pointer (SP) register

The following tests are performed

- 1. Write h'5555 to the register

- 2. Read out the register and check that it is equal to h'5554

- 3. Write h'AAAA to the register

- 4. Read out the register and check that it is equal to the written value

It is the calling function's responsibility to ensure no interrupts occur during this test.

The original register content is restored on completion of the test

| Input Parameters  |                                    |  |

|-------------------|------------------------------------|--|

| None              | N/A                                |  |

| Output Parameters |                                    |  |

| None              | N/A                                |  |

| Return Values     |                                    |  |

|                   | Test Result                        |  |

| unsigned char     | 0 = Test passed₀                   |  |

|                   | 1 = Test or parameter check failed |  |

Table 2-6 Source file: CPU register test - CS

| STL File Name                          | Header File |

|----------------------------------------|-------------|

| stl_RL78_registertest_cs.asm           | stl.h       |

| Anomality Monitoring Process File Name | Header File |

| r_main.c                               |             |

unsigned char stl\_RL78\_registertest\_cs(void)

## Description

Test the 8-bit CS register

The following tests are performed.

- 1. Write h'05 to the register

- 2. Read out the register and check that it is equal to the written value

- 3. Write h'0A to the register

- 4. Read out the register and check that it is equal to the written value

Please note that the top 4 bits are fixed to '0'

It is the calling function's responsibility to ensure no interrupts occur during this test.

The original register content is restored on completion of the test

| Input Parameters  |                                    |

|-------------------|------------------------------------|

| None              | N/A                                |

| Output Parameters |                                    |

| None              | N/A                                |

| Return Values     |                                    |

|                   | Test result                        |

| unsigned char     | 0 = Test passed                    |

|                   | 1 = Test or parameter check failed |

Table 2-7 Source file: CPU register test - ES

| STL File Name                          | Header File |

|----------------------------------------|-------------|

| stl_RL78_registertest_es.asm           | stl.h       |

| Anomality Monitoring Process File Name | Header File |

| r_main.c                               |             |

unsigned char stl\_RL78\_registertest\_es(void)

## Description

Test the 8bit data extension (ES) register

The following tests are performed

- 1. Write h'05 to the register

- 2. Read out the register and check that it is equal to the written value

- 3. Write h'0A to the register

- 4. Read out the register and check that it is equal to the written value

Please note that the top 4 bits are fixed to '0'

It is the calling function's responsibility to ensure no interrupts occur during this test.

The original register content is restored on completion of the test

| Input Parameters  |                                    |

|-------------------|------------------------------------|

| None              | N/A                                |

| Output Parameters |                                    |

| None              | N/A                                |

| Return Values     |                                    |

|                   | Test Result                        |

| unsigned char     | 0 = Test passed                    |

|                   | 1 = Test or parameter check failed |

Table 2-8 Source file: CPU register test - PC

| STL File Name                | Header File |

|------------------------------|-------------|

| stl_RL78_Registertest_pc.asm | stl.h       |

| Test Harness File Name       | Header File |

| main.c                       |             |

unsigned char stl\_RL78\_RegisterTest\_pc(void)

## Description

The following tests are performed

- 1. Set the argument (A register) to 0x55

- 2. Call a function that returns the reversed result of the argument

- 3. Confirm that the return value is 0xAA

- 4. Confirm that the return value is equal to the return address.

It is the calling function's responsibility to ensure no interrupts occur during this test.

| dotootod.         |                                    |  |

|-------------------|------------------------------------|--|

| Input Parameters  |                                    |  |

| None              | N/A                                |  |

| Output Parameters |                                    |  |

| None              | N/A                                |  |

| Return Values     |                                    |  |

|                   | Test result                        |  |

| unsigned char     | 0 = Test passed                    |  |

|                   | 1 = Test or parameter check failed |  |

## 2.3 Invariable Memory Test – Flash ROM

This section describes the Flash memory test using CRC routines. CRC is a fault / error control technique which generates a single word or checksum to represent the contents of memory. A CRC checksum is the remainder of a binary division with no bit carry (XOR used instead of subtraction), of the message bit stream, by a predefined (short) bit stream of length n + 1, which represents the coefficients of a polynomial with degree n. Before the division 'n' zeros are appended to the message stream. CRCs are popular because they are simple to implement in binary hardware and are easy to analyze mathematically.

The Flash ROM test can be verified by generating a reference CRC value for the contents of the ROM and storing this in memory. During the memory self-test, the same CRC algorithm is used to generate a CRC value, which is compared with the reference CRC value. The technique recognizes all one-bit errors and a high percentage of multi-bit errors.

The complicated part of using CRCs is if you need to generate a CRC value that will then be compared with other CRC values produced by other CRC generators. This proves difficult because there are a number of factors that can change the resulting CRC value even if the basic CRC algorithm is the same. This includes the combination of the order that the data is supplied to the algorithm, the assumed bit order in any look-up table used and the required order of the bits of the actual CRC value. Any of the test functions can be repeated, thus allowing the option of a full CRC calculation to be made or a CRC calculation of a smaller segments suitable to the operation of the end application. For a full calculation (or first part of an iterative calculation), an initial value of h'0000 is used or the previous partial result is provided as the starting point for the next calculation stage.

The hardware module is "the general-purpose CRC function" embedded in RL78 device. The hardware module while using the same fundamental CRC algorithm uses a different data format (LSB first) for calculating the reference CRC value.

As a note for debugging, when a software break is set in the debugger, the instruction code at the specified address is temporarily rewritten to the instruction for the break since any of the test functions can be executed repeatedly. Therefore, CRC mismatch may occur.

### 2.3.1 CRC 16-CCITT algorithm

RL78 CRC module supports CRC16-CCITT.

Hardware algorithm

- CCITT 16 Polynomial =  $0x1021 (x^{16} + x^{12} + x^5 + 1)$

- Input Data width = 8bits

- LSB first (operation is performed with the bit order reversed on input, and the operation result is also output with the bit order reversed)

- Initial value = 0x0000 or 16 bit result of previous partial CRC calculation

### 2.3.2 Hardware CRC - Software API

Table 2-9 Source file: Hardware CRC calculation

| STL File Name               | Header File |

|-----------------------------|-------------|

| stl_RL78_peripheral_crc.asm | stl.h       |

| Test Harness File           | Header File |

| main.c                      |             |

### **Syntax**

unsigned short stl\_RL78\_peripheral crc(unsigned short crc, CHECKSUM\_CRC\_TEST\_AREA \*p)

## Description

This function calculates a CRC value over the address range supplied using the hardware CRC peripheral (general purpose CRC). The start address and calculation range (Length) are passed by the calling function via the structure detailed in the table below. The calculated result is returned. This can be either a partial result of full result depending upon the parameters provided.

The harness file (main.c) compares the result of calculated CRC in the divided areas.

Note: Set the same value as that set in CC-RL for the range subject to CRC check and the address where CRC value is saved in the invariable memory.

| Input Parameters          |                                                                                                                  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------|--|

| unsigned short crc        | Initial value for CRC calculation (0 is specified only for the first block, otherwise it is the previous result) |  |

| CHECKSUM_CRC_TEST_AREA *p | Pointer to structure that stores the start address and calculation range                                         |  |

| Output Parameters         |                                                                                                                  |  |

| None                      | N/A                                                                                                              |  |

| Return Values             |                                                                                                                  |  |

| unsigned short            | 16bit CRC value (Full or partial result)                                                                         |  |

Table 2-10 Source file: Hardware CRC parameter structure

| Syntax                                                                                                                                                               |                                                   |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|

| static CHECK_CRC_TEST_AREA_lv_CheckCrc;                                                                                                                              |                                                   |  |

| Description                                                                                                                                                          |                                                   |  |

| Structure declaration and instance providing the parameters to be passed to the hardware CRC module (stl_RL78_peripheral_crc.asm) by the calling function in main.c. |                                                   |  |

| Input Parameters                                                                                                                                                     |                                                   |  |

| unsigned long m_length;                                                                                                                                              | Range (length = number of bytes) of target memory |  |

| unsigned long m_start_address                                                                                                                                        | Start address for CRC calculation                 |  |

| Output parameters                                                                                                                                                    |                                                   |  |

| None                                                                                                                                                                 | N/A                                               |  |

| Return Values                                                                                                                                                        |                                                   |  |

| None                                                                                                                                                                 | N/A                                               |  |

### Definition of test harness CRC calculation target

```

typedef struct CRC_RANGE

{

uint32_t Start;

uint32_t End;

}CRC RANGE;

```

The ROM test calculates the CRC value in units of 32 Kbytes and checks for a match with the CRC saved in a specific area.

Note: On-chip debugger occupies 512bytes from the last address in ROM. Therefore, the CRC storage address is the last address of ROM – 512 – (Number of blocks\*2) at the beginning.

```

#define CRC_RANGE_NUM (sizeof(CRC_Ranges)/sizeof(CRC RANGE))

const CRC RANGE CRC Ranges[] =

/* 32K */

\{0x00000,0x07FFF\},

/* 64K */

{0x08000,0x0FFFF},

\{0x10000,0x17FFF\},

/* 96K ,0x17FFF - 512 - (3 * 2) */

{0x18000,0x1FFFF},

/* 128K ,0x1FFFF - 512 - (4 * 2) */

/* 160K */

\{0x20000,0x27FFF\},

/* 192K ,0x2FFFF - 512 - (6 * 2) */

{0x28000,0x2FFFF},

/* 224K */

\{0x30000,0x37FFF\},

{0x38000,0x3FFFF},

/* 256K ,0x3FFFF - 512 - (8 * 2) */

/* 288K */

\{0x40000,0x47FFF\},

/* 320K */

\{0x48000,0x4FFFF\},

/* 384K ,0x5FFFF - 512 - (12 * 2) */

\{0x58000, 0x5FFFF\},\

/* 416K */

\{0x60000, 0x67FFF\},\

```

```

{0x68000,0x6FFFF},

/* 448K */

/* 480K */

\{0x70000,0x77FFF\},

\{0x78000,0x7FFFF\},

/* 512K ,0x7FFFF - 512 - (16 * 2) */

{0x80000,0x87FFF},

/* 544K */

/* 576K */

{0x88000,0x8FFFF},

\{0x90000,0x97FFF\},

/* 608K */

{0x98000,0x9FFFF},

/* 640K */

{ 0xA0000, 0xA7FFF},

/* 672K */

/* 704K */

{ 0xA8000, 0xAFFFF},

/* 736K */

{0xB0000,0xB7FFF},

\{0xB8000,0xBFFFF - 512 - (24 * 2)\} /* 768K */

};

```

Please change with the target MCU.

Definition of CRC calculation result storage area

It is defined in stl.h.

```

#define DEF ROM CRC (0xBFDD0)

```

Please change with the target MCU.

## 2.4 Variable Memory Test - SRAM

ABRAHAM test is a method of RAM test that meets IEC 60730-1:2013+A1:2015+A2:2020 Annex H – H2.19.1.

The algorithm itself is destructive and does not save the current RAM values. Therefore, RAM contents must be saved if tests are performed after initialization of the application system or during running. The additional test module (stl\_RL78\_InitialRamTest) is designed to be executed before initializing the system, so that the whole memory area can be tested before starting the main application.

The RAM area to be tested can't be used for any other purpose during testing. This makes testing RAM used as a stack particularly difficult. This area can only be tested before the application's C stack is initialized or after the application process is finished.

The next chapter describes the ABRAHAM test.

## 2.4.1 Algorithm

#### (1) ABRAHAM

ABRAHAM algorithm consists of 10 elements that perform 30 different processes in total. It detects the following faults:

- 1. Stuck At Faults (SAF)

- The logic value of a single cell or contiguous cells is always 0 or 1

- 2. Transition Faults (TF)

- · A single cell or contiguous cells does not transit from 0→1 or 1→0

- 3. Coupling Faults (CF)

- The state or transition of a cell value causes the value of other cell to change

- 4. Address Decoder Faults (AF)

- · Failure affects address decoding

- · Unable to access a certain address cell

- · Unable to access a certain cell

- · Unable to access multiple cells simultaneously with a certain address

- A certain cell is accessed from multiple addresses

| ⇔ (w0)                                    | Initialize | $\Leftrightarrow\ :$ Perform in ascending or descending order of address |

|-------------------------------------------|------------|--------------------------------------------------------------------------|

| ↓ (r0, w1) ↑ (r1)                         | Sequence 1 | ↓ : Perform in a descending order of the address                         |

| ↓ (r1, w0) ↑ (r0)                         | Sequence 2 | $\uparrow$ : Perform in an ascending order of the address                |

| ↑ (r0, w1) ↓ (r1)                         | Sequence 3 | w0 : write 0 to the cell                                                 |

| ↑ (r1, w0) ↓ (r0)                         | Sequence 4 | w1 : write 1 to the cell                                                 |

| ↓ (r0, w1, w0) ↑ (r0)                     | Sequence 5 | r0 : Read 0 from the cell as expected                                    |

| ↑ (r0, w1, w0) ↑ (r0)                     | Sequence 6 | r1 : Read 1 from the cell as expected                                    |

| ⇔ (w1)                                    | Reset      |                                                                          |

| ↑ (r1, w0, w1) ↑ (r1)                     | Sequence 7 |                                                                          |

| $\downarrow$ (r1, w0, w1) $\uparrow$ (r1) | Sequence 8 |                                                                          |

## 2.4.2 Variable Memory Test - Software API

## 2.4.2.1 Time Division ABRAHAM

Execute after initialization of the application system. Uses C stack resources for execution with normal function calls from the test harness. It is possible to test part or all of RAM area, but the area to be tested must be buffered because it is destructive. Therefore, it is not recommended to test the entire RAM area in a single run. Also, be careful that the test itself does not destroy the RAM area used as the stack area. The time division ABRAHAM executes ABRAHAM by treating the divided areas.

| ⇔[x,y] (w0)                                     | Initialize | ⇔[x,y]:  | Perform in ascending or descending order |

|-------------------------------------------------|------------|----------|------------------------------------------|

| $\downarrow$ [x,y](r0, w1) $\uparrow$ (r1)      | Sequence 1 |          | of address in the range of x and y       |

| $\downarrow$ [x,y](r1, w0) $\uparrow$ (r0)      | Sequence 2 | ↓[x,y] : | Perform in descending order of address   |

| $\uparrow$ [x,y](r0, w1) $\downarrow$ (r1)      | Sequence 3 |          | in the range of x and y                  |

| $\uparrow$ [x,y] (r1, w0) $\downarrow$ (r0)     | Sequence 4 | ↑[x,y]:  | Perform in ascending order of address    |

| $\downarrow$ [x,y] (r0, w1, w0) $\uparrow$ (r0) | Sequence 5 |          | in the range of x and y                  |

| $\uparrow$ [x,y] (r0, w1, w0) $\uparrow$ (r0)   | Sequence 6 | w0:      | write 0 to the cell                      |

| $\Leftrightarrow$ [x,y] (w1)                    | Reset      | w1:      | write 1 to the cell                      |

| $\uparrow$ [x,y] (r1, w0, w1) $\uparrow$ (r1)   | Sequence 7 | r0:      | Read 0 from the cell as expected         |

| $\downarrow$ [x,y] (r1, w0, w1) $\uparrow$ (r1) | Sequence 8 | r1:      | Read 1 from the cell as expected         |

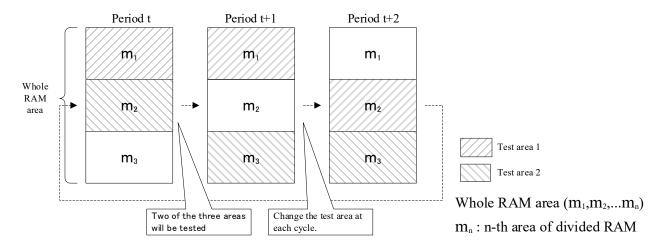

3-partition case is shown in Figure 2-7. [x,y] is [m1,m2], [m1,m3], [m2,m3] respectively.

For example, if the memory is divided into 3 parts, testing the combination of m1 and m2 at period t, m1 and m3 at period t+1, m2 and m3 at period t+2, the results are equivalent to the test the entire memory at once.

Figure 2-7 Overview of Time Division ABRAHAM

Table 2-11 Source file: Variable memory test

| STL File Name     | Header File |

|-------------------|-------------|

| stl_RL78_Ram.asm  | stl.h       |

| Test Harness File | Header File |

| main.c            |             |

unsigned char stl\_RL78\_RamTest (unsigned char \*pRam1, unsigned char \*pRam2, unsigned short Size)

## Description

Test the address range of RAM specified by the calling function using the time division ABRAHAM algorithm and return the result (pass/fail). This module should be executed after initialization of the application system.

The calling function must always start with register bank 0 selected.

The contents of the area under test must be saved beforehand. The test is executed destructively.

Use register bank 1 as the work area.

| Input Parameters     |                                                   |  |

|----------------------|---------------------------------------------------|--|

| unsigned char *pRam1 | Pointer to the first address of RAM1 to be tested |  |

| unsigned char *pRam2 | Pointer to the first address of RAM2 to be tested |  |

| unsigned short Size  | RAM range to be tested (number of bytes)          |  |

| Output Parameters    |                                                   |  |

| None                 | N/A                                               |  |

| Return values        |                                                   |  |

|                      | Test result                                       |  |

| unsigned char        | 0 = Test passed                                   |  |

|                      | 1 = Test or parameter check failed                |  |

### 2.4.2.2 Initial ABRAHAM

Initial ABRAHAM test is performed before the application system is initialized. It does not use function calls from the test harness for execution. The test is started by a jump from the modified "startup.asm" module, and a return to the "startup.as" module is also done by a jump. The test results are stored in the 8-bit accumulator(A). Thus, the entire area of RAM can be tested before booting the system and initializing the "C" environment.

Table 2-12 Source file: Initial ABRAHAM

| STL File Name            | Header File |

|--------------------------|-------------|

| stl_RL78_InitialmRam.asm | None        |

| Test Harness File        | Header File |

| startup.asm              | None        |

| ,   |       |                |

|-----|-------|----------------|

| stl | RI 78 | InitialRamTest |

### Description

Svntax

Test the address range of RAM specified by the calling function using the time division ABRAHAM algorithm and return the result (pass/fail). This module should be executed after initialization of the application system. No function call is used. The test result if done through the function 'stl\_RL78\_InitialRamTestResult'.

Note: the function 'stl\_RL78\_InitialRamTestResult' is in the module main.c.

| Input Parameters  |                                                                    |  |

|-------------------|--------------------------------------------------------------------|--|

| CPU register AX   | 16-bit register that stores the first address of the target RAM    |  |

| CPU register BC   | 16-bit register that stores the target RAM range (number of bytes) |  |

| Output Parameters |                                                                    |  |

| None              | N/A                                                                |  |

| Return Values     |                                                                    |  |

|                   | Test result                                                        |  |

| CPU register A    | 0 = Test passed                                                    |  |

|                   | 1 = Test or parameter check failed                                 |  |

## 2.5 System Clock Test

A self test module provided for RL78 self test library in order to be able to test the internal system clock (CPU and Peripheral clocks). These modules can be used by the application to detect the correct operation and deviation in the main system clock during operation of the application. Please note that if the internal low speed oscillator is used for measurement, the accuracy of the system clock measurement will be reduced due to the greater tolerance of the internal low speed oscillator. Therefore, only the relative operation of the system clock can be obtained, which should still be sufficient to establish that the system clock is operating correctly and within acceptable limits.

The principle behind both measurement approaches is that the system can detect if the operating frequency of the main clock deviates from a predefined range during runtime. The accuracy of the measurement obviously depends on the accuracy of the reference clock source. For example, an external signal input or 32KHz crystal can provide a more accurate measurement for the system clock than the internal low speed oscillator. However, it requires extra components.

A "Pass / Fail" status of the test is returned. Also implemented is a "No Reference Clock" detection scheme which returns a different status value to the normal test, to identify the appropriate fault state. The module compares the measure (captured) time is within a reference window (upper and lower limit values) using the user defined reference values set in 'stl\_RL78\_hw\_clocktest.inc' header file. The header file defines the reference values for hardware measurement and input test port pins.

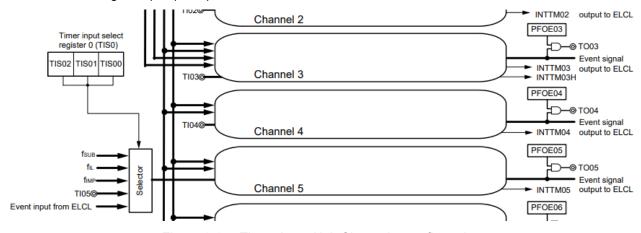

#### 2.5.1 Hardware Measurement

All current RL78 devices include an option in the Timer Array Unit (TAU) channel 5 that provides additional input capture sources that are designed to be able to test the system clock operation. The extra capture inputs are selected as part of the "safety" register (TIS0) and include the following:

- · Internal Low-speed oscillator (fiL)

- External 32KHz oscillator (Sub Clock) (fsub)

- External signal input (TIO5)

Figure 2-8 Timer Array Unit Channel 5 configuration

Note: In RL78/G14, F24, Channel 1 is the measurement channel.

The principle behind the hardware measurement is based on the input capture measurement of the reference clock in TAU channel 5. As this is a hardware capture measurement the time captured is the "period" of the reference clock as that of the system clock.

The measurement sequence is.

- · Synchronize to the reference clock (Wait for first capture event)

- · Wait for the next capture event

- Compare the value in the capture register against the high and lower limit reference values

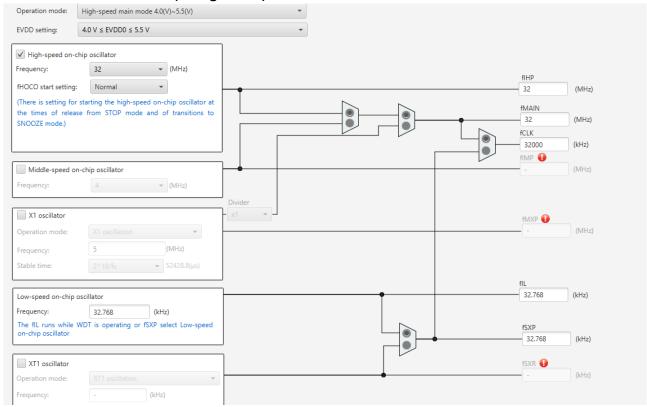

The anomaly monitoring process provides a sample based on the following settings.

System clock = 32 MHz

Reference clock = 32.768 kHz

Therefore, the calculation is 32000000/32768 = 976

Note: The internal low-speed oscillator of RL78/G14, F24 is 15kHz.

The capture value should be set to the allowed fluctuation range relative to the upper and lower limits of the reference values.

[Timer setting (setting of automatic generation function)]

Channel 5: Input pulse interval measurement

Timer input; flL

Pin input valid range: Rising edge.

Interrupt: not generated

Note: RL78/G14, F24 use Channel 1

Table 2-13 Source File: Hardware Clock test

| STL File Name             | Header File               |  |

|---------------------------|---------------------------|--|

| stl_RL78_hw_clocktest.asm | stl_RL78_hw_clocktest.inc |  |

|                           | stl.h                     |  |

| Test Harness File         | Header File               |  |

| main.c                    |                           |  |

| Syntax                                                                       |                                                 |  |

|------------------------------------------------------------------------------|-------------------------------------------------|--|

| void stl_RL78_Init_hw_clocktest (unsigned char Select)                       |                                                 |  |

| Description                                                                  |                                                 |  |

| Start capturing the system clock using hardware measurements (TAU channel 5) |                                                 |  |

| Input Parameters                                                             |                                                 |  |

|                                                                              | Input of TAU Channel 5                          |  |

| Select                                                                       | 0: Input signal of timer input pin (TI05)       |  |

|                                                                              | 5: Subsystem clock (fsub)                       |  |

|                                                                              | Other: Low-speed on-chip oscillator clock (flL) |  |

| Output Parameters                                                            |                                                 |  |

| None                                                                         | N/A                                             |  |

| Return Values                                                                |                                                 |  |

| None                                                                         | N/A                                             |  |

| C. | ntax |

|----|------|

| S۷ | шах  |

unsigned char stl\_RL78\_hw\_clocktest(void)

## Description

This function tests the system clock using the hardware measurement (TAU channel 5) feature. The measured result (capture value) is compared against the upper and lower limit values defined in the clock test header file (stl\_RL78\_hw\_clocktest.inc) and the result status (Pass / Fail / No reference clock) is returned to the calling function.

| Input Parameters       |                                                                       |  |

|------------------------|-----------------------------------------------------------------------|--|

| hwMAXTIME              | Upper time limit compare value (defined in stl_RL78_hw_clocktest.inc) |  |

| hwMINTIME              | Lower time limit compare value (Defined in stl_RL78_hw_clocktest.inc) |  |

| CAPTURE_interrupt_FLAG | Timer channel Capture Interrupt Flag (stl_RL78_hw_clocktest.inc)      |  |

| Output Parameters      |                                                                       |  |

| None                   | N/A                                                                   |  |

| Return Values          |                                                                       |  |

|                        | Test result                                                           |  |

| unsigned char          | 0 = Test passed.                                                      |  |

|                        | 1 = Test measurement failed (Outside the reference window)            |  |

|                        | 2 = Test measurement failed (No reference clock detected)             |  |

## 2.6 Watchdog

A built-in watchdog timer monitors whether the program is operating as expected.

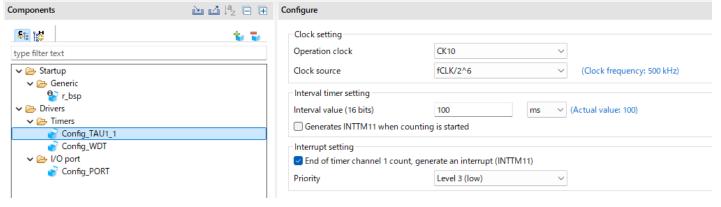

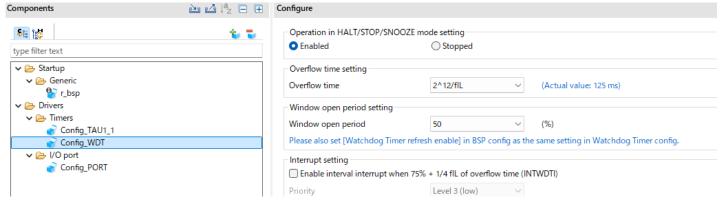

[Watchdog setting (setting of automatic generation function)]

Waterdog timer: enable.

Watchdog timer operation in HALT/STOP mode: continues.

Overflow Time: 125ms(2^12/flL) Window Open Period: 50%

Interval interrupt is generated when 75% of the overflow time + 1/4 flL is reached: not used.

## 2.6.1 Monitoring by built-in WDT

Table 2-14 Source file: built-in WDT clear

| STL File Name     | Header File  |

|-------------------|--------------|

| Config_WDT.c      | Config_WDT.h |

| Test Harness File | Header File  |

| main.c            |              |

| Syntax                   |                                  |  |  |

|--------------------------|----------------------------------|--|--|

| void R_Config_WDT_Resta  | void R_Config_WDT_Restart (void) |  |  |

| Description              |                                  |  |  |

| Refresh the built-in WDT |                                  |  |  |

| Input Parameters         |                                  |  |  |

| None                     | N/A                              |  |  |

| Output Parameters        |                                  |  |  |

| None                     | N/A                              |  |  |

| Return Values            |                                  |  |  |

| Noe                      | N/A                              |  |  |

# 2.7 MCU Anomaly Detection

RL78/G23 has SFR to check the reset factor. The self-test library can be configured to analyze the reset factor and call the following function when it is not a power-up reset.

| Factor                      | Option settings                      | Calling functions            |

|-----------------------------|--------------------------------------|------------------------------|

|                             | (stl_RL78_TestConfig.inc)            |                              |

| Header File                 | Illegal_MemoryAccess_enabled         | Illegal_MemoryAccess         |

| RAM parity error            | RAM_Parity_Failure_enabled           | RAM_Parity_Failure           |

| Watchdog timer over         | Watchdog_Test_enabled                | Watchdog_Test_Failure        |

| Execution of illegal orders | Illegal_InstructionExecution_enabled | Illegal_InstructionExecution |

| Voltage abnormal            | Voltage_Test_Reset_enabled           | Voltage_Test_Failure_Reset   |

Note: RL78/F24 has no RAM parity error.

## 3. Example Usage

In addition to the actual test software source files, the CS+/e²studio test harness workspace is provided which includes application examples demonstrating how the tests can be run. This code should be examined in conjunction with this document to see how the various test functions are used. The testing can be split into two parts:

#### (1) Power-on Tests

These are tests can be run following a power on or reset. They should be run as soon as possible to ensure that the system is working correctly. These tests are

- All instructions test

- Initial RAM test using ABRAHAM algorithm

- All register test

- Flash memory CRC test

The clock test may be run at a later time depending on the initial clock speed if the clock is to establish that the maximum clock speed is to be measured.

#### (2) Periodic Tests

These are tests that are run regularly throughout normal program operation. This document does not provide a judgment of how often a particular test should be ran. How the scheduling of the periodic tests is performed is up to the user depending upon how their application is structured.

#### RAM test

These tests should use the "system" Ram test modules as these are designed to test the memory in small once the system is initialised. They can be used in small in order to minimise the size of the buffer area needed to save the application data.

#### Register test

These are dependent upon the application timing.

## Periodic instruction test

These are dependent upon the application timing.

#### Flash memory test

These modules are designed to be able to accumulate a CRC result over a number of passes. In this way they can be used to suit the system operation.

The clock test modules can be run at any time to suit the application timing

The following sections provide an example of how each test can be used.

## 3.1 CPU

If a fault is detected by any of the CPU tests, then this is very serious. The aim of this test should be to get to a safe operating point, where software execution is not relied upon, as soon as possible.

### 3.1.1 Power-on Tests

All the CPU tests should be run as soon as possible following a reset.

#### 3.1.2 Periodic

If testing the CPU registers periodically the function is designed to be run independently and so can be operated at any time to suit the application. Each function restores the original register data on completion of test so as not to corrupt the operation of the application system. It is important that interrupts are disabled during these tests.

#### 3.2 Flash ROM

The ROM is tested by calculating a CRC value over a certain range of the Flash memory contents and comparing with a reference CRC value that must be added to a specific location in the ROM not included in the CRC calculation.

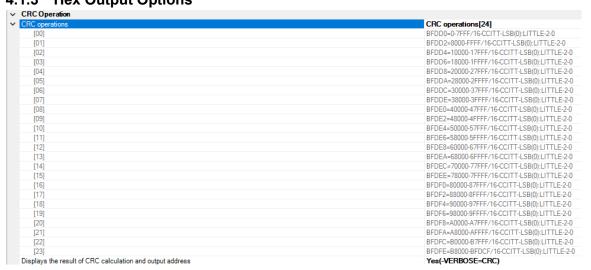

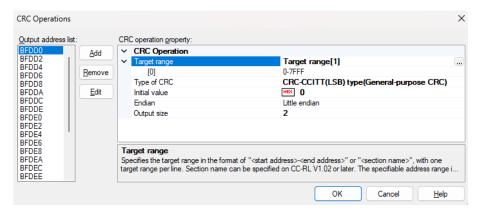

The CS+ /e²Studio tool chain can be used to calculate and add a CRC value and place at a location specified by the user. CS+ /e²Studio grants three types of CRC: "general-purpose CRC", "high-speed CRC (CCR-16-CCITT)", and "high-speed CRC (SENT)". Hardware CRC calculation provides in this library (function "stl\_RL78\_peripheral\_crc") corresponds to the "general-purpose CRC". See Figure 4-3 CS+/e²Studio Hex Output Options for how to incorporate the CRC value in CC-RL

#### 3.2.1 Power-on Tests

All the ROM memory used must be tested at power up. Both hardware and software CRC modules are capable of calculating the CRC value over the whole memory range.

#### 3.2.2 Periodic

It is suggested that the periodic testing of Flash memory is done in stages, depending on the time available to the application. The application will need to save the partially calculated result if using the software module. This value can then be set as starting point for the next stage of the CRC calculation.

When using the hardware peripheral unit, the partial CRC result value could be left in the result register of the hardware CRC peripheral unit, but it is advised to save this value and compare it before starting the next part of the calculation.

In this way all of the Flash memory can be verified in time slots convenient to the application.

#### 3.3 RAM

When verifying the RAM, it is important to remember the following points:

- RAM being tested cannot be used for anything else including the current stack.

- Any test requires a RAM buffer where memory contents can be safely copied to and restored from.

- The stack area cannot be tested after initializing the system unless its contents are relocated to another area and the stack pointer is changed accordingly. Also, no interrupt processing is allowed during the operation.

#### 3.3.1 Power-on Tests

All instructions test of MCU is performed at Power-on or reset. If the test fails, it jumps to stl\_RL78\_InstructionTest\_Fail without calling the main function. It is recommended to use initial RAM test modules after all instructions test is done. These modules are designed specifically for testing all RAM areas at Power-on or reset. They are also suitable to be executed before initializing the system and C stack, since they do not require function calls but destroy the RAM contents. In this library, the initial RAM test is implemented in the assembler file startup.asm.

#### 3.3.2 Periodic

Periodic testing of the Ram memory is usually done in small stages, depending on the time available to the application and the available space necessary to buffer the system Ram contents during testing. Each stage provides a pass / fail status over the range specified, in this way all of the Ram memory can be verified time slots convenient to the application.

## 3.4 System Clock

If a fault is detected with the system clock then this is very serious. The aim of this test should be to get to a safe operating point, where the system can be controlled using a different known clock.

### 3.4.1 Power-on Tests

The system clock should be verified at power on or reset. It may be necessary to test the clock once the system has been initialized and the full system clock frequency has been set and stabilized.

### 3.4.2 Periodic

Periodic testing of the system clock can be made at any time where the application has the time available. This is because the reference clock is typically much slower than the system clock in order to increase the accuracy of the clock measurement.

(System Clock = 32MHz, Reference Clock = 32KHz)

Note: The reference clock of RL78/G14, F24 is 15KHz.

## 4. Development Environment

• EZ-LITE

• RL78/G23 Fast Prototyping Board

Tool chain

• MCU

Internal clock

Low speed clock

On-chip debugging emulator RL78/G23 (128 pin LFQFP)

R7F100GSN2DFB

32 MHz High speed on-chip Oscillator

System clock = 32 MHz

32 kHz Low speed on-chip oscillator

### 4.1 CS+ Settings

### 4.1.1 Common Options

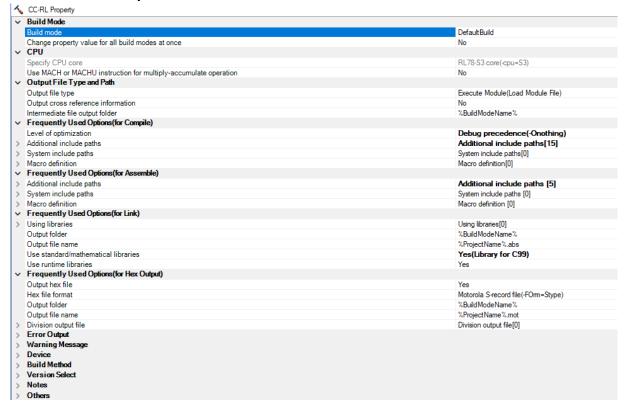

Figure 4-1 CS+ Common Options

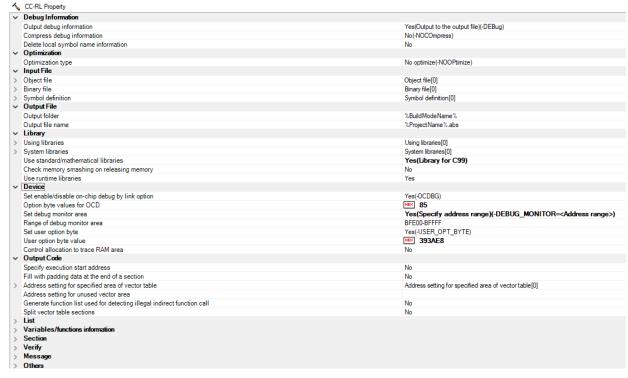

### 4.1.2 Link Options

Figure 4-2 CS+ Link Options

### 4.1.3 Hex Output Options

Figure 4-3 CS+ Hex Output Options

### 4.1.4 Download file for Debug Tool Configuration

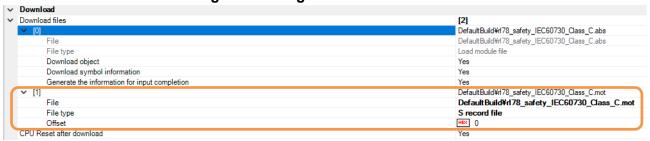

Figure 4-4 CS+ Download file for Debug Tool Configuration

### 4.1.5 Code Generation (Design Tool)

Figure 4-5 Clock Generation Circuit

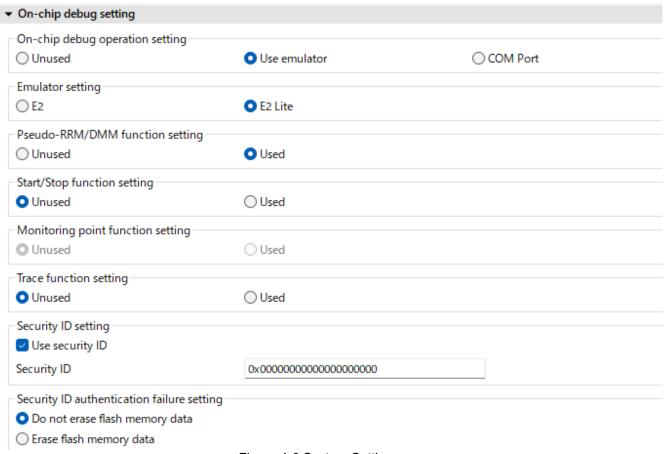

Figure 4-6 System Setting

Figure 4-7 Periodic Timer Setting

Figure 4-8 WDT Setting

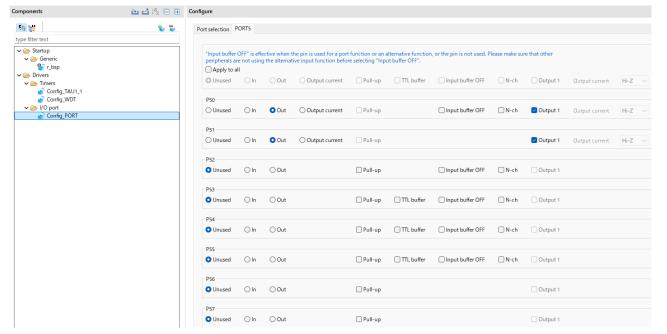

Figure 4-9 Port Setting

### 4.2 e<sup>2</sup>stuido Settings

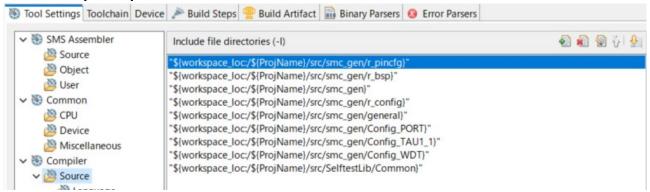

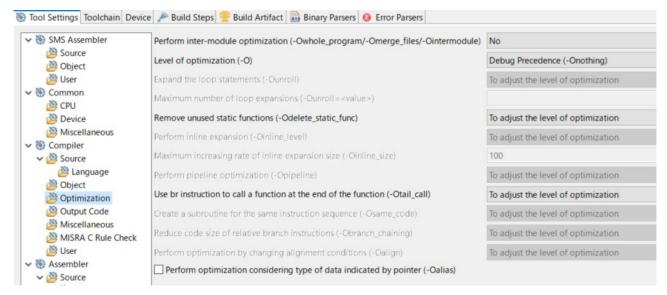

### 4.2.1 Complier Options

Figure 4-10 C Source Include Path

Figure 4-11 Optimization

### 4.2.2 Assembler Options

Figure 4-12 asm Source Include Path

### 4.2.3 Linker Options

Figure 4-13 Device Setting

### 4.2.4 Converter Options

Figure 4-14 CRC Calculation Setting

Set the output destination address and calculation range according to the MCU

# **4.2.5 Debug Configurations**Debug Configurations

Figure 4-15 Download file for e<sup>2</sup> studio debug tool configuration

## 5. Benchmark Test results

| Library functions                 | Number of bytes tested | Processing time | ROM size   |

|-----------------------------------|------------------------|-----------------|------------|

| CPU instruction decode test       | -                      | 600µs           | 562bytes   |

| stl_RL78_InitialInstructionTest   |                        |                 |            |

| CPU instruction decode test       | -                      | 300µs           | 12939bytes |

| stl_RL78_InstructionTest          |                        |                 |            |

| CPU general-purpose register test | -                      | 200µs           | 1126bytes  |

| stl_RL78_registertest             |                        |                 |            |

| CPU register test - PSW           | -                      | 1.343µs         | 43bytes    |

| stl_RL78_registertest_psw         |                        |                 |            |

| CPU register test - SP            | -                      | 1.125µs         | 50bytes    |

| stl_RL78_registertest_stack       |                        |                 |            |

| CPU register test - CS            | -                      | 1.031µs         | 43bytes    |

| stl_RL78_registertest_cs          |                        |                 |            |

| CPU register test - ES            | -                      | 1.031µs         | 41bytes    |

| stl_RL78_registertest_es          |                        |                 |            |

| CPU register test - PC            | -                      | 0.857µs         | 17bytes    |

| stl_RL78_registertest_pc          |                        |                 |            |

| Hardware CRC                      | 1024 bytes             | 700us           | 73bytes    |

| stl_RL78_peripheral_crc           |                        |                 |            |

| System RAM test                   | 32 bytes* 2            | 1.4ms           | 1305bytes  |

| stl_RL78_RamTest                  |                        |                 |            |

| Initial RAM test                  | 508 bytes              | 10.8ms          | 980bytes   |

| stl_RL78_InitialRamTest           |                        |                 | -          |

| Hardware clock test               | -                      | 56.40µs         | 136bytes   |

| stl_RL78_hw_clocktest             |                        |                 |            |

### 6. Related Application Note

The application note related to this application note is listed below for reference.

·RL78 Family VDE Certified IEC60730/60335 Self Test Library APPLICATION NOTE (R01AN1062J)

### **Home page and Support Contact**

Renesas Electronics Home Page

http://www.renesas.com/index.jsp

Contact for inquiries

http://www.renesas.com/contact/

# **Revision History**

|      |            | Description |                                                              |

|------|------------|-------------|--------------------------------------------------------------|

| Rev. | Date       | Page        | Summary                                                      |

| 1.00 | 2025.5.31  |             | First edition issued                                         |

| 1.01 | 2025.10.20 |             | Add e <sup>2</sup> studio version in Development Environment |

# General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

1. Precaution against Electrostatic Discharge (ESD)

A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

2. Processing at power-on

The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

3. Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

4. Handling of unused pins

Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

5. Clock signals

After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

- 6. Voltage application waveform at input pin

- Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

- 7. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

8. Differences between products

Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.