## PCB Layout Considerations for VersaClock® Clock Generator Family

## Introduction

This document describes general layout guidelines and recommendations for the VersaClock family of devices. This includes the fifth and sixth generation 5P49V5/5P49V6, as well as the third-generation 5P35021/23 of programmable clocks.

## Contents

|                                                                          |    |

|--------------------------------------------------------------------------|----|

| 1. Overview .....                                                        | 2  |

| 2. Power Supply Filtering .....                                          | 3  |

| 2.1 Bulk Capacitance .....                                               | 4  |

| 2.2 Decoupling Capacitors .....                                          | 4  |

| 2.3 Bypass Capacitors .....                                              | 4  |

| 2.4 Capacitor Model .....                                                | 4  |

| 2.5 Ferrite Beads .....                                                  | 5  |

| 2.6 Methodology to Use for Computing Bypass Values .....                 | 7  |

| 3. VersaClock Inputs .....                                               | 8  |

| 3.1 XIN/XOUT .....                                                       | 8  |

| 3.2 Recommended Crystal for VersaClock Devices .....                     | 9  |

| 4. Device Electrical and Thermal Pad .....                               | 9  |

| 5. Recommendations for Optimal Return Path (cutouts in GND planes) ..... | 10 |

| 6. Output Signal Integrity .....                                         | 11 |

| 6.1 Trace Length Considerations .....                                    | 11 |

| 6.2 Guidelines for Routing VersaClock's Single-ended Traces .....        | 13 |

| 6.3 Routing VersaClock's Differential Traces .....                       | 13 |

| 6.4 EMI .....                                                            | 13 |

| 7. Conclusion .....                                                      | 14 |

| 8. Revision History .....                                                | 14 |

| A. Methodology for Computing Bypass Values .....                         | 15 |

| B. Board Layout .....                                                    | 16 |

| C. Impedance of Common Transmission Lines .....                          | 17 |

## 1. Overview

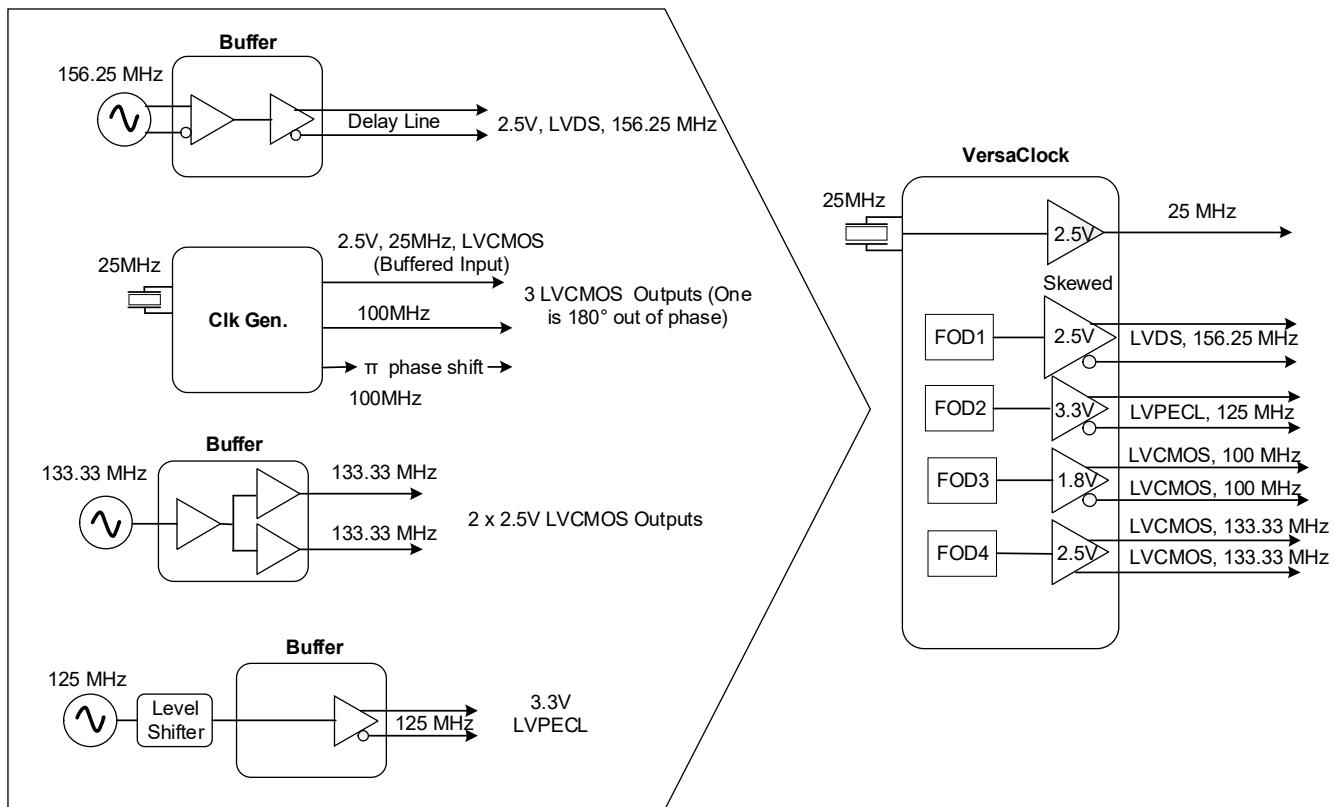

The VersaClock family of devices generate highly configurable outputs from a single reference clock that can be selected in a glitch free manual manner between two input clocks. Configurability includes spread spectrum, output termination as LVCMS single or differential, standard differential LVDS, LVPECL or HCSL as well as slew rate, loop bandwidth, and individual output enable. The VersaClock family of devices is intended for high performance consumer, networking, industrial, computing, and data-communications applications. Up to four different configurations can be stored and selected using two select pins or through I<sup>2</sup>C. VersaClock's excellent jitter performance enables it to land itself in a wide range of applications including PCIe Gen1 through 5, USB 3.0, 1 and 10 GbE applications. As shown in [Figure 1](#), the VersaClock family can enable a major BOM reduction and board simplification with not much more layout effort.

**Figure 1. VersaClock Family Replacing Multiple Timing Components**

Single ended LVCMS input reference and output frequencies can range from 1MHz to 200MHz. Differential (HCSL, LVPECL and LVDS) input reference and output clocks can range from 1MHz up to 350MHz. Although IDT recommends using 25MHz Crystal (see [603-25-150](#)), any fundamental mode crystal from 8MHz to 40MHz can be used.

The VersaClock 6 family offers multiple parts with different numbers of outputs. The 5P49V6965 offers a standard 4 universal output pairs, while the 5P49V6967 offers more outputs, including 3 universal output pairs and 4 extra LPHCSL pairs. The 5P49V6968 has the most outputs including 3 universal output pairs and 8 extra LPHCSL pairs. The VersaClock 6 family supports PCIe Gen1–5, different output frequencies up to 350MHz, and also an automotive version AEC-Q100 qualified 5P49V60 variant.

The VersaClock 5/6 family offers multiple parts with different number of outputs. The 5P49V5923, 5P49V5925, 5P49V5927 provide options for up to 3, 5, 7 and 9 single ended LVCMS outputs. An integrated crystal version of VersaClock 5/6 is also offered with the 5P49V5933 and 5P49V5935 devices. Other devices with more configurable outputs satisfying the performance requirement of PCIe and various applications such as 1Gb and 10Gb Ethernet, PCIe Gen1-2-3 etc. are available, such as 5P49V5907 and 5P49V5908. To accommodate these

frequency ranges, few principles and recommendations are provided when designing VersaClock 5/6 clocks into a printed circuit board for best results.

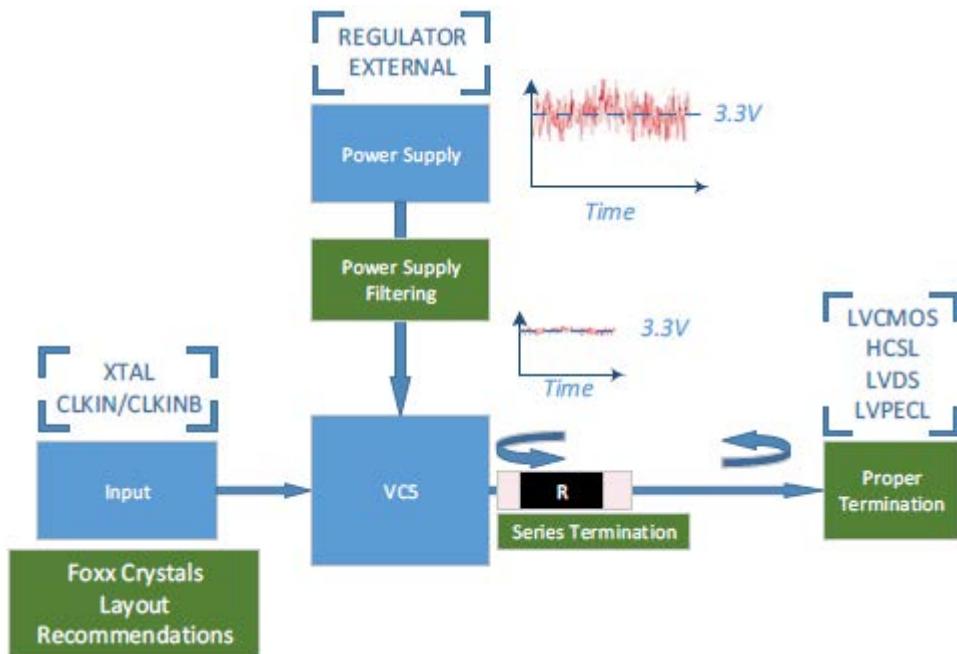

In this document, we will discuss some layout recommendations and best practices in designing PCB planes and traces with Renesas clock devices in general, and VersaClock family generation in particular, to ensure a solid pathway to power system and good signal integrity to get the best performance out of Renesas Clock devices. These best practices and recommendations land themselves into three major areas as illustrated in [Figure 2](#): power supply filtering, signal trace and terminations as well as crystal input reference and quality crystal sourcing recommendations for optimal performance.

**Figure 2. Block Diagram of the Three Categories – Power Supply Filtering, Signal Trace and Terminations, and Crystal Input Reference**

## 2. Power Supply Filtering

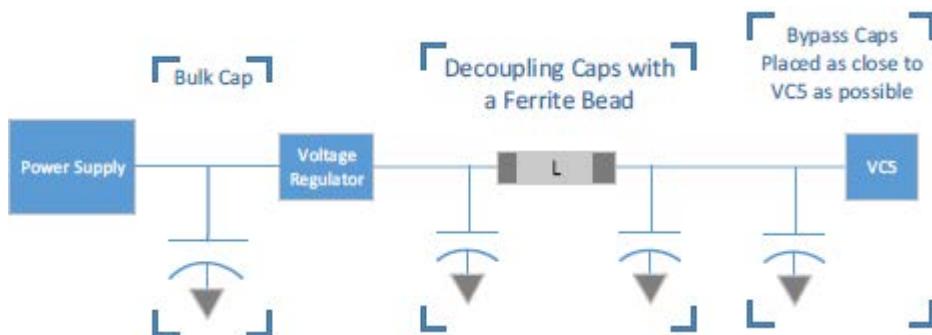

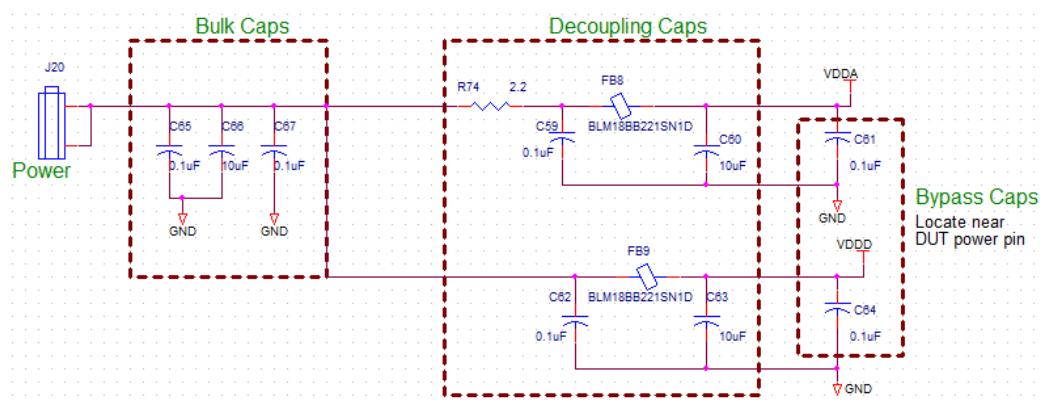

Power filtering is one of the most important measures to prevent power supply noise from coupling to the device outputs, adversely affecting performance, especially when using switched power supplies. Renesas recommends power supply filtering with a parallel combination of Bulk, decoupling and bypass capacitors as shown in [Figure 3](#). In this section, the roles of different filtering caps will be briefly outlined.

**Figure 3. VersaClock 5/6 Power Supply Filtering Block Diagram**

## 2.1 Bulk Capacitance

These are usually large size capacitors. Their benefits include limiting supply surge currents.

## 2.2 Decoupling Capacitors

Multiple types of regulators (Linear and Switching) are often used to shift voltage levels and to reject power supply ripple and provide a clean power to the device. Power supply decoupling is achieved with a ferrite bead (or a resistor) and capacitors forming a pi-low pass filter topology, as shown in [Figure 3](#). The benefits include:

- Preventing the transmission of noise from power supply to the device

- Acting as a low pass filter

- Assisting the bypass role

## 2.3 Bypass Capacitors

Bypass caps, often small size caps and placed close to the device, are used to shunt the high-frequency noise to ground.

**Figure 4. Isolating VDDA and VDDD in VersaClock Devices**

Because of their ubiquitous presence in circuits, it is important to understand the frequency response of a capacitor over a wide range of frequencies.

## 2.4 Capacitor Model

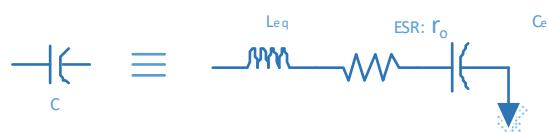

In light of the structure of the capacitor, an intuitive model would suggest a series inductor (leads), a series resistance associated with the leads (unless the connections are made out of supra-conductors) and a 2-plate capacitor. Having a good understanding of the capacitor model will help grasp their use, the filtering role they play, and will allow better power supply filtering.

$$C = r_o + j \left( \omega L_{eq} - \frac{1}{\omega C_{eq}} \right) \quad (1) \quad (2)$$

**Figure 5. Capacitor Model**

Examining equation (2), at low frequencies both  $r_o$  and  $\omega L_{eq}$  are negligible in front of the quantity  $\frac{1}{\omega C_{eq}}$  which rolls off at -20 dB/decade.

The frequency at which resonance occurs  $\omega L_{eq} = \frac{1}{\omega C_{eq}}$  or  $f = \frac{1}{2\pi\sqrt{L_{eq}C_{eq}}}$ , the capacitor looks just like  $r_o$ .

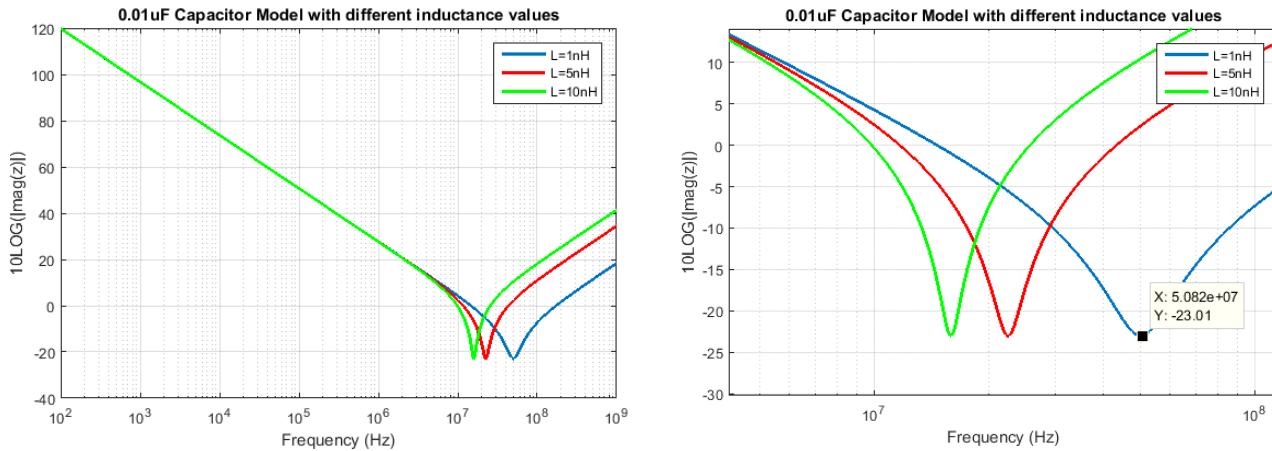

Above this frequency,  $\omega L_{eq}$  starts dominating with a positive 20 dB/decade growth as shown in [Figure 6](#) below illustrating an example for  $C = 0.01\mu F$ ,  $Leq: (1,5,10)nH$  and  $R_o = 0.1\Omega$  resulting in  $f_r = 50.82MHz$  and  $\text{Min}(\text{Mag}) = 10\text{Log}_{10}(0.1) = -23.01$  for  $Leq = 1nH$ .

**Figure 6. a) Log Plot of the Complex Impedance of a  $0.01\mu F$ , 2W and  $1\mu H$  Capacitance Model b) Zoom into the Resonance  $20\log(2) = 6\text{dB}$**

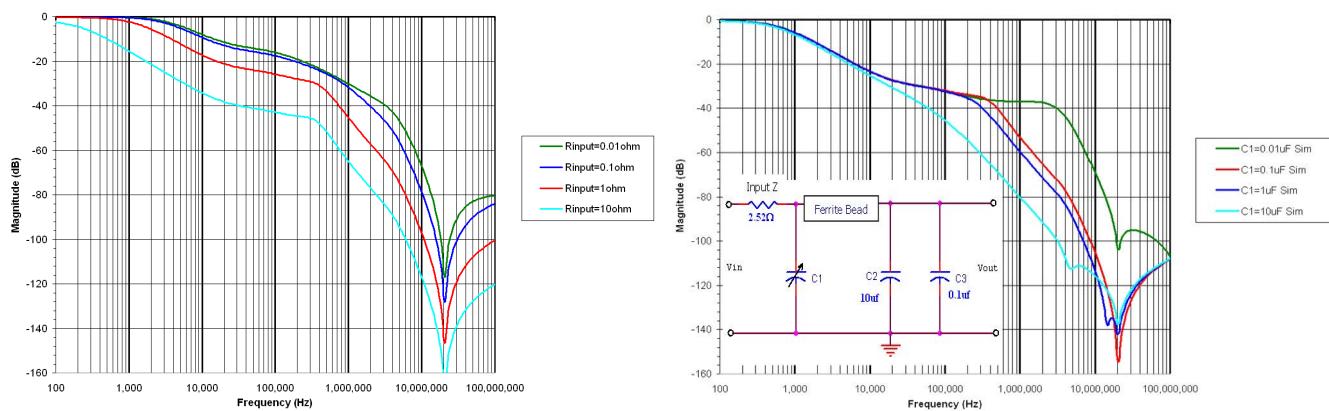

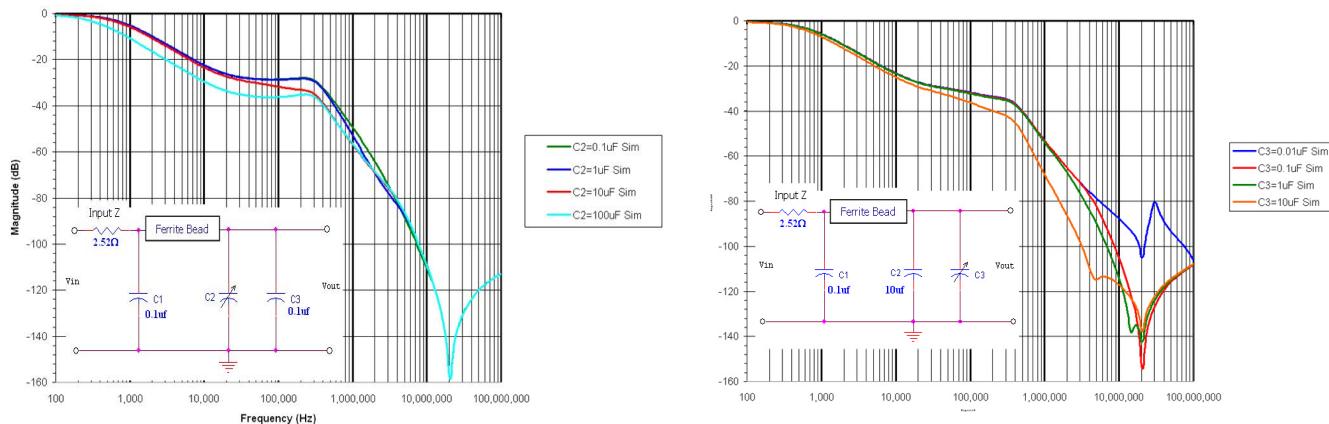

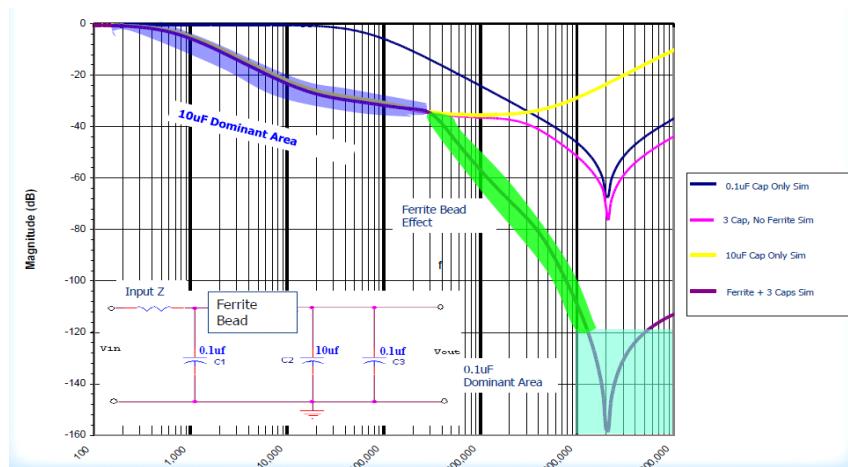

[Figure 7](#) and [Figure 8](#) show the role of each element in the power supply filter. These graphs show that designing power filtering for various purposes is possible. Examples are attenuating a specific frequency component or providing modest spread attenuation over a wide frequency range.

We recommend to place bypass capacitors as close to the device as possible. [Figure 6](#) illustrates the effect of increasing the parasitic inductance of the capacitor model (for a copper micro-strip it's about  $1nH/mm$  trace). The resonance frequency above which the capacitor starts acting like an inductor drops.

## 2.5 Ferrite Beads

To remove high frequency energy that may be present on the supply lines due to various sources, Ferrite beads are recommended in line with the filtering capacitors. These can be seen as high frequency resistors (attenuators) that can allow DC to pass while absorbing the RF energy, dissipating it in the form of heat.

**Figure 7. Ferrite Bead's Role along with Three Other Capacitors (Varying R and C1)**

**Figure 8. Ferrite Bead's Role with Three Other Capacitors (Varying C2 and C3)**

Figure 8 illustrates the importance of a ferrite bead the device power filtering. Ferrite Bead advantages include:

- High impedance values removes a broad range of RF energy.

- Closed magnetic circuit eliminating cross talk.

- Inherent shielding.

- Great current carrying capacity.

- Spurious circuit oscillations are reduced because of their resistive feature to RF energy.

- Great selection of frequency ranges and resistance values.

In order to choose the proper bead to use, the following are items that should be considered:

- Range of unwanted frequencies on the power supply.

- Source of EMI contamination.

- Amount of contamination.

- Size and real estate depending on application.

- Typically, their impedance is specified only at 100MHz, but the board designer should consider studying several graphs from the datasheet to properly select the right bead.

VersaClock 5/6 has multiple power pins; digital circuitry supply VDDD and analog PLL power supply VDDA. It is important to provide a degree of isolation so noise emanating from the digital supply will not pollute VDDA and prevent negative impact on PLL performance.

**Figure 9. Power Filter Impedance with Individually Varying Each Component**

Table 1. Recommended Ferrite Beads for VersaClock 5/6 Power Supply

| Manufacturer | Part Number      | Z @ 100MHz | Package Size | DC Res. | I (mA) |

|--------------|------------------|------------|--------------|---------|--------|

| Murata       | BLM18AG601SN1    | 600        | 0603         | 0.50    | 200    |

| Murata       | BLM18BD601SN1_PB | 600        | 0603         | 0.65    | 200    |

| Ceratech     | HB-1T1608-601    | 600        | 0603         | 0.50    | 200    |

| TDK          | MMZ1608R301A     | 300        | 0603         | 0.20    | 500    |

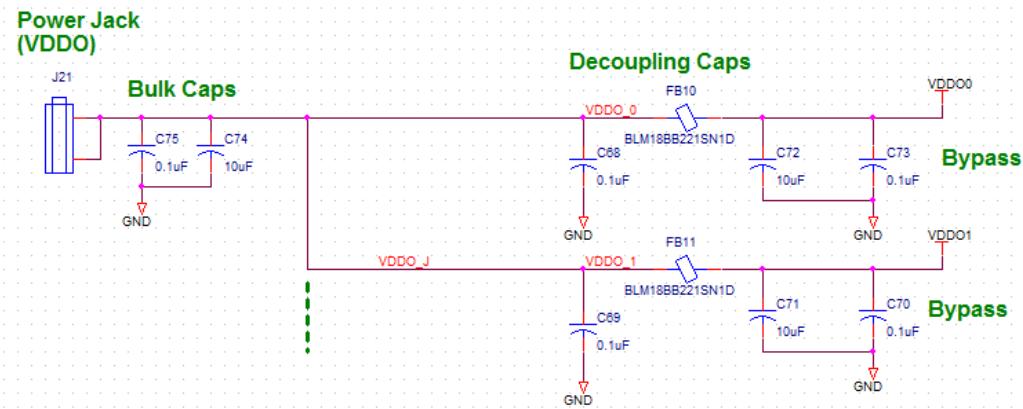

Figure 10 shows an example of deriving VDDO [0, 1...] from a single supply source.

Figure 10. Output Clk0 VDD (VDDO0)

## 2.6 Methodology to Use for Computing Bypass Values

In this section, a methodology to figure out the bypass capacitance to use is outlined. The method depends on multiple board/design specific parameters such as total number of gates (output buffers and drivers), wiring trace length the device, slew rates, load caps of the outputs, etc.

Assume that:

- VersaClock 5/6 shares VDD with other circuitry

- The number of switching gates is  $N = 30$  (output buffers and drivers)

- The average amount of load capacitance per driver is  $20\text{pF}$

- The average slew rate is  $3\text{ns}$

- Inductance,  $L$ , for the wiring of the power supply to the DUT is known to be  $100\text{nH}$

- Assume a power supply of  $3.3\text{V}$  and a noise margin to be  $V_n = 100\text{mV}$  which is the maximum tolerated noise level

Then the methodology outlined in [Methodology for Computing Bypass Values](#) shows that a  $4.7\mu\text{F}$  bypass cap is needed for power supply operating frequency above  $241\text{kHz}$ . With an ESL (Equivalent Series Inductance) of  $1\text{nH}$ , this capacitor is effective up to  $24.1\text{MHz}$ .

### 3. VersaClock Inputs

VersaClock devices have two input reference options. Refer to the part specific datasheet on how to multiplex between  $X_{IN}/X_{OUT}$  crystal input or an external differential input.

#### 3.1 $X_{IN}/X_{OUT}$

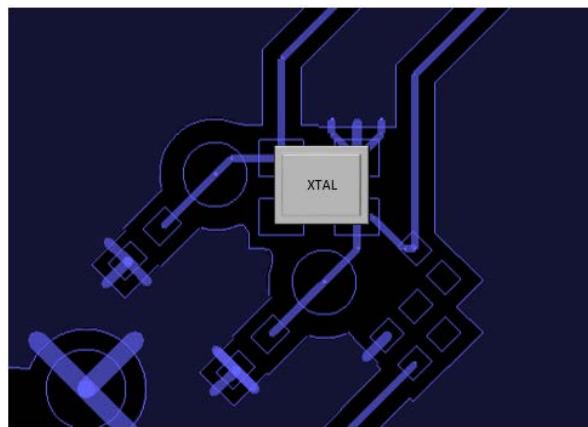

$X_{IN}/X_{OUT}$  are the crystal oscillator circuit interface pins. The following recommendations should be kept in mind when using a crystal:

1. Place the crystal as close as possible to the crystal pins on the IC to minimize crystal trace length, in order to minimize parasitic capacitance and interference. For the same reason, avoid using vias in the crystal traces.

2. When using capacitors on each crystal pin to set the load capacitance value, connect the ground side of the two capacitors close together and close to the ground connection of the IC ground. The reason is to minimize noise coupling from the ground plane.

3. With on-chip capacitors, for making a load capacitance of 8pF or larger, it is preferred to use a crystal with that load capacitance to avoid using external capacitors.

4. Treat crystal component area as a keep out area for signal routing on other layers.

Figure 11. Example of a Crystal Footprint

5. Follow the directions for the load capacitance in the datasheet. A load capacitance mismatch results in a frequency offset (refer to the [VersaClock 5 Evaluation Board User Guide](#)). Also, higher load capacitance values mean lower oscillator gain so when adding external capacitors, be careful not to exceed the maximum load capacitance in the datasheet to assure enough oscillator gain margin. Refer to the [datasheet](#) and [VersaClock 5 – 5P49V59xx Family Programmer Board](#) for the proper way of setting the internal load capacitance values.

6. Route  $X_{IN}$  and  $X_{OUT}$  traces as non-coupled high impedance traces. Separate them by at least 3 times the trace width.

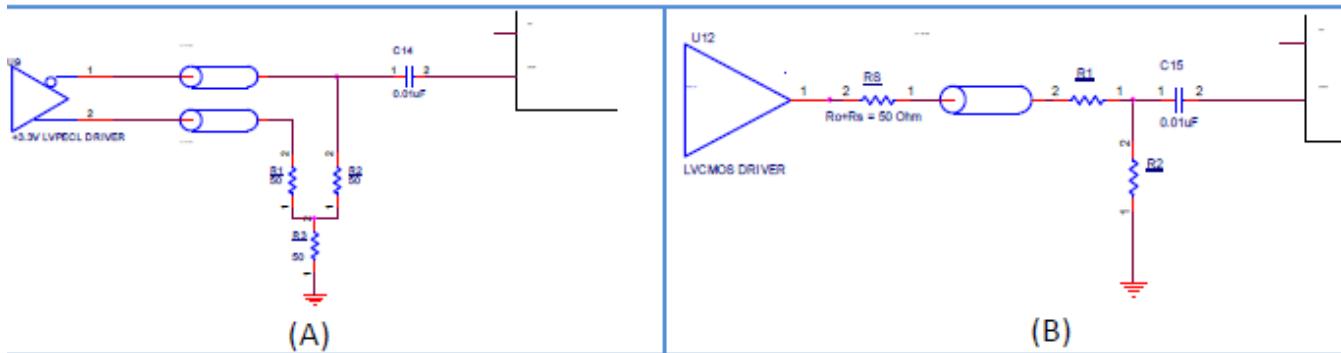

7.  $X_{IN}$  pin can be driven by a single ended LVC MOS signal or one AC-coupled end of a differential pair, provided that the amplitude remain between 500mV and 1.2V and a slew rate of at least 0.2V/ns. In this case, the internal load cap should be set to a minimum value.

Figure 12. Driving  $X_{IN}$  Pin (A) LVPECL input, (B) LVCMSO Driver

A separate input buffer for a differential input is also available and can be multiplexed with the crystal inputs externally and through I<sup>2</sup>C.

### 3.2 Recommended Crystal for VersaClock Devices

The following table summarizes the Renesas recommended crystal characteristics:

Table 2. Recommended Crystal for VersaClock Family

| Feature                                                           | Recommended Value                                   |

|-------------------------------------------------------------------|-----------------------------------------------------|

| Recommended Part                                                  | 603-25-150JA4I                                      |

| Frequency (MHz)                                                   | 25                                                  |

| Frequency Tolerance at 25°C                                       | ±20 PPM Max                                         |

| Frequency Stability, ref at 25°C Over Operating Temperature Range | ±20 PPM Max                                         |

| Operating Mode                                                    | Fundamental Mode                                    |

| Load Capacitance ( $C_L$ )                                        | 8 pF                                                |

| Equivalent Series Resistance (ESR)                                | 50 ohms or less                                     |

| Operating Temperature (°C)                                        | Commercial: 0 to +70°<br>Industrial: -40°C to +85°C |

## 4. Device Electrical and Thermal Pad

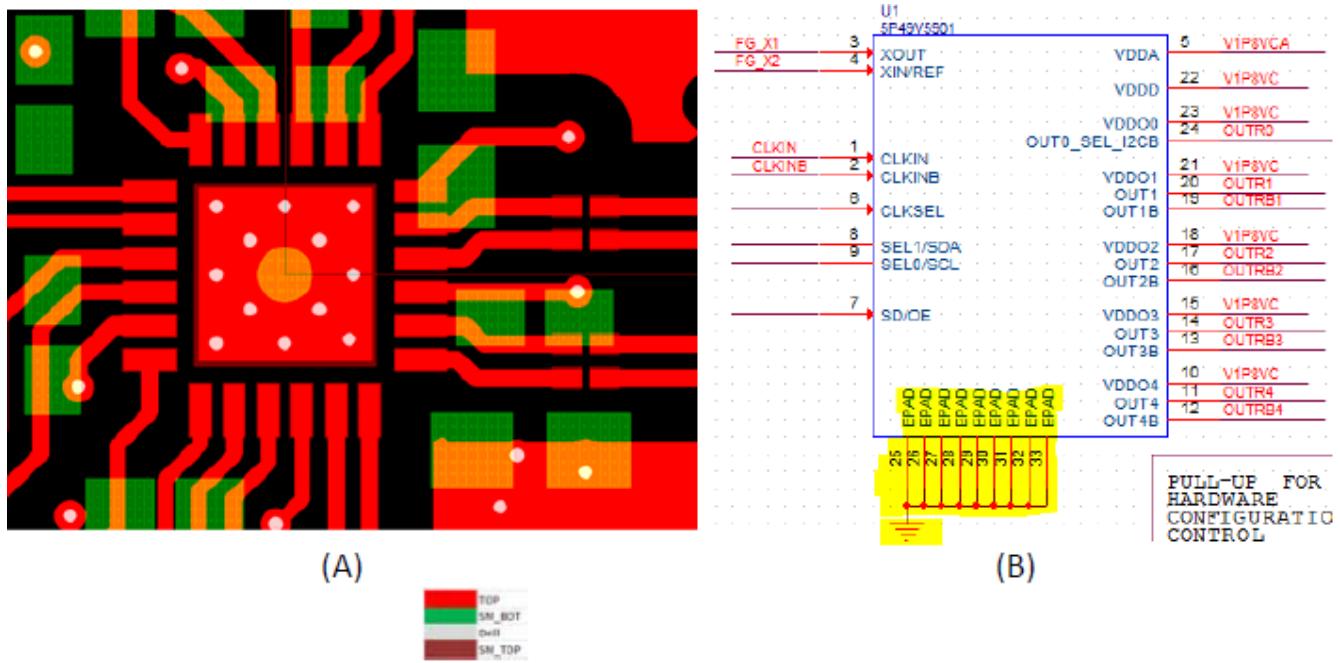

Renesas VersaClock 5/6 Frequency generators and buffers come with an EPAD, a ground island directly beneath the device on the same layer the DUT is soldered on, which is to be connected to GND. Short traces are then drawn from there to the ground pin as shown in [Figure 13](#). These traces should be made as wide as possible.

The ground island is then stapled with equally spaced vias to the inner ground plane as illustrated below in [Figure 13](#). For more details on Epads and ground vias, refer to Ref. [12] and Ref. [13].

Figure 13. (A) QFN package with a GND Island (B) Part Symbol

VDD traces are filtered with ferrite beads prior to the connection to the power plane. The ferrite bead and its associated bulk and decoupling capacitors should be as close to the power source as possible. Bypass capacitors should be placed as close to the device power pins as possible.

## 5. Recommendations for Optimal Return Path (cutouts in GND planes)

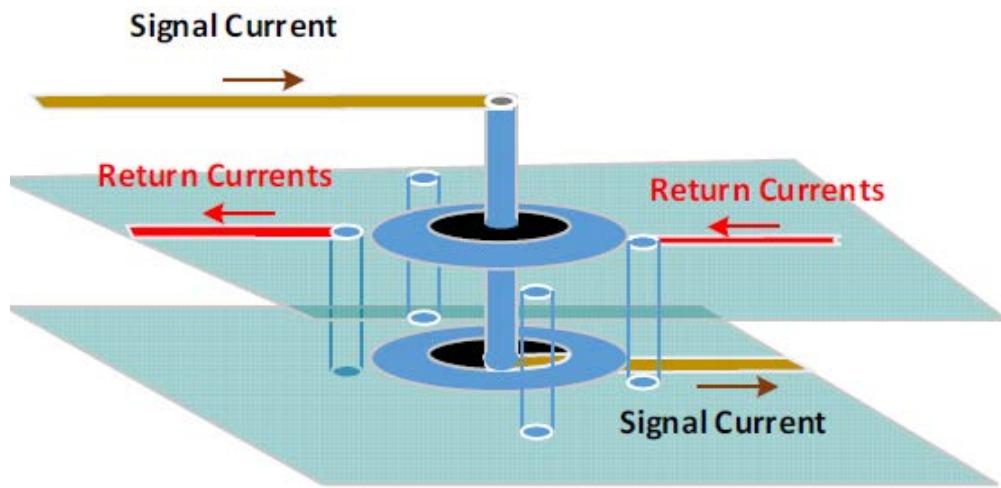

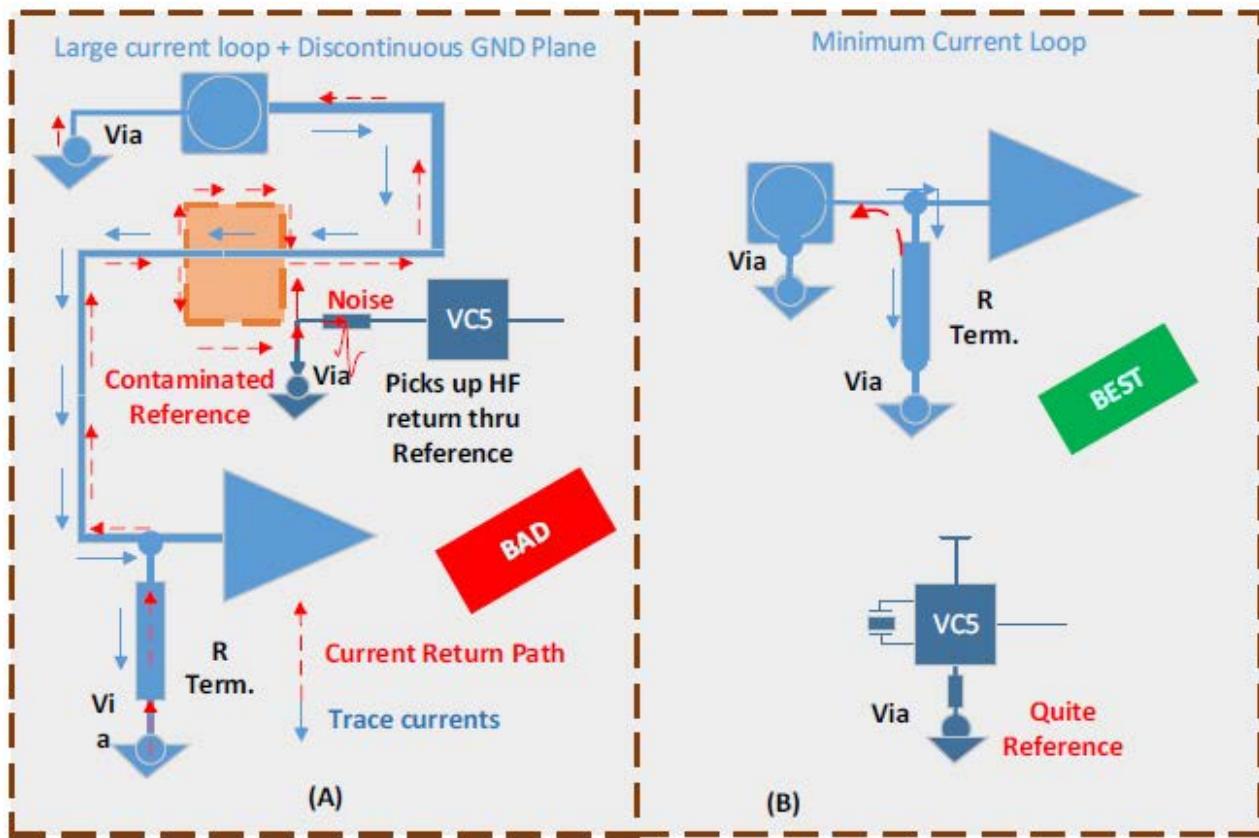

Considering their density, current return paths can be thought of as fictitious wires directly beneath or above the actual signal traces.

Figure 14. Signal Return Path

Therefore, any obstruction to traces such as cutouts in GND plane (see [Figure 15 A](#)) should be avoided.

Figure 15. Illustration of Problems that can occur with Current Return Paths

These problems are deemed “ghost” issues, and are often brought up during new board designs when the performance differs from that seen in simulations. Figure 15 illustrates this point.

## 6. Output Signal Integrity

VersaClock device output drivers can be configured for various output termination configuration; Traditional HCSL (see [AN-879](#)), LVDS, LVPECL and single-ended or differential LVCMS outputs. Details of these terminations are well documented and written about in other literature and are beyond the scope of this application note.

In order to avoid signal reflections, signal transmission lines must be terminated with an impedance equal to the transmission line characteristic impedance. A trace is considered as a transmission line whenever the one-way propagation delay of the PCB track is equal to or greater than one-half the applied signal rise/fall time (whichever edge is faster). For example, a 2-inch micro-strip line, over a dielectric of  $\epsilon_r = 4.0$ , would have a delay of about 270ps. Using the above rule, termination would be appropriate whenever the signal fastest transition time is less than 500ps.

A 2ns/ft. propagation delay (average between Microstrip and Striplines) is another conservative rule.

Stubs can be unterminated as long as their length ( $L_{in}$ ) does not exceed the signal rise time ( $tr(ns)$ ) or when the prop delay has to be less than 1/3 of the 10% to 90% rise time. If multiple stubs are used to distribute the clock signal, all stub lengths must be made equal to avoid skew issues.

### 6.1 Trace Length Considerations

A question often arises: what is the maximum trace length can I drive with my clock? This question is not complete unless the type of the clock, frequency, trace geometry, type of PCB, the dielectric used (and so on) are specified. Figure 16 [Mantaro website] shows a calculation of  $r$ ,  $L$  and  $C$  per inch for a micro-strip (see Ref. 13).

Calculator Group: [PCB Microstrip Structures](#) ▾ [Show All](#)

### Microstrip Impedance Calculator

Note: valid for (w/h) from 0.1 to 3.0

Dimensional units:  mm  mils

|                                                                                                                                                         |         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| w (trace width) =                                                                                                                                       | 8       |

| t (trace thickness) =                                                                                                                                   | 1.4     |

| h (dielectric thickness) =                                                                                                                              | 4.7     |

| er (relative dielectric constant) =                                                                                                                     | 4.2     |

|  <span style="border: 1px solid black; padding: 2px;">Calculate</span> |         |

| Zo (Single Ended Impedance, Ohms) =                                                                                                                     | 47.085  |

| Propagation Delay, Tpd (ps/inch) =                                                                                                                      | 138.20  |

| Inductance, L (nH/in) =                                                                                                                                 | 6.507   |

| Capacitance, C (pF/in) =                                                                                                                                | 2.93521 |

| DC Resistance, Rdc (mOhm/in) =                                                                                                                          | 60.461  |

Note: 1oz = 1.4mils = 0.03556mm

$$Z_0 = \frac{87}{\sqrt{\epsilon_r + 1.41}} \ln \left( \frac{5.98h}{(0.8w+t)} \right) \quad T_{pd} = 3.333 \sqrt{0.475 \cdot \epsilon_r + 0.67} \left( \frac{ns}{meter} \right)$$

Figure 16. Transmission Line Distributed Parameter Calculation for a Microstrip

It is tempting to ignore L and C for the ranges of frequencies of VersaClock 5/6 and compute the resistive part of the trace impedance ( $r = \rho L/A$ ) and to figure out what length of that trace results in a 30% drop in voltage. This reasoning is incorrect because we would be using a lumped parameter formula to perform computations in the distributed model case.

The question is what is the maximum length of a trace before termination becomes crucial. As a rule of thumb, this distance is given by [Ref. 3]:

$$L_{\max} = 9 \times t_r \text{ (Microstrip topology, in cm)}$$

$$L_{\max} = 7 \times t_r \text{ (Stripline topology, in cm)}$$

Where  $t_r$  is the rise time in nano-seconds. If possible, layout the traces below these max limits. Reflections would be significantly reduced.

For example, for a 300ps rise time, the maximum unterminated Microstrip trace is:  $9 \times (0.3) = 2.7$  cm and  $7 \times (0.3) = 2.1$  cm for a Stripline trace.

For traces above this max value, the clock can drive very long traces, in comparison to the usual PCB dimensions, as long as proper recommended terminations are taken care of. Loss through PCB dielectric starts becoming significant in the GHz range, which is unlikely for VersaClock devices.

In very high frequencies, among other factors, dielectric dissipation (Df) is one of the major factor contributing to RF loss of signal. These are usually not the case in the frequency range of VersaClock 5/6 outputs. Insertion loss as a function of frequency, for different dielectrics, is well documented in the literature. This is usually given in dB/inch and is typically less than 0.1dBc/inch for most dielectric constants and trace sizes. If we take this as a conservative limit, than in order to have 30% loss in the signal (3dB point), one would have to have a trace ( $3/0.05 = 60$  inches). The day you have to lay a board with a 60-inch trace, you can worry about the trace length for the distributed case, otherwise, correct termination is the only thing of concern.

## 6.2 Guidelines for Routing VersaClock's Single-ended Traces

- Keep clock traces as straight as possible. Use arc-shaped traces instead of right-angle bends.

- Do not use multiple signal layers for clock signals

- Do not use vias in clock transmission lines. Vias can cause impedance mismatch resulting in reflection.

- Place a ground plane next to the outer layer to minimize noise. If you use an inner layer to route the clock trace, sandwich the layer between ground planes.

- Properly terminate clock signals to minimize reflections

## 6.3 Routing VersaClock's Differential Traces

VersaClock 5/6 clocks are highly configurable. They feature 4 totally independent Fractional Output Dividers (FODs). The output drivers can be configured for different types of termination including HCSL, LVDS, LVPECL or as two in phase or out of phase LVCMOS outputs. This section includes some guidelines to keep in mind when routing differential traces.

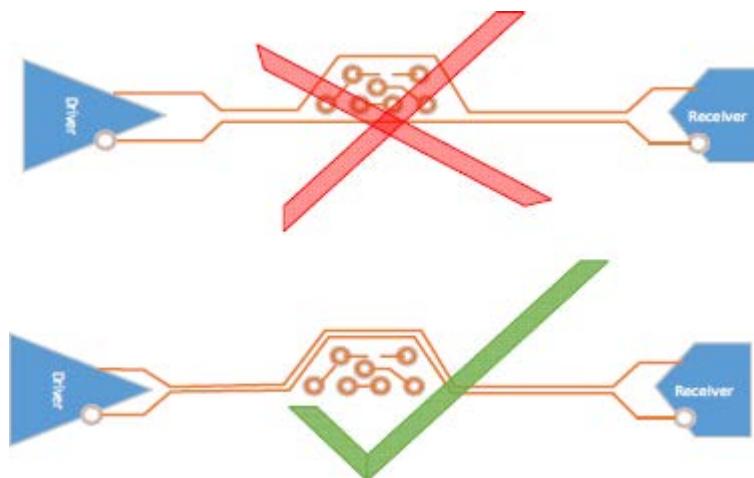

Differential traces should always be routed together (side-by-side). This keeps any noise injection into the signal a true common-mode noise which gets rejected by the receiver. If the differential traces part away from each other at any point, noise can only get into one line and not the other, hindering its rejection at the receiver. In addition, in order for the signals not to arrive at the receiver at different times which cause serious performance degradation, the lengths of both differential traces must be kept identical.

Figure 17 illustrates a scenario where it's attempting to deflect one trace from another to go around an obstacle.

Figure 17. Avoid Separating Differential Line Traces

## 6.4 EMI

Any conductor under certain conditions can become a great antenna. PCB traces are no exception to this aspect and can act as small antennas to the clock signals on the traces. This happens when the length of an unshielded conductor (trace) approaches and exceeds one tenth of the signal wavelength. Always take steps to minimize antenna effect and, hence, reduce Electro-Magnetic Emission (EMI).

EMI also happens when the signal's power is concentrated on a single frequency. VersaClock allows spreading the signal energy over a certain frequency interval by virtue of Spread Spectrum available that can be turned on or off for each output independently.

## 7. Conclusion

It is not uncommon to design a board, simulate it, and have the highest confidence that the board will work when it comes back from production. When it does, bringing it up and debugging it gives its designer grief with some of the weirdest behaviors. Often times, these issues are caused by layout aspects, many of which are covered in this document and others in subsequent ones. These included traces, vias, power planes, ground loops, return paths, cross talk, radiation etc. Understanding these layout guidelines and some of the layout element behaviors at different frequencies will help designing more sound PCB boards, achieve greater performance, and decrease risks of multiple revisions.

## 8. Revision History

| Revision | Date         | Description                                                                                                                                                                                                                                                    |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.02     | Sep 4, 2025  | <ul style="list-style-type: none"><li>Added a section heading called <a href="#">Ferrite Beads</a>; however, no new content was added</li><li>Changed VersaClock 5 references to VersaClock 5/6</li></ul>                                                      |

| 1.01     | Oct 5, 2022  | <ul style="list-style-type: none"><li>Rebranded to Renesas and updated to the latest template.</li><li>Removed former application note number AN-909 from document title.</li><li>Updated text throughout to encompass the entire VersaClock family.</li></ul> |

| -        | Oct 27, 2015 | Initial release.                                                                                                                                                                                                                                               |

## A. Methodology for Computing Bypass Values

In this section, a methodology to figure out the bypass capacitance is outlined. The method depends on multiple board/design specific parameters such as total number of gates (output drivers and buffers), wiring trace length the device, slew rates, load caps of the outputs, etc.

Assume that a VersaClock device shares VDD with other circuitry, assume the number of switching gates to be (N=30 output buffers, and drivers) and the amount (average) load capacitance (e.g. 20pF) each drives and the average slew rate it does it with (e.g. 3ns).

Then, a good estimate of the inductance for the wiring of the power supply to the DUT is known (say L is 100nH). Assume a power supply of 3.3V and a noise margin to be  $V_n = 100$  mV which is the maximum tolerated noise level.

1. We compute the current ( $di$ ) as  $\frac{V_{CC}}{\left(\frac{dt}{nC}\right)} = \frac{nCV_{CC}}{dt}$ , (dt is switching time). With the numbers chosen here,  $di = 0.66$  A

2. Compute the max impedance:  $Z_{max} = \frac{V_n}{di} = 0.1515\Omega$

3. Compute the frequency above which power supply wiring needs bypass caps:

$$F_{psw} = \frac{Z_{max}}{2\pi L} = \frac{0.1515}{2 \cdot 3.14 \cdot 100e^{-9}} = 241kHz$$

4. If the operating power supply frequency is higher than 241 KHz, then a bypass capacitor is needed. That is calculated as follows:

5.  $C_{bypass} = \frac{1}{2\pi F_{psw}} = 4.356\mu F$ . Since this is not common cap,  $4.7\mu F$  would do.

6. If the capacitor used has an ESL (Equivalent series inductance) of 1 nH, the max frequency up to which this value will work effectively can be computed as follows:

$$F_{bypass} = \frac{1}{2 \cdot \pi \cdot ESL} = 24.1MHz$$

## B. Board Layout

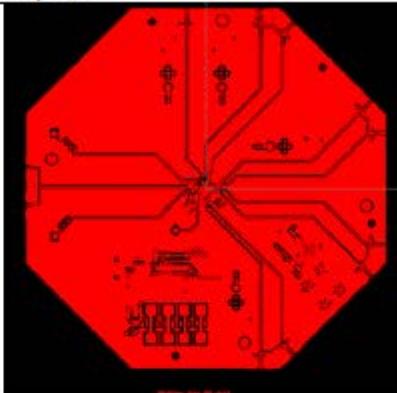

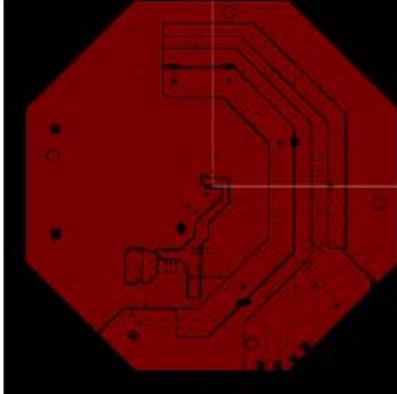

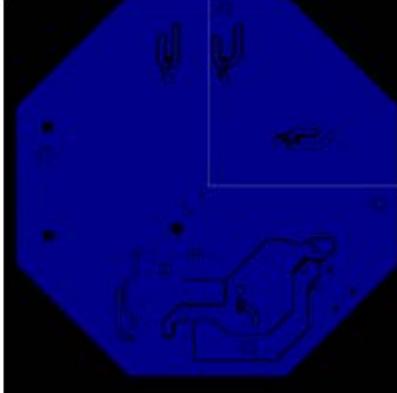

| Typical Layer Stack up                                                                                                                                                                                                                                                     | Layer    | Layout                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------|

| 1* ASSY.art<br>2+ L1_TOP.art<br>3+ L2_GND.art<br>4+ L3_POWER.art<br>5+ L4_POWER.art<br>6+ L5_GND.art<br>7+ L6_BOTTOM.art<br>8~ PM_BOTTOM.art<br>9~ PM_TOP.art<br>10~ SILKSCREEN_BOTTOM.art<br>11~ SILKSCREEN_TOP.art<br>12~ SM_BOTTOM.art<br>13~ SM_TOP.art<br>14~ FAB.art | L1_TOP   |    |

|                                                                                                                                                                                                                                                                            | L4_POWER |   |

|                                                                                                                                                                                                                                                                            | L5_GND   |  |

|                                                                                                                                                                                                                                                                            | L3_POWER |  |

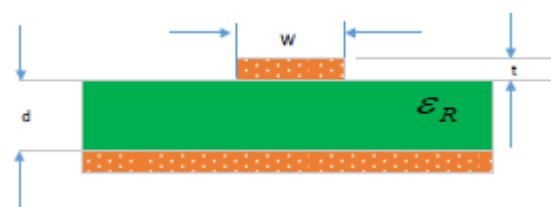

## C. Impedance of Common Transmission Lines

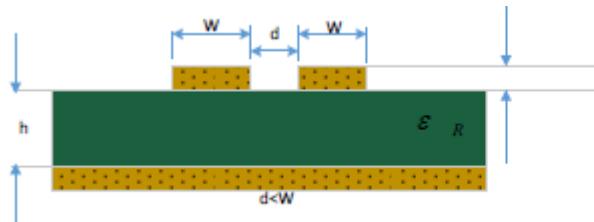

### C.1 Microstrip

This is the most commonly used layout. Microstrip lines have less propagation delay than their stripline counterparts with the same dielectric material. Because Microstrips are on the outer layer (unshielded), they can radiate more RF to the external world. Their advantage is that only two PCB layers are required.

$$Z_{diff}(\Omega) \approx 2 \cdot Z_o \left( 1 - 0.48 e^{-\frac{0.96d}{h}} \right) \quad (3)$$

$$Z_o(\Omega) \approx \frac{87}{\sqrt{\epsilon_r + 1.41}} \ln \left( \frac{6h}{0.8W + t} \right) \quad (4)$$

Figure 18. Microstrip Differential Line Impedance

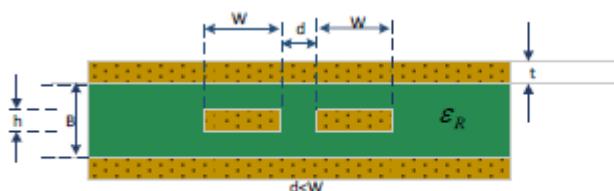

### C.2 Stripline

Striplines are traces sandwiched or buried between two other layers. While these lines have better noise immunity/radiation, they exhibit more propagation delays. The drawback of this kind of traces is that they require at least 3 layers and may be harder to control  $Z_o$ .

$$Z_{diff}(\Omega) \approx 2 \cdot Z_o \left( 1 - 0.347 e^{-\frac{2.9d}{B}} \right) \quad (5)$$

$$Z_o(\Omega) \approx \frac{60}{\sqrt{\epsilon_r}} \ln \left( \frac{1.9h}{(0.8W + t)} \right) \quad (6)$$

Figure 19. Differential Line Impedance in a Stripline

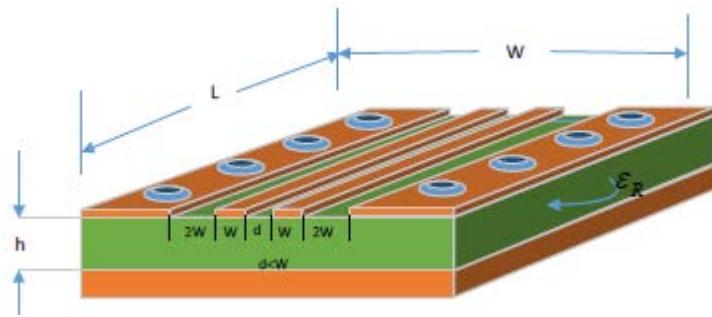

In cases where ground pour is on the same layer as the differential pair, it is important to keep a distance at least twice the trace width from the ground. This minimizes the capacitance of the plane that can dramatically alter the characteristic impedance of the trace. To minimize current loop area, it is recommended to place vias on the ground copper pour to connect to the bottom ground layer as shown in [Figure 20](#). The distance between vias should not be more than 0.1".

Figure 20. Running Differential Traces Surrounded with GND Layer

### C.3 Trace Inductance and Capacitance

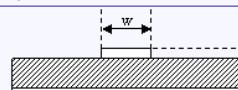

Figure 21 shows a trace running on the top layer of the PCB. A trace has both, inductance and capacitance, in addition to resistance, that are given by the following:

$$L(nH) = 2 \cdot \pi \cdot \ln\left(\frac{5.98h}{0.8W + t}\right) \quad (7)$$

$$C(pF) = 0.264 \cdot x \cdot \left( \frac{\varepsilon_R + 1.41}{\ln\left(\frac{5.98h}{0.8W + t}\right)} \right) \quad (8)$$

$$Z_0(\Omega) = 31.6 \frac{L(nH)}{C(pF)}, \quad T_p(ps/cm) = 31.6 \sqrt{L(nH)C(pF)}$$

where X is the length of the trace, W: Width of the trace, t: thickness of the trace, d: thickness of the dielectric material and is its relative dielectric permittivity.

Figure 21. PCB Trace Running on the Top Side of the Board

**Example:** A 0.8mm (0.031") copper trace on 0.8mm (0.031") thick PCB (FR-4) would show approximately 4nH and 0.8pF per cm trace (10nH and 2.0pF per inch) (FR-4: ( $\varepsilon_R = 4.5$ )

## References

1. VersaClock 5 - 5P49V5901 Evaluation Board

2. VersaClock 5 - 5P49V59xx Family Programmer Board

3. Mark I. Montrose, "Printed Circuit Board Design Techniques for EMC Compliance", IEEE Press Editorial Board, 1996

4. John Coonrod, Advanced Circuit Materials Division, "Circuit Materials and High-Frequency Losses of PCBs", The PCB Magazine, Feb. 2012

5. Mark I. Montrose, "EMC AND THE PRINTED CIRCUIT BOARD", Design, Theory and Layout Made Simple, IEEE Press, 1998

6. Standard IPC-2141A, "Controlled Impedance Circuit Boards and High Speed Logic Design," 2004, Institute for Interconnection and Packaging Electronic Circuits, 3000 Lakeside Drive, 309 S, Bannockburn,

7. Howard Johnson and Martin Graham, "High-Speed Digital Design - A Handbook for Black Magic", Prentice-Hall, 1993

8. AN-879, Low-Power HCSL vs. Traditional HCSL

9. Simon Ramo, John R. Whinnery, Theodore Van Duzer, "Fields and Waves in Communication Electronics", John Wiley & Sons, Inc., 3rd Edition

10. Cypress Semiconductors, Perfect Timing II, "Design Guide for Clock Generation and Distribution"

11. Wheeler, Introduction to Microwaves. New Jersey: Prentice Hall

12. Amkor AppNote0301

13. Mantaro website: [http://www.mantaro.com/resources/impedance\\_calculator.htm](http://www.mantaro.com/resources/impedance_calculator.htm)

## Notice

1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

(Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

(Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Disclaimer Rev.5.0-1)

## Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

## Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

[www.renesas.com/contact/](http://www.renesas.com/contact/)

## Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.