致尊敬的顾客

---

## 关于产品目录等资料中的旧公司名称

---

NEC电子公司与株式会社瑞萨科技于2010年4月1日进行业务整合（合并），整合后的新公司暨“瑞萨电子公司”继承两家公司的所有业务。因此，本资料中虽还保留有旧公司名称等标识，但是并不妨碍本资料的有效性，敬请谅解。

瑞萨电子公司网址：<http://www.renesas.com>

2010年4月1日

瑞萨电子公司

【发行】瑞萨电子公司 (<http://www.renesas.com>)

【业务咨询】<http://www.renesas.com/inquiry>

## Notice

1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

(Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

(Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## 概要

7548 群为采用了 740 族内核的 8 位单片机。

内置 8 位定时器、16 位定时器、串行接口、A/D 转换器、上电复位电路及低电压检测电路。另外，具备功能设定 ROM。

## 特点

|                                                 |                                  |

|-------------------------------------------------|----------------------------------|

| • 基本机器指令 .....                                  | 71                               |

| • 指令执行时间 .....                                  | 0.25μs<br>(最短指令、振荡频率 8MHz、倍速模式时) |

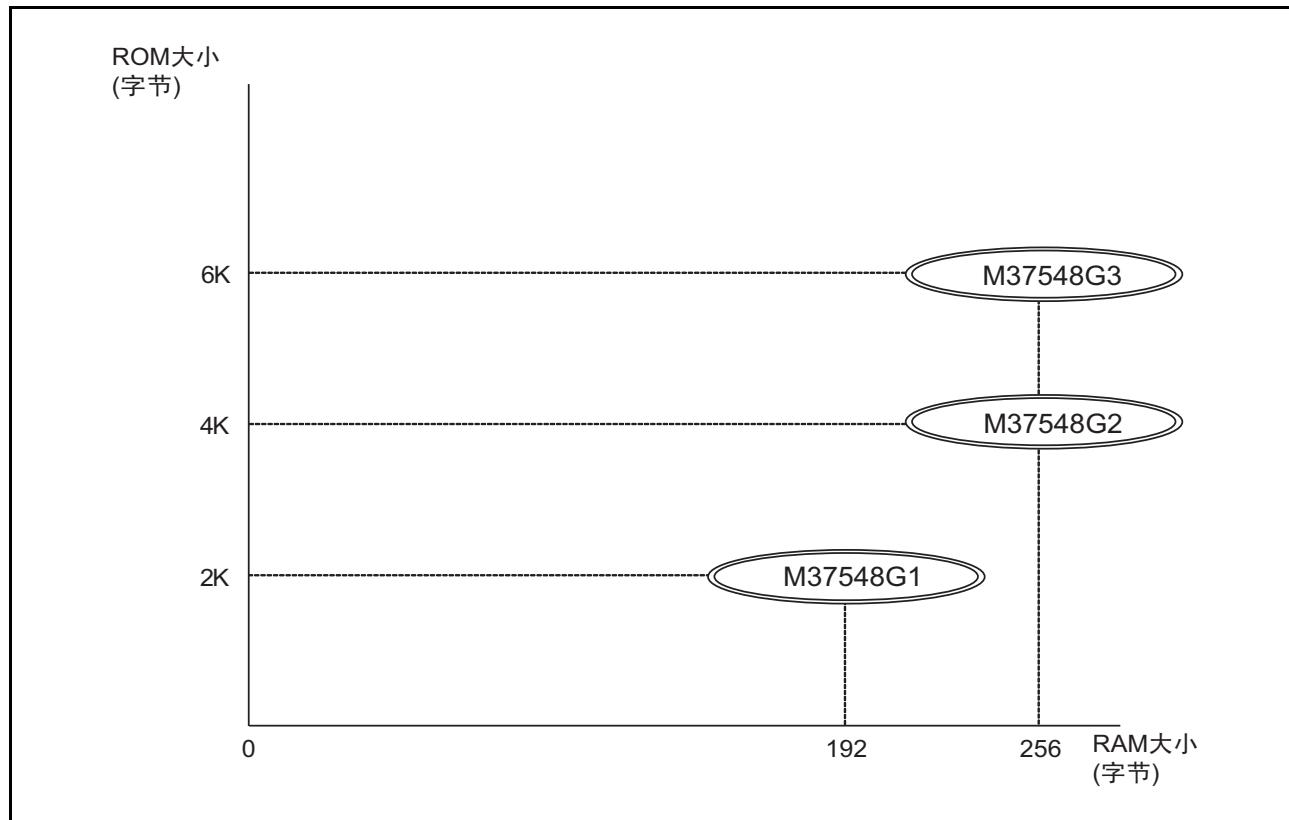

| • 存储器容量 ROM .....                               | 2K、4K、6K 字节                      |

| RAM .....                                       | 192/256 字节                       |

| • 可编程输入/输出端口 .....                              | 输入/输出端口 × 15 个<br>输出专用端口 × 1 个   |

| • 键唤醒输入 .....                                   | 6 个                              |

| • LED 驱动端口 .....                                | 8 个                              |

| • 中断 .....                                      | 12 个源、12 个向量                     |

| • 定时器 .....                                     | 8 位 × 2<br>16 位 × 1              |

| • 输出比较 .....                                    | 3 个通道                            |

| • 输入捕捉 .....                                    | 1 个通道                            |

| • 串行接口 .....                                    | 8 位 × 1<br>(时钟异步或时钟同步)           |

| • A/D 转换器 .....                                 | 10 位分辨率 × 6 个通道                  |

| • 时钟产生电路 .....                                  | 内置<br>(可外接陶瓷谐振器或晶体谐振器、32kHz 晶振)  |

| • 高速内部振荡器 .....                                 | 典型值：4MHz                         |

| • 低速内部振荡器 .....                                 | 典型值：250kHz                       |

| • 看门狗定时器 .....                                  | 16 位 × 1                         |

| • 上电复位电路 .....                                  | 内置                               |

| • 低电压检测电路 .....                                 | 内置                               |

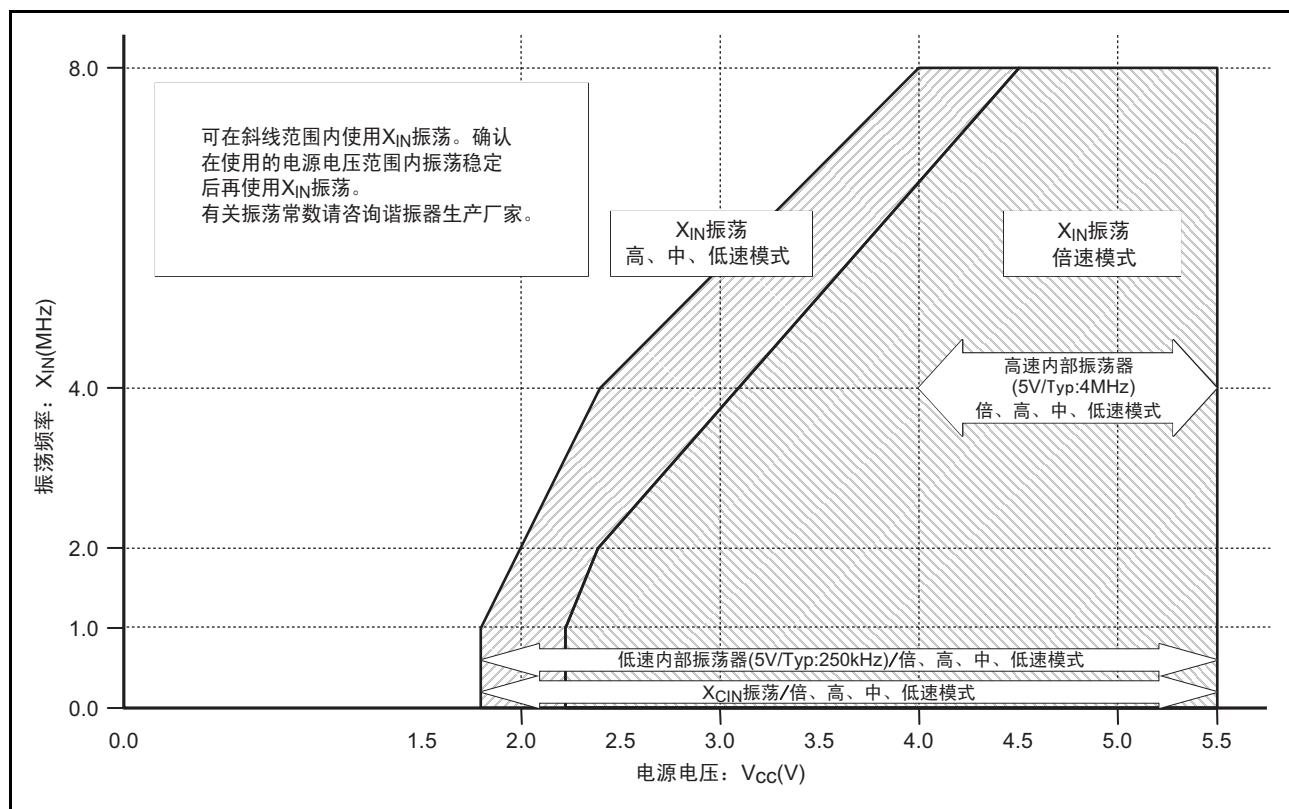

| • 电源电压 X <sub>IN</sub> 振荡频率 (在陶瓷振荡、倍速模式时) ..... |                                  |

| 8MHz 时 .....                                    | 4.5 ~ 5.5V                       |

| 2MHz 时 .....                                    | 2.4 ~ 5.5V                       |

| 1MHz 时 .....                                    | 2.2 ~ 5.5V                       |

| • 电源电压 X <sub>IN</sub> 振荡频率 (在陶瓷振荡、高速模式时) ..... |                                  |

| 8MHz 时 .....                                    | 4.0 ~ 5.5V                       |

| 4MHz 时 .....                                    | 2.4 ~ 5.5V                       |

| 1MHz 时 .....                                    | 1.8 ~ 5.5V                       |

高速内部振荡器振荡频率

4MHz 时 ..... 4.0 ~ 5.5V

低速内部振荡器振荡频率

250kHz (V<sub>CC</sub>=5V 时典型值) 时 ..... 1.8 ~ 5.5V

- 功耗 ..... 30mW

- 工作环境温度 ..... -20 ~ 85°C

## 应用

OA 设备、FA 设备、家电、民用设备等。

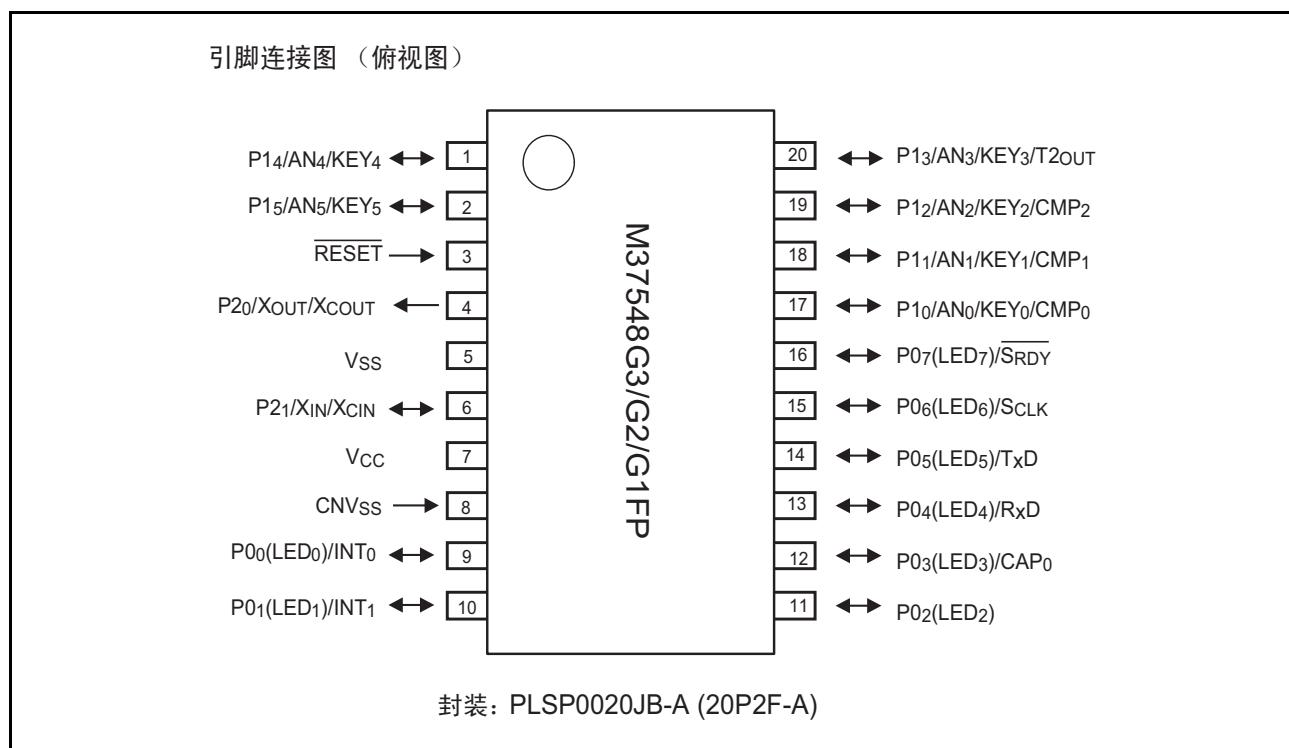

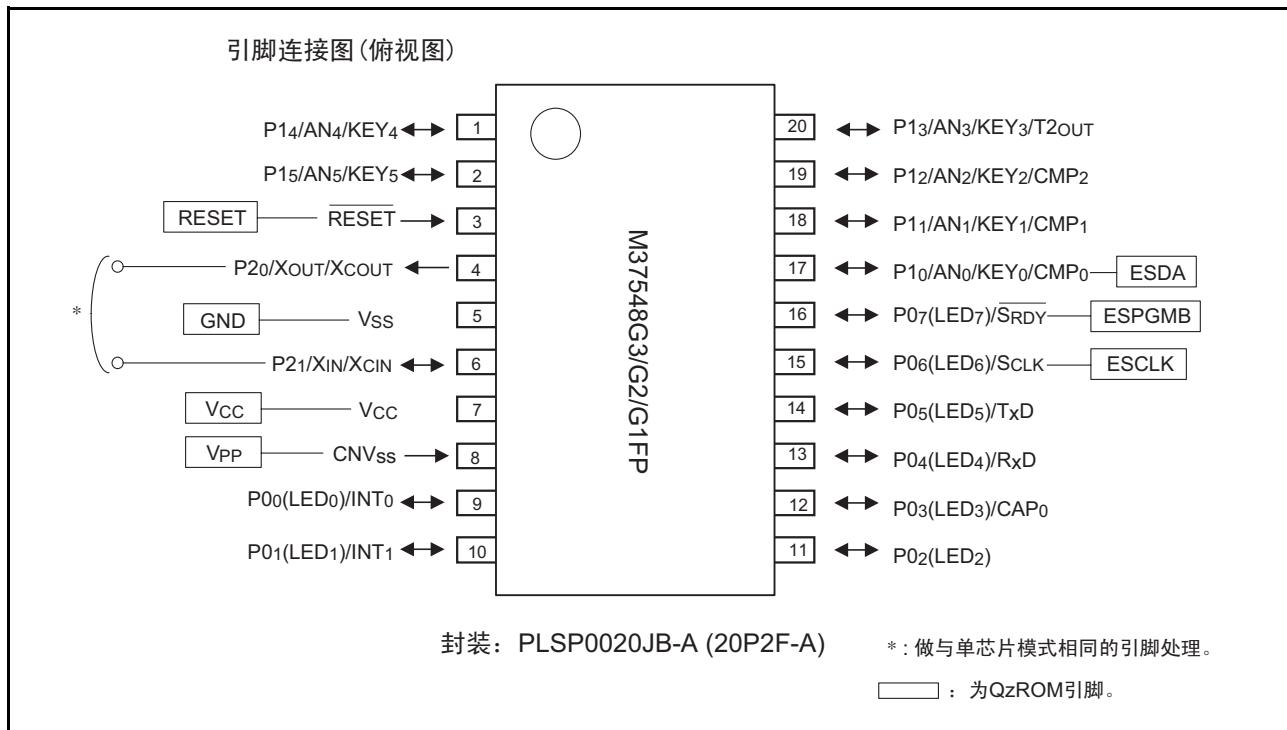

图 1 引脚连接图 (PLSP0020JB-A 封装类型)

引脚连接图 (俯视图)

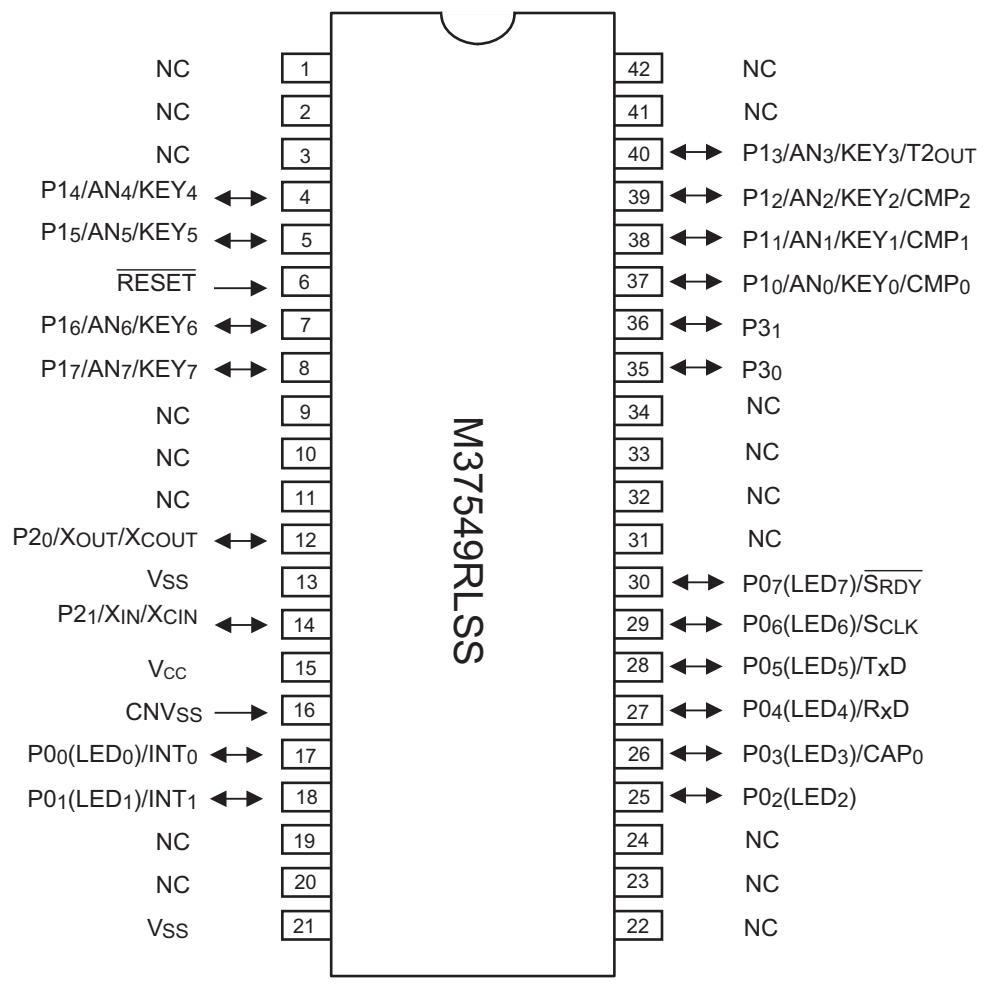

图 2 引脚连接图 (42S1M 封装类型)

## 性能概要

表 1 性能概要 (1)

| 项 目           |                                   | 性 能                                                                                   |               |

|---------------|-----------------------------------|---------------------------------------------------------------------------------------|---------------|

| 基本指令数         |                                   | 71                                                                                    |               |

| 指令执行时间        |                                   | 0.25μs (最短指令振荡频率 8MHz: 倍速模式)                                                          |               |

| 振荡频率          |                                   | 8MHz (最大)                                                                             |               |

| 存储器容量         | ROM                               | M37548G1                                                                              | 2K 字节 ×8 位    |

|               |                                   | M37548G2                                                                              | 4K 字节 ×8 位    |

|               |                                   | M37548G3                                                                              | 6K 字节 ×8 位    |

|               | RAM                               | M37548G1                                                                              | 192 字节 ×8 位   |

|               |                                   | M37548G2                                                                              | 256 字节 ×8 位   |

|               |                                   | M37548G3                                                                              | 256 字节 ×8 位   |

| 输入 / 输出端口     | P0 <sub>0</sub> ~ P0 <sub>7</sub> | 输入 / 输出                                                                               | 8 位、 LED 驱动端口 |

|               | P1 <sub>0</sub> ~ P1 <sub>5</sub> | 输入 / 输出                                                                               | 6 位           |

|               | P2 <sub>0</sub>                   | 输出                                                                                    | 1 位           |

|               | P2 <sub>1</sub>                   | 输入 / 输出                                                                               | 1 位           |

| 中断            | 中断源                               | 12 个源、 12 个向量                                                                         |               |

| 定时器           |                                   | 8 位 ×2、 16 位 ×1                                                                       |               |

| 输出比较          |                                   | 3 个通道                                                                                 |               |

| 输入捕捉          |                                   | 1 个通道                                                                                 |               |

| 串行接口          |                                   | 8 位 ×1 (时钟异步或时钟同步)                                                                    |               |

| A/D 转换器       |                                   | 10 位分辨率 ×6 个通道                                                                        |               |

| 看门狗定时器        |                                   | 16 位 ×1                                                                               |               |

| 上电复位电路        |                                   | 内置                                                                                    |               |

| 低电压检测电路       |                                   | 内置                                                                                    |               |

| 时钟产生电路        |                                   | 内置<br>(可外接陶瓷谐振器或晶体谐振器、 32kHz 晶振)<br>(内置高速 / 低速内部振荡器)                                  |               |

| 功能设定<br>ROM 区 | 功能设定 ROM                          | 配置在地址 FFD816 ~ FFDA16<br>可选择振荡方式<br>可选择低电压检测电路的有效 / 无效<br>可选择看门狗定时器的允许 / 禁止、 STP 指令功能 |               |

|               | ROM 代码保护                          | 配置在地址 FFDB16<br>设定 “00” 来禁止对串行编程器内部 QzROM 的读取和写入。                                     |               |

表 1 性能概要 (2)

| 项 目                  |                             | 性 能        |             |

|----------------------|-----------------------------|------------|-------------|

| 电源电压<br>(陶瓷振荡时)      | 倍速模式                        | 8MHz 运行时   | 4.5V ~ 5.5V |

|                      |                             | 2MHz 运行时   | 2.4 ~ 5.5V  |

|                      |                             | 1MHz 运行时   | 2.2 ~ 5.5V  |

|                      | 高速模式                        | 8MHz 运行时   | 4.0 ~ 5.5V  |

|                      |                             | 4MHz 运行时   | 2.4 ~ 5.5V  |

|                      |                             | 1MHz 运行时   | 1.8 ~ 5.5V  |

| 电源电压<br>(高速内部振荡器振荡时) | 倍速模式                        | 4MHz 运行时   | 4.0 ~ 5.5V  |

| 电源电压<br>(低速内部振荡器振荡时) | 倍速模式                        | 250kHz 运行时 | 1.8 ~ 5.5V  |

| 功耗                   | 30mW                        |            |             |

| 工作环境温度               | -20 ~ 85°C                  |            |             |

| 元件结构                 | CMOS 硅栅                     |            |             |

| 封装                   | 20 引脚塑封 SSOP (PLSP0020JB-A) |            |             |

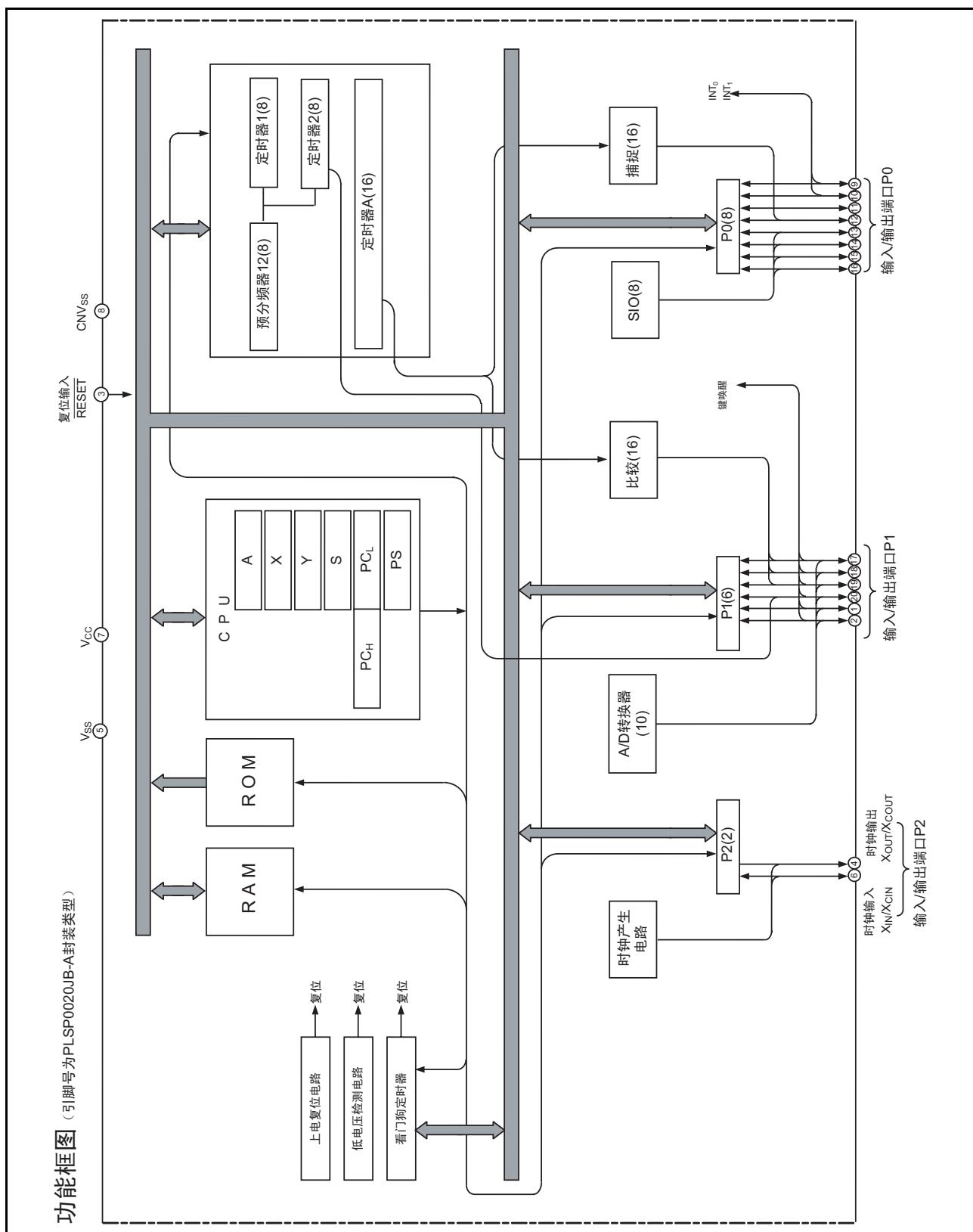

图 3 功能框图 (PLSP0020JB-A 封装类型)

## 引脚功能说明

表 2 引脚功能说明

| 引脚名                                                                | 名称           | 功能                                                                                                                    | 端口以外的功能                              |                                      |                                                                                                                                 |

|--------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                                                                    |              |                                                                                                                       |                                      |                                      |                                                                                                                                 |

| VCC、VSS                                                            | 电源输入         | 给 VCC 外加 1.8 ~ 5.5V、给 VSS 外加 0V。                                                                                      |                                      |                                      |                                                                                                                                 |

| CNVSS                                                              | CNVSS        | 控制芯片运行模式的引脚，与 VSS 连接。                                                                                                 |                                      |                                      |                                                                                                                                 |

| RESET                                                              | 复位输入         | 低电平有效的复位输入引脚。                                                                                                         |                                      |                                      |                                                                                                                                 |

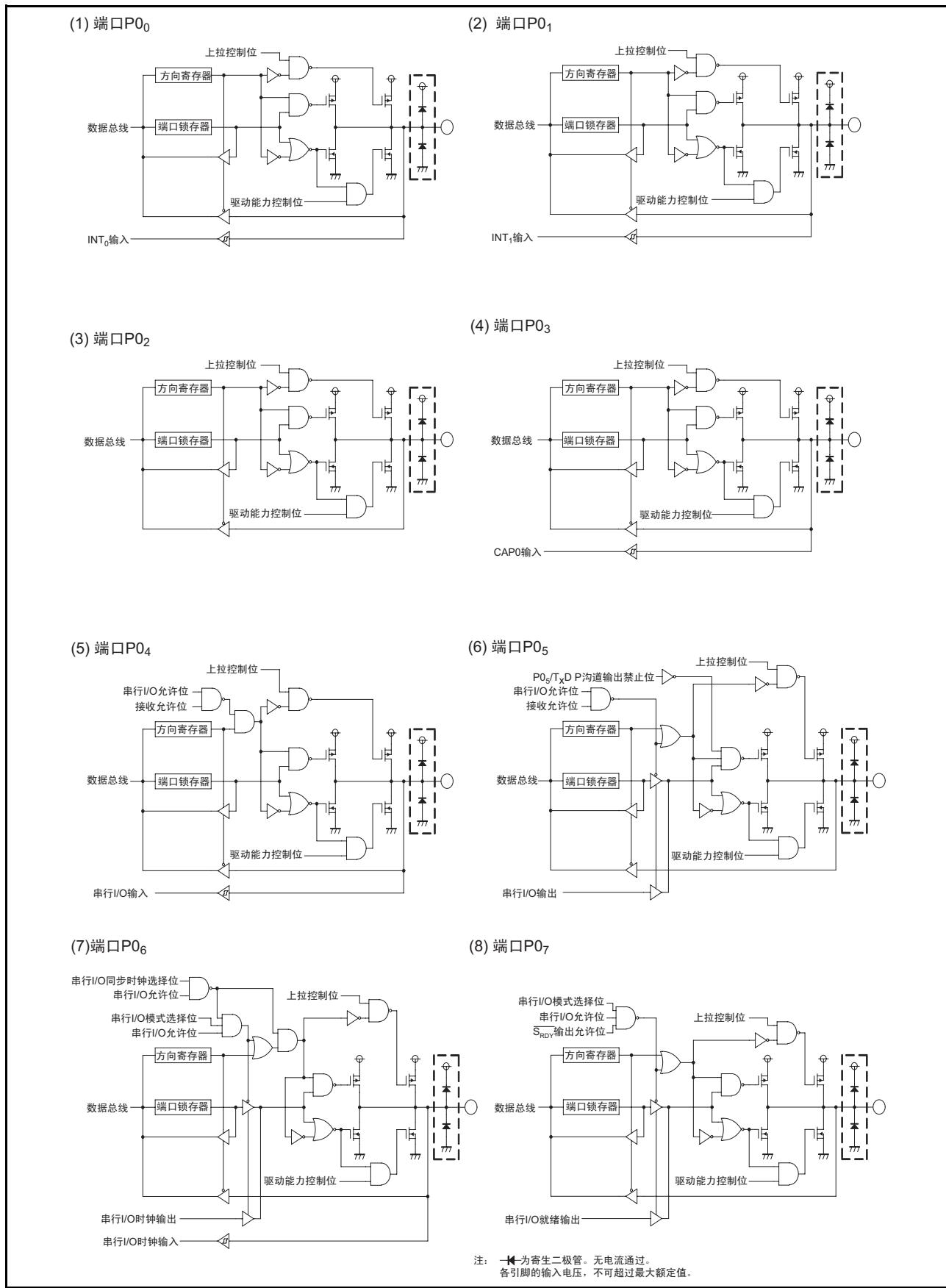

| P00(LED0)/INT0<br>P01(LED1)/INT1                                   | 输入 / 输出端口 P0 | 为 8 位输入 / 输出端口。可通过程序以位单位进行输入 / 输出的指定。输入电平为 CMOS 输入电平，输出方式为 CMOS 三态。<br>可通过程序选择是否使用内部上拉电阻。<br>亦可通过程序作为 LED 驱动端口使用。     | 中断输入引脚<br><br>捕捉输入引脚<br><br>串行接口功能引脚 | A/D 转换器输入引脚<br><br>定时器 2 输出引脚        | 比较输出引脚<br><br>输入 (键唤醒中断输入)<br><br>引脚                                                                                            |

| P02(LED2)                                                          |              |                                                                                                                       |                                      |                                      |                                                                                                                                 |

| P03(LED3)/CAP0                                                     |              |                                                                                                                       |                                      |                                      |                                                                                                                                 |

| P04(LED4)/RXD<br>P05(LED5)/TXD<br>P06(LED6)/SCLK<br>P07(LED7)/SRDY |              |                                                                                                                       |                                      |                                      |                                                                                                                                 |

| P10/AN0/KEY0/CMP0<br>P11/AN1/KEY1/CMP1<br>P12/AN2/KEY2/CMP2        | 输入 / 输出端口 P1 | 为 6 位输入 / 输出端口。可通过程序以位单位进行输入 / 输出的指定。输入电平为 CMOS 输入电平，输出方式为 CMOS 三态。<br>可通过程序选择是否使用内部上拉电阻。                             | A/D 转换器输入引脚<br><br>定时器 2 输出引脚        | 比较输出引脚<br><br>输入 (键唤醒中断输入)<br><br>引脚 | A/D 转换器输入引脚<br><br>定时器 2 输出引脚                                                                                                   |

| P13/AN3/KEY3/T2OUT                                                 |              |                                                                                                                       |                                      |                                      |                                                                                                                                 |

| P14/AN4/KEY4<br>P15/AN5/KEY5                                       |              |                                                                                                                       |                                      |                                      |                                                                                                                                 |

| P20/XOUT/XCOUT<br>P21/XIN/XCIN (注)                                 | 输入 / 输出端口 P2 | 为 2 位输入 / 输出端口 (P20/XOUT/XCOUT 为输出专用)。可通过程序以位单位进行输入 / 输出的指定。输入电平为 CMOS 输入电平，输出方式为 CMOS 三态。<br>此引脚可通过功能设定 ROM 作为时钟用引脚。 |                                      |                                      | XIN-XOUT、XCIN-XCOUT 之间连接陶瓷谐振器、晶振器或 32kHz 晶体谐振器，可作为振荡引脚使用。另外，使用外部时钟输入时，从 P20/XOUT/XCOUT 引脚输入时钟。此时，P21/XIN/XCIN 引脚可作为输入 / 输出端口使用。 |

【注】由于 P20/XOUT/XCOUT 引脚、P21/XIN/XCIN 引脚内置振荡电路，作为输入 / 输出端口使用时，单片机的 VCC 电压低于工作下限电压时，连接振荡电路，有时从这些引脚输出不定值。

## 群展开

7548 群按下面的计划展开。

### 存储器种类

支持 QzROM 版、仿真器专用 MCU。

### 存储容量

|              |              |

|--------------|--------------|

| PROM 容量..... | 2K ~ 6K 字节   |

| RAM 容量.....  | 192 ~ 256 字节 |

### 封装

|                    |                            |

|--------------------|----------------------------|

| PLSP0020JB-A ..... | 0.65mm 间距 20 引脚<br>塑封 SSOP |

| 42S1M .....        | 42 引脚陶瓷封装<br>PIGGY BACK    |

图 4 ROM 及 RAM 展开计划

表 3 支持产品一览表

2007 年 9 月

| 产品型号           | ROM 容量 (字节)<br>( ) 内为用户<br>ROM 容量 | RAM 容量<br>(字节) | 封装           | 备注                |

|----------------|-----------------------------------|----------------|--------------|-------------------|

| M37548G3-XXXFP | 6144<br>(6014)                    | 256            | PLSP0020JB-A | QzROM 版 (已编程出货产品) |

| M37548G3FP     |                                   |                |              | QzROM 版 (空白产品)    |

| M37548G2-XXXFP | 4096<br>(3966)                    | 256            | PLSP0020JB-A | QzROM 版 (已编程出货产品) |

| M37548G2FP     |                                   |                |              | QzROM 版 (空白产品)    |

| M37548G1-XXXFP | 2048<br>(1918)                    | 192            | PLSP0020JB-A | QzROM 版 (已编程出货产品) |

| M37548G1FP     |                                   |                |              | QzROM 版 (空白产品)    |

| M37549RLSS     | —                                 | 256            | 42S1M        | 仿真器专用 MCU         |

【注】 ROM 容量中包含功能设定 ROM 区。

## 功能块运行说明

### 中央运算处理器（CPU）

7548 群具有和 740 族共同的 CPU。关于各指令的运行，请参考 740 族寻址方式与机器指令一览表或 740 族软件手册。

关于依存产品种类的指令如下：

1. 无FST、SLW指令。

2. 可使用MUL、DIV指令。

3. 可使用WIT指令。

4. 可使用STP指令。

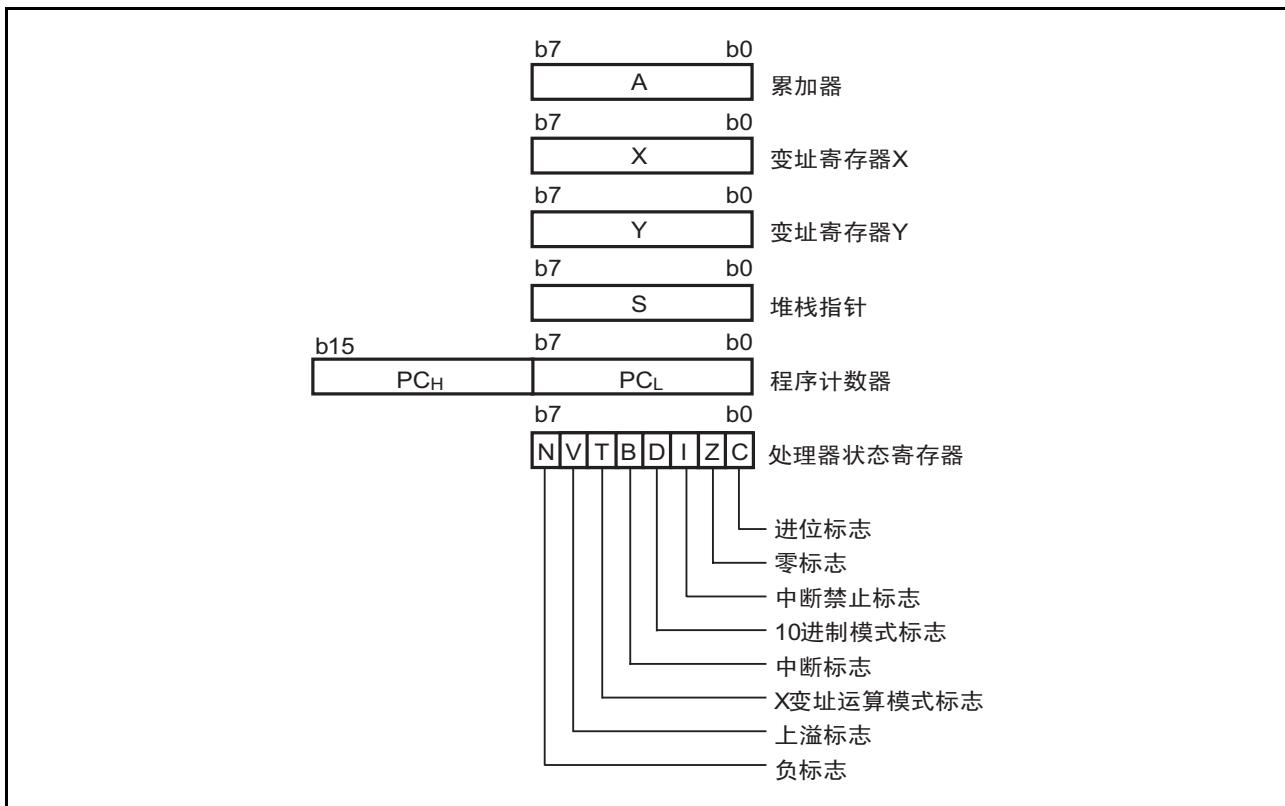

中央运算处理器（CPU）有 6 个寄存器。740 族 CPU 寄存器的结构如图 5 所示。

#### 【累加器】（A）

累加器为 8 位寄存器。以此寄存器为中心进行运算、传送等数据处理。

#### 【变址寄存器 X】（X）

变址寄存器 X 为 8 位寄存器。在变址寻址方式，使用此寄存器进行寻址。

#### 【变址寄存器 Y】（Y）

变址寄存器 Y 为 8 位寄存器。在变址寻址方式，使用此寄存器进行寻址。

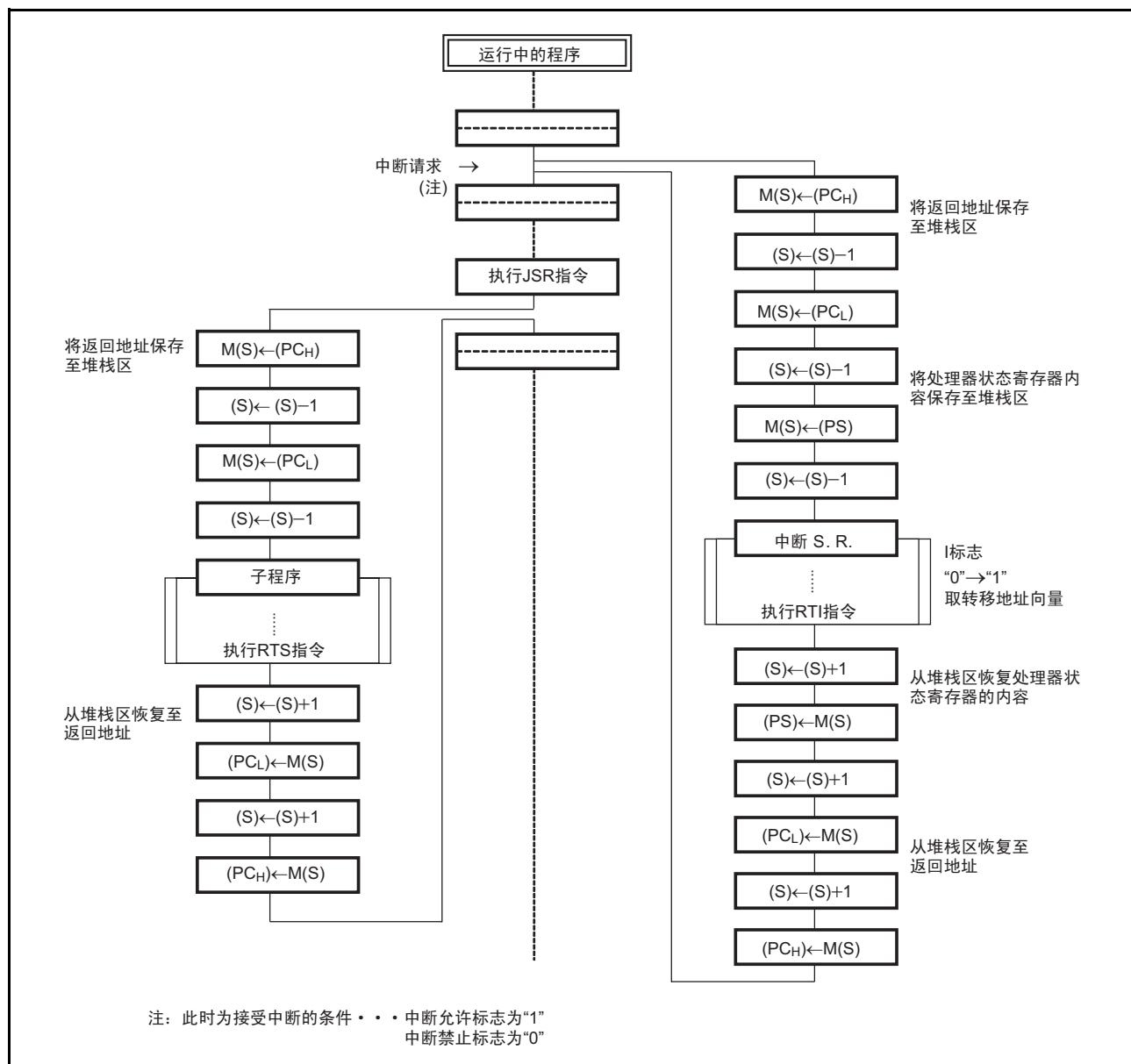

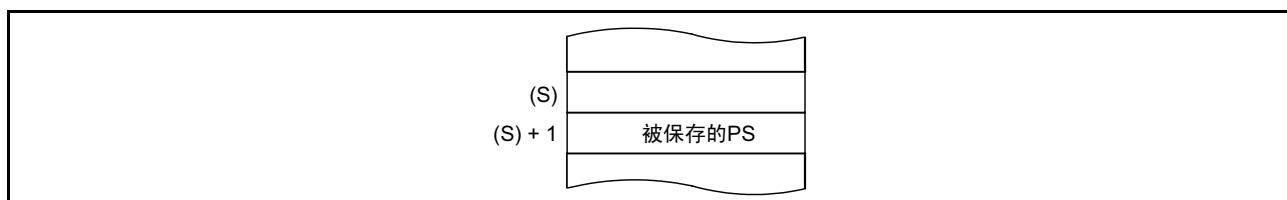

#### 【堆栈指针】（S）

堆栈指针为 8 位寄存器。调用子程序或中断时，此寄存器指向保存寄存器的存储位置（堆栈）的起始地址。

以此寄存器指定堆栈的低 8 位地址。高 8 位地址由栈页面选择位的内容决定，此位为“0”时，高 8 位为“ $00_{16}$ ”，此位为“1”时，高 8 位为“ $01_{16}$ ”。

堆栈的保存与恢复运行如图 6 所示。在此所示以外的必要寄存器请以程序保存（参照表 4）。

#### 【程序计数器】（PC）

程序计数器为由  $PC_H$  与  $PC_L$  构成的 16 位计数器。 $PC_H$  与  $PC_L$  均为 8 位结构。程序计数器指定下一个该执行的程序存储器的地址。

图 5 740 族 CPU 寄存器结构

图 6 堆栈的保存及恢复运行

表 4 累加器和处理器状态寄存器的保存指令及恢复指令

|          | 保存至堆栈的指令 | 从堆栈恢复的指令 |

|----------|----------|----------|

| 累加器      | PHA      | PLA      |

| 处理器状态寄存器 | PHP      | PLP      |

### 【处理器状态寄存器】(PS)

处理器状态寄存器为 8 位寄存器，由保持运算后的状态的 5 个标志和决定 MCU 运行的 3 个标志构成。

C、Z、V、N 标志可用于转移指令的检测，十进制模式时，Z、V、N 标志无效。

- **bit0: 进位标志 (C)**

保持来自运算处理后的算术逻辑运算器的进位或借位。执行移位指令或循环指令也改变此标志。

- **bit1: 零标志 (Z)**

运算处理或数据传送的结果为“0”时，此标志置位；结果不为“0”时，此标志清除。

- **bit2: 中断禁止标志 (I)**

用于禁止除 BRK 指令以外的所有中断的标志。此标志为“1”时，为中断禁止状态。

- **bit3: 十进制运算标志 (D)**

决定以二进制还是以十进制进行加减运算的标志。此标志为“1”时，将1字作为2位的十进制数进行运算。自动进行十进制调整，但只有ADC指令与SBC指令可进行十进制运算。

- **bit4: 中断标志 (B)**

用于识别是否以BRK指令中断的标志。以BRK指令中断时，标志内容自动置“1”，除此以外的中断时此位置“0”，然后保存至堆栈。

- **bit5: X 变址运算模式标志 (T)**

此标志为“0”时，在累加器与存储器之间进行运算；此标志为“1”时，可不通过累加器进行存储器与存储器之间的直接运算。

- **bit6: 上溢标志 (V)**

将1字作为带符号的二进制数进行加减运算时，使用此标志。加减运算结果超过+127或-128时，此标志置位。另外，执行BIT指令时，执行BIT指令的存储器的bit6存入此标志。

- **bit7: 负标志 (N)**

运算处理或数据传送的结果为负时，此标志置位。另外，执行BIT指令时，执行BIT指令的存储器的bit7存入此标志。

表 5 置位或清除处理器状态寄存器各标志的指令

|      | C 标志 | Z 标志 | I 标志 | D 标志 | B 标志 | T 标志 | V 标志 | N 标志 |

|------|------|------|------|------|------|------|------|------|

| 置位指令 | SEC  | —    | SEI  | SED  | —    | SET  | —    | —    |

| 清除指令 | CLC  | —    | CLI  | CLD  | —    | CLT  | CLV  | —    |

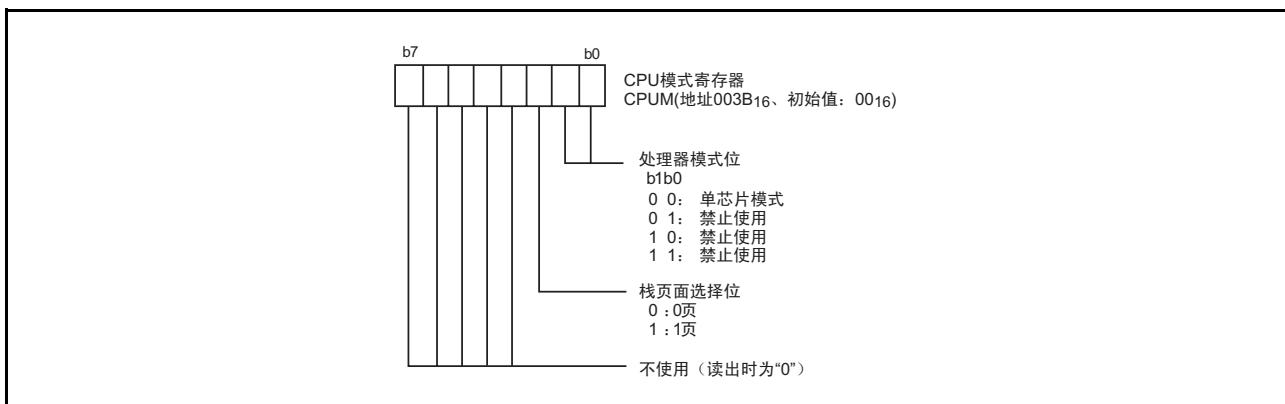

### 【CPU 模式寄存器】 CPUM

在 CPU 模式寄存器中，分配了栈页面选择位。此寄存器配置在地址  $003B_{16}$ 。

图 7 CPU 模式寄存器的结构

处理器模式位在复位解除后仅可写入 1 次。必须设定为 “ $00_2$ ”。写入后被锁定，因此再次写入无效（除仿真器专用 MCU）。

不锁定 bit2 的栈页面选择位。为防止单片机失控时向处理器模式位的误写入，在复位解除后的程序起始，进行 CPU 模式寄存器的写入。

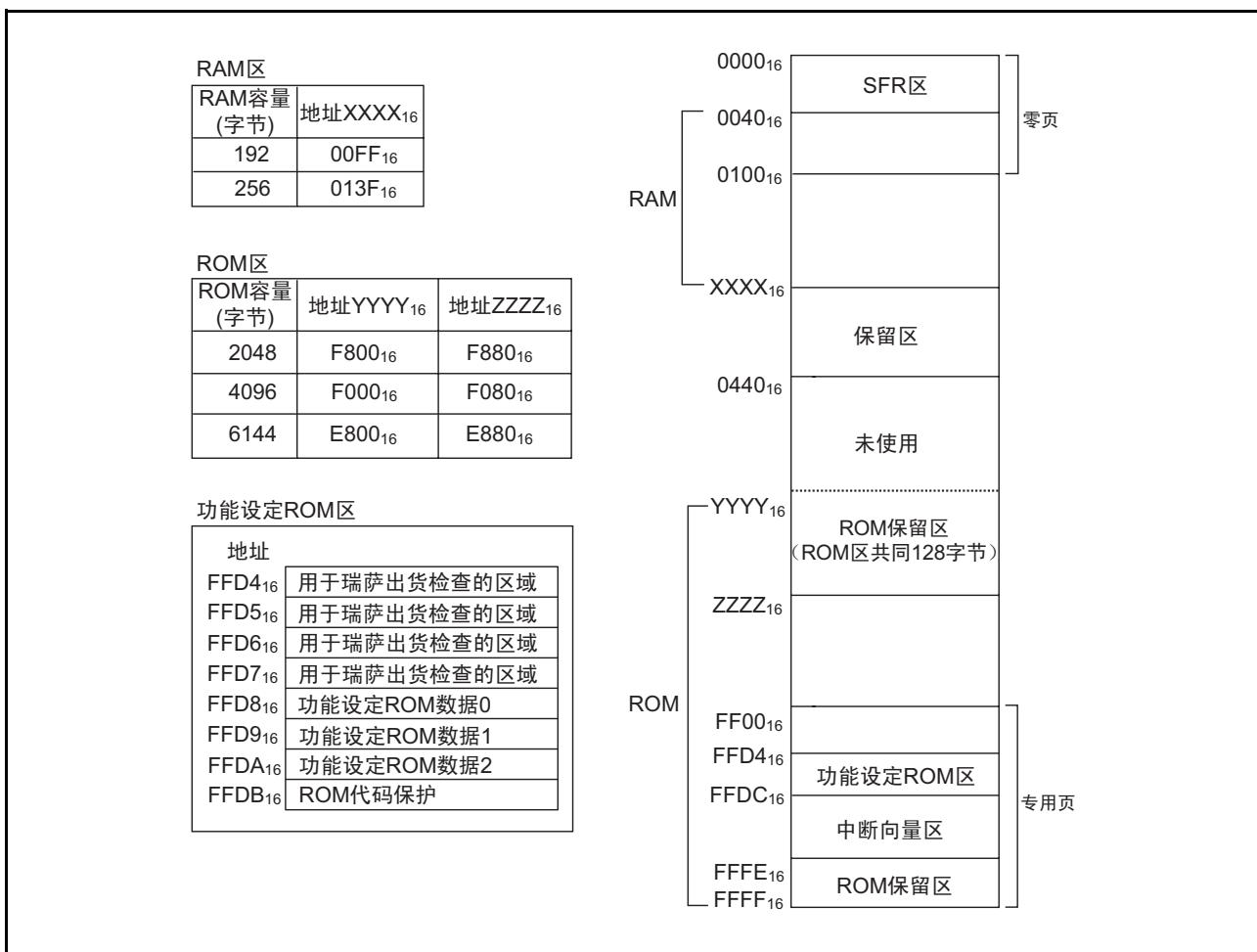

## 存储器

### SFR 区

此区域在零页内，配置有输入 / 输出端口、定时器等控制寄存器。

### RAM

用于数据保存、子程序调用以及中断时的堆栈等。

### ROM

起始的 128 字节与最后 2 字节是用于检查产品的保留区，除此以外为用户区。用户区包含功能设定 ROM 区。

### 中断向量区

复位及中断的向量地址保存区。

### 零页

使用零页寻址方式，能用 2 字存取的区域。

### 专用页

使用专用页寻址方式，能用 2 字存取的区域。

### 功能设定 ROM 区

#### 【用于瑞萨科出货检查的区域】

功能设定 ROM 区的配置图如图 8 所示。瑞萨科技产品出货检查时，在地址  $FFD4_{16} \sim FFD7_{16}$  的用于瑞萨出货检查的区域设定随机数据。请勿改写此区域的数据。另外，通过用户程序计算校验和时，不要包括此区域。

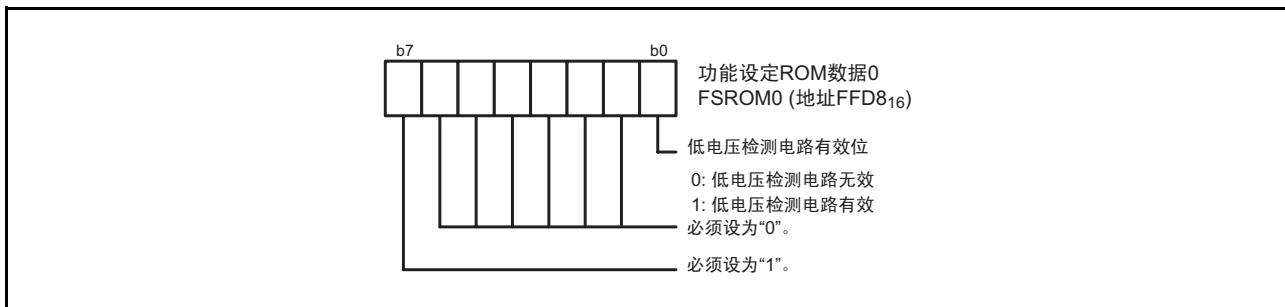

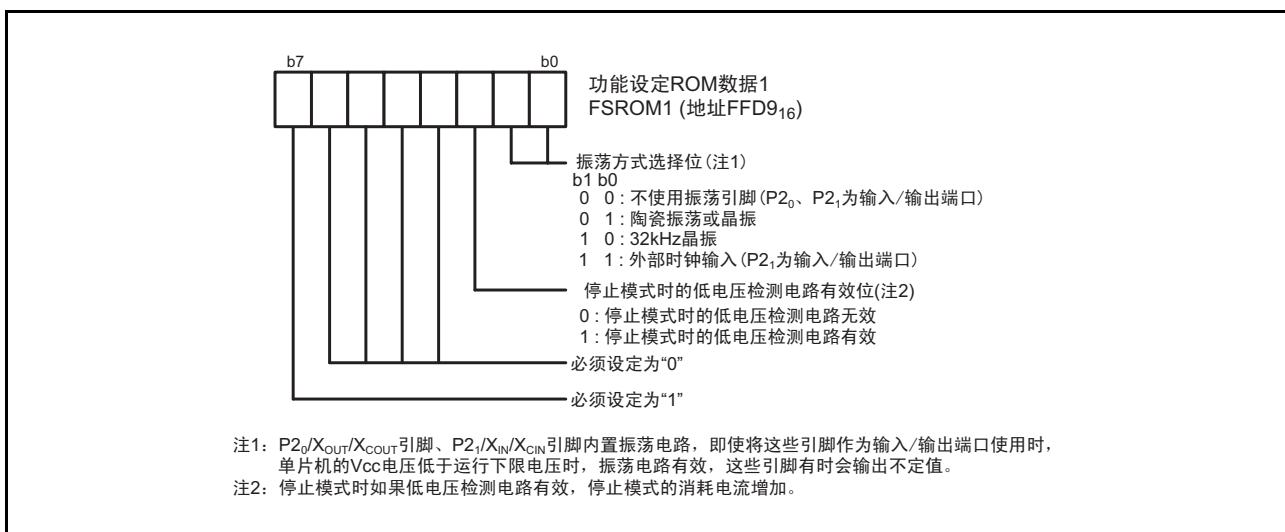

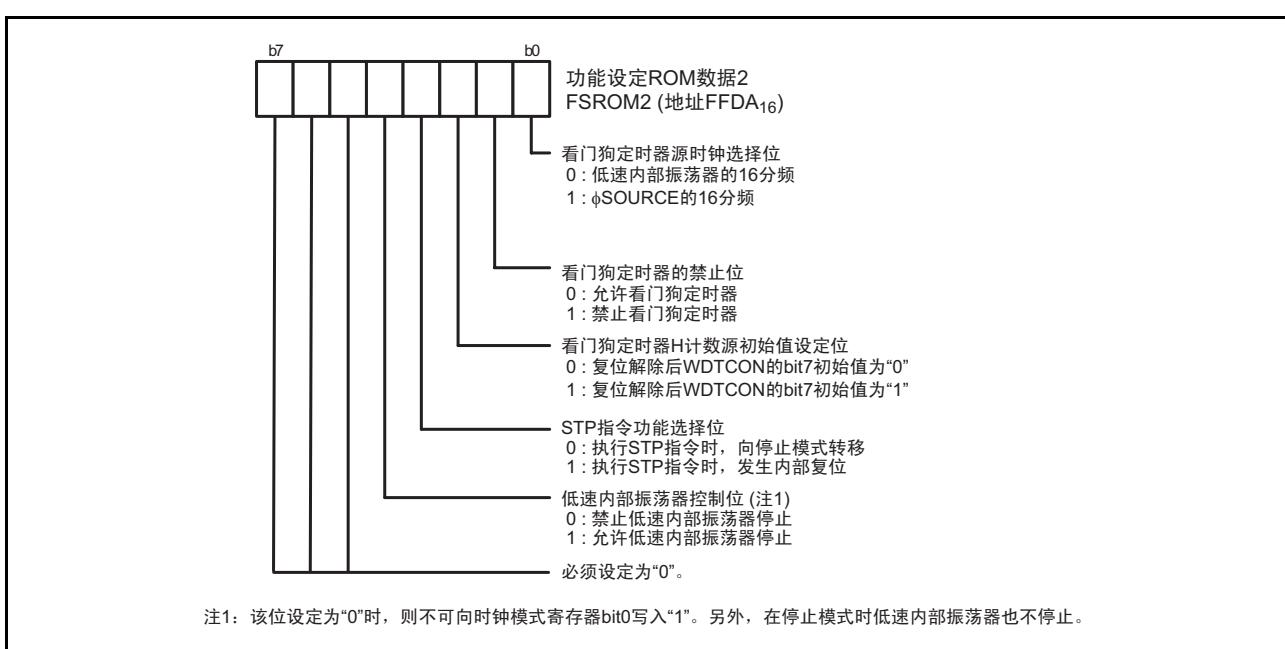

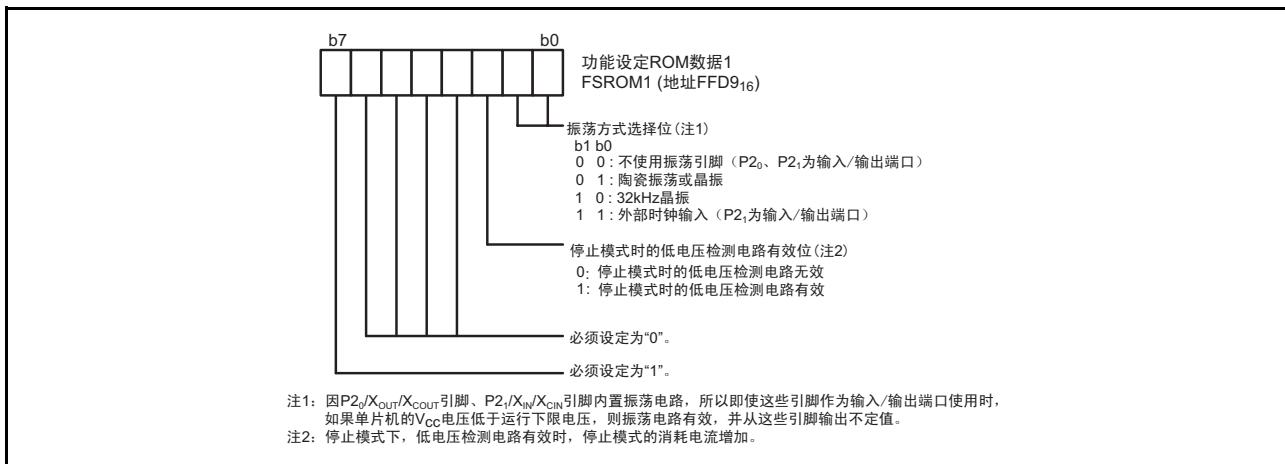

### 【功能设定 ROM 数据】FSROM0、FSROM1、FSROM2

功能设定 ROM 数据 0 ~ 2 (地址 FFD8<sub>16</sub> ~ FFDA<sub>16</sub>) 为进行外围功能模式设定的区域。通过在此区域设定值，解除单片机复位时，即可设定各外围功能的运行模式。外围功能具体运行请参考各外围功能的说明部分。

- 时钟产生电路：58页

- 看门狗定时器：53页

- 低电压检测电路：55页

### 【ROM 代码保护】

QzROM 版的 ROM 保留区的地址 FFDB<sub>16</sub> 为 ROM 代码保护地址且不能在程序中使用。如果选择了“串行编程器的保护位写入”或者在已编程产品出货（本公司）时选择了“有保护”，“00<sub>16</sub>”就被写入该地址。如果将“00<sub>16</sub>”写入 ROM 代码保护地址，保护功能就有效，此后串行编程器不可对其读写。

由串行编程器对 QzROM 空白产品进行 ROM 写入操作时，选择“保护位写入”来保护 ROM 代码。

对于 QzROM 已编程出货产品，本公司进行编程时，将“00<sub>16</sub>”（有保护）或“FF<sub>16</sub>”（无保护）写入 ROM 代码保护地址。

订货时作为 ROM 选项（在掩模转换工具中记为“掩模选项”）可选择写入“00<sub>16</sub>”或写入“FF<sub>16</sub>”。

### 注意事项

- (1) RAM 的内容在复位时为不确定，因此使用前必须设定初始值。

- (2) 请不要存取保留区。

- (3) 在瑞萨出货检查的区域、ROM 保留区，写入每个产品的随机数据。请勿改写此区域的数据。

这些区域的数据有时不预先通知而作变更，因此在确认 ROM 所有区域的校验和的程序中，请不要包含这些区域。

- (4) 通过功能设定 ROM 数据的 0 ~ 2 的 QzROM 值，解除单片机的复位时，可设定各外围功能的运行模式。必须设定所选功能的值。指定固定值“1”或“0”的位，需要设定指定的值。

图 8 存储器分配图

|                    |                     |                    |                     |

|--------------------|---------------------|--------------------|---------------------|

| 0000 <sub>16</sub> | 端口P0(P0)            | 0020 <sub>16</sub> | 保留区                 |

| 0001 <sub>16</sub> | 端口P0方向寄存器(P0D)      | 0021 <sub>16</sub> | 保留区                 |

| 0002 <sub>16</sub> | 端口P1(P1)            | 0022 <sub>16</sub> | 保留区                 |

| 0003 <sub>16</sub> | 端口P1方向寄存器(P1D)      | 0023 <sub>16</sub> | 保留区                 |

| 0004 <sub>16</sub> | 端口P2(P2)            | 0024 <sub>16</sub> | 保留区                 |

| 0005 <sub>16</sub> | 端口P2方向寄存器(P2D)      | 0025 <sub>16</sub> | 保留区                 |

| 0006 <sub>16</sub> | 端口P3(P3) (注1)       | 0026 <sub>16</sub> | 保留区                 |

| 0007 <sub>16</sub> | 端口P3方向寄存器(P3D) (注2) | 0027 <sub>16</sub> | 保留区                 |

| 0008 <sub>16</sub> | 保留区                 | 0028 <sub>16</sub> | 预分频器12(PRE12)       |

| 0009 <sub>16</sub> | 保留区                 | 0029 <sub>16</sub> | 定时器1(T1)            |

| 000A <sub>16</sub> | 保留区                 | 002A <sub>16</sub> | 定时器2(T2)            |

| 000B <sub>16</sub> | 保留区                 | 002B <sub>16</sub> | 定时器模式寄存器(TM)        |

| 000C <sub>16</sub> | 端口P0驱动能力控制寄存器(DCCR) | 002C <sub>16</sub> | 定时计数源设定寄存器(TCSS)    |

| 000D <sub>16</sub> | 端口P0上拉控制寄存器(PULL0)  | 002D <sub>16</sub> | 比较设定值重加载寄存器(CMPR)   |

| 000E <sub>16</sub> | 端口P1上拉控制寄存器(PULL1)  | 002E <sub>16</sub> | 捕捉/比较端口寄存器(CCPR)    |

| 000F <sub>16</sub> | 键唤醒输入选择寄存器(KEYS)    | 002F <sub>16</sub> | 捕捉/比较状态寄存器(CCSR)    |

| 0010 <sub>16</sub> | 捕捉/比较寄存器(低位)(CRAL)  | 0030 <sub>16</sub> | 比较中断源设定寄存器(CISR)    |

| 0011 <sub>16</sub> | 捕捉/比较寄存器(高位)(CRAH)  | 0031 <sub>16</sub> | 捕捉软件触发寄存器(CSTR)     |

| 0012 <sub>16</sub> | 捕捉/比较寄存器R/W指针(CCRP) | 0032 <sub>16</sub> | 捕捉模式寄存器(CAPM)       |

| 0013 <sub>16</sub> | 比较输出模式寄存器(CMOM)     | 0033 <sub>16</sub> | 保留区                 |

| 0014 <sub>16</sub> | 定时器A(低位)(TAL)       | 0034 <sub>16</sub> | AD控制寄存器(ADCON)      |

| 0015 <sub>16</sub> | 定时器A(高位)(TAH)       | 0035 <sub>16</sub> | AD转换低位寄存器(ADL)      |

| 0016 <sub>16</sub> | 保留区                 | 0036 <sub>16</sub> | AD转换高位寄存器(ADH)      |

| 0017 <sub>16</sub> | 保留区                 | 0037 <sub>16</sub> | 时钟模式寄存器(CLKM)       |

| 0018 <sub>16</sub> | 发送/接收缓冲寄存器(TB/RB)   | 0038 <sub>16</sub> | 振荡停止检测寄存器(CLKSTP)   |

| 0019 <sub>16</sub> | 串行I/O状态寄存器(SIOSTS)  | 0039 <sub>16</sub> | 看门狗定时器控制寄存器(WDTCON) |

| 001A <sub>16</sub> | 串行I/O控制寄存器(SIOCON)  | 003A <sub>16</sub> | 中断边沿选择寄存器(INTEDGE)  |

| 001B <sub>16</sub> | 时钟异步控制寄存器(UARTCON)  | 003B <sub>16</sub> | CPU模式寄存器(CPUM)      |

| 001C <sub>16</sub> | 波特率发生器(BRG)         | 003C <sub>16</sub> | 中断请求寄存器1(IREQ1)     |

| 001D <sub>16</sub> | 保留区                 | 003D <sub>16</sub> | 中断请求寄存器2(IREQ2)     |

| 001E <sub>16</sub> | 保留区                 | 003E <sub>16</sub> | 中断控制寄存器1(ICON1)     |

| 001F <sub>16</sub> | 保留区                 | 003F <sub>16</sub> | 中断控制寄存器2(ICON2)     |

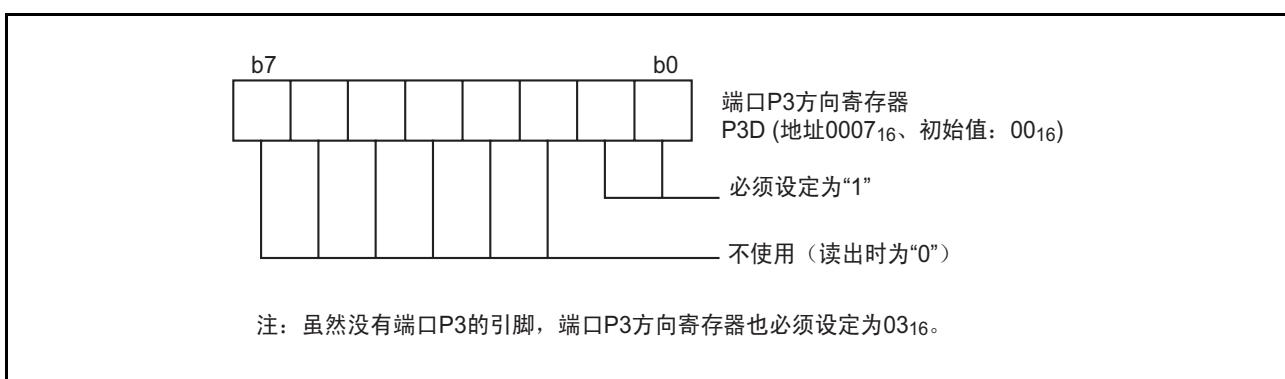

注1. 没有端口P3的引脚。

注2. 虽然没有端口P3，也必须将端口P3方向寄存器设定为03<sub>16</sub>。

注3. 不要对SFR的保留区进行存储器存取。

图 9 SFR (专用功能寄存器) 存储器映射

图 10 功能设定 ROM 数据 0 的结构

图 11 功能设定 ROM 数据 1 的结构

图 12 功能设定 ROM 数据 2 的结构

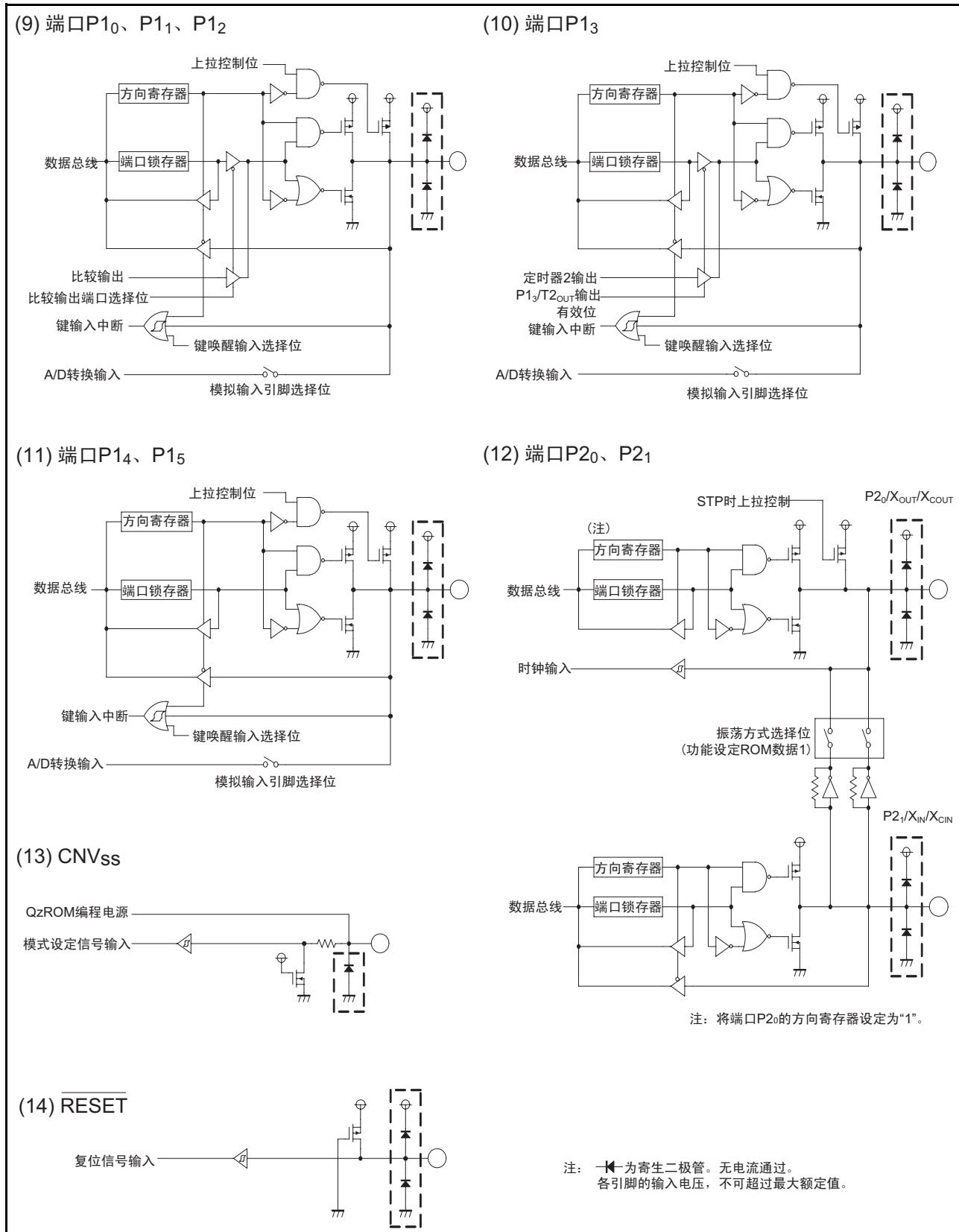

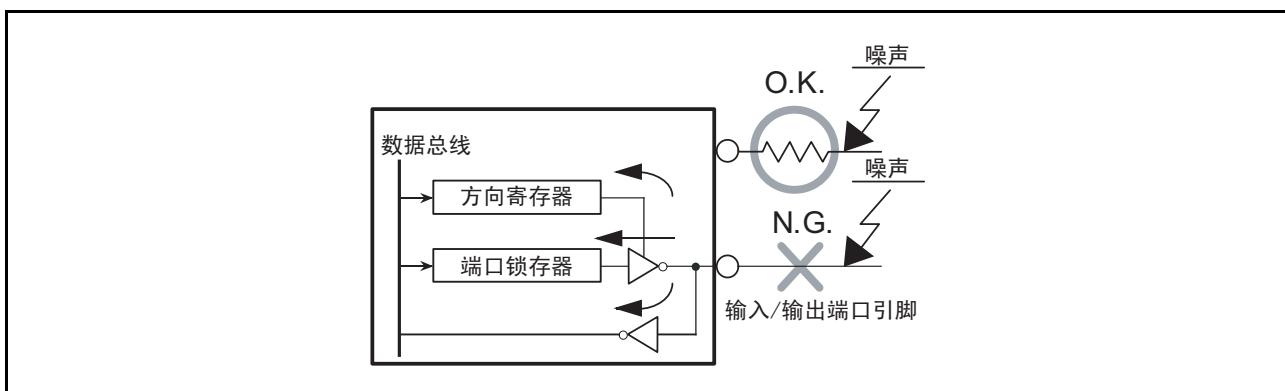

## 输入 / 输出端口

### 【方向寄存器】 PiD

输入 / 输出端口具有方向寄存器，以位为单位设定作为输入端口还是作为输出端口使用。如果将方向寄存器置位为“1”，此引脚为输出端口；如果清“0”，为输入端口。

从被设定为输出端口的引脚读取时，读到的不是引脚的值而是端口锁存器的内容。设定为输入端口的引脚为浮动状态，可读取引脚的值。写入时，数据虽然被写入端口锁存器，但是引脚仍为浮动状态。

- 将端口 P20 作为输出端口使用时，复位解除后请在端口 P20 的方向寄存器写入“1”。

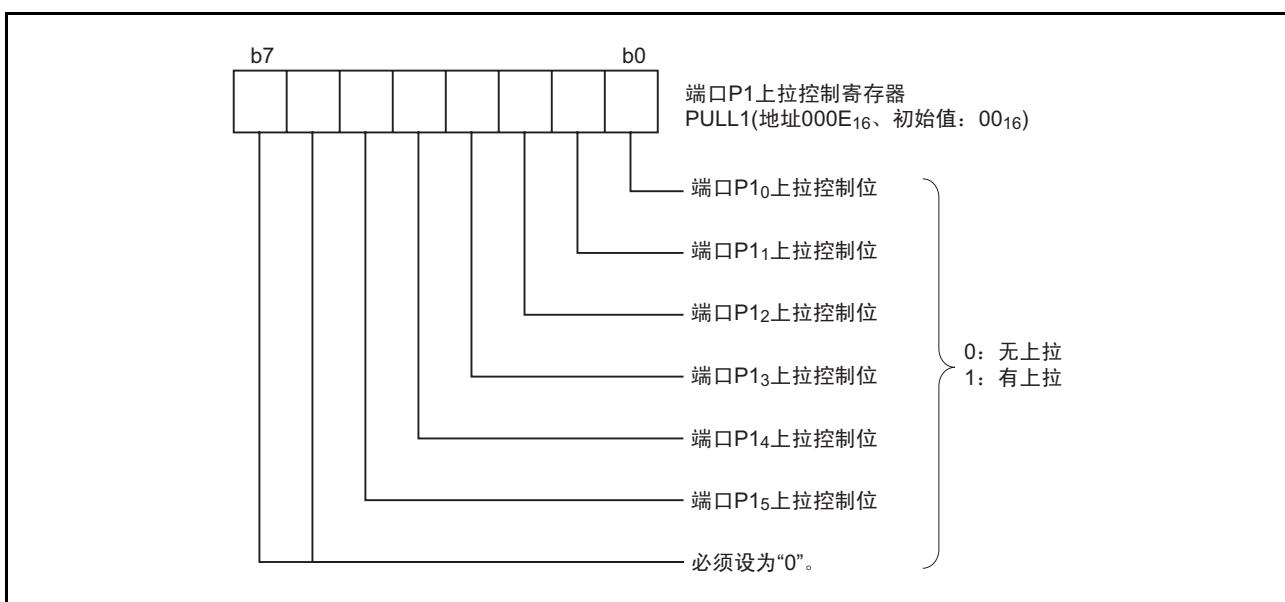

- 端口 P1 方向寄存器的 bit6、7 设定为“1”。

- 端口 P3 方向寄存器的 bit0、1 设定为“1”。

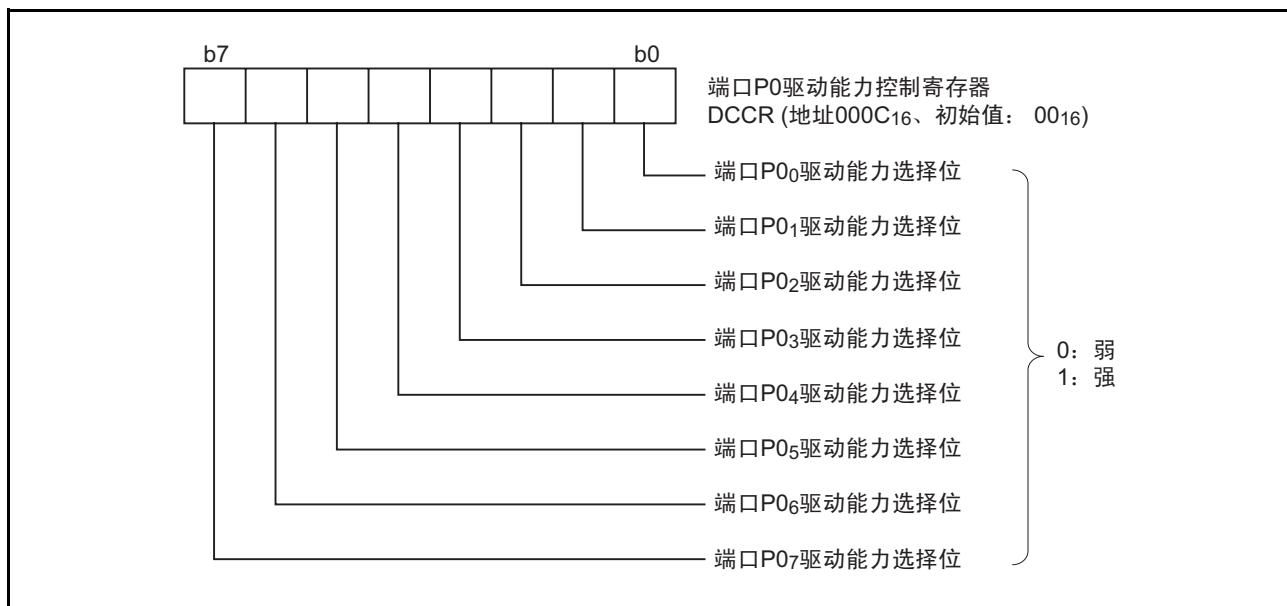

### 【端口 P0 驱动能力控制寄存器】 DCCR

可通过设定端口 P0 驱动能力控制寄存器（地址 000C<sub>16</sub>）选择端口 P0 的 N 沟道输出晶体管的驱动能力。

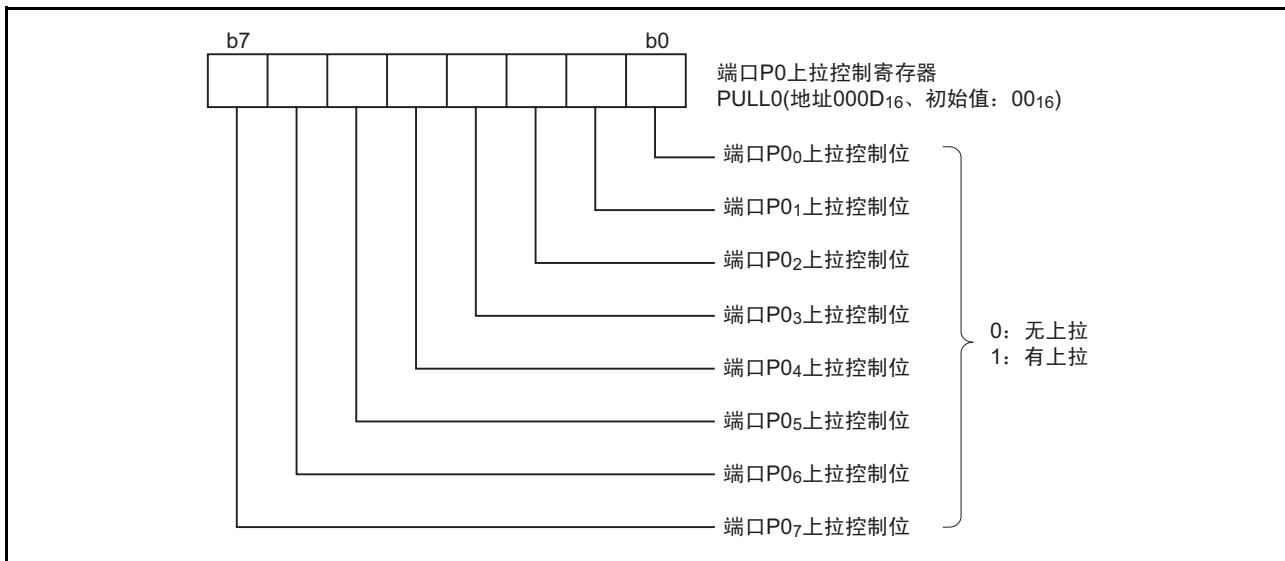

### 【上拉控制寄存器】 PULL0、PULL1

通过设定上拉控制寄存器（地址 000D<sub>16</sub>、000E<sub>16</sub>），端口 P0、P1 可由程序进行上拉控制。但是，端口的方向寄存器仅在设定为输入时有效。设定为输出时，即使设定为“有上拉”，端口也不上拉。

图 13 端口 P0 驱动能力控制寄存器的结构

图 14 端口 P0 上拉控制寄存器的结构

图 15 端口 P1 上拉控制寄存器的结构

图 16 端口 P3 方向寄存器的结构

表 6 输入 / 输出引脚功能一览表

| 引脚名                                                                                                                                                                                                                  | 名称    | 输入 / 输出方式                  | 除引脚以外的功能    | 与各引脚相关的 SFR                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------|-------------|---------------------------------------------------------------|

| P0 <sub>0</sub> (LED <sub>0</sub> )/INT <sub>0</sub><br>P0 <sub>1</sub> (LED <sub>1</sub> )/INT <sub>1</sub>                                                                                                         | 端口 P0 | CMOS 输入电平<br>CMOS 三态输出     | 外部中断输入      | 中断边沿选择寄存器<br>端口 P0 驱动能力控制寄存器<br>端口 P0 上拉控制寄存器                 |

| P0 <sub>2</sub> (LED <sub>2</sub> )                                                                                                                                                                                  |       |                            |             | 端口 P0 驱动能力控制寄存器<br>端口 P0 上拉控制寄存器                              |

| P0 <sub>3</sub> (LED <sub>3</sub> )/CAP <sub>0</sub>                                                                                                                                                                 |       |                            | 捕捉输入        | 捕捉 / 比较端口寄存器<br>端口 P0 驱动能力控制寄存器<br>端口 P0 上拉控制寄存器              |

| P0 <sub>4</sub> (LED <sub>4</sub> )/RXD                                                                                                                                                                              |       |                            | 串行接口输入 / 输出 | 串行 I/O 控制寄存器<br>端口 P0 驱动能力控制寄存器<br>端口 P0 上拉控制寄存器              |

| P0 <sub>5</sub> (LED <sub>5</sub> )/TXD                                                                                                                                                                              |       |                            |             | 串行 I/O 控制寄存器<br>时钟异步控制寄存器<br>端口 P0 驱动能力控制寄存器<br>端口 P0 上拉控制寄存器 |

| P0 <sub>6</sub> (LED <sub>6</sub> )/SCLK                                                                                                                                                                             |       |                            |             | 串行 I/O 控制寄存器<br>端口 P0 驱动能力控制寄存器<br>端口 P0 上拉控制寄存器              |

| P0 <sub>7</sub> (LED <sub>7</sub> )/RDY                                                                                                                                                                              |       |                            |             | 串行 I/O 控制寄存器<br>端口 P0 驱动能力控制寄存器<br>端口 P0 上拉控制寄存器              |

| P1 <sub>0</sub> /AN <sub>0</sub> /KEY <sub>0</sub> /CMP <sub>0</sub><br>P1 <sub>1</sub> /AN <sub>1</sub> /KEY <sub>1</sub> /CMP <sub>1</sub><br>P1 <sub>2</sub> /AN <sub>2</sub> /KEY <sub>2</sub> /CMP <sub>2</sub> | 端口 P1 | 比较输出<br>键输入中断<br>A/D 转换器输入 |             | 捕捉 / 比较端口寄存器<br>端口 P1 上拉控制寄存器<br>键唤醒输入选择寄存器<br>AD 控制寄存器       |

| P1 <sub>3</sub> /AN <sub>3</sub> /KEY <sub>3</sub> /T2OUT                                                                                                                                                            |       |                            |             | 定时器模式寄存器<br>端口 P1 上拉控制寄存器<br>键唤醒输入选择寄存器<br>AD 控制寄存器           |

| P1 <sub>4</sub> /AN <sub>4</sub> /KEY <sub>4</sub><br>P1 <sub>5</sub> /AN <sub>5</sub> /KEY <sub>5</sub>                                                                                                             |       |                            |             | 端口 P1 上拉控制寄存器<br>键唤醒输入选择寄存器<br>AD 控制寄存器                       |

| P2 <sub>0</sub> /XOUT/XCOUT                                                                                                                                                                                          | 端口 P2 | CMOS 三态输出                  | 时钟用引脚       | 功能设定 ROM 数据 1 (注)<br>时钟模式寄存器                                  |

| P2 <sub>1</sub> /XIN/XCIN                                                                                                                                                                                            |       | CMOS 输入电平<br>CMOS 三态输出     | 时钟用引脚       | 功能设定 ROM 数据 1 (注)<br>时钟模式寄存器                                  |

【注】 存在于功能设定 ROM 区。

图 17 引脚框图 (1)

图 18 引脚框图 (2)

## 未使用引脚的处理方法

- 一般的引脚处理方法

输入/输出端口：必须根据各自的处理方法选择输入端口或输出端口。

输出端口： 必须开路。

输入端口： 输入电平不稳定时，穿透电流流通至输入电路，尤其在期待低消耗电流的状态

(STP、WIT指令执行中)，有时会增大电源电流，因此必须上拉或下拉（可使用内部电阻）。

将具有输入/输出端口及输出功能的引脚作为输入端口进行未使用引脚

处理时，假设由于误动作等而作为输出端口运行的情况，推荐通过可确保 $I_{OH}(\text{avg})$ 或 $I_{OL}(\text{avg})$ 的电阻进行引脚处理。

表 7 未使用引脚的处理方法

| 引脚名                                                                  | 处理方法                 |

|----------------------------------------------------------------------|----------------------|

| P0 <sub>0</sub> /INT <sub>0</sub>                                    | 进行输入 / 输出端口处理。       |

| P0 <sub>1</sub> /INT <sub>1</sub>                                    |                      |

| P0 <sub>2</sub>                                                      |                      |

| P0 <sub>3</sub> /CAP <sub>0</sub>                                    |                      |

| P0 <sub>4</sub> /RXD                                                 |                      |

| P0 <sub>5</sub> /TXD                                                 |                      |

| P0 <sub>6</sub> /SCLK                                                |                      |

| P0 <sub>7</sub> /SRDY                                                |                      |

| P1 <sub>0</sub> /AN <sub>0</sub> /KEY <sub>0</sub> /CMP <sub>0</sub> |                      |

| P1 <sub>1</sub> /AN <sub>1</sub> /KEY <sub>1</sub> /CMP <sub>1</sub> |                      |

| P1 <sub>2</sub> /AN <sub>2</sub> /KEY <sub>2</sub> /CMP <sub>2</sub> |                      |

| P1 <sub>3</sub> /AN <sub>3</sub> /KEY <sub>3</sub> /T2OUT            |                      |

| P1 <sub>4</sub> /AN <sub>4</sub> /KEY <sub>4</sub>                   |                      |

| P1 <sub>5</sub> /AN <sub>5</sub> /KEY <sub>5</sub>                   |                      |

| P2 <sub>0</sub> /XOUT/XCOUT                                          | 将方向寄存器置“1”，进行输出端口处理。 |

| P2 <sub>1</sub> /XIN/XCIN                                            | 进行输入 / 输出端口处理。       |

| RESET                                                                | 使用内置上电复位电路时，设为开路。    |

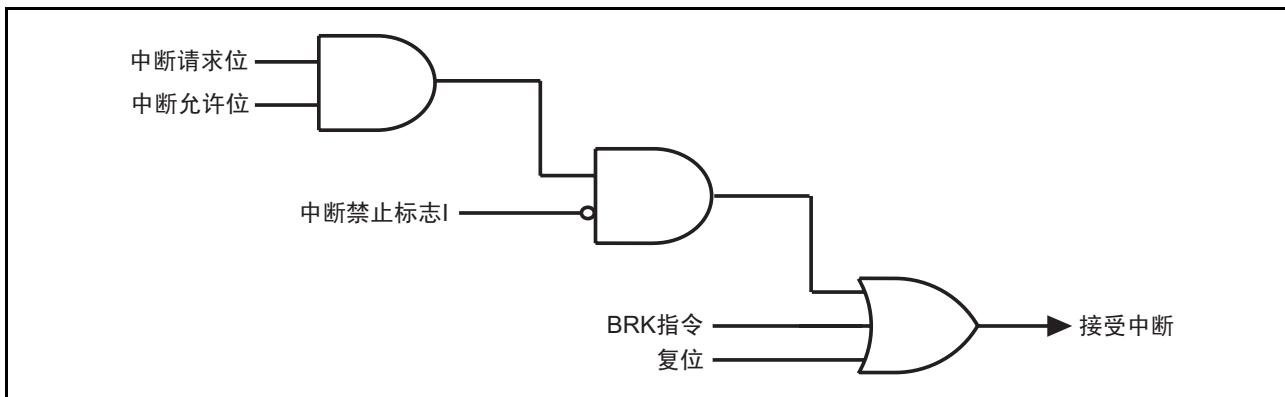

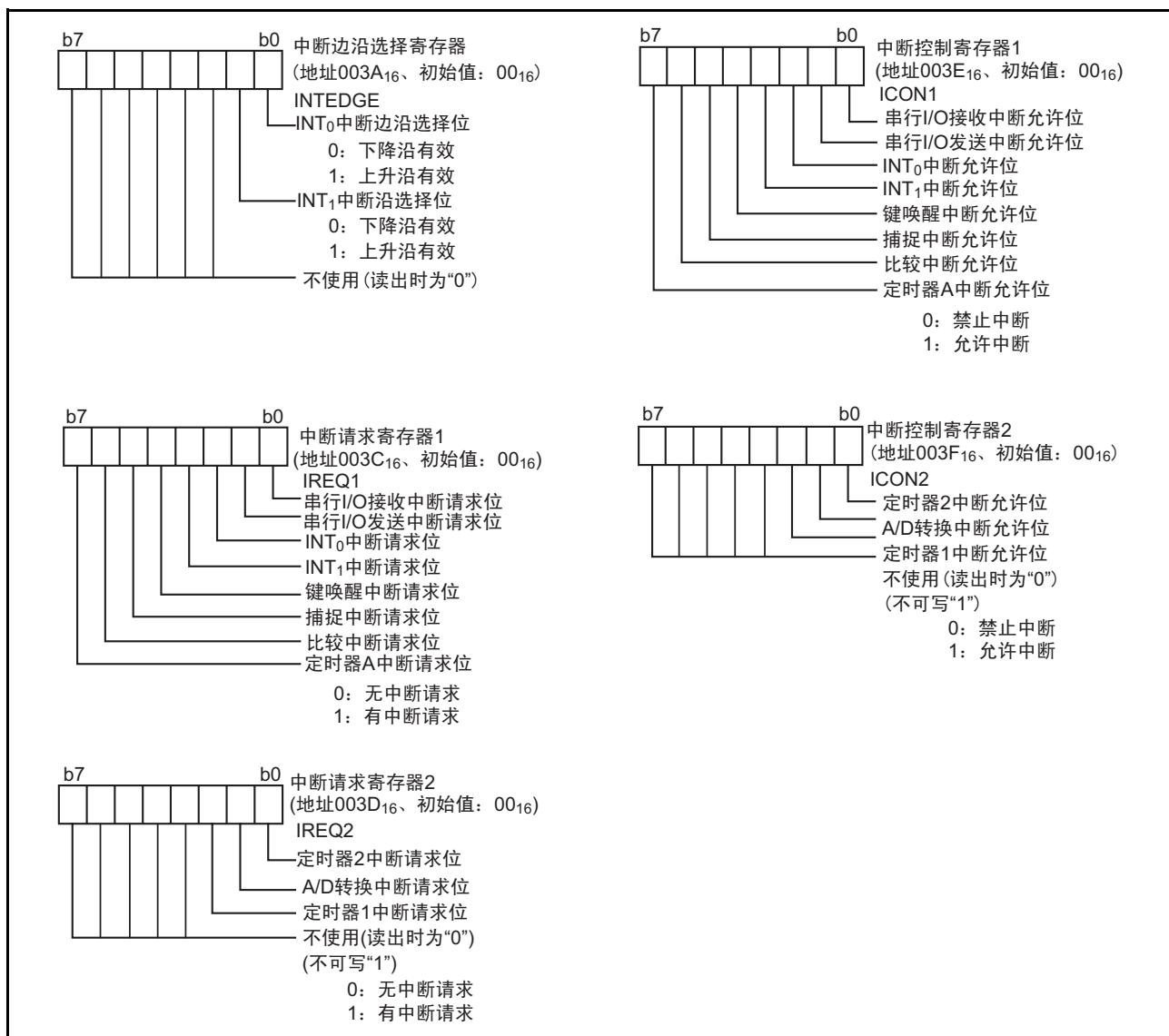

## 中断

7548 群的中断是固定优先级方式的向量中断，可以由 4 个外部中断源、7 个内部中断源和 1 个软件中断源的共 12 个中断源产生。中断源、向量地址（注 1）和中断的优先顺序如表 8 所示。

除 BRK 指令中断外的各中断具有中断请求位与中断允许位，通过上述位和中断禁止标志（I 标志）可控制中断请求的接受。中断控制图如图 19 所示。当具备下述全部条件时，可接受中断请求。

- 中断禁止标志 ..... “0”

- 中断请求位 ..... “1”

- 中断允许位 ..... “1”

中断优先顺序可通过硬件进行固定，也可以使用上述位及标志，通过程序进行优先处理。

表 8 中断向量地址和优先顺序

| 中断源              | 优先顺序 | 向量地址（注 1）           |                    | 中断请求产生条件                        | 备注             |

|------------------|------|---------------------|--------------------|---------------------------------|----------------|

|                  |      | 高位                  | 低位                 |                                 |                |

| 复位（注 2）          | 1    | FFFFD <sub>16</sub> | FFFC <sub>16</sub> | 复位时                             | 非屏蔽            |

| 串行 I/O 接收        | 2    | FFFFB <sub>16</sub> | FFFA <sub>16</sub> | 接收串行 I/O 数据时                    | 仅在选择串行 I/O 时有效 |

| 串行 I/O 发送        | 3    | FFF9 <sub>16</sub>  | FFF8 <sub>16</sub> | 在串行 I/O 发送移位结束时或发送缓冲器空时         | 仅在选择串行 I/O 时有效 |

| INT <sub>0</sub> | 4    | FFF7 <sub>16</sub>  | FFF6 <sub>16</sub> | 检测 INT <sub>0</sub> 输入的上升沿或下降沿时 | 外部中断（极性可编程）    |

| INT <sub>1</sub> | 5    | FFF5 <sub>16</sub>  | FFF4 <sub>16</sub> | 检测 INT <sub>1</sub> 输入的上升沿或下降沿时 | 外部中断（极性可编程）    |

| 键唤醒              | 6    | FFF3 <sub>16</sub>  | FFF2 <sub>16</sub> | 端口 P1（输入时）的输入逻辑电平的逻辑积下降时        | 外部中断（下降沿有效）    |

| 捕捉               | 7    | FFF1 <sub>16</sub>  | FFF0 <sub>16</sub> | 检测捕捉输入的上升沿或下降沿时                 | 外部中断（极性可编程）    |

| 比较               | 8    | FFEF <sub>16</sub>  | FFEE <sub>16</sub> | 比较输出信号取反时                       | 中断源通道可编程       |

| 定时器 A            | 9    | FFED <sub>16</sub>  | FFEC <sub>16</sub> | 定时器 A 下溢时                       |                |

| 定时器 2            | 10   | FFEB <sub>16</sub>  | FFEA <sub>16</sub> | 定时器 2 下溢时                       |                |

| A/D 转换           | 11   | FFE9 <sub>16</sub>  | FFE8 <sub>16</sub> | A/D 转换结束时                       |                |

| 定时器 1            | 12   | FFE7 <sub>16</sub>  | FFE6 <sub>16</sub> | 定时器 1 下溢时                       | STP 解除定时器下溢    |

| 未使用              | 13   | FFE5 <sub>16</sub>  | FFE4 <sub>16</sub> |                                 |                |

|                  | 14   | FFE3 <sub>16</sub>  | FFE2 <sub>16</sub> |                                 |                |

|                  | 15   | FFE1 <sub>16</sub>  | FFE0 <sub>16</sub> |                                 |                |

|                  | 16   | FFDF <sub>16</sub>  | FFDE <sub>16</sub> |                                 |                |

| BRK 指令           | 17   | FFDD <sub>16</sub>  | FFDC <sub>16</sub> | 执行 BRK 指令时                      | 非屏蔽软件中断        |

- 【注】 1. 向量地址表示中断转移地址的保存地址。

2. 复位作为具有最高优先顺序的中断进行处理。

图 19 中断控制图

### 中断禁止标志

处理器状态寄存器的 bit2 为中断禁止标志。中断禁止标志控制除 BRK 指令外的所有中断请求的接受。

如果将此标志设为“1”，就禁止接受中断请求；如果设为“0”，就允许接受中断请求。设为“1”或“0”的指令分别为 SEI 和 CLI 指令。

如果接受中断请求，中断禁止标志就会保持为“0”，并将处理器状态寄存器保存至堆栈。

然后，此标志将自动变为“1”并禁止多重中断。如果使用多重中断，请在中断程序内通过 CLI 指令将此标志设为“0”。

处理器状态寄存器通过 RTI 指令返回。

### 中断请求位

如果产生中断请求，与之相对应的中断请求位变为“1”，并且在接受此中断请求之前保持为“1”。如果接受此中断请求将自动为“0”。

可通过程序将中断请求位设为“0”，但不能设为“1”。

### 中断允许位

中断允许位是指控制接受与之相对应的中断请求的位。

此位为“0”时，禁止接受中断请求。此时即使产生中断请求，也只是中断请求位变为“1”，并不接受中断请求。此位为“1”时，允许接收中断请求。

可通过程序将中断允许位设为“0”或“1”。

请将不使用的中断允许位设为“0”。

图 20 中断相关寄存器的结构

### 中断请求的产生 / 接受 / 处理

中断分为以下 3 个阶段:

(i) 中断请求的产生

由于各种中断源 (外部中断信号的输入、定时器的下溢等) 而产生中断请求，并且中断请求位为“1”。

(ii) 中断请求的接受

中断控制电路通过每个指令周期的中断接受时序来判定中断请求的接受条件 (中断请求位、中断允许位、中断禁止标志) 和中断优先顺序，并接受中断请求。在同一时序产生多个中断请求时，将接受优先顺序最高的中断请求。未被接受的中断请求位仍继续保持，并在下一个中断接受时序再次接受判定。

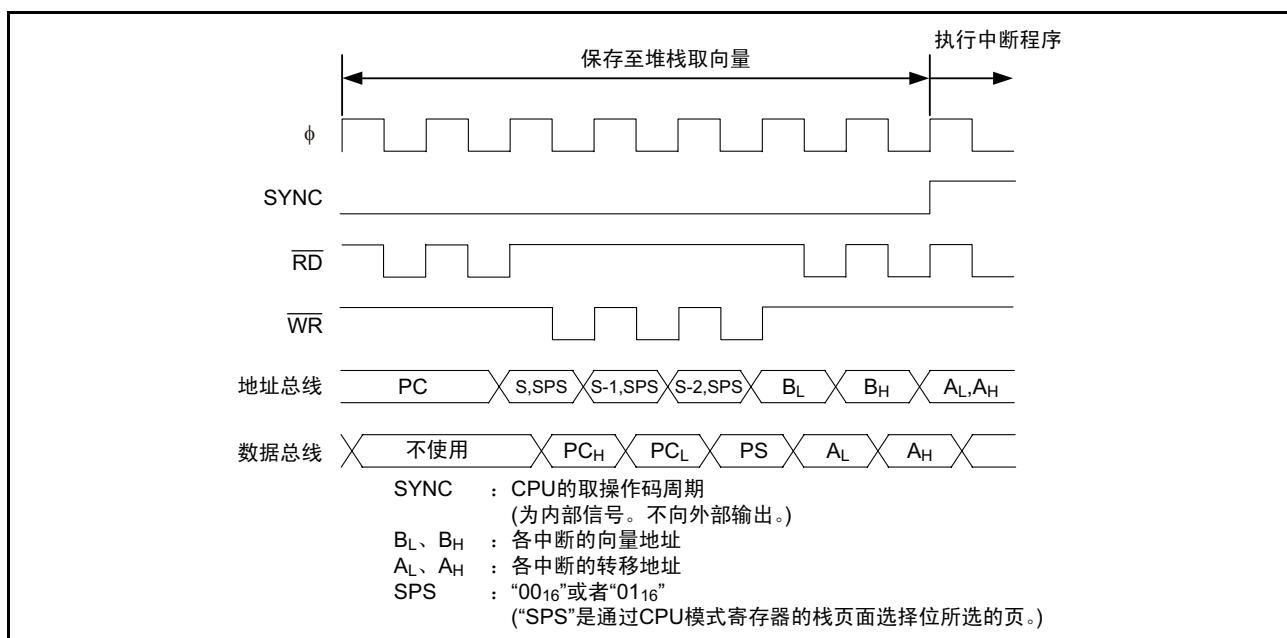

(iii) 接受中断的处理

执行接受中断的处理。

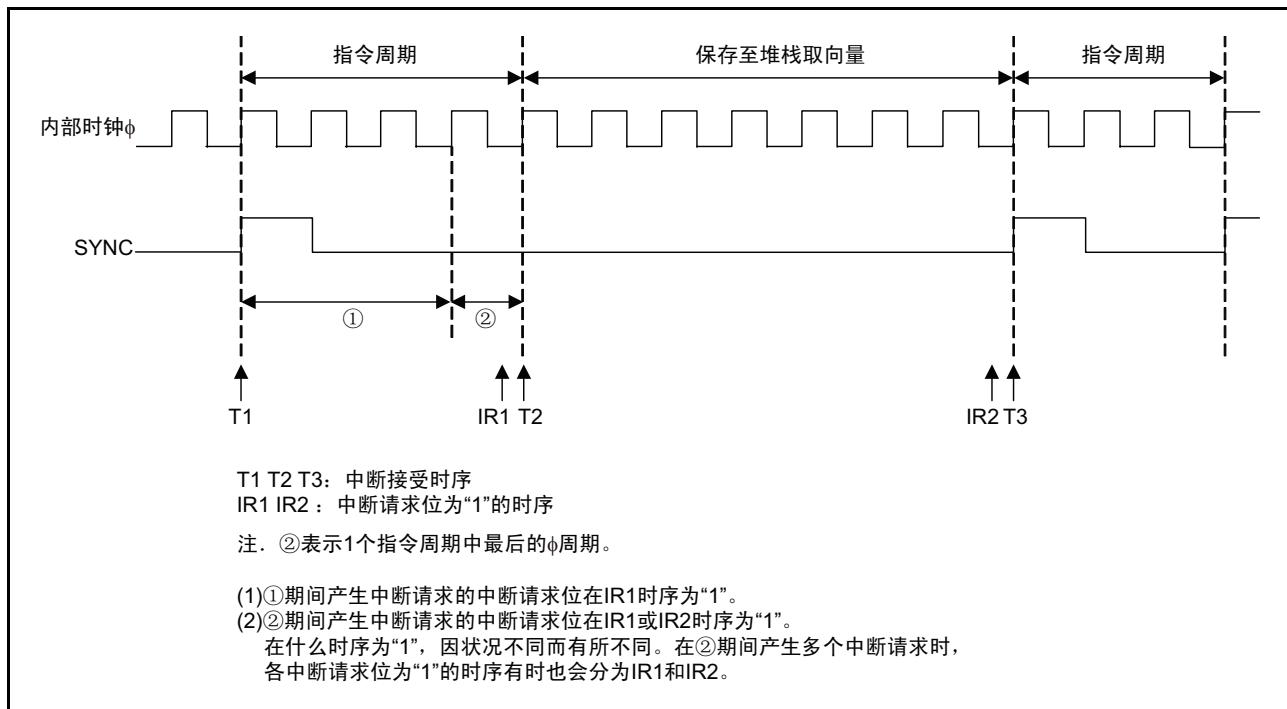

执行中断程序前的时间如图 21 所示，中断响应顺序如图 22 所示，中断请求产生、中断请求位和中断请求接受的时序如图 23 所示。

## 执行中断处理

执行中断处理时，将自动执行下述运行：

- (1) 执行中的指令结束后，接受中断请求。

- (2) 此时的程序计数器及处理器状态寄存器的内容将以①→②→③的顺序保存至堆栈区。

- ①程序计数器高位 (PCH)

- ②程序计数器低位 (PCL)

- ③处理器状态寄存器 (PS)

- (3) 在保存的同时，将与之相对应的中断转移地址（中断程序的起始地址）由中断向量传送至程序计数器。

- (4) 与之相对应的中断的中断请求位为“0”。另外，中断禁止标志为“1”，禁止多重中断。

- (5) 执行中断程序。

- (6) 如果执行RTI指令，保存至堆栈区的寄存器内容将以③→②→①的顺序返回，并继续执行中断处理前的程序。

因此，为了执行中断程序，必须对堆栈指针及对应各中断的向量内的转移地址进行设定。

图 21 到执行中断程序前的时间

图 22 中断响应顺序

图 23 中断请求产生、中断请求位和中断请求接受的时序

### 注意事项

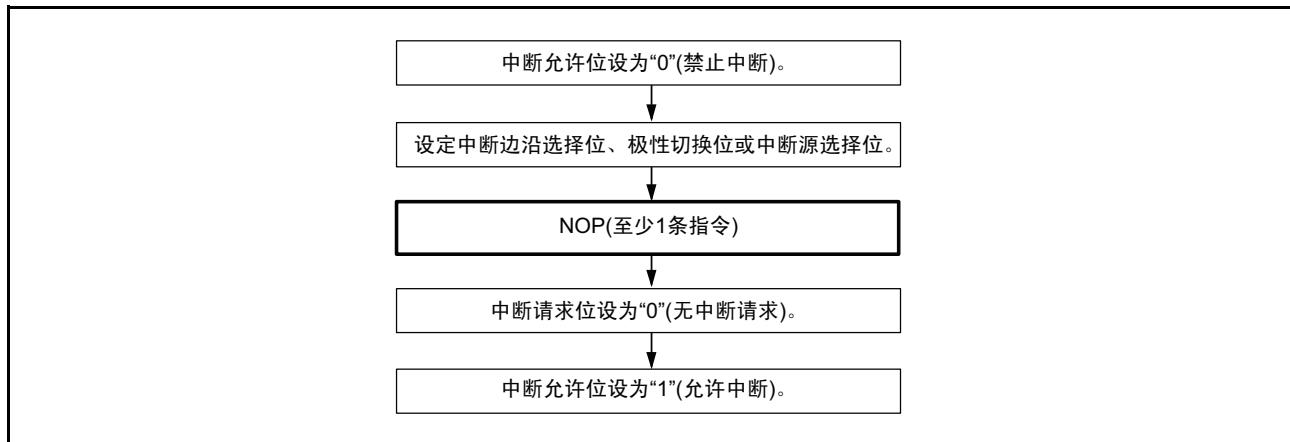

在下述情况中，中断请求位有可能为“1”。

<切换外部中断的有效沿时>

- INT<sub>0</sub>中断边沿选择位

(中断边沿选择寄存器 (地址 003A<sub>16</sub>) 的 bit0)

- INT<sub>1</sub>中断边沿选择位

(中断边沿选择寄存器的 bit1)

如果不需要在上述设定的同时产生中断，请按照以下的步骤进行设定。

- (1) 将对应的中断允许位设为“0”(禁止)。

- (2) 设定中断边沿选择位(极性切换位)和中断源位。

- (3) 执行至少一条的指令后，将对应的中断请求位设为“0”。

- (4) 将对应的中断允许位设为“1”(允许)。

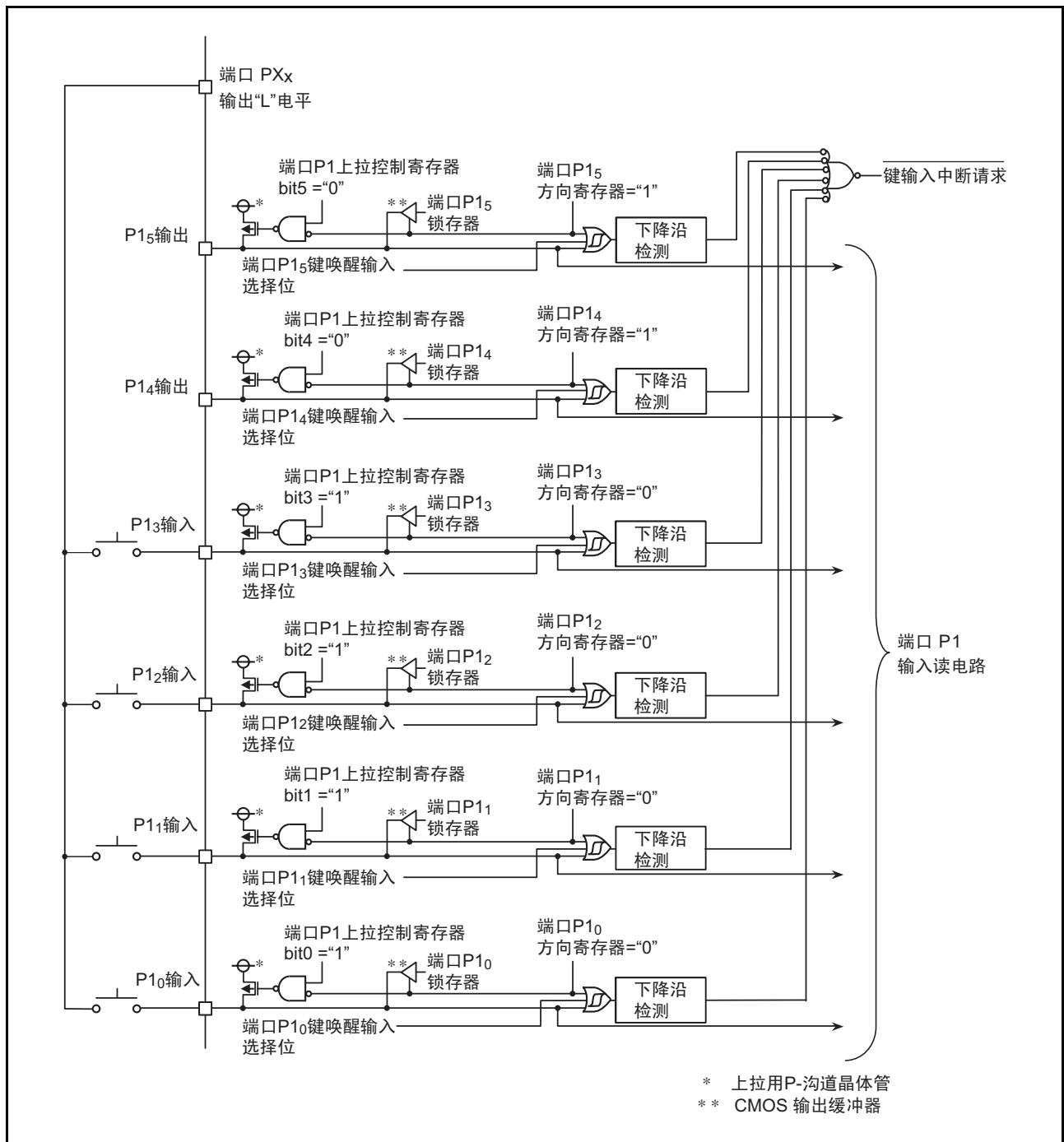

## 键输入中断（键唤醒）

如果给端口 P1 中任何一个设定成输入的引脚外加“L”电平的电压，即：输入电平的逻辑积从“1”变为“0”时，就产生键输入中断请求。图 24 是使用键输入中断的一个例子，将端口 P10 ~ P13 作为输入，构成“L”电平有效的键矩阵，通过按键产生中断。

图 24 使用键输入中断时的接线例子与端口 P1 的框图

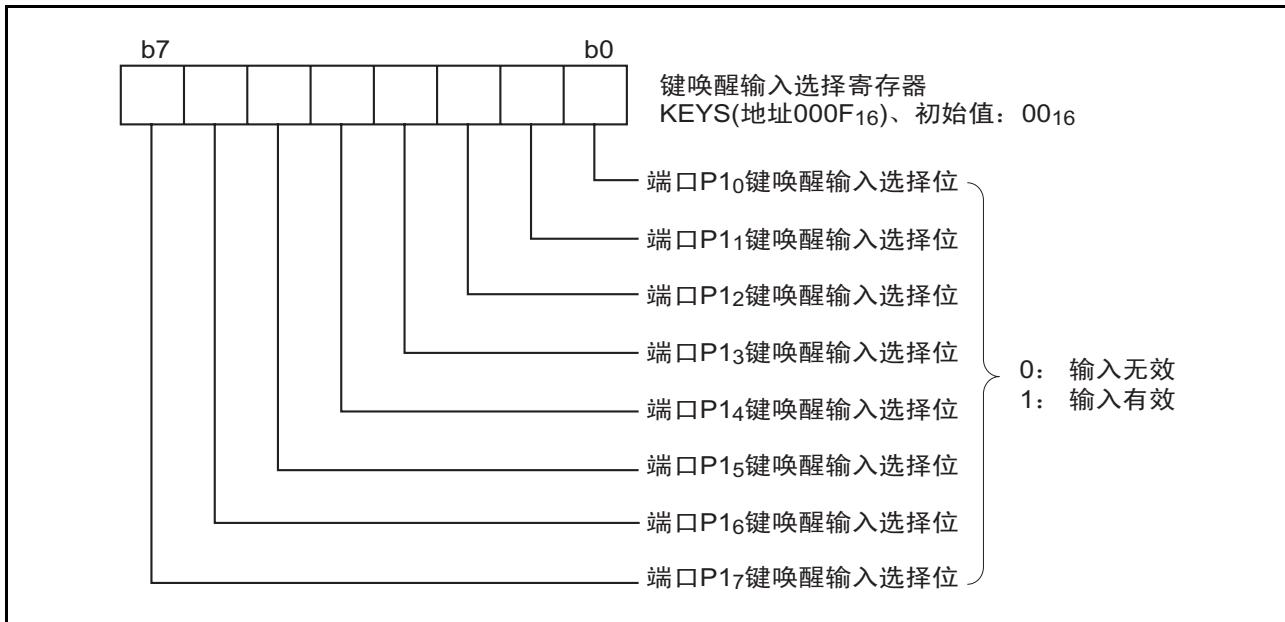

**【键唤醒输入选择寄存器】KEYS**

可通过键唤醒输入选择位分别选择 P10 ~ P17 引脚的键唤醒的允许 / 禁止。

图 25 键唤醒输入选择寄存器的结构

## 定时器

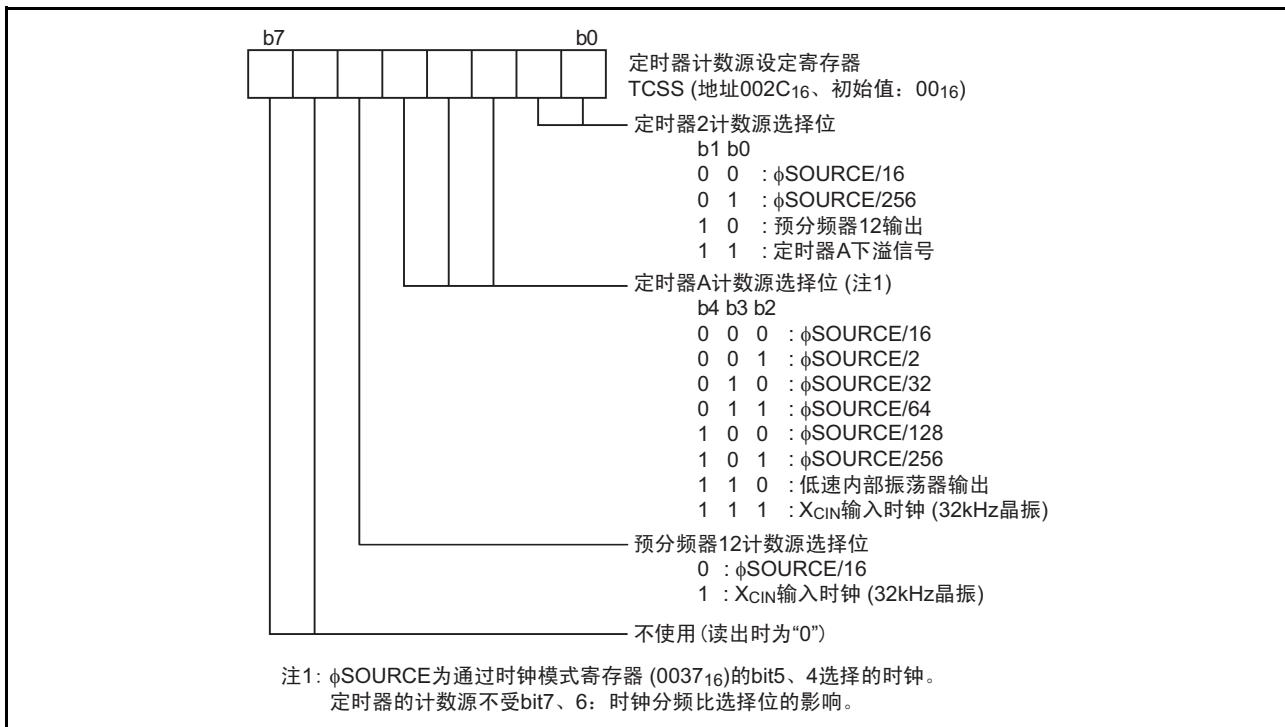

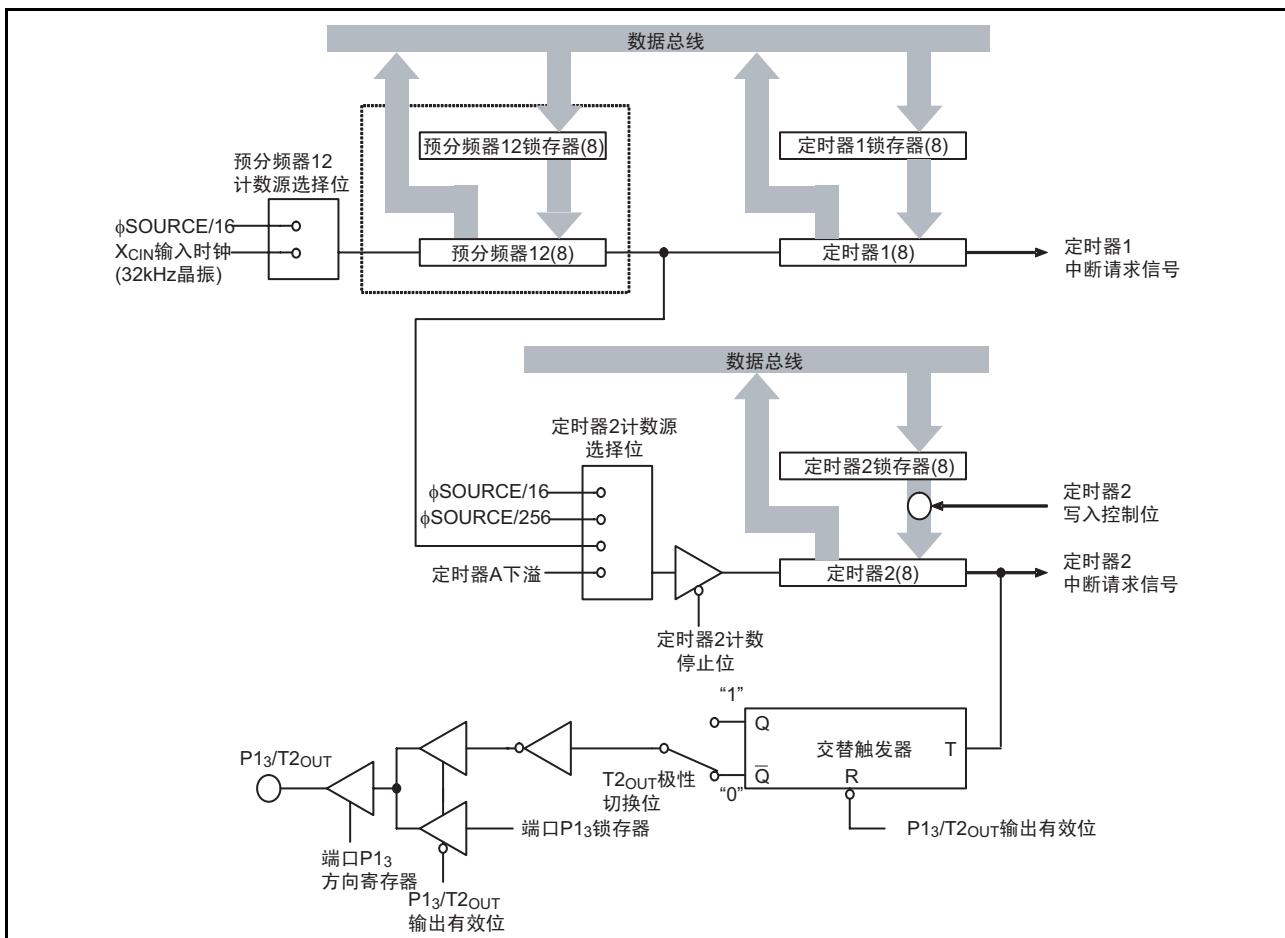

有 2 个 8 位定时器（定时器 1、定时器 2）与 1 个 16 位定时器（定时器 A）。定时器 1、定时器 2 共同有 8 位预分频器（预分频器 12）。另外，各定时器、预分频器分别具备定时器锁存器、预分频器锁存器。

如果定时器锁存器或预分频器锁存器的内容为  $n$ ，所有定时器或预分频器的分频比为  $1/(n+1)$ 。

每次输入计数时钟，定时器即进行递减计数，在计数器的内容为“0”的下一个计数脉冲发生下溢。在下溢的时序，定时器锁存器的内容重加载至定时器后，计数继续。另外，定时器下溢时，各定时器对应的中断请求位置“1”。

### 预分频器 12 (PRE12)

预分频器 12 为 8 位预分频器，计数通过预分频器 12 计数源选择位所选的信号。

计数源可从  $\phi_{SOURCE}$  的 16 分频或  $X_{CIN}$  输入时钟信号中选择。

如果向预分频器 12 写入时，所写的值会同时写入预分频器 12 锁存器与预分频器 12。

读取预分频器 12 时，读取预分频器 12 的计数值。

复位后为“ $FF_{16}$ ”。

设定值为  $n$  时，预分频器 12 的分频比为  $1/(n+1)$ 。

预分频器 12 不可通过软件停止计数。

### 定时器 1 (T1)

定时器 1 为 8 位定时器，计数预分频器 12 的输出，下溢时，定时器 1 中断请求位置“1”。

向定时器 1 写入时，所写值同时写入定时器 1 锁存器与定时器 1。

读取定时器 1 时，读取定时器 1 的计数值。

复位后为“ $01_{16}$ ”。

定时器 1 的设定值为  $m$  时，定时器 1 的分频比为  $1/(m+1)$ 。因此，假设预分频器 12 的设定值为  $n$ 、定时器 1 的设定值为  $m$ ，预分频器 12 与定时器 1 合在一起的分频比为  $1/((n+1) \times (m+1))$ 。

定时器 1 不可通过软件停止计数。

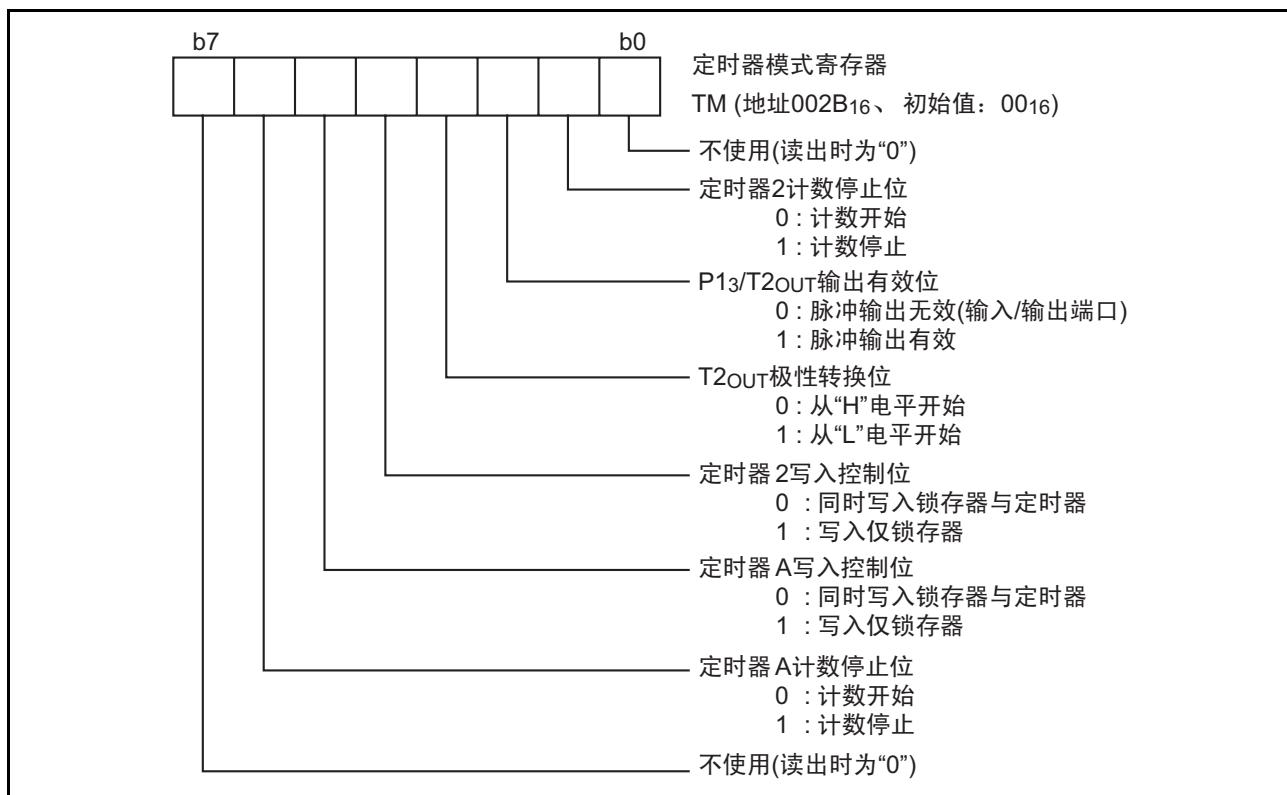

### 定时器 2 (T2)

定时器 2 为 8 位定时器，计数通过定时器 2 计数源选择位所选的信号。

计数源可从  $\phi_{SOURCE}$  的 16 分频、256 分频、预分频器 12 输出及定时器 A 下溢信号中选择。

定时器 2 计数所选计数源，通过下溢，定时器 2 中断请求位置“1”。

向定时器 2 写入时，通过定时器 2 写入控制位可选择同时向定时器 2 锁存器及定时器 2 写入或仅向定时器 2 锁存器写入。

读取定时器 2 时，读取定时器 2 的计数值。

复位后从“ $FF_{16}$ ”开始计数。

如果定时器 2 的设定值为  $n$ ，定时器 2 的分频比为  $1/(n+1)$ 。

定时器 2 计数停止位为“1”时，定时器 2 停止。

另外， $P1_3/T2OUT$  输出有效位为“1”时，定时器 2 每次下溢时，均从  $P1_3/T2OUT$  引脚输出极性取反波形。

通过  $T2OUT$  极性切换位可选择  $T2OUT$  引脚的输出起始电平。此位为“0”时，从“H”开始，为“1”时，从“L”开始。

## 注意事项

### (1) 定时器1、2与预分频器12的读取/写入

定时器/预分频器的计数源时钟与 $\phi_{SOURCE}$ 为不同时钟时，不可进行定时器/预分频器的读取/写入。读取/写入时，请选择相同时钟。

但是，在定时器2的计数停止状态，即使为不同时钟也可读取/写入。

#### ① 不可进行预分频器12、定时器1的读取/写入的条件

预分频器12的计数源：XCIN输入时钟

$\phi_{SOURCE}$ ：XCIN输入时钟以外的时钟

#### ② 计数运行中，不可进行定时器2读取/写入的条件

定时器2的计数源：预分频器12

预分频器12的计数源：XCIN输入时钟

$\phi_{SOURCE}$ ：XCIN输入时钟以外的时钟

或者

定时器2的计数源：定时器A下溢

定时器A的计数源：XCIN输入时钟

$\phi_{SOURCE}$ ：XCIN输入时钟以外的时钟

或者

定时器2的计数源：定时器A下溢

定时器A的计数源：低速内部振荡器输出

$\phi_{SOURCE}$ ：低速内部振荡器以外的时钟

### (2) 预分频器12的计数源

XCIN输入时钟作为预分频器12的计数源的条件是：仅在通过FSROM1的振荡方式选择位选择32kHz晶振时有效。

图 26 定时器模式寄存器的结构

图 27 定时器计数源设定寄存器的结构

图 28 定时器 1、2 的框图

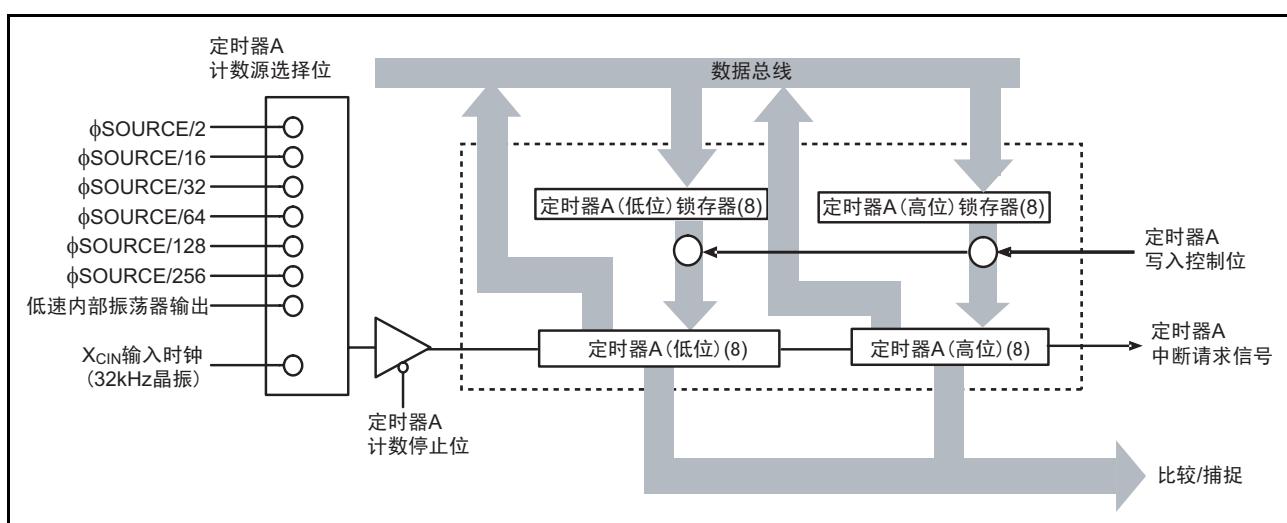

## 定时器 A (TA)

定时器 A 为 16 位定时器，对定时器 A 计数源选择位所选择的信号进行计数。

计数源可从  $\phi_{SOURCE}$  的 2 分频、16 分频、32 分频、64 分频、128 分频、256 分频、低速内部振荡器输出及 XCIN 输入时钟中选择。

定时器 A 计数所选的计数源，通过下溢，定时器 A 中断请求位置“1”。

向定时器 A 写入时，可通过定时器 A 写入控制位的设定值选择同时向定时器 A 锁存器及定时器写入或仅向定时器 A 锁存器写入。

读取定时器 A 时，可读取定时器 A 的计数值。

必须按以下顺序进行定时器 A 低位 (TAL) 与定时器 A 高位 (TAH) 的写入、读取：

- 读取：必须按定时器 A 高位 (TAH)、定时器 A 低位 (TAL) 的顺序，同时读取两个寄存器。

- 写入：必须按定时器 A 低位 (TAL)、定时器 A 高位 (TAH) 的顺序，同时写入两个寄存器。

复位后，从“ $FFFF_{16}$ ”开始计数。

如果定时器 A 的设定值为 n，则定时器 A 的分频比为  $1/(n+1)$ 。

定时器 A 的停止位为“1”时，定时器 A 停止。

定时器 A 可用作输出比较与输入捕捉时序的定时器。

## 注意事项

### (1) 定时器值的设定

将定时器 A 写入控制位设定为“仅向锁存器写入”时，即使定时器处于停止中，写入数据也仅可写入锁存器。因此，对于定时器的初始设定，在定时器停止期间设定值时，必须在选择“同时写入锁存器与定时器”状态下进行。

### (2) 定时器 A 的读取/写入

定时器 A 的计数源时钟与  $\phi_{SOURCE}$  为不同时钟时，定时器 A 运行中不可进行定时器 A 的读取/写入。

只能在选择相同时钟或在停止定时器 A 的状态进行读取/写入。

- 定时器 A 运行中不可进行定时器 A 读取/写入的条件：

定时器 A 的计数源：XCIN 输入时钟

$\phi_{SOURCE}$ ：XCIN 输入时钟以外的时钟

或者

定时器 A 的计数源：低速内部振荡器输出

$\phi_{SOURCE}$ ：低速内部振荡器以外的时钟

### (3) 定时器 A 的计数源

XCIN 输入时钟作为预分频器 12 的计数源的条件是：仅在通过 FSROM1 的振荡方式选择位选择 32kHz 晶振时有效。

图 29 定时器 A 的框图

## 输出比较

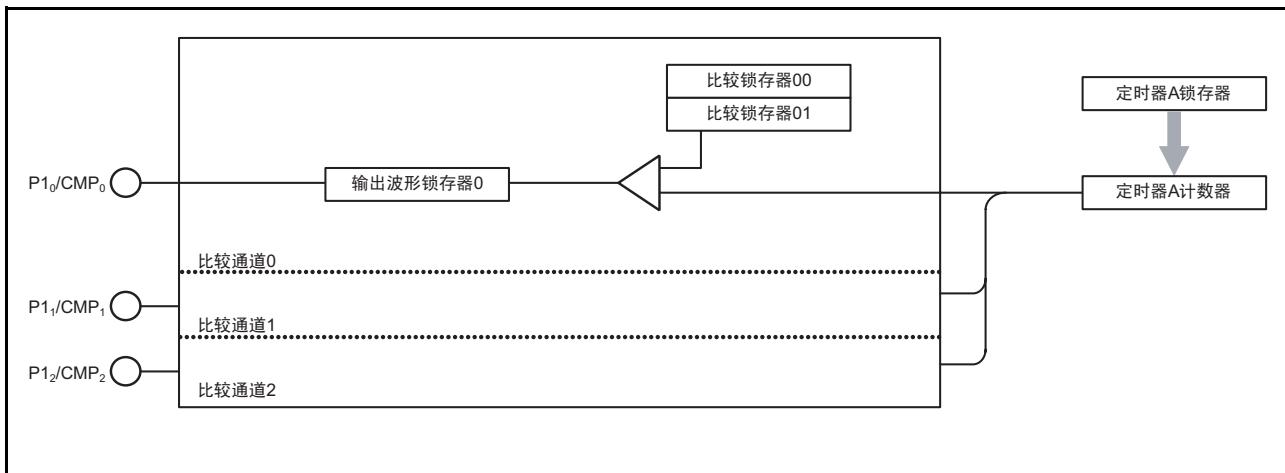

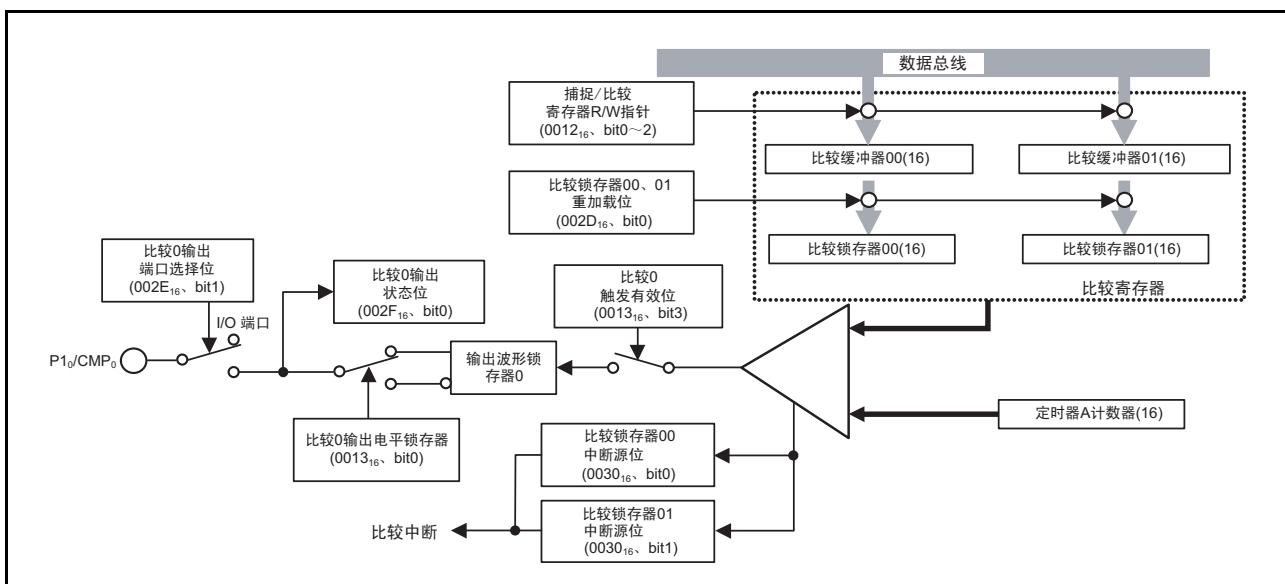

7548 群内置 3 个比较输出通道。通道 0 ~ 2 具有完全相同的功能，可使用定时器 A 的计数值输出波形。

3 个比较输出通道，与输入捕捉（1 个通道）共用寄存器，但是分别具有独立电路，因此可同时使用所有通道。

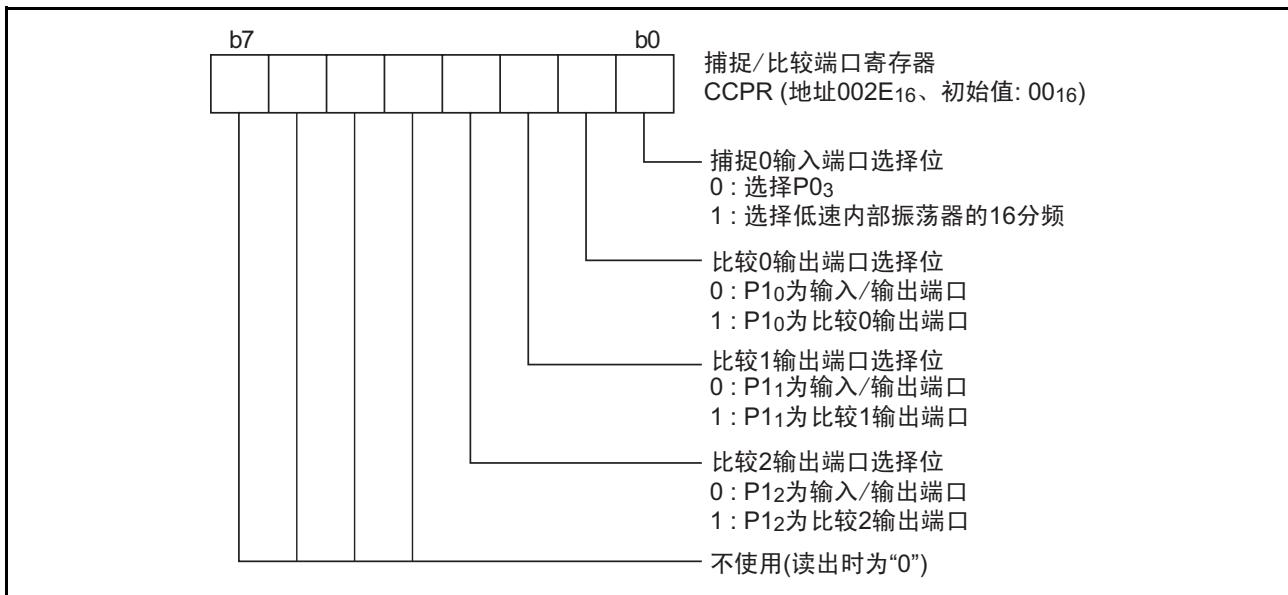

使用比较输出时，设定比较  $x$  ( $x=0, 1, 2$ ) 输出端口选择位，并将输出端口方向寄存器设定“1”。

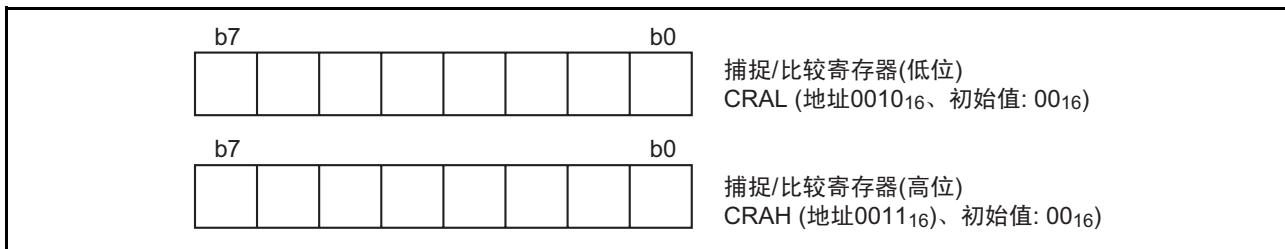

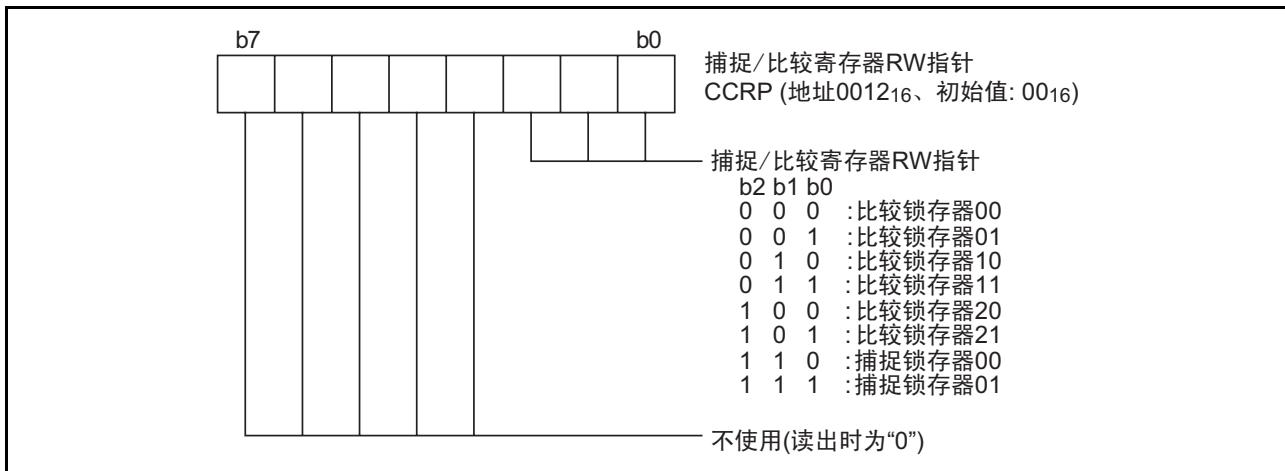

给捕捉 / 比较寄存器（低位）和捕捉 / 比较寄存器（高位）设定比较输出的设定值，用捕捉 / 比较寄存器 R/W 指针控制对各个通道的写入。

(1) 定时器运行时向比较锁存器写入的步骤：

- ① 在捕捉 / 比较寄存器 RW 指针设定写入地址的比较锁存器。

- ② 在捕捉 / 比较寄存器（低位）和捕捉 / 比较寄存器（高位）设定值（无论先写入高位还是低位都没关系）。

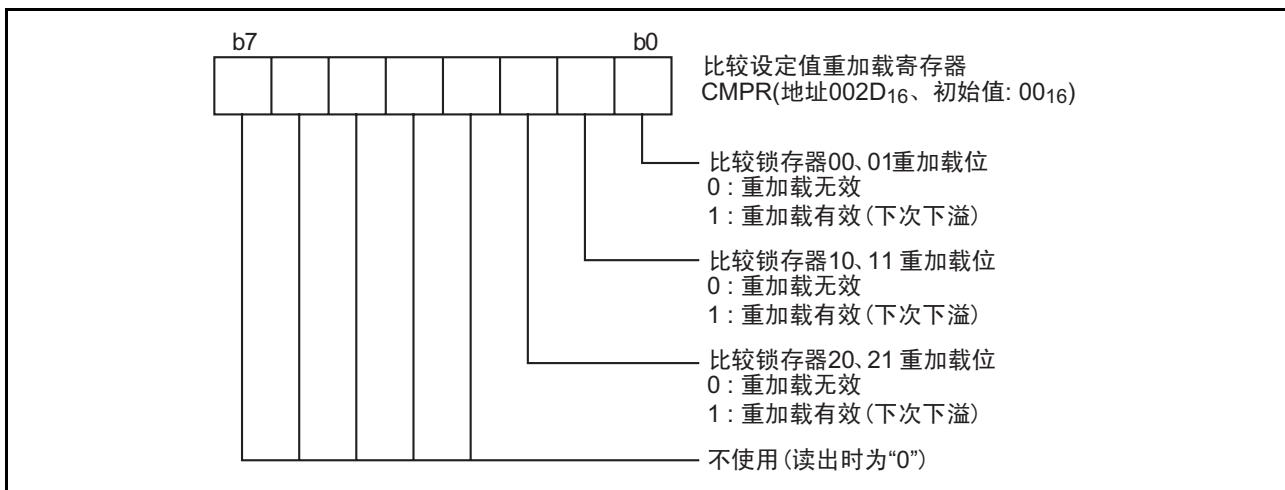

- ③ 在比较锁存器  $y$  ( $y=00, 01, 10, 11, 20, 21$ ) 重加载位设定“1”。

比较锁存器  $y$  重加载位设定“1”时，写入比较寄存器的值在定时器 A 的下一次下溢时传送至比较锁存器。

传送后重加载位自动清“0”。

比较锁存器设定的值与定时器 A 的计数值一致时，产生比较输出电路的触发。

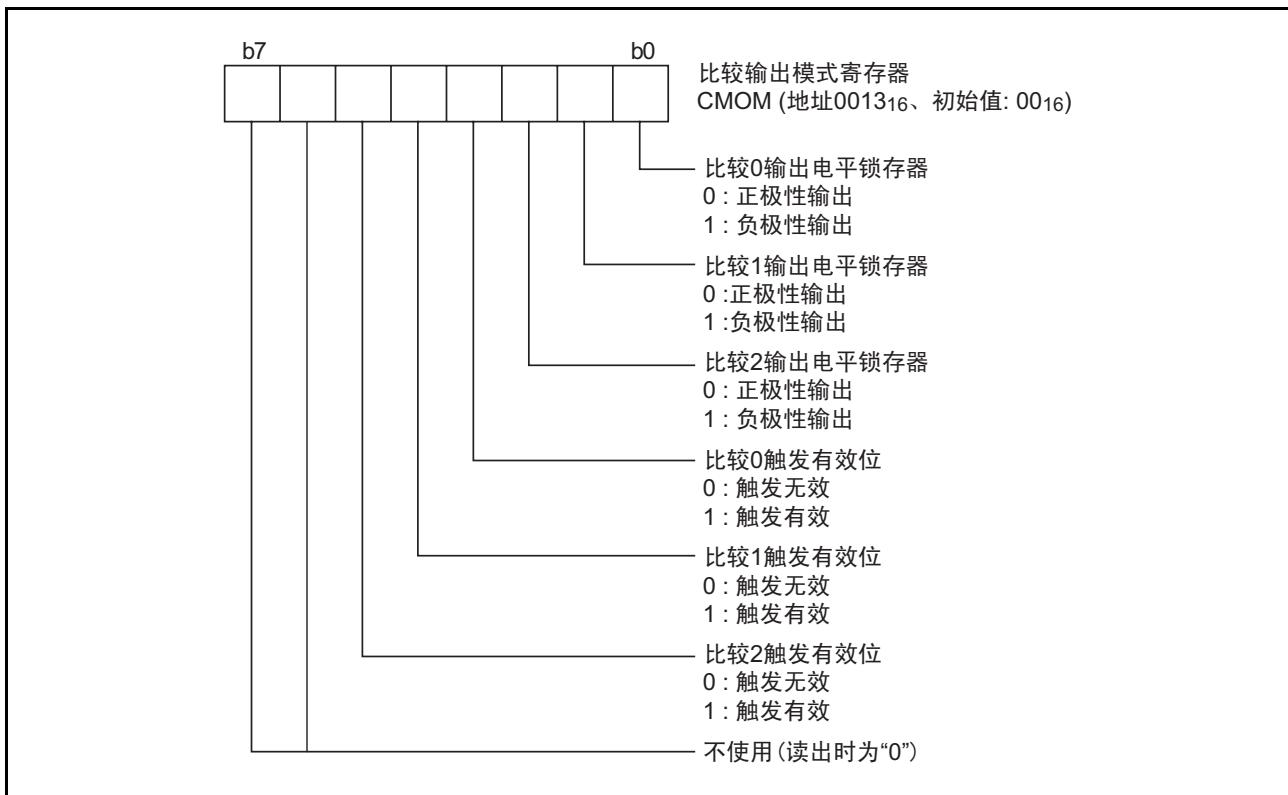

触发有效 / 无效通过比较  $x$  触发有效位设定。

比较  $x$  触发有效位设定为“1”时，从端口输出的波形如下：

- 比较  $x$  输出电平锁存器为“0”时

- 比较锁存器  $x0$  匹配时为“H”

- 比较锁存器  $x1$  匹配时为“L”

- 比较输出电平锁存器为“1”时

- 比较锁存器  $x0$  匹配时为“L”

- 比较锁存器  $x1$  匹配时为“H”

比较  $x$  触发有效位为“0”时输出波形无变化，可将端口输出固定为“L”或“H”。

比较输出状态可通过读取比较  $x$  输出状态位确认为高电平或低电平。

比较锁存器的值与定时器计数值一致时可产生比较中断。来自各比较锁存器的中断信号可通过比较锁存器  $y$  中断源位设定为有效或无效。

## 注意事项

- (1) 定时器 A 停止时，向捕捉 / 比较寄存器写入值的同时，也将值传送至比较锁存器。

另外，定时器 A 停止且比较  $x$  触发有效位为“1”时，输出锁存器被初始化。

- (2) 请不要在比较锁存器  $x0$  与比较锁存器  $x1$  中设定相同的值。

- (3) 比较锁存器的设定值大于定时器的设定值时，不产生比较匹配信号。因此，输出波形固定为“H”电平或“L”电平。

但是另一个比较锁存器的设定值小于定时器的设定值时，小于定时器设定值的一方产生比较匹配信号，因此产生比较中断。

- (4) 如果给比较  $x$  触发有效位设定“0”（无效），由于对波形输出电路的匹配触发被禁止，因此能将输出波形固定成“H”电平或者“L”电平。但是，即使在这种情况下产生比较匹配信号，因此产生比较中断。

图 30 捕捉 / 比较寄存器的结构

图 31 捕捉 / 比较寄存器 RW 指针的结构

图 32 比较设定值重加载寄存器的结构

图 33 捕捉 / 比较端口寄存器的结构

图 34 比较输出模式寄存器的结构

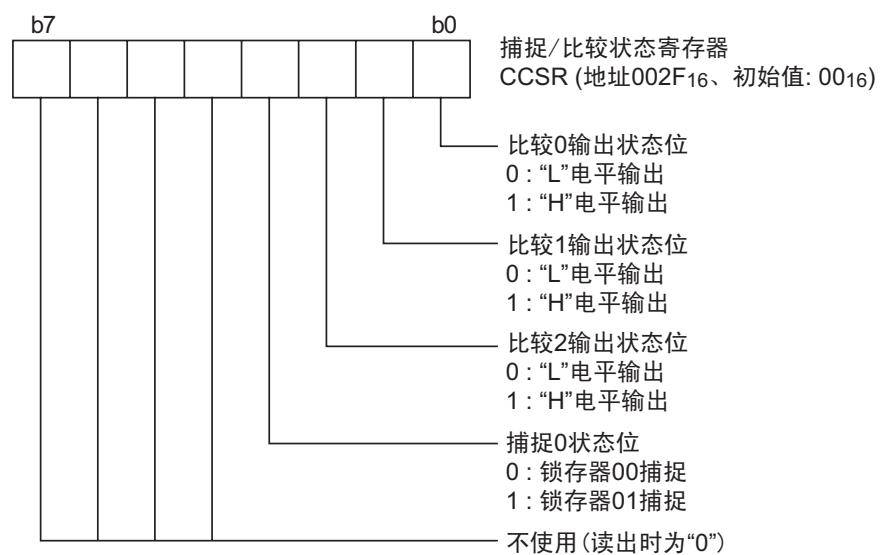

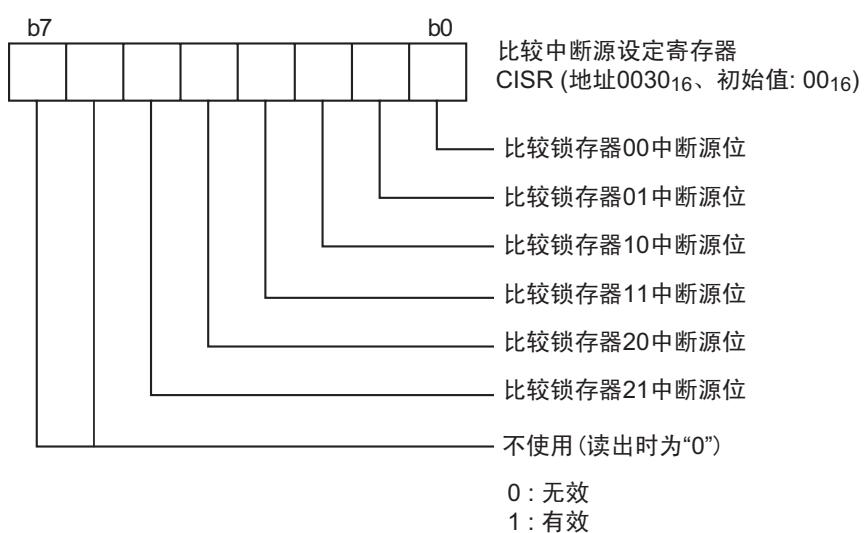

图 35 捕捉 / 比较状态寄存器的结构

图 36 比较由断源设定寄存器的结构

图 37 比较输出电路框图

图 38 比较通道 0 的框图

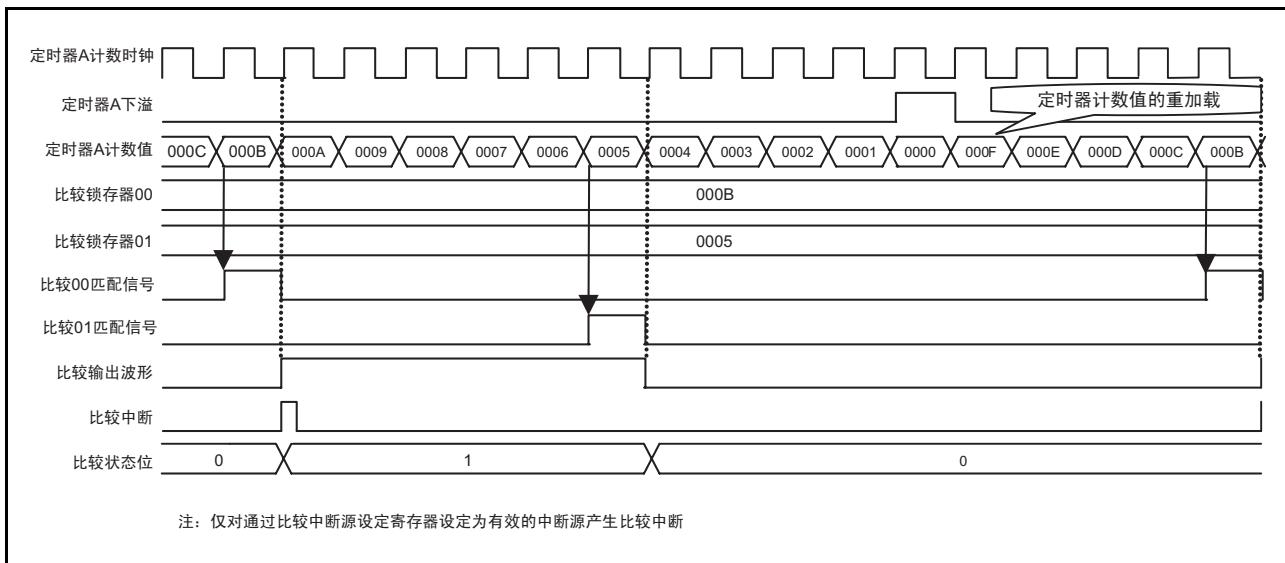

图 39 比较输出波形图（基本输出波形）

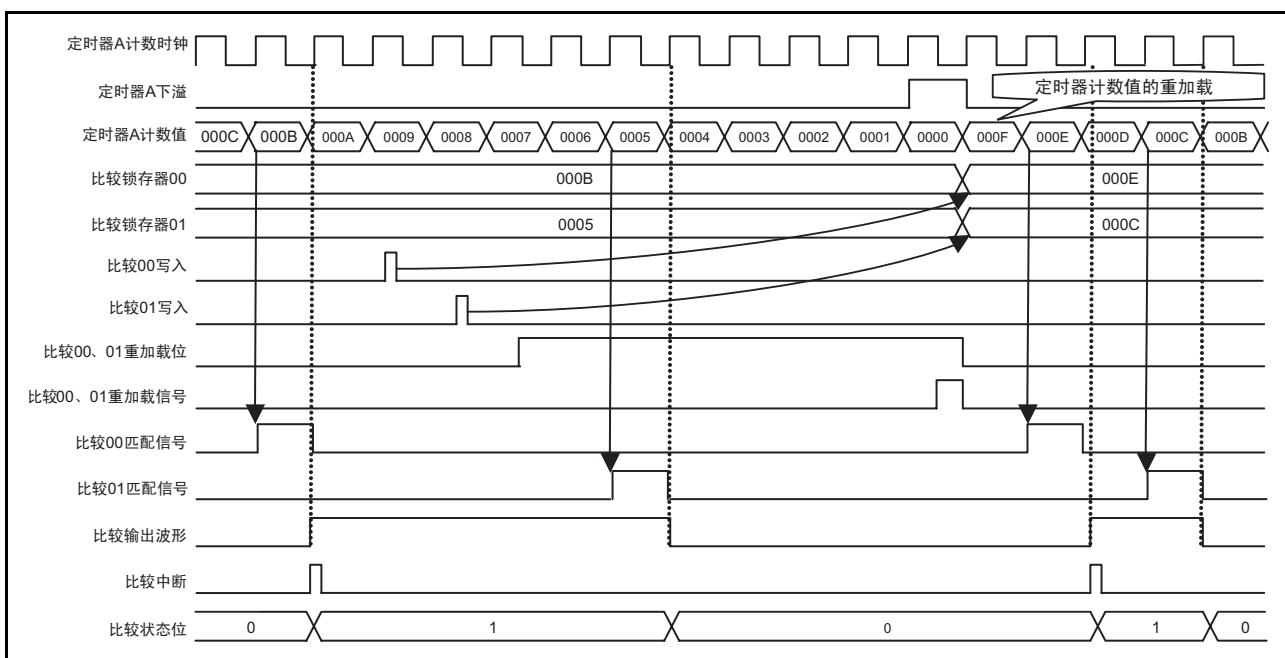

图 40 比较输出波形图（比较寄存器写入时）

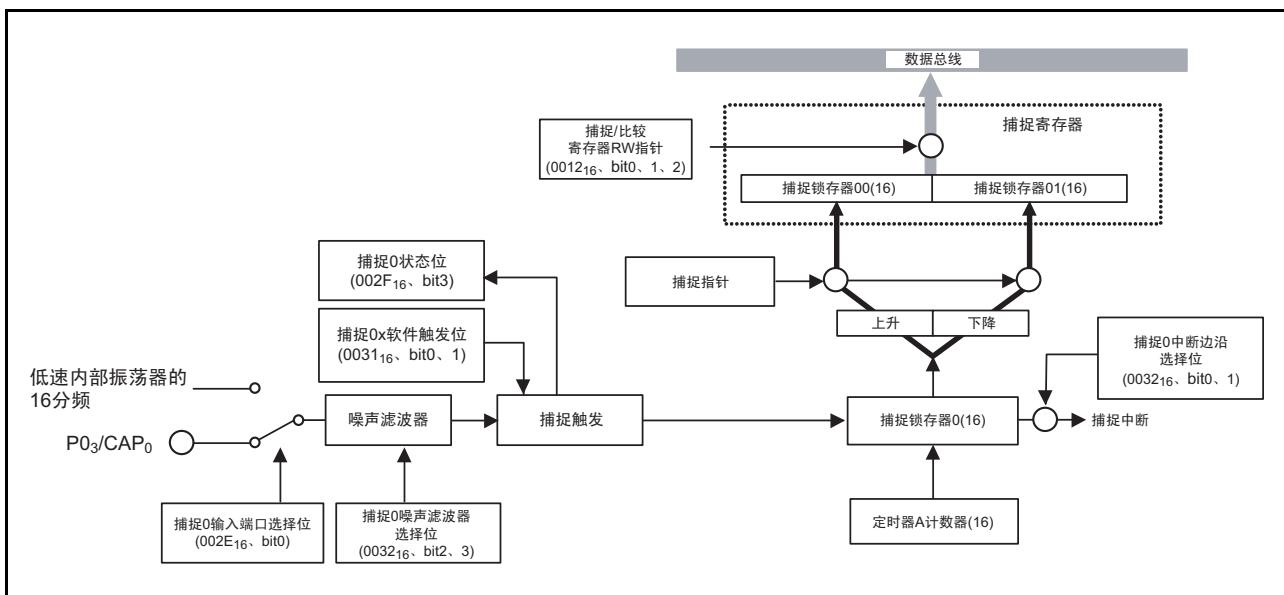

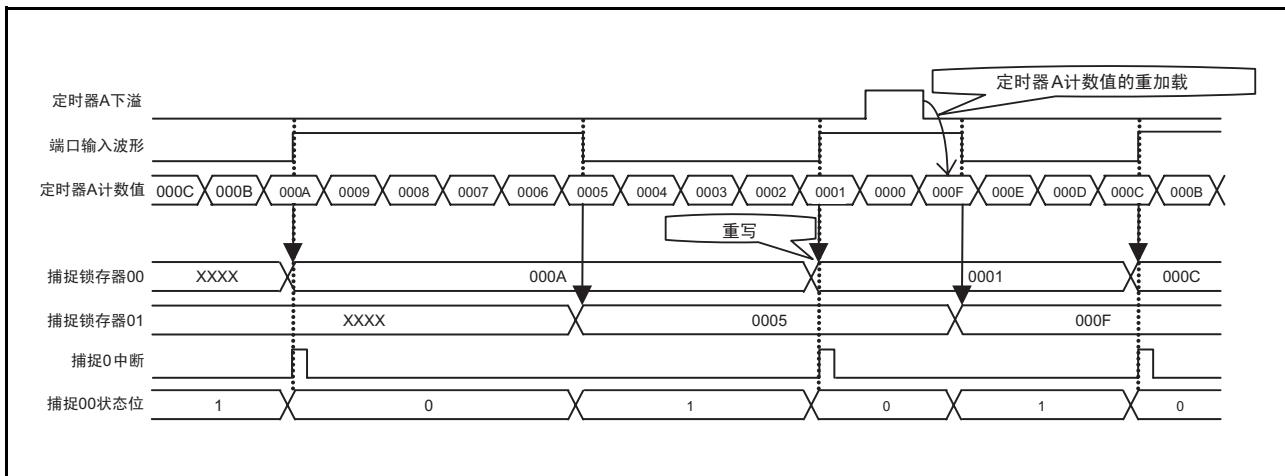

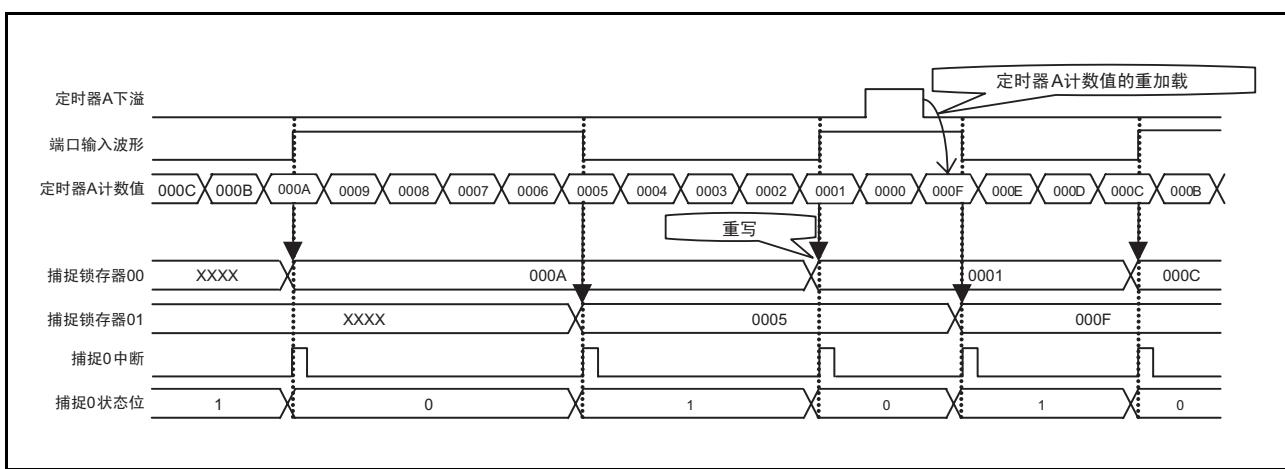

## 输入捕捉

7548 群内置 1 个通道的捕捉输入，可捕捉定时器 A 的计数值。

输入捕捉虽与输出比较的 3 个通道共用寄存器，但是各自的电路分别独立，因此可同时使用所有通道。

使用捕捉输入时，设定捕捉 0 输入端口选择位，选择 P03 时，在 P03 的方向寄存器设定“0”。

捕捉输入电路在输入捕捉输入触发时，将定时器 A 的计数值保存至捕捉锁存器。在捕捉锁存器 00 中保存外部输入触发上升时的定时器计数值，在捕捉锁存器 01 中保存外部输入触发下降时的定时器计数值。捕捉锁存器 00 及捕捉锁存器 01 可按照以下顺序读取。

1. 在捕捉/比较寄存器 R/W 指针设定读取地址的捕捉锁存器。

2. 先读取捕捉/比较寄存器（高位），然后读取捕捉/比较寄存器（低位）。（必须按先高位后低位的顺序同时读取两个寄存器。）

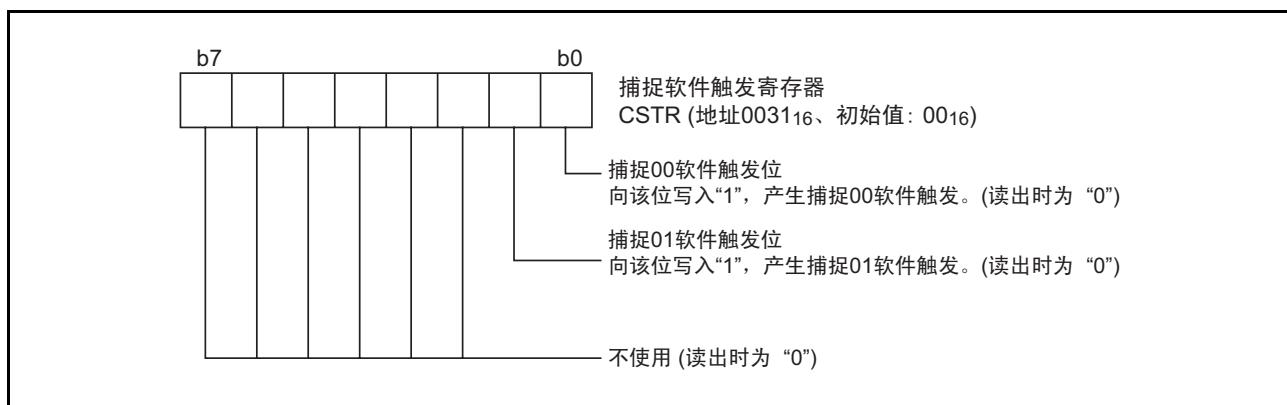

通过使用捕捉 y(y=00、01) 软件触发位，也能保存由捕捉 y 软件触发产生的定时器计数值。通过给捕捉 y 软件触发位写“1”，将定时器计数值保存到对应的捕捉锁存器。

在读取捕捉 y 软件触发位时，读取“0”。

## 注意事项

- (1) 定时器 A 的计数源作为低速内部振荡器输出或 XCIN 输入时钟选择时，仅限 SOURCE 选择与定时器 A 的计数源相同的时钟源时，可使用输入捕捉。

- (2) 给捕捉锁存器 00 及 01 的捕捉 y 软件触发位同时写入“1”及外部触发与软件触发同时产生时，如果捕捉锁存器 00 和 01 同时进行捕捉输入，捕捉 0 状态位的值为不定。

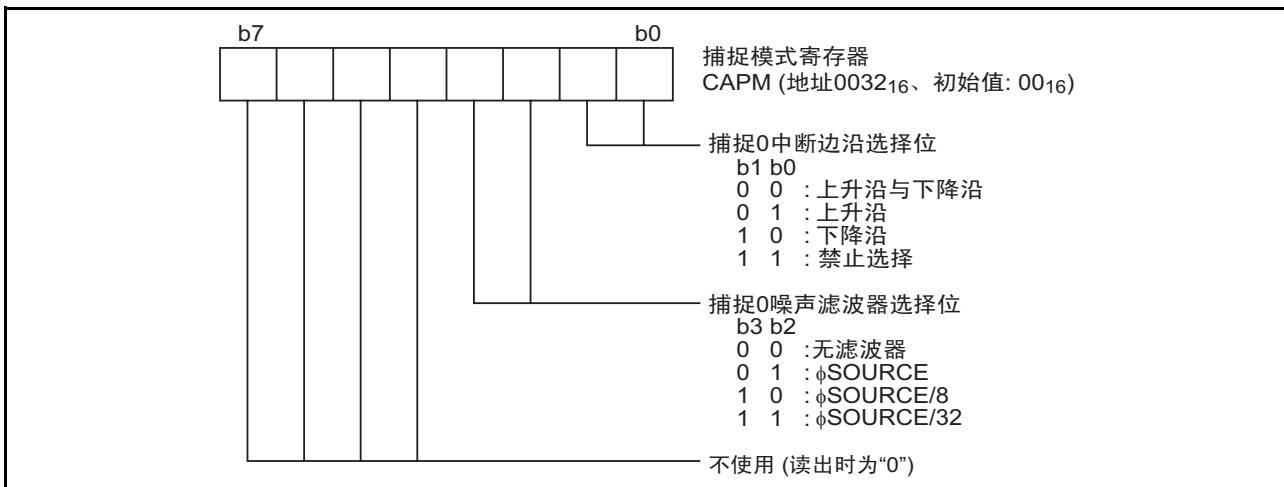

- (3) 设定捕捉 0 的中断边沿选择位及噪声滤波器选择位时，中断请求位可能置“1”。如果不需与中断边沿选择位或噪声滤波器选择位的设定同步的中断时，请按以下顺序设定：

- ① 将捕捉中断允许位置“0”（禁止）。

- ② 设定中断边沿选择位或噪声滤波器选择位。

- ③ 执行至少一条指令后，捕捉中断请求位置“0”。

- ④ 捕捉中断允许位置“1”（允许）。

- (4) 将捕捉中断作为从停止模式返回的中断使用时，请将捕捉 0 噪声滤波器选择位设定为“00：无滤波器”。

图 41 捕捉软件触发寄存器的结构

图 42 捕捉模式寄存器的结构

图 43 捕捉通道 0 的框图

图 44 捕捉输入波形图（捕捉 0 中断边沿选择位：选择上升沿时）

图 45 捕捉输入波形图（捕捉 0 中断边沿选择位：选择上升沿及下降沿时）

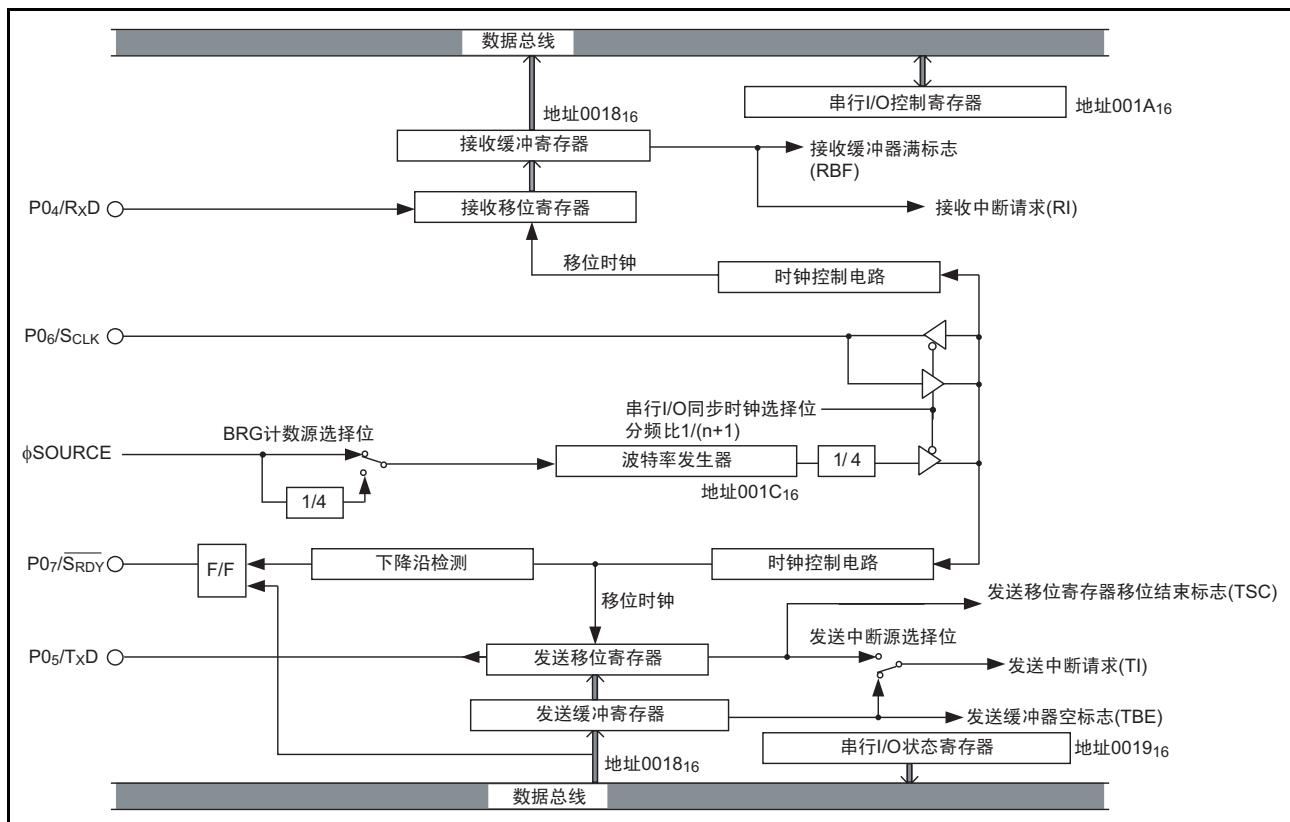

## 串行接口

### 串行 I/O

串行 I/O 在时钟同步模式或时钟异步模式（UART）下均可运行。另外，具备串行 I/O 运行时的波特率发生专用定时器（波特率发生器）。

#### (1) 时钟同步串行 I/O 模式

通过将串行 I/O 控制寄存器的串行 I/O 模式选择位（b6）置“1”，选择时钟同步串行 I/O。

在时钟同步串行 I/O，对于串行 I/O 运行时钟，发送方单片机、接收方单片机均使用同一时钟。使用内部时钟作为运行时钟时，通过发送/接收缓冲寄存器的写入信号，开始发送和接收。

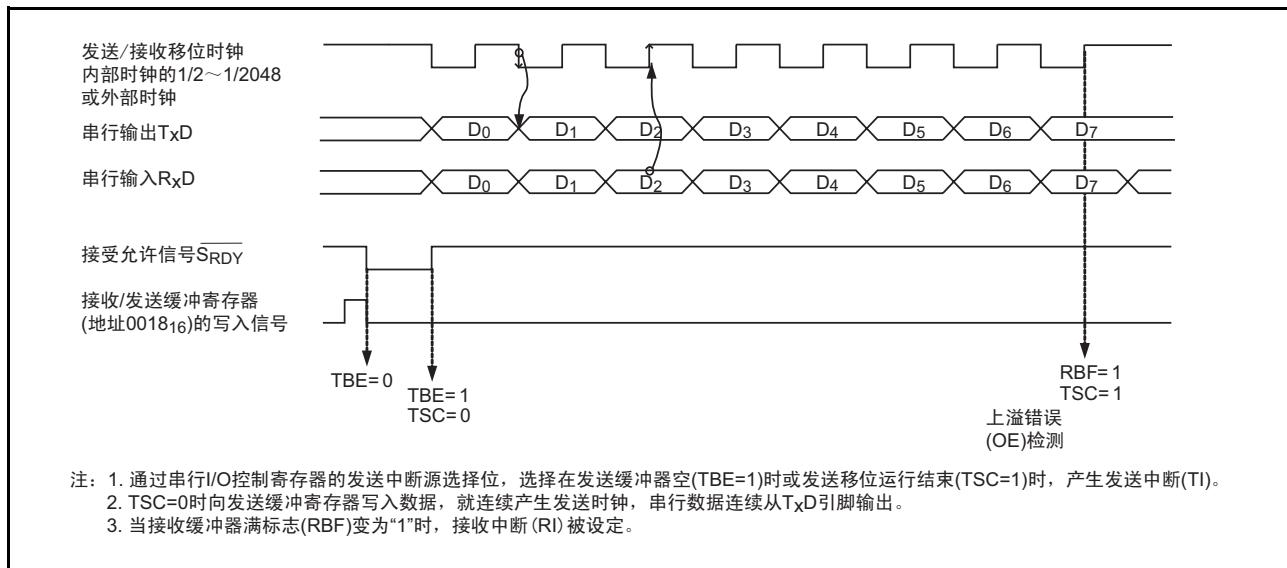

图 46 时钟同步串行 I/O 框图

图 47 时钟同步串行 I/O 运行图

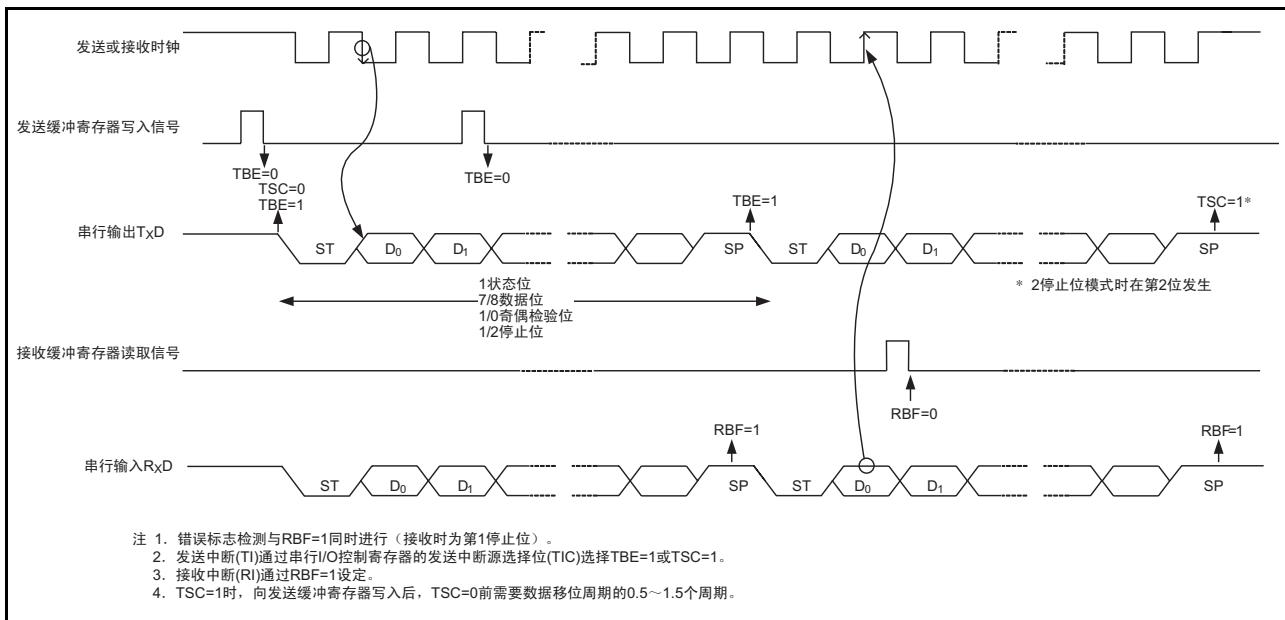

## (2) 时钟异步串行 I/O (UART) 模式

通过将串行 I/O 控制寄存器的串行 I/O 模式选择位 (b6) 置 “0”，选择时钟异步。

7548 群可选择 8 种串行数据传送格式。必须预先在发送方与接收方将传送格式统一。

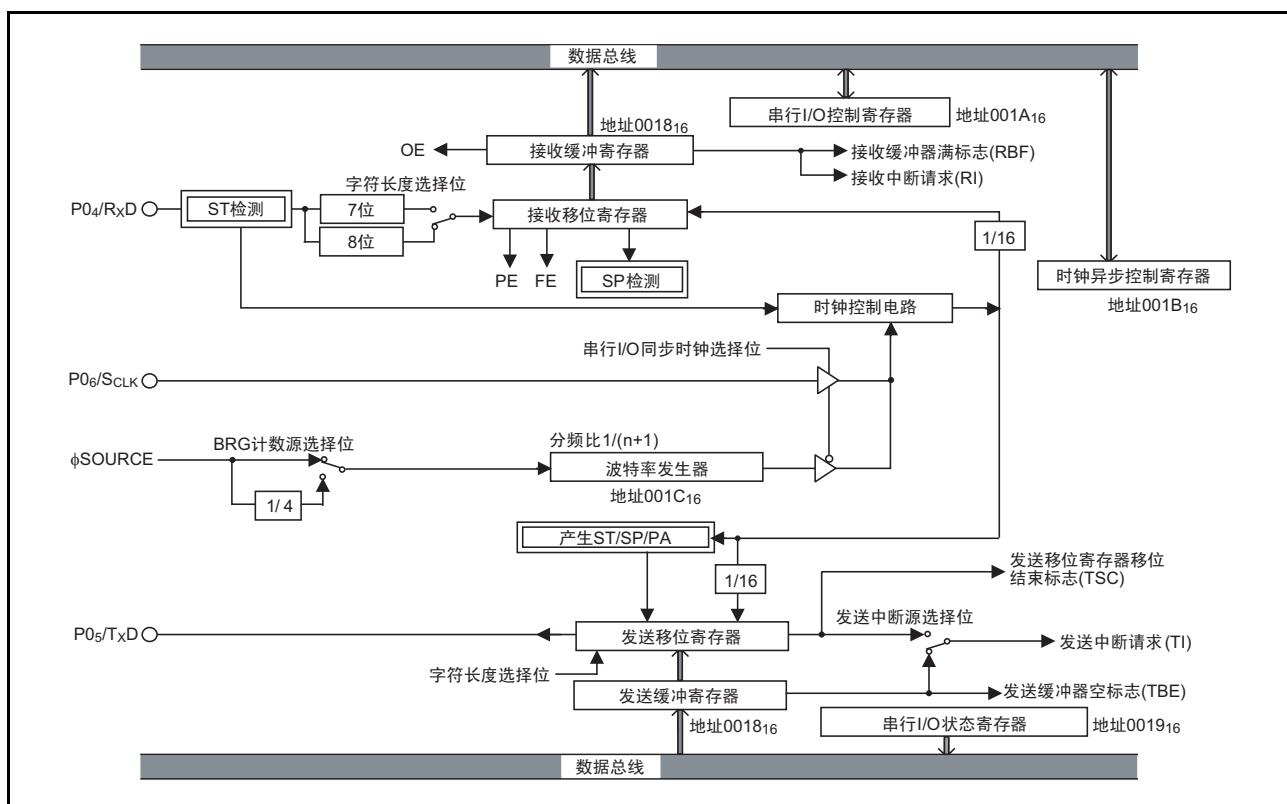

7548 群进行串行数据发送、接收的发送移位寄存器、接收移位寄存器具有各自的缓冲寄存器（存储器中的地址相同）。由于不可直接读写移位寄存器，因此对各自缓冲寄存器写入发送数据和读取接收数据。另外，可通过这些缓冲寄存器，预先写入下一个应发送的数据，也可连续接收 2 字节的接收数据。

图 48 时钟异步串行 I/O 框图

图 49 时钟异步串行 I/O 运行图

**【发送缓冲寄存器 / 接收缓冲寄存器】 TB/RB**

发送缓冲寄存器与接收缓冲寄存器配置在相同地址，发送缓冲寄存器为只写寄存器，接收缓冲寄存器为只读寄存器。另外，字符位长为 7 位时，保存至接收缓冲寄存器的接收数据的 MSB 为“0”。

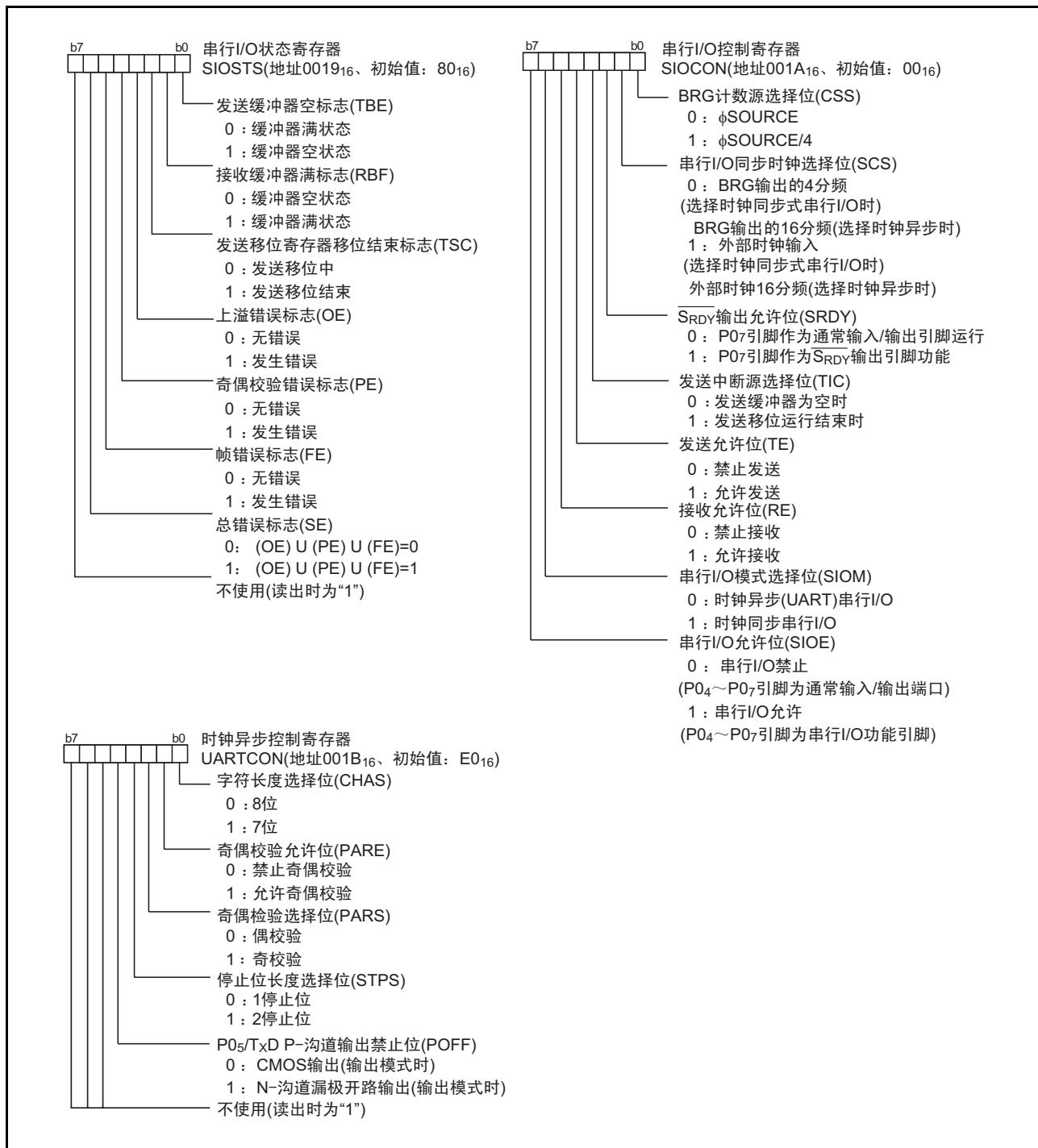

**【串行 I/O 状态寄存器】 SIOSTS**

本寄存器是由表示串行 I/O 运行状态的标志及各种错误标志构成的 7 位只读寄存器。bit4 ~ bit6 的 3 位仅在选择时钟异步模式时有效。

读取接收缓冲寄存器的内容时，接收缓冲器满标志清“0”。

将数据从接收移位寄存器传送至接收缓冲寄存器，与接收缓冲器满标志被设定的同时，进行错误检测。通过向串行 I/O 状态寄存器的写入，即可清除所有错误标志（OE、PE、FE、SE）。另外，如果给串行 I/O 允许位（SIOE）写入“0”，含错误标志的所有状态标志均被清“0”。

复位时，此寄存器的 bit0 ~ bit6 初始化为“0”，但是，将串行 I/O 控制寄存器的发送允许位置“1”时，bit2 与 bit0 变为“1”。

**【串行 I/O 控制寄存器】 SIOCON**

串行 I/O 控制寄存器由进行串行 I/O 各种控制的 8 位选择位构成。

**【时钟异步控制寄存器】 UARTCON**

本寄存器是由选择时钟异步时有效的 4 位控制位与总是有效的 1 位控制位构成的 5 位寄存器。通过此寄存器的内容，设定发送 / 接收串行数据时的数据格式、P05/TxD 引脚的输出形式等。

**【波特率发生器】 BRG**

波特率发生器决定串行传送的位速率。

是具有重加载寄存器的 8 位计数器，通过设定值 n，以  $1/(n+1)$  的分频比分频计数源。

## 注意事项

### 串行 I/O 中断

将串行 I/O 发送允许位置 “1” 时，串行 I/O 发送中断请求位变为 “1”。当无需产生与发送允许同步的中断时，请按以下顺序设定：

- ① 将串行 I/O 发送中断允许位置 “0”（禁止）。

- ② 将发送允许位置 “1”。

- ③ 执行至少一条指令后，将串行 I/O 发送中断请求位置 “0”。

- ④ 将串行 I/O 发送中断允许位置 “1”（允许）。

### 串行 I/O 允许时的输入 / 输出引脚功能

根据串行 I/O 模式选择位及串行 I/O 同步时钟选择位的设定值，P0<sub>6</sub>、P0<sub>7</sub> 的功能发生如下变化：

- (1) 串行 I/O 模式选择位 → “1”：

选择时钟同步串行 I/O 时

- 串行 I/O 同步时钟选择位的设定

- “0”：P0<sub>6</sub> 引脚为同步时钟输出引脚。

- “1”：P0<sub>6</sub> 引脚为同步时钟输入引脚。

- $\bar{SRDY}$  输出允许位（SRDY）的设定

- “0”：P0<sub>7</sub> 引脚可作为通常输入/输出引脚使用。

- “1”：P0<sub>7</sub> 引脚为  $\bar{SRDY}$  输出引脚。

- (2) 串行 I/O 模式选择位 → “0”：

选择时钟异步（UART）串行 I/O 时，

- 串行 I/O 同步时钟选择位的设定

- “0”：P0<sub>6</sub> 引脚可作为通常输入/输出引脚使用。

- “1”：P0<sub>6</sub> 引脚为外部时钟输入引脚。

- 选择时钟异步（UART）串行 I/O 时，P0<sub>7</sub> 引脚可作为通常输入/输出引脚使用。

图 50 串行 I/O 相关寄存器的结构

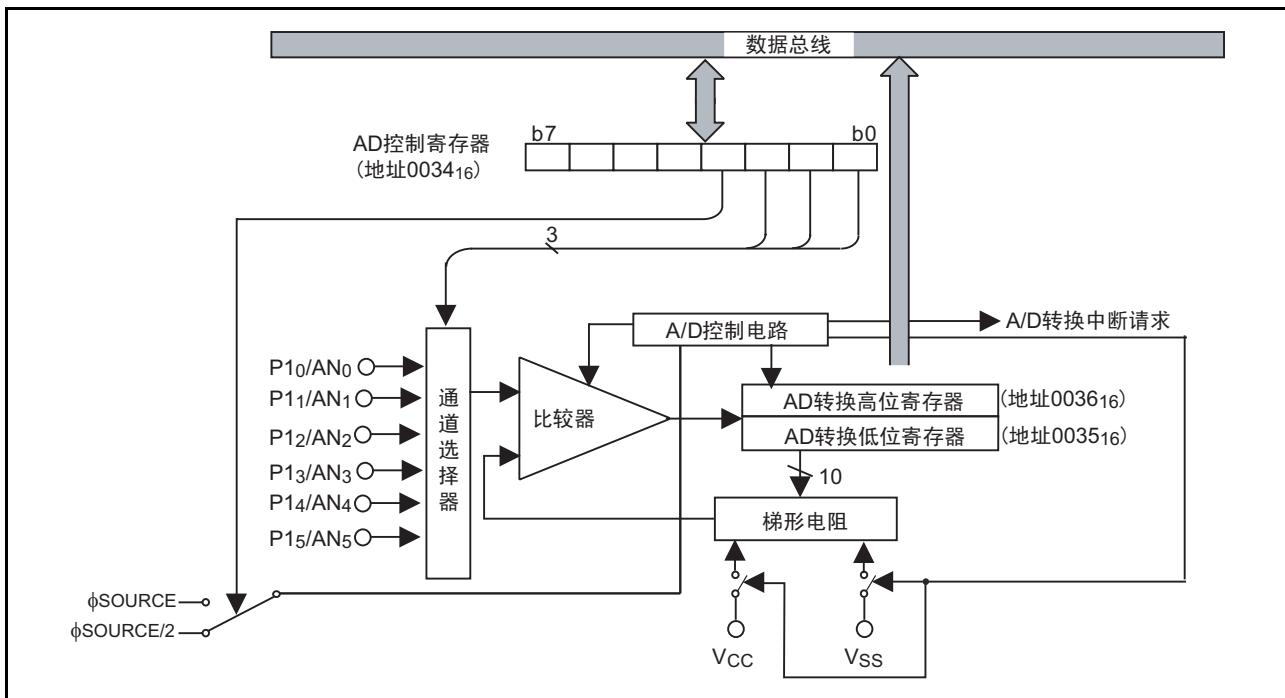

## A/D 转换器

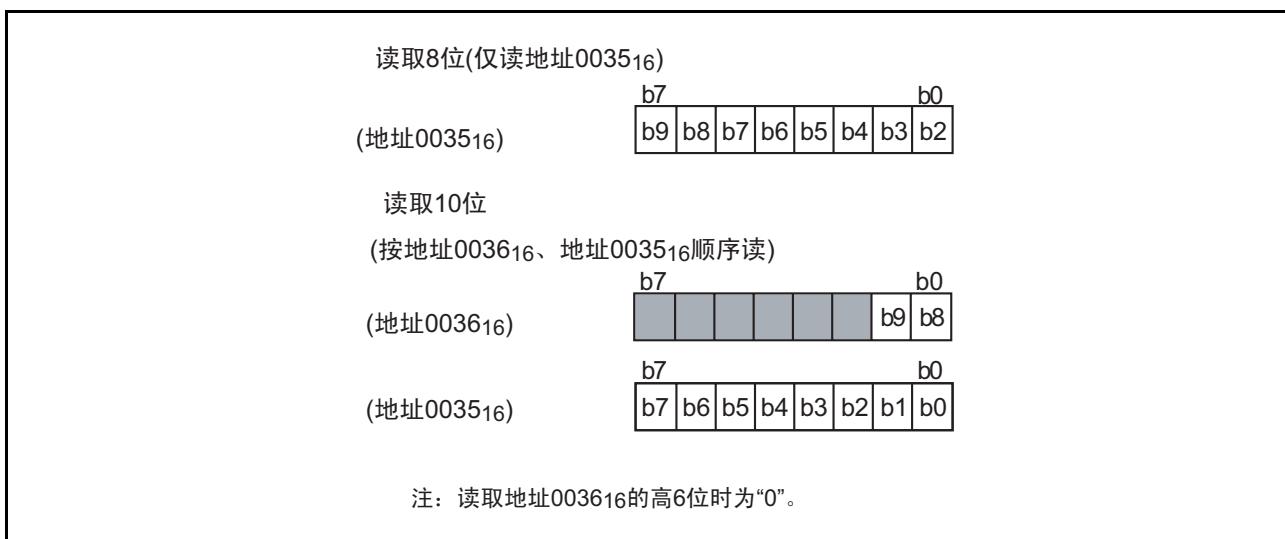

### 【AD 转换寄存器】 AD

本寄存器为保存 A/D 转换结果的只读寄存器。

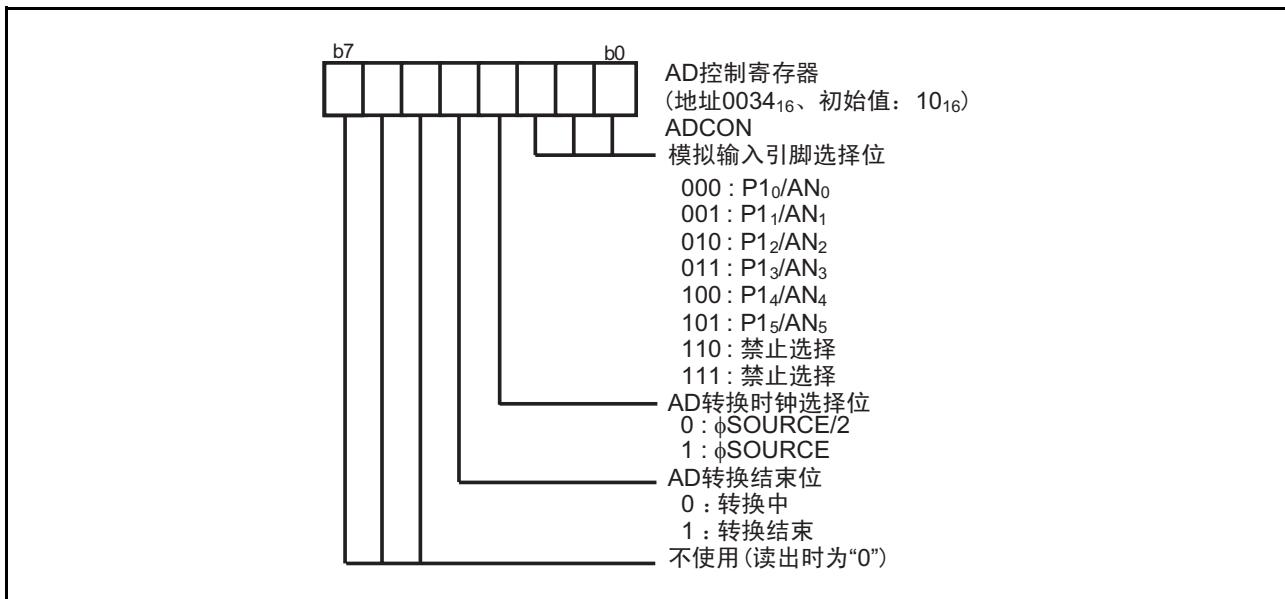

### 【AD 控制寄存器】 ADCON

本寄存器为控制 A/D 转换器的寄存器。

bit2 ~ bit0 为模拟输入引脚的选择位。

bit3 为 AD 转换时钟选择位，如果置“0”，AD 转换时钟为  $\phi_{SOURCE}/2$ ，AD 转换时间为  $\phi_{SOURCE}$  的 122 个周期。如果置“1”，A/D 转换时钟为  $\phi_{SOURCE}$ ，AD 转换时间为  $\phi_{SOURCE}$  的 61 个周期。

bit4 为 AD 转换结束位，在 A/D 转换期间为“0”，如果 A/D 转换结束，成为“1”。通过向此位写入“0”，开始 A/D 转换。

### 【比较电压发生器】

通过梯形电阻，将 V<sub>SS</sub> 与 V<sub>CC</sub> 之间的电压分成 1024 份，进行分压输出。除 A/D 转换中外，由于与 V<sub>CC</sub> 引脚、V<sub>SS</sub> 引脚分离，因此电流未流通至梯形电阻。

### 【通道选择器】

从端口 P15/AN5 ~ P10/AN0 中选择 1 个通道，输入至比较器。

### 【比较器及控制电路】

进行模拟输入电压与比较电压的比较，将此结果保存至 AD 转换寄存器。另外，A/D 转换结束时，将 AD 转换结束位及 AD 转换中断请求位置“1”。由于比较器由电容耦合构成，因此设定  $\phi_{SOURCE}$  的值时必须使 A/D 转换中的 AD 转换时钟不低于 250kHz。

## 注意事项

以下使用条件下有时会降低 A/D 转换精度：

- (1) V<sub>CC</sub> 电压低于 3.0V 时，低温时的精度与常温时相比可能会大幅度下降。假设在低温下使用的系统，推荐在  $V_{CC} \geq 3.0V$  时使用。

- (2)  $\phi_{SOURCE}$  为 X<sub>CIN</sub>、低速内部振荡器时，不可使用 A/D 转换器。

图 51 AD 控制寄存器的结构

图 52 AD 转换寄存器的结构

图 53 A/D 转换器框图

## 看门狗定时器

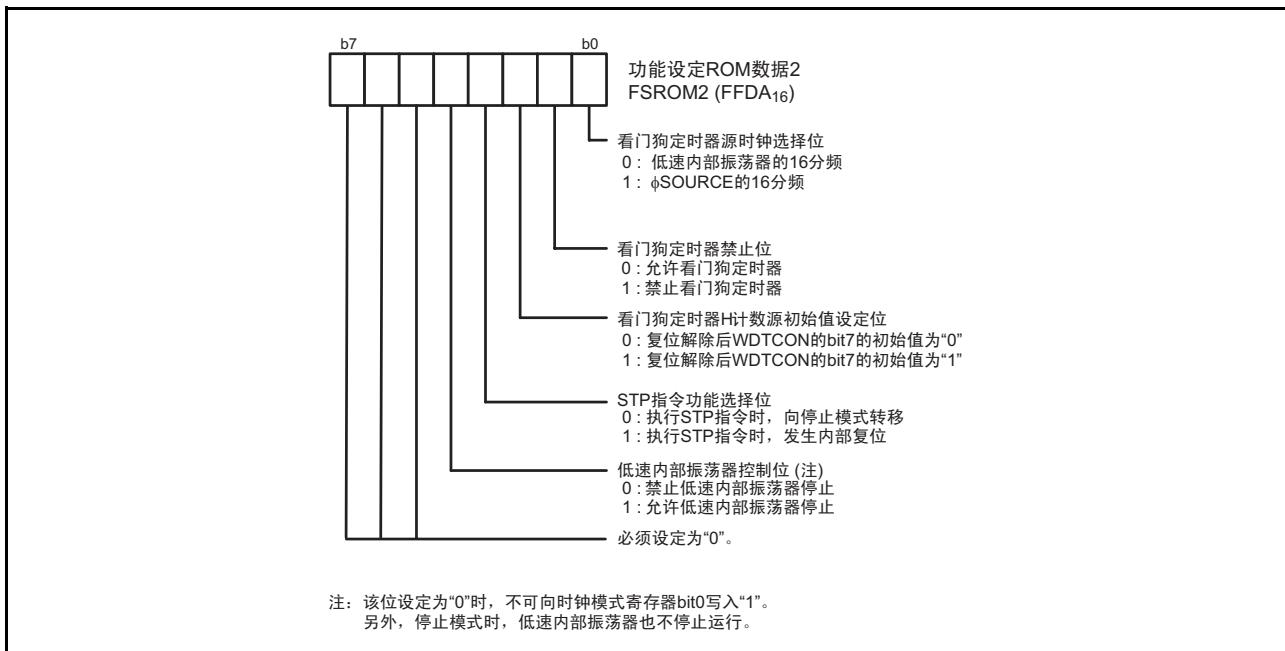

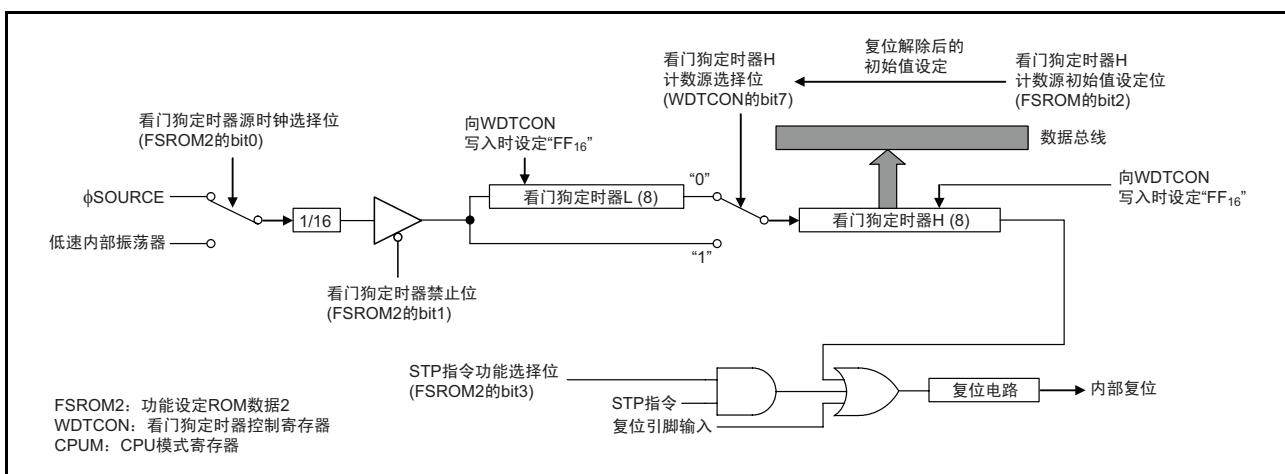

看门狗定时器提供因失控等原因使程序不能正常运行时返回复位状态的措施。看门狗定时器由 8 位看门狗定时器 H 与 8 位看门狗定时器 L（总计 16 位的递减计数器）构成。看门狗定时器的运行通过功能设定 ROM 数据 2 的 bit2 ~ 0 及看门狗定时器控制寄存器进行控制。

功能设定 ROM 数据 2 在 QzROM 区内并设定外围功能，不可通过执行指令进行改写。

### 看门狗定时器禁止位

看门狗定时器禁止位（功能设定 ROM 数据 2（FSROM2）的 bit1）设定为“0”时，看门狗定时器有效，复位解除后开始计数。

设定为“1”时，看门狗定时器不运行。

此位不可通过执行指令进行改写。

使用看门狗定时器时，必须将此位置“0”。

看门狗定时器在复位解除后不可通过程序开始计数。

### 看门狗定时器源时钟选择位

看门狗定时器的计数源时钟可通过看门狗定时器源时钟选择位（FSROM2 的 bit0）选择。

此位不可通过执行指令进行改写。

将看门狗定时器源时钟选择位置“0”时，总是为低速内部振荡器输出的 16 分频。

将看门狗定时器源时钟选择位置为“1”时，为  $\phi_{SOURCE}$  的 16 分频。 $\phi_{SOURCE}$  根据时钟选择位（时钟模式寄存器（地址 CLKM：0037<sub>16</sub>）的 bit5, 4）的设定而发生变化。

### 看门狗定时器 H 计数源选择位

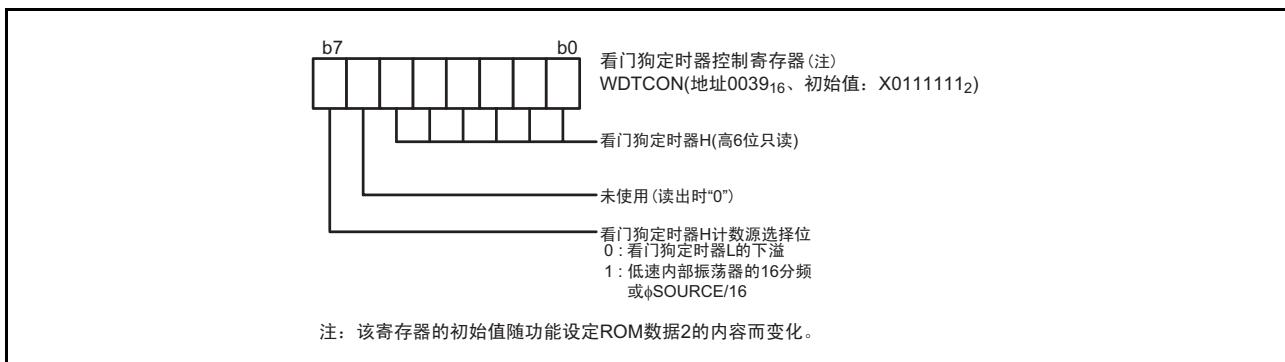

看门狗定时器 H 的计数源可通过看门狗定时器控制寄存器（地址 WDTCON：0039<sub>16</sub>）选择。

将看门狗定时器 H 计数源选择位（WDTCON 的 bit7）置“0”时，看门狗定时器 H 的计数源为看门狗定时器 L 的下溢信号。

置“1”时，将看门狗定时器 L 的计数源所选的时钟输入至看门狗定时器 H。

可通过 FSROM2 的 bit2 设定此位复位解除后的初始值。

### 看门狗定时器的运行

通过复位或向 WDTCON 写入任意数据，看门狗定时器 H 为“FF<sub>16</sub>”，如果看门狗定时器 L 为“FF<sub>16</sub>”。如果看门狗定时器开始运行，就对所选时钟计数。由于看门狗定时器 H 的下溢而发生内部复位，因此，通常如下编程：下溢前，对 WDTCON 进行写入操作。

读取 WDTCON 时，读取看门狗定时器 H 计数器的高 6 位、看门狗定时器 H 计数源选择位的值。

向看门狗定时器控制寄存器执行写入后，看门狗定时器到发生下溢前的时间如下所示：

以作为  $\phi_{SOURCE}$  选择 X<sub>IN</sub> 输入时钟、f(X<sub>IN</sub>)=8MHz 时为例。

- 看门狗定时器 H 计数源选择位 = “0”时：131.072ms

- 看门狗定时器 H 计数源选择位 = “1”时：512μs

图 54 功能设定 ROM 数据 2 的结构

图 55 看门狗定时器控制寄存器的结构

图 56 看门狗定时器的框图

## 注意事项

(1) 等待模式时，看门狗定时器运行，为了不发生下溢，向看门狗定时器控制寄存器写入。

停止模式时，看门狗定时器停止，但在解除停止模式的同时开始计数。解除停止模式后的等待振荡稳定时间仍进行计数。

在此期间，为了不发生下溢，执行 STP 指令前，将 WDTCON 的看门狗定时器 H 计数源选择位（bit7）置“0”。

以下 2 种条件下，即使执行 STP 指令时，看门狗定时器仍继续计数。

① 低速部振荡器的停止：禁止(FSROM2 的 bit4 )

看门狗定时器的源时钟：低速内部振荡器的 16 分频(FSROM2 的 bit0 )

② 低速内部振荡器的停止：禁止(FSROM2 的 bit4)

看门狗定时器的源时钟： $\phi$ SOURCE(FSROM2 的 bit0)

$\phi$ SOURCE：低速内部振荡器(时钟模式寄存器的 bit5、4)

(2) STP 指令功能选择位

STP 指令的功能可通过 FSROM2 的 bit3 选择。此位不可通过执行指令进行改写。

- 此位为“0”时，如果执行 STP 指令，转移至停止模式。

- 此位为“1”时，如果执行 STP 指令，产生内部复位。

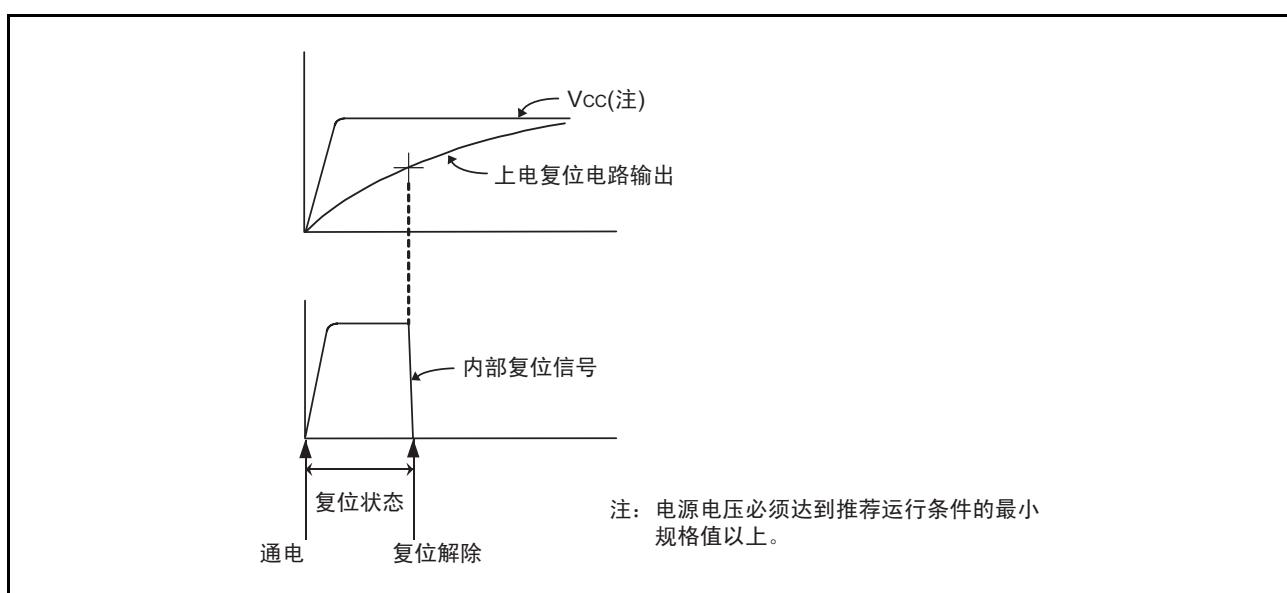

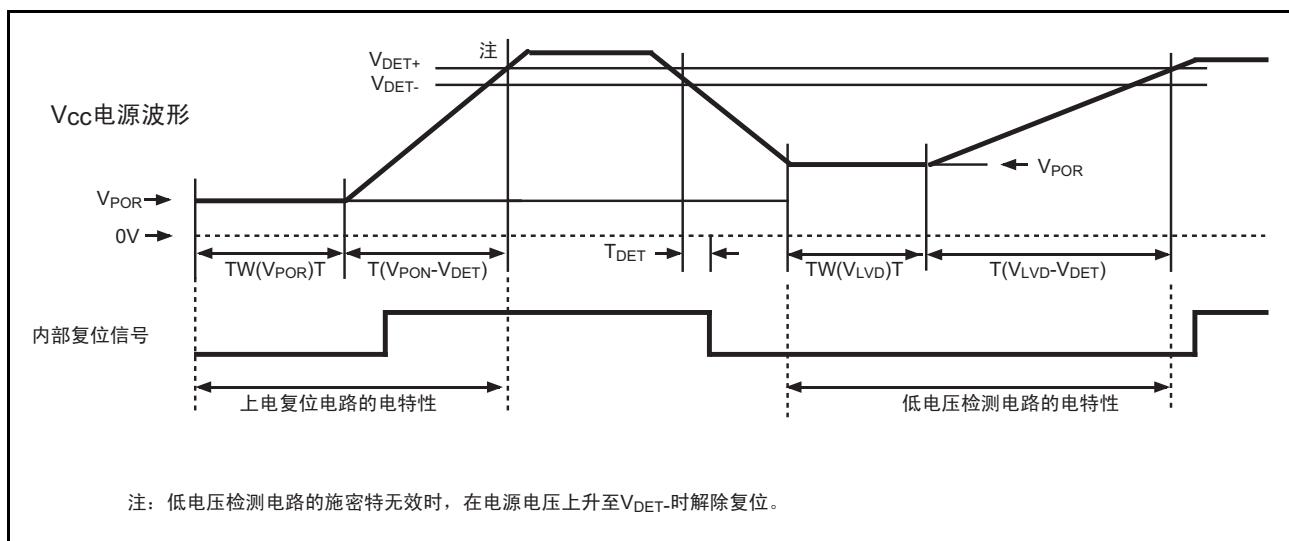

## 上电复位电路

本产品通过内部上电复位电路，通电时，自动进行系统复位（上电复位）。使用内部上电复位电路时，必须使 RESET 引脚开路（RESET 引脚内置上拉电阻）。

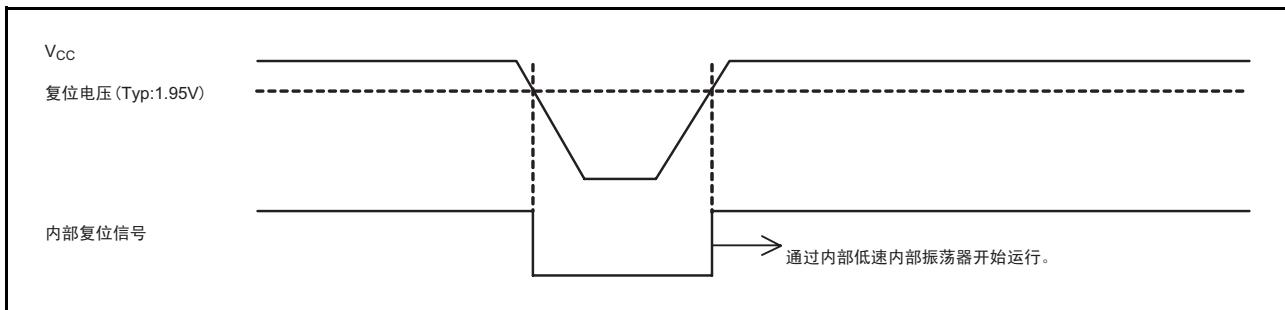

## 低电压检测电路

本产品内置低电压检测电路，该检测电路监视运行中的电源电压，电源电压降低至规定值以下 (Typ:1.95V) 时，对单片机进行系统复位。

通过将功能设定 ROM 数据 0 的 bit0 设定为“1”，使低电压检测电路有效。

另外，通过将功能设定 ROM 数据 1 的 bit2 设定为“1”，即使在停止模式下，也可使低电压检测电路有效；在此位设定为“0”的情况下，执行 STP 指令时，低电压检测电路停止工作，降低消耗电流。

图 58 低电压检测电路的运行波形图

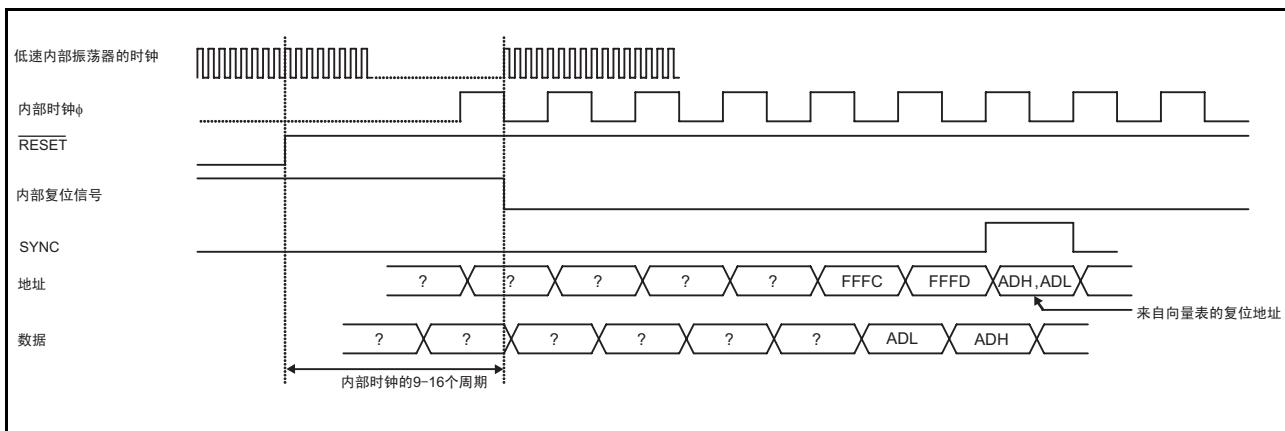

图 59 复位时的时序图

|      |                       |                    |                                    |

|------|-----------------------|--------------------|------------------------------------|

| (1)  | 端口P0方向寄存器(P0D)        | 0001 <sub>16</sub> | 00 <sub>16</sub>                   |

| (2)  | 端口P1方向寄存器(P1D)        | 0003 <sub>16</sub> | 00 <sub>16</sub>                   |

| (3)  | 端口 P2 方向寄存器 (P2D)     | 0005 <sub>16</sub> | 00 <sub>16</sub>                   |

| (4)  | 端口 P3 方向寄存器 (P3D)     | 0007 <sub>16</sub> | 00 <sub>16</sub>                   |

| (5)  | 端口 P0 驱动能力控制寄存器(DCCR) | 000C <sub>16</sub> | 00 <sub>16</sub>                   |

| (6)  | 端口P0上拉控制寄存器(PULL0)    | 000D <sub>16</sub> | 00 <sub>16</sub>                   |

| (7)  | 端口P1上拉控制寄存器(PULL1)    | 000E <sub>16</sub> | 00 <sub>16</sub>                   |

| (8)  | 键唤醒输入选择寄存器(KEYS)      | 000F <sub>16</sub> | 00 <sub>16</sub>                   |

| (9)  | 捕捉/比较寄存器(低位) (CRAL)   | 0010 <sub>16</sub> | 00 <sub>16</sub>                   |

| (10) | 捕捉/比较寄存器(高位) (CRAH)   | 0011 <sub>16</sub> | 00 <sub>16</sub>                   |

| (11) | 捕捉/比较寄存器RW指针(CCRP)    | 0012 <sub>16</sub> | 00 <sub>16</sub>                   |

| (12) | 比较输出模式寄存器(CMOM)       | 0013 <sub>16</sub> | 00 <sub>16</sub>                   |

| (13) | 定时器A (低位) (TAL)       | 0014 <sub>16</sub> | FF <sub>16</sub>                   |

| (14) | 定时器A (高位) (TAH)       | 0015 <sub>16</sub> | FF <sub>16</sub>                   |

| (15) | 串行I/O 状态寄存器(SIOSTS)   | 0019 <sub>16</sub> | 1   0   0   0   0   0   0   0   0  |

| (16) | 串行I/O 控制寄存器(SIOCON)   | 001A <sub>16</sub> | 00 <sub>16</sub>                   |

| (17) | 时钟异常控制寄存器(UARTCON)    | 001B <sub>16</sub> | 1   1   1   0   0   0   0   0   0  |

| (18) | 预分频器12 (PRE12)        | 0028 <sub>16</sub> | FF <sub>16</sub>                   |

| (19) | 定时器1(T1)              | 0029 <sub>16</sub> | 0   0   0   0   0   0   0   0   1  |

| (20) | 定时器2(T2)              | 002A <sub>16</sub> | FF <sub>16</sub>                   |

| (21) | 定时器模式寄存器(TM)          | 002B <sub>16</sub> | 00 <sub>16</sub>                   |

| (22) | 定时器计数源设定寄存器(TCSS)     | 002C <sub>16</sub> | 00 <sub>16</sub>                   |

| (23) | 比较设定值重加载寄存器(CMPR)     | 002D <sub>16</sub> | 00 <sub>16</sub>                   |

| (24) | 捕捉/比较端口寄存器(CCPR)      | 002E <sub>16</sub> | 00 <sub>16</sub>                   |

| (25) | 比较/捕捉状态寄存器(CCSR)      | 002F <sub>16</sub> | 00 <sub>16</sub>                   |

| (26) | 比较中断源设定寄存器(CISR)      | 0030 <sub>16</sub> | 00 <sub>16</sub>                   |

| (27) | 捕捉软件触发寄存器(CSTR)       | 0031 <sub>16</sub> | 00 <sub>16</sub>                   |

| (28) | 捕捉模式寄存器(CAPM)         | 0032 <sub>16</sub> | 00 <sub>16</sub>                   |

| (29) | AD控制寄存器(ADCON)        | 0034 <sub>16</sub> | 0   0   0   1   0   0   0   0   0  |

| (30) | 时钟模式寄存器(CLKM)         | 0037 <sub>16</sub> | 0   0   0   0   0   0   0   1   0  |

| (31) | 振荡停止检测寄存器(CLKSTP)     | 0038 <sub>16</sub> | 00 <sub>16</sub>                   |

| (32) | 看门狗定时器控制寄存器(WDTCON)   | 0039 <sub>16</sub> | 注4   0   1   1   1   1   1   1   1 |

| (33) | 中断边沿选择寄存器(INTEDGE)    | 003A <sub>16</sub> | 00 <sub>16</sub>                   |

| (34) | CPU模式寄存器(CPUM)        | 003B <sub>16</sub> | 00 <sub>16</sub>                   |

| (35) | 中断请求寄存器1 (IREQ1)      | 003C <sub>16</sub> | 00 <sub>16</sub>                   |

| (36) | 中断请求寄存器2 (IREQ2)      | 003D <sub>16</sub> | 00 <sub>16</sub>                   |

| (37) | 中断控制寄存器1 (ICON1)      | 003E <sub>16</sub> | 00 <sub>16</sub>                   |

| (38) | 中断控制寄存器2 (ICON2)      | 003F <sub>16</sub> | 00 <sub>16</sub>                   |

注1: X为不定。

注2: 上述以外寄存器及RAM的内容因复位时不定, 请设定初始值。

注3: 不要进行SFR保留区的存储器存取。

注4: 根据功能设定ROM数据2(FSROM2)的设定值, 复位后的初始值发生变化。

图 60 复位时的内部状态

## 时钟产生电路

时钟电路有可使用陶瓷振荡或晶振的 X<sub>IN</sub> 时钟、可使用 32kHz 晶振的 X<sub>CIN</sub> 时钟、外部时钟输入、高速内部振荡器、低速内部振荡器。

时钟引脚为端口、X<sub>IN</sub> 振荡、X<sub>CIN</sub> 振荡兼用的 P2<sub>0</sub>/X<sub>OUT</sub>/X<sub>COUT</sub> 引脚、P2<sub>1</sub>/X<sub>IN</sub>/X<sub>CIN</sub> 引脚。

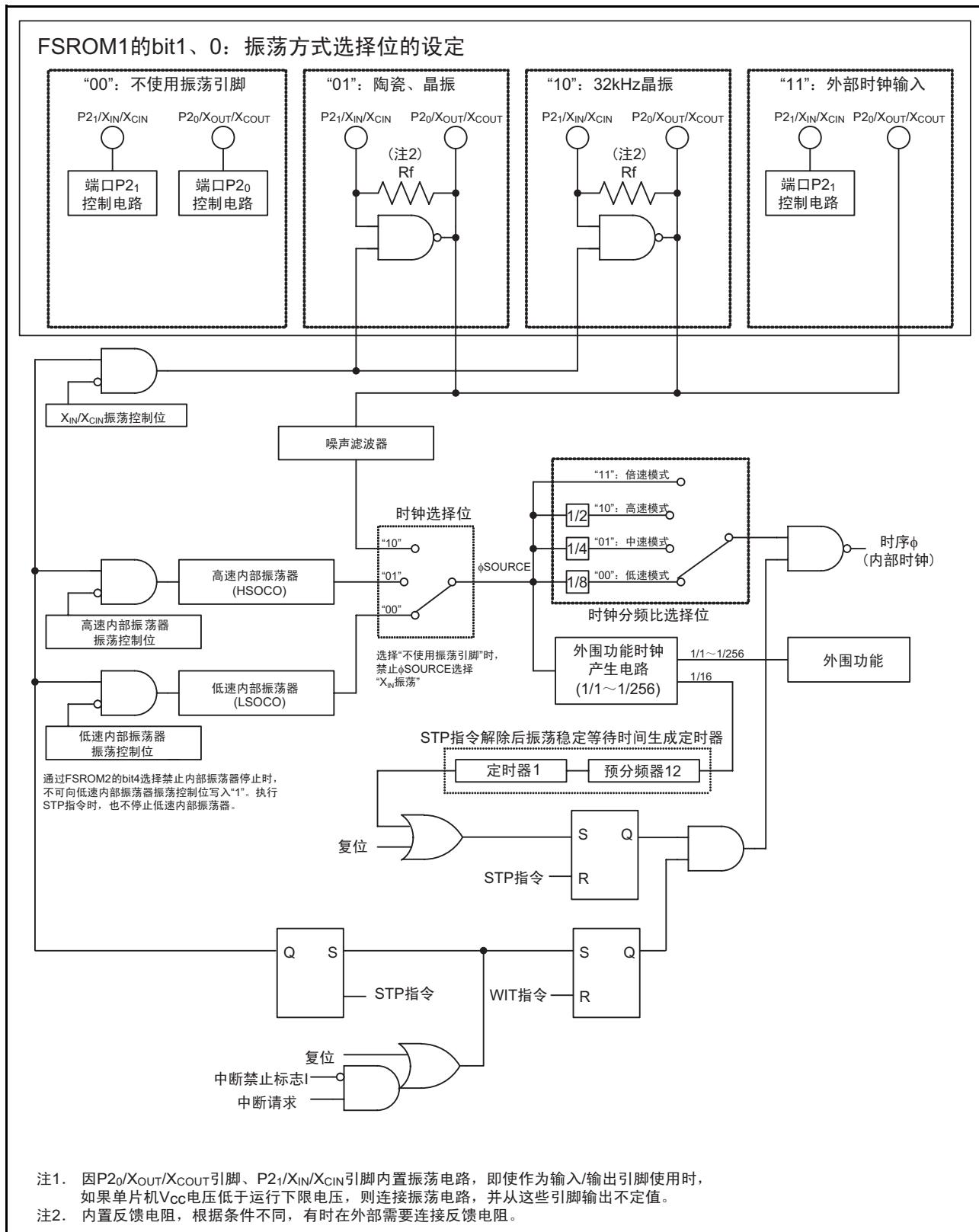

通过振荡方式选择位（功能设定 ROM 数据 1（FSROM1）的 bit1、0），设定该引脚的功能。

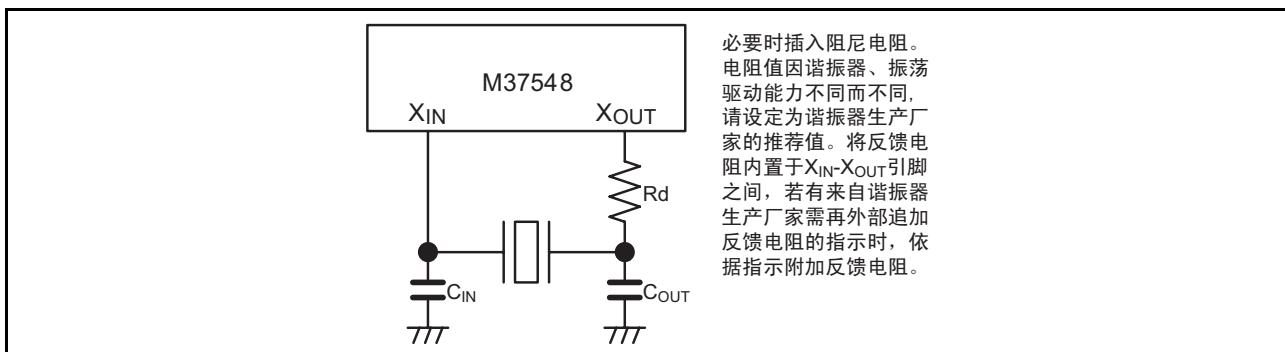

### 陶瓷振荡或晶振

将振荡方式选择位（FSROM1 的 bit1、0）设定为“01<sub>2</sub>”，并将陶瓷谐振器（或晶体谐振器）以最短的距离与外部电路连接。

振荡电路的各常数因谐振器不同而有所不同，因此请使用谐振器生产厂家的推荐值。

内置反馈电阻（根据条件，有时需外接反馈电阻）。

将 X<sub>IN</sub>/X<sub>CIN</sub> 振荡控制位设定为“0”时，开始振荡。此位复位后为“0”。

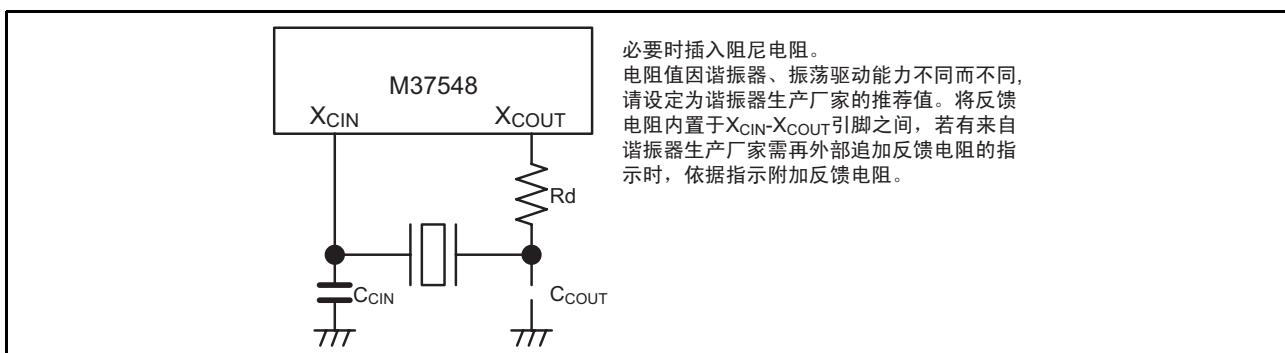

### 32kHz 晶振

将振荡方式选择位（FSROM1 的 bit1、0）设定为“10<sub>2</sub>”，并将 32kHz 晶体谐振器以最短的距离与外部电路连接。

振荡电路的各常数因谐振器不同而有所不同，因此请使用谐振器生产厂家的推荐值。

内置反馈电阻（根据条件，有时需外接反馈电阻）。

将 X<sub>IN</sub>/X<sub>CIN</sub> 振荡控制位设定为“0”时，开始振荡。此位复位后为“0”。

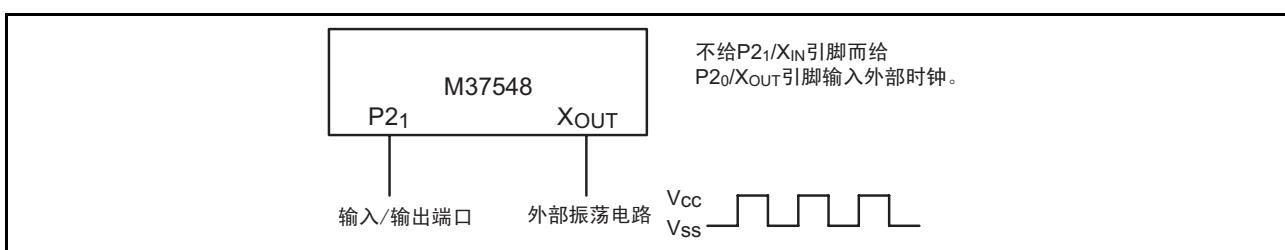

### 外部时钟输入

将振荡方式选择位设定为“11<sub>2</sub>”，并将时钟产生源连接至 P2<sub>0</sub>/X<sub>OUT</sub> 引脚。此时，P2<sub>1</sub>/X<sub>IN</sub> 引脚可以作为输入 / 输出端口使用。

### 高速内部振荡器

高速内部振荡器复位后，处于停止状态。

将高速内部振荡器振荡控制位（CLKM 的 bit1）设定为“0”时，开始振荡。此位复位后为“1”。

### 低速内部振荡器

低速内部振荡器复位后，自动开始振荡。

低速内部振荡器振荡控制位（CLKM 的 bit0）设定为“1”时，停止振荡。此位在复位后为“0”。

低速内部振荡器控制位（FSROM2 的 bit4）设定为“0”，而且设定禁止低速内部振荡器的停止时，就不能将低速内部振荡器振荡控制位设定为“1”，也不可停止低速内部振荡器的振荡。另外，即使执行 STP 指令时，也不停止低速内部振荡器。

### 不使用振荡引脚（P2<sub>0</sub>、P2<sub>1</sub> 为输入 / 输出端口）

仅使用内置内部振荡器时，如果将振荡方式选择位设定为“00<sub>2</sub>”，则可将 P2<sub>0</sub>/X<sub>OUT</sub> 引脚作为输出端口、P2<sub>1</sub>/X<sub>IN</sub> 引脚作为输入 / 输出端口使用。

图 61 功能设定 ROM 数据 1 的结构

图 62 陶瓷谐振器，晶体谐振器外接电路

图 63 32kHz 晶体谐振器外接电路

图 64 外部时钟输入电路

图 65 时钟模式寄存器的结构

### 注意事项

- 向XIN振荡 / XCIN振荡的切换

复位解除后，低速内部振荡器开始运行。将φSOURCE向XIN振荡 / XCIN振荡切换时，请在XIN振荡 / XCIN振荡稳定之前，通过内部振荡器设定等待时间。

## 振荡控制

### 时钟模式寄存器

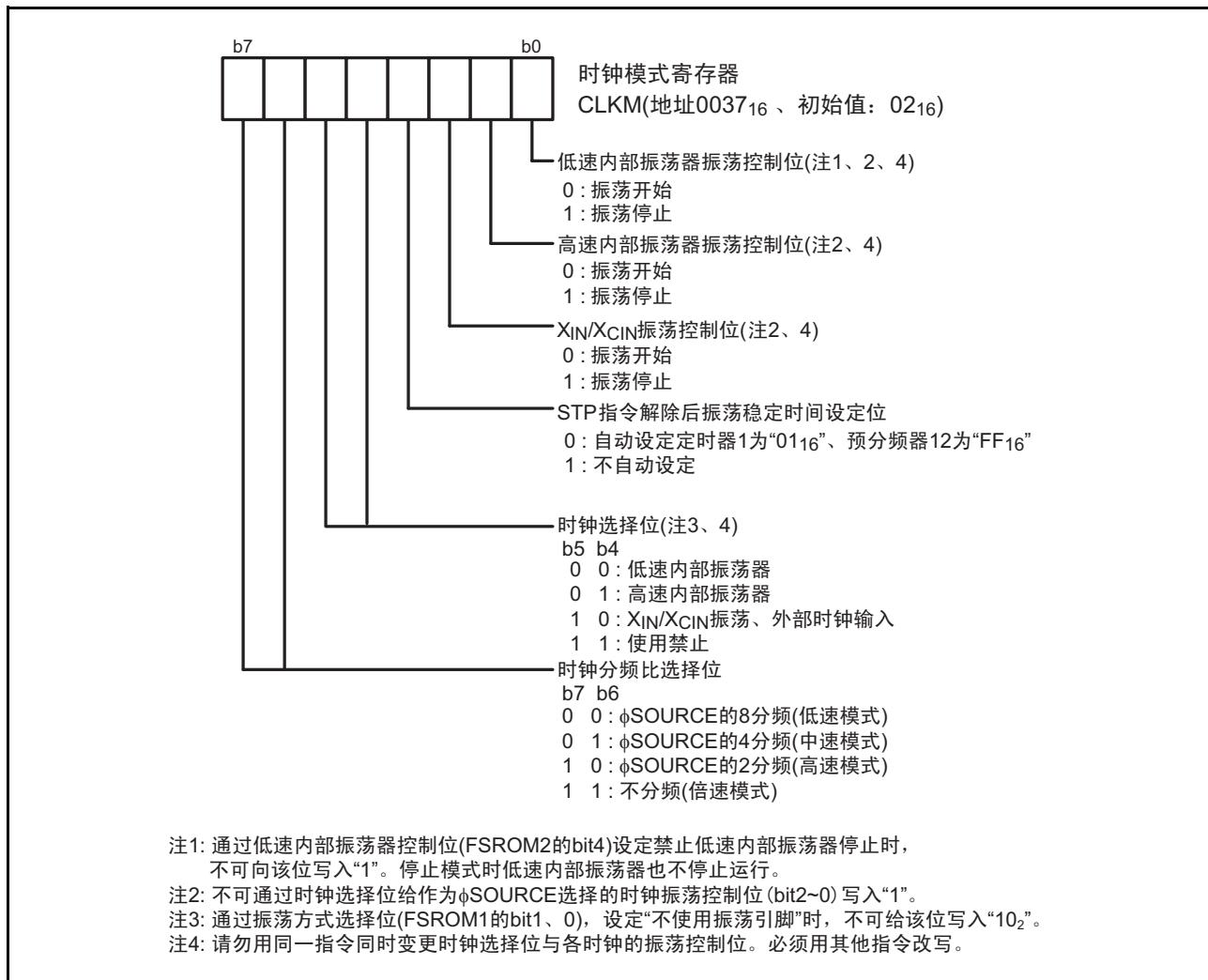

时钟模式寄存器包含各振荡电路的振荡控制位、时钟选择位等。

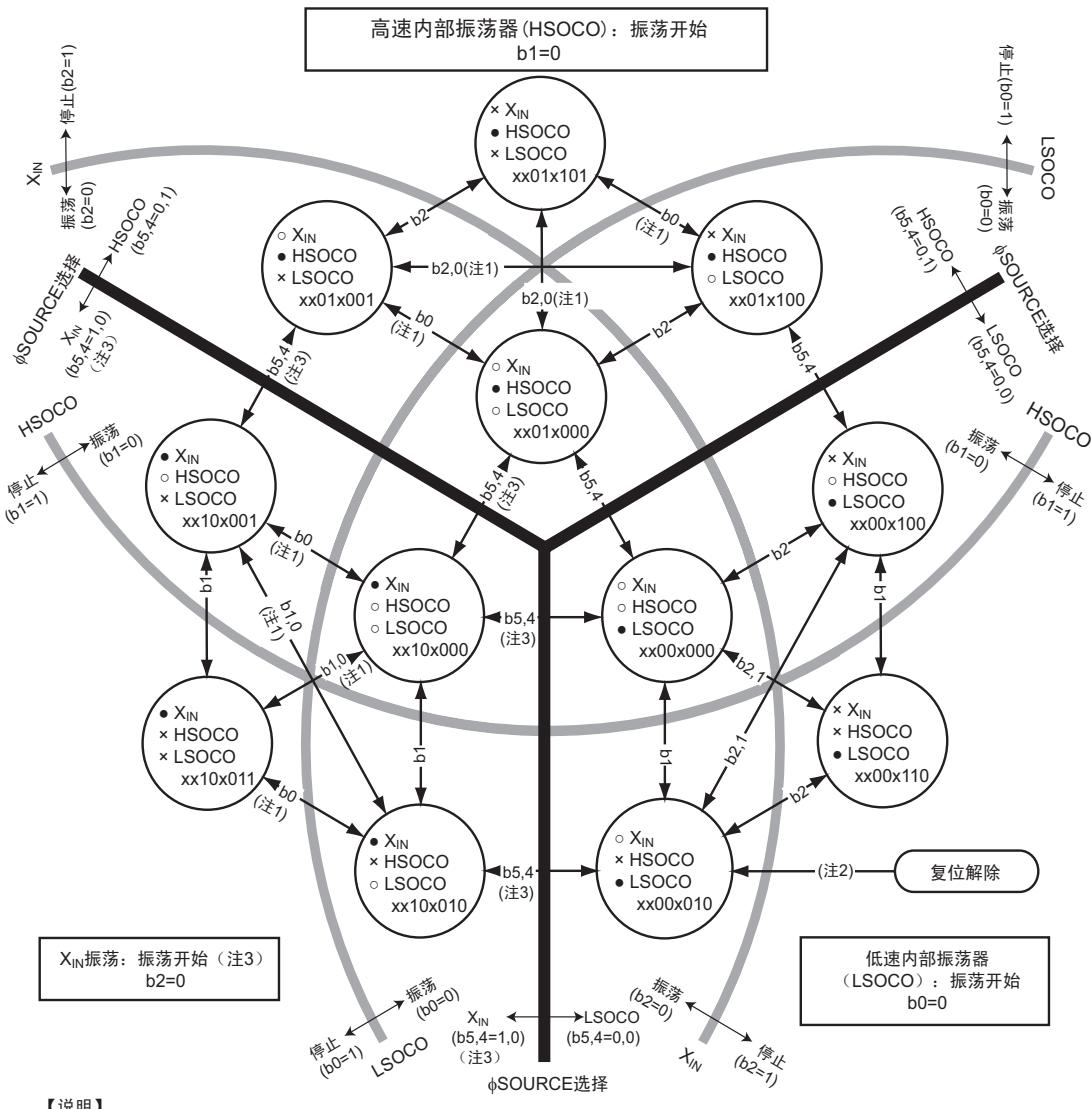

### 时钟选择位

$\phi$ SOURCE 可通过时钟选择位（CLKM 的 bit5、4）进行选择。

通过时钟选择位，作为  $\phi$ SOURCE 可选择低速内部振荡器、高速内部振荡器、X<sub>IN</sub>/X<sub>CIN</sub> 振荡或外部时钟输入。

$\phi$ SOURCE 也可作为外围功能用的时钟使用。

作为振荡方式选择位（FSROM1 的 bit1、0）设定为“00<sub>2</sub>”（不使用振荡引脚）时，不可将时钟选择位设定为“10<sub>2</sub>”（X<sub>IN</sub> / X<sub>CIN</sub> 振荡、外部时钟输入）。

### 时钟分频比选择位

内部时钟  $\phi$  通过分频  $\phi$ SOURCE 生成。通过时钟分频比选择位（CLKM 的 bit7、6）选择分频比。

分频比有 8 分频（低速模式）、4 分频（中速模式）、2 分频（高速模式）、无分频（倍速模式）几种。

各分频（模式）的设定如表 9 所示。

复位解除时，将低速内部振荡器作为  $\phi$ SOURCE，并选择将  $\phi$ SOURCE/8 分频作为内部时钟  $\phi$ 。

此时，高速内部振荡器处于停止状态。另外，将振荡电路连接至时钟引脚时，开始振荡。

$\phi$ SOURCE 向 X<sub>IN</sub> 振荡 / X<sub>CIN</sub> 振荡切换时，请在 X<sub>IN</sub> / X<sub>CIN</sub> 振荡稳定之前，通过内部振荡器生成等待时间。

表 9 时钟分频（模式）的设定

| φSOURCE          | 位<br>模式 | CLKM     |        |               |              |              | FSROM1  | FSROM2     |

|------------------|---------|----------|--------|---------------|--------------|--------------|---------|------------|

|                  |         | 时钟分频比选择位 | 时钟选择位  | XIN/XCIN振荡控制位 | 高速内部振荡器振荡控制位 | 低速内部振荡器振荡控制位 | 振荡方式选择位 | 低速内部振荡器控制位 |

|                  |         | bit7、6   | bit5、4 | bit2          | bit1         | bit0         | bit1、0  | bit4       |

| X <sub>IN</sub>  | 倍速      | 11       | 10     | 0             | —            | —            | 01      | —          |

|                  | 高速      | 10       | 10     | 0             | —            | —            | 01      | —          |

|                  | 中速      | 01       | 10     | 0             | —            | —            | 01      | —          |

|                  | 低速      | 00       | 10     | 0             | —            | —            | 01      | —          |

| X <sub>CIN</sub> | 倍速      | 11       | 10     | 0             | —            | —            | 10      | —          |

|                  | 高速      | 10       | 10     | 0             | —            | —            | 10      | —          |

|                  | 中速      | 01       | 10     | 0             | —            | —            | 10      | —          |

|                  | 低速      | 00       | 10     | 0             | —            | —            | 10      | —          |

| 外部时钟             | 倍速      | 11       | 10     | —             | —            | —            | 11      | —          |

|                  | 高速      | 10       | 10     | —             | —            | —            | 11      | —          |

|                  | 中速      | 01       | 10     | —             | —            | —            | 11      | —          |

|                  | 低速      | 00       | 10     | —             | —            | —            | 11      | —          |

| 高速内部振荡器          | 倍速      | 11       | 01     | —             | 0            | —            | —       | —          |

|                  | 高速      | 10       | 01     | —             | 0            | —            | —       | —          |

|                  | 中速      | 01       | 01     | —             | 0            | —            | —       | —          |

|                  | 低速      | 00       | 01     | —             | 0            | —            | —       | —          |

| 低速内部振荡器          | 倍速      | 11       | 00     | —             | —            | 0            | —       | 1/0        |

|                  | 高速      | 10       | 00     | —             | —            | 0            | —       | 1/0        |

|                  | 中速      | 01       | 00     | —             | —            | 0            | —       | 1/0        |

|                  | 低速      | 00       | 00     | —             | —            | 0            | —       | 1/0        |

—：无论是“0”还是“1”均无影响。

### 停止模式

执行 STP 指令时，内部时钟  $\phi$  在 “H” 状态下停止运行，XIN/XCIN、内部振荡器也停止振荡。此时，如果 STP 指令解除后振荡稳定时间设定位为 “0”，则定时器 1 设定为 “01<sub>16</sub>”，预分频器 12 设定为 “FF<sub>16</sub>”。相反，如果 STP 指令解除后振荡稳定时间设定位为 “1”，因为定时器 1 与预分频器 12 不作任何设定，所以请设定与所使用谐振器振荡稳定时间合适的等待时间。

接受外部中断时重新开始振荡，但在定时器 1 下溢之前，内部时钟  $\phi$  仍为 “H”。定时器 1 下溢后，开始提供内部时钟  $\phi$ 。这是因为使用陶瓷振荡等时，起振需要时间。通过复位重新振荡时，因为没有生成等待时间，所以必须在振荡稳定之前给  $\overline{\text{RESET}}$  引脚外加 “L” 电平或复位解除后在振荡稳定之前通过内部振荡器运行来设定等待时间。

### 等待模式

执行 WIT 指令时，内部时钟  $\phi$  在 “H” 状态下停止运行，但振荡器不停止运行。产生复位或接受中断时，内部时钟  $\phi$  的停止解除。因为振荡器并没有停止运行，所以可立即执行指令。

解除 STP 或 WIT 状态时，为了接受中断，需要在执行 STP 或 WIT 指令之前，将相应的中断允许位设定为 “1”。

### 注意事项

STP 指令解除后，将振荡稳定时间设定位设定为 “1”，使用时，必须在充分评价所使用振荡器的谐振稳定时间后，再设定定时器 1、预分频器 12 的值。

图 66 内部时钟  $\phi$  产生电路框图

时钟模式寄存器CLKM(地址0037<sub>16</sub>)的设定值与时钟的状态转移图

(X<sub>IN</sub>振荡时、X<sub>CIN</sub>振荡、外部时钟输入时也一样)

模式的转移沿着箭头进行。可从所有的模式转移至等待模式、停止模式，恢复时返回至原来模式。

#### 等待模式时

- 低速内部振荡器：保持执行WIT指令前的状态

- 高速内部振荡器：保持执行WIT指令前的状态

- X<sub>IN</sub>振荡：维持执行WIT指令前状态

#### 停止模式时

- 低速内部振荡器：停止(注1)

- 高速内部振荡器：停止

- X<sub>IN</sub>振荡：停止

1. 通过低速内部振荡器控制位(FSROM2的bit4)设定禁止低速内部振荡器停止时，不可给CLKM的bit0写入“1”。即使为停止模式时，低速内部振荡器也不停止。

2. 复位解除后，φSOURCE选择低速内部振荡器、内部时钟φ选择8分频模式。

3. 通过振荡方式选择位(FSROM1的bit1,0)设定不使用振荡引脚时，不可给CLKM的bit5,4写入“10”。φSOURCE使用X<sub>IN</sub>/X<sub>CIN</sub>振荡时，须在X<sub>IN</sub>/X<sub>CIN</sub>振荡稳定后进行转换。使用外部时钟时提供稳定时钟。

4. 请勿用同一指令同时变更CLKM的时钟选择位(bit5,4)与各时钟振荡控制位(bit2~bit0)的值。必须用其他指令改写。

5. 在转移到目标运行模式前，须在使用的振荡稳定后再转移。

图 67 φSOURCE 状态转移图

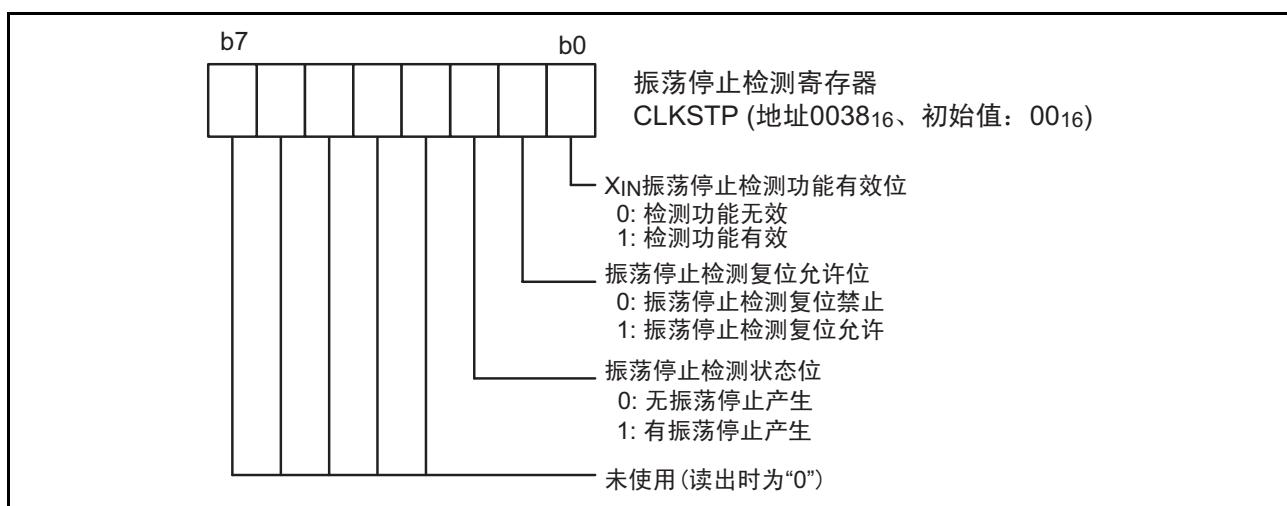

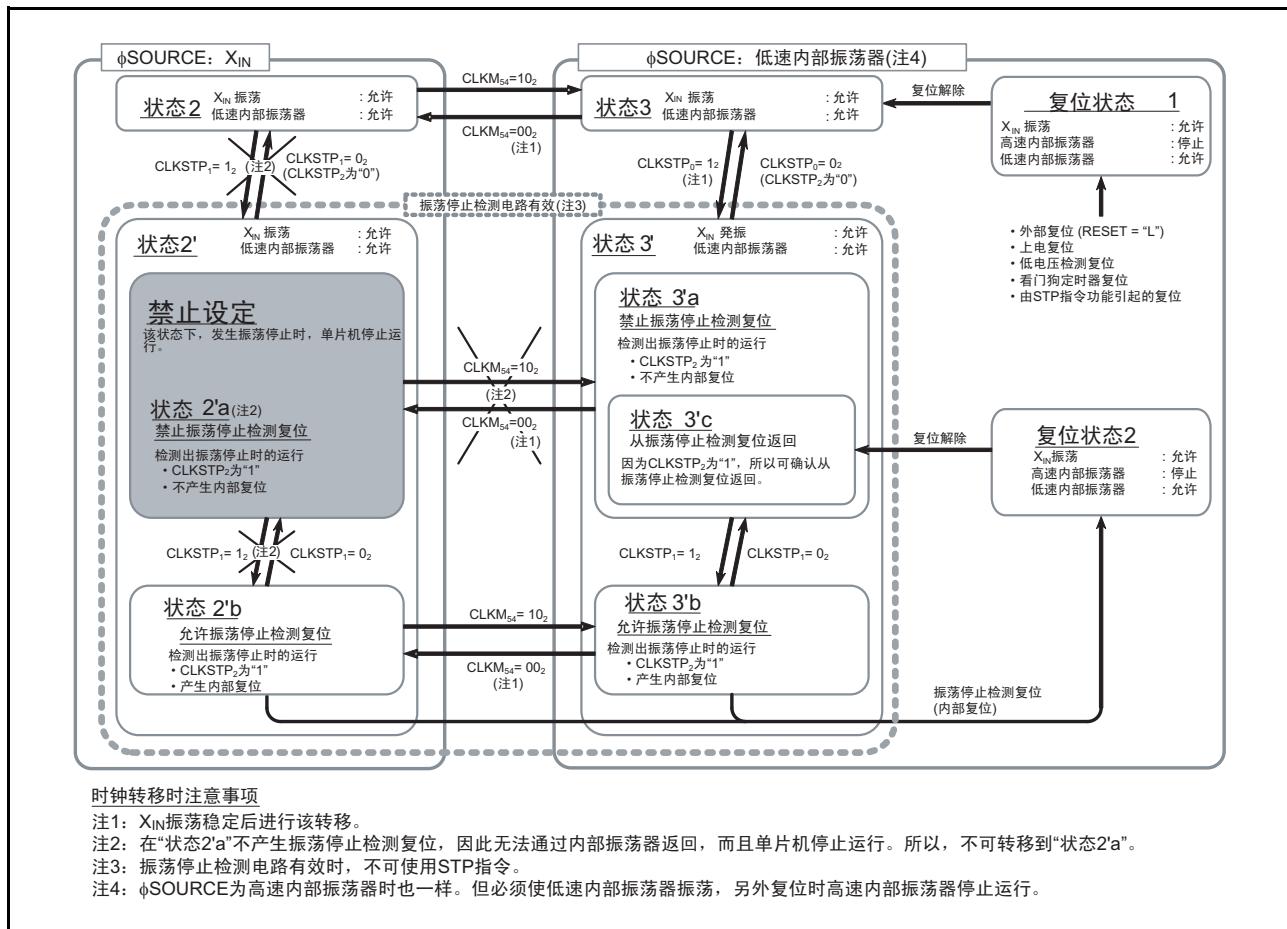

## 振荡停止检测电路

振荡停止检测电路检测因陶瓷谐振器或振荡电路的断路引起的振荡停止。使用振荡停止检测电路时，需运行低速内部振荡器。

将 XIN 振荡停止检测功能有效位设定为“1”时振荡停止检测电路有效。在振荡停止检测电路有效的状态下，通过低速内部振荡器监视 XIN 振荡电路的运行状态，检测出振荡停止时，振荡停止检测状态位为“1”。另外，通过将振荡停止检测复位允许位设定为“1”，振荡停止检测时，产生内部复位。

产生振荡停止检测复位时，XIN 振荡停止检测功能有效位及振荡停止检测状态位不进行初始化，仍保持为“1”。外部复位时振荡停止检测状态位初始化为“0”，因此，通过确认此位，可判断振荡停止检测复位。

通过向 XIN 振荡停止检测功能有效位写入“0”，振荡停止检测状态位变为“0”。振荡停止检测电路有效时，执行一次向 XIN 振荡停止检测功能有效位写入“0”，再在振荡停止检测状态位设定为“0”后，将振荡停止检测功能设定为“1”。

可检测振荡停止的时钟为 XIN 振荡、外部时钟输入。可检测的频率请参考电特性。

图 68 振荡停止检测寄存器的结构

### 注意事项

- 由于在“图 69 振荡停止检测电路的状态转移图”所记载的“状态2’ a”，即使在 XIN 的振荡停止时，也不产生复位，由于单片机停止运行，因此不可转移道“状态2’ a”。

- 振荡停止检测复位后，如果保持 XIN 振荡停止检测功能有效位与振荡停止检测状态位的状态下允许振荡停止检测复位，将再次产生复位。

- 振荡停止检测状态位，在下述情况下进行初始化。

- 外部复位、上电复位、低电压检测复位、看门狗定时器复位、STP 指令功能引起的复位。

- 向 XIN 振荡停止检测功能有效位写入“0”。

- 振荡停止检测功能有效时，由看门狗定时器下溢或者 STP 指令功能选择位为“1”时执行 STP 指令产生的复位，有可能使振荡停止检测状态位为“1”。振荡停止检测复位振荡时，请再次确认振荡停止。

- 仿真专用 MCU “M37549RLSS” 中无振荡停止检测电路。

图 69 振荡停止检测电路的状态转移图

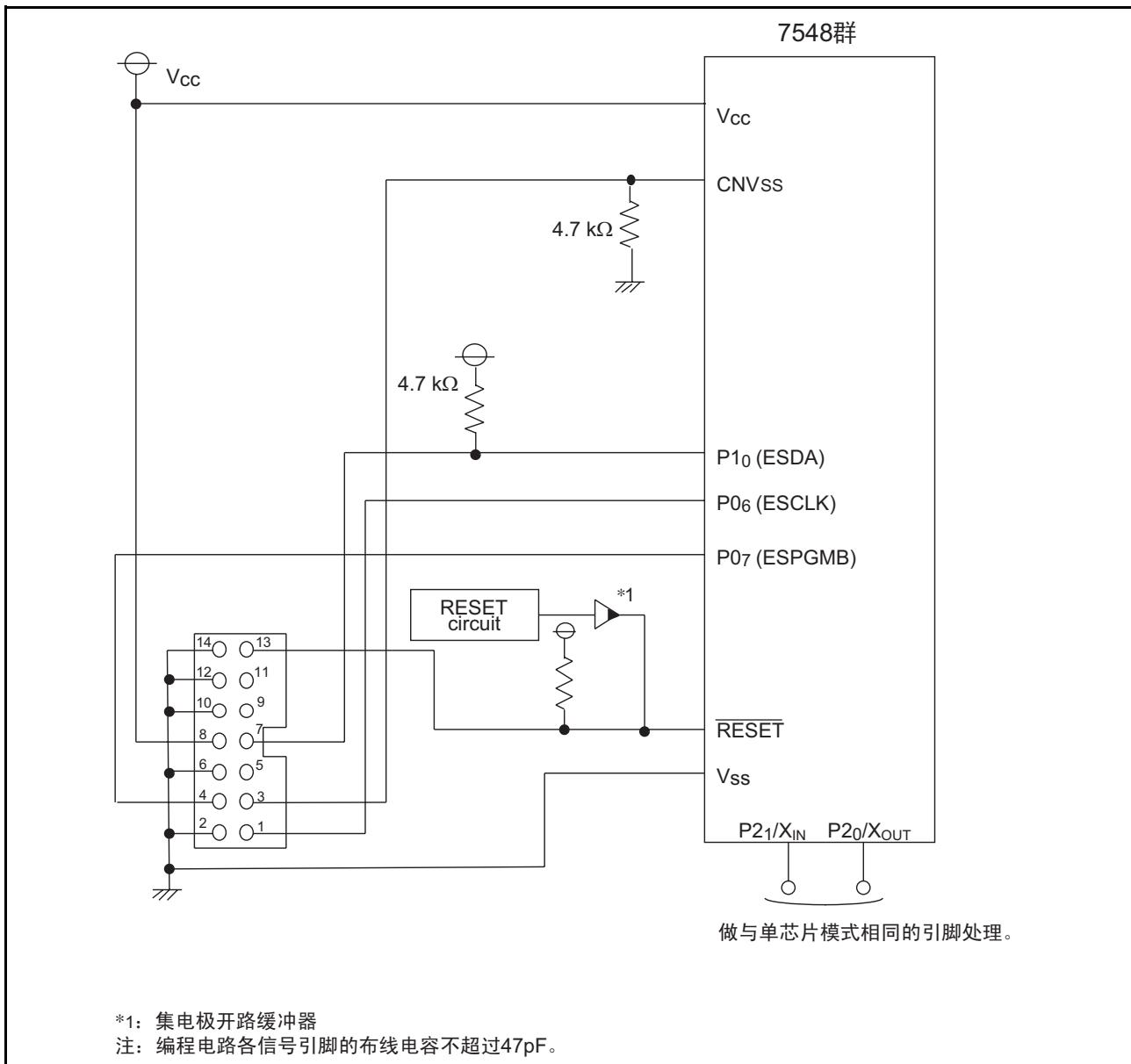

## QzROM 编程模式

QzROM 编程模式下，使用适用于本单片机的串行编程器，在将单片机安装在电路板的状态下，可写入用户 ROM 区。

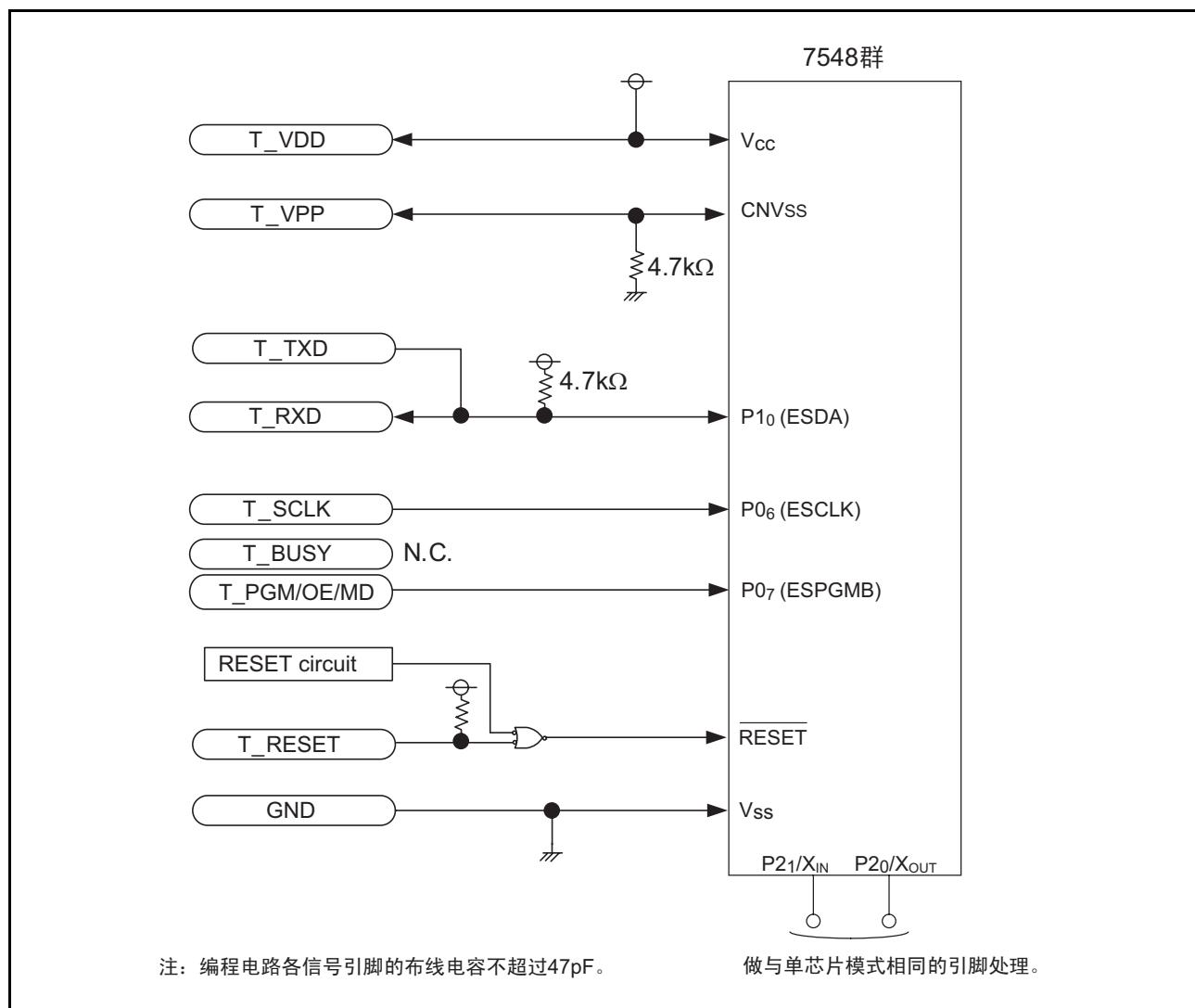

引脚功能说明（QzROM 编程模式）如表 10 所示，引脚接线图如图 70 所示。

与串行编程器的连接时，请参考电路板上的引脚处理例（图 71、图 72）。关于串行编程器，请询问各厂家。另外，串行编程器的操作方法，请参考串行编程器用户手册。

表 10 引脚功能说明（QzROM 编程模式）

| 引脚名称                                                                 | 名称                 | 输入 / 输出 | 功能                                                           |

|----------------------------------------------------------------------|--------------------|---------|--------------------------------------------------------------|

| V <sub>CC</sub> 、V <sub>SS</sub>                                     | 电源输入               | 输入      | 给 V <sub>CC</sub> 外加 2.7~5.5V 电压，给 V <sub>SS</sub> 外加 0V 电压。 |

| RESET                                                                | 复位输入               | 输入      | 复位输入引脚。                                                      |

| P <sub>21</sub> /X <sub>IN</sub>                                     | 时钟输入               | 输入      | 进行与单片模式时相同的引脚处理。                                             |

| P <sub>20</sub> /X <sub>OUT</sub>                                    | 时钟输出               | 输出      |                                                              |

| P <sub>00</sub> ~P <sub>05</sub><br>P <sub>11</sub> ~P <sub>15</sub> | 输入 / 输出端口          | 输入 / 输出 | 输入“H”、输入“L”或开路。                                              |

| CNV <sub>SS</sub>                                                    | V <sub>PP</sub> 输入 | 输入      | QzROM 的电源输入引脚。                                               |

| P <sub>10</sub>                                                      | ESDA 输入 / 输出       | 输入 / 输出 | 串行数据的输入 / 输出引脚。                                              |

| P <sub>06</sub>                                                      | ESCLK 输入           | 输入      | 串行时钟的输入引脚。                                                   |

| P <sub>07</sub>                                                      | ESPGMB 输入          | 输入      | 读取 / 编程脉冲信号的输入引脚。                                            |

图 70 引脚接线图（M37548G3/G2/G1FP）

图 71 使用 E8 编程时电路板上的引脚处理例

图 72 使用彗星编程器时电路板上的引脚处理例

## 编程时的注意事项

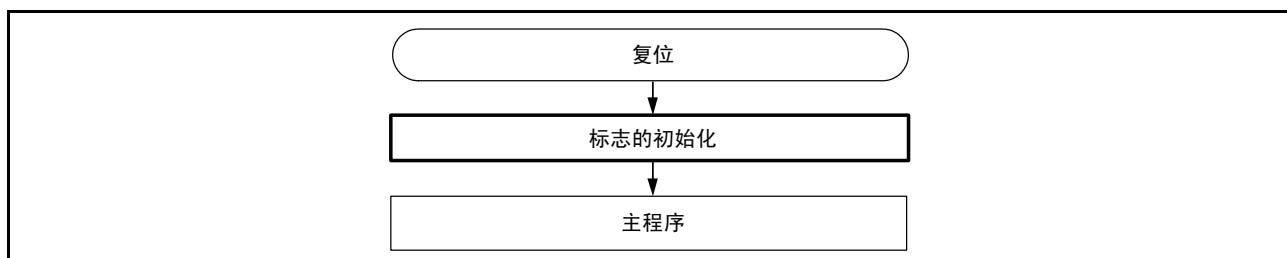

### (1) 处理器状态寄存器

处理器状态寄存器（PS）除中断禁止标志 I 为“1”以外，刚复位后的值不定。因此，必须对影响程序执行的标志进行初始化。

特别是影响运算本身的 T 标志、D 标志，必须进行初始化。

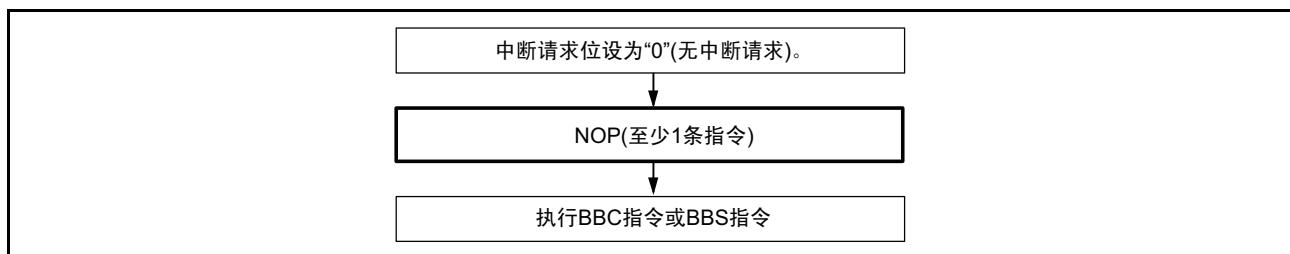

### (2) 中断

通过程序改变中断请求位的内容后，即使立即执行 BBC、BBS 指令，也只执行改变前的内容，因此为了执行改变后的内容，必须在执行一条或一条以上的指令后才能进行。

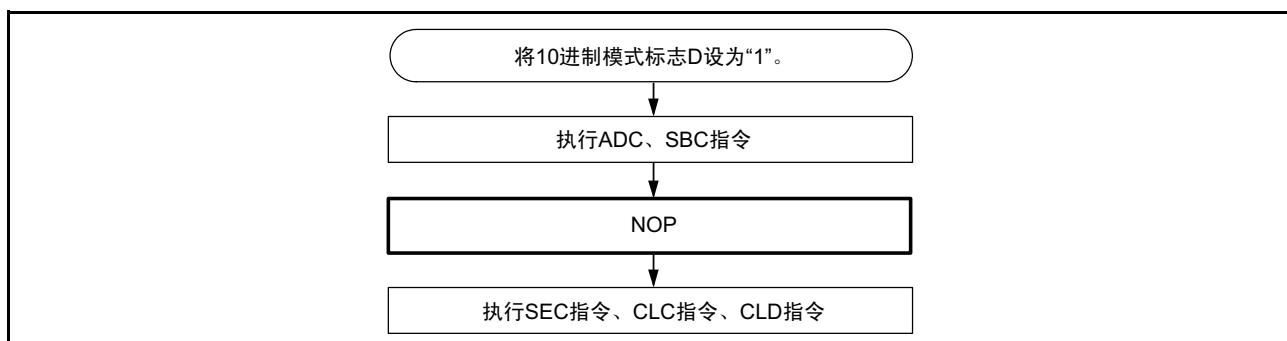

### (3) 十进制运算

- 进行十进制运算时，将十进制模式标志 D 设定为“1”后执行 ADC 指令或者 SBC 指令，此时，必须从 ADC 指令或 SBC 指令开始执行一条或一条以上的指令后，才可执行 SEC 指令、CLC 指令或者 CLD 指令。

- 十进制模式下，N（负）、V（上溢）及 Z（零）标志无效。

### (4) 端口

不可读取端口方向寄存器的值。即：不可使用 LDA 指令、T 标志为“1”时的存储器运算指令、将方向寄存器的值作为寻址值的寻址方式以及 BBC、BBS 等位测试指令。另外，也不可使用 CLB、SEB 等位操作指令、方向寄存器的读取/修改/写入指令（如 ROR 等的运算）。方向寄存器的设定必须使用 LDM、STA 等指令。

### (5) A/D 转换

A/D 转换期间，不可执行 STP 指令。

### (6) 指令执行时间

指令执行时间请参考《740 族 软件手册》。通过所记载的周期数乘以内部时钟  $\phi$  的周期得出指令执行时间。内部时钟  $\phi$  的周期在倍速模式下与  $\phi_{SOURCE}$  相同，在高速模式下为  $\phi_{SOURCE}$  周期的 2 倍、在中速模式下为  $\phi_{SOURCE}$  周期的 4 倍、在低速模式下为  $\phi_{SOURCE}$  的 8 倍。

### (7) CPU 模式寄存器 CPUM

处理器模式位在复位解除后仅可进行一次写入。必须设定“00<sub>2</sub>”。因为写入后被锁定，所以再次写入无效（仿真器专用的 MCU 除外）。

### (8) 时钟模式寄存器

不可通过 bit0、1、2 来停止运行时钟源所选择的时钟。

## 有关硬件的注意事项

### (1) 电源引脚的使用

使用时，为了防止闩锁现象，必须将高频特性良好的电容作为旁路电容外接到元件的电源引脚（VCC 引脚）与 GND 引脚（VSS 引脚）之间。推荐旁路电容使用 0.01μF ~ 0.1μF 的陶瓷电容。

另外，请将旁路电容以最短距离外接至电源引脚与 GND 引脚之间。

## 使用时的注意事项

### 噪声的注意事项

请按以下方法，进行防止噪声的系统设计与充分评价。

#### 1. 缩短布线长度

##### (1) 封装

为了缩短总布线长度，请尽可能采用小型封装的单片机。

<理由>

单片机的封装影响布线长度，与 DIP 相比，使用小型 QFP 等可缩短总布线长度，更不易受噪声影响。

图 73 封装的选择

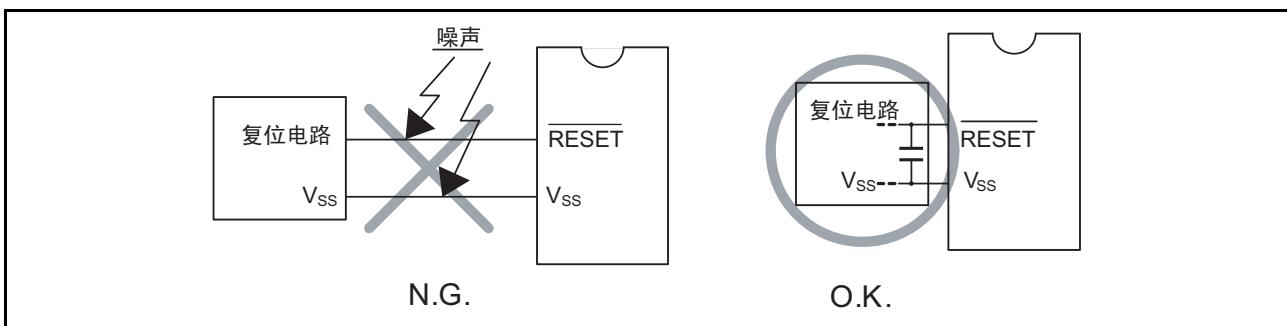

##### (2) 复位引脚的布线

请缩短连接复位引脚的布线。特别是连接在复位引脚与 V<sub>ss</sub> 引脚之间的电容必须以尽可能短（20mm 以内）的布线连接。

<理由>

时序必要条件规定了输入复位引脚的脉宽。因此，比规定宽度短的脉宽噪声输入复位引脚时，在单片机内部完全进入初始化状态前解除复位，会导致程序失控。

图 74 复位输入引脚的布线

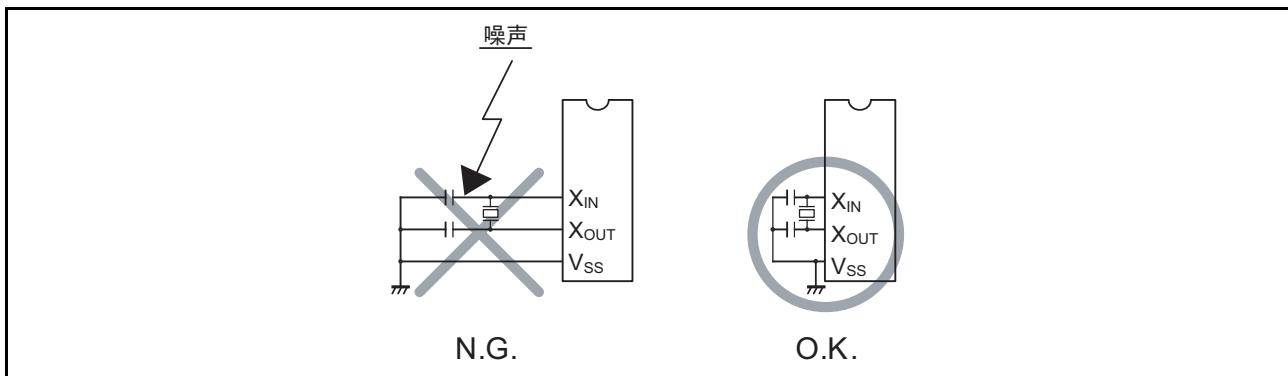

## (3) 时钟输入 / 输出引脚的布线

- 请缩短连接时钟输入 / 输出引脚的布线。

- 请以最短（20mm 以内）的布线将连接谐振器的电容接地端引线与单片机的 Vss 引脚相连接。

- 请将振荡用的 Vss 布线作为振荡电路专用布线，并与其它 Vss 布线分离。

&lt;理由&gt;

如果有噪声侵入时钟输入 / 输出引脚，时钟的波形就会发生紊乱，导致误动作和失控。另外，如果在单片机 Vss 电平和谐振器 Vss 电平之间产生噪声引起的电位差，就不能将正确的时钟输入单片机。

图 75 时钟输入 / 输出引脚的布线

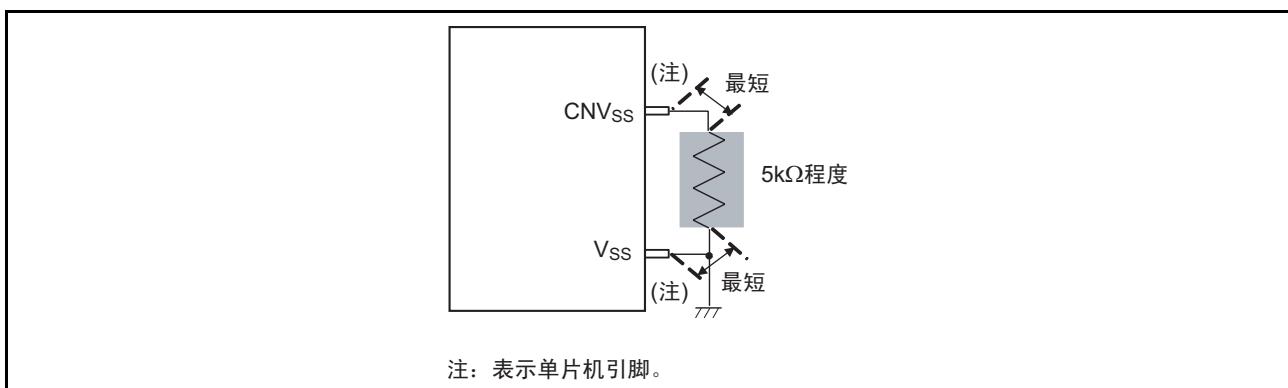

## (4) CNVss 引脚布线

请将 CNVss 引脚以最短距离连接至离提供给单片机 Vss 引脚的 GND 尽可能近的 GND 布线上。另外，通过串联接入  $5k\Omega$  左右的电阻并连接至 GND，有可能改善抗噪声能力。此时，也尽可能将其以最短距离连接至离提供给单片机 Vss 引脚的 GND 最近的 GND 布线上。

&lt;理由&gt;

CNVss 引脚是内部 QzROM 的电源输入引脚。

向 QzROM 写入程序时，为了通过写入电流，降低 CNVss 引脚的阻抗，所以噪声易于侵入。如果噪声从 CNVss 引脚侵入，QzROM 的指令码、数据的读取就不能正常进行，并且导致失控。

图 76 QzROM 版的 CNVss 引脚布线

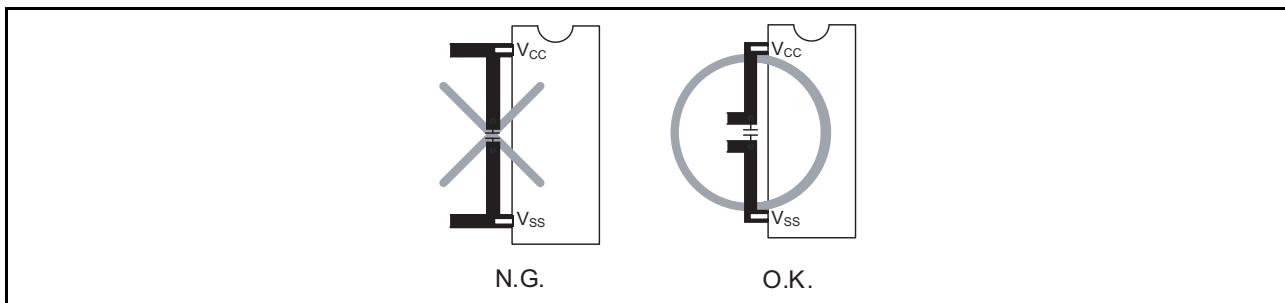

## 2. 在 Vss-Vcc 线之间接入旁路电容

在 Vss-Vcc 线之间接入 0.1 $\mu$ F 左右的旁路电容的条件如下：

- 使 Vss 引脚—旁路电容间的布线长度与 Vcc 引脚—旁路电容间的布线长度相等

- 使 Vss 引脚—旁路电容间的布线长度与 Vcc 引脚—旁路电容间的布线长度最短

- Vss 线与 Vcc 线要使用比其他信号线更粗的布线

- 电源布线经由旁路电容连接至 Vss 引脚及 Vcc 引脚

图 77 Vss-Vcc 线之间的旁路电容

## 3. 模拟输入引脚的布线处理

模拟输入引脚与电压比较电路的电容连接。因此，模拟输入引脚上连接高阻抗模拟信号源时，通过 A/D 转换时的充放电电流，有时得不到十分精度的结果。为了获得更稳定的 A/D 转换结果，请降低模拟信号源的阻抗或给模拟输入引脚连接平滑电容。

## 4. 对谐振器的考虑

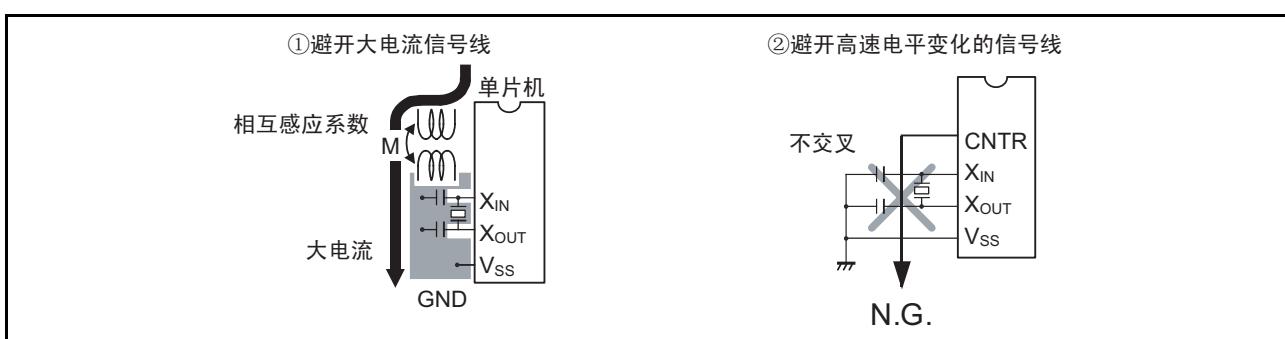

必须考虑使生成单片机运行基本时钟的谐振器不受其他信号的影响。

### (1) 避开大电流信号线

请尽可能将超过单片机处理电流值范围的大电流信号线远离单片机（特别是谐振器）。

<理由>

使用单片机的系统中，存在控制马达、LED 及热敏头等的信号线。这些信号线有大电流流经时，会产生因互感引起的噪声。

### (2) 避开高速电平变化的信号线

请尽可能将高速电平变化的信号线远离谐振器及谐振器的布线。

另外，高速电平变化的信号线不可与时钟相关的信号线及其他易受噪声影响的信号线相交叉。

<理由>

高速电平变化的 CNTR 引脚等的信号，由于上升或下降时的电平变化，很容易影响其他信号线。特别是在与时钟相关的信号线交叉时，会发生时钟波形紊乱，导致误动作及失控。

图 78 大电流信号的布线和高速电平变化信号线的布线

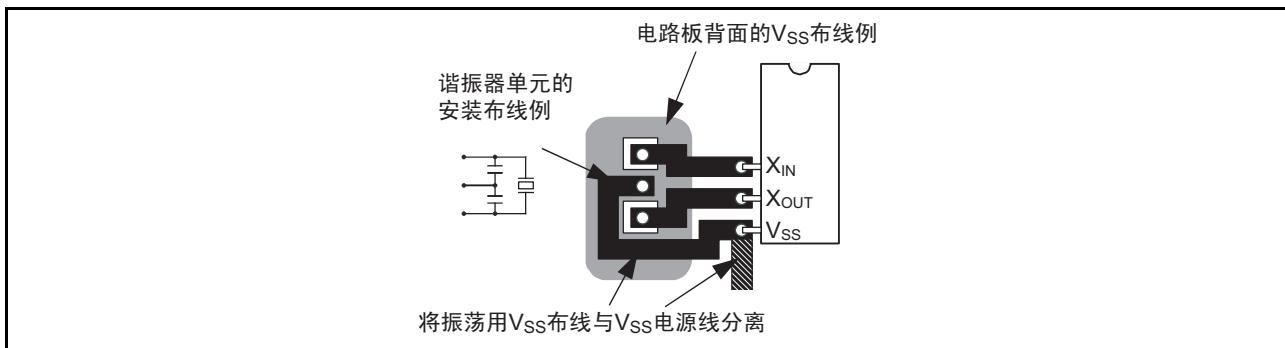

## (3) 通过 Vss 布线保护

为双面电路板时，必须在谐振器安装面（安装面）的背面（焊接面）且与谐振器相同的位置上设计 Vss 布线。

必须以最短的布线将此 Vss 布线与单片机的 Vss 引脚连接，并独立于其他 Vss 布线。

图 79 谐振器背面的 Vss 布线

## 5. 输入 / 输出端口的处理

必须按下列硬件、软件方法处理输入 / 输出端口：

<硬件方面>

- 必须给输入/输出端口串联接入不低于  $100\Omega$  的电阻。

<软件方面>

- 必须通过程序对输入端口进行多次读，并确认电平是否一致。

- 输出端口有可能因噪声而引起输出数据取反，所以必须以固定周期对端口锁存器进行再次写入。

- 必须以固定周期对方向寄存器与上拉控制寄存器进行再次写入。

图 80 输入 / 输出端口的处理

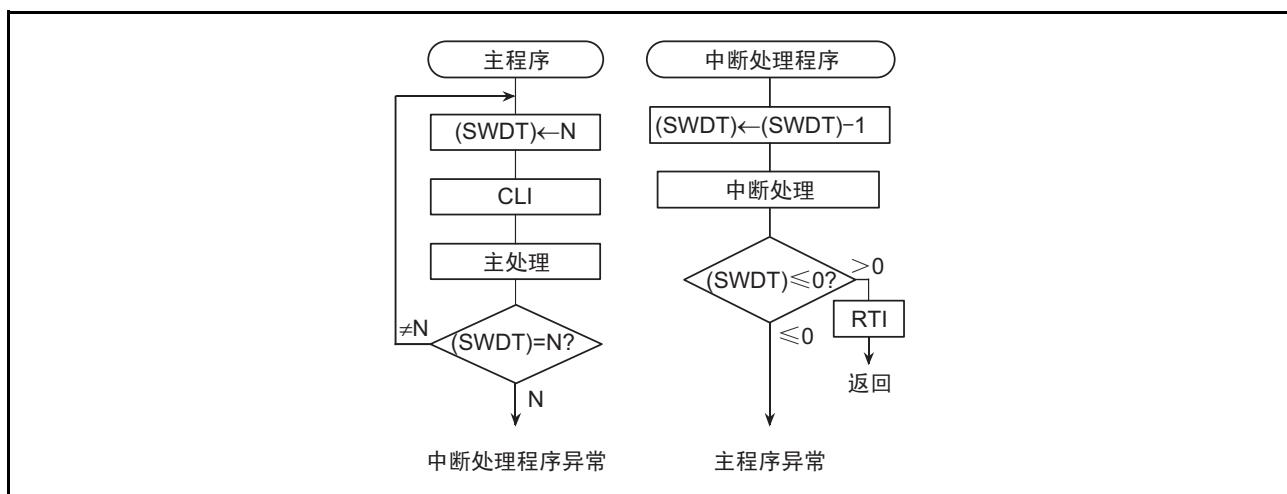

## 6. 通过软件实现看门狗定时器的功能

噪声等引起单片机失控时，通过软件看门狗定时器检测失控，并且使其返回至正常运行状态。此方法与使用硬件看门狗定时器检测失控的方法具有同等效果或效果更好。软件看门狗定时器例如下所示：

在此例中，主程序监视中断处理程序的运行，中断处理程序监视主程序的运行，检测出异常时，将单片机返回到正常状态。

但是，此例的前提是在主程序的1个周期内进行多次中断处理。

<主程序>

- 将RAM的1个字节分配给软件看门狗定时器（SWDT），在主程序的每1个周期给SWDT写入一次初始值N。初始值N满足以下条件：

$N + 1 \geq$  在主程序的1个周期中进行的中断处理次数

【注】因为主程序的周期根据中断处理等而发生变化，所以必须给初始值N设定充裕的值。

- 通过将SWDT的内容与设定初始值N后的中断处理次数进行比较来监视中断处理程序的运行。

- 即使进行中断处理，SWDT的内容也不发生变化时，就会判断中断处理程序运行异常，并进行向程序初始化程序转移等恢复处理。

<中断处理程序>

- 每进行1次中断处理，SWDT的内容减1。

- 通过以几乎固定的周期（固定的中断处理次数）将SWDT的内容返回至初始值N来确认主程序的正常运行。

- SWDT的内容不初始为N而继续减1，且SWDT的内容小于等于0时，就会判断主程序运行异常，并进行向程序初始化程序转移等恢复处理。

图 81 软件看门狗定时器

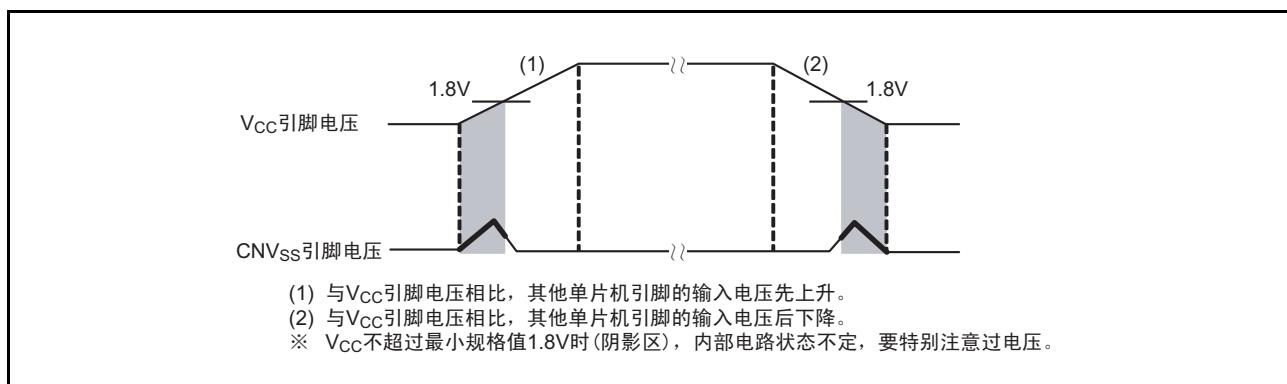

## 使用时的注意事项

### 有关电源电压的注意事项

在单片机的电源电压低于推荐运行条件的值时，单片机可能无法正常运行，处于不稳定的运行状态。对于在电源电压下降和切断电源时电源电压缓慢下降的系统，系统设计时必须考虑即使在电源电压低于推荐运行条件时的不稳定运行状态下也能通过单片机复位等手段使系统不发生异常。

### 有关空白出货产品的注意事项

虽然在组装工程前对空白出货产品进行了充分的 QzROM 写测试，但是在组装工程后对用户 ROM 区没有进行写测试，因此有可能发生 0.1% 左右写失败。另外，环境也会造成写失败，所以在使用时必须充分注意电缆的接触和插座上的异物等。

### 有关过电压的注意事项

不能将超过 V<sub>CC</sub> 引脚电压的电压加到其他引脚上，特别注意，不能使 CNV<sub>SS</sub> 引脚（QzROM 的 V<sub>PP</sub> 电源输入引脚）上的电压上升与下降值进入图 82 中所示的粗线区域。因为，在此电压状态下，QzROM 的内容可能也被改写。

图 82 时序图（粗线区间）

## 订购 QzROM 编程后的产品时的注意事项

在订购 QzROM 编程的出货产品时，必须提交用掩模文件转换使用程序（MM）建立的掩模文件（扩展名 .msk）。另外，在执行掩模文件转换使用程序（MM）建立掩模文件时，必须设定 ROM 选项（在掩模转换使用程序中记为“掩模选项”的数据）。

### 有关 ROM 代码保护的注意事项（QzROM 编程后的出货产品）

QzROM 编程后的出货产品的 ROM 代码保护，由订货时提出的在建立掩模文件时的 ROM 选项数据决定。

建立掩模文件时的 ROM 选项数据为“有保护”时，设定“00<sub>16</sub>”；为“无保护”时，设定“FF<sub>16</sub>”。因此，QzROM 编程后的出货产品的 ROM 代码保护地址 ROM 保留区的内容为“00<sub>16</sub>”或者“FF<sub>16</sub>”。

另外，必须注意：ROM 选项数据没有设定或设定为“00<sub>16</sub>”、“FF<sub>16</sub>”以外的数据时，不接受掩模文件。

## 订购 QzROM 编程后的产品时的提交资料

必须在订购 QzROM 编程后的出货产品时提交以下资料：

- QzROM 编程确认书\*

- 标记指定书\*

- ROM 的数据…掩模文件

\* 有关 QzROM 编程确认书和标记指定书，请参考瑞萨科技网页（<http://www.renesas.com/homepage.jsp>）。另外，QzROM 单片机不支持特殊字体标记（贵公司商标等）。

## 7548 群的电特性

### (1) 绝对最大额定值

表 11 绝对最大额定值

| 符号               | 项 目                                                                                                            | 条 件                                                | 额 定 值                        | 单 位 |

|------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------|-----|

| V <sub>CC</sub>  | 电源电压                                                                                                           |                                                    | -0.3 ~ 6.5                   | V   |

| V <sub>I</sub>   | 输入电压<br>P <sub>00</sub> ~ P <sub>07</sub> 、P <sub>10</sub> ~ P <sub>15</sub> 、P <sub>20</sub> 、P <sub>21</sub> | 以 V <sub>SS</sub> 引脚为基准测定。<br>在测定输入电压时，输出晶体管为截止状态。 | -0.3 ~ V <sub>CC</sub> + 0.3 | V   |

| V <sub>I</sub>   | 输入电压 RESET                                                                                                     |                                                    | -0.3 ~ V <sub>CC</sub> + 0.3 | V   |

| V <sub>I</sub>   | 输入电压 CNV <sub>SS</sub>                                                                                         |                                                    | -0.3 ~ V <sub>CC</sub> + 0.3 | V   |

| V <sub>O</sub>   | 输出电压<br>P <sub>00</sub> ~ P <sub>07</sub> 、P <sub>10</sub> ~ P <sub>15</sub> 、P <sub>20</sub> 、P <sub>21</sub> |                                                    | -0.3 ~ V <sub>CC</sub> + 0.3 | V   |

| P <sub>d</sub>   | 功耗                                                                                                             | T <sub>a</sub> =25°C                               | 300                          | mW  |

| T <sub>opr</sub> | 工作环境温度                                                                                                         | —                                                  | -20 ~ 85                     | °C  |

| T <sub>stg</sub> | 保存温度                                                                                                           | —                                                  | -40 ~ 125                    | °C  |

## (2) 推荐运行条件

表 12 推荐运行条件

(未指定时,  $V_{CC}=1.8 \sim 5.5V$ 、 $V_{SS}=0V$ 、 $T_a=-20 \sim 85^{\circ}C$ )

| 符号                    | 项 目                                                                             |                                       |                | 规 格 值                   |     |               | 单位 |

|-----------------------|---------------------------------------------------------------------------------|---------------------------------------|----------------|-------------------------|-----|---------------|----|

|                       |                                                                                 |                                       |                | 最 小                     | 典 型 | 最 大           |    |

| $V_{CC}$              | 电源电压                                                                            | 高速内部振荡器运行时                            | 倍、高、中、低速模式     | 4.0                     | 5.0 | 5.5           | V  |