# **Description**

The 8V41NS0412 is a clock generator with four output dividers: three integer, and one that is either integer or fractional. When used with an external crystal, the 8V41NS0412 generates high performance timing geared towards the communications and datacom markets, especially for applications demanding extremely low phase noise, such as 10GE, 40GE, 100G, and 400GE.

The 8V41NS0412's versatile frequency configurations are optimized to deliver excellent phase noise performance. The device delivers an optimum combination of high clock frequency and low-phase noise performance, combined with high-power supply noise rejection.

The 8V41NS0412 supports HCSL type of output level on eleven of its outputs. In addition, there is a single LVCMOS output that has the option of providing a generated clock or acting as a reference bypass output.

The device can be configured to deliver specific configurations under pin control only, or additional configurations through an I<sup>2</sup>C serial interface by an external processor.

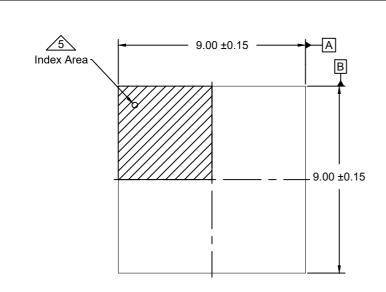

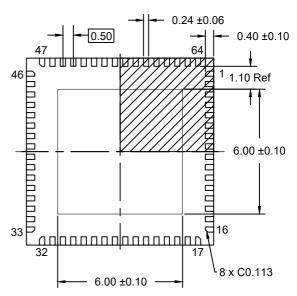

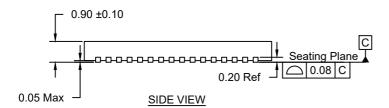

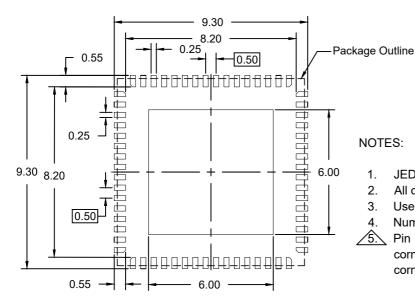

The 8V41NS0412 is offered in a lead-free (RoHS6) 64-VFQFN package.

# **Typical Applications**

- PCI Express Clocking

- 10G/40G/100G/400G Ethernet

- Gb Ethernet, Terabit IP switches / routers

- CPRI Interfaces

- Fiber Optics

#### **Features**

- Eleven differential HCSL outputs

- One LVCMOS output; input reference can be bypassed to this output

- The clock input operates in full differential mode (LVDS, LVPECL) or single-ended LVCMOS mode

- Driven from a crystal or differential clock input

- A 2.4–2.5GHz PLL frequency range supports Ethernet, SONET, and CPRI frequency plans

- 1.25GHz maximum output frequency

- Four integer output dividers with a range of output divide ratios (see Table 5)

- One fractional output divider can generate any desired output frequency

- Support of output power-down

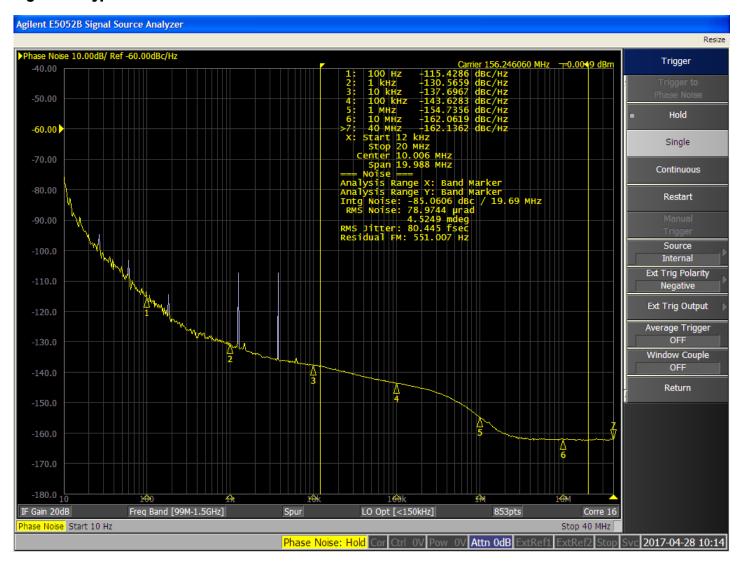

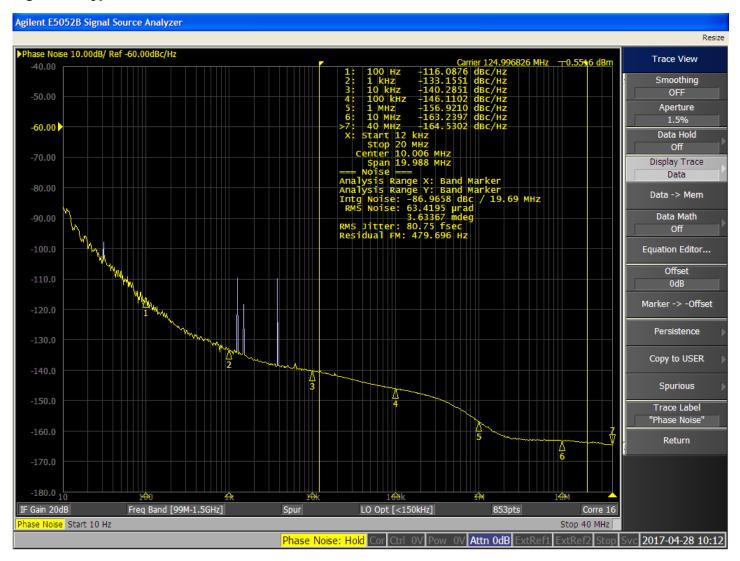

- Excellent clock output phase noise

Offset Output Frequency Single-side Band Phase Noise

100kHz 156.25MHz -143dBc/Hz

- Phase noise RMS, 156.25MHz, 12kHz to 20MHz integration range: 80fs (typical)

- Selected configurations can be controlled via the use of control input pins without need for serial port access

- LVCMOS compatible I<sup>2</sup>C serial interface gives access to additional configurations by external processor or in combination with the control input pins

- Single 3.3V supply voltage

- Lead-free (RoHS 6) 64-VFQFN packaging

- -40°C to 85°C ambient operating temperature

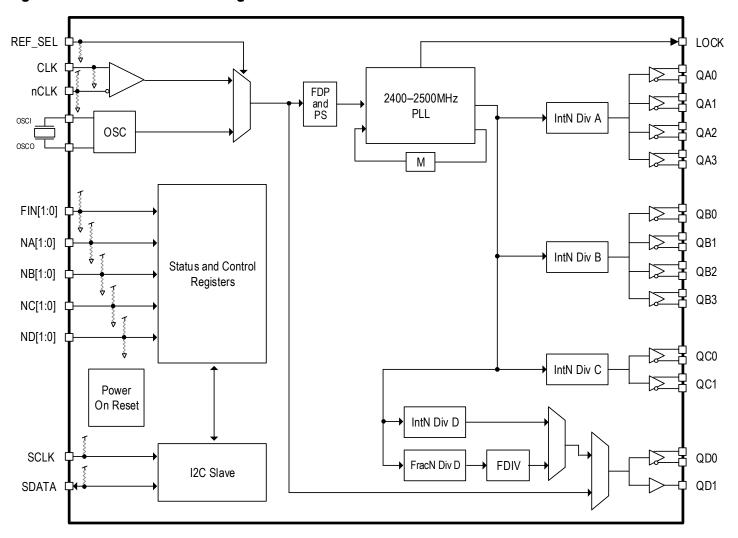

# **Block Diagram**

Figure 1. 8V41NS0412 Block Diagram

8V41NS0412 transistor count: 131,496

# **Contents**

| Description                                                 | 1              |

|-------------------------------------------------------------|----------------|

| Typical Applications                                        | 1              |

| Features                                                    | 1              |

| Pin Description                                             | 4              |

| Principles of Operation                                     |                |

| Pin versus Register Control                                 |                |

| Input Clock Selection (REF_SEL)                             | 8              |

| Prescaler and PLL Configuration                             | 8              |

| PLL Loop Bandwidth                                          |                |

| Output Divider Frequency Sources                            | 9              |

| Integer Output Dividers (Banks A, B, C, and D)              | 10             |

| Fractional Output Divider (Bank D)                          | 11             |

| Output Drivers                                              | 11             |

| Pin Control of the Output Frequencies and Protocols         | 11             |

| Device Start-up and Reset Behavior                          | 13             |

| Serial Control Port Description                             | 13             |

| Serial Control Port Configuration Description               | 13             |

| I2C Mode Operation                                          | 13             |

| Recommendations for Unused Input and Output Pins            | 35             |

| Inputs 3                                                    | 35             |

| Outputs                                                     | 35             |

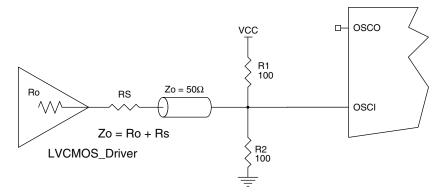

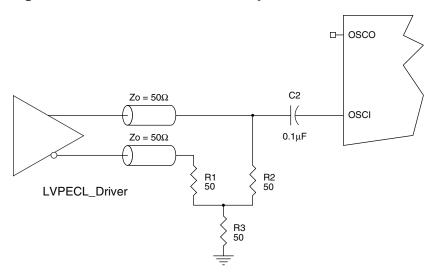

| Overdriving the XTAL Interface                              | 35             |

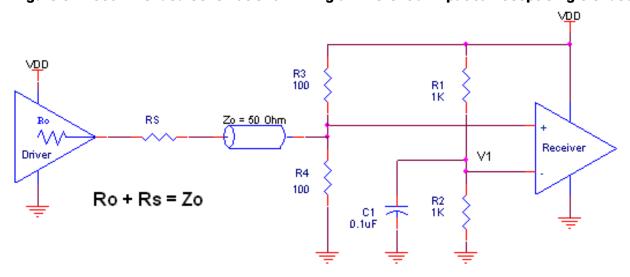

| Wiring the Differential Input to Accept Single-Ended Levels | 36             |

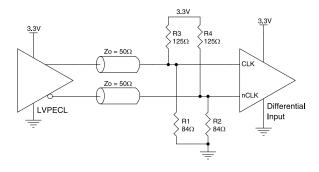

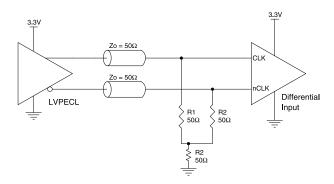

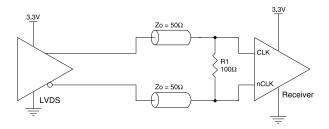

| 3.3V Differential Clock Input Interface                     | 37             |

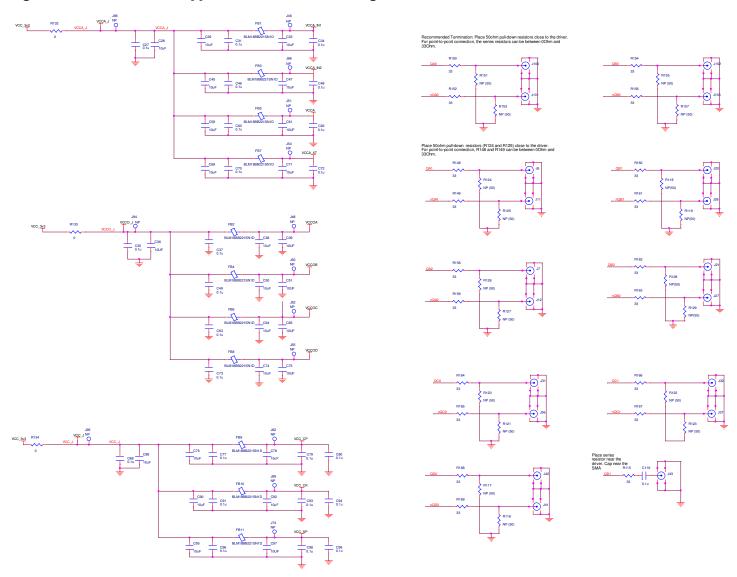

| Recommended Termination                                     | 38             |

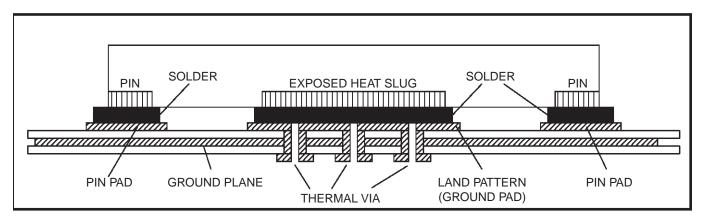

| VFQFN EPAD Thermal Release Path                             | 39             |

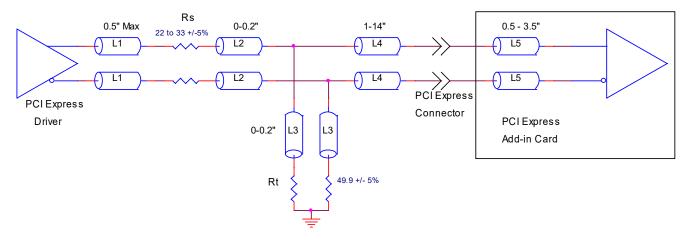

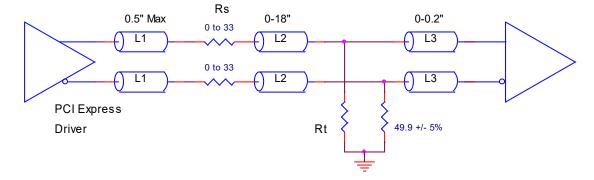

| PCI Express Application Note                                | 10             |

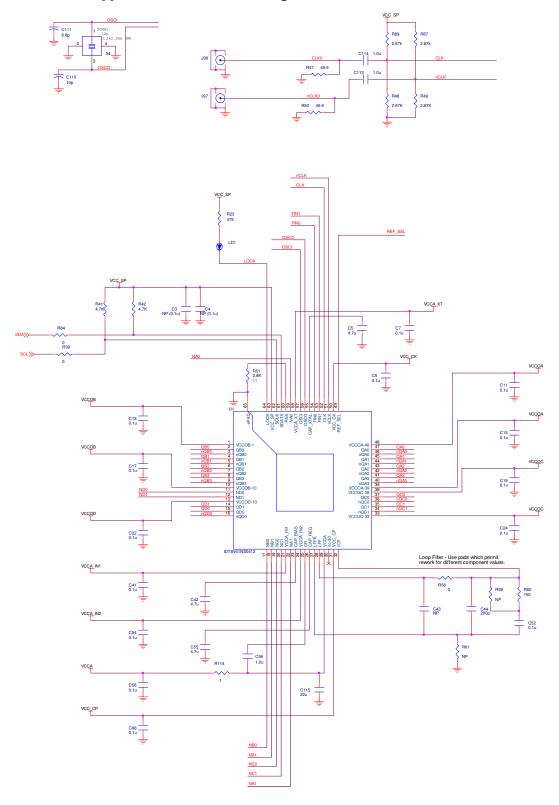

| Schematic and Layout Recommendations                        | <del>1</del> 2 |

| Power Dissipation and Thermal Considerations                | 14             |

| Example of Junction Temperature Calculation                 | <del>1</del> 5 |

| Marking Diagram                                             | <del>1</del> 7 |

| Revision History                                            | 17             |

# **Pin Assignment**

Figure 2. Pin Assignments for 9mm × 9mm 64-VFQFN Package – Top View

# **Pin Description**

Table 1. Pin Descriptions<sup>[a]</sup>

| Number | Name       | Туре             | Description                                                      |  |

|--------|------------|------------------|------------------------------------------------------------------|--|

| 1      | $V_{DDOB}$ | Power            | Power supply voltage for output Bank B (3.3V).                   |  |

| 2      | QB0        | Output           | Differential clock output pair HCSL interface levels             |  |

| 3      | nQB0       | Output           | Differential clock output pair. HCSL interface levels.           |  |

| 4      | QB1        | Output           | Differential clock output pair. HCSL interface levels.           |  |

| 5      | nQB1       | Output           |                                                                  |  |

| 6      | QB2        | Output           | Differential clock output pair. HCSL interface levels.           |  |

| 7      | nQB2       | Output           |                                                                  |  |

| 8      | QB3        | Output           | Differential clock output weig LICCL interface levels            |  |

| 9      | nQB3       | Output           | Differential clock output pair. HCSL interface levels.           |  |

| 10     | $V_{DDOB}$ | Power            | Power supply voltage for output Bank B (3.3V).                   |  |

| 11     | ND[0]      | Input<br>(PU/PD) | Control input for output Bank D. 3-level signals (see Table 10). |  |

# Table 1. Pin Descriptions<sup>[a]</sup> (Cont.)

| Number | Name                 | Туре             | Description                                                                                                         |  |

|--------|----------------------|------------------|---------------------------------------------------------------------------------------------------------------------|--|

| 12     | ND[1]                | Input<br>(PU/PD) | Control input for output Bank D. 3-level signals (see Table 10).                                                    |  |

| 13     | V <sub>DDOD</sub>    | Power            | Power supply voltage for output Bank D (3.3V).                                                                      |  |

| 14     | QD1                  | Output           | Single-ended output clock. LVCMOS output levels.                                                                    |  |

| 15     | QD0                  | Output           | Differential clock output pair. HCSL interface levels.                                                              |  |

| 16     | nQD0                 | Output           | Differential clock output pair. HCSL interface levels.                                                              |  |

| 17     | NB[0]                | Input<br>(PU/PD) | Control input for output Bank B. 3-level signals (see Table 8).                                                     |  |

| 18     | NB[1]                | Input<br>(PU/PD) | Control input for output Bank B. 3-level signals (see Table 8).                                                     |  |

| 19     | NC[0]                | Input<br>(PU/PD) | Control input for output Bank C. 3-level signals (see Table 9).                                                     |  |

| 20     | NC[1]                | Input<br>(PU/PD) | Control input for output Bank C. 3-level signals (see Table 9).                                                     |  |

| 21     | V <sub>DDA_IN1</sub> | Power            | Analog power supply voltage for PLL (3.3V).                                                                         |  |

| 22     | NA[1]                | Input<br>(PU/PD) | Control input for output Bank A. 3-level signals (see Table 7).                                                     |  |

| 23     | CAP <sub>BIAS</sub>  | Analog           | Internal VCO bias decoupling capacitor. Use a 4.7µF capacitor between the CAP <sub>BIAS</sub> terminal and GND.     |  |

| 24     | V <sub>DDA_IN2</sub> | Power            | Analog power supply voltage for VCO (3.3V).                                                                         |  |

| 25     | CR                   | Analog           | Internal VCO regulator decoupling capacitor. Use a $1\mu F$ capacitor between the CR and the $V_{DDA}$ terminals.   |  |

| 26     | CAP <sub>REG</sub>   | Analog           | Internal VCO regulator decoupling capacitor. Use a 4.7µF capacitor between the CAP <sub>REG</sub> terminal and GND. |  |

| 27     | LFFR                 | Analog           | Ground return path pin for the PLL loop filter.                                                                     |  |

| 28     | LFF                  | Output           | Loop filter/charge pump output for the FemtoClock NG PLL. Connect to the external loop filter.                      |  |

| 29     | $V_{DDA}$            | Power            | Analog power supply voltage for VCO (3.3V).                                                                         |  |

| 30     | nc                   | -                | No connect. Do not use.                                                                                             |  |

| 31     | V <sub>DD_CP</sub>   | Power            | Power supply voltage for PLL charge pump (3.3V).                                                                    |  |

| 32     | ICP                  | Analog           | Charge pump current input for PLL. Connect to LFF pin (28).                                                         |  |

| 33     | V <sub>DDOC</sub>    | Power            | Power supply voltage for output Bank C (3.3V).                                                                      |  |

| 34     | nQC1                 | Output           | Differential clock output pair LICCL interface levels                                                               |  |

| 35     | QC1                  | Output           | Differential clock output pair. HCSL interface levels.                                                              |  |

| 36     | nQC0                 | Output           | Differential clock output pair HCSL interface levels                                                                |  |

| 37     | QC0                  | Output           | Differential clock output pair. HCSL interface levels.                                                              |  |

| 38     | V <sub>DDOC</sub>    | Power            | Power supply voltage for output Bank C (3.3V).                                                                      |  |

| 39     | $V_{DDOA}$           | Power            | Power supply voltage for output Bank A (3.3V).                                                                      |  |

Table 1. Pin Descriptions<sup>[a]</sup> (Cont.)

| Number | Name                | Туре             | Description                                                                                                                    |  |  |

|--------|---------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| 40     | nQA3                | Output           | Differential alealy systems as a LICCL interface levels                                                                        |  |  |

| 41     | QA3                 | Output           | Differential clock output pair. HCSL interface levels.                                                                         |  |  |

| 42     | nQA2                | Output           | Differential alealy systems as a LICCL interface levels                                                                        |  |  |

| 43     | QA2                 | Output           | Differential clock output pair. HCSL interface levels.                                                                         |  |  |

| 44     | nQA1                | Output           | Differential clock output pair HCSL interface levels                                                                           |  |  |

| 45     | QA1                 | Output           | Differential clock output pair. HCSL interface levels.                                                                         |  |  |

| 46     | nQA0                | Output           | Differential alask sutput pair LICCL interface levels                                                                          |  |  |

| 47     | QA0                 | Output           | Differential clock output pair. HCSL interface levels.                                                                         |  |  |

| 48     | $V_{DDOA}$          | Power            | Power supply voltage for output Bank A (3.3V).                                                                                 |  |  |

|        |                     |                  | Selects input reference source. LVCMOS interface levels.                                                                       |  |  |

| 49     | REF_SEL             | Input (PD)       | 0 = Crystal input on pins OSCI, OSCO (default)                                                                                 |  |  |

|        |                     | _                | 1 = Reference clock input on pins CLK, nCLK                                                                                    |  |  |

| 50     | V <sub>DD_CK</sub>  | Power            | Power supply voltage for input CLK, nCLK (3.3V).                                                                               |  |  |

| 51     | nCLK                | Input<br>(PU/PD) | Inverting differential clock input. Internal resistor bias to $V_{DD\_CK}/2$ .                                                 |  |  |

| 52     | CLK                 | Input (PD)       | Non-inverting differential clock input.                                                                                        |  |  |

| 53     | FIN[1]              | Input<br>(PU/PD) | Control input for input reference frequencies. 3-level signals (see Table 3).                                                  |  |  |

| 54     | FIN[0]              | Input<br>(PU/PD) | Control input for input reference frequencies. 3-level signals (see Table 3).                                                  |  |  |

| 55     | CAP <sub>XTAL</sub> | Analog           | Crystal oscillator circuit decoupling capacitor. Use a $4.7\mu F$ capacitor between the CAP <sub>XTAL</sub> and GND terminals. |  |  |

| 56     | OSCO                | Output           | Crystal oscillator interface.                                                                                                  |  |  |

| 57     | OSCI                | Input            | Crystal oscillator interface.                                                                                                  |  |  |

| 58     | V <sub>DDA_XT</sub> | Power            | Analog power supply voltage for the crystal oscillator (3.3V).                                                                 |  |  |

| 59     | NA[0]               | Input<br>(PU/PD) | Control input for output Bank A. 3-level signals (see Table 7).                                                                |  |  |

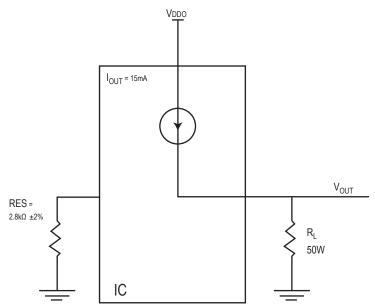

| 60     | RES                 | Analog           | Connect a 2.8kΩ (±2%) resistor to GND for output current calibration.                                                          |  |  |

| 61     | SDATA               | I/O (PU)         | I <sup>2</sup> C data input/output. LVCMOS interface levels. Open-drain pin.                                                   |  |  |

| 62     | SCLK                | Input (PU)       | I <sup>2</sup> C clock input. LVCMOS interface levels.                                                                         |  |  |

| 63     | $V_{DD\_SP}$        | Power            | Power supply voltage for the I <sup>2</sup> C port (3.3V).                                                                     |  |  |

| 64     | LOCK                | Output           | Lock status output. LVCMOS interface levels.  Logic low = PLL not locked  Logic high = PLL locked                              |  |  |

| ePad   | GND                 | Power            | Power supply ground. Exposed pad must be connected to ground.                                                                  |  |  |

<sup>[</sup>a] Internal pull-up (PU) and pull-down (PD) resistors are indicated in parentheses. For typical values, see Table 19.

## **Principles of Operation**

The 8V41NS0412 can be locked to either an input reference clock or a 10MHz to 50MHz fundamental-mode crystal and generate a wide range of synchronized output clocks. Lock status can be monitored via the LOCK pin. For example, it could be used in either the transmit or receive path of Synchronous Ethernet or SONET/SDH equipment.

The 8V41NS0412 accepts a differential or single-ended input clock ranging from 5MHz up to 1GHz. It generates up to twelve output clocks with up to four different output frequencies, ranging from 10.91MHz up to 1.25GHz.

The device outputs are divided into four output banks. Each bank supports conversion of the input frequency to a different output frequency: one independent or integer related output frequency on Bank D (QD[0:1]). Three additional integer related frequencies are on Bank A (QA[0:3]), Bank B (QB[0:3]) and Bank C (QC[0:1]). All outputs within a bank will have the same frequency.

The device is programmable through an I<sup>2</sup>C serial interface by an external processor or via control input pins.

### **Pin versus Register Control**

The 8V41NS0412 can be configured by the use of input control pins and/or over an I<sup>2</sup>C serial port. The pins / registers used to control each function are shown in Table 2. At power-up, control of each function is via the control input pins. Access over the serial port can change each function individually to be controlled by registers. This allows for any mixture of register or pin control. However any of the indicated functions can only be controlled by register or by pin at any given time, not by both. Use of register control will allow access to a wider range of configuration options but values are lost on power-down. If the output bank or PLL is controlled by control input pins (at power-up or through the Control Select bit), corresponding register values remain unchanged and have no impact on device functions.

**Table 2. Control of Specific Functions**

| Function                           | Control Select Bit | Control Input Pins | Register Fields Affected                                                         |

|------------------------------------|--------------------|--------------------|----------------------------------------------------------------------------------|

| Prescaler and PLL Feedback divider | FIN_CTL            | FIN[1:0]           | PS[5:0], FDP, M[8:0]                                                             |

| Bank A Divider and output type     | NA_CTL             | NA[1:0]            | NA[5:0], PD_A, PD_QAx                                                            |

| Bank B<br>Divider and output type  | NB_CTL             | NB[1:0]            | NB[5:0], PD_B, PD_QBx                                                            |

| Bank C<br>Divider and output type  | NC_CTL             | NC[1:0]            | NC[5:0], PD_C, PD_QCx                                                            |

| Bank D<br>Divider and output type  | ND_CTL             | ND[1:0]            | ND[5:0], ND_FINT[3:0], ND_FRAC[23:0], ND_DIVF[1:0], ND_DIV, ND_SRC, PD_D, PD_QDx |

Changes to the control pins while the part is active are allowed, but limited and cannot be guaranteed a glitch-free output transition. During the state transition of the control pins, the output phase alignment (synchronization) may be lost and Bank D outputs in Fractional Mode (FOD) may not be available. If the I<sup>2</sup>C registers are accessible, then assertion of the INIT\_CLK bit or powering down and then powering up the device will restore phase alignment and activate the Fractional output frequency.

Glitch-free operation can be performed by disabling the outputs using the I<sup>2</sup>C-accessible registers, then re-enabling once changes are completed.

Any change to the output dividers performed over the I<sup>2</sup>C interface must be followed by an assertion of the INIT\_CLK register bit to force the loading of the new divider values, as well as to synchronize the output dividers.

### Input Clock Selection (REF\_SEL)

The 8V41NS0412 needs to be provided with an input reference frequency either from its crystal input pins (OSCI, OSCO) or its reference clock input pins (CLK, nCLK). The REF\_SEL input pin controls which source is used.

The crystal input on the 8V41NS0412 is capable of being driven by a parallel-resonant, fundamental mode crystal with a frequency of 10MHz to 50MHz.

The crystal input also supports being driven by a single-ended crystal oscillator or reference clock, but only a frequency from 10MHz to 50MHz can be used on these pins.

The reference clock input accepts clocks with frequencies ranging from 5MHz up to 1GHz. The input can accept LVPECL, LVDS, LVHSTL, HCSL, or LVCMOS inputs using 2.5V or 3.3V logic levels as shown in Applications Information.

### **Prescaler and PLL Configuration**

When the input frequency (f<sub>IN</sub>), whether generated by a crystal or clock input is known, and the desired PLL operating frequency has been determined, several constraints need to be met:

- The Phase/ Frequency Detector operating frequency (f<sub>PFD</sub>) must be within the specified limits shown in Table 27. This is controlled by selecting a doubler (FDP) or an appropriate prescaler (PS) value. If multiple values are possible, a higher f<sub>PFD</sub> will provide better phase noise performance.

- The VCO operating frequency (f<sub>VCO</sub>) must be within the specified limits shown in Table 27. This is controlled by selecting an appropriate PLL feedback divider (M) value. Note that it may be necessary to choose a different prescaler value if the limits cannot be met by the available values of M. It may also be necessary to select an appropriate input frequency value.

Several preset configurations can be selected directly from the FIN[1:0] control input pins. These configurations are based on a particular input frequency  $f_{IN}$  and a particular  $f_{VCO}$  (see Table 3). These selections apply whether the input frequency is provided from the crystal or reference clock inputs

**Table 3. Input Selection Control**

| FIN[1] | FIN[0]                | f <sub>IN</sub> (MHz) | f <sub>VCO</sub> (MHz) |

|--------|-----------------------|-----------------------|------------------------|

| High   | High                  | 38.88                 | 2488.32                |

| High   | Middle <sup>[a]</sup> | 38.4                  | 2457.6                 |

| High   | High Low 31.25        |                       | 2500                   |

| Middle | High                  | 312.5                 | 2500                   |

| Middle | Middle                | 125                   | 2500                   |

| Middle | Low                   | 156.25                | 2500                   |

| Low    | High                  | 100                   | 2500                   |

| Low    | Middle                | 25                    | 2500                   |

| Low    | Low                   | 50                    | 2500                   |

<sup>[</sup>a] A "middle" voltage level is defined in Table 22. Leaving the input pin open will also generate this level via a weak internal resistor network.

Alternatively, the user can directly access the registers for M, FDP, and PS over the serial interface for a wider range of options (see Table 4 for some examples).

Inputs do not support transmission of spread-spectrum clocking sources. Since this family is intended for high-performance applications, it will assume input reference sources to have stabilities of  $\pm 100$ ppm or better.

**Table 4. PLL Frequency Control Examples**

| f <sub>IN</sub> (MHz) | PS | FDP | f <sub>PFD</sub> (MHz) | М  | PLL Operating<br>Frequency (MHz) |

|-----------------------|----|-----|------------------------|----|----------------------------------|

| 25                    | 1  | 2   | 50                     | 50 | 2500                             |

| 39.0625               | 1  | 2   | 78.125                 | 32 | 2500                             |

| 50                    | 1  | 2   | 100                    | 25 | 2500                             |

| 100                   | 1  | 1   | 100                    | 25 | 2500                             |

| 125                   | 1  | 1   | 125                    | 20 | 2500                             |

| 156.25                | 1  | 1   | 156.25                 | 16 | 2500                             |

| 200                   | 2  | 1   | 100                    | 25 | 2500                             |

| 250                   | 2  | 1   | 125                    | 20 | 2500                             |

| 312.5                 | 2  | 1   | 156.25                 | 16 | 2500                             |

| 400                   | 4  | 1   | 100                    | 25 | 2500                             |

| 500                   | 4  | 1   | 125                    | 20 | 2500                             |

| 625                   | 4  | 1   | 156.25                 | 16 | 2500                             |

| 19.44                 | 1  | 2   | 38.88                  | 64 | 2488.32                          |

| 38.88                 | 1  | 2   | 77.76                  | 32 | 2488.32                          |

| 38.4                  | 1  | 2   | 76.8                   | 32 | 2457.6                           |

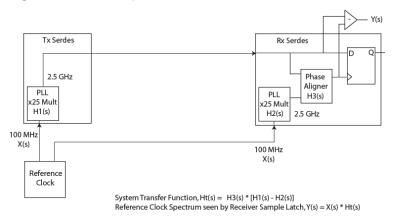

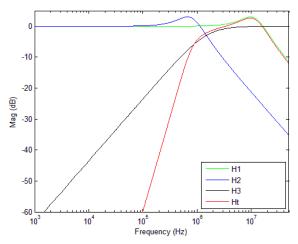

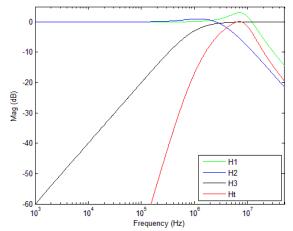

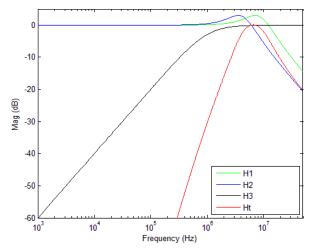

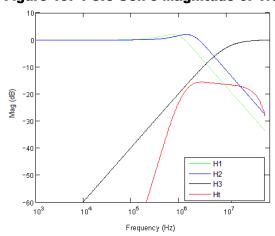

### **PLL Loop Bandwidth**

The 8V41NS0412 PLL requires external loop components (resistor and capacitors) connecting in between ICP and LFF pins. The PLL loop bandwidth generally depends on the loop components, charge pump current, PFD frequency, and VCO gain.

### **Output Divider Frequency Sources**

Output dividers associated with banks A, B and C take their input frequency directly from the PLL. Bank D also has the option to bypass the input frequency (after mux) directly to the output.

### Integer Output Dividers (Banks A, B, C, and D)

The 8V41NS0412 supports four integer output dividers: one per output bank. Each integer output divider block independently supports one of several divide ratios as shown in their respective register descriptions (Table 13, Table 14, Table 15, or Table 16). Selected divide ratios can be chosen directly from the control input pins for that particular output bank. The remaining ratios can only be selected via the serial interface. Bank D may choose whether to use the integer divider or a separate fractional divider to generate the output frequency.

Some example output frequencies are shown in Table 5 for the minimum  $f_{VCO}$  (2400MHz), the maximum  $f_{VCO}$  (2500MHz) and two other common VCO frequencies. With appropriate input frequencies and configuration selections, any  $f_{VCO}$  and  $f_{OUT}$  between the minimum and maximum can be generated.

**Table 5. Integer Output Divider Control Examples**

|              | (MHz)                      |                              |                               |                            |

|--------------|----------------------------|------------------------------|-------------------------------|----------------------------|

| Divide Ratio | f <sub>VCO</sub> = 2400MHz | f <sub>VCO</sub> = 2457.6MHz | f <sub>VCO</sub> = 2488.32MHz | f <sub>VCO</sub> = 2500MHz |

| 2            | 1200                       | 1228.8                       | 1244.16                       | 1250                       |

| 4            | 600                        | 614.4                        | 622.08                        | 625                        |

| 5            | 480                        | 491.52                       | 497.664                       | 500                        |

| 6            | 400                        | 409.6                        | 414.72                        | 416.667                    |

| 8            | 300                        | 307.2                        | 311.04                        | 312.5                      |

| 9            | 266.667                    | 273.07                       | 276.48                        | 277.78                     |

| 10           | 240                        | 245.76                       | 248.832                       | 250                        |

| 12           | 200                        | 204.8                        | 207.36                        | 208.333                    |

| 16           | 150                        | 153.6                        | 155.52                        | 156.25                     |

| 18           | 133.333                    | 136.533                      | 138.24                        | 138.889                    |

| 20           | 120                        | 122.88                       | 124.416                       | 125                        |

| 25           | 96                         | 98.3                         | 99.53                         | 100                        |

| 32           | 75                         | 76.8                         | 77.76                         | 78.125                     |

| 36           | 66.667                     | 68.267                       | 69.12                         | 69.444                     |

| 40           | 60                         | 61.44                        | 62.208                        | 62.5                       |

| 50           | 48                         | 49.152                       | 49.766                        | 50                         |

| 64           | 37.5                       | 38.4                         | 38.88                         | 39.063                     |

| 72           | 33.333                     | 34.133                       | 34.56                         | 34.722                     |

| 80           | 30                         | 30.72                        | 31.104                        | 31.25                      |

| 100          | 24                         | 24.576                       | 24.883                        | 25                         |

| 128          | 18.75                      | 19.2                         | 19.44                         | 19.531                     |

| 160          | 15                         | 15.36                        | 15.552                        | 15.625                     |

| 200          | 12                         | 12.29                        | 12.44                         | 12.5                       |

| 220          | 10.91                      | 11.17                        | 11.31                         | 11.36                      |

### Fractional Output Divider (Bank D)

For the fractional output divider in Bank D, the output divide ratio is given by:

$$f_{OUT} = \frac{f_{VCO}}{2 \times \left(FINT + \frac{FRAC}{2^{24}}\right) \times (FDIV)}$$

Where.

- FINT = Integer part: 5, 6, ...(2<sup>4</sup>-1) given by ND\_FINT[3:0]

- FRAC = Fractional part: 0, 1, 2, ...(2<sup>24</sup>-1) given by ND FRAC[23:0]

- FDIV = post-divider: 1, 2 or 4 given by ND\_DIVF[1:0]

This provides a frequency range of 20 to 250MHz.

#### **Output Drivers**

Each of the four output banks are provided with pin or register-controlled output drivers. Differential outputs can be individually selected as HCSL or POWER-DOWN. When powered-down, both outputs of the differential output pair and the single-ended QD1 output will be in High-Impedance state.

Note that under pin-control, all differential outputs within an output bank will assume the same configuration. Pin-control does not allow configuration of individual outputs within a bank.

#### **Pin Control of the Output Frequencies and Protocols**

For pin-control settings, see Table 6 to Table 10. All of the output frequencies assume  $f_{VCO}$  = 2500MHz. With different  $f_{VCO}$  configurations, the pins may still be used to select the indicated divide ratios for each bank, but the  $f_{OLIT}$  will be different.

The control pins do not affect the internal register values but act directly on the output structures. As a result, register values will not change to match the control input pin selections.

Each output bank can be powered up/down and enabled/ disabled by register bits. In the disabled state, an output will drive a logic low level. The default state is all outputs enabled. Pin-control does not require register access to enable the outputs. Additionally, individual outputs within a bank can be powered up/down by register bits only.

Table 6. Definition of Output Disabled / Power-down<sup>[a]</sup>

| Output Condition                                    | Q <sub>MN</sub> <sup>[b]</sup> | nQ <sub>MN</sub> <sup>[c]</sup> | QD1            |

|-----------------------------------------------------|--------------------------------|---------------------------------|----------------|

| DISABLED (register-control only)                    | LOW                            | HIGH                            | LOW            |

| Buffer POWER-DOWN (pin-control or register-control) | High-Impedance                 | High-Impedance                  | High-Impedance |

<sup>[</sup>a] Do not terminate the differential outputs when DISABLED or POWER-DOWN.

<sup>[</sup>b] Q<sub>MN</sub> refers to output pins QA[0:3], QB[0:3], QC[0:1], and QD0.

<sup>[</sup>c]  $nQ_{MN}$  refers to output pins nQA[0:3], nQB[0:3], nQC[0:1], and nQD0.

Table 7. Bank A Divider / Driver Pin-Control

(3-level control signals)

| NA[1]  | NA[0]  | Output Type             | Divide<br>Ratio | f <sub>OUT</sub><br>(MHz) |

|--------|--------|-------------------------|-----------------|---------------------------|

| Low    | Low    | HCSL                    | 16              | 156.25                    |

| Low    | Middle | HCSL                    | 10              | 250                       |

| Low    | High   | HCSL                    | 8               | 312.5                     |

| Middle | Low    | HCSL                    | 5               | 500                       |

| Middle | Middle | PD <sup>[a]</sup>       | -               | _                         |

| Middle | High   | HCSL                    | 20              | 125                       |

| High   | Low    | HCSL                    | 25              | 100                       |

| High   | Middle | HCSL                    | 50              | 50                        |

| High   | High   | Reserved <sup>[b]</sup> |                 |                           |

<sup>[</sup>a] PD denotes Power-down.

Table 8. Bank B Divider / Driver Pin-Control

(3-level control signals)

| NB[1]  | NB[0]  | Output Type       | Divide<br>Ratio | f <sub>OUT</sub><br>(MHz) |

|--------|--------|-------------------|-----------------|---------------------------|

| Low    | Low    | HCSL              | 16              | 156.25                    |

| Low    | Middle | HCSL              | 10              | 250                       |

| Low    | High   | HCSL              | 8               | 312.5                     |

| Middle | Low    | HCSL              | 5               | 500                       |

| Middle | Middle | PD <sup>[a]</sup> | _               | _                         |

| Middle | High   | HCSL              | 20              | 125                       |

| High   | Low    | HCSL              | 25              | 100                       |

| High   | Middle | HCSL              | 50              | 50                        |

| High   | High   | HCSL              | 100             | 25                        |

<sup>[</sup>a] PD denotes Power-down.

**Table 9. Bank C Divider / Driver Pin-Control** (3-level control signals)

| NC[1]  | NC[0]  | Output Type       | Divide<br>Ratio | f <sub>OUT</sub><br>(MHz) |

|--------|--------|-------------------|-----------------|---------------------------|

| Low    | Low    | HCSL              | 16              | 156.25                    |

| Low    | Middle | HCSL              | 10              | 250                       |

| Low    | High   | HCSL              | 8               | 312.5                     |

| Middle | Low    | HCSL              | 5               | 500                       |

| Middle | Middle | PD <sup>[a]</sup> | -               | _                         |

| Middle | High   | HCSL              | 20              | 125                       |

| High   | Low    | HCSL              | 25              | 100                       |

| High   | Middle | HCSL              | 50              | 50                        |

| High   | High   | HCSL              | 100             | 25                        |

<sup>[</sup>a] PD denotes Power-down.

**Table 10. Bank D Divider / Driver Pin-Control** (3-level control signals)

|        |        | QD0               | QD1                   | Divide | £                         |

|--------|--------|-------------------|-----------------------|--------|---------------------------|

| ND[1]  | ND[0]  | Outp              | ut Type               | Ratio  | f <sub>OUT</sub><br>(MHz) |

| Low    | Low    | HCSL              | Hi-Imp <sup>[a]</sup> | 16     | 156.25                    |

| Low    | Middle | HCSL              | Hi-Imp                | 20     | 125                       |

| Low    | High   | HCSL              | Hi-Imp                | 25     | 100                       |

| Middle | Low    | PD                | LVCMOS                | 75     | 33.333                    |

| Middle | Middle | PD <sup>[b]</sup> | Hi-Imp                | -      | _                         |

| Middle | High   | -                 | -                     | -      | _                         |

| High   | Low    | HCSL              | Hi-Imp                | 18.75  | 133.33                    |

| High   | Middle | HCSL              | Hi-Imp                | 37.5   | 66.66                     |

| High   | High   | HCSL              | LVCMOS                | N/A    | f <sub>IN</sub>           |

<sup>[</sup>a] Hi-Imp denotes High-Impedance.

<sup>[</sup>b] It is imperative not to connect or switch NA[1] and NA[0] pins to HIGH/Power Supply ( $V_{DD}$ ) at any time

<sup>[</sup>b] PD denotes Power-down.

### **Device Start-up and Reset Behavior**

The 8V41NS0412 has an internal power-on reset (POR) circuit. The POR circuit will remain active for a maximum of 175msec after device power-up when recommended CR (pin 25) value is used, 1.0uF. For faster power-up to Lock Time, a minimum CR value of 0.1uF can be used.

While in the reset state (POR active), the device will operate as follows:

- 1. All registers will return to and be held in their default states as indicated in the applicable register description.

- 2. All internal state machines will be in their reset conditions.

- 3. The serial interface will not respond to read or write cycles.

- 4. Lock status will be cleared.

Upon the internal POR circuit expiring, the device will exit reset and begin self-configuration. Self-configuration initiates the loading of appropriate values indicated by the control input pins and the default values into the registers indicated in the register descriptions.

Once the full configuration has been loaded, the device will respond to accesses on the serial port and will attempt to lock the PLL to the input frequency, if available. Once the PLL is locked, all the outputs will be synchronized.

### **Serial Control Port Description**

#### **Serial Control Port Configuration Description**

The 8V41NS0412 has a serial control port that can respond as a slave in an  $I^2C$  compatible configuration at a base address of 1101100b, to allow access to any of the internal registers for device programming or examination of internal status.

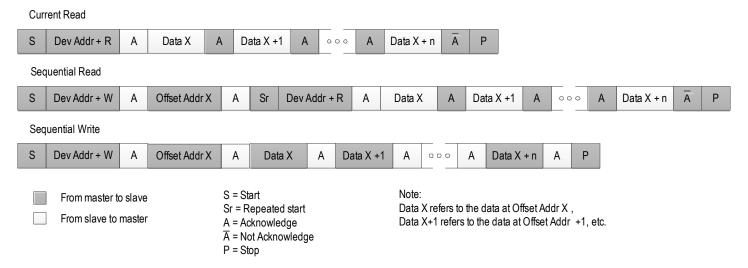

### I<sup>2</sup>C Mode Operation

The I<sup>2</sup>C interface is designed to fully support v1.2 of the I<sup>2</sup>C Specification for Fast mode operation. The 8V41NS0412 acts as a slave device on the I<sup>2</sup>C bus at 400kHz using a fixed base address of 1101100b. The interface accepts byte-oriented block write and block read operations. One address byte specifies the register address of the byte position of the first register to write or read. Data bytes (registers) are accessed in sequential order from the lowest to the highest byte (most significant bit first). Read and write block transfers can be stopped after any complete byte transfer.

For full electrical I<sup>2</sup>C compliance, it is recommended to use external pull-up resistors for SDATA and SCLK. The internal pull-up resistors have a size of  $51k\Omega$  typical.

Figure 3. I<sup>2</sup>C Slave Read and Write Cycle Sequencing

# **Register Description**

Table 11. Register Blocks

| Register Ranges Offset (Hex) | Register Block Description          |

|------------------------------|-------------------------------------|

| 00–08                        | Prescaler and PLL Control Registers |

| 09–0F                        | Reserved <sup>[a]</sup>             |

| 10–17                        | Bank A Control Registers            |

| 18–1F                        | Bank B Control Registers            |

| 20–27                        | Bank C Control Registers            |

| 28–31                        | Bank D Control Registers            |

| 32–3C                        | Reserved                            |

| 3D-40                        | Device Control Registers            |

| 41–FF                        | Reserved                            |

<sup>[</sup>a] Reserved registers should not be written to and have indeterminate read values.

Table 12. Prescaler and PLL Control Register Bit Field Locations and Descriptions

|               | Prescaler and PLL Control Register Block Field Locations |              |                   |      |       |         |  |      |  |  |  |  |

|---------------|----------------------------------------------------------|--------------|-------------------|------|-------|---------|--|------|--|--|--|--|

| Address (Hex) | D7                                                       | D6           | D5 D4 D3 D2 D1 D0 |      |       |         |  |      |  |  |  |  |

| 00            | Rsvd                                                     | Rsvd         |                   |      | PS    | S[5:0]  |  |      |  |  |  |  |

| 01            |                                                          |              |                   | Rsvd |       |         |  | FDP  |  |  |  |  |

| 02            |                                                          | Rsvd FIN_CTL |                   |      |       |         |  |      |  |  |  |  |

| 03            |                                                          |              |                   | R    | svd   |         |  |      |  |  |  |  |

| 04            |                                                          |              |                   | Rsvd |       |         |  | M[8] |  |  |  |  |

| 05            |                                                          |              |                   | M    | [7:0] |         |  |      |  |  |  |  |

| 06            |                                                          | Rsvd         |                   |      |       |         |  |      |  |  |  |  |

| 07            | Rsvd                                                     |              |                   |      |       |         |  |      |  |  |  |  |

| 08            |                                                          | Rsvd         |                   |      |       | CP[4:0] |  |      |  |  |  |  |

|                | Prescaler and PLL Control Register Block Field Descriptions |               |                                                                                                  |  |  |  |  |  |

|----------------|-------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit Field Name | Field Type                                                  | Default Value | Description                                                                                      |  |  |  |  |  |

| PS[5:0]        | R/W                                                         | 000000b       | Prescaler – scales input frequency by the value:                                                 |  |  |  |  |  |

|                |                                                             |               | 00h = Reserved                                                                                   |  |  |  |  |  |

|                |                                                             |               | 01h – 3Fh = divide by the value used (e.g. 04 = divide-by-4)                                     |  |  |  |  |  |

|                |                                                             |               | Note: When FDP = 1, prescalar values are ignored and have no impact on device functions.         |  |  |  |  |  |

| FDP            | R/W                                                         | 1b            | Input Frequency Doubler:                                                                         |  |  |  |  |  |

|                |                                                             |               | 0 = Disabled                                                                                     |  |  |  |  |  |

|                |                                                             |               | 1 = Enabled                                                                                      |  |  |  |  |  |

| FIN_CTL        | R/W                                                         | 0b            | Prescaler and PLL Configuration Control:                                                         |  |  |  |  |  |

|                |                                                             |               | 0 = PS, FDP, and M settings determined by FIN[1:0] control pins                                  |  |  |  |  |  |

|                |                                                             |               | 1 = PS, FDP, and M settings determined by register settings over I <sup>2</sup> C                |  |  |  |  |  |

| OSC_LOW        | R/W                                                         | 0b            | Crystal Oscillator Gain Control Selection:                                                       |  |  |  |  |  |

|                |                                                             |               | 0 = Normal gain for crystal frequencies of 25MHz and up                                          |  |  |  |  |  |

|                |                                                             |               | 1 = Low gain for crystal frequencies less than 25MHz                                             |  |  |  |  |  |

| M[8:0]         | R/W                                                         | 019h          | PLL Feedback Divider Ratio:                                                                      |  |  |  |  |  |

|                |                                                             |               | 000h–003h = Reserved (do not use)                                                                |  |  |  |  |  |

|                |                                                             |               | 004h–1FFh = Divide f <sub>VCO</sub> by the value (e.g. 04 = divide by -4)                        |  |  |  |  |  |

| CP[4:0]        | R/W                                                         | 11001b        | PLL Charge Pump Current Control:                                                                 |  |  |  |  |  |

|                |                                                             |               | $I_{CP} = 200 \mu A \times (CP[4:0] + 1)$                                                        |  |  |  |  |  |

|                |                                                             |               | Maximum charge pump current is 6.4mA. Default setting is 5.2mA: ((25 + 1) $\times$ 200 $\mu$ A). |  |  |  |  |  |

| Rsvd           | R/W                                                         | -             | Reserved. Always write 0 to this bit location. Read values are not defined.                      |  |  |  |  |  |

Table 13. Bank A Control Register Bit Field Locations and Descriptions

|               | Bank A Control Register Block Field Locations |          |                      |   |      |        |  |        |  |  |  |  |

|---------------|-----------------------------------------------|----------|----------------------|---|------|--------|--|--------|--|--|--|--|

| Address (Hex) | D7                                            | D6       | D6 D5 D4 D3 D2 D1 D0 |   |      |        |  |        |  |  |  |  |

| 10            | Rs                                            | vd       |                      |   | N.A  | \[5:0] |  |        |  |  |  |  |

| 11            |                                               |          |                      | R | svd  |        |  |        |  |  |  |  |

| 12            | PD_A                                          |          |                      | R | svd  |        |  | NA_CTL |  |  |  |  |

| 13            |                                               |          |                      | R | svd  |        |  |        |  |  |  |  |

| 14            | PD_QA0                                        |          |                      |   | Rsvd |        |  |        |  |  |  |  |

| 15            | PD_QA1                                        | QA1 Rsvd |                      |   |      |        |  |        |  |  |  |  |

| 16            | PD_QA2                                        | Rsvd     |                      |   |      |        |  |        |  |  |  |  |

| 17            | PD_QA3                                        |          |                      |   | Rsvd |        |  |        |  |  |  |  |

|                               | Bank A Control Register Block Field Descriptions |               |                                   |                                 |                                    |  |  |  |  |

|-------------------------------|--------------------------------------------------|---------------|-----------------------------------|---------------------------------|------------------------------------|--|--|--|--|

| Bit Field Name <sup>[a]</sup> | Field Type                                       | Default Value | Description                       |                                 |                                    |  |  |  |  |

| NA[5:0]                       | R/W                                              | 0Dh           | Divider Ratio for Bank A:         |                                 |                                    |  |  |  |  |

|                               |                                                  |               | Any changes made to this toggled. | s register will not take effect | until the INIT_CLK register bit is |  |  |  |  |

|                               |                                                  |               | 00 0000b = Reserved               |                                 |                                    |  |  |  |  |

|                               |                                                  |               | 00 0001b = Reserved               | 01 0110b = ÷30                  | 10 1011b = ÷88                     |  |  |  |  |

|                               |                                                  |               | 00 0010b = ÷2                     | 01 0111b = ÷32                  | 10 1100b = ÷90                     |  |  |  |  |

|                               |                                                  |               | 00 0011b = ÷3                     | 01 1000b = ÷33                  | 10 1101b = ÷96                     |  |  |  |  |

|                               |                                                  |               | 00 0100b = ÷4                     | 01 1001b = ÷35                  | 10 1110b = ÷100                    |  |  |  |  |

|                               |                                                  |               | 00 0101b = ÷5                     | 01 1010b = ÷36                  | 10 1111b = ÷108                    |  |  |  |  |

|                               |                                                  |               | 00 0110b = ÷6                     | 01 1011b = ÷40                  | 11 0000b = ÷110                    |  |  |  |  |

|                               |                                                  |               | 00 0111b = ÷8                     | 01 1100b = ÷42                  | 11 0001b = ÷112                    |  |  |  |  |

|                               |                                                  |               | 00 1000b = ÷9                     | 01 1101b = ÷44                  | 11 0010b = ÷120                    |  |  |  |  |

|                               |                                                  |               | 00 1001b = ÷10                    | 01 1110b = ÷45                  | 11 0011b = ÷128                    |  |  |  |  |

|                               |                                                  |               | 00 1010b = ÷12                    | 01 1111b = ÷48                  | 11 0100b = ÷132                    |  |  |  |  |

|                               |                                                  |               | 00 1011b = ÷14                    | 10 0000b = ÷50                  | 11 0101b = ÷140                    |  |  |  |  |

|                               |                                                  |               | 00 1100b = ÷15                    | 10 0001b = ÷54                  | 11 0110b = ÷144                    |  |  |  |  |

|                               |                                                  |               | 00 1101b = ÷16                    | 10 0010b = ÷55                  | 11 0111b = ÷160                    |  |  |  |  |

|                               |                                                  |               | 00 1110b = ÷18                    | 10 0011b = ÷56                  | 11 1000b = ÷176                    |  |  |  |  |

|                               |                                                  |               | 00 1111b = ÷20                    | 10 0100b = ÷60                  | 11 1001b = ÷180                    |  |  |  |  |

|                               |                                                  |               | 01 0000b = ÷21                    | 10 0101b = ÷64                  | 11 1010b = ÷200                    |  |  |  |  |

|                               |                                                  |               | 01 0001b = ÷22                    | 10 0110b = ÷66                  | 11 1011b = ÷220                    |  |  |  |  |

|                               |                                                  |               | 01 0010b = ÷24                    | 10 0111b = ÷70                  | 11 1100b = Reserved                |  |  |  |  |

|                               |                                                  |               | 01 0011b = ÷25                    | 10 1000b = ÷72                  | 11 1101b = Reserved                |  |  |  |  |

|                               |                                                  |               | 01 0100b = ÷27                    | 10 1001b = ÷80                  | 11 1110b = Reserved                |  |  |  |  |

|                               |                                                  |               | 01 0101b = ÷28                    | 10 1010b = ÷84                  | 11 1111b = Reserved                |  |  |  |  |

|                               | Bank A Control Register Block Field Descriptions                   |    |                                                                                                                                              |  |  |  |  |  |  |

|-------------------------------|--------------------------------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit Field Name <sup>[a]</sup> | Bit Field Name <sup>[a]</sup> Field Type Default Value Description |    |                                                                                                                                              |  |  |  |  |  |  |

| PD_A                          | R/W                                                                | 0b | Power-down Bank A:                                                                                                                           |  |  |  |  |  |  |

|                               |                                                                    |    | 0 = Bank A and all QA outputs powered and operate normally.                                                                                  |  |  |  |  |  |  |

|                               |                                                                    |    | 1 = Bank A and all QA outputs powered-down. When powering-down the output bank, it is recommended to also write a 1 to the PD_QAx registers. |  |  |  |  |  |  |

| NA_CTL                        | R/W                                                                | 0b | Bank A Configuration Control:                                                                                                                |  |  |  |  |  |  |

|                               |                                                                    |    | 0 = NA[5:0] and PD_A settings are determined by NA[1:0] control pins                                                                         |  |  |  |  |  |  |

|                               |                                                                    |    | 1 = NA[5:0] and PD_A settings are determined by register settings over I <sup>2</sup> C                                                      |  |  |  |  |  |  |

| PD_QAx                        | R/W                                                                | 0b | Power-down Output QAx:                                                                                                                       |  |  |  |  |  |  |

|                               |                                                                    |    | 0 = QAx output powered and operates normally                                                                                                 |  |  |  |  |  |  |

|                               |                                                                    |    | 1 = QAx output powered-down                                                                                                                  |  |  |  |  |  |  |

| Rsvd                          | R/W                                                                | -  | Reserved. Always write 0 to this bit location. Read values are not defined.                                                                  |  |  |  |  |  |  |

<sup>[</sup>a] Where x = 0, 1, 2, or 3.

Table 14. Bank B Control Register Bit Field Locations and Descriptions

|               | Bank B Control Register Block Field Locations |      |                                                                      |   |      |        |  |        |  |  |  |  |

|---------------|-----------------------------------------------|------|----------------------------------------------------------------------|---|------|--------|--|--------|--|--|--|--|

| Address (Hex) | D7                                            | D6   | D6         D5         D4         D3         D2         D1         D0 |   |      |        |  |        |  |  |  |  |

| 18            | Rs                                            | vd   |                                                                      |   | NE   | 3[5:0] |  |        |  |  |  |  |

| 19            |                                               |      |                                                                      | R | svd  |        |  |        |  |  |  |  |

| 1A            | PD_B                                          |      |                                                                      | R | svd  |        |  | NB_CTL |  |  |  |  |

| 1B            |                                               |      |                                                                      | R | svd  |        |  |        |  |  |  |  |

| 1C            | PD_QB0                                        |      |                                                                      |   | Rsvd |        |  |        |  |  |  |  |

| 1D            | PD_QB1                                        | Rsvd |                                                                      |   |      |        |  |        |  |  |  |  |

| 1E            | PD_QB2                                        | Rsvd |                                                                      |   |      |        |  |        |  |  |  |  |

| 1F            | PD_QB3                                        |      |                                                                      |   | Rsvd |        |  |        |  |  |  |  |

|                               | Bank B Control Register Block Field Descriptions |               |                                     |                                    |                              |  |  |  |  |

|-------------------------------|--------------------------------------------------|---------------|-------------------------------------|------------------------------------|------------------------------|--|--|--|--|

| Bit Field Name <sup>[a]</sup> | Field Type                                       | Default Value | Description                         |                                    |                              |  |  |  |  |

| NB[5:0]                       | R/W                                              | 0Dh           | Divider Ratio for Bank B:           |                                    |                              |  |  |  |  |

|                               |                                                  |               | Any changes made to this retoggled. | egister will not take effect until | the INIT_CLK register bit is |  |  |  |  |

|                               |                                                  |               | 00 0000b = Reserved                 |                                    |                              |  |  |  |  |

|                               |                                                  |               | 00 0001b = Reserved                 | 01 0110b = ÷30                     | 10 1011b = ÷88               |  |  |  |  |

|                               |                                                  |               | 00 0010b = ÷2                       | 01 0111b = ÷32                     | 10 1100b = ÷90               |  |  |  |  |

|                               |                                                  |               | 00 0011b = ÷3                       | 01 1000b = ÷33                     | 10 1101b = ÷96               |  |  |  |  |

|                               |                                                  |               | 00 0100b = ÷4                       | 01 1001b = ÷35                     | 10 1110b = ÷100              |  |  |  |  |

|                               |                                                  |               | 00 0101b = ÷5                       | 01 1010b = ÷36                     | 10 1111b = ÷108              |  |  |  |  |

|                               |                                                  |               | 00 0110b = ÷6                       | 01 1011b = ÷40                     | 11 0000b = ÷110              |  |  |  |  |

|                               |                                                  |               | 00 0111b = ÷8                       | 01 1100b = ÷42                     | 11 0001b = ÷112              |  |  |  |  |

|                               |                                                  |               | 00 1000b = ÷9                       | 01 1101b = ÷44                     | 11 0010b = ÷120              |  |  |  |  |

|                               |                                                  |               | 00 1001b = ÷10                      | 01 1110b = ÷45                     | 11 0011b = ÷128              |  |  |  |  |

|                               |                                                  |               | 00 1010b = ÷12                      | 01 1111b = ÷48                     | 11 0100b = ÷132              |  |  |  |  |

|                               |                                                  |               | 00 1011b = ÷14                      | 10 0000b = ÷50                     | 11 0101b = ÷140              |  |  |  |  |

|                               |                                                  |               | 00 1100b = ÷15                      | 10 0001b = ÷54                     | 11 0110b = ÷144              |  |  |  |  |

|                               |                                                  |               | 00 1101b = ÷16                      | 10 0010b = ÷55                     | 11 0111b = ÷160              |  |  |  |  |

|                               |                                                  |               | 00 1110b = ÷18                      | 10 0011b = ÷56                     | 11 1000b = ÷176              |  |  |  |  |

|                               |                                                  |               | 00 1111b = ÷20                      | 10 0100b = ÷60                     | 11 1001b = ÷180              |  |  |  |  |

|                               |                                                  |               | 01 0000b = ÷21                      | 10 0101b = ÷64                     | 11 1010b = ÷200              |  |  |  |  |

|                               |                                                  |               | 01 0001b = ÷22                      | 10 0110b = ÷66                     | 11 1011b = ÷220              |  |  |  |  |

|                               |                                                  |               | 01 0010b = ÷24                      | 10 0111b = ÷70                     | 11 1100b = Reserved          |  |  |  |  |

|                               |                                                  |               | 01 0011b = ÷25                      | 10 1000b = ÷72                     | 11 1101b = Reserved          |  |  |  |  |

|                               |                                                  |               | 01 0100b = ÷27                      | 10 1001b = ÷80                     | 11 1110b = Reserved          |  |  |  |  |

|                               |                                                  |               | 01 0101b = ÷28                      | 10 1010b = ÷84                     | 11 1111b = Reserved          |  |  |  |  |

|                                                                    | Bank B Control Register Block Field Descriptions |    |                                                                                                                                              |  |  |  |  |  |  |

|--------------------------------------------------------------------|--------------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit Field Name <sup>[a]</sup> Field Type Default Value Description |                                                  |    |                                                                                                                                              |  |  |  |  |  |  |

| PD_B                                                               | R/W                                              | 0b | Power-down Bank B:                                                                                                                           |  |  |  |  |  |  |

|                                                                    |                                                  |    | 0 = Bank B and all QB outputs powered and operate normally                                                                                   |  |  |  |  |  |  |

|                                                                    |                                                  |    | 1 = Bank B and all QB outputs powered-down. When powering-down the output bank, it is recommended to also write a 1 to the PD_QBx registers. |  |  |  |  |  |  |

| NB_CTL                                                             | R/W                                              | 0b | Bank B Configuration Control:                                                                                                                |  |  |  |  |  |  |

|                                                                    |                                                  |    | 0 = NB[5:0] and PD_B settings are determined by NB[1:0] control pins                                                                         |  |  |  |  |  |  |

|                                                                    |                                                  |    | 1 = NB[5:0] and PD_B settings are determined by register settings over I <sup>2</sup> C                                                      |  |  |  |  |  |  |

| PD_QBx                                                             | R/W                                              | 0b | Power-down Output QBx:                                                                                                                       |  |  |  |  |  |  |

|                                                                    |                                                  |    | 0 = QBx output powered and operates normally.                                                                                                |  |  |  |  |  |  |

|                                                                    |                                                  |    | 1 = QBx output powered-down                                                                                                                  |  |  |  |  |  |  |

| Rsvd                                                               | R/W                                              | -  | Reserved. Always write 0 to this bit location. Read values are not defined.                                                                  |  |  |  |  |  |  |

<sup>[</sup>a] Where x = 0, 1, 2, or 3.

Table 15. Bank C Control Register Bit Field Locations and Descriptions

|               | Bank C Control Register Block Field Locations |      |      |    |     |       |    |        |  |  |  |  |

|---------------|-----------------------------------------------|------|------|----|-----|-------|----|--------|--|--|--|--|

| Address (Hex) | D7                                            | D6   | D5   | D4 | D3  | D2    | D1 | D0     |  |  |  |  |

| 20            | Rs                                            | vd   |      |    | NC  | [5:0] |    |        |  |  |  |  |

| 21            |                                               |      |      | R  | svd |       |    |        |  |  |  |  |

| 22            | PD_C                                          |      |      | R  | svd |       |    | NC_CTL |  |  |  |  |

| 23            |                                               |      |      | R  | svd |       |    |        |  |  |  |  |

| 24            | PD_QC0                                        | Rsvd |      |    |     |       |    |        |  |  |  |  |

| 25            | PD_QC1                                        |      | Rsvd |    |     |       |    |        |  |  |  |  |

|                               | Bank C Control Register Block Field Descriptions |               |                                                                                                                                              |                                 |                                    |  |  |  |  |  |

|-------------------------------|--------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------------|--|--|--|--|--|

| Bit Field Name <sup>[a]</sup> | Field Type                                       | Default Value |                                                                                                                                              | Description                     |                                    |  |  |  |  |  |

| NC[5:0]                       | R/W                                              | 0Dh           | Divider Ratio for Bank C:                                                                                                                    |                                 |                                    |  |  |  |  |  |

|                               |                                                  |               | Any changes made to this toggled.                                                                                                            | s register will not take effect | until the INIT_CLK register bit is |  |  |  |  |  |

|                               |                                                  |               | 00 0000b = Reserved                                                                                                                          |                                 |                                    |  |  |  |  |  |

|                               |                                                  |               | 00 0001b = Reserved                                                                                                                          | 01 0110b = ÷30                  | 10 1011b = ÷88                     |  |  |  |  |  |

|                               |                                                  |               | 00 0010b = ÷2                                                                                                                                | 01 0111b = ÷32                  | 10 1100b = ÷90                     |  |  |  |  |  |