# 1.8V Low-Power Wide-Range Frequency Clock Driver

### **Recommended Application:**

- DDR2 Memory Modules / Zero Delay Board Fan Out

- Provides complete DDR DIMM logic solution with ICSSSTU32864/SSTUF32864/SSTUF32866

### **Product Description/Features:**

- Low skew, low jitter PLL clock driver

- 1 to 4 differential clock distribution (SSTL\_18)

- Feedback pins for input to output synchronization

- Spread Spectrum tolerant inputs

- Auto PD when input signal is at a certain logic state

### **Switching Characteristics:**

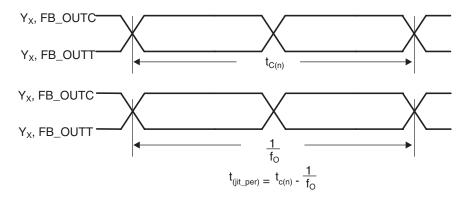

Period jitter: 40ps

Half-period jitter: 60ps

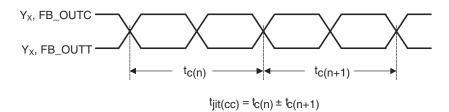

• CYCLE - CYCLE jitter 40ps

• OUTPUT - OUTPUT skew: 40ps

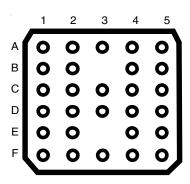

# Pin Configuration

28-Ball BGA Top View

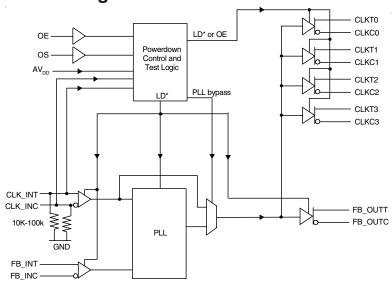

## **Block Diagram**

## \* The Logic Detect (LD) powers down the device when a logic low is applied to both CLK\_INT and CLK\_INC.

## **Ball Assignments**

|   |        | •        |          |          |         |

|---|--------|----------|----------|----------|---------|

|   | 1      | 2        | 3        | 4        | 5       |

| Α | CLKT0  | CLKC0    | CLKC1    | CLKT1    | FB_INT  |

| В | CK_INT | $V_{DD}$ | NB       | $V_{DD}$ | FB_INC  |

| С | CK_INC | OE       | $V_{DD}$ | os       | FB_OUTC |

| D | AGND   | GND      | $V_{DD}$ | GND      | FB_OUTT |

| E | AVDD   | GND      | NB       | GND      | GND     |

| F | CLKC3  | CLKT3    | CLKC2    | CLKT2    | GND     |

### **Pin Descriptions**

| Terminal<br>Name | Description                                                     | Electrical<br>Characteristics |

|------------------|-----------------------------------------------------------------|-------------------------------|

| AGND             | Analog Ground                                                   | Ground                        |

| AV <sub>DD</sub> | Analog power                                                    | 1.8 V nominal                 |

| CLK_INT          | Clock input with a (10K-100K Ohm) pulldown resistor             | Differential input            |

| CLK_INC          | Complentary clock input with a (10K-100K Ohm) pulldown resistor | Differential input            |

| FB_INT           | Feedback clock input                                            | Differential input            |

| FB_INC           | Complementary feedback clock input                              | Differential input            |

| FB_OUTT          | Feedback clock output                                           | Differential output           |

| FB_OUTC          | Complementary feedback clock output                             | Differential output           |

| OE               | Output Enable (Asynchronous)                                    | LVCMOS input                  |

| OS               | Output Select (tied to GND or V <sub>DDQ</sub> )                | LVCMOS input                  |

| GND              | Ground                                                          | Ground                        |

| V <sub>DDQ</sub> | Logic and output power                                          | 1.8V nominal                  |

| CLKT[0:3]        | Clock outputs                                                   | Differential outputs          |

| CLKC[0:3]        | Complementary clock outputs                                     | Differential outputs          |

| NB               | No ball                                                         |                               |

The PLL clock buffer, **ICS97ULP844A**, is designed for a  $V_{DDQ}$  of 1.8 V, a AV<sub>DD</sub> of 1.8 V and differential data input and output levels. Package options include a plastic 28-ball VFBGA.

ICS97ULP844A is a zero delay buffer that distributes a differential clock input pair (CLK\_INT, CLK\_INC) to four differential pair of clock outputs (CLKT[0:3], CLKC[0:3]) and one differential pair feedback clock outputs (FB\_OUTT, FBOUTC). The clock outputs are controlled by the input clocks (CLK\_INT, CLK\_INC), the feedback clocks (FB\_INT, FB\_INC), the LVCMOS program pins (OE, OS) and the Analog Power input (AVDD). When OE is low, the outputs (except FB\_OUTT/FB\_OUTC) are disabled while the internal PLL continues to maintain its locked-in frequency. OS (Output Select) is a program pin that must be tied to GND or  $V_{DDQ}$ . When OS is high, OE will function as described above. When OS is low, OE has no effect on CLKT2/CLKC2 (they are free running in addition to FB\_OUTT/FB\_OUTC). When AVDD is grounded, the PLL is turned off and bypassed for test purposes.

When both clock signals (CLK\_INT, CLK\_INC) are logic low, the device will enter a low power mode. An input logic detection circuit on the differential inputs, independent from the input buffers, will detect the logic low level and perform a low power state where all outputs, the feedback and the PLL are OFF. When the inputs transition from both being logic low to being differential signals, the PLL will be turned back on, the inputs and outputs will be enabled and the PLL will obtain phase lock between the feedback clock pair (FB\_INT, FB\_INC) and the input clock pair (CLK\_INT, CLK\_INC) within the specified stabilization time tstab.

The PLL in **ICS97ULP844A** clock driver uses the input clocks (CLK\_INT, CLK\_INC) and the feedback clocks (FB\_INT, FB\_INC) to provide high-performance, low-skew, low-jitter output differential clocks (CLKT[0:4], CLKC[0:4]). **ICS97ULP844A** is also able to track Spread Spectrum Clocking (SSC) for reduced EMI.

ICS97ULP844A is characterized for operation from 0°C to 70°C.

1110A-05/16/05

# **Function Table**

|           |    | Inp | outs    |         | Outputs                   |                           |         |         | PLL          |  |

|-----------|----|-----|---------|---------|---------------------------|---------------------------|---------|---------|--------------|--|

| AVDD      | OE | os  | CLK_INT | CLK_INT | CLKT                      | CLKC                      | FB_OUTT | FB_OUTC | PLL          |  |

| GND       | Н  | Х   | L       | Н       | L                         | Н                         | L       | Н       | Bypassed/Off |  |

| GND       | Н  | Х   | Н       | L       | Н                         | L                         | Н       | L       | Bypassed/Off |  |

| GND       | L  | Н   | L       | Н       | *L(Z)                     | *L(Z)                     | L       | Н       | Bypassed/Off |  |

| GND       | L  | L   | Н       | L       | *L(Z),<br>CLKT2<br>active | *L(Z),<br>CLKC2<br>active | Н       | L       | Bypassed/Off |  |

| 1.8V(nom) | L  | Н   | L       | Н       | *L(Z)                     | *L(Z)                     | L       | Н       | On           |  |

| 1.8V(nom) | L  | L   | Н       | L       | *L(Z),<br>CLKT2<br>active | *L(Z),<br>CLKC2<br>active | Н       | L       | On           |  |

| 1.8V(nom) | Н  | Х   | L       | Н       | L                         | Н                         | L       | Н       | On           |  |

| 1.8V(nom) | Н  | Х   | Н       | L       | Н                         | L                         | Н       | L       | On           |  |

| 1.8V(nom) | Х  | Х   | L       | L       | *L(Z)                     | *L(Z)                     | *L(Z)   | *L(Z)   | Off          |  |

| 1.8V(nom) | Х  | Х   | Н       | Н       | Reserved                  |                           |         |         |              |  |

$<sup>^{\</sup>star}L(Z)$  means the outputs are disabled to a low stated meeting the  $I_{ODL}$  limit.

## **Absolute Maximum Ratings**

Supply Voltage (VDDQ & AVDD) .....-0.5V to 2.5V

Ambient Operating Temperature . . . . . . 0°C to +70°C Storage Temperature . . . . . -65°C to +150°C

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

### **Electrical Characteristics - Input/Supply/Common Output Parameters**

$TA = 0 - 70^{\circ}C$ ; Supply Voltage AVDDQ, VDDQ = 1.8 V +/- 0.1V (unless otherwise stated)

| PARAMETER                                  | SYMBOL             | CONDITIONS                                  | MIN                    | TYP  | MAX  | UNITS |

|--------------------------------------------|--------------------|---------------------------------------------|------------------------|------|------|-------|

| Input High Current (CLK_INT, CLK_INC)      | I <sub>IH</sub>    | $V_I = V_{DDQ}$ or GND                      |                        |      | ±250 | μΑ    |

| Input Low Current (OE, OS, FB_INT, FB_INC) | I <sub>IL</sub>    | $V_I = V_{DDQ}$ or GND                      |                        |      | ±10  | μΑ    |

| Output Disabled Low<br>Current             | I <sub>ODL</sub>   | OE = L, V <sub>ODL</sub> = 100mV            | 100                    |      |      | μΑ    |

| Operating Supply                           | I <sub>DD1.8</sub> | C <sub>L</sub> = 0pf @ 270MHz               |                        |      | TBD  | mA    |

| Current                                    | I <sub>DDLD</sub>  | $C_L = 0pf$                                 |                        |      | 500  | μΑ    |

| Input Clamp Voltage                        | $V_{IK}$           | $V_{DDQ} = 1.7V \text{ lin} = -18\text{mA}$ |                        |      | -1.2 | V     |

| High lovel output voltage                  | $V_{OH}$           | I <sub>OH</sub> = -100 μA                   | V <sub>DDQ</sub> - 0.2 |      |      | V     |

| High-level output voltage                  | <b>∨</b> OH        | I <sub>OH</sub> = -9 mA                     | 1.1                    | 1.45 |      | V     |

| Low lovel output voltage                   | V <sub>OL</sub>    | I <sub>OL</sub> =100 μA                     |                        | 0.25 | 0.10 | V     |

| Low-level output voltage                   | <b>V</b> OL        | I <sub>OL</sub> =9 mA                       |                        |      | 0.6  | V     |

| Input Capacitance <sup>1</sup>             | C <sub>IN</sub>    | $V_I = GND \text{ or } V_{DDQ}$             | 2                      |      | 3    | pF    |

| Output Capacitance <sup>1</sup>            | C <sub>OUT</sub>   | $V_{OUT} = GND \text{ or } V_{DDQ}$         | 2                      |      | 3    | pF    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Recommended Operating Condition** (see note1)

$T_A = 0 - 70$ °C; Supply Voltage AVDD, VDDQ = 1.8 V +/- 0.1V (unless otherwise stated)

| PARAMETER                                      | SYMBOL             | CONDITIONS                               | MIN                        | TYP                | MAX                     | UNITS |

|------------------------------------------------|--------------------|------------------------------------------|----------------------------|--------------------|-------------------------|-------|

| Supply Voltage                                 | $V_{DDQ}, A_{VDD}$ |                                          | 1.7                        | 1.8                | 1.9                     | V     |

| Low level input voltage                        | V <sub>IL</sub>    | CLK_INT, CLK_INC, FB_INC, FB_INT         |                            |                    | 0.35 x V <sub>DDQ</sub> | ٧     |

|                                                |                    | OE, OS                                   |                            |                    | 0.35 x V <sub>DDQ</sub> | V     |

| High level input voltage                       | V <sub>IH</sub>    | CLK_INT, CLK_INC, FB_INC, FB_INT         | 0.65 x V <sub>DDQ</sub>    |                    |                         | V     |

|                                                |                    | OE, OS                                   | 0.65 x V <sub>DDQ</sub>    |                    |                         | V     |

| DC input signal voltage (note 2)               | V <sub>IN</sub>    |                                          | -0.3                       |                    | V <sub>DDQ</sub> + 0.3  | V     |

| Differential input signal                      | V                  | DC - CLK_INT, CLK_INC,<br>FB_INC, FB_INT | 0.3                        |                    | V <sub>DDQ</sub> + 0.4  | V     |

| voltage (note 3)                               | V <sub>ID</sub>    | AC - CLK_INT, CLK_INC, FB_INC, FB_INT    | 0.6                        |                    | V <sub>DDQ</sub> + 0.4  | V     |

| Output differential cross-<br>voltage (note 4) | V <sub>OX</sub>    |                                          | V <sub>DDQ</sub> /2 - 0.10 |                    | $V_{DDQ}/2 + 0.10$      | V     |

| Input differential cross-<br>voltage (note 4)  | V <sub>IX</sub>    |                                          | V <sub>DDQ</sub> /2 - 0.15 | V <sub>DD</sub> /2 | $V_{DDQ}2 + 0.15$       | V     |

| High level output current                      | I <sub>OH</sub>    |                                          |                            |                    | -9                      | mA    |

| Low level output current                       | I <sub>OL</sub>    |                                          |                            |                    | 9                       | mA    |

| Operating free-air temperature                 | T <sub>A</sub>     |                                          | 0                          |                    | 70                      | °C    |

#### Notes:

- 1. Unused inputs must be held high or low to prevent them from floating.

- 2. DC input signal voltage specifies the allowable DC execution of differential input.

- 3. Differential inputs signal voltages specifies the differential voltage [VTR-VCP] required for switching, where VTR is the true input level and VCP is the complementary input level.

- 4. Differential cross-point voltage is expected to track variations of V<sub>DDQ</sub> and is the voltage at which the differential signal must be crossing.

### **Timing Requirements**

$T_A = 0 - 70^{\circ}C$  Supply Voltage AVDD, VDDQ = 1.8 V +/- 0.1V (unless otherwise stated)

|                                |                     | •                |     |     |      |

|--------------------------------|---------------------|------------------|-----|-----|------|

| PARAMETER                      | SYMBOL              | CONDITIONS       | MIN | TYP | MAX  |

| Max clock frequency            | freq <sub>op</sub>  | 1.8V±0.1V @ 25°C | 95  |     | 370  |

| Application Frequency<br>Range | freq <sub>App</sub> | 1.8V±0.1V @ 25°C | 160 |     | 350  |

| Input clock duty cycle         | d <sub>tin</sub>    |                  | 40  |     | 60   |

| CLK stabilization              | T <sub>STAB</sub>   |                  |     | 2.4 | 2.95 |

# **Switching Characteristics**<sup>1</sup>

$T_A = 0 - 70^{\circ}C$  Supply Voltage AVDD, VDDQ = 1.8 V +/- 0.1V (unless otherwise stated)

|                              |                               | ,                        |       | ,    |       |       |

|------------------------------|-------------------------------|--------------------------|-------|------|-------|-------|

| PARAMETER                    | SYMBOL                        | CONDITION                | MIN   | TYP  | MAX   | UNITS |

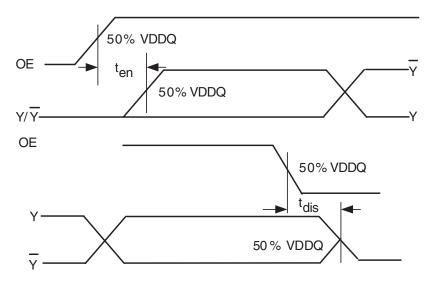

| Output enable time           | t <sub>en</sub>               | OE to any output         |       | 4.73 | 8     | ns    |

| Output disable time          | t <sub>dis</sub>              | OE to any output         |       | 5.82 | 8     | ns    |

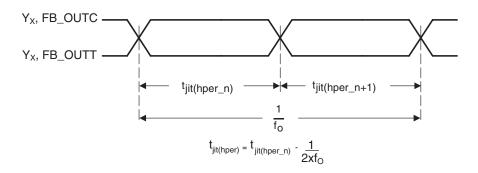

| Period jitter                | t <sub>jit (per)</sub>        |                          | -30   |      | 30    | ps    |

| Half-period jitter           | t <sub>jit(hper)</sub>        |                          | -60   |      | 60    | ps    |

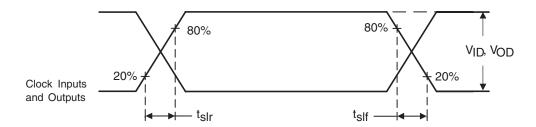

| Input alow rate              |                               | Input Clock              | 1     | 2.5  | 4     | v/ns  |

| Input slew rate              | SLr1(i)                       | Output Enable (OE), (OS) | 0.5   |      |       | v/ns  |

| Output clock slew rate       | SLr1(o)                       |                          | 1.5   | 2.5  | 3     | v/ns  |

| O   - t     :: t             | $t_{jit(\mathtt{cc+})}$       |                          | 0     |      | 40    | ps    |

| Cycle-to-cycle period jitter | t <sub>jit(cc-)</sub>         |                          | 0     |      | -40   | ps    |

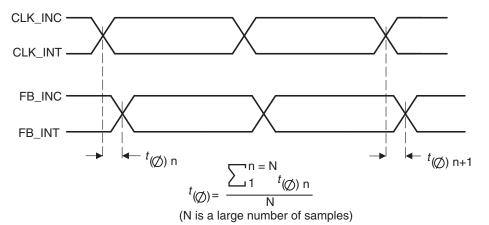

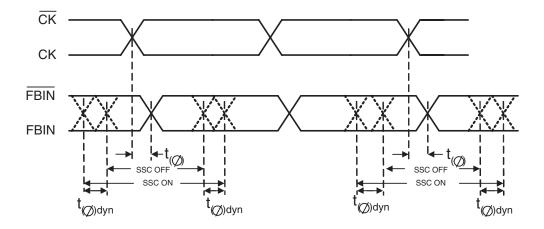

| Dynamic Phase Offset         | t <sub>( )dyn</sub>           |                          | -20   |      | 20    | ps    |

| Static Phase Offset          | t <sub>SPO</sub> <sup>2</sup> |                          | -50   | 0    | 50    | ps    |

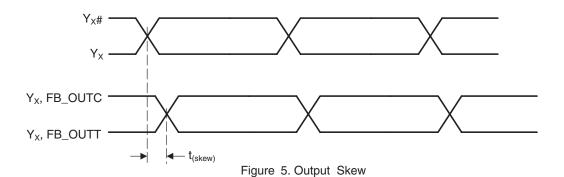

| Output to Output Skew        | t <sub>skew</sub>             |                          |       |      | 40    | ps    |

| SSC modulation frequency     |                               |                          | 30.00 |      | 33    | kHz   |

| SSC clock input frequency    |                               |                          | 0.00  |      | -0.50 | %     |

| deviation                    |                               |                          | 0.00  |      | -0.50 | /0    |

| PLL Loop bandwidth (-3 dB    |                               |                          | 2.0   |      |       | MHz   |

| from unity gain)             |                               |                          | 2.0   |      |       | IVITZ |

### Notes:

- 1. Switching characteristics guaranteed for application frequency range.

- 2. Static phase offset shifted by design.

#### Parameter Measurement Information

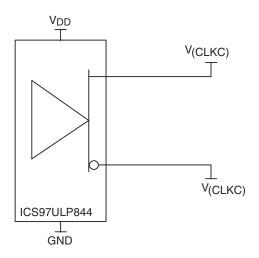

Figure 1. IBIS Model Output Load

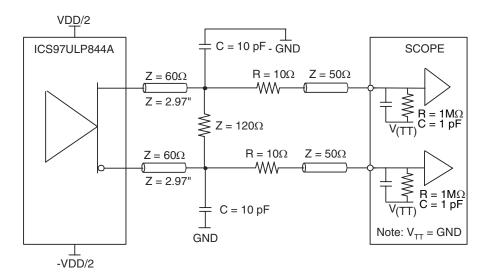

Figure 2. Output Load Test Circuit

Figure 3. Cycle-to-Cycle Jitter

#### Parameter Measurement Information

Figure 4. Static Phase Offset

Figure 6. Period Jitter

#### Parameter Measurement Information

Figure 7. Half-Period Jitter

Figure 8. Input and Output Slew Rates

Figure 9. Dynamic Phase Offset

Figure 10. Time delay between OE and Clock Output  $(Y, \overline{Y})$

# RENESAS

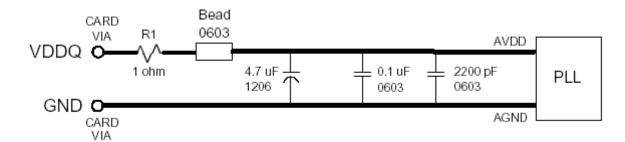

Figure 11.  $AV_{DD}$  Filtering

- Place the 2200pF capacitor close to the PLL.

- Use a wide trace for the PLL analog power & ground. Connect PLL & caps to AGND trace & connect trace to one GND via (farthest from PLL).

- Recommended bead: Fair-Rite P/N 2506036017Y0 or equivalent (0.8 Ohm DC max, 600 Ohms @ 100 MHz).

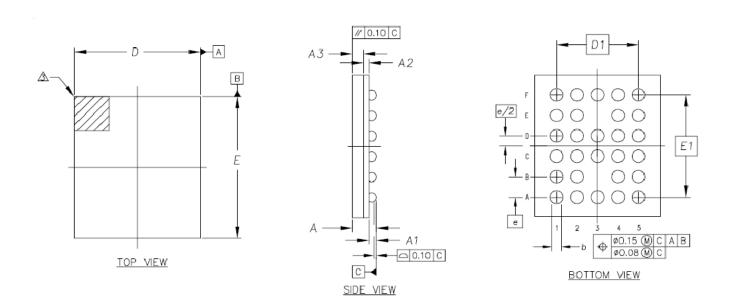

# RENESAS

| SYMBOL |                    | Millimeter |       |           | Inch      |       |

|--------|--------------------|------------|-------|-----------|-----------|-------|

|        | MIN                | NOM        | MAX   | MIN       | NOM       | MAX   |

| Α      | 0.80               | 0.90       | 1.00  | 0.031     | 0.035     | 0.039 |

| A1     | 0.165              | 0.20       | 0.235 | 0.006     | 0.008     | 0.009 |

| A2     | 0.16               | 0.20       | 0.24  | 0.006     | 0.008     | 0.009 |

| A3     | 0.475              | 0.50       | 0.525 | 0.019     | 0.020     | 0.021 |

| b      | 0.35               | 0.40       | 0.45  | 0.014     | 0.016     | 0.018 |

| D      | 3.90               | 4.00       | 4.10  | 0.154     | 0.157     | 0.161 |

| D1     | 2.60 BSC 0.102 BSC |            |       |           |           |       |

| E      | 4.40               | 4.50       | 4.60  | 0.173     | 0.177     | 0.181 |

| E1     | 3.25 BSC           |            |       |           | 0.128 BSC |       |

| е      |                    | 0.65 BSC   |       | 0.026 BSC |           |       |

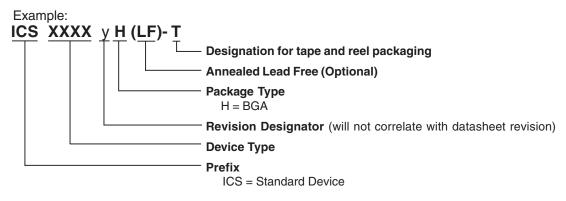

# **Ordering Information**

## ICS97ULP844AyH(LF)-T

1110A-05/16/05

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.