## CA91L862A (QSpan II)

### PowerQUICC-to-PCI Bridge

The CA91L862A is a PCI-to-Host processor bridge for the NXP® PowerQUICC (MPC860/850/821), the QUICC (MC68360), and the MC68040.

The CA91L862A operates at speeds up to 50 MHz on the Host processor bus, with programmable parity and burst/prefetch capability. Its 32-bit/33 MHz PCI 2.2 Interface support is ideal for embedded processor applications.

Another key feature of the CA91L862A is its integrated PCI bus arbiter. This arbiter supports up to seven external bus masters and uses a fairness algorithm to prevent deadlocks on the bus.

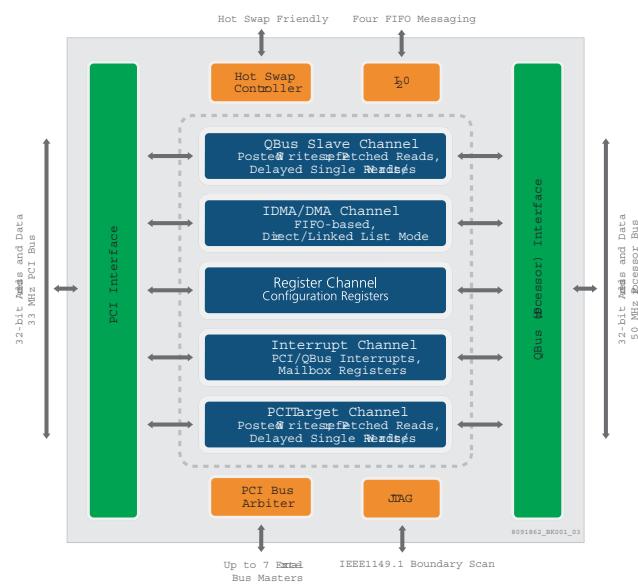

### Block Diagram

### Features

- High-Performance Processor Interface

- MPC860 interface supports prefetched reads and burst writes

- Operates up to 50 MHz

- High-Performance PCI Bus Interface

- Zero-wait state bursts, prefetch reads and writes on PCI

- Serial EEPROM interface for Plug and Play compatibility on PCI

- Universal PCI signaling (3.3 and 5V compliant)

- PCI version 2.2 Enhancements

- Vital Product Data: offers an improved method of communicating board-specific information to the system

- PCI Power Management interface: enables operating systems to control the power supplied to CA91L862A related hardware (for example, an add-in card)

- Integrated PCI Bus Arbiter

- Supports up to seven external bus masters

- Fairness algorithm for preventing deadlocks

- CompactPCI Hot Swap Friendly

- High-performance DMA controller with support for Direct and Linked List modes

- Mailbox registers for passing parameters between host and embedded environments

### Applications

- LAN/WAN Infrastructure

- Network interface cards

- Routers (including SOHO applications)

- Servers

- Remote and Local Access Equipment

- xDSL concentrators

- VoIP gateways

- CPE Equipment

- Process control equipment

- Data acquisition systems

## Contents

|                                          |           |

|------------------------------------------|-----------|

| <b>1. Overview</b>                       | <b>3</b>  |

| 1.1 Typical Applications                 | 3         |

| <b>2. Pin Information</b>                | <b>4</b>  |

| 2.1 Terminology                          | 4         |

| 2.2 Overview                             | 4         |

| 2.3 Pin Assignments                      | 5         |

| 2.4 Pin Descriptions                     | 7         |

| <b>3. Signals and DC Characteristics</b> | <b>18</b> |

| 3.1 Terminology                          | 18        |

| 3.2 Packaging and Voltage Level Support  | 18        |

| 3.3 Signals and DC Characteristics       | 18        |

| <b>4. Specifications</b>                 | <b>28</b> |

| 4.1 Absolute Maximum Ratings             | 28        |

| 4.2 Recommended Operating Conditions     | 28        |

| 4.3 Thermal Specifications               | 28        |

| 4.4 Power Dissipation                    | 29        |

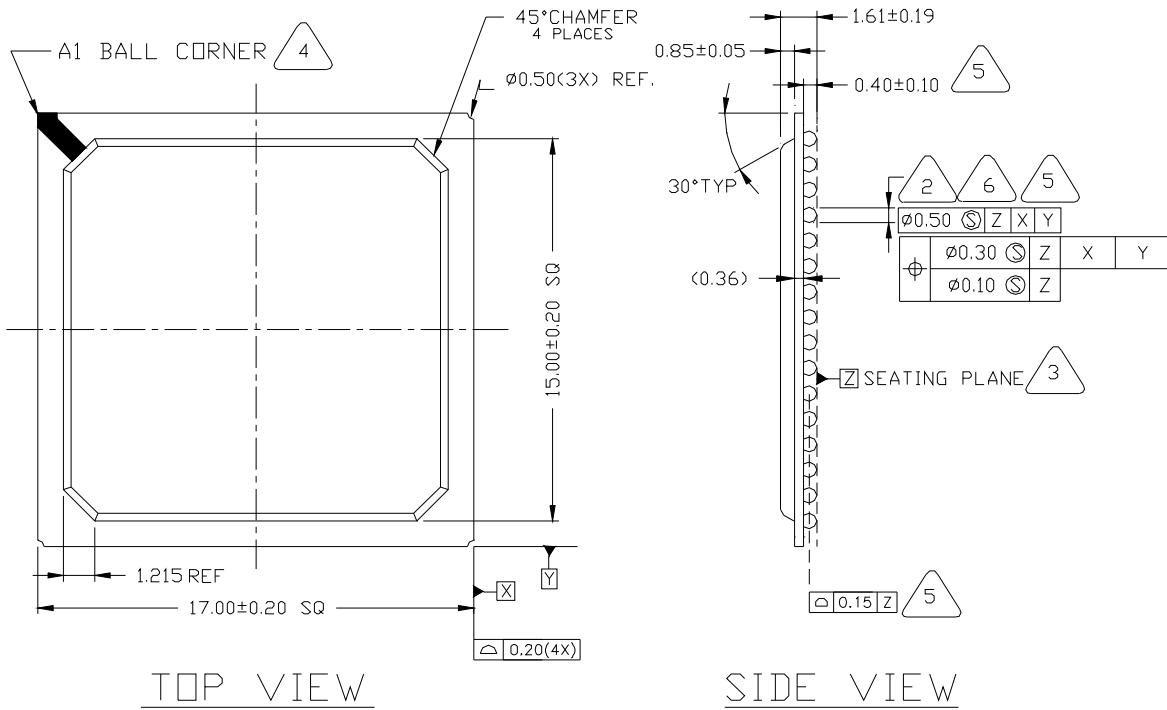

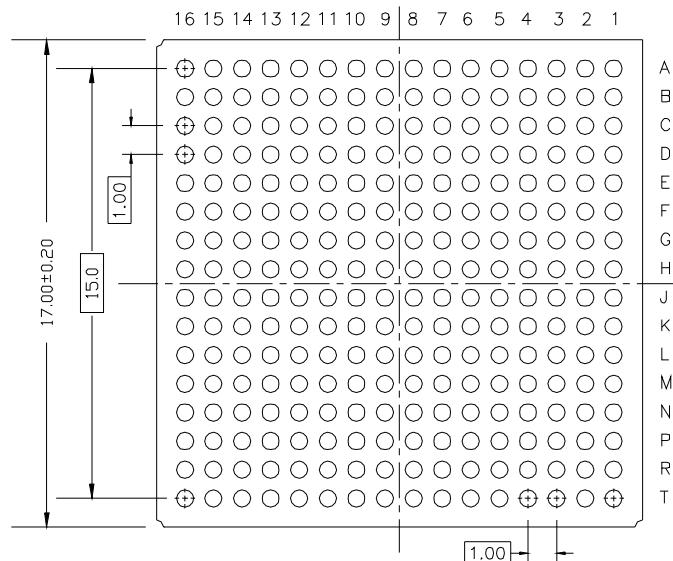

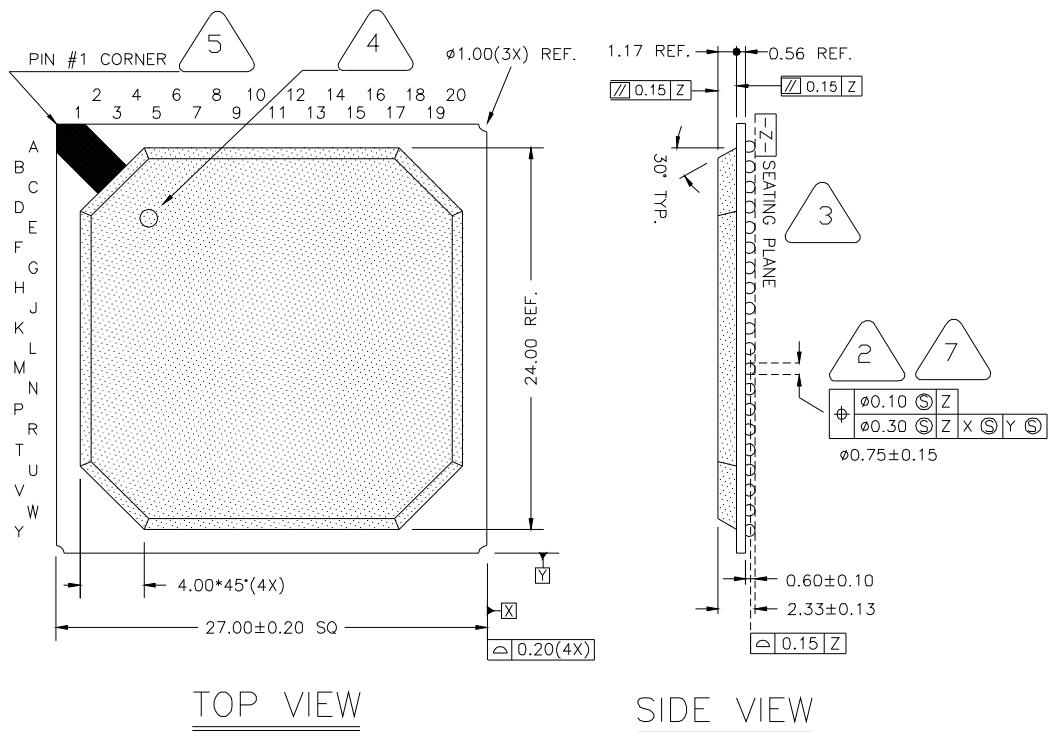

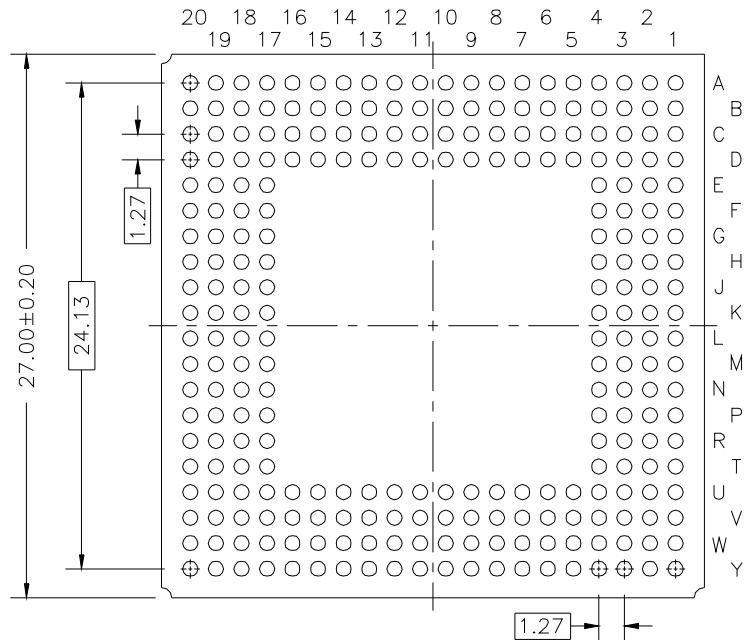

| <b>5. Package Outline Drawings</b>       | <b>29</b> |

| 5.1 256 PBGA—17 mm                       | 29        |

| 5.2 256 PBGA—27 mm                       | 30        |

| <b>6. Ordering Information</b>           | <b>32</b> |

| <b>7. Revision History</b>               | <b>32</b> |

## 1. Overview

The CA91L862A™ chip is a member of Renesas' family of PCI bus-bridging devices. CA91L862A enables board designers to bring PCI-based embedded products to market faster, for less cost, and with high performance.

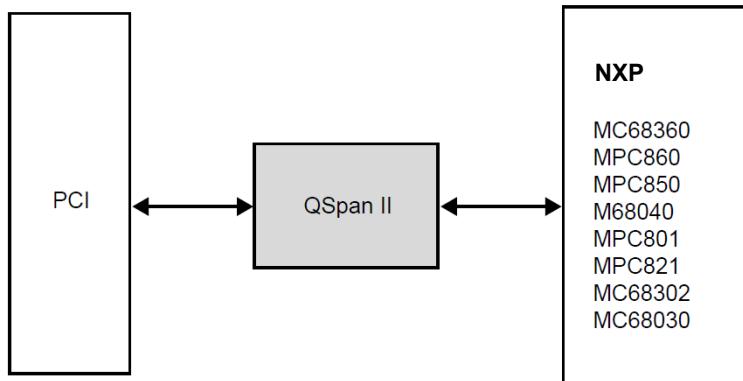

Developed as part of a strategic relationship with NXP, CA91L862A is designed to gluelessly bridge the MC68360 (QUICC™), the MPC860 (PowerQUICC™), other MPCxxx devices, and the M68040/M68060 to PCI (see [Figure 1](#)). With additional glue logic, CA91L862A can also be connected to lower-end communications controllers and processors, such as the MC68302 and MC68030.

Figure 1. CA91L862A Bridging PCI and Processor Buses

### 1.1 Typical Applications

For typical applications information, see “Appendix C” in the *QSpan II User Manual*.

## 2. Pin Information

### 2.1 Terminology

The following abbreviations are used in this chapter:

|       |                                                                                        |

|-------|----------------------------------------------------------------------------------------|

| in    | Defines a signal as a standard input-only signal.                                      |

| out   | Defines a signal as a standard output-only signal.                                     |

| t/s   | Defines a signal as a bidirectional, tristate input/output signal.                     |

| s/t/s | Defines a signal as a sustained tristate signal that is driven by one owner at a time. |

| o/d   | Defines a signal as an open drain.                                                     |

### 2.2 Overview

CA91L862A's QBus Interface defines a number of signals that can be mapped to MC68360 (QUICC), MPC860 (PowerQUICC), or M68040 buses (see the following table).

**Table 1. QBus Signal Names Compared to NXP Signals**

| QBus Interface | MC68360  | MPC860    | M68040                            |

|----------------|----------|-----------|-----------------------------------|

| BB/_BGACK_     | BGACK_   | BB_       | BB_                               |

| BERR/_TEA_     | BERR_    | TEA_      | TEA_                              |

| BURST/_TIP_    | N/A      | BURST_    | TIP_                              |

| DACK/_SDACK_   | DACK_    | SDACK_    | N/A                               |

| DSACK1/_TA_    | DSACK1_  | TA_       | TA_                               |

| SIZ[1:0]       | SIZ[1:0] | TSIZ[0:1] | SIZ[1:0]                          |

| TC[3:0]        | FC[3:0]  | AT[0:3]   | TT[1:0]<br>TM[2:0] <sup>[1]</sup> |

| HALT/_TRETRY_  | HALT_    | TRETRY_   | N/A                               |

1. TC[3:0] can be connected to four out of the five TT[1:0] and TM[2:0] M68040 signals. The unused TC pins, if any, must be connected to pull-up resistors (see Appendix C: "Typical Applications" in the *QSpan II User Manual*).

*Note:* MPC860 signals do not necessarily operate in the same manner as MC68360 signals of the same name.

## 2.3 Pin Assignments

Table 2. Pin Assignments – 17x17 mm Package

|                |                  |                      |                    |                  |

|----------------|------------------|----------------------|--------------------|------------------|

| A1. N/C        | D5. D[21]        | G9. VSS              | K13. TDO           | P1. AD[30]       |

| A2. D[25]      | D6. A[23]        | G10. VSS             | K14. BDIP_         | P2. AD[29]       |

| A3. D[23]      | D7. A[17]        | G11. VSS             | K15. TDI           | P3. AD[26]       |

| A4. D[22]      | D8. QCLK         | G12. VDD             | K16. BG_           | P4. EXT_GNT[4]#  |

| A5. DP[0]      | D9. D[14]        | G13. DREQ_           | L1. BR_            | P5. AD[21]       |

| A6. A[25]      | D10. D[12]       | G14. A[0]            | L2. BB_ /BGACK_    | P6. AD[16]       |

| A7. A[21]      | D11. A[12]       | G15. A[2]            | L3. N/C            | P7. FRAME#       |

| A8. A[20]      | D12. A[10]       | G16. A[1]            | L4. BURST_ /TIP_   | P8. PCLK         |

| A9. A[16]      | D13. N/C         | H1. TMODE[1]         | L5. VDD            | P9. AD[15]       |

| A10. D[17]     | D14. D[7]        | H2. HS_LED           | L6. VSS            | P10. AD[11]      |

| A11. D[13]     | D15. D[4]        | H3. SCL              | L7. VSS            | P11. AD[9]       |

| A12. A[14]     | D16. D[3]        | H4. IMSEL            | L8. VSS            | P12. AD[7]       |

| A13. A[13]     | E1. A[29]        | H5. VDD              | L9. VSS            | P13. EXT_REQ[4]# |

| A14. TEST2     | E2. N/C          | H6. VSS              | L10. VSS           | P14. AD[6]       |

| A15. A[9]      | E3. A[27]        | H7. VSS              | L11. VSS           | P15. AD[3]       |

| A16. VH        | E4. A[28]        | H8. VSS              | L12. VDD           | P16. CSPCI_      |

| B1. D[28]      | E5. VDD          | H9. VSS              | L13. TC3           | R1. EXT_GNT[1]#  |

| B2. VH         | E6. VDD          | H10. VSS             | L14. TC1           | R2. AD[24]       |

| B3. D[26]      | E7. VDD          | H11. VSS             | L15. BERR_ /TEA_   | R3. AD[25]       |

| B4. D[24]      | E8. VDD          | H12. VDD             | L16. AS_           | R4. EXT_GNT[2]#  |

| B5. DP[2]      | E9. VDD          | H13. TCK             | M1. HALT_ /TRETRY_ | R5. EXT_GNT[5]#  |

| B6. D[20]      | E10. VDD         | H14. TRST_           | M2. RST#           | R6. AD[19]       |

| B7. A[22]      | E11. VDD         | H15. ENID            | M3. GNT#           | R7. IRDY#        |

| B8. A[18]      | E12. VDD         | H16. QINT_           | M4. REQ#           | R8. DEVSEL#      |

| B9. D[18]      | E13. D[6]        | J1. PME#             | M5. VDD            | R9. CBE[1]       |

| B10. D[15]     | E14. D[2]        | J2. HS_SWITCH        | M6. VDD            | R10. AD[12]      |

| B11. A[15]     | E15. D[1]        | J3. TMODE[0]         | M7. VDD            | R11. CBE[0]      |

| B12. TEST1     | E16. A[5]        | J4. RESETI_          | M8. VDD            | R12. EXT_REQ[2]# |

| B13. N/C       | F1. DSACK1_ /TA_ | J5. VDD              | M9. VDD            | R13. EXT_REQ[6]# |

| B14. D[10]     | F2. A[31]        | J6. VSS              | M10. VDD           | R14. N/C         |

| B15. D[11]     | F3. A[30]        | J7. VSS              | M11. VDD           | R15. VH          |

| B16. A[7]      | F4. SIZ[1]       | J8. VSS              | M12. VDD           | R16. N/C         |

| C1. A[26]      | F5. VDD          | J9. VSS              | M13. CSREG_        | T1. AD[23]       |

| C2. D[31]      | F6. VSS          | J10. VSS             | M14. INT#          | T2. CBE[3]       |

| C3. D[27]      | F7. VSS          | J11. VSS             | M15. SERR#         | T3. EXT_GNT[3]#  |

| C4. PCI_ARB_EN | F8. VSS          | J12. VDD             | M16. TC[2]         | T4. EXT_GNT[6]#  |

| C5. DP[1]      | F9. VSS          | J13. DACK_ /SDACK_   | N1. VH             | T5. AD[18]       |

| C6. A[24]      | F10. VSS         | J14. BM_EN/FIFO_RDY_ | N2. AD[31]         | T6. AD[17]       |

| C7. A[19]      | F11. VSS         | J15. DONE_           | N3. AD[27]         | T7. STOP#        |

| C8. D[19]      | F12. VDD         | J16. TMS             | N4. AD[28]         | T8. AD[14]       |

| C9. D[16]      | F13. D[5]        | K1. RESETO_          | N5. AD[22]         | T9. AD[13]       |

| C10. DS_       | F14. A[3]        | K2. TS_              | N6. AD[20]         | T10. AD[8]       |

| C11. A[11]     | F15. D[0]        | K3. PCI_DIS          | N7. CBE[2]         | T11. EXT_REQ[1]# |

| C12. TEST3     | F16. A[4]        | K4. HS_HEALTHY_      | N8. TRDY#          | T12. EXT_REQ[5]# |

| C13. A[6]      | G1. SDA          | K5. VDD              | N9. PERR#          | T13. AD[5]       |

| C14. A[8]      | G2. SIZ[0]       | K6. VSS              | N10. PAR           | T14. AD[4]       |

| C15. D[9]      | G3. DSACK0_      | K7. VSS              | N11. AD[10]        | T15. N/C         |

| C16. D[8]      | G4. ENUM#        | K8. VSS              | N12. IDSEL         | T16. AD[2]       |

| D1. R/W_       | G5. VDD          | K9. VSS              | N13. EXT_REQ[3]#   |                  |

| D2. D[30]      | G6. VSS          | K10. VSS             | N14. AD[1]         |                  |

| D3. D[29]      | G7. VSS          | K11. VSS             | N15. AD[0]         |                  |

| D4. DP[3]      | G8. VSS          | K12. VDD             | N16. TC[0]         |                  |

**Table 3. Pin Assignments – 27x27 mm Package**

|                |            |                    |                  |                  |

|----------------|------------|--------------------|------------------|------------------|

| A1. VSS        | C13. A[14] | H1. DSACK1_TA_     | P17. N/C         | V13. AD[12]      |

| A2. D[26]      | C14. A[11] | H2. A[31]          | P18. TC[0]       | V14. AD[8]       |

| A3. D[22]      | C15. TEST3 | H3. A[30]          | P19. TC[1]       | V15. N/C         |

| A4. DP[2]      | C16. A[10] | H4. VSS            | P20. TC[2]       | V16. EXT_REQ[2]# |

| A5. VDD        | C17. A[6]  | H17. VSS           | R1. BB_BGACK_    | V17. EXT_REQ[6]# |

| A6. A[24]      | C18. D[8]  | H18. N/C           | R2. BR_          | V18. AD[5]       |

| A7. A[22]      | C19. VDD   | H19. VSS           | R3. VH           | V19. AD[3]       |

| A8. VSS        | C20. D[4]  | H20. N/C           | R4. VDD          | V20. AD[0]       |

| A9. A[17]      | D1. VSS    | J1. SDA            | R17. VDD         | W1. AD[28]       |

| A10. QCLK      | D2. VDD    | J2. SIZ[0]         | R18. N/C         | W2. AD[27]       |

| A11. D[17]     | D3. D[29]  | J3. SIZ[1]         | R19. N/C         | W3. AD[24]       |

| A12. VSS       | D4. VSS    | J4. DSACK0_        | R20. CSPCI_      | W4. CBE[3]       |

| A13. DS_       | D5. D[24]  | J17. DREQ_         | T1. HALT_TRETRY_ | W5. EXT_GNT[2]#  |

| A14. A[13]     | D6. VDD    | J18. ENID          | T2. VDD          | W6. EXT_GNT[6]#  |

| A15. N/C       | D7. D[21]  | J19. QINT_         | T3. REQ#         | W7. VSS          |

| A16. N/C       | D8. VSS    | J20. TCK           | T4. AD[31]       | W8. AD[19]       |

| A17. N/C       | D9. A[19]  | K1. ENUM#          | T17. VSS         | W9. AD[16]       |

| A18. A[8]      | D10. A[16] | K2. N/C            | T18. INT#        | W10. FRAME#      |

| A19. D[11]     | D11. VDD   | K3. SCL            | T19. CSREG_      | W11. PCLK        |

| A20. D[9]      | D12. D[12] | K4. VDD            | T20. N/C         | W12. CBE[1]      |

| B1. D[28]      | D13. VSS   | K17. DONE_         | U1. VSS          | W13. AD[13]      |

| B2. VDD        | D14. TEST2 | K18. TRST_         | U2. GNT#         | W14. AD[10]      |

| B3. D[25]      | D15. VDD   | K19. DACK_SDACK_   | U3. AD[29]       | W15. CBE[0]      |

| B4. PCI_ARB_EN | D16. VDD   | K20. TMS           | U4. VSS          | W16. N/C         |

| B5. DP[1]      | D17. VSS   | L1. IMSEL          | U5. AD[23]       | W17. EXT_REQ[3]# |

| B6. D[20]      | D18. D[5]  | L2. HS_LED         | U6. VDD          | W18. AD[6]       |

| B7. A[23]      | D19. VSS   | L3. TMODE[1]       | U7. EXT_GNT[5]#  | W19. VSS         |

| B8. A[20]      | D20. VDD   | L4. HS_SWITCH      | U8. VSS          | W20. AD[2]       |

| B9. N/C        | E1. A[27]  | L17. VDD           | U9. AD[17]       | Y1. AD[26]       |

| B10. D[18]     | E2. VDD    | L18. TDI           | U10. VDD         | Y2. AD[25]       |

| B11. D[15]     | E3. A[26]  | L19. N/C           | U11. PERR#       | Y3. N/C          |

| B12. D[14]     | E4. D[31]  | L20. VSS           | U12. VDD         | Y4. N/C          |

| B13. A[15]     | E17. D[3]  | M1. TMODE[0]       | U13. VSS         | Y5. EXT_GNT[3]#  |

| B14. A[12]     | E18. D[2]  | M2. PME#           | U14. AD[7]       | Y6. N/C          |

| B15. TEST1     | E19. D[1]  | M3. RESETI_        | U15. VDD         | Y7. AD[21]       |

| B16. A[9]      | E20. A[4]  | M4. PCI_DIS        | U16. EXT_REQ[5]# | Y8. AD[18]       |

| B17. A[7]      | F1. VSS    | M17. BDIP_         | U17. VSS         | Y9. CBE[2]       |

| B18. D[10]     | F2. A[28]  | M18. BG_           | U18. AD[1]       | Y10. TRDY#       |

| B19. D[7]      | F3. N/C    | M19. TDO           | U19. VDD         | Y11. DEVSEL#     |

| B20. D[6]      | F4. VDD    | M20.BM_EN/FIFO_RDY | U20. SERR#       | Y12. PAR         |

| C1. D[30]      | F17. VDD   | N1. RESETO_        | V1. VSS          | Y13. AD[14]      |

| C2. D[27]      | F18. D[0]  | N2.HS_HEALTHY_     | V2. AD[30]       | Y14. AD[11]      |

| C3. N/C        | F19. A[3]  | N3. BURST_TIP_     | V3. VDD          | Y15. AD[9]       |

| C4. D[23]      | F20. A[2]  | N4. VSS            | V4. N/C          | Y16. IDSEL       |

| C5. DP[3]      | G1. N/C    | N17. VSS           | V5. EXT_GNT[1]#  | Y17. EXT_REQ[1]# |

| C6. DP[0]      | G2. A[29]  | N18. TC[3]         | V6. EXT_GNT[4]#  | Y18. EXT_REQ[4]# |

| C7. A[25]      | G3. R/W_   | N19. BERR_TEA_     | V7. AD[22]       | Y19. VDD         |

| C8. A[21]      | G4. N/C    | N20. AS_           | V8. AD[20]       | Y20. AD[4]       |

| C9. A[18]      | G17. A[5]  | P1. N/C            | V9. VSS          |                  |

| C10. D[19]     | G18. VDD   | P2. TS_            | V10. IRDY#       |                  |

| C11. D[16]     | G19. A[1]  | P3. VSS            | V11. STOP#       |                  |

| C12. D[13]     | G20. A[0]  | P4. RST#           | V12. AD[15]      |                  |

## 2.4 Pin Descriptions

Table 4. Pin Descriptions

| Pin Name                                   | Pin Type                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>MC68360 Signals: QUICC (see Note 1)</b> |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A[31:0]                                    | Tristate bidirectional                        | <p>Address Bus: address for the current bus cycle. It is driven by the CA91L862A when it is the QBus master and input when QBus slave. It is qualified at the start of a transaction by AS_.</p> <p>As a slave, the CA91L862A samples A[31:0] on the same falling edge of the QCLK as AS_. Both A[31:0] and AS_ must meet the synchronous set-up and hold time parameters about the falling edge of the QCLK to ensure correct operation.</p> <p>As a master, the CA91L862A maintains the correct asynchronous timing relationships between A[31:0] and AS_. The address bus is driven valid after the rising edge of the QCLK, while the AS_ is driven only after the subsequent falling edge of the same clock period, ensuring the correct address before AS_ timing.</p> <p>When accesses are made to CA91L862A registers from the QBus, only the lower 12 bits of the address bus are used to determine the offset.</p>                                                                                                                                                                         |

| AS_                                        | Rescinding Tristate bidirectional             | <p>Address Strobe: indicates the beginning (and duration) of a transaction on the QBus. As an output AS_ is driven by the CA91L862A when the CA91L862A is the QBus master, and is tristated at all other times. The Address Strobe is driven low after a falling edge of the QCLK. The Address Strobe qualifies the following signals as valid when it is asserted: A[31:0], TC[3:0], SIZ[1:0], and R/W_. CA91L862A guarantees a minimum set-up time for the qualified signals before AS_ is asserted (all qualified signals are driven from the rising edge of QCLK preceding the assertion of AS_). QSpan II rescinds AS_ prior to tristate.</p> <p>As an input, AS_ is sampled on the falling edge of the QCLK. AS_ must meet a minimum set-up and hold time around the falling edge of the clock for correct operation. CA91L862A recognizes a transaction as intended for it, and acknowledges it accordingly, only if one of CSREG_ or CSPCI_ is sampled low in conjunction with AS_. CA91L862A does not require that the input signals qualified by the AS_ be valid when it is asserted.</p> |

| BB_/BGACK_                                 | Rescinding Tristate bidirectional             | <p>Bus Busy: indicates ownership of the QBus. It, along with BR_ and BG_, provides the three-wire handshake for QBus arbitration. BB_/BGACK_ is intended to connect to the BGACK_ bus.</p> <p>As an output the CA91L862A asserts BB_/BGACK_ from the falling edge of QCLK (while master). QSpan II rescinds BB_/BGACK_ prior to tristate.</p> <p>As an input, the CA91L862A double-samples BB_/BGACK_ on the falling edge of QCLK: when it is master. CA91L862A can also be programmed to use a synchronous mode for QBus arbitration.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BGACK_                                     | Rescinding Tristate bidirectional             | See BB_/BGACK_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BDIP_                                      | Input (MC68360 mode) / Bidirectional (MPC860) | Burst Data In Progress: On the MC68360 interface, this pin is used only to determine the QBus master mode of the CA91L862A. This is determined at reset by sensing the level of this pin. If BDIP_ is sampled as low (at power-up or reset) the QBus master module will operate as an MC68360 master. If the BDIP_ signal is sampled as high — at power-up or reset — the CA91L862A will operate as an MPC860 master (see Table 48 in the <i>QSpan II User Manual</i> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BERR_/TEA_                                 | Rescinding tristate bidirectional pin         | <p>Bus Error: used to indicate a bus error that occurs during a transaction. It can be used in conjunction with HALT_/TRETRY_ to indicate a busy-retry to the bus master.</p> <p>As an MC68360 master, the CA91L862A samples BERR_/TEA_ on the falling edge of QCLK during cycles in which it is a QBus master.</p> <p>As an MC68360 slave, BERR_/TEA_ is driven by the CA91L862A from the falling edge of QCLK. CA91L862A negates BERR_/TEA_ prior to tristate.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 4. Pin Descriptions (Cont.)

| Pin Name         | Pin Type                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BG_              | Input                             | Bus Grant: indicates that the CA91L862A may become the next QBus master. BG_, along with BR_ and BB_/_BGACK_, provide the three-wire handshake for QBus arbitration.<br>BG_ is doubled-sampled on the falling edge of QCLK. CA91L862A can be programmed to use a synchronous mode for QBus arbitration.                                                                                                                                                                |

| BM_EN/_FIFO_RDY_ | Bidirectional                     | Bus Master Enable/FIFO Ready: If this input is asserted — set as 1 — during a PCI Reset, the Bus Master Enable bit in the PCI_CS register will be set.                                                                                                                                                                                                                                                                                                                 |

| BR_              | Output                            | Bus Request: used by the CA91L862A to request ownership of the QBus. BR_, along with BG_ and BB_/_BGACK_, provide the three-wire handshake for QBus arbitration. BR_ is asserted and negated from the falling edge of QCLK in MC68360 mode.                                                                                                                                                                                                                            |

| CSPCI_           | Input                             | PCI Chip Select: indicates that the current transaction on the QBus is an access to the PCI Bus. During IDMA cycles, if this is sampled high, a single address transfer is indicated; if sampled low, a dual address transfer is indicated. It is sampled on the falling edge of clock.                                                                                                                                                                                |

| CSREG_           | Input                             | Register Chip Select: indicates that the current transaction on the QBus is an access to the CA91L862A's registers. It is sampled on the falling edge of clock.                                                                                                                                                                                                                                                                                                        |

| D[31:0]          | Tristate bidirectional            | Data Bus: provides the data information for the CA91L862A's inputs and outputs on the QBus.<br>As an MC68360 slave the CA91L862A does not use DS_ to qualify data on writes. It also provides data on reads without decoding DS_, since DS is output only.<br>As an MC68360 master, the CA91L862A does use DS to qualify data on writes and to request data on reads.                                                                                                  |

| DACK_/_SDACK_    | Input                             | IDMA Acknowledge: indicates to the CA91L862A that the current transaction is an IDMA transaction. The timing of DACK_ should be the same as for AS_. Using the IDMA handshakes, the CA91L862A is capable of supporting MC68360 fast termination cycles.                                                                                                                                                                                                                |

| DONE_            | Input                             | IDMA Done: indicates that the IDMA controller has completed the current sequence of IDMA operations, and that the CA91L862A should no longer use DREQ_ to request transactions. Setup for DONE is to falling edge of QCLK.                                                                                                                                                                                                                                             |

| DREQ_            | Output                            | IDMA Request: request to the MC68360 IDMA to either transfer data to CA91L862A IFIFO (PCI Write) or remove data from I-FIFO (PCI Read). It is asserted from the falling edge of QCLK in MC68360 mode.                                                                                                                                                                                                                                                                  |

| DSACK0_          | Rescinding tristate bidirectional | Data and Size Acknowledge 0: in conjunction with DSACK1_/_TA_, is driven by the addressed slave to acknowledge the completion of a data transfer on the QBus. DSACK0_ has the same timing and characteristics as DSACK1_/_TA_ (see the following description).                                                                                                                                                                                                         |

| DSACK1_/_TA_     | Rescinding tristate bidirectional | Data and Size Acknowledge 1: Used in conjunction with DSACK0_. This signal is driven by the addressed slave to acknowledge the completion of a data transfer on the QBus.<br>CA91L862A terminates all normal bus cycles by asserting both DSACK1_/_TA_ and DSACK0_ (indicating a 32-bit port width at all times). The DSACK1_/_TA_ output is driven high (inactive) after the release of AS_ until the next falling edge of the clock, at which point it is tristated. |

Table 4. Pin Descriptions (Cont.)

| Pin Name      | Pin Type                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS_           | Rescinding tristate output        | <p>Data Strobe: used to indicate valid data on the data bus during write transactions, and to request data during read transactions. DS_ is driven by the CA91L862A when it is a QBus master, and is tristated otherwise.</p> <p>As a slave the CA91L862A assumes write data is valid on the rising edge of QCLK following the clock edge where AS_ is sampled asserted. For read transactions, the CA91L862A provide information independent of DS_. DS_ is output only.</p> <p>As a master on the QBus, the CA91L862A asserts DS_ to qualify data during reads and writes. For write transactions, the DS_ is driven from the falling edge of QCLK one half a clock period after the data is driven onto the Data bus. For read transactions, DS is driven at the same time as AS_. CA91L862A negates DS_ prior to tristate.</p>                                                                                             |

| HALT_/TRETRY_ | Rescinding tristate bidirectional | <p>Halt: Suspends external bus activity. It is used for generating retries.</p> <p>As an MC68360 slave CA91L862A uses HALT_/TRETRY_ as stated in Table 11 in the <i>QSpan II User Manual</i>.</p> <p>As an MC68360 master CA91L862A uses HALT_/TRETRY_ as stated in Table 27 in the <i>QSpan II User Manual</i>.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| IMSEL         | Input                             | <p>Image Select: selects which QBus Slave Image to use when CSPCI_ is asserted.</p> <p>The timing requirements for IMSEL are the same as those of the address bus when the CA91L862A is a QBus slave.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| QCLK          | Input                             | QBus Clock: All devices intended to interface with QBus side of the CA91L862A must be synchronized to this clock. The QCLK can operate up to 33 MHz (with an MC68360 bus). During IDMA fast termination cycles the maximum MC68360 QCLK frequency is 30 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| QINT_         | Open drain bidirectional          | QBus Interrupt: as an output, this open drain signal is asserted by the CA91L862A when an interrupt event occurs. As an input, this signal can be mapped to the PCI INT# output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RESETI_       | Input                             | QBus Reset Input: resets the CA91L862A from the QBus side of the CA91L862A. RESETI_ does not reset PCI configuration and status registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RESETO_       | Open drain output                 | QBus Reset Output: asserted whenever the CA91L862A's PCI RST# input is asserted, or the internal software reset bit is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| R/W_          | Tristate bidirectional            | <p>Read Write: indicates the direction of the data transfer on the Data bus. High indicates a read transaction; low indicates a write. It has the same timing as the Address bus.</p> <p>As a <b>master</b>, the CA91L862A drives R/W_, and tristates it otherwise. As a slave, the R/W_ pin is an input.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SIZ[1:0]      | Tristate bidirectional            | Size: indicates the number of bytes to be transferred during a bus cycle. The value of the Size bits, along with the lower two address bits and the port width, define the byte lanes that are active. Table 5 in the <i>QSpan II User Manual</i> shows the encoding for the Size bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TC[3:0]       | Tristate bidirectional            | <p>Transaction Code: provides additional information about a bus cycle when the CA91L862A is a QBus master. Driven by the CA91L862A when it is a QBus master, and tristated otherwise.</p> <p>As a slave, the CA91L862A samples TC[3:0] on the first falling edge of the QCLK after AS_ is asserted. TC[3:0] can optionally be used with DACK_/SDACK_ to decode an IDMA operation. For use in IDMA transfers, TC[3:0] should be set to all ones.</p> <p>The timing for the TC[3:0] outputs is the same as the timing for the address bus when the CA91L862A is a QBus master.</p> <p>The values output on the TC[3:0] bus during a transaction in which the CA91L862A is the bus master is determined by the value programmed in the Transaction Code field of the corresponding CA91L862A PCI target image. TC[3:0] is intended to connect to the MC68360's FC[3:0], but may be used for other special decoding purposes.</p> |

Table 4. Pin Descriptions (Cont.)

| Pin Name                                       | Pin Type                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>MPC860 Signals: PowerQUICC (see Note 1)</b> |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A[31:0]                                        | Tristate bidirectional            | <p>Address bus: address for the current bus cycle. It is driven by the CA91L862A when it is the QBus master and input as slave. It is qualified at the start of a transaction by TS_.</p> <p>As a slave, the CA91L862A samples A[31:0] on the rising edge of QCLK, and is qualified by Transaction Start (TS_) on the same rising clock edge.</p> <p>As a master, the address is driven out following a rising edge of the QCLK.</p> <p>When accesses are made to CA91L862A registers from the QBus, only the lower 12 bits of the address bus are used to determine the register offset.</p>                                                                                                                                                                                                                                                                                                                                                    |

| AT[0:3]                                        | Tristate bidirectional            | See TC[3:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BB_/BGACK_                                     | Rescinding tristate bidirectional | <p>Bus Busy: indicates ownership of the QBus. BB_ is asserted low by a master to show that it owns the bus. BB_, along with BR_ and BG_, provides the three-wire handshake for QBus arbitration.</p> <p>As an output the CA91L862A asserts BB_/BGACK_ from the rising edge of QCLK (while master). QSpan II drives BB_/BGACK_ to the prior to tristate. Note in the MPC860 mode, the CA91L862A asserts BB_ one clock after receiving BG_: in compliance with the MPC860 arbiter.</p> <p>As an input, the CA91L862A samples BB_/BGACK_ on the rising edge of QCLK. CA91L862A can also be programmed to use a asynchronous mode for QBus arbitration.</p>                                                                                                                                                                                                                                                                                          |

| BDIP_                                          | Bidirectional                     | <p>Burst Data In Progress: As MPC860 master, the CA91L862A uses BDIP_ in burst writes to indicate the second last data beat of a transaction. This allows the CA91L862A to perform burst writes of two, three, or four beats. CA91L862A does not use BDIP_ in the same manner for burst reads. Burst reads are always cacheline aligned and four beats in length.</p> <p>As MPC860 slave, the CA91L862A monitors BDIP_ as a signal indicating the second last data beat in the burst. This allows the CA91L862A to support bursts of two, three, or four data beats.</p> <p>The QBus master mode of the CA91L862A is determined at power-up and reset by sensing the level of this pin. If BDIP_ is sampled as low (at reset) the QBus master module will operate as a MC68360 master. At reset, if the BDIP_ signal is sampled as high the CA91L862A will operate as an MPC860 or M68040 master (see Table 48 in the QSpan II User Manual).</p> |

| BERR_/TEA_                                     | Rescinding tristate bidirectional | <p>Transfer Error Acknowledge: indicates that a bus error occurred in the current transaction.</p> <p>Driven by the CA91L862A when it is a QBus slave, and tristated otherwise.</p> <p>As an output BERR_/TEA_ is driven by the CA91L862A from the rising edge of QCLK. CA91L862A negates BERR_/TEA_ prior to tristate.</p> <p>As an input, the CA91L862A samples BERR_/TEA_ on the rising edge of QCLK during cycles in which it is a QBus master.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BG_                                            | Input                             | <p>Bus Grant: indicates that the CA91L862A may become the next QBus master. BG_, along with BR_ and BB_/BGACK_, provide the three-wire handshake for QBus arbitration. BG_ is sampled on the rising edge of QCLK.</p> <p>CA91L862A can be programmed to use a asynchronous mode for QBus arbitration.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BR_                                            | Output                            | <p>Bus Request: used by the CA91L862A to request ownership of the QBus. BR_, along with BG_ and BB_/BGACK_, provide the three-wire handshake for QBus arbitration. BR_ is asserted and released from the rising edge of QCLK.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BM_EN/<br>FIFO_RDY_                            | Bidirectional                     | <p>Bus Master Enable: If this input is asserted — set as 1 — during a PCI Reset, the Bus Master Enable bit in the PCI_CS register will be set.</p> <p>(FIFO_RDY) FIFO Ready functionality is not relevant to MPC860 applications.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 4. Pin Descriptions (Cont.)

| Pin Name       | Pin Type                          | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BURST_ /TIP    | Tristate bidirectional            | Burst: indicates that the current initiated transfer is a burst cycle. This signal matches the MPC860 signal of the same name.                                                                                                                                                                                                                                                                  |

| CSPCI_         | Input                             | PCI Chip Select: indicates that the current transaction on the QBus is an access to the PCI Bus. CSPCI_ can be sampled on the same clock as TS or up to three clocks following TS_ assertion. During IDMA cycles, if this is sampled high, a single address transfer is indicated; otherwise, a dual address transfer is indicated.                                                             |

| CSREG_         | Input                             | Register Chip Select: indicates that the current transaction on the QBus is an access to the QSpan II's registers. CSREG_ can be sampled on the same clock as TS_ or up to three clocks following TS_ assertion. This signal is sampled synchronously on the rising edge of clock after TS_.                                                                                                    |

| DP[3:0]        | Bidirectional                     | Data Parity: provides the parity information for the data on D[31:0]. It is valid on the same clock as the data.                                                                                                                                                                                                                                                                                |

| D[31:0]        | Tristate bidirectional            | Data Bus: provides the general-purpose data path between the QSpan II, the MPC860, and other devices.                                                                                                                                                                                                                                                                                           |

| DACK_ /SDACK_  | Input                             | IDMA Acknowledge: indicates to the CA91L862A that the current transaction is an IDMA transaction.                                                                                                                                                                                                                                                                                               |

| DONE_          | Input                             | IDMA Done: This signal is not used with MPC860 transfers.                                                                                                                                                                                                                                                                                                                                       |

| DREQ_          | Output                            | IDMA Request: request to the MPC860 IDMA to either transfer data to CA91L862A IFIFO (PCI Write) or remove data from I-FIFO (PCI Read). It is asserted from the rising edge of QCLK in MPC860 mode.                                                                                                                                                                                              |

| DSACK1_ /TA_   | Rescinding tristate bidirectional | Transaction Acknowledge: driven by the addressed slave to acknowledge the completion of a data transfer on the QBus.<br>As a slave the CA91L862A terminates all normal bus cycles by asserting TA_. CA91L862A negates DSACK1_ /TA_ prior to tristate.                                                                                                                                           |

| HALT_ /TRETRY_ | Rescinding tristate bidirectional | Transfer Retry: used for generating retries.<br>As a MPC860 slave, CA91L862A uses HALT_ /TRETRY_ as stated in Table 12 in the <i>QSpan II User Manual</i> .<br>As a MPC860 master, CA91L862A uses HALT_ /TRETRY_ as stated in Table 28 in the <i>QSpan II User Manual</i> . As a slave, HALT_ /TRETRY_ has the same timing as DSACK1_ /TA_. CA91L862A negates HALT_ /TRETRY_ prior to tristate. |

| IMSEL          | Input                             | Image Select: selects which QBus Slave Image to use when CSPCI_ is asserted.<br>The timing requirements for IMSEL are the same as those of the address bus when the CA91L862A is a QBus slave.                                                                                                                                                                                                  |

| QCLK           | Input                             | QBus Clock: All devices intended to interface with QBus side of the CA91L862A must be synchronized to this clock.<br>The maximum QCLK frequency with a MPC860 is 50 MHz.                                                                                                                                                                                                                        |

| QINT_          | Open drain bidirectional          | QBus Interrupt: as an output, this open drain signal is asserted by the CA91L862A when an interrupt event occurs. As an input, this signal can be mapped to the PCI INT# output.                                                                                                                                                                                                                |

| RESETI_        | Input                             | QBus Reset Input: resets the CA91L862A from the QBus side of the CA91L862A. Note that RESETI_ does not reset PCI configuration and status registers.                                                                                                                                                                                                                                            |

| RESETO_        | Open drain output                 | QBus Reset Output: asserted whenever the CA91L862A's PCI RST# input is asserted, or the internal software reset bit is set.                                                                                                                                                                                                                                                                     |

| R/W_           | Tristate bidirectional            | Read Write: indicates the direction of the data transfer on the Data bus. High indicates a read transaction; low indicates a write. It has the same timing as the Address bus.<br>As an active master, the CA91L862A drives R/W_, and tristates it otherwise.<br>As an addressed slave, the R/W_ pin is an input.                                                                               |

Table 4. Pin Descriptions (Cont.)

| Pin Name                           | Pin Type                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIZ[1:0]                           | Tristate bidirectional            | <p>Size: indicates the number of bytes to be transferred during a bus cycle. The value of the Size bits, along with the lower two address bits and the port width, define the byte lanes that are active. Table 5 in the <i>QSpan II User Manual</i> shows the encoding for the Size bits.</p> <p>SIZ[1:0] is intended to connect to MPC860 TSIZ[0:1].</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TA_                                | Rescinding tristate bidirectional | See DSACK1_/TA_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TC[3:0]                            | Tristate bidirectional            | <p>Transaction Code Bus: provides additional information about a bus cycle when the CA91L862A is a QBus master.</p> <p>Driven by the CA91L862A when it is a QBus master, and tristated otherwise.</p> <p>As a slave, the CA91L862A samples TC[3:0] on the first rising edge of the QCLK after TS_ is asserted. TC[3:0] can optionally be used with DACK_/SDACK_ to decode an IDMA operation. For use in IDMA transfers, TC[3:0] should be set to all ones.</p> <p>The timing for the TC[3:0] outputs is the same as the timing for the address bus when the CA91L862A is a QBus master.</p> <p>The values output on the TC[3:0] bus during a transaction in which the CA91L862A is the bus master is determined by the value programmed in the Transaction Code field of the corresponding CA91L862A PCI target image. TC[3:0] is intended to connect to the MPC860's AT[0:3], but can be used for other special decoding purposes.</p> |

| TEA_                               | Rescinding tristate bidirectional | See BERR_/TEA_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TRETRY_                            | Rescinding tristate bidirectional | See HALT_/TRETRY_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TS_                                | Rescinding Tristate bidirectional | <p>Transfer Start: TS_ is a three state bi-directional signal used to indicate the beginning of an MPC860 bus transaction on the QBus.</p> <p>The TS_ output is driven by the CA91L862A when the CA91L862A is the QBus master, and is tri-stated at all other times.</p> <p>As an output, TS_ is driven low after a rising edge of the QCLK. Transfer Start indicates the following signals will be valid on the next rising edge of the QCLK: A[31:0], TC[3:0], SIZ[1:0], and R/W_. QSpan II rescinds TS_ prior to tri-state.</p> <p>As an input, TS_ is sampled on the rising edge of the QCLK. CA91L862A samples the address bus and other TS_ qualified signals on the same rising edge of QCLK in which it samples TS_ asserted. CSPCI_ and CSREG_ may have up to three wait states after TS_ is sampled.</p>                                                                                                                      |

| <b>M68040 Signals (see Note 2)</b> |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A[31:0]                            | Tristate bidirectional            | <p>Address bus: Address for the current bus cycle. It is driven by the CA91L862A when the CA91L862A is the M68040 master and input when the CA91L862A is the slave. It is qualified at the start of a transaction by TS_.</p> <p>As a slave, the CA91L862A samples A[31:0] on the rising edge of QCLK, and is qualified by Transaction Start (TS_).</p> <p>As a master, the address is driven out following a rising edge of the QCLK.</p> <p>When accesses are made to CA91L862A registers from the QBus, only the lower 12 bits of the address bus are used to determine the register offset.</p>                                                                                                                                                                                                                                                                                                                                     |

Table 4. Pin Descriptions (Cont.)

| Pin Name         | Pin Type                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BB_/_BGACK_      | Rescinding tristate bidirectional | <p>Bus Busy: This signal is asserted by the current bus master to indicate ownership of the M68040 bus. BB_ along with BR_ and BG_, provide the three-wire handshake for M68040 bus arbitration.</p> <p>As an output the CA91L862A asserts BB_/_BGACK_ from the rising edge of QCLK (while master). QSpan II negates BB_/_BGACK_ prior to tristate.</p> <p>As an input, the CA91L862A samples BB_/_BGACK_ on the rising edge of QCLK (while master).</p> <p>CA91L862A can also be programmed to use an asynchronous mode for M68040 bus arbitration.</p> |

| BDIP_            | Bidirectional                     | <p>Burst Data In Progress: This signal is only used in the 68040 mode at reset.</p> <p>CA91L862A Master/Slave mode is determined at reset by sensing the level of this pin in conjunction with SIZ[1]. See Table 48 in the <i>QSpan II User Manual</i>.</p>                                                                                                                                                                                                                                                                                              |

| BERR_/_TEA_      | Rescinding tristate bidirectional | <p>Transfer Error Acknowledge: indicates an error condition exists for a bus transfer. Driven by the CA91L862A when it is a M68040 bus slave to signal an errored transaction.</p> <p>As an input, the CA91L862A samples BERR_/_TEA_ during M68040-style cycles in which it is a M68040 bus master on the rising edge of QCLK.</p> <p>Target retries are indicated by the simultaneous assertion of DSACK1_/_TA_ and BERR_/_TEA_.</p>                                                                                                                    |

| BG_              | Input                             | <p>Bus Grant: indicates that the CA91L862A may become the next M68040 bus master. BG_, along with BR_ and BB_/_BGACK_, provide the three-wire handshake for M68040 bus arbitration. BG_ is sampled on the rising edge of QCLK.</p> <p>CA91L862A can be programmed to use an asynchronous mode for M68040 bus arbitration.</p>                                                                                                                                                                                                                            |

| BM_EN/_FIFO_RDY_ | Bidirectional                     | Bus Master Enable: If this input is asserted (set as 1) during a PCI Reset, the Bus Master Enable bit in the PCI_CS register will be set.                                                                                                                                                                                                                                                                                                                                                                                                                |