## Bus Interface IC (Driver, Receiver)

### General Description

The CCA1224 is a bus interface IC with driver and receiver function. The bus driver provides two or combined inputs and a differential current bus output. The receiver uses the driver outputs as input and delivers the signal to an open collector output. This device is functional and pin compatible to the obsolete part no. HA12240.

Typical applications are automotive audio equipment controllers.

#### 1.1 FEATURES

- Two or combined data inputs (3.3 V and 5.0 V)

- Hysteresis input comparator

- Current drive output typ. 3.8 mA

- Hysteresis comparator for receiver

- Wide receiver common-mode input range of 0 to 5V typ.

- Open collector receiver output

- Operating VCC 5 V  $\pm 0.5$  V

- Standby function ( $I_{VCC} < 1 \mu A$ )

- ESD protection 2 kV

- on all IO pins

- SOP8 package

- Automotive qualified (AECQ100)

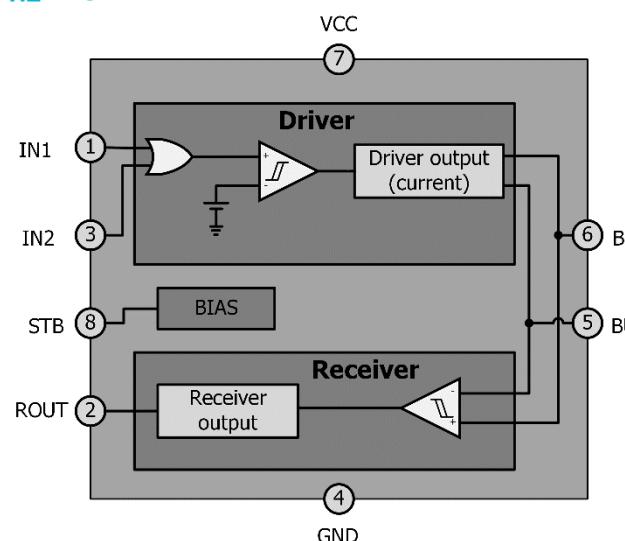

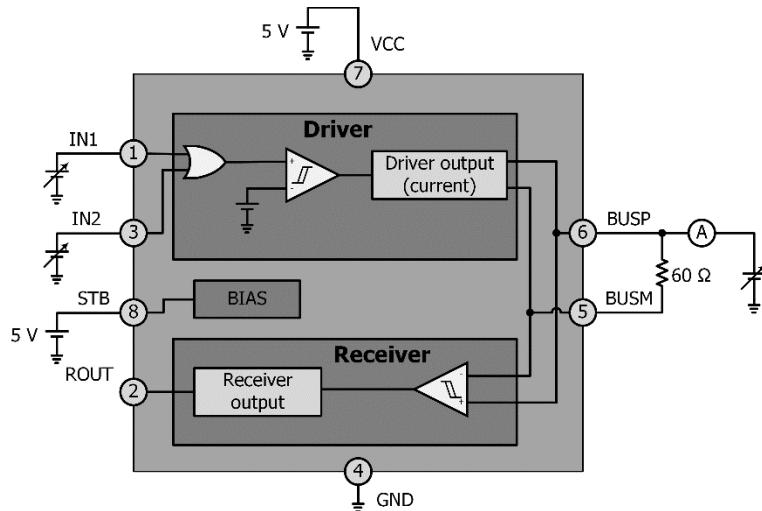

#### 1.2 SCHEMATIC

Figure 1: Block Diagram

## Bus Interface IC (Driver, Receiver)

### 2 Pinout

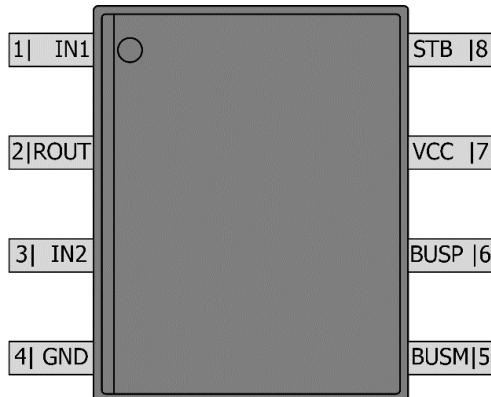

#### 2.1 PACKAGE

Figure 2: Package SOP8 (3.9x4.9mm)

#### 2.2 PIN DESCRIPTIONS

Table 1: Pin Descriptions

| Symbol | Pin no. | Type   | Description                                            | Schematic                                                                             |

|--------|---------|--------|--------------------------------------------------------|---------------------------------------------------------------------------------------|

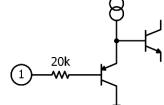

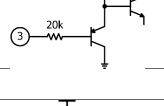

| IN1    | 1       | IN     | Data input 1                                           |  |

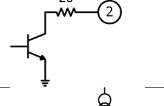

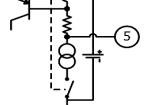

| ROUT   | 2       | OUT    | Receiver output (open collector)                       |  |

| IN2    | 3       | IN     | Data input 2                                           |  |

| GND    | 4       | PWR    | Ground                                                 |                                                                                       |

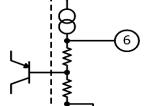

| BUSM   | 5       | IN/OUT | Minus bus driver output, receiver input                |  |

| BUPSP  | 6       | IN/OUT | Plus bus driver output, receiver input                 |  |

| VCC    | 7       | PWR    | Voltage supply                                         |                                                                                       |

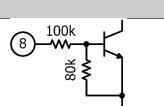

| STB    | 8       | IN     | Stand by input: H => operating mode; L => standby mode |  |

## Bus Interface IC (Driver, Receiver)

### 3 Absolute Maximum Ratings

Table 2: Absolute Maximum Ratings

| Parameter               | Symbol                             | Conditions                                                 | Min  | Typ | Max | Unit |

|-------------------------|------------------------------------|------------------------------------------------------------|------|-----|-----|------|

| Supply Voltage          | V <sub>CC</sub>                    | static                                                     | -0.7 |     | 36  | V    |

| Power dissipation QFN48 | P <sub>TOT_QFN</sub> <sub>48</sub> | Multilayer PCB, Exp. Pad soldered, θ <sub>AMB</sub> = 60°C |      |     | 2   | W    |

| Power dissipation QFN24 | P <sub>TOT_QFN</sub> <sub>24</sub> | Multilayer PCB, Exp. Pad soldered, θ <sub>AMB</sub> = 60°C |      |     | 1.5 | W    |

| Junction Temperature    | θ <sub>JUNC</sub>                  |                                                            |      |     | 150 | °C   |

| ESD-sensitivity         | V <sub>ESD</sub>                   | Human Body Model EIA/JESD22-A114-B                         | 2    |     |     | kV   |

| Storage Temperature     | θ <sub>STORAGE</sub>               |                                                            | -55  |     | 155 | °C   |

| Soldering Temperature   | θ <sub>SOLDER</sub>                | 12 s max                                                   |      |     | 260 | °C   |

| FIT Rate                |                                    |                                                            |      |     | 50  | FIT  |

Functional operation is only guaranteed within operating conditions listed under "Electrical Characteristics". Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability. Exposure to conditions beyond those ratings may cause permanent damage to the device.

### 4 Electrical Characteristics

Electrical characteristics are valid for the whole specified temperature range and supply voltage range, if not otherwise noted.

#### 4.1 GENERAL PARAMETERS

Table 3: General Parameters

| Parameter                  | Symbol                 | Conditions          | Min | Typ | Max | Unit |

|----------------------------|------------------------|---------------------|-----|-----|-----|------|

| Supply Voltage             | V <sub>CC</sub>        |                     | 4.5 | 5   | 5.5 | V    |

| Supply Current             | I <sub>VCC</sub>       |                     | 0.8 |     | 8.5 | mA   |

| Operating Temperature      | θ <sub>AMB</sub>       |                     | -40 |     | 105 | °C   |

| Thermal Resistance Ambient | θ <sub>JA_SOPN-8</sub> | Junction to Ambient |     | 100 |     | K/W  |

## Bus Interface IC (Driver, Receiver)

### 4.2 DRIVER

Table 4: Driver

| Parameter                                      | Symbol     | Conditions                                                                                                                                                                                                                                                           | Min | Typ | Max  | Unit             |

|------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------------------|

| High-level input voltage IN1                   | $V_{IHS1}$ | $V1 = 0 \text{ V} \rightarrow 5 \text{ V}; V3 = 0 \text{ V}; V6 - V5 = 110 \text{ mV} \uparrow$                                                                                                                                                                      | 2.1 |     |      | V                |

| Low-level input voltage IN1                    | $V_{ILS1}$ | $V1 = 5 \text{ V} \rightarrow 0 \text{ V}; V3 = 0 \text{ V}; V6 - V5 = 30 \text{ mV} \downarrow$                                                                                                                                                                     |     |     | 1.65 | V                |

| High-level input current IN1                   | $I_{IHS1}$ | $V1 = 5 \text{ V}$                                                                                                                                                                                                                                                   | -1  | 0   | 1    | $\mu\text{A}$    |

| Low-level input current IN1                    | $I_{ILS1}$ | $V1 = 0 \text{ V}$                                                                                                                                                                                                                                                   | -1  | 0.1 | 1    | $\mu\text{A}$    |

| High-level input voltage IN2                   | $V_{IHS2}$ | $V3 = 0 \text{ V} \rightarrow 5 \text{ V}; V1 = 0 \text{ V}; V6 - V5 = 110 \text{ mV} \uparrow$                                                                                                                                                                      | 2.1 |     |      | V                |

| Low-level input voltage IN2                    | $V_{ILS2}$ | $V3 = 5 \text{ V} \rightarrow 0 \text{ V}; V1 = 0 \text{ V}; V6 - V5 = 30 \text{ mV} \downarrow$                                                                                                                                                                     |     |     | 1.65 | V                |

| High-level input current IN2                   | $I_{ILS2}$ | $V3 = 5 \text{ V}$                                                                                                                                                                                                                                                   | -1  | 0   | 1    | $\mu\text{A}$    |

| Low-level input current IN2                    | $I_{ILS2}$ | $V3 = 0 \text{ V}$                                                                                                                                                                                                                                                   | -1  | 0.1 | 1    | $\mu\text{A}$    |

| High-level output voltage BUSP                 | $V_{OHDp}$ | $V1 \text{ or } V3 > 2.1 \text{ V}$                                                                                                                                                                                                                                  | 1.8 | 2.5 | 3.2  | V                |

| Low-level output voltage BUSM                  | $V_{OHDm}$ | $V1 \text{ or } V3 > 2.1 \text{ V}$                                                                                                                                                                                                                                  | 1.8 | 2.5 | 3.2  | V                |

| High-level output current (BUPSP out; BUSM in) | $I_{OH}$   | $V1 \text{ or } V3 > 2.1 \text{ V}$                                                                                                                                                                                                                                  | 3.1 | 3.8 | 4.5  | mA               |

| Low-level output voltage BUPSP, BUSM           | $V_{OLD}$  | $V1 \text{ and } V3 < 1.65 \text{ V}$                                                                                                                                                                                                                                | 2.3 | 2.5 | 2.7  | V                |

| Driver output resistance                       | $R_O$      | $V1 \text{ or } V3 > 2.1 \text{ V} \text{ Fehler! Verweisquelle konnte nicht gefunden werden.. 3; measure } I_{61} \text{ at } V6 = V_{OLD} + 0.3 \text{ V then measure } I_{62} \text{ at } V6 = V_{OLD} - 0.3 \text{ V; } R_O = 0.6 \text{ V} / (I_{61} - I_{62})$ | 5   | 10  | 15   | $\text{k}\Omega$ |

| Driver delay time low -> high                  | $T_{DDR}$  | $V1 = 4.5 \text{ V} \uparrow; V6 - V5 = 110 \text{ mV} \uparrow;$                                                                                                                                                                                                    |     | 80  | 150  | ns               |

| Driver delay time high -> low                  | $T_{DDF}$  | $V1 = 0.5 \text{ V} \downarrow; V6 - V5 = 30 \text{ mV} \downarrow;$                                                                                                                                                                                                 |     | 40  | 70   | ns               |

### 4.3 RECEIVER

Table 5: Receiver

| Parameter                                               | Symbol    | Conditions                                                                                                                                       | Min | Typ | Max | Unit |

|---------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| High-level input voltage at low common-mode BUPSP-BUSM  | $V_{IH1}$ | $V6 = 0 \text{ V} \rightarrow 5 \text{ V}; V5 = 0 \text{ V}; V1 = 0 \text{ V}; V3 = 0 \text{ V}; V2 = 4 \text{ V} \uparrow; V_{IH1} = V6 - V5$   | 45  | 80  | 110 | mV   |

| High-level input voltage at high common-mode BUPSP-BUSM | $V_{IH2}$ | $V6 = 0 \text{ V} \rightarrow 5 \text{ V}; V5 = 4.5 \text{ V}; V1 = 0 \text{ V}; V3 = 0 \text{ V}; V2 = 4 \text{ V} \uparrow; V_{IH2} = V6 - V5$ | 45  | 80  | 110 | mV   |

| Low-level input voltage at low common-mode BUPSP-BUSM   | $V_{IL1}$ | $V6 = 5 \text{ V} \rightarrow 0 \text{ V}; V5 = 0 \text{ V}; V1 = 0 \text{ V}; V3 = 0 \text{ V}; V2 = 1 \text{ V} \downarrow; V_{IL1} = V6 - V5$ | 30  | 50  | 95  | mV   |

| High-level input voltage at high common-mode BUPSP-BUSM | $V_{IL2}$ | $V6 = 5 \text{ V} \rightarrow 0 \text{ V}; V5 = 4.5 \text{ V}; V1 = 0 \text{ V};$                                                                | 30  | 50  | 95  | mV   |

## Bus Interface IC (Driver, Receiver)

| Parameter                                              | Symbol      | Conditions                                                                                                                                                                                                                                        | Min | Typ | Max | Unit          |

|--------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

|                                                        |             | $V3 = 0 \text{ V}; V2 = 1 \text{ V} \downarrow; V_{IL2} = V6 - V5$                                                                                                                                                                                |     |     |     |               |

| Input hysteresis voltage at low common-mode BUSP-BUSM  | $V_{IHYS1}$ | $V_{IHYS1} = V_{IH1} - V_{IL1}$                                                                                                                                                                                                                   | 15  | 30  | 45  | mV            |

| Input hysteresis voltage at high common-mode BUSP-BUSM | $V_{IHYS2}$ | $V_{IHYS2} = V_{IH2} - V_{IL2}$                                                                                                                                                                                                                   | 15  | 30  | 45  | mV            |

| High-level common-mode input voltage BUSM              | $V_{HCOM}$  | $V5 = 0 \text{ V} \rightarrow 5 \text{ V}; V1 = 0 \text{ V}; V3 = 0 \text{ V}; V_{HCOM} = V5 \text{ when } V2 = 4 \text{ V} \downarrow; V6 - V5 = 110 \text{ mV}$                                                                                 | 4.5 |     |     | V             |

| Low-level common-mode input voltage BUSM               | $V_{LCOM}$  | $V5 = 0 \text{ V} \rightarrow 5 \text{ V}; V1 = 0 \text{ V}; V3 = 0 \text{ V}; V_{HCOM} = V5 \text{ when } V4 = 1 \text{ V} \uparrow; V6 - V5 = 30 \text{ mV}$                                                                                    | 5   |     |     | V             |

| Receiver input resistance                              | $R_I$       | $V1 \text{ and } V3 < 1.65 \text{ V}$ Fehler! Verweisquelle konnte nicht gefunden werden.. 3; measure $I_{63}$ at $V6 = V_{OLD} + 0.3 \text{ V}$ then measure $I_{64}$ at $V6 = V_{OLD} - 0.3 \text{ V}; R_I = 0.6 \text{ V} / (I_{63} - I_{64})$ | 25  | 35  | 45  | k $\Omega$    |

| High-level receiver output leakage current ROUT        | $I_{ROH}$   | $V1 = 5 \text{ V}; V3 = 0 \text{ V}; V2 = 5 \text{ V}$                                                                                                                                                                                            | -1  | 0   | 1   | $\mu\text{A}$ |

| Standby 1 receiver output leakage current ROUT         | $I_{ROS1}$  | $V1 = 0 \text{ V}; V3 = 0 \text{ V}; V8 = 0 \text{ V}; VCC = 0 \text{ V}; V2 = 5 \text{ V}$                                                                                                                                                       | -1  | 0   | 1   | $\mu\text{A}$ |

| Standby 2 receiver output leakage current ROUT         | $I_{ROS2}$  | $V1 = 0 \text{ V}; V3 = 0 \text{ V}; V8 = 0 \text{ V}; V2 = 5 \text{ V}$                                                                                                                                                                          | -1  | 0   | 1   | $\mu\text{A}$ |

| Low-level 1 receiver output voltage ROUT               | $V_{ROL1}$  | $V1 = 0 \text{ V}; V3 = 0 \text{ V}; I2 = 1.5 \text{ mA}$                                                                                                                                                                                         |     |     | 0.6 | V             |

| Low-level 2 receiver output voltage ROUT               | $V_{ROL2}$  | $V1 = 0 \text{ V}; V3 = 0 \text{ V}; I2 = 200 \mu\text{A}$                                                                                                                                                                                        |     |     | 0.3 | V             |

| Receiver delay time low $\rightarrow$ high             | $T_{RDR}$   | $V6 - V5 = 110 \text{ mV} \uparrow; V2 = 4.5 \text{ V} \uparrow$                                                                                                                                                                                  |     | 600 | 700 | ns            |

| Receiver delay time high $\rightarrow$ low             | $T_{RDF}$   | $V6 - V5 = 30 \text{ mV} \downarrow; V2 = 0.5 \text{ V} \downarrow$                                                                                                                                                                               |     | 110 | 150 | ns            |

## 4.4 BIAS AND VCC

Table 6: BIAS and VCC

| Parameter                                  | Symbol     | Conditions                                                                                                                                     | Min | Typ | Max | Unit          |

|--------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| Quiescent current high Vcc                 | $I_{CCH}$  | $V1 \text{ or } V3 > 2.1 \text{ V}$                                                                                                            | 3   |     | 8.5 | mA            |

| Quiescent current low Vcc                  | $I_{CCL}$  | $V1 \text{ and } V3 < 1.65 \text{ V}$                                                                                                          | 0.8 |     | 1.8 | mA            |

| Standby driver output leakage current BUSP | $I_{DOS}$  | $V8 = 0 \text{ V}; V1 \text{ or } V3 > 2.1 \text{ V}; V6 = 5 \text{ V}$                                                                        | -1  |     | 1   | $\mu\text{A}$ |

| Standby supply leakage current Vcc         | $I_{VCCS}$ | $V8 = 0 \text{ V}; V1 \text{ or } V3 > 2.1 \text{ V};$                                                                                         | -1  |     | 1   | $\mu\text{A}$ |

| Standby high-level input voltage STB       | $V_{STBH}$ | $V8 = 0 \text{ V} \rightarrow 5 \text{ V}; V1 = 0 \text{ V}; V3 = 0 \text{ V}; V_{STBH} = V8 \text{ when } V5, V6 = 2.3 \text{ V} \uparrow$    | 0.9 |     | 2   | V             |

| Standby low-level input voltage STB        | $V_{STBL}$ | $V8 = 5 \text{ V} \rightarrow 0 \text{ V}; V1 = 5 \text{ V}; V3 = 0 \text{ V}; V_{STBH} = V8 \text{ when } I_{VCC} = 1 \mu\text{A} \downarrow$ | 0.9 |     | 2   | V             |

## Bus Interface IC (Driver, Receiver)

| Parameter                               | Symbol     | Conditions                                                 | Min | Typ | Max | Unit          |

|-----------------------------------------|------------|------------------------------------------------------------|-----|-----|-----|---------------|

| Standby high-level input current<br>STB | $I_{STBH}$ | $V_8 = 5 \text{ V}; V_1 = 5 \text{ V}; V_3 = 0 \text{ V};$ |     | 50  | 100 | $\mu\text{A}$ |

| Standby low-level input current<br>STB  | $I_{STBL}$ | $V_8 = 0 \text{ V}; V_1 = 5 \text{ V}; V_3 = 0 \text{ V};$ | -1  | 0   | 1   | $\mu\text{A}$ |

Figure 3: Measurement Circuits

## 5 Functional Description

### 5.1 DRIVER

The “Driver block” has two inputs and a differential current output. The inputs IN1 (Pin 1) and IN2 (Pin 3) are “or”-connected and their switching level and hysteresis are 3.3V and 5V compatible. The output BUSP (Pin 6) delivers a source current and BUSM (Pin 5) delivers a sink current of the same amount, so that with an external 60 Ohm Resistor between BUSP and BUSM the differential voltage is 230 mV (high) and 0 mV (low). The common-mode voltage is about 2.5 V, but the output can withstand external voltage up to VCC + 0.3V.

## Bus Interface IC (Driver, Receiver)

### 5.2 RECEIVER

The “Receiver block” has a differential voltage input and an open collector output. It share the Pins BUSP (Pin 6) and BUSM (Pin 5) with the driver block, but for the receiver block they are the differential voltage input. They have a large common-mode operating voltage from 0 V to 4.5 V and can withstand external voltage up to VCC + 0.3V. The receiver output ROUT is open collector, so that the supply voltage for the external resistor at this Pin determines the following logic level.

### 5.3 BIAS

The “Bias block” delivers an internal reference voltage (2.5 V), several reference currents and the chance with the signal of Pin STB (Pin 8) to activate or deactivate the supply for all function blocks, so that in the standby mode ( $V(STB) < 0.9$  V) the power supply current falls to less than 1 $\mu$ A.

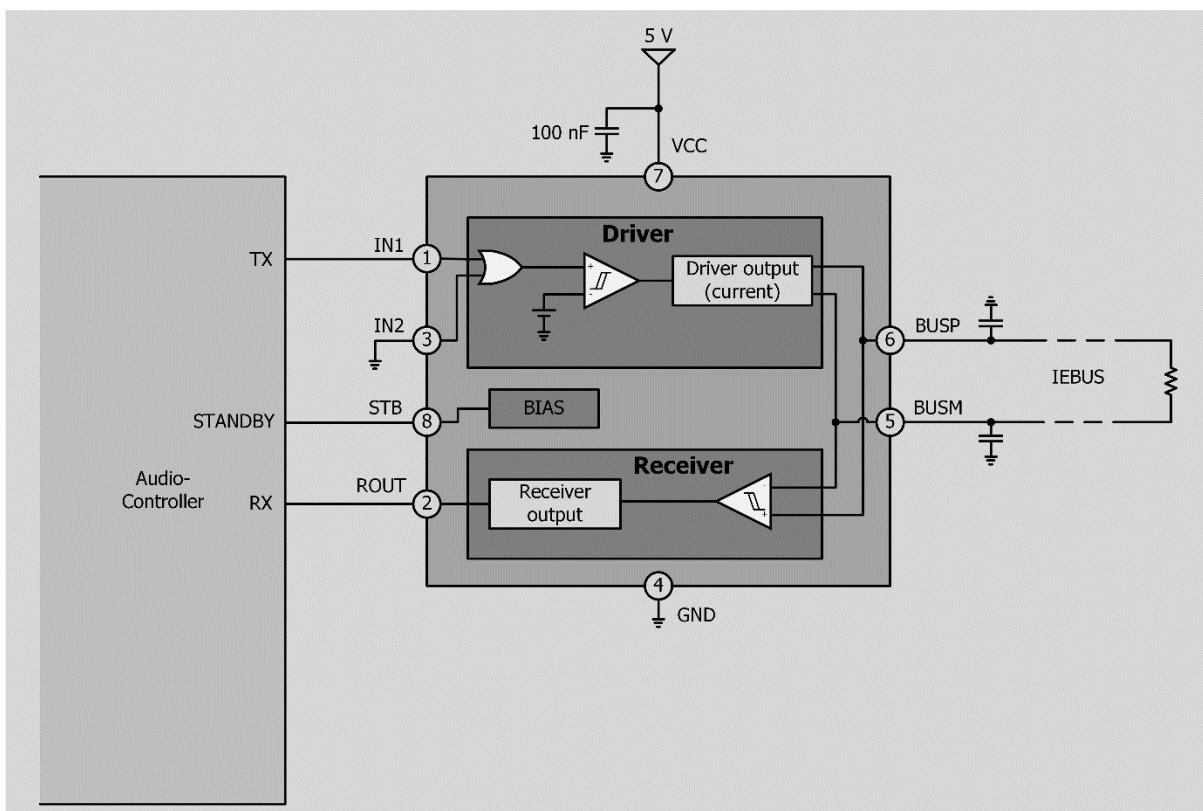

## 6 Application notes

Figure 4: Application

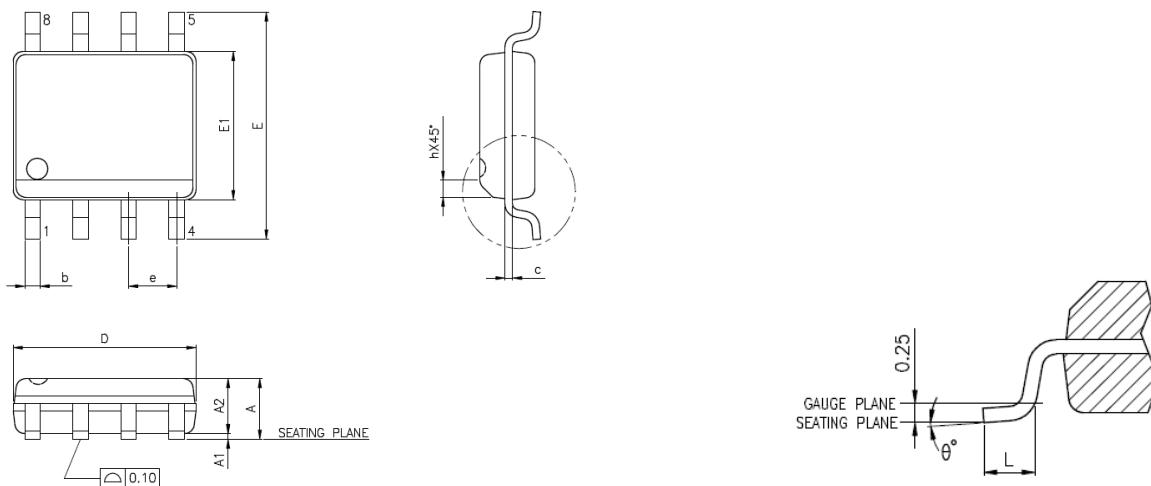

## 7 Package Outline

### 7.1 SOP8 Package

**Figure 5: SOP8 Package**

| Symbol     | A    | A1   | A2   | b    | C    | D    | E    | E1   | e    | L    | h    | $\Theta^\circ$ |

|------------|------|------|------|------|------|------|------|------|------|------|------|----------------|

| <b>Min</b> | --   | 0.10 | 1.25 | 0.31 | 0.10 | 4.90 | 6.00 | 3.90 | 1.27 | 0.40 | 0.25 | 5.15           |

| <b>Max</b> | 1.75 | 0.25 | --   | 0.51 | 0.25 | BSC. | BSC. | BSC. | BSC. | 1.27 | 0.50 | 5.25           |

NOTES:

- 1.JEDEC OUTLINE : MS-012 AA REV.F (STANDARD)

MS-012 BA REV.F (THERMAL)

- 2.DIMENSIONS "D" DOES NOT INCLUDE MOLD FLASH,

PROTRUSIONS OR GATE BURRS.MOLD FLASH, PROTRUSIONS

AND GATE BURRS SHALL NOT EXCEED 0.15mm.

PER SIDE.

- 3.DIMENSIONS "E1" DOES NOT INCLUDE INTER-LEAD FLASH,

OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS

SHALL NOT EXCEED 0.25mm PER SIDE.

## Bus Interface IC (Driver, Receiver)

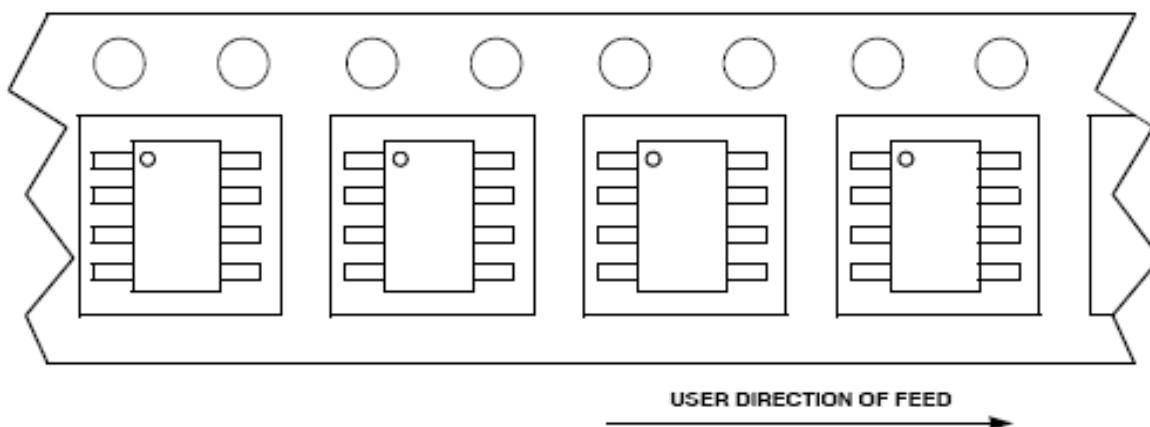

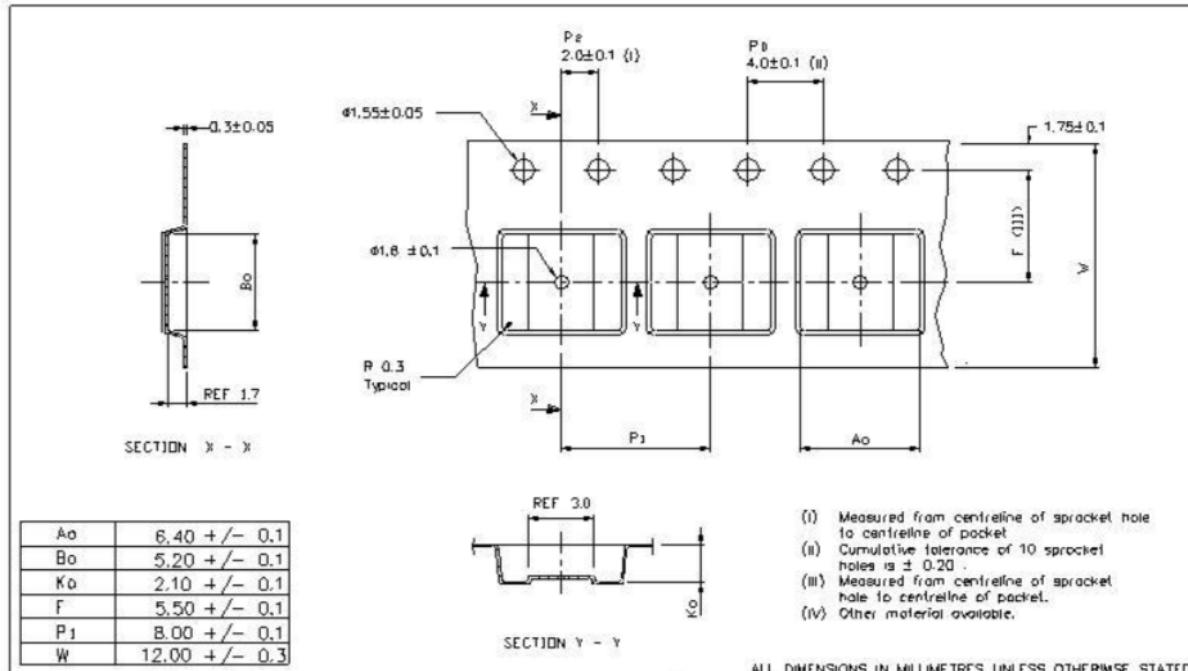

## 8 Tape and Reel Information

## 8.1 TAPE INFORMATION

Figure 6: Tape Information

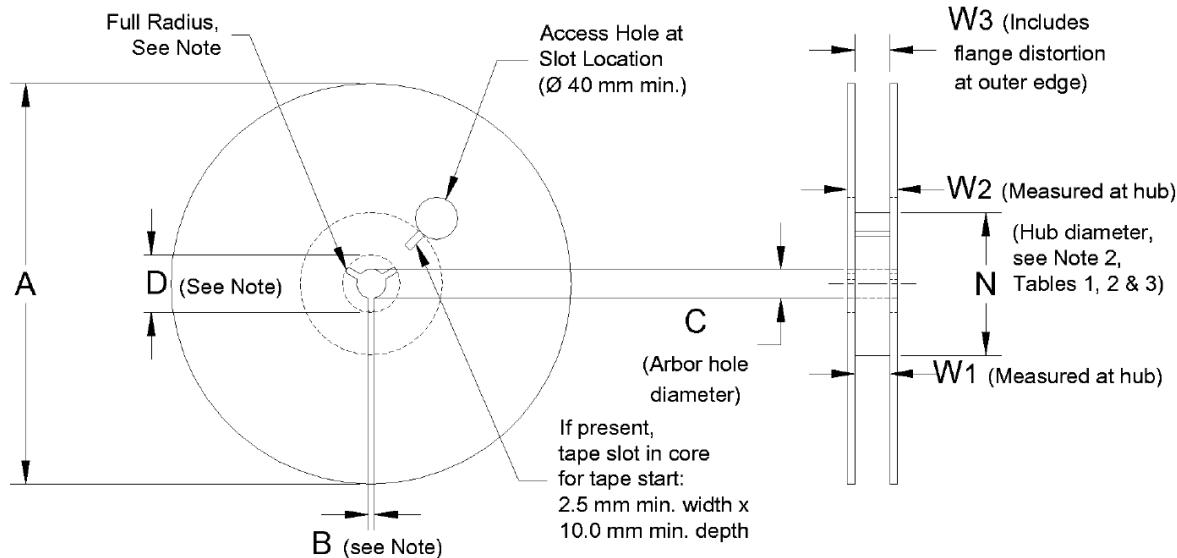

## 8.2 Reel Information

Note: Drive spokes optional; if used, dimensions B and D shall apply.

**Figure 7: Reel Information**

| Symbol         | A   | B   | C    | D    | W <sub>1</sub> |

|----------------|-----|-----|------|------|----------------|

| <b>Minimal</b> | -   | 1.5 | 12.8 | 20.2 | 13.25          |

| <b>Typical</b> | -   | -   | 13.0 | -    | -              |

| <b>Maximum</b> | 330 | -   | 13.5 | -    | 13.75          |

## 9 Ordering Information

**Table 7: Ordering Information**

| Part    | Order No.     | Package | Delivery    | Quantity             |

|---------|---------------|---------|-------------|----------------------|

| CCA1224 | CCA1224_SO-P8 | SOPN-8  | Tape & Reel | 3.800 parts per reel |

|         |               |         |             |                      |

## Bus Interface IC (Driver, Receiver)

### 10 Revision History

| Revision | Date        | Description               |

|----------|-------------|---------------------------|

| 1.4      | 31-Oct-2019 | Updated Template          |

| 1.3      | 24-Jul-2015 | Updated Form              |

| 1.2      | 30-Apr-2015 | Change of Part Number     |

| 1.1      | 25-Mar-2015 | Changes in Timing and Bus |

| 1.0      | 28-Aug-2014 | Initial version           |

|          |             |                           |

### 11 Disclaimer

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website ([www.dialog-semiconductor.com](http://www.dialog-semiconductor.com)) unless otherwise stated.

Dialog and the Dialog logo are trademarks of Dialog Semiconductor plc or its subsidiaries. All other product or service names are the property of their respective owners.

© 2019 Dialog Semiconductor. All rights reserved.

**Bus Interface IC (Driver, Receiver)****Contents**

|                                   |    |

|-----------------------------------|----|

| General Description .....         | 1  |

| 1.1    Features .....             | 1  |

| 1.2    Schematic.....             | 1  |

| 2 Pinout .....                    | 2  |

| 2.1    Package .....              | 2  |

| 2.2    Pin Descriptions .....     | 2  |

| 3 Absolute Maximum Ratings .....  | 3  |

| 4 Electrical Characteristics..... | 3  |

| 4.1    General Parameters.....    | 3  |

| 4.2    Driver .....               | 4  |

| 4.3    Receiver .....             | 4  |

| 4.4    BIAS and VCC.....          | 5  |

| 5 Functional Description.....     | 6  |

| 5.1    Driver .....               | 6  |

| 5.2    Receiver .....             | 7  |

| 5.3    BIAS .....                 | 7  |

| 6 Application notes .....         | 7  |

| 7 Package Outline .....           | 8  |

| 8 Tape and Reel Information.....  | 9  |

| 8.1    Tape Information .....     | 9  |

| 8.2    Reel Information .....     | 10 |

| 9 Ordering Information .....      | 10 |

| 10 Revision History .....         | 11 |

| 11 Disclaimer .....               | 11 |

| Contents .....                    | 12 |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).