# 1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER

## IDTCSPU877A

#### **FEATURES:**

- · 1 to 10 differential clock distribution

- Optimized for clock distribution in DDR2 (Double Data Rate) SDRAM applications

- Operating frequency: 125MHz to 340MHz

- Very low skew: ≤40ps

- Very low jitter: ≤40ps

- 1.8V AVDD and 1.8V VDDQ

- · CMOS control signal input

- · Test mode enables buffers while disabling PLL

- · Low current power-down mode

- Tolerant of Spread Spectrum input clock

- Available in 52-Ball VFBGA and 40-pin VFQFPN packages

### APPLICATIONS:

- Meets or exceeds JEDEC standard 82.8 for registered DDR2 clock driver

- Along with SSTU32864/65/66, DDR2 register, provides complete solution for DDR2 DIMMs

#### **DESCRIPTION:**

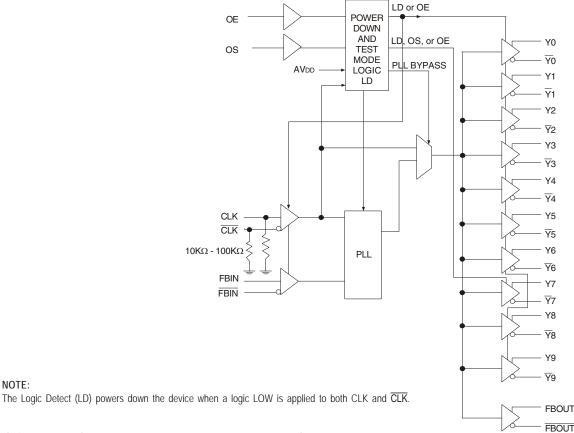

The CSPU877A is a PLL based clock driver that acts as a zero delay buffer to distribute one differential clock input pair(CLK,  $\overline{\text{CLK}}$ ) to 10 differential output pairs ( $\overline{\text{Y}}$  [0:9], Y [0:9]) and one differential pair of feedback clock output (FBOUT,  $\overline{\text{FBOUT}}$ ). External feedback pins (FBIN,  $\overline{\text{FBIN}}$ ) for synchronization of the outputs to the input reference is provided. OE, OS, and AVDD control the power-down and test mode logic. When AVDD is grounded, the PLL is turned off and bypassed for test mode purposes. When the differential clock inputs (CLK,  $\overline{\text{CLK}}$ ) are both at logic low, this device will enter a low power-down mode. In this mode, the receivers are disabled, the PLL is turned off, and the output clock drivers are disabled, resulting in a current consumption device of less than 500µA.

The CSPU877A requires no external components and has been optimised for very low phase error, skew, and jitter, while maintaining frequency and duty cycle over the operating voltage and temperature range. The CSPU877A, designed for use in both module assemblies and system motherboard based solutions, provides an optimum high-performance clock source.

The CSPU877A is available in Commercial Temperature Range (0°C to +70°C). See Ordering Information for details.

#### **FUNCTIONAL BLOCK DIAGRAM**

COMMERCIAL TEMPERATURE RANGE

OCTOBER 2006

# **PIN CONFIGURATION**

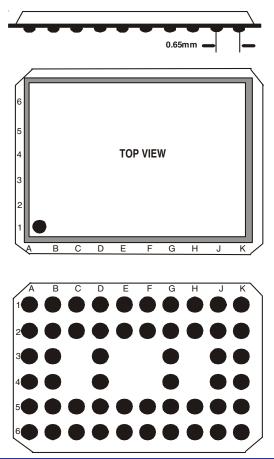

|   |            |           |                |            |      | ı    | 1     |       |            |            |

|---|------------|-----------|----------------|------------|------|------|-------|-------|------------|------------|

| 6 | Y6         | <u>Y6</u> | <del>Y</del> 7 | <b>Y</b> 7 | FBIN | FBIN | FBOUT | FBOUT | Y8         | <u>Y8</u>  |

| 5 | <b>Y</b> 5 | GND       | GND            | os         | VDDQ | OE   | VDDQ  | GND   | GND        | <u></u>    |

| 4 | <u>Y</u> 5 | GND       | NB             | VDDQ       | NB   | NB   | VDDQ  | NB    | GND        | <b>Y</b> 9 |

| 3 | <u>Y</u> 0 | GND       | NB             | VDDQ       | NB   | NB   | VDDQ  | NB    | GND        | <b>Y</b> 4 |

| 2 | Yo         | GND       | GND            | VDDQ       | VDDQ | VDDQ | VDDQ  | GND   | GND        |            |

| 1 | Y1         | <u>Y1</u> | Y2             | Y2         | CLK  | CLK  | AGND  | AVDD  | <b>Y</b> 3 | <u>Y3</u>  |

|   | Α          | В         | С              | D          | E    | F    | G     | Н     | J          | K          |

VFBGA TOP VIEW

## **52 BALL VFBGA PACKAGE LAYOUT**

# PIN CONFIGURATION, CONT.

## ABSOLUTE MAXIMUM RATINGS(1,2)

| Symbol            | Rating                          | Max                            | Unit |

|-------------------|---------------------------------|--------------------------------|------|

| Vddq, AVdd        | Supply Voltage Range            | -0.5 to +2.5                   | V    |

| VI(3)             | Input Voltage Range             | -0.5 to V <sub>DDQ</sub> + 0.5 | V    |

| Vo <sup>(3)</sup> | Voltage range applied to any    | -0.5 to VDDQ + 0.5             | V    |

|                   | output in the high or low state |                                |      |

| lık               | Input clamp current             | ±50                            | mA   |

| (VI <0)           |                                 |                                |      |

| Іок               | Output Clamp Current            | ±50                            | mA   |

| (Vo <0 or         |                                 |                                |      |

| Vo > Vddq)        |                                 |                                |      |

| lo                | Continuous Output Current       | ±50                            | mA   |

| (Vo =0 to VDDQ)   |                                 |                                |      |

| VDDQ or GND       | Continuous Current              | ±100                           | mA   |

| TSTG              | Storage Temperature Range       | - 65 to +150                   | °C   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation of

the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

- The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils.

- The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed. This value is limited to 2.5V max.

## CAPACITANCE(1)

| Parameter | Description             | Min. | Тур. | Max. | Unit |

|-----------|-------------------------|------|------|------|------|

| CIN       | Input Capacitance       | 2    | _    | 3    | pF   |

|           | VI = VDDQ or GND        |      |      |      |      |

| CιΔ       | Delta Input Capacitance |      |      | 0.25 | pF   |

|           | CLK, CLK, FBIN, FBIN    |      |      |      |      |

| CL        | Load Capacitance        | _    | 10   | _    | pF   |

#### NOTE:

1. Unused inputs must be held high or low to prevent them from floating.

## RECOMMENDED OPERATING CONDITIONS

| Symbol                          | Parameter                      | Min. | Тур. | Max. | Unit |

|---------------------------------|--------------------------------|------|------|------|------|

| AV <sub>DD</sub> <sup>(1)</sup> | Supply Voltage                 |      | Vddq |      | V    |

| VDDQ                            | I/O Supply Voltage             | 1.7  | 1.8  | 1.9  | V    |

| TA                              | Operating Free-Air Temperature | 0    | _    | +70  | °C   |

#### NOTE:

1. The PLL is turned off and bypassed for test purposes when AVpp is grounded. During this test mode, Vppp remains within the recommended operating conditions and no timing parameters are guaranteed.

# PIN DESCRIPTION (VFBGA)

| Pin Name      | Pin Number                             | Description                                                                     |

|---------------|----------------------------------------|---------------------------------------------------------------------------------|

| AGND          | G1                                     | Ground for 1.8V analog supply                                                   |

| AVdd          | H1                                     | 1.8V analog supply                                                              |

| CLK, CLK      | E1, F1                                 | Differential clock input with a 10K $\Omega$ to 100K $\Omega$ pulldown resistor |

| FBIN, FBIN    | E6, F6                                 | Feedback differential clock input                                               |

| FBOUT, FBOUT  | G6, H6                                 | Feedback differential clock output                                              |

| GND           | B2 - B5, C2, C5, H2, H5, J2 - J5       | Ground                                                                          |

| VDDQ          | D2 - D4, E2, E5, F2, G2 - G5           | 1.8V supply                                                                     |

| OE            | F5                                     | Output Enable                                                                   |

| OS            | D5                                     | Output Select (tied to GND or VDDQ)                                             |

| <u>Y[0:9]</u> | A3, A4, B1, B6, C1, C6, K1, K2, K5, K6 | Buffered output of input clock, CLK                                             |

| Y[0:9]        | A1, A2, A5, A6, D1, D6, J1, J6, K3, K4 | Buffered output of input clock, CLK                                             |

| NB            |                                        | No Ball                                                                         |

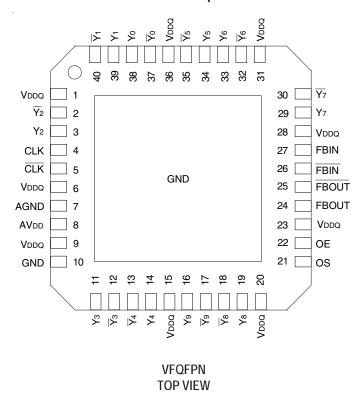

# PIN DESCRIPTION (VFQFPN)

| Pin Name     | Pin Number                            | Description                                                                     |

|--------------|---------------------------------------|---------------------------------------------------------------------------------|

| AGND         | 7                                     | Ground for 1.8V analog supply                                                   |

| AVDD         | 8                                     | 1.8V analog supply                                                              |

| CLK, CLK     | 4, 5                                  | Differential clock input with a 10K $\Omega$ to 100K $\Omega$ pulldown resistor |

| FBIN, FBIN   | 26,27                                 | Feedback differential clock input                                               |

| FBOUT, FBOUT | 24,25                                 | Feedback differential clock output                                              |

| GND          | 10                                    | Ground                                                                          |

| VDDQ         | 1, 6, 9, 15, 20, 23, 28, 31, 36       | 1.8V supply                                                                     |

| OE           | 22                                    | Output Enable                                                                   |

| OS           | 21                                    | Output Select (tied to GND or VDDQ)                                             |

| Y[0:9]       | 3, 11, 14, 16, 19, 29, 33, 34, 38, 39 | Buffered output of input clock, CLK                                             |

| Y[0:9]       | 2, 12, 13, 17, 18, 30, 32, 35, 37, 40 | Buffered output of input clock, CLK                                             |

| NB           |                                       | No Ball                                                                         |

## **FUNCTION TABLE**(1,2)

| INPUTS     |    |    |                  |                  |            | 0              | UTPUTS |       |     |

|------------|----|----|------------------|------------------|------------|----------------|--------|-------|-----|

| AVDD       | OE | OS | CLK              | CLK              | Υ          | Y              | FBOUT  | FBOUT | PLL |

| GND        | Н  | Х  | L                | Н                | L          | Н              | L      | Н     | OFF |

| GND        | Н  | Х  | Н                | L                | Н          | L              | Н      | L     | OFF |

| GND        | L  | Н  | L                | Н                | L(z)       | L(z)           | L      | Н     | OFF |

|            |    |    |                  |                  | L(z)       | L(z)           |        |       |     |

| GND        | L  | L  | Н                | L                | <b>Y</b> 7 | <del>Y</del> 7 | Н      | L     | OFF |

|            |    |    |                  |                  | Active     | Active         |        |       |     |

| 1.8V (nom) | L  | Н  | L                | Н                | L(z)       | L(z)           | L      | Н     | ON  |

|            |    |    |                  |                  | L(z)       | L(z)           |        |       |     |

| 1.8V (nom) | L  | L  | Н                | L                | <b>Y</b> 7 | <del>Y</del> 7 | Н      | L     | ON  |

|            |    |    |                  |                  | Active     | Active         |        |       |     |

| 1.8V (nom) | Н  | Х  | L                | Н                | L          | Н              | L      | Н     | ON  |

| 1.8V (nom) | Н  | Х  | Н                | L                | Н          | L              | Н      | L     | ON  |

| 1.8V (nom) | Х  | Х  | L <sup>(3)</sup> | L <sup>(3)</sup> | L(z)       | L(z)           | L(z)   | L(z)  | OFF |

| Х          | Х  | Х  | Н                | Н                | Reserved   |                |        |       |     |

#### NOTES:

- 1. H = HIGH Voltage Level

- L = LOW Voltage Level

- X = Don't Care

- 2. L(z) means the outputs are disabled to a LOW state, meeting the lopL limit in DC Electrical Characteristics table.

- 3. The device will enter a low power-down mode when CLK and  $\overline{\text{CLK}}$  are both at logic LOW.

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Commercial:  $TA = 0^{\circ}C$  to  $+70^{\circ}C$

| Symbol                 | Parameter                             | Conditions                                              | Min.       | Тур. | Max.       | Unit |

|------------------------|---------------------------------------|---------------------------------------------------------|------------|------|------------|------|

| Vik                    | Input Clamp Voltage (All Inputs)      | VDDQ = 1.7V, II = -18mA                                 | _          | _    | -1.2       | V    |

| VIL <sup>(2)</sup>     | Input LOW Voltage (OE, OS, CLK, CLK)  |                                                         | _          | _    | 0.35VDDQ   | V    |

| VIH <sup>(2)</sup>     | Input HIGH Voltage (OE, OS, CLK, CLK) |                                                         | 0.65Vddq   | _    | _          |      |

| VIN <sup>(1)</sup>     | Input Signal Voltage                  |                                                         | -0.3       | _    | VDDQ + 0.3 | V    |

| VID(DC) <sup>(2)</sup> | DC Input Differential Voltage         |                                                         | 0.3        |      | VDDQ + 0.4 | V    |

| Vop <sup>(3)</sup>     | Output Differential Voltage           | AVDD/VDDQ = 1.7V                                        | 0.5        | _    | _          | V    |

| Voн                    | Output HIGH Voltage                   | IOH = -100μA, VDDQ = 1.7V to 1.9V                       | VDDQ - 0.2 |      | _          | V    |

|                        |                                       | IOH = -9mA, VDDQ = 1.7V                                 | 1.1        |      | _          |      |

| Vol                    | Output LOW Voltage                    | IOL = 100μA, VDDQ = 1.7V to 1.9V                        |            |      | 0.1        | V    |

|                        |                                       | IOL = 9mA, VDDQ = 1.7V                                  |            |      | 0.6        |      |

| IODL                   | Output Disabled LOW Current           | OE = L, Vodl = 100mV, Avdd/Vddq = 1.7V                  | 100        | _    | _          | μΑ   |

| lin                    | Input Current CLK, CLK                | AVDD/VDDQ = Max., VI = 0V to VDDQ                       |            |      | ±250       | μΑ   |

|                        | OE, OS, FBIN, FBIN                    |                                                         |            |      | ±10        |      |

| IDDLD                  | Static Supply Current (IDDQ and IADD) | AVDD/VDDQ = Max., CLK and $\overline{\text{CLK}}$ = GND |            |      | 500        | μΑ   |

| IDD                    | Dynamic Power Supply Current          | AVDD/VDDQ = Max., CLK = 270MHz                          |            |      | 300        | mA   |

|                        | (IDDQ and IADD) <sup>(4,5)</sup>      |                                                         |            |      |            |      |

#### NOTES:

- 1. VIN specifies the allowable DC excursion of each different output.

- 2. VID is the magnitude of the difference between the input level on CLK and the input level on CLK and The CLK an

- 3. Vod is the magnitude of the difference between the true output level and the complementary level.

- 4. All Outputs are left open (unconnected to PCB).

- 5. Total IDD = IDDD + IADD = FCK \* CPD \* VDDD, for Cpd = (IDDD + IADD) / (FCK \* VDDD) where FCK is the input frequency, VDDD is the Power Dissipation Capacitance.

#### TIMING REQUIREMENTS

| Symbol | Parameter                                    | Min. | Max. | Unit |

|--------|----------------------------------------------|------|------|------|

| fclk   | Operating Clock Frequency <sup>(1,2,3)</sup> | 125  | 340  | MHz  |

|        | Application Clock Frequency <sup>(2,4)</sup> | 160  | 340  | MHz  |

| toc    | Input Clock Duty Cycle                       | 40   | 60   | %    |

| t_     | Stabilization Time <sup>(5)</sup>            |      | 15   | μs   |

#### NOTES:

- 1. 270MHz max clock frequency for parts assembled and tested prior to WW37.

- 2. The PLL will track a spread spectrum clock input.

- 3. Operating clock frequency is the range over which the PLL will lock, but may not meet all timing specifications. To be used only for low speed system debug.

- 4. Application clock frequency is the range over which timing specifications apply.

- 5. Stabilization time is the time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal after power up. During normal operation, the stabilization time is also the time required for the PLL circuit to obtain phase lock of its feedback signal to its reference signal when CLK and CLK go to a logic LOW state, enters the power-down mode, and later return to active operation. CLK and CLK may be left floating after they have been driven LOW for one complete clock cycle.

# AC ELECTRICAL CHARACTERISTICS(1)

| Symbol                    | Description                                         | Test Conditions                                  | Min.              | Typ. <sup>(2)</sup> | Max.          | Unit |

|---------------------------|-----------------------------------------------------|--------------------------------------------------|-------------------|---------------------|---------------|------|

| tPLH <sup>(2)</sup>       | LOW to HIGH Level Propagation Delay Time            | AVDD = GND, OE = H, OS = L,                      |                   | TBD                 |               | ns   |

|                           |                                                     | CLK to any output                                |                   |                     |               |      |

| t <sub>PHL</sub> (2)      | HIGH to LOW Level Propagation Delay Time            | AVDD = GND, OE = H, OS = L,                      |                   | TBD                 |               | ns   |

|                           |                                                     | CLK to any output                                |                   |                     |               |      |

| tjit(cc+)                 | Jitter (cycle-to-cycle)                             | 166/200/266MHz                                   | 0                 |                     | 40            | ps   |

| t/IT(CC-)                 | 1                                                   |                                                  | 0                 |                     | -40           |      |

| UIT(PER) <sup>(3)</sup>   | Jitter (period)                                     | 166/200/266MHz                                   | -40               |                     | 40            | ps   |

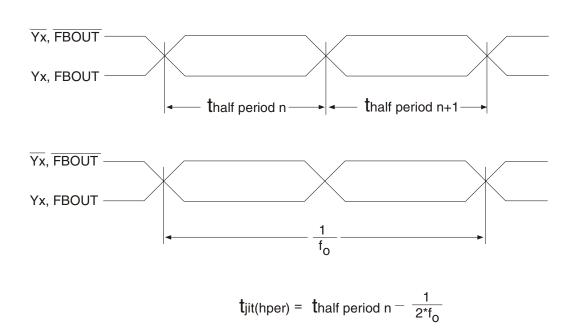

| tjit(HPER) <sup>(3)</sup> | Half-Period Jitter                                  | 166/200/266MHz                                   | -60               |                     | 60            | ps   |

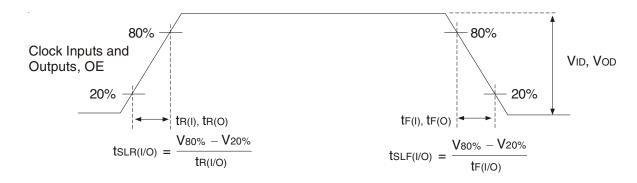

| tslr(0) <sup>(1,4)</sup>  | Output Clock Slew Rate (single-ended)               | 166/200/266MHz (20% to 80%)                      | 1.5               | 2.5                 | 3             | V/ns |

| tslr(1) <sup>(1,4)</sup>  | Output Enable (OE)                                  |                                                  | 0.5               | _                   |               | V/ns |

|                           | Input Clock Slew Rate                               |                                                  | 1                 | 2.5                 | 4             |      |

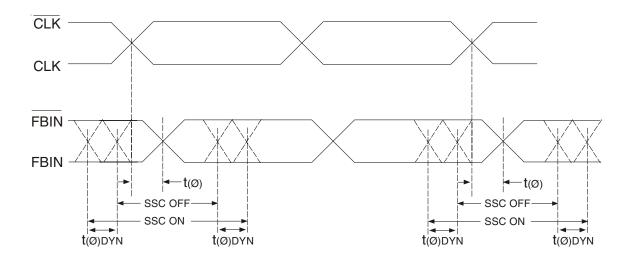

| t(∅) <sup>(5)</sup>       | Static Phase Offset                                 | 166/200/266MHz                                   | -50               |                     | 50            | ps   |

| t(∅)DYN                   | Dynamic Phase Offset                                | 166/200/266MHz                                   | -50               |                     | 50            | ps   |

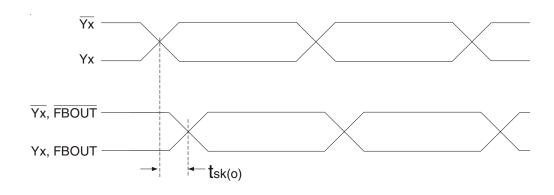

| tsk(o)                    | Output Skew                                         |                                                  |                   |                     | 40            | ps   |

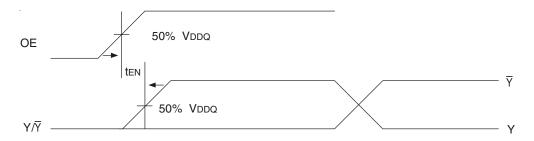

| ten                       | Output Enable to any Y or $\overline{Y}$            |                                                  |                   |                     | 8             | ns   |

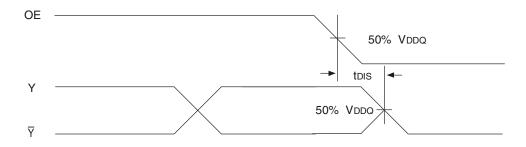

| tdis                      | Output Disable to any Y or $\overline{Y}$           |                                                  |                   |                     | 8             | ns   |

| Vox <sup>(6)</sup>        | AC Differential Output Crosspoint Voltage           | Differential outputs terminated with $120\Omega$ | (VDDQ/2)-0.1      |                     | (VDDQ/2)+0.1  | V    |

| VID(AC)                   | AC Differential Input Voltage                       |                                                  | 0.6               |                     | VDDQ+0.4      | V    |

| Vıx                       | AC Differential Input Crosspoint Voltage            |                                                  | (VDDQ/2)-0.15     |                     | (VDDQ/2)+0.15 | V    |

| The PLL on th             | ne CSPU877A will meet all the above test parameters | s while supporting SSC synthesizers with the fo  | ollowing paramete | rs:                 |               |      |

| SSC                       | Modulation Frequency                                |                                                  | 30                | _                   | 33            | KHz  |

| SSC                       | Clock Input Frequency Deviation                     |                                                  | 0                 | _                   | -0.5          | %    |

| f3dB                      | PLL Loop Bandwidth                                  |                                                  | 2                 |                     |               | MHz  |

#### NOTES

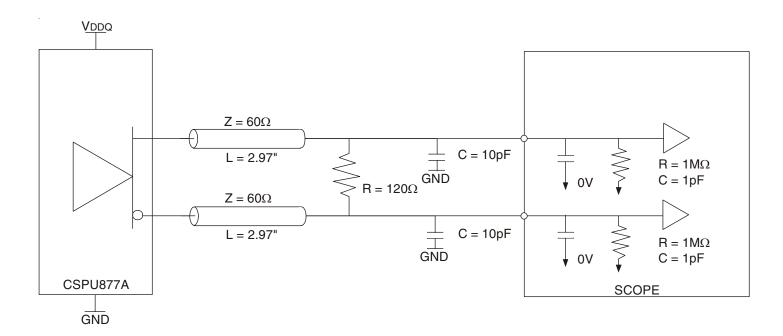

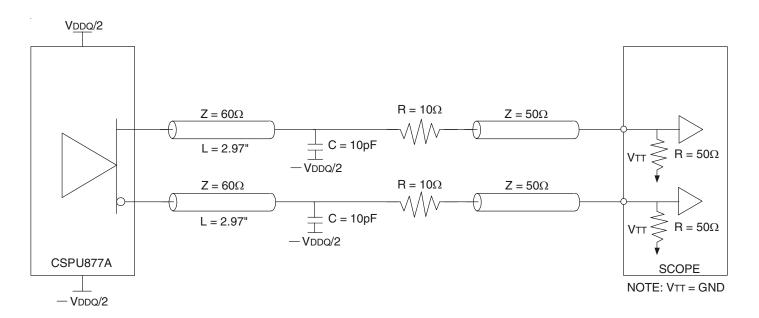

- There are two different terminations that are used with the above AC tests. The output load shown in figure 1 is used to measure the input and output differential pair cross-voltage only. The output load shown in figure 2 is used to measure all other tests, including input and output slew rates. For consistency, use 50Ω equal length cables with SMA connectors on the test board.

- 2. Refers to transition of non-inverting output.

- 3. Period jitter and half-period jitter specifications are seperate specifications that must be met independently of each other.

- 4. To eliminate the impact of input slew rates on static phase offset, the input slew rates of reference clock input (CLK, CLK) and feedback clock input (FBIN, FBIN) are recommended to be nearly equal. The 2.5V/ns slew rates are shown as a recommended target. Compliance with these nominal values is not mandatory if it can be adequately demonstrated that alternative characteristics meet the requirements of the registered DDR2 DIMM application.

- 5. Static phase offset does not include jitter.

- 6. Vox is specified at the DDR DRAM clock input or test load.

Figure 1: Output Load Test Circuit 1

Figure 2: Output Load Test Circuit 2

(N is a large number of samples)

## **TEST CIRCUIT AND SWITCHING WAVEFORMS**

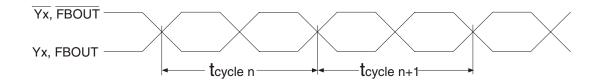

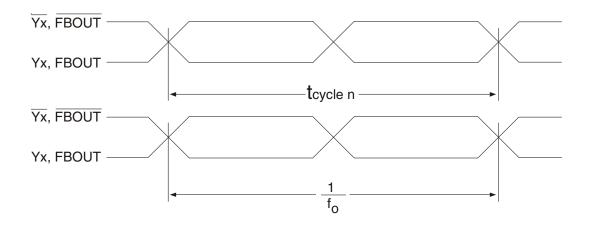

$t_{jit(cc)} = t_{cycle n} - t_{cycle n+1}$

## Cycle-to-Cycle jitter

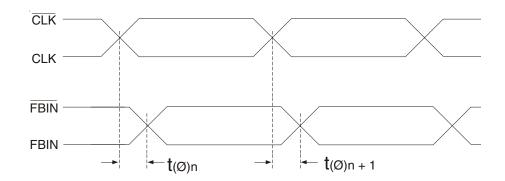

$$t_{(\emptyset)} = \frac{\sum_{1}^{n = N} t_{(\emptyset)n}}{N}$$

Static Phase Offset

**Output Skew**

$$t_{jit(per)} = t_{cycle} n - \frac{1}{f_0}$$

NOTE:

fo = Average input frequency measured at CLK / CLK

## Period jitter

NOTE:

fo = Average input frequency measured at CLK /  $\overline{\text{CLK}}$

Half-Period jitter

Time Delay Between Output Enable (OE) and Clock Output (Y,  $\overline{\mathbf{Y}}$ )

**Dynamic Phase Offset**

Input and Output Slew Rates

#### NOTES:

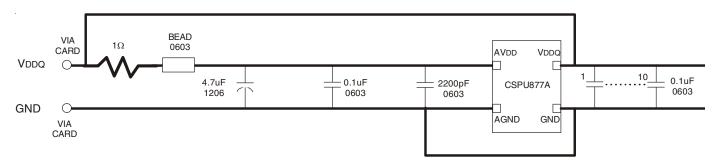

Place all decoupling capacitors as close to the CSPU877A pins as possible.

Use wide traces for AVDD and AGND.

Recommended bead: Fair-rite P/N 2506036017Y0 or equivalent (0.8 $\Omega$  DC max., 600 $\Omega$  at 100MHz).

Recommended Filtering for the Analog and Digital Power Supplies (AVDD and VDDD)

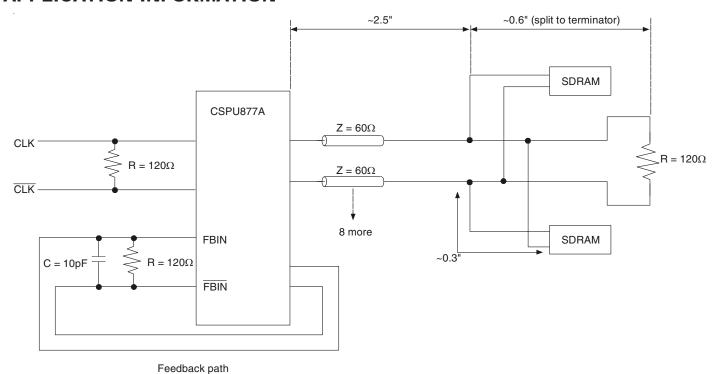

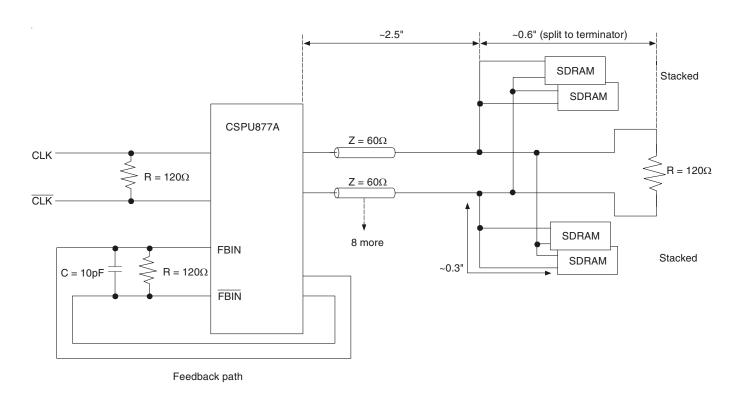

## **APPLICATION INFORMATION**

|                 |                            | Clock Loading on the PLL outputs (pF) |      |  |

|-----------------|----------------------------|---------------------------------------|------|--|

| Clock Structure | # of SDRAM Loads per Clock | Min.                                  | Max. |  |

| #1              | 2                          | 3                                     | 5    |  |

| #2              | 4                          | 6                                     | 10   |  |

# **APPLICATION INFORMATION**

Clock Structure 1

Clock Structure 2

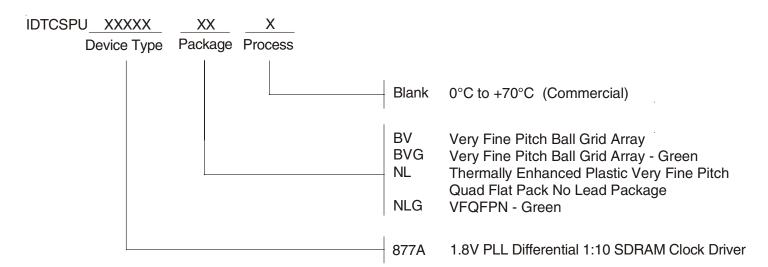

## **ORDERING INFORMATION**

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.