### **Bluetooth Low Energy 4.2 SoC**

# RENESAS

FINAL

# **General description**

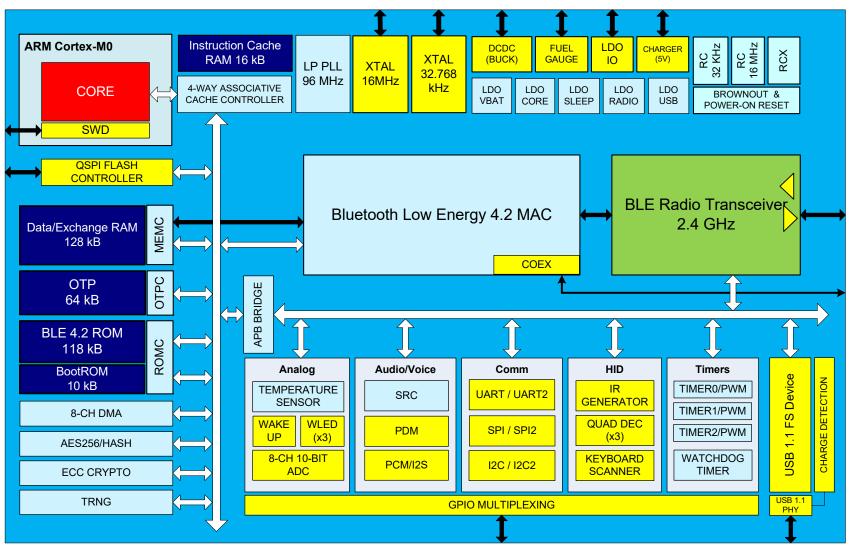

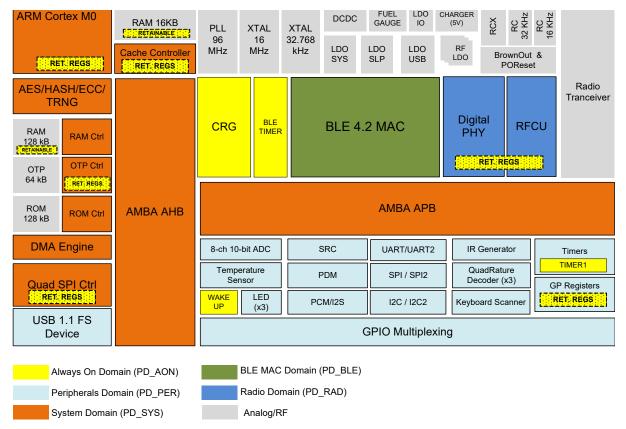

The DA14681 is a flexible System-on-Chip combining an application processor, memories, cryptography engine, power management unit, digital and analog peripherals and a Bluetooth Low Energy MAC engine and radio transceiver.

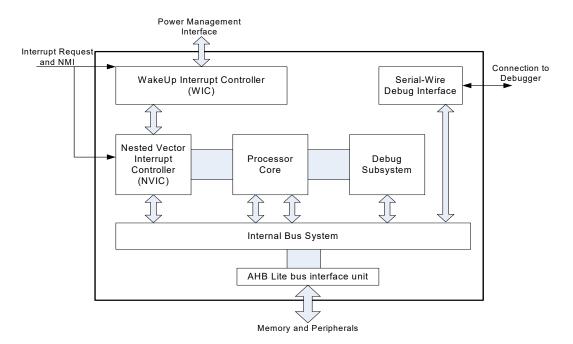

The DA14681 is based on an ARM<sup>®</sup> Cortex<sup>®</sup>-M0 CPU delivering up to 84 DMIPS and provides a flexible memory architecture, enabling code execution from embedded memory (RAM, ROM) or non-volatile memory (OTP or external Quad-SPI FLASH).

The advanced power management unit of the DA14681 enables it to run from primary and secondary batteries, as well as provide power to external devices. The on-chip charger and state-of-charge fuel gauge allow the DA14681 to natively charge rechargeable batteries over USB.

An on-chip PLL enables on-the-fly tuning of the system clock between 32 kHz and 96 MHz to meet high processing requirements. Several optimised sleep modes are available to reduce power dissipation when there is no activity.

### **Features**

- Complies to *Bluetooth v4.2*, ETSI EN 300 328 and EN 300 440 Class 2 (Europe), FCC CFR47 Part 15 (US) and ARIB STD-T66 (Japan)

- Flexible processing power

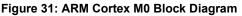

- 0 Hz up to 96 MHz 32-bit ARM Cortex-M0 with 4-way associative cache

- Three optimised power modes (Extended sleep, Deep sleep and Hibernation) reducing current to 1.4 uA

- Memories

- 64 kB One-Time-Programmable (OTP) memory

- 128 kB Data SRAM with retention capabilities

- 16 kB Cache SRAM with retention capabilities

- 128 kB ROM (including boot ROM and BLE stack)

- Power management

- Integrated Buck DC-DC converter (1.7 V 4.75 V)

- Three power supply pins for external devices

- Supports Li-Polymer, Li-Ion, coin, NiMH and alka-

#### line batteries

- Charger (up to 5.0 V) with programmable curves

- High accuracy state-of-charge fuel gauge

- Programmable threshold for brownout detection

- Digitally controlled oscillators and PLL

- 16 MHz crystal oscillator

- 16 MHz RC oscillator

- 32 kHz crystal and RC oscillator

- 11.7 kHz RCX oscillator

- Low power PLL up to 96 MHz

- Three general purpose timer/counters with PWM

- One 16-bit up/down timer/counter with PWM available in extended/deep sleep mode

- Application cryptographic engine with ECC, AES-256, SHA-1, SHA-256, SHA-512 and True Random Number Generator

- Digital interfaces

- 37 (AQFN) or 21 (WLCSP) general purpose I/Os with programmable voltage levels

- Quad-SPI FLASH interface

- Two UARTs, one with hardware flow control

- Two SPI+™ interfaces

- Two I2C bus interfaces at 100 kHz, 400 kHz

- Three-axes capable Quadrature Decoder

- PDM + HW decimator (2 mics or 2 speakers)

- I2S/PCM master/slave interface up to 8 channels

- Keyboard scanner with debouncing

- Infrared (IR) interface (PWM)

- USB 1.1 Full Speed (FS) device interface

- Analog interfaces

- 8-channel 10-bit ADC with averaging capability

- Three matched white LED drivers

- Temperature sensor

- Radio transceiver

- 2.4 GHz CMOS transceiver with integrated balun

- 50  $\Omega$  matched single wire antenna interface

- 0 dBm transmit output power

- -94 dBm receiver sensitivity (BLE)

- Supply current at VBAT1 (3 V): TX: 3.4 mA RX: 3.1 mA (with ideal DC-DC converter)

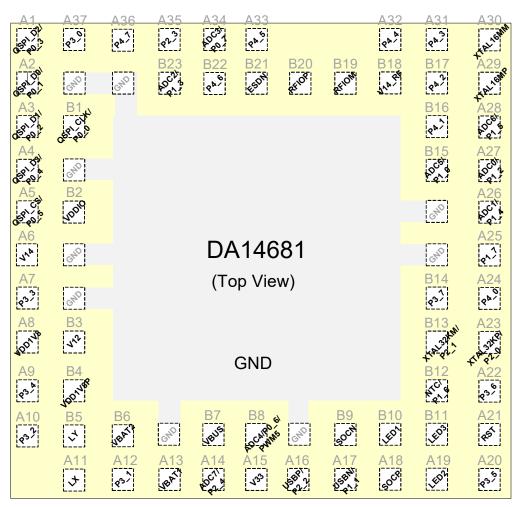

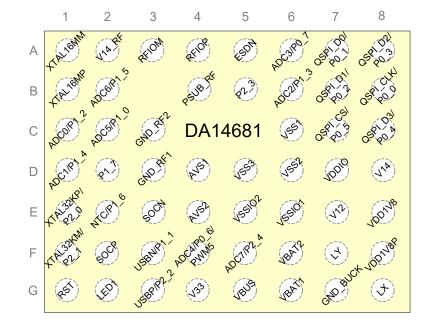

- Packages:

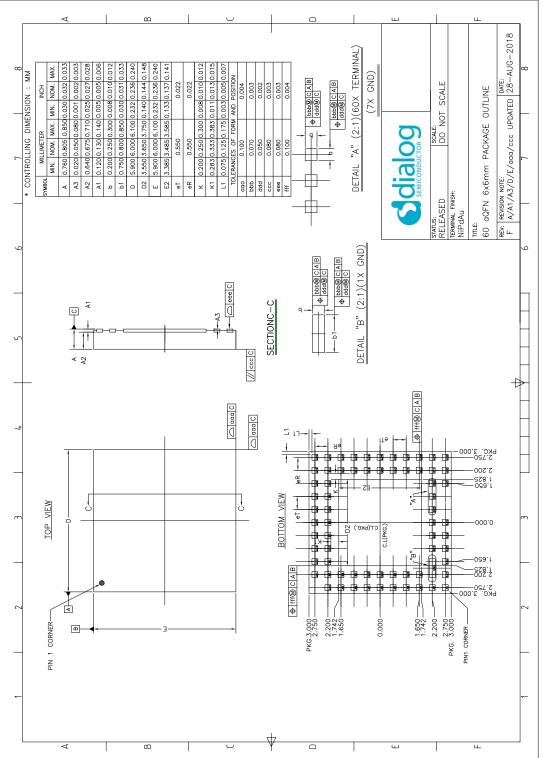

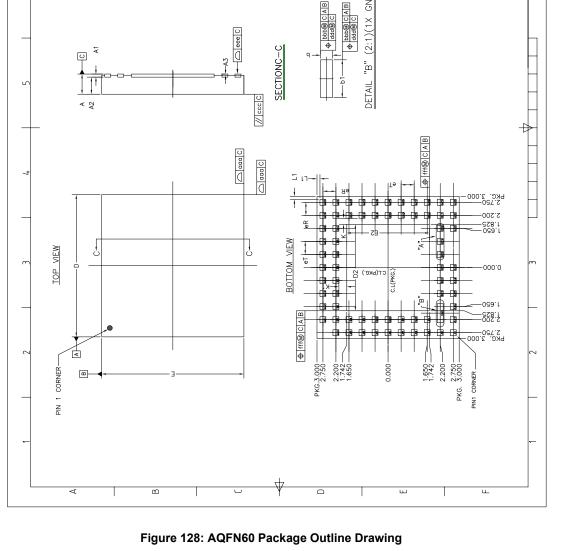

- AQFN with 60 pins, 6 mm x 6 mm

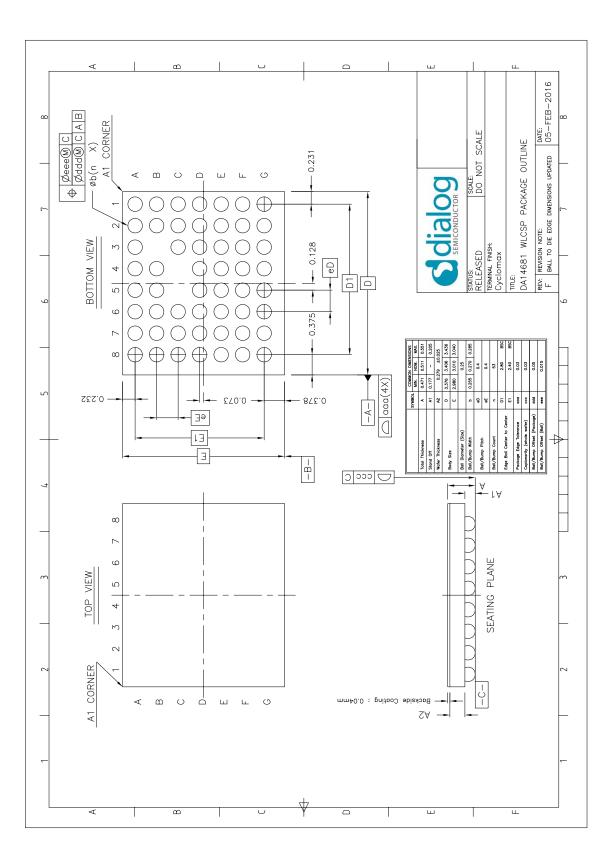

- WLCSP with 53 balls, 3.406 mm x 3.010 mm

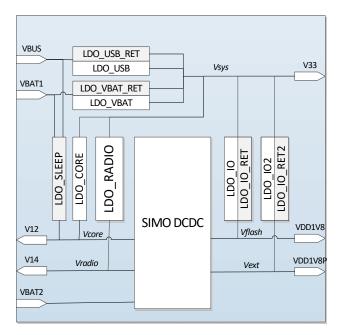

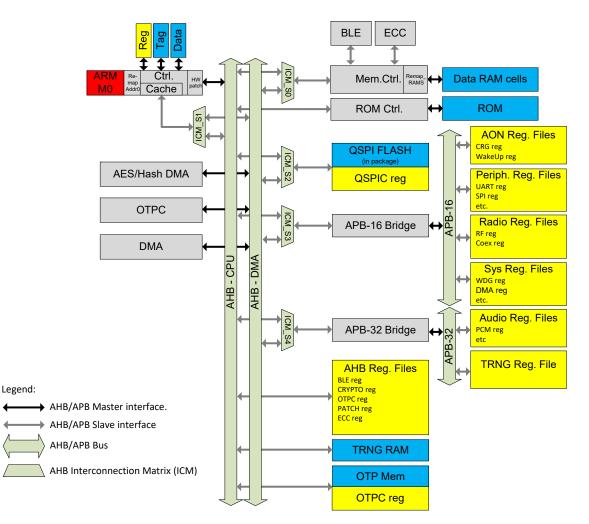

## System diagram

# Bluetooth Low Energy 4.2 SoC

| 1 Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 6                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 Package and pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 7                                                                                                                                                                                                        |

| 3 System overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19                                                                                                                                                                                                         |

| 3.1 INTERNAL BLOCKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                                                                                                                                                                         |

| 3.2 FUNCTIONAL MODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                                                                                                                                                                         |

| 3.3 SYSTEM CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20                                                                                                                                                                                                         |

| 3.4 SYSTEM STARTUP PROCEDURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23                                                                                                                                                                                                         |

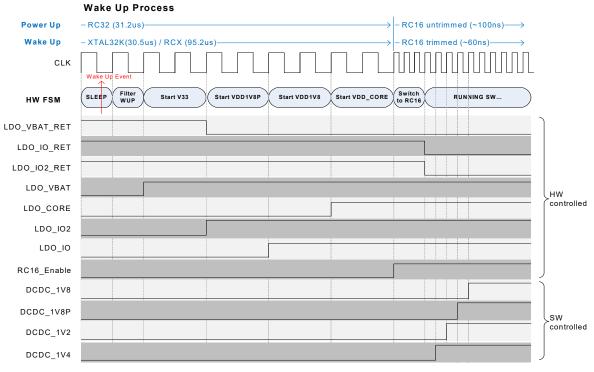

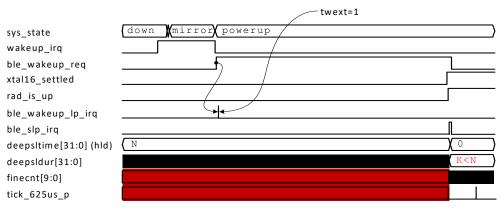

| 3.4.1 Power/Wakeup FSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24                                                                                                                                                                                                         |

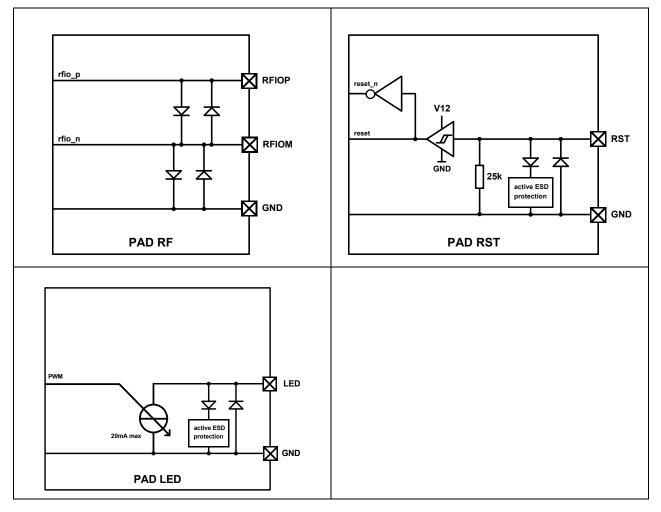

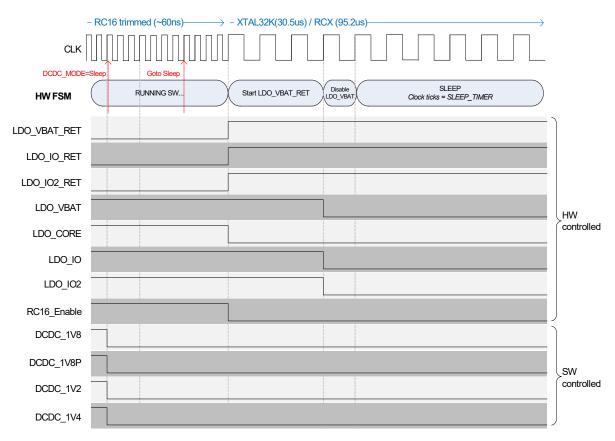

| 3.4.2 Goto Sleep FSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24                                                                                                                                                                                                         |

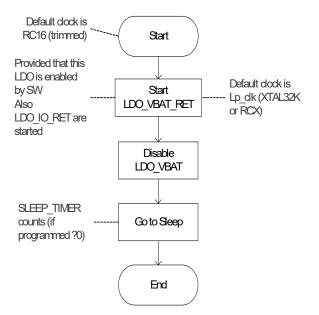

| 3.4.3 BootROM sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25                                                                                                                                                                                                         |

| 3.5 POWER CONTROL AND MODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27                                                                                                                                                                                                         |

| 3.5.1 System Power Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27                                                                                                                                                                                                         |

| 3.5.2 Power domains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28                                                                                                                                                                                                         |

| 3.5.3 Power modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29                                                                                                                                                                                                         |

| 4 Power management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31                                                                                                                                                                                                         |

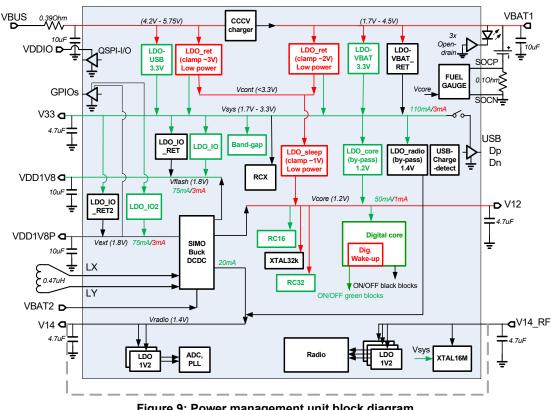

| 4.1 ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31                                                                                                                                                                                                         |

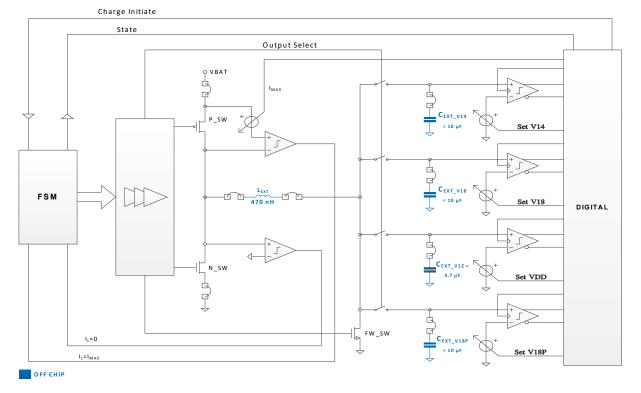

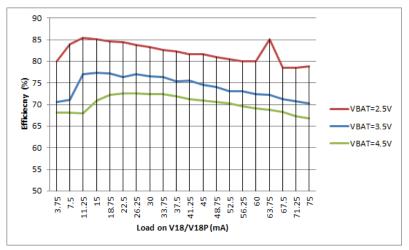

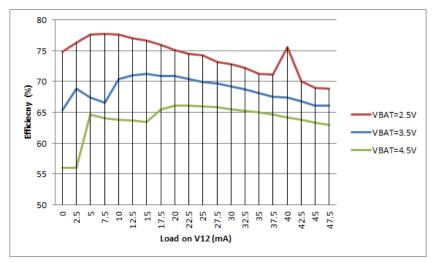

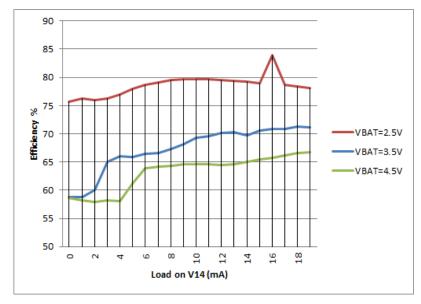

| 4.1.1 SIMO DC-DC converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32                                                                                                                                                                                                         |

| 4.1.2 LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 34                                                                                                                                                                                                         |

| 4.1.3 Switching from DC-DC to LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36                                                                                                                                                                                                         |

| 4.1.4 PMU configurations in Sleep modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37                                                                                                                                                                                                         |

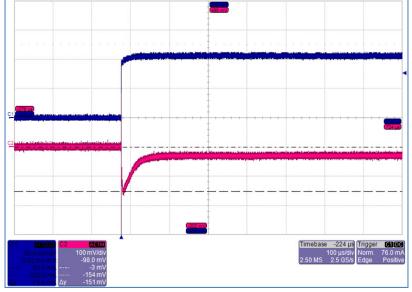

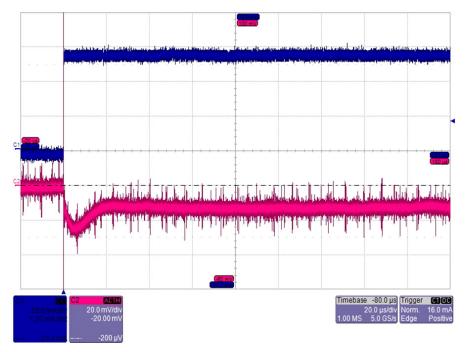

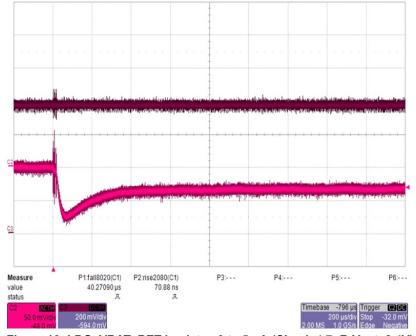

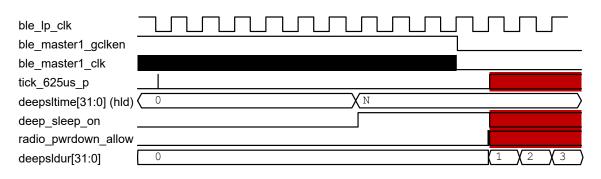

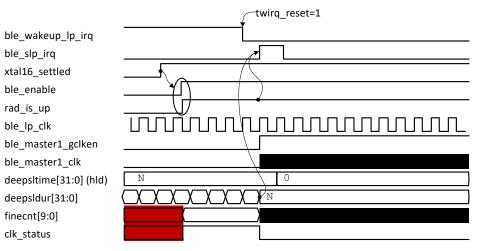

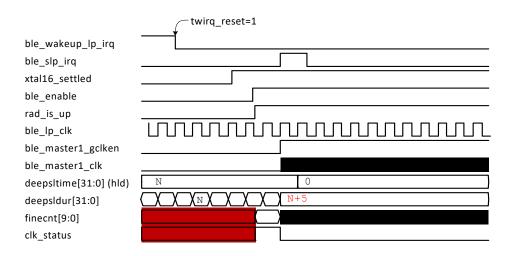

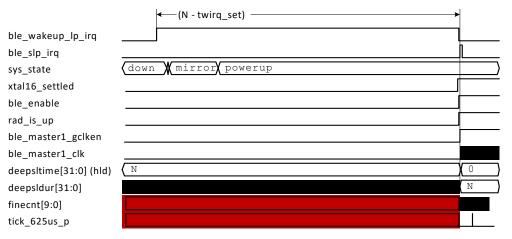

| 4.1.5 Wake/Power up - Sleep Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37                                                                                                                                                                                                         |

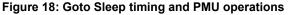

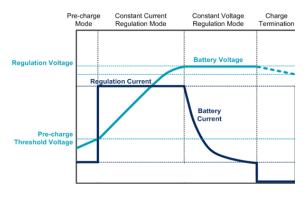

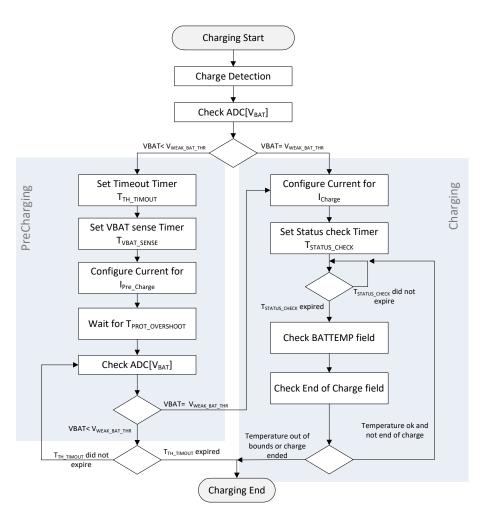

| 4.1.6 Charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                            |

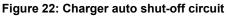

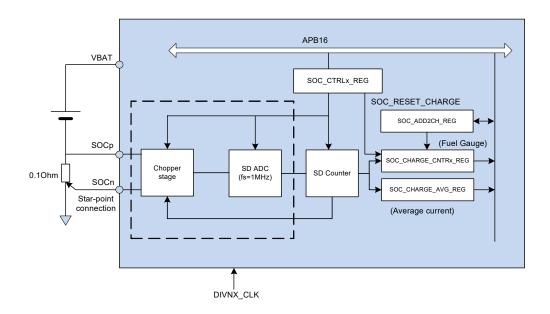

| 4.1.7 Fuel gauge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 42                                                                                                                                                                                                         |

| 4.1.7 Fuel gauge         4.1.8 USB charger detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44                                                                                                                                                                                                         |

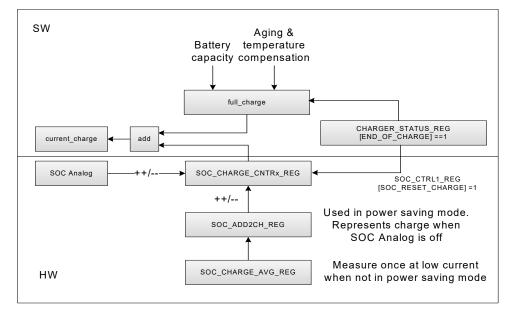

| 4.1.8 USB charger detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44<br><b>47</b>                                                                                                                                                                                            |

| 4.1.8 USB charger detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44<br><b>47</b><br>47                                                                                                                                                                                      |

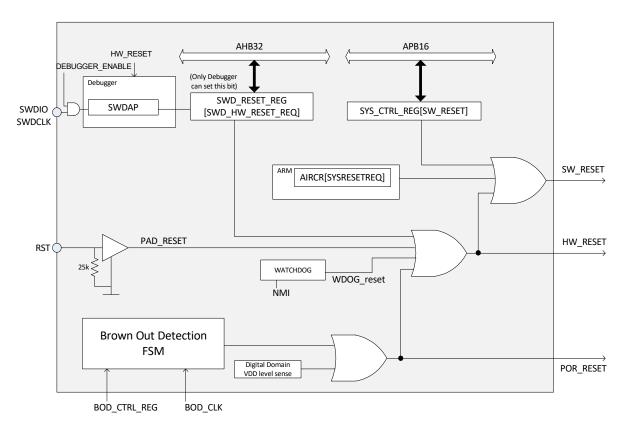

| 4.1.8 USB charger detection.         5 Reset.         5.1 POR, HW AND SW RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44<br><b>47</b><br>47<br>48                                                                                                                                                                                |

| 4.1.8 USB charger detection.         5 Reset.         5.1 POR, HW AND SW RESET         5.2 BROWN OUT DETECTION                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44<br>47<br>48<br>49                                                                                                                                                                                       |

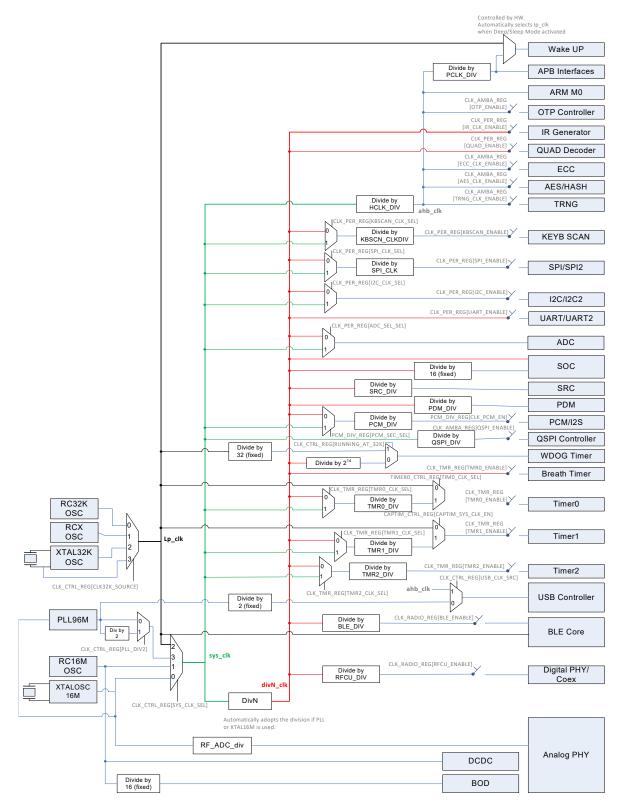

| 4.1.8 USB charger detection.         5 Reset.         5.1 POR, HW AND SW RESET         5.2 BROWN OUT DETECTION         6 Clock generation.                                                                                                                                                                                                                                                                                                                                                                                                                  | 44<br>47<br>48<br><b>49</b>                                                                                                                                                                                |

| 4.1.8 USB charger detection.         5 Reset.         5.1 POR, HW AND SW RESET         5.2 BROWN OUT DETECTION         6 Clock generation.         6.1 CLOCK TREE                                                                                                                                                                                                                                                                                                                                                                                           | 44<br>47<br>48<br><b>49</b><br>50                                                                                                                                                                          |

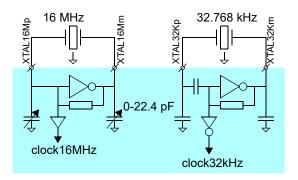

| 4.1.8 USB charger detection.         5 Reset.         5.1 POR, HW AND SW RESET         5.2 BROWN OUT DETECTION         6 Clock generation.         6.1 CLOCK TREE         6.2 CRYSTAL OSCILLATORS                                                                                                                                                                                                                                                                                                                                                           | 44<br>47<br>48<br><b>49</b><br>50<br>50                                                                                                                                                                    |

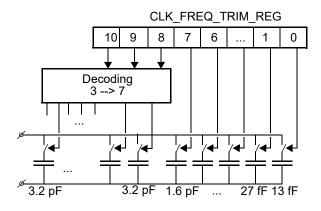

| 4.1.8 USB charger detection.         5 Reset.         5.1 POR, HW AND SW RESET         5.2 BROWN OUT DETECTION         6 Clock generation.         6.1 CLOCK TREE         6.2 CRYSTAL OSCILLATORS         6.2.1 Frequency control (16 MHz crystal).         6.2.2 Automated trimming and settling notification                                                                                                                                                                                                                                              | 44<br>47<br>48<br>49<br>50<br>50<br>50                                                                                                                                                                     |

| 4.1.8 USB charger detection.         5 Reset.         5.1 POR, HW AND SW RESET         5.2 BROWN OUT DETECTION         6 Clock generation.         6.1 CLOCK TREE         6.2 CRYSTAL OSCILLATORS         6.2.1 Frequency control (16 MHz crystal).         6.2.2 Automated trimming and settling notificat         50                                                                                                                                                                                                                                      | 44<br>47<br>48<br>49<br>50<br>50<br>tion<br>51                                                                                                                                                             |

| <ul> <li>4.1.8 USB charger detection.</li> <li>5 Reset.</li> <li>5.1 POR, HW AND SW RESET</li> <li>5.2 BROWN OUT DETECTION</li> <li>6 Clock generation.</li> <li>6.1 CLOCK TREE</li> <li>6.2 CRYSTAL OSCILLATORS</li> <li>6.2.1 Frequency control (16 MHz crystal)</li> <li>6.2.2 Automated trimming and settling notificat 50</li> <li>6.3 RC OSCILLATORS.</li> </ul>                                                                                                                                                                                      | 44<br>47<br>48<br>49<br>50<br>50<br>tion<br>51<br>52                                                                                                                                                       |

| <ul> <li>4.1.8 USB charger detection.</li> <li>5 Reset.</li> <li>5.1 POR, HW AND SW RESET</li> <li>5.2 BROWN OUT DETECTION</li> <li>6 Clock generation.</li> <li>6.1 CLOCK TREE</li> <li>6.2 CRYSTAL OSCILLATORS</li> <li>6.2.1 Frequency control (16 MHz crystal).</li> <li>6.2.2 Automated trimming and settling notificat 50</li> <li>6.3 RC OSCILLATORS.</li> <li>6.3.1 Frequency calibration</li> </ul>                                                                                                                                                | <ul> <li>44</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>50</li> <li>51</li> <li>52</li> <li>52</li> </ul>                                                                         |

| <ul> <li>4.1.8 USB charger detection.</li> <li>5 Reset.</li> <li>5.1 POR, HW AND SW RESET</li> <li>5.2 BROWN OUT DETECTION</li> <li>6 Clock generation.</li> <li>6.1 CLOCK TREE</li> <li>6.2 CRYSTAL OSCILLATORS</li> <li>6.2.1 Frequency control (16 MHz crystal).</li> <li>6.2.2 Automated trimming and settling notificat 50</li> <li>6.3 RC OSCILLATORS</li> <li>6.3.1 Frequency calibration</li> <li>6.4 PLL</li> </ul>                                                                                                                                | <ul> <li>44</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>50</li> <li>51</li> <li>52</li> <li>52</li> <li>53</li> </ul>                                                             |

| 4.1.8 USB charger detection.         5 Reset.         5.1 POR, HW AND SW RESET         5.2 BROWN OUT DETECTION         6 Clock generation.         6.1 CLOCK TREE         6.2 CRYSTAL OSCILLATORS         6.2.1 Frequency control (16 MHz crystal)         6.2.2 Automated trimming and settling notificat         50         6.3 RC OSCILLATORS         6.4 PLL         7 ARM Cortex M0                                                                                                                                                                    | <ul> <li>44</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>50</li> <li>51</li> <li>52</li> <li>52</li> <li>53</li> <li>54</li> </ul>                                                 |

| <ul> <li>4.1.8 USB charger detection.</li> <li>5 Reset.</li> <li>5.1 POR, HW AND SW RESET</li> <li>5.2 BROWN OUT DETECTION</li> <li>6 Clock generation.</li> <li>6.1 CLOCK TREE</li> <li>6.2 CRYSTAL OSCILLATORS</li> <li>6.2.1 Frequency control (16 MHz crystal).</li> <li>6.2.2 Automated trimming and settling notificat 50</li> <li>6.3 RC OSCILLATORS.</li> <li>6.3.1 Frequency calibration</li> <li>6.4 PLL</li> <li>7 ARM Cortex M0</li> <li>7.1 SYSTEM TIMER (SYSTICK).</li> </ul>                                                                 | <ul> <li>44</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>50</li> <li>51</li> <li>52</li> <li>52</li> <li>53</li> <li>54</li> <li>54</li> </ul>                                     |

| <ul> <li>4.1.8 USB charger detection.</li> <li>5 Reset.</li> <li>5.1 POR, HW AND SW RESET</li> <li>5.2 BROWN OUT DETECTION</li> <li>6 Clock generation.</li> <li>6.1 CLOCK TREE</li> <li>6.2 CRYSTAL OSCILLATORS</li> <li>6.2.1 Frequency control (16 MHz crystal).</li> <li>6.2.2 Automated trimming and settling notificat</li> <li>50</li> <li>6.3 RC OSCILLATORS</li> <li>6.3.1 Frequency calibration</li> <li>6.4 PLL</li> <li>7 ARM Cortex M0</li> <li>7.1 SYSTEM TIMER (SYSTICK).</li> <li>7.2 WAKEUP INTERRUPT CONTROLLER</li> </ul>                | <ul> <li>44</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>50</li> <li>51</li> <li>52</li> <li>52</li> <li>53</li> <li>54</li> <li>54</li> <li>54</li> </ul>                         |

| <ul> <li>4.1.8 USB charger detection.</li> <li>5 Reset.</li> <li>5.1 POR, HW AND SW RESET</li> <li>5.2 BROWN OUT DETECTION</li> <li>6 Clock generation.</li> <li>6.1 CLOCK TREE</li> <li>6.2 CRYSTAL OSCILLATORS</li> <li>6.2.1 Frequency control (16 MHz crystal)</li> <li>6.2.2 Automated trimming and settling notificat 50</li> <li>6.3 RC OSCILLATORS.</li> <li>6.3.1 Frequency calibration</li> <li>6.4 PLL</li> <li>7 ARM Cortex M0</li> <li>7.1 SYSTEM TIMER (SYSTICK).</li> <li>7.2 WAKEUP INTERRUPT CONTROLLER</li> <li>7.3 REFERENCE</li> </ul>  | <ul> <li>44</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>50</li> <li>51</li> <li>52</li> <li>52</li> <li>53</li> <li>54</li> <li>54</li> <li>54</li> <li>55</li> </ul>             |

| <ul> <li>4.1.8 USB charger detection.</li> <li>5 Reset.</li> <li>5.1 POR, HW AND SW RESET</li> <li>5.2 BROWN OUT DETECTION</li> <li>6 Clock generation.</li> <li>6.1 CLOCK TREE</li> <li>6.2 CRYSTAL OSCILLATORS</li> <li>6.2.1 Frequency control (16 MHz crystal)</li> <li>6.2.2 Automated trimming and settling notificat 50</li> <li>6.3 RC OSCILLATORS.</li> <li>6.3.1 Frequency calibration</li> <li>6.4 PLL</li> <li>7 ARM Cortex M0</li> <li>7.1 SYSTEM TIMER (SYSTICK).</li> <li>7.2 WAKEUP INTERRUPT CONTROLLER</li> <li>7.4 INTERRUPTS</li> </ul> | <ul> <li>44</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>50</li> <li>51</li> <li>52</li> <li>52</li> <li>53</li> <li>54</li> <li>54</li> <li>54</li> <li>55</li> <li>57</li> </ul> |

# RENESAS

# FINAL

|     | 8.2 RUNTIME RECONFIGURATION           |    |

|-----|---------------------------------------|----|

|     | 8.2.1 Cache Line reconfiguration      |    |

|     | 8.2.2 TAG memory word                 |    |

|     | 8.2.3 Associativity reconfiguration   |    |

|     | 8.3 2 AND 4 WAY REPLACEMENT STRATEGY. |    |

|     | 8.4 CACHE RESETS.                     |    |

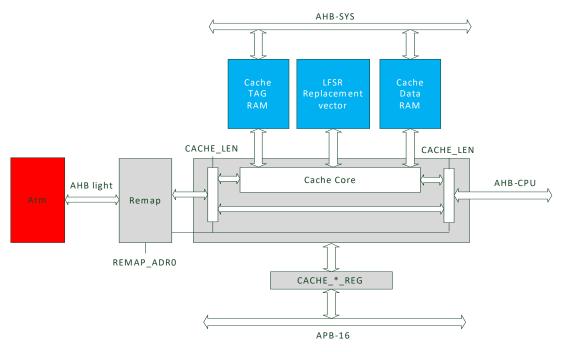

|     | 8.5 CACHE MISS RATE MONITOR           |    |

|     | 8.6 CACHE MISS LATENCY AND POWER      | 59 |

| 9 A | MBA Bus                               | 61 |

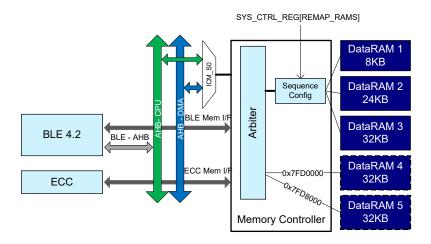

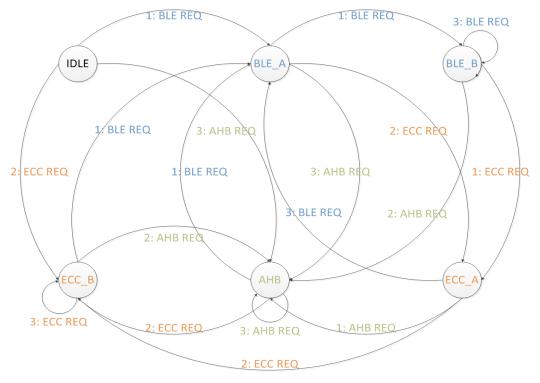

| 10  | Memory Controller                     | 63 |

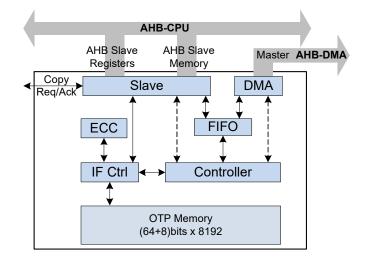

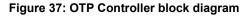

| 11  | OTP Controller                        | 65 |

|     | 11.1 OPERATING MODES                  | 65 |

|     | 11.2 AHB MASTER INTERFACE             | 66 |

|     | 11.3 AHB SLAVE INTERFACES             | 66 |

|     | 11.4 ERROR CORRECTING CODE (ECC)      | 66 |

|     | 11.5 BUILD-IN SELF REPAIR (BISR)      |    |

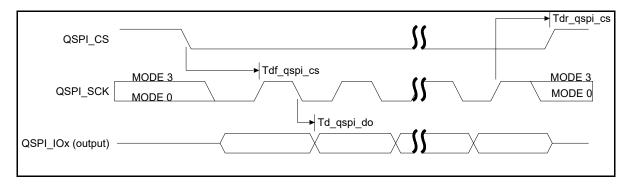

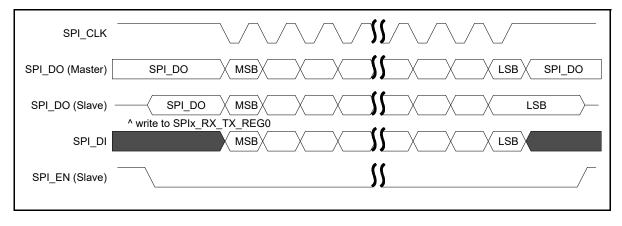

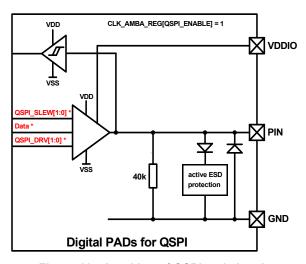

| 12  | Quad SPI Controller                   | 67 |

|     | 12.1 ARCHITECTURE                     |    |

|     | 12.1.1 Interface                      |    |

|     | 12.1.2 Initialization FSM             |    |

|     | 12.1.3 SPI modes                      |    |

|     | 12.1.4 Access modes                   |    |

|     | 12.1.5 Endianess                      |    |

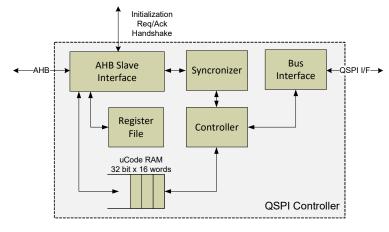

|     | 12.1.6 Erase Suspend/Resume           |    |

|     | 12.1.7 QSPI FLASH Programming         |    |

|     | 12.2 PROGRAMMING                      |    |

|     | 12.2.1 Auto Mode                      |    |

|     | 12.2.2 Manual Mode                    |    |

|     | 12.2.3 Clock selection                |    |

|     | 12.2.4 Received data                  |    |

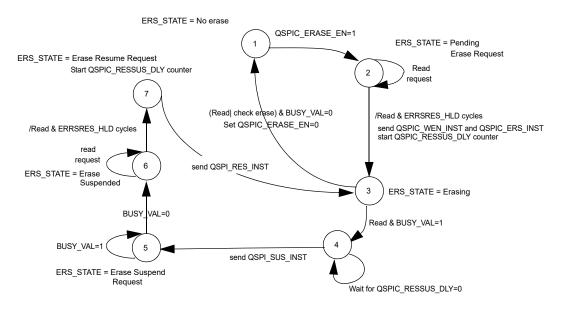

|     | 12.3 TIMING                           |    |

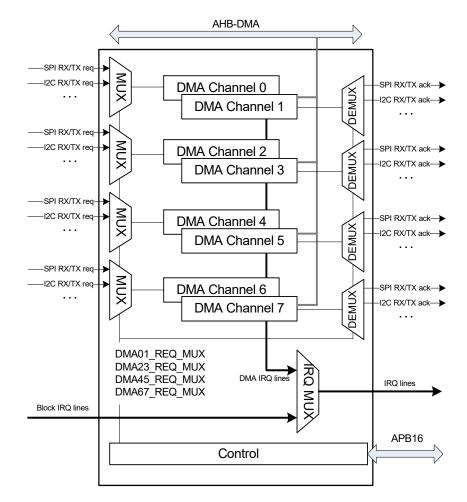

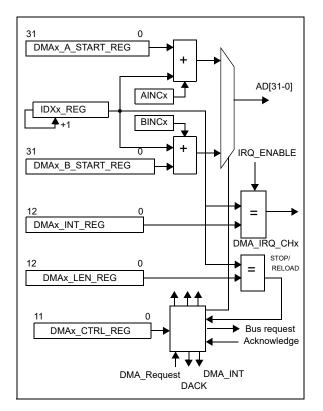

| 13  | DMA Controller                        | 73 |

|     | 13.1 DMA PERIPHERALS                  | 74 |

|     | 13.2 INPUT/OUTPUT MULTIPLEXER         |    |

|     | 13.3 DMA CHANNEL OPERATION            |    |

|     | 13.4 DMA ARBITRATION                  |    |

|     | 13.5 FREEZING DMA CHANNELS            |    |

|     |                                       |    |

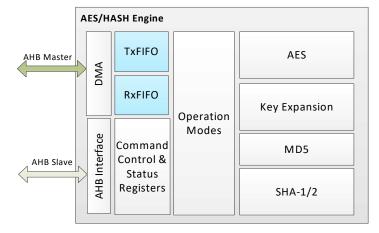

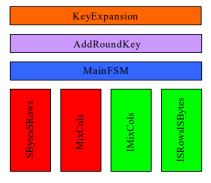

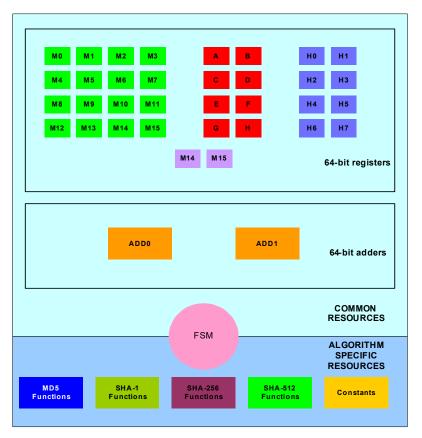

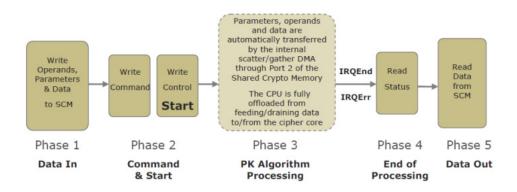

| 14  | AES/Hash Engine                       |    |

|     | 14.1 DESCRIPTION                      |    |

|     | 14.2 ARCHITECTURE                     |    |

|     | 14.2.1 AES/HASH engine                |    |

|     | 14.2.2 AES                            |    |

|     | 14.2.3 Modes                          |    |

|     | 14.2.4 HASH                           | 78 |

# Bluetooth Low Energy 4.2 SoC

| 14.3 PROGRAMMING                                                                      |          |

|---------------------------------------------------------------------------------------|----------|

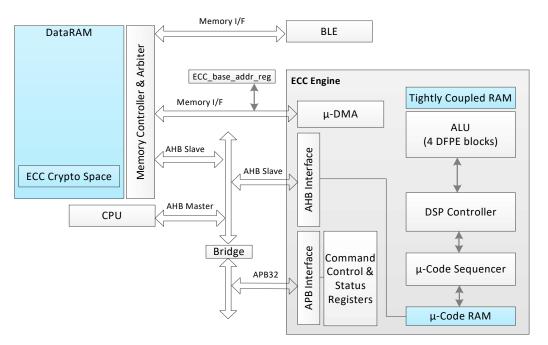

| 15 ECC Engine 82                                                                      |          |

| 15.1 ARCHITECTURE                                                                     |          |

| 15.1.1 Supported curves                                                               |          |

| 15.1.2 Supported high level algorithms 83                                             |          |

| 15.2 PROGRAMMING                                                                      |          |

| 15.2.1 Example: ECDSA signature generation 83                                         |          |

|                                                                                       | 23 U     |

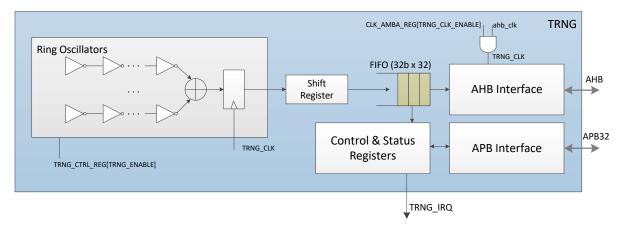

| 16 True Random Number Generator (TRNG) 86                                             | 2        |

| 16.1 ARCHITECTURE 86                                                                  | 2        |

| 16.2 PROGRAMMING 86                                                                   | 2        |

| 16.2.1 Latency 86                                                                     | 2        |

| 17 Temperature Sensor 87                                                              | 2        |

| 17.1 PROGRAMMING 87                                                                   | 2        |

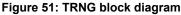

| 18 Wakeup Timer 88                                                                    | 2        |

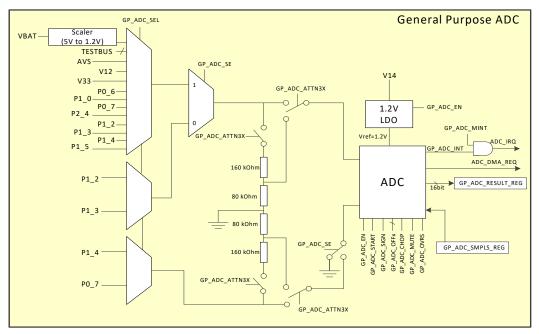

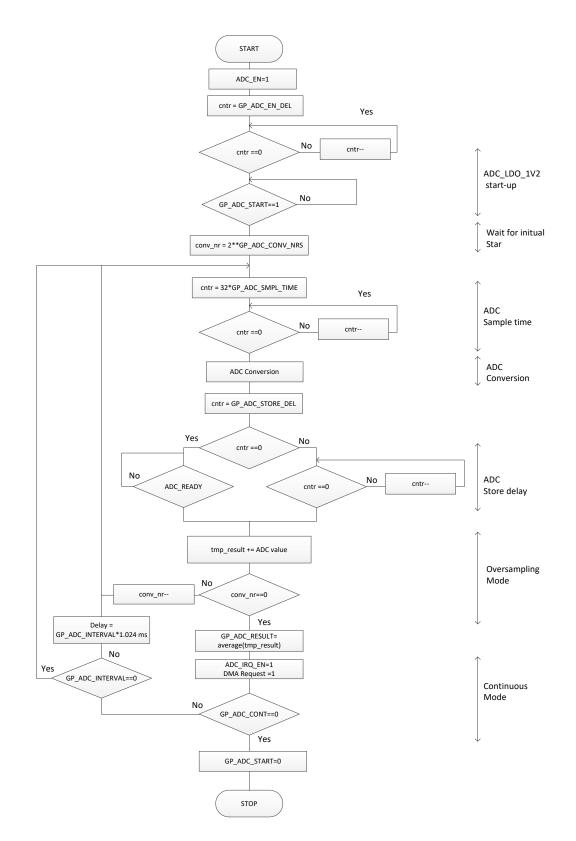

| 19 General purpose ADC                                                                | 24 S     |

|                                                                                       | 2        |

| 19.1 ARCHITECTURE                                                                     | 2        |

| 19.2 INPUT CHANNELS AND INPUT SCALE 91                                                | 25 12    |

| 19.3 STARTING THE ADC                                                                 |          |

| 19.4 ADC CONVERSION MODES                                                             | 2        |

| 19.4.1 Manual Mode                                                                    |          |

| 19.4.2 Continuous Mode                                                                | 2        |

| 19.5 NON-IDEAL EFFECTS                                                                |          |

| 19.6         SAMPLING TIME (SMPL_TIME)                                                |          |

|                                                                                       | 2        |

| 19.8         CHOPPING         93           19.9         OFFSET CALIBRATION         93 |          |

|                                                                                       |          |

| 19.10 ZERO-SCALE ADJUSTMENT                                                           |          |

| 19.11 COMMON MODE ADJUSTMENT                                                          | 2        |

| 19.12 INPUT IMPEDANCE, INDUCTANCE AND IN-                                             | 2        |

| PUT SETTLING                                                                          | 2        |

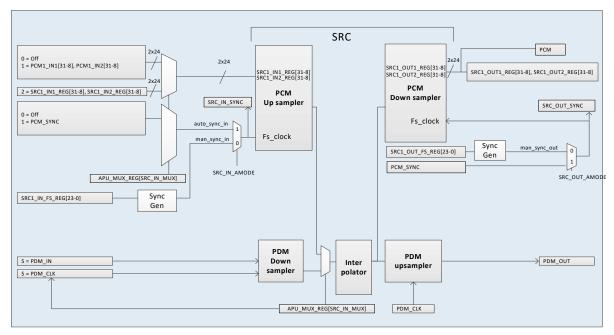

| 20 Sample rate Converter (SRC)                                                        |          |

| 20.1 ARCHITECTURE                                                                     |          |

| 20.1.1 I/O channels                                                                   |          |

| 20.1.2 I/O multiplexers                                                               | 26 Ir    |

| 20.1.3 Input and Output Sample rate conversion                                        | 2        |

| 96                                                                                    | 2        |

| 20.1.4       SRC conversion modes of operation                                        | 27 Q     |

| 20.1.6 Interrupts                                                                     | 2        |

| 20.1.7 SRC use cases                                                                  | 2        |

|                                                                                       | 28 K     |

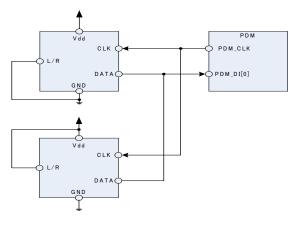

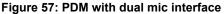

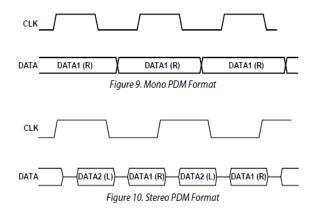

| 21 PDM interface                                                                      | 2        |

| 22 PCM Controller                                                                     | 2        |

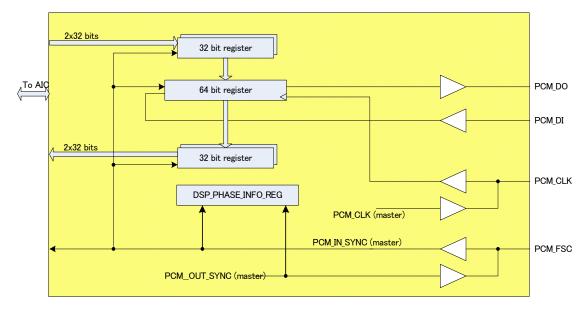

| 22.1 ARCHITECTURE                                                                     |          |

| Datasheet Revi                                                                        | sion 3.2 |

# RENESAS

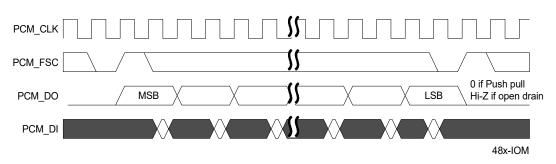

|    | 22.1.1 Interface Signals                    | 98 |

|----|---------------------------------------------|----|

|    | 22.1.2 Channel ACCESS                       | 98 |

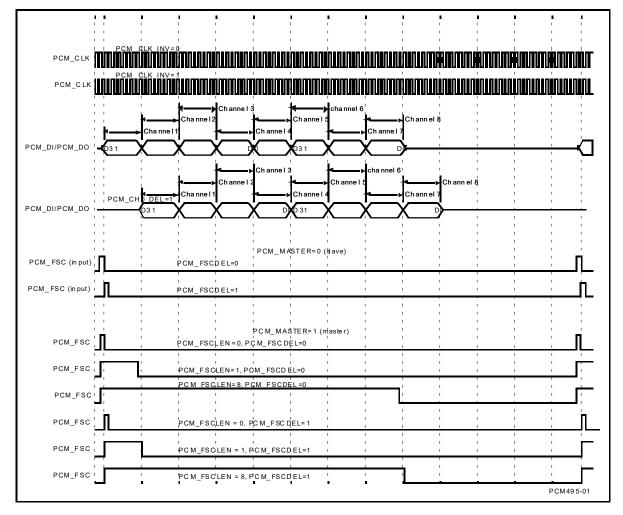

|    | 22.1.3 Channel delay                        | 99 |

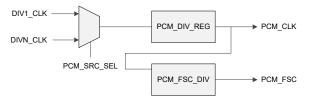

|    | 22.1.4 Clock generation                     | 99 |

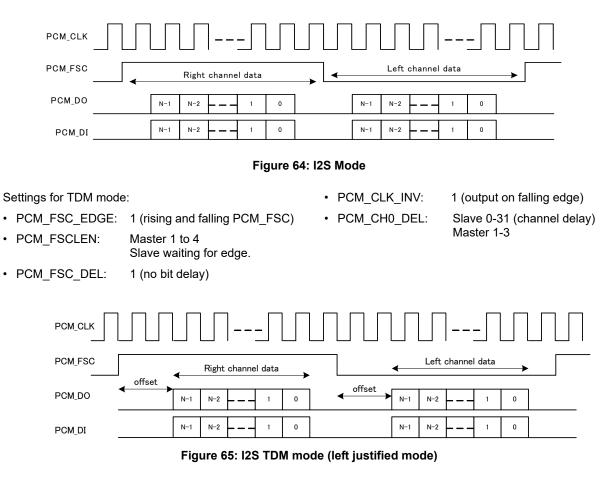

|    | 22.1.5 DATA FORMATS 1                       | 00 |

|    | 22.1.6 IOM mode 1                           | 01 |

|    | 22.1.7 External synchronisation 1           | 01 |

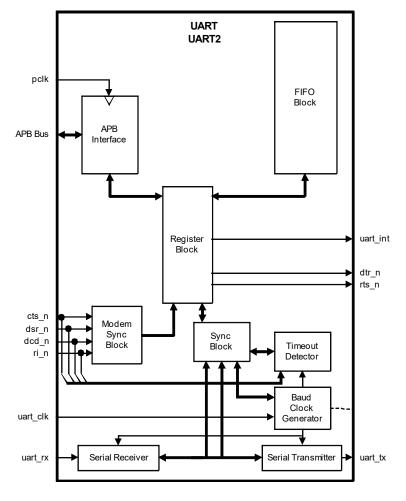

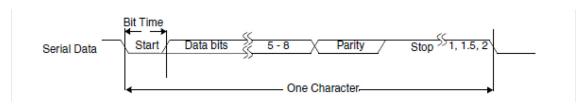

| 23 | UART 1                                      | 03 |

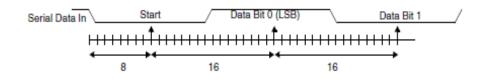

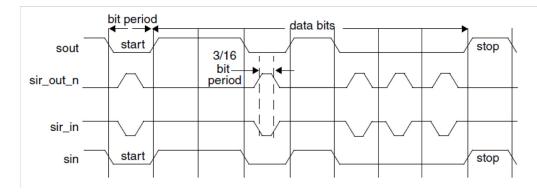

|    | 23.1 UART (RS232) SERIAL PROTOCOL 1         | 04 |

|    |                                             | 05 |

|    |                                             | 05 |

|    |                                             | 06 |

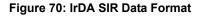

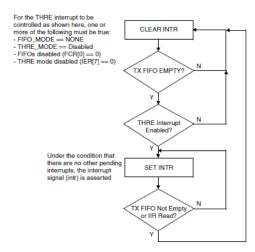

|    | 23.5 PROGRAMMABLE THRE INTERRUPT 1          | 06 |

|    | 23.6 SHADOW REGISTERS 1                     | 08 |

|    | 23.7 DIRECT TEST MODE                       | 08 |

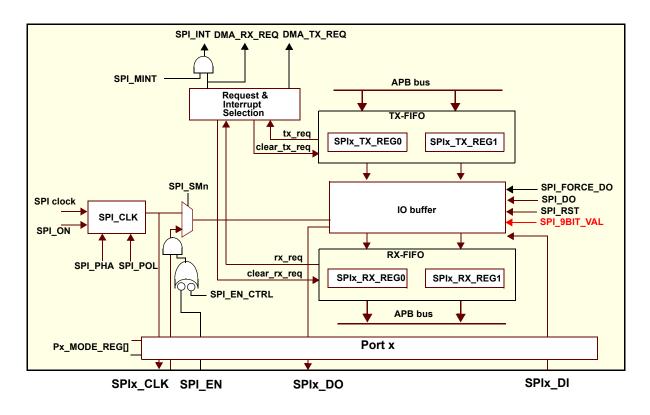

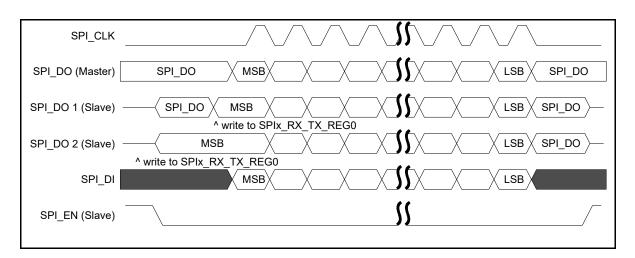

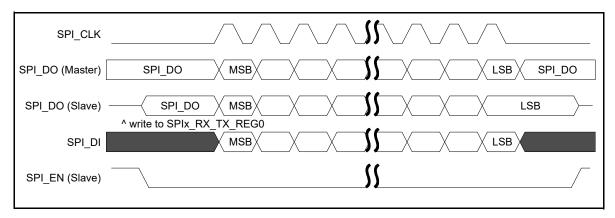

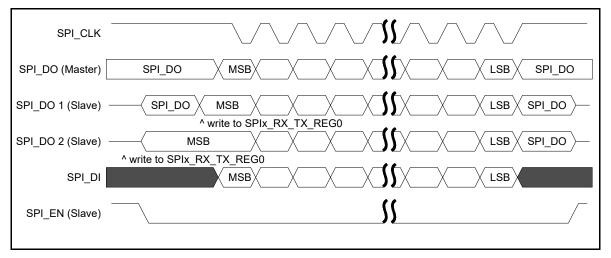

| 24 | SPI+ Interface                              | ٥٥ |

| 24 | 24.1 OPERATION WITHOUT FIFOS                |    |

|    | 24.1 OPERATION WITHOUT FIFUS                |    |

|    | 24.2 9 BITS MODE                            | 10 |

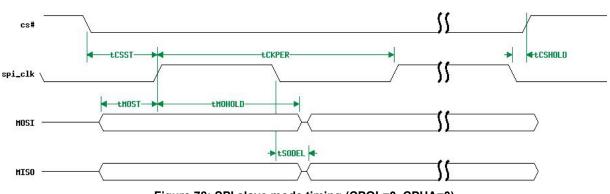

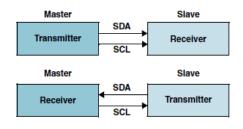

| 25 | I2C 1                                       | 13 |

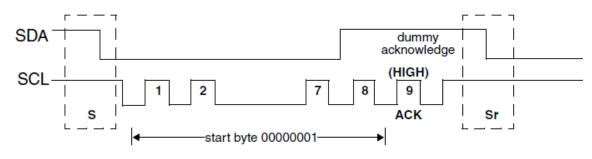

|    | 25.1 I2C BUS TERMS1                         |    |

|    | 25.1.1 Bus Transfer Terms1                  | 14 |

|    | 25.2 I2C BEHAVIOUR1                         | 14 |

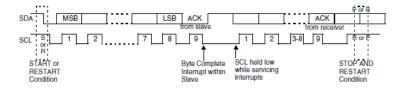

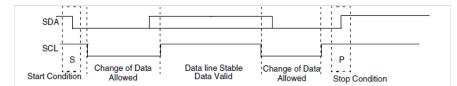

|    | 25.2.1 START and STOP Generation 1          |    |

|    | 25.2.2 Combined Formats1                    | 15 |

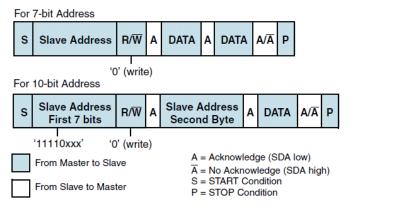

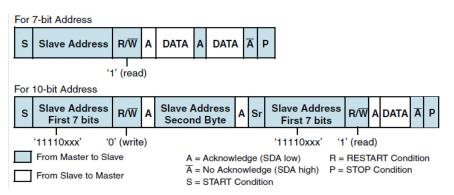

|    | 25.3 I2C PROTOCOLS                          |    |

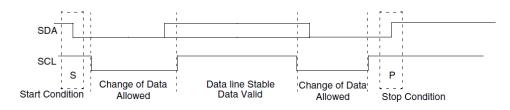

|    | 25.3.1 START and STOP Conditions 1          |    |

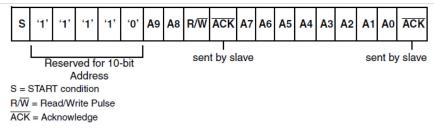

|    | 25.3.2 Addressing Slave Protocol            |    |

|    | 25.3.3 Transmitting and Receiving Protocol1 |    |

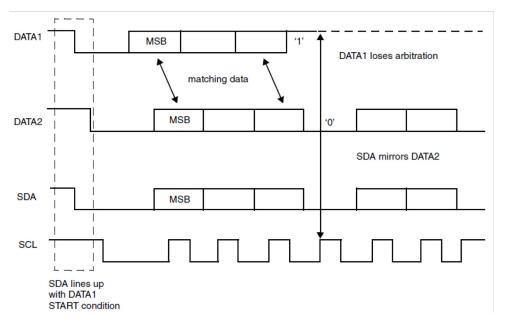

|    | 25.4 MULTIPLE MASTER ARBITRATION1           |    |

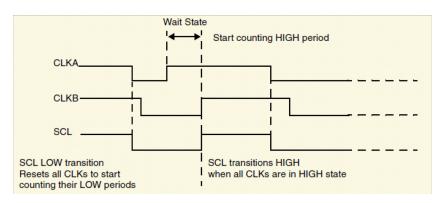

|    | 25.5 CLOCK SYNCHRONIZATION                  |    |

|    |                                             | 20 |

|    | 25.6.1 Slave Mode Operation                 |    |

|    | 25.6.2 Master Mode Operation                |    |

|    | 25.6.3 Disabling I2C controller 1           | 22 |

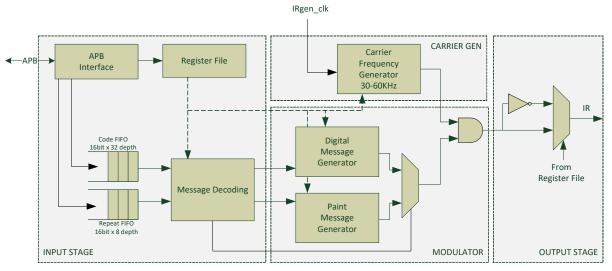

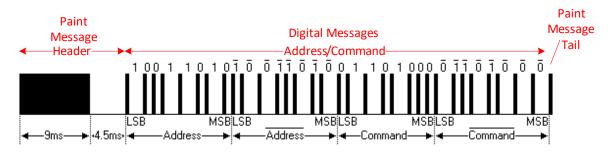

| 26 | InfraRed Generator 1                        | 23 |

|    | 26.1 ARCHITECTURE 1                         | 23 |

|    | 26.2 PROGRAMMING 1                          | 24 |

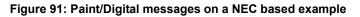

| 27 | Quadrature Decoder 1                        | 25 |

|    | 27.1 ARCHITECTURE 1                         | 25 |

|    | 27.2 PROGRAMMING 1                          | 25 |

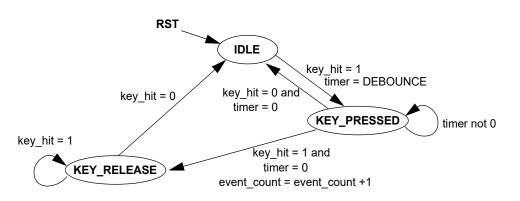

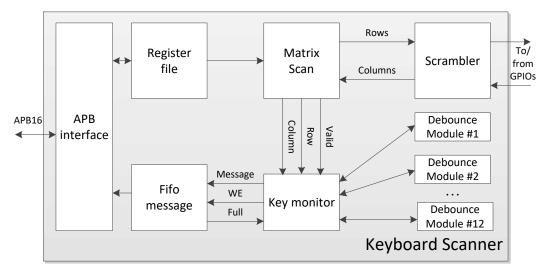

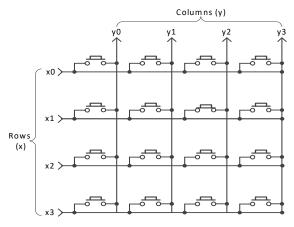

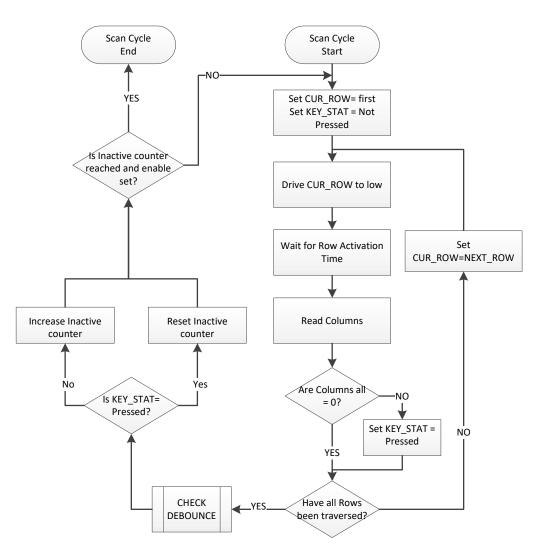

| 28 | Keyboard Scanner 1                          | 26 |

|    |                                             | 26 |

|    | 28.2 PROGRAMMING                            |    |

|    |                                             | 2  |

13-Jan-2022

# Bluetooth Low Energy 4.2 SoC

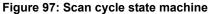

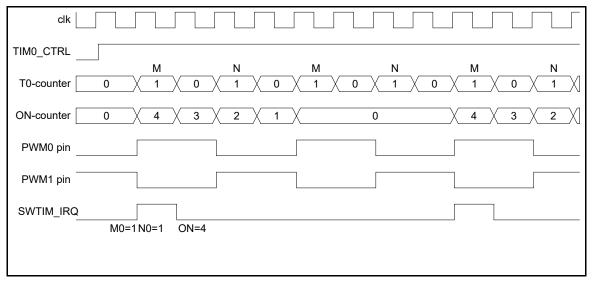

| 29.1 TIMER0 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

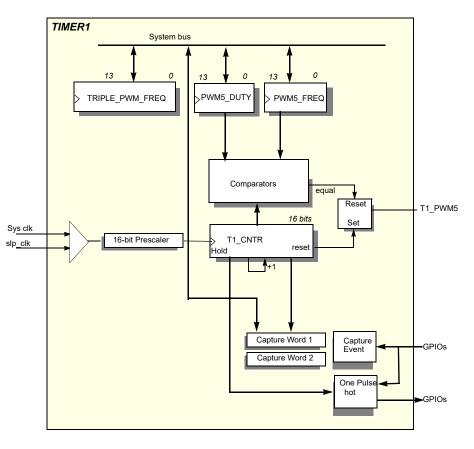

| 29.2 TIMER1 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

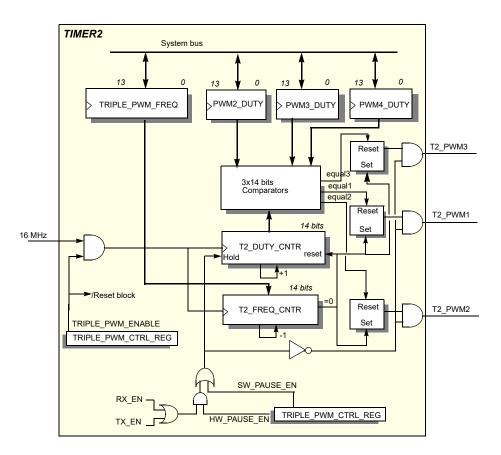

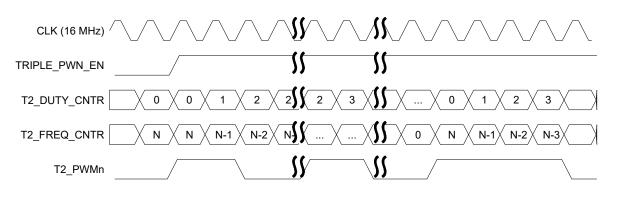

| 29.3 TIMER2 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 29.4 BRTH_TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

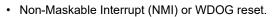

| 30 Watchdog Timer 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

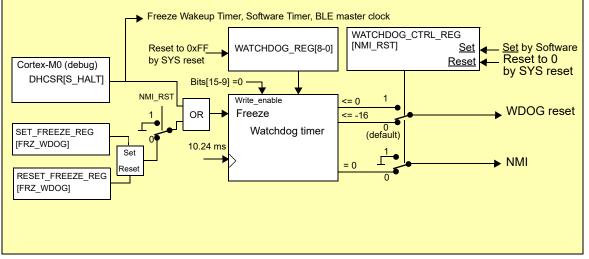

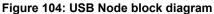

| 31 USB Interface 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 31.1 SERIAL INTERFACE ENGINE 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

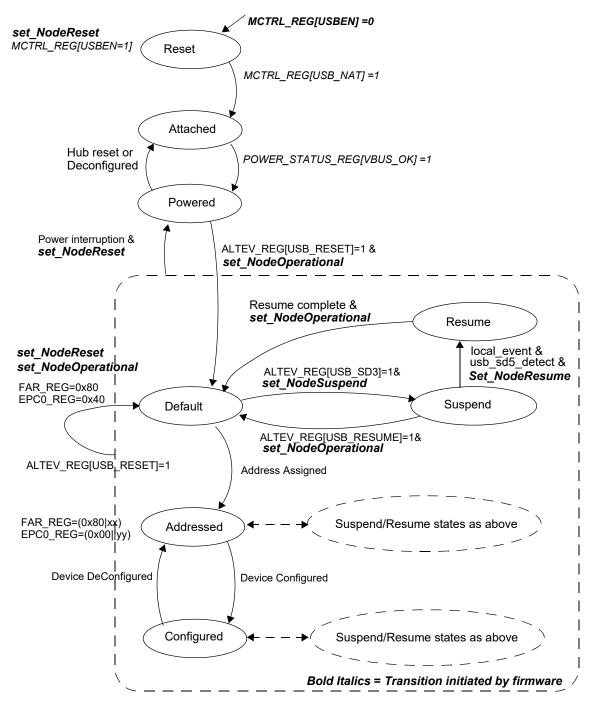

| 31.2 ENDPOINT PIPE CONTROLLER (EPC) 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

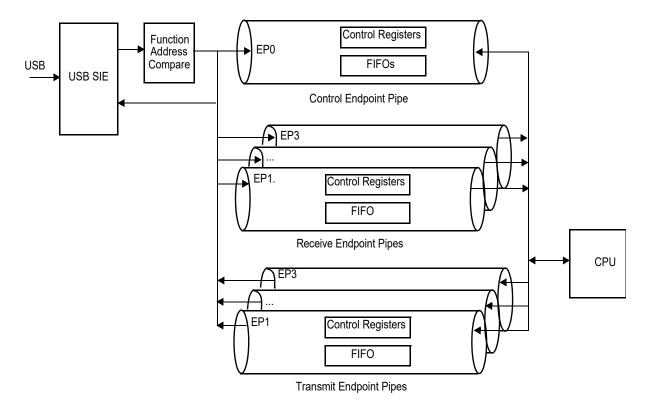

| 31.3 FUNCTIONAL STATES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 31.3.1 Line Condition Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 31.4 FUNCTIONAL STATE DIAGRAM 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

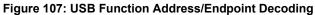

| 31.5 ADDRESS DETECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 31.6 TRANSMIT AND RECEIVE ENDPOINT FIFOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

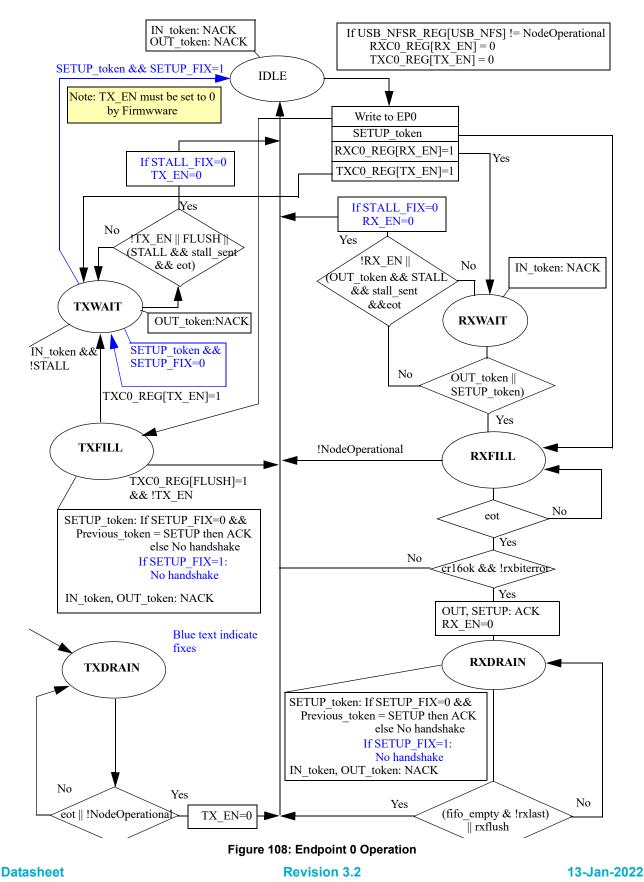

| 31.7 BIDIRECTIONAL CONTROL ENDPOINT FIF00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

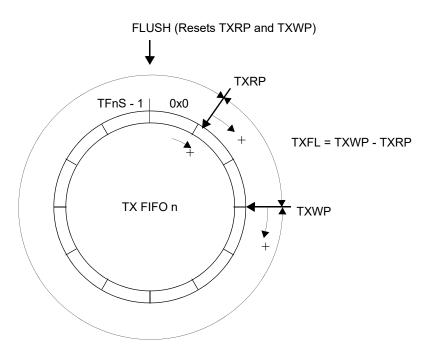

| 31.8 TRANSMIT ENDPOINT FIFO (TXFIFO1 TO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TXFIFO5) 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

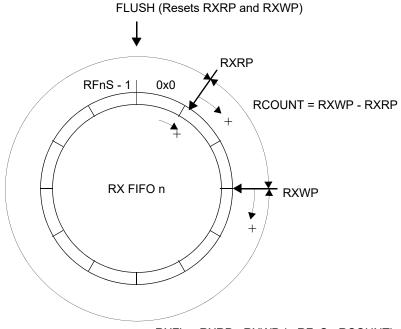

| 31.9 RECEIVE ENDPOINT FIFO (RXFIFO2 TO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RXFIFO6145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 31.10 INTERRUPT HIERARCHY 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 31.11 USB POWER SAVING MODES 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 31.11.1 Freezing USB node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21.11.0 Integrated registers 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 31.11.2 Integrated resistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

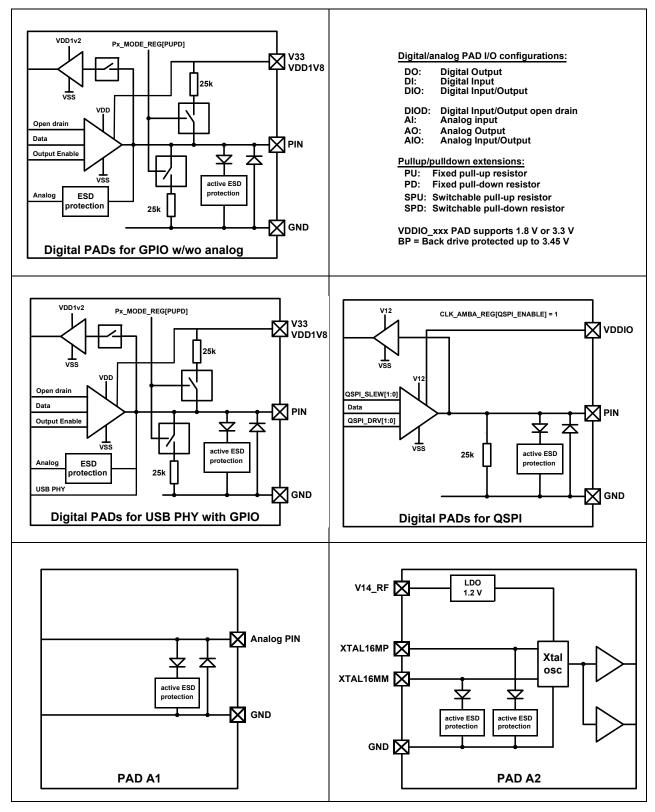

| 31.11.2 Integrated resistors         140           32 Input/Output ports         149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

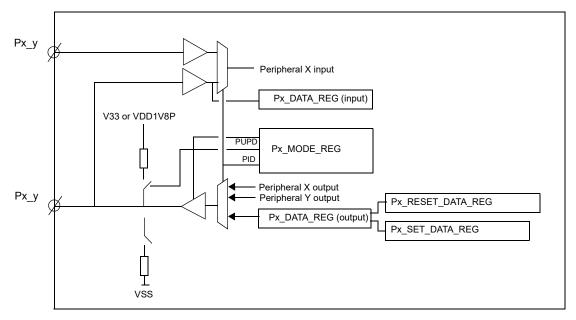

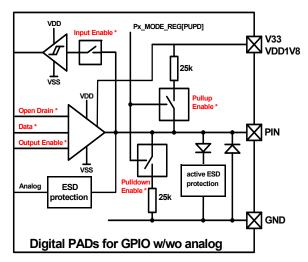

| 32 Input/Output ports 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>32 Input/Output ports</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>32 Input/Output ports</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 32 Input/Output ports.14932.1 PROGRAMMABLE PIN ASSIGNMENT14932.2 GENERAL PURPOSE PORT REGISTERS14932.2.1 Port Data Register149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 32 Input/Output ports.14932.1 PROGRAMMABLE PIN ASSIGNMENT14932.2 GENERAL PURPOSE PORT REGISTERS14932.2.1 Port Data Register14932.2.2 Port Set Data Output Register150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 32 Input/Output ports.14932.1 PROGRAMMABLE PIN ASSIGNMENT14932.2 GENERAL PURPOSE PORT REGISTERS14932.2.1 Port Data Register14932.2.2 Port Set Data Output Register15032.2.3 Port Reset Data Output Register150                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 32 Input/Output ports.14932.1 PROGRAMMABLE PIN ASSIGNMENT14932.2 GENERAL PURPOSE PORT REGISTERS14932.2.1 Port Data Register14932.2.2 Port Set Data Output Register15032.2.3 Port Reset Data Output Register15032.3 FIXED ASSIGNMENT FUNCTIONALITY150                                                                                                                                                                                                                                                                                                                                                                                                              |

| 32 Input/Output ports.14932.1 PROGRAMMABLE PIN ASSIGNMENT14932.2 GENERAL PURPOSE PORT REGISTERS14932.2.1 Port Data Register14932.2.2 Port Set Data Output Register15032.2.3 Port Reset Data Output Register15032.3 FIXED ASSIGNMENT FUNCTIONALITY15032.4 STATE RETENTION WHILE SLEEPING150                                                                                                                                                                                                                                                                                                                                                                        |

| 32 Input/Output ports.14932.1 PROGRAMMABLE PIN ASSIGNMENT14932.2 GENERAL PURPOSE PORT REGISTERS14932.2.1 Port Data Register14932.2.2 Port Set Data Output Register15032.2.3 Port Reset Data Output Register15032.3 FIXED ASSIGNMENT FUNCTIONALITY15032.4 STATE RETENTION WHILE SLEEPING15032.5 SPECIAL I/O CONSIDERATIONS151                                                                                                                                                                                                                                                                                                                                      |

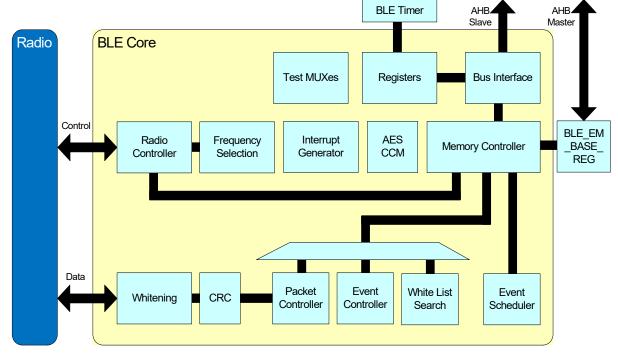

| 32 Input/Output ports.14932.1 PROGRAMMABLE PIN ASSIGNMENT14932.2 GENERAL PURPOSE PORT REGISTERS14932.2.1 Port Data Register14932.2.2 Port Set Data Output Register15032.2.3 Port Reset Data Output Register15032.3 FIXED ASSIGNMENT FUNCTIONALITY15032.4 STATE RETENTION WHILE SLEEPING15133 BLE Core152                                                                                                                                                                                                                                                                                                                                                          |

| 32 Input/Output ports.       149         32.1 PROGRAMMABLE PIN ASSIGNMENT       149         32.2 GENERAL PURPOSE PORT REGISTERS       149         32.2.1 Port Data Register       149         32.2.2 Port Set Data Output Register       150         32.3 FIXED ASSIGNMENT FUNCTIONALITY       150         32.4 STATE RETENTION WHILE SLEEPING       151         33 BLE Core       152         33.1 ARCHITECTURE       152                                                                                                                                                                                                                                        |

| 32 Input/Output ports.       149         32.1 PROGRAMMABLE PIN ASSIGNMENT       149         32.2 GENERAL PURPOSE PORT REGISTERS       149         32.2.1 Port Data Register       149         32.2.2 Port Set Data Output Register       150         32.2.3 Port Reset Data Output Register       150         32.3 FIXED ASSIGNMENT FUNCTIONALITY       150         32.4 STATE RETENTION WHILE SLEEPING       151         33 BLE Core       152         33.1 ARCHITECTURE       152         33.1.1 Exchange Memory       152                                                                                                                                      |

| 32 Input/Output ports.       149         32.1 PROGRAMMABLE PIN ASSIGNMENT       149         32.2 GENERAL PURPOSE PORT REGISTERS       149         32.2.1 Port Data Register       149         32.2.2 Port Set Data Output Register       150         32.2.3 Port Reset Data Output Register       150         32.4 STATE RETENTION WHILE SLEEPING       150         32.5 SPECIAL I/O CONSIDERATIONS       151         33 BLE Core       152         33.1 ARCHITECTURE       152         33.2 PROGRAMMING       152                                                                                                                                                |

| 32 Input/Output ports.       149         32.1 PROGRAMMABLE PIN ASSIGNMENT       149         32.2 GENERAL PURPOSE PORT REGISTERS       149         32.2.1 Port Data Register       149         32.2.2 Port Set Data Output Register       150         32.3 FIXED ASSIGNMENT FUNCTIONALITY       150         32.4 STATE RETENTION WHILE SLEEPING       151         33 BLE Core       152         33.1 ARCHITECTURE       152         33.2 PROGRAMMING       152         33.2.1 Wake up IRQ       152                                                                                                                                                                |

| 32 Input/Output ports.       149         32.1 PROGRAMMABLE PIN ASSIGNMENT       149         32.2 GENERAL PURPOSE PORT REGISTERS       149         32.2.1 Port Data Register       149         32.2.2 Port Set Data Output Register       150         32.3 FIXED ASSIGNMENT FUNCTIONALITY       150         32.4 STATE RETENTION WHILE SLEEPING       150         32.5 SPECIAL I/O CONSIDERATIONS       151         33 BLE Core       152         33.1 ARCHITECTURE       152         33.2.1 Exchange Memory       152         33.2.1 Wake up IRQ       152         33.2.2 Switch from Active Mode to Deep Sleep       152                                         |

| 32 Input/Output ports.       149         32.1 PROGRAMMABLE PIN ASSIGNMENT       149         32.2 GENERAL PURPOSE PORT REGISTERS       149         32.2.1 Port Data Register       149         32.2.2 Port Set Data Output Register       150         32.3 FIXED ASSIGNMENT FUNCTIONALITY       150         32.4 STATE RETENTION WHILE SLEEPING       150         32.5 SPECIAL I/O CONSIDERATIONS       151         33 BLE Core       152         33.1 ARCHITECTURE       152         33.2.1 Wake up IRQ       152         33.2.2 Switch from Active Mode to Deep Sleep       Mode         Mode       153                                                          |

| 32 Input/Output ports.       149         32.1 PROGRAMMABLE PIN ASSIGNMENT       149         32.2 GENERAL PURPOSE PORT REGISTERS       149         32.2.1 Port Data Register       149         32.2.2 Port Set Data Output Register       150         32.3 FIXED ASSIGNMENT FUNCTIONALITY       150         32.4 STATE RETENTION WHILE SLEEPING       151         33 BLE Core       152         33.1 ARCHITECTURE       152         33.2.1 Wake up IRQ       152         33.2.2 Switch from Active Mode to Deep Sleep       Mode         Mode       153         33.2.3 Switch from Deep Sleep Mode to Active                                                       |

| 32 Input/Output ports.       149         32.1 PROGRAMMABLE PIN ASSIGNMENT       149         32.2 GENERAL PURPOSE PORT REGISTERS       149         32.2.1 Port Data Register       149         32.2.2 Port Set Data Output Register       150         32.2.3 Port Reset Data Output Register       150         32.3 FIXED ASSIGNMENT FUNCTIONALITY       150         32.4 STATE RETENTION WHILE SLEEPING       150         32.5 SPECIAL I/O CONSIDERATIONS       151         33 BLE Core       152         33.1 ARCHITECTURE       152         33.2.1 Wake up IRQ       152         33.2.2 Switch from Active Mode to Deep Sleep       Mode         Mode       153 |

# RENESAS

# FINAL

|     | 33.3 DIAGNOSTIC SIGNALS                 | 156 |

|-----|-----------------------------------------|-----|

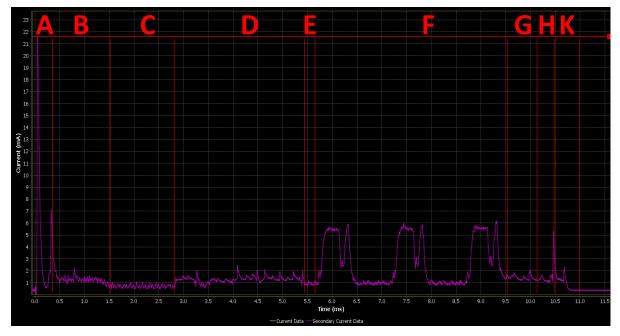

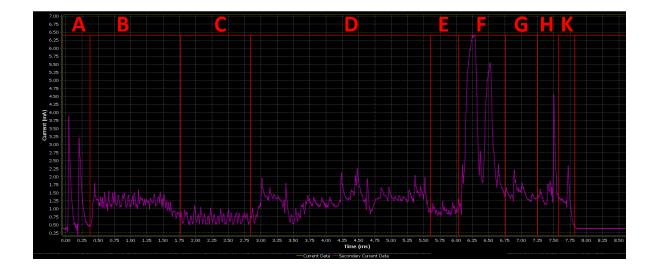

|     | 33.4 POWER PROFILE                      | 157 |

|     | 33.4.1 Advertising Event                |     |

|     | 33.4.2 Connection Event                 |     |

| • • |                                         |     |

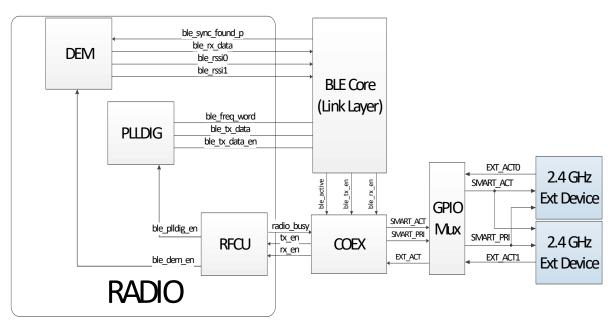

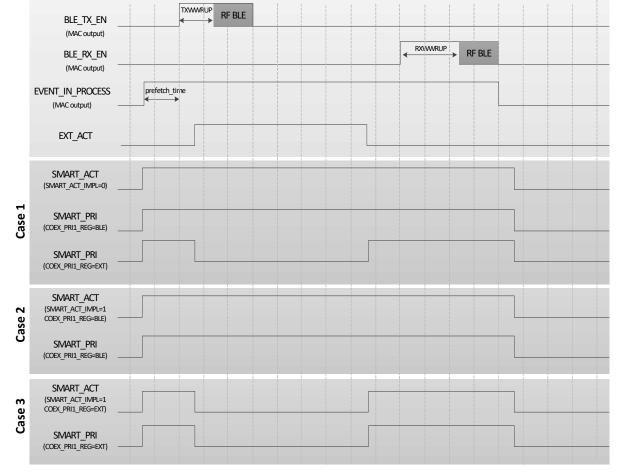

| 34  | CoEx interface                          |     |

|     | 34.1 ARCHITECTURE                       |     |

|     | 34.2 PROGRAMMING                        | 159 |

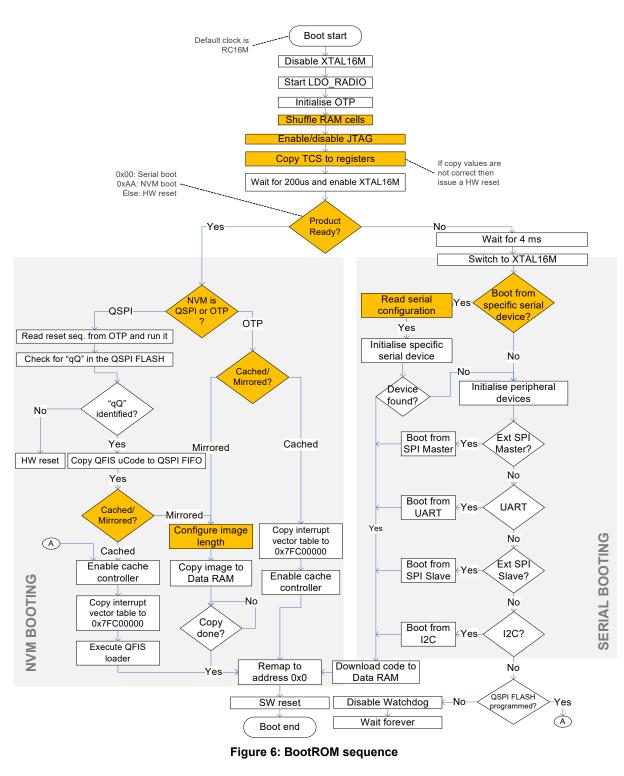

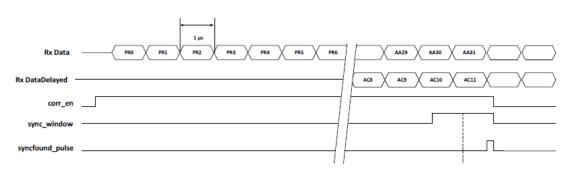

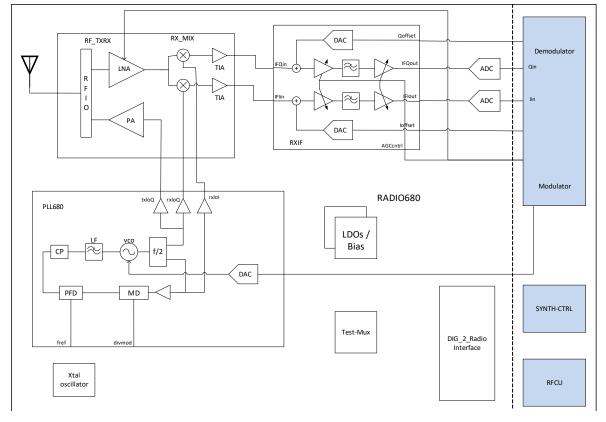

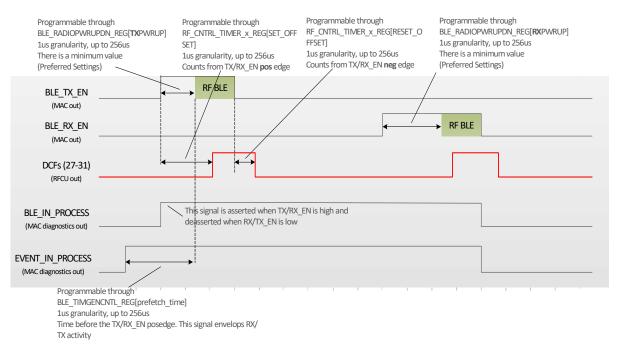

| 35  | Radio                                   | 161 |

|     | 35.1 ARCHITECTURE                       | 161 |

|     | 35.1.1 Receiver                         | 161 |

|     | 35.1.2 Synthesizer                      | 161 |

|     | 35.1.3 Transmitter                      | 162 |

|     | 35.1.4 RFIO                             | 162 |

|     | 35.1.5 Biassing                         | 162 |

|     | 35.1.6 Control                          | 162 |

|     | 35.2 DYNAMIC CONTROLLED FUNCTIONS       | 162 |

|     | 35.3 DIAGNOSTIC SIGNALS                 | 162 |

| 36  | Memory map                              | 161 |

| 50  |                                         | 104 |

| 37  | Registers                               | 166 |

|     | 37.1 OTPC REGISTER FILE                 | 168 |

|     | 37.2 QSPIC REGISTER FILE                | 175 |

|     | 37.3 BLE REGISTER FILE                  | 186 |

|     | 37.4 AES_HASH REGISTER FILE             | 205 |

|     | 37.5 CACHE REGISTER FILE                |     |

|     | 37.6 CRG REGISTER FILE                  | 213 |

|     | 37.7 DCDC REGISTER FILE                 | 223 |

|     | 37.8 WAKEUP REGISTER FILE               | 233 |

|     | 37.9 TIMER1 REGISTER FILE               |     |

|     | 37.10 UART REGISTER FILE                | 239 |

|     | 37.11 SPI REGISTER FILE                 | 277 |

|     | 37.12 I2C REGISTER FILE                 | 282 |

|     | 37.13 KEYBOARD SCAN REGISTER FILE       | 316 |

|     | 37.14 IR REGISTER FILE                  | 324 |

|     | 37.15 USB REGISTER FILE                 | 327 |