### **DA9098**

Ultra-Low IQ Charger PMIC with 4-Output SIMO

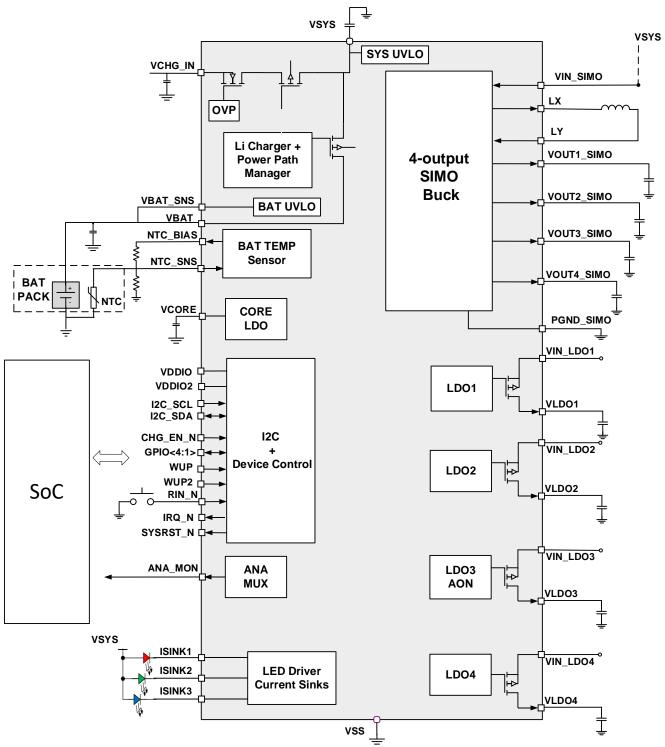

The **DA9098** is a highly integrated, configurable, ultra-low quiescent current charger PMIC with a host of additional functionality to support the needs of TWS Systems (Hearables), Wearables, and other small Li-lon battery operated applications.

The Charger PMIC integrates a 500 mA linear battery charger with power-path manager (PPM), a 4-output SIMO capable of delivering 400 mA of total current, four LDOs and a 3-channel LED driver. In addition to this highly integrated functionality, the DA9098 features a complete set of robust protection features, watchdog, additional GPIOs for system flexibility, and I<sup>2</sup>C control in a compact WLCSP package.

DA9098 has several power saving modes to increase battery life, whether the product sits on the shelf or is in operation.

DA9098 provides charge current up to 500 mA for fast charging cycle. The charge profile is programmable and includes dynamic power path management which automatically balances current delivered to the system and battery charging.

Suitable for small battery applications, the battery monitor facilitates on-demand battery voltage, charge and discharge current monitors, as well as temperature management.

# **Key Features**

- Increased battery life

- 1.3 µA IQ in deep sleep mode

- Power saving modes optimized for storage and low-power operation

- Multiple wake-up sources supported for maximum user flexibility

- Charger & Power Path Management

- Fast charge: 500 mA (max) programmable charge current

- Programmable pre-charge, fast charge, and termination conditions

- · Dynamic power path

- Supports adaptive power source voltage to minimize power dissipation

- 4-output 0.5 V to 1.85 V SIMO for total 400 mA

- Four LDOs

- LDO1/2 V<sub>OUT</sub>: 0.5 V to 1.2 V, I<sub>OUT</sub>: 100 mA (max)

- LDO3 V<sub>OUT</sub>: 1.8 V,

I<sub>OUT</sub>: 20 mA (max), I<sub>Q</sub> = 300 nA (typ)

- LDO4 V<sub>OUT</sub>: 1.2 V to 3.3 V, I<sub>OUT</sub>: 100 mA (max)

- Protection features

- · Over-voltage protection

- · Thermal shutdown protection

- · Over-discharge protection

- LED driver current sinks

- High integration and configurability

- I2C enabled battery monitors

- · Charging status monitors

- Compact 7x7 WLCSP package with 0.35 mm ball pitch

# **Applications**

- TWS systems, hearables

- Wearable devices Wireless headphones, fitness trackers, smart watches,

- Home automation devices Smoke detectors, Smart thermostats, Smart door locks

- Health monitoring medical accessories

- Rechargeable toys

- High efficiency, ultra-low power applications

Figure 1. System diagram

# **Contents**

| Key  | Featu    | ıres      |                                            |    |

|------|----------|-----------|--------------------------------------------|----|

| App  | olicatio | ons       |                                            |    |

| Con  | itents   |           |                                            | 3  |

| Figu | ıres     |           |                                            | 5  |

| Tab  | les      |           |                                            | 5  |

| 1.   | Term     | s and De  | efinitions                                 | 7  |

| 2.   | Refe     | rences    |                                            | 7  |

| 3.   | Pin lı   | nformatio | on                                         | 8  |

|      | 3.1      | Pin Assi  | ignments                                   | 8  |

|      | 3.2      | Pin Des   | criptions                                  | 9  |

| 4.   | Spec     | ification | s                                          | 11 |

|      | 4.1      | Absolute  | e Maximum Ratings                          | 11 |

|      | 4.2      | Electros  | static Discharge Ratings                   | 11 |

|      | 4.3      | Recomm    | mended Operating Conditions                | 11 |

|      | 4.4      | Recomm    | mended External Components                 | 12 |

|      | 4.5      | Current   | Consumption Characteristics                | 13 |

|      | 4.6      | SIMO B    | uck Regulator Characteristics              | 14 |

|      | 4.7      | LDO Ch    | naracteristics                             | 15 |

|      |          | 4.7.1     | LDO1 Characteristics                       | 15 |

|      |          | 4.7.2     | LDO3 Characteristics                       | 16 |

|      |          | 4.7.3     | LDO4 Characteristics                       | 17 |

|      | 4.8      | ISINK -   | LED Driver Characteristics                 | 19 |

|      | 4.9      |           | Path Management Electrical Characteristics |    |

|      | 4.10     | Battery   | Charger Electrical Characteristics         | 20 |

|      | 4.11     | Battery   | Temperature Sensor Characteristics         | 21 |

|      | 4.12     |           | on Electrical Characteristics              |    |

|      | 4.13     | Interface | e Characteristics                          | 22 |

|      | 4.14     | Timing (  | Characteristics                            | 23 |

|      | 4.15     | Therma    | l Characteristics                          | 24 |

| 5.   | Func     | tional De | escription                                 | 25 |

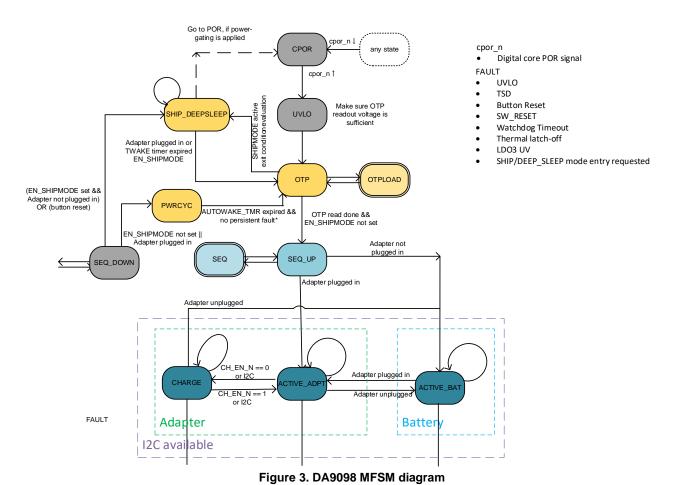

|      | 5.1      | System    | State Machine                              | 25 |

|      |          | 5.1.1     | First Startup and SHIP Mode Entry/Exit     | 25 |

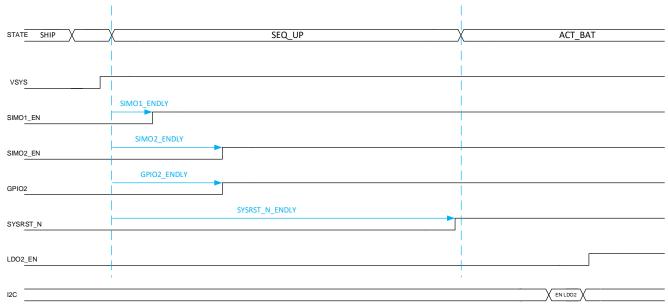

|      |          | 5.1.2     | Startup Sequence                           | 26 |

|      |          | 5.1.3     | ACTIVE Modes and Transitions               | 26 |

|      |          | 5.1.4     | SEQ_DOWN Sequence                          | 26 |

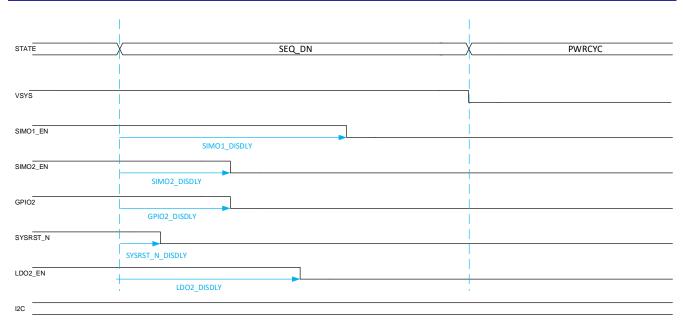

|      |          | 5.1.5     | Power Up/Down Sequences                    | 27 |

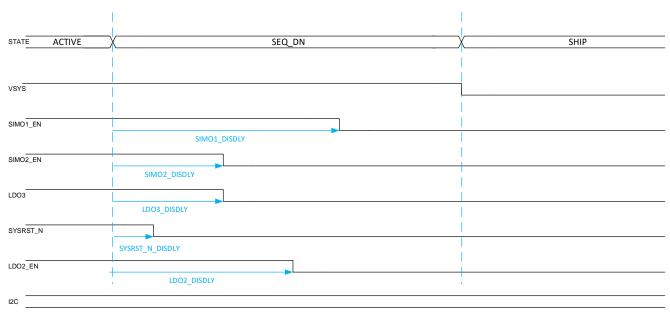

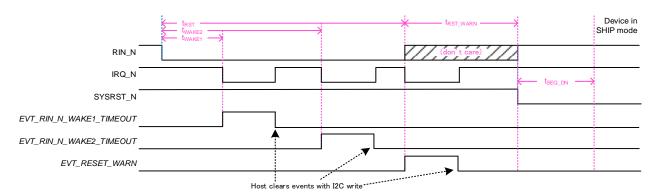

|      |          | 5.1.6     | SHIP Mode                                  | 29 |

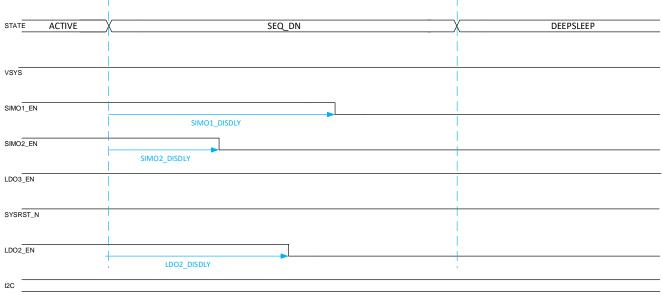

|      |          | 5.1.7     | DEEPSLEEP Mode                             | 29 |

|      |          | 5.1.8     | CHG_EN_N                                   | 30 |

|      |          | 5.1.9     | Push Button Interface (RIN_N)              | 30 |

|      |          | 5.1.10    | SW Reset                                   | 31 |

|      |          | 5.1.11    | General Purpose Input Output               | 32 |

|      |          | 5.1.12    | Watchdog Reset                             | 33 |

|      |          | 5.1.13    | IRQ_N Generation                           | 34 |

|      |          |           |                                            |    |

|    | 5.2   | Therma    | al Protections                                  | 34 |

|----|-------|-----------|-------------------------------------------------|----|

|    |       | 5.2.1     | Thermal Warning                                 | 34 |

|    |       | 5.2.2     | Thermal Shutdown                                | 34 |

|    |       | 5.2.3     | Thermal Latch-Off                               | 34 |

|    | 5.3   | Battery   | Charging                                        | 34 |

|    |       | 5.3.1     | Pre-Charge and Fast Charge Operation            | 34 |

|    |       | 5.3.2     | Charge Done State and Recharge                  | 35 |

|    |       | 5.3.3     | Safety Timer                                    | 35 |

|    |       | 5.3.4     | Battery Temperature Range Detection             | 36 |

|    |       | 5.3.5     | Dynamic Power Path Management                   | 38 |

|    |       | 5.3.6     | Battery Supplement Mode                         | 39 |

|    |       | 5.3.7     | Adaptive Input Voltage Charging                 | 39 |

|    | 5.4   | Charge    | r Mode Operation and Power Path Management      | 39 |

|    |       | 5.4.1     | Input Voltage Dynamic Power Management (VINDPM) | 39 |

|    |       | 5.4.2     | VCHG_IN Current Limit (VINILIM)                 | 40 |

|    |       | 5.4.3     | Under-Voltage Lockout (VCHG_IN_UV)              | 40 |

|    |       | 5.4.4     | Sleep Mode (SLP)                                | 40 |

|    |       | 5.4.5     | Input Over-Voltage Protection (VCHG_IN_OV)      | 40 |

|    |       | 5.4.6     | VSYS Voltage Regulation and Power LDO (LDOPWR)  | 40 |

|    | 5.5   | SIMO B    | Buck                                            | 40 |

|    | 5.6   | Analog    | Monitor                                         | 42 |

|    |       | 5.6.1     | Channels Selection                              | 42 |

|    |       | 5.6.2     | Analog Performances                             | 43 |

|    | 5.7   | LED Dr    | iver - Current Sink                             | 43 |

|    |       | 5.7.1     | Constant Mode                                   | 43 |

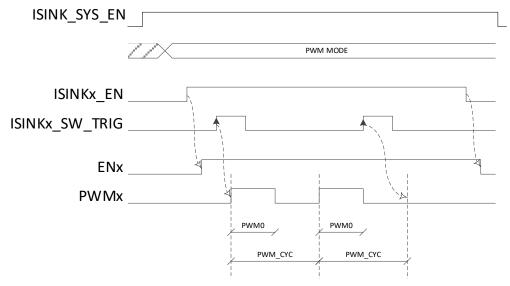

|    |       | 5.7.2     | PWM Mode                                        | 44 |

|    |       | 5.7.3     | LED Driver Register Configuration               | 44 |

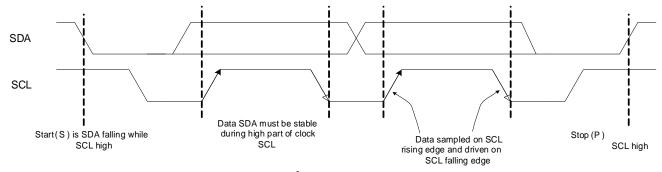

|    | 5.8   | Commu     | unication Interface I <sup>2</sup> C            | 44 |

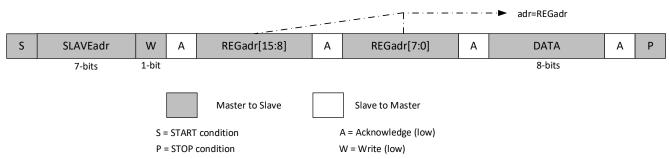

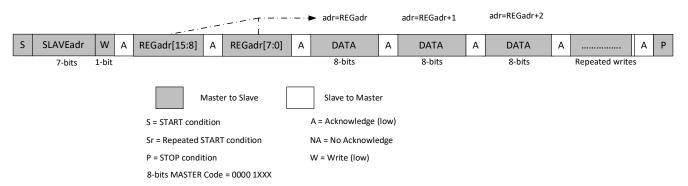

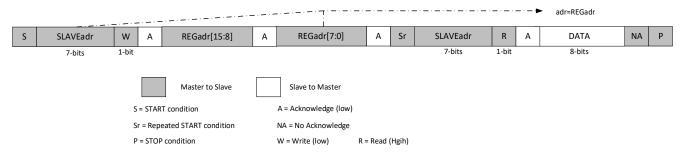

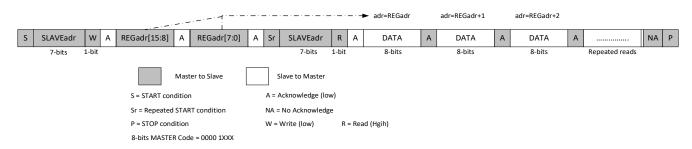

|    |       | 5.8.1     | Frame Format                                    | 45 |

|    |       | 5.8.2     | Single-Byte Write                               | 45 |

|    |       | 5.8.3     | Multiple-Byte Write                             | 46 |

|    |       | 5.8.4     | Single-Byte Read                                | 46 |

|    |       | 5.8.5     | Multiple-Bytes Read                             | 46 |

|    | 5.9   | Lock Re   | egister Handling                                | 47 |

|    | 5.10  | Fault ar  | nd Event Table                                  | 47 |

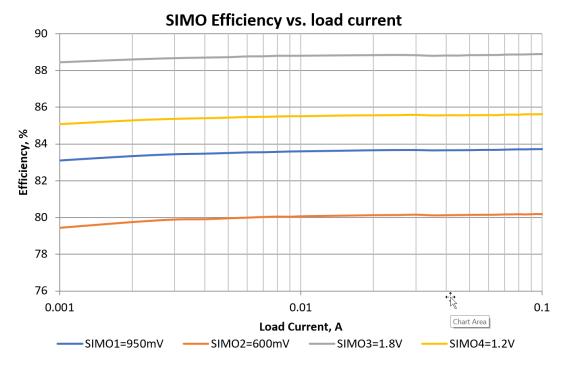

| 6. | Туріс | cal Perfo | ormance Graphs                                  | 50 |

|    | 6.1   | SIMO E    | Efficiency                                      | 50 |

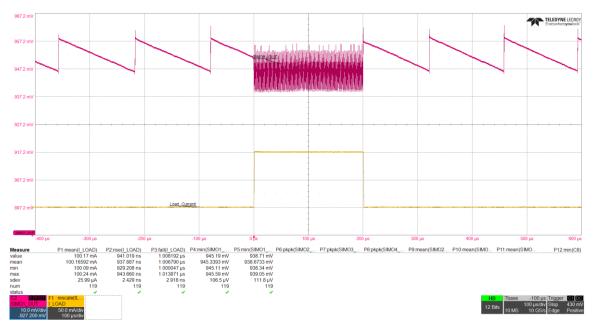

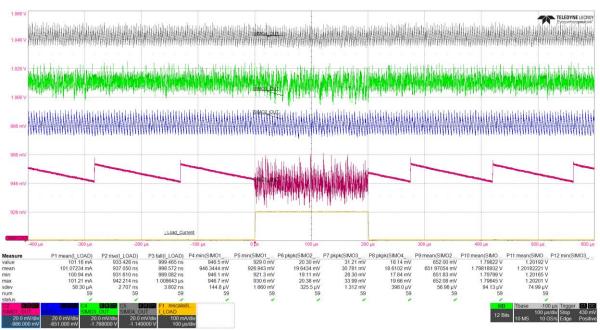

|    | 6.2   | SIMO D    | Oynamic Performances                            | 50 |

|    |       | 6.2.1     | Load Transient                                  | 50 |

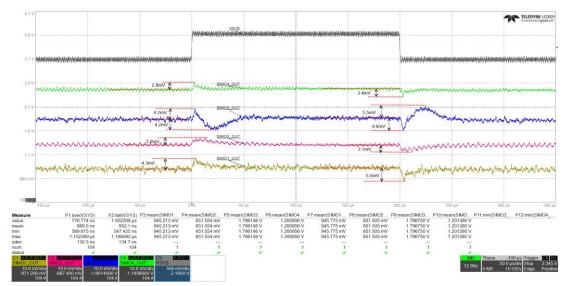

|    |       | 6.2.2     | Line Transient                                  | 52 |

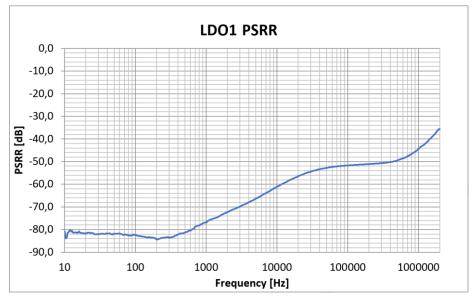

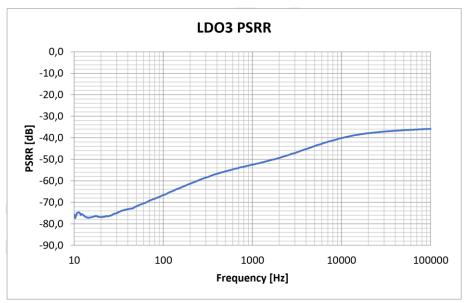

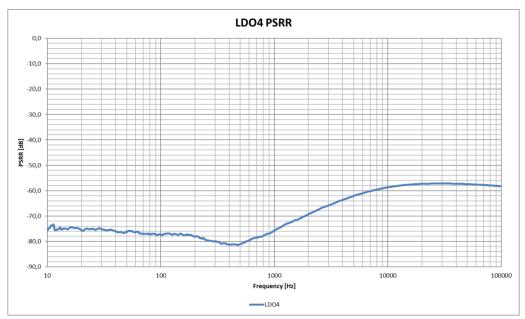

|    | 6.3   | LDO PS    | SRR                                             | 53 |

| 7. | Regi  | ster Defi | initions                                        | 55 |

|    | 7.1   | Snapsh    | not Mechanism                                   | 55 |

|    | 7.2   | Registe   | er Map                                          | 55 |

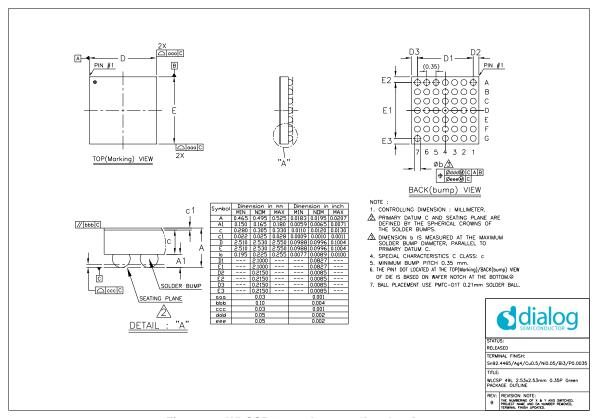

| 8. | Pack  | age Info  | ormation                                        | 56 |

|    | 8.1   | Packag    | ge Outlines                                     | 56 |

|     | 8.2     | Moisture Sensitivity Level                                                                     | 56 |

|-----|---------|------------------------------------------------------------------------------------------------|----|

|     | 8.3     | WLCSP Handling                                                                                 | 56 |

|     | 8.4     | Soldering Information                                                                          |    |

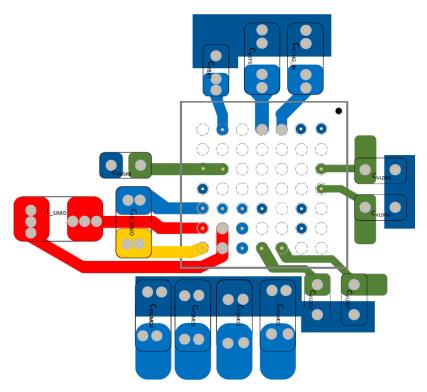

| 9.  |         | ering Information                                                                              |    |

|     |         | out Guidelines                                                                                 |    |

|     | •       |                                                                                                |    |

| Fi  | gure    | es                                                                                             |    |

| _   |         | System diagram                                                                                 |    |

| _   |         | WLCSP pinout diagram (top view)                                                                |    |

| _   |         | DA9098 MFSM diagram                                                                            |    |

| _   |         | Example of a power-up sequence (SHIP to ACTIVE). LDO2 is enabled later on via I <sup>2</sup> C |    |

| _   |         | Example of a power-down sequence. LDO2 sequenced down according to the DISDLY setting          |    |

| -   |         | Example for ACTIVE to DEEPSLEEP (EN_SHIPMODE=1, EN_DEEPSLEEP=1)                                |    |

| _   |         | Example of ACTIVE to SHIPMODE (EN_SHIPMODE=1, EN_DEEPSLEEP=0)                                  |    |

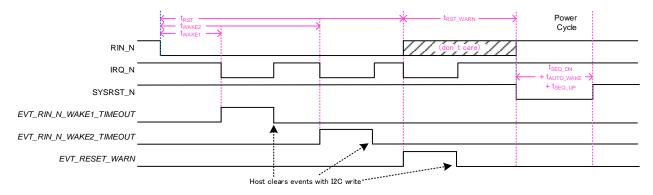

| _   |         | Manual reset to SHIP timing diagram (BUTTON_HARD_RESET_EN=1)                                   |    |

| _   |         | Manual reset to POWER CYCLE timing diagram (BUTTON_HARD_RESET_EN=0)                            |    |

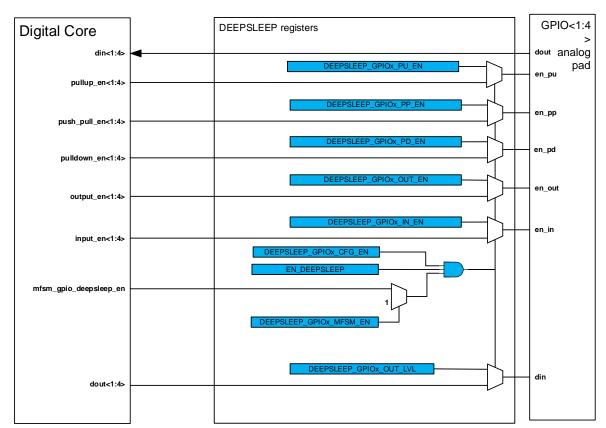

| _   |         | . DEEPSLEEP registers for the 4 GPIOs                                                          |    |

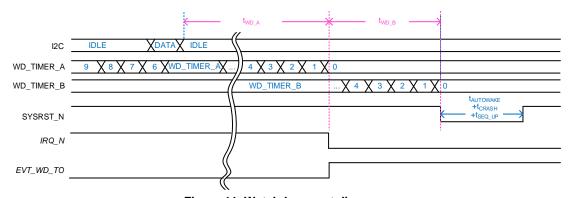

| _   |         | . Watchdog reset diagram                                                                       |    |

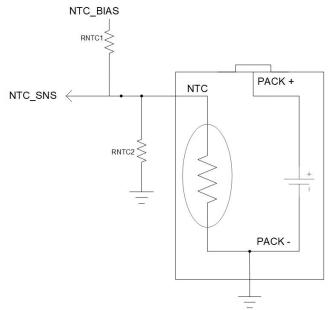

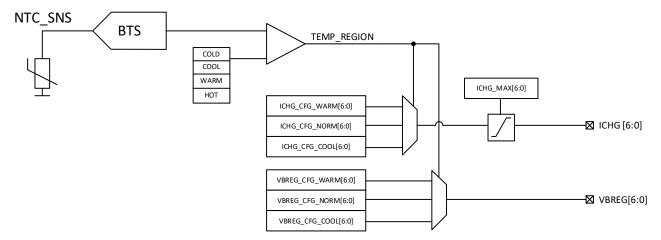

|     |         | NTC battery temperature sensing with NTC                                                       |    |

|     |         | . ICHG and VBREG selection depending on NTC_SNS                                                |    |

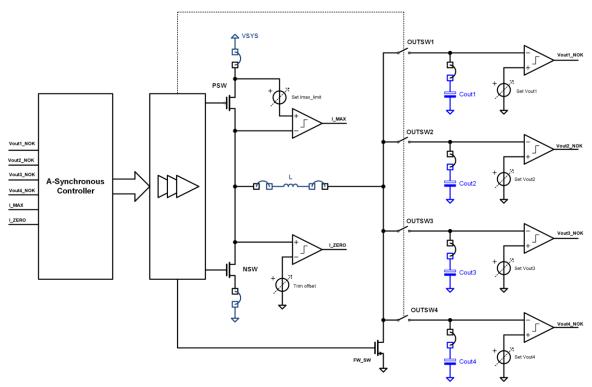

| _   |         | SIMO buck simplified block diagram                                                             |    |

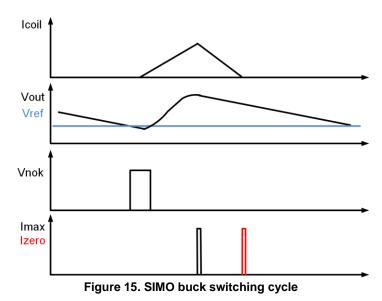

| -   |         | . SIMO buck switching cycle                                                                    |    |

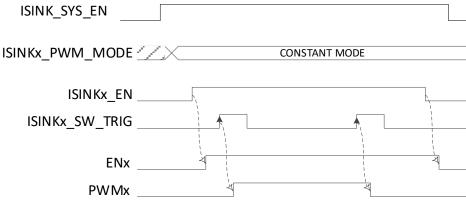

| _   |         | . ISINK constant mode                                                                          |    |

| _   |         | . I <sup>2</sup> C start (S) and stop (P)                                                      |    |

| -   |         | Single write                                                                                   |    |

| -   |         | . Consecutive write                                                                            |    |

| _   |         | Single read                                                                                    |    |

| -   |         | . Consecutive read                                                                             |    |

| _   |         | DA9098 typical SIMO efficiency for 4 different voltages                                        |    |

| _   |         | . DA9098 SIMO1 load transient response - other rails not loaded                                |    |

| _   |         | DA9098 SIMO1 load transient response with large total load                                     |    |

| _   |         | DA9098 SIMO buck line transient response                                                       |    |

| _   |         | . DA9098 LDO1/2 PSRR                                                                           |    |

| _   |         | . DA9098 LDO3 PSRR                                                                             |    |

| _   |         | . DA9098 LDO4 PSRR                                                                             |    |

| _   |         | . WLCSP-49 package outline drawing                                                             |    |

| _   |         | DA9098 layout example                                                                          |    |

|     |         |                                                                                                |    |

| Ta  | ble     | S                                                                                              |    |

| Tab | le 1. F | Pin descriptions                                                                               | 9  |

| Tab | le 2. F | Pin type definition                                                                            | 10 |

| Tab | le 3. A | Absolute maximum ratings                                                                       | 11 |

| Tab | le 4. E | Electrostatic discharge ratings                                                                | 11 |

|     |         | Recommended operating conditions                                                               |    |

|     |         | Recommended external components                                                                |    |

|     |         | nput currents electrical characteristics                                                       |    |

|     |         | SIMO buck electrical characteristics                                                           |    |

| Tab | le 9: L | DO1 electrical characteristics                                                                 | 15 |

## **DA9098 Datasheet**

| Table 10: LDO2 electrical obstractoristics                 | 16 |

|------------------------------------------------------------|----|

| Table 10: LDO3 electrical characteristics                  |    |

| Table 11: LDO4 electrical characteristics                  |    |

| Table 12: ISINK electrical characteristics                 |    |

| Table 13: Power-path management electrical characteristics |    |

| Table 14: Battery charger electrical characteristics       | 20 |

| Table 15: Battery temperature sensor characteristics       | 21 |

| Table 16: Protection electrical characteristics            | 21 |

| Table 17: Interface electrical characteristics             | 22 |

| Table 18: Timing characteristics                           | 23 |

| Table 19. Thermal characteristics                          | 24 |

| Table 20. Push button wake-up timers and control registers | 30 |

| Table 21. Manual reset timer event registers               | 31 |

| Table 22. Charge mode control                              | 34 |

| Table 23. Safety timers                                    | 35 |

| Table 24. List of charge faults and timer changes          | 35 |

| Table 25. TMR register settings                            | 36 |

| Table 26. TMRX2_EN register                                |    |

| Table 27. ANA_MON output signals                           | 42 |

| Table 28. Fault and event table                            |    |

| Table 29. MSL classification                               | 56 |

| Table 30. Ordering information                             | 58 |

# 1. Terms and Definitions

DPM Dynamic power management

DPPM Dynamic power path management

TWS True wireless stereo

OTP One-time programable (memory)

# 2. References

[1] None

**Note 1** References are for the latest published version, unless otherwise indicated.

# 3. Pin Information

# 3.1 Pin Assignments

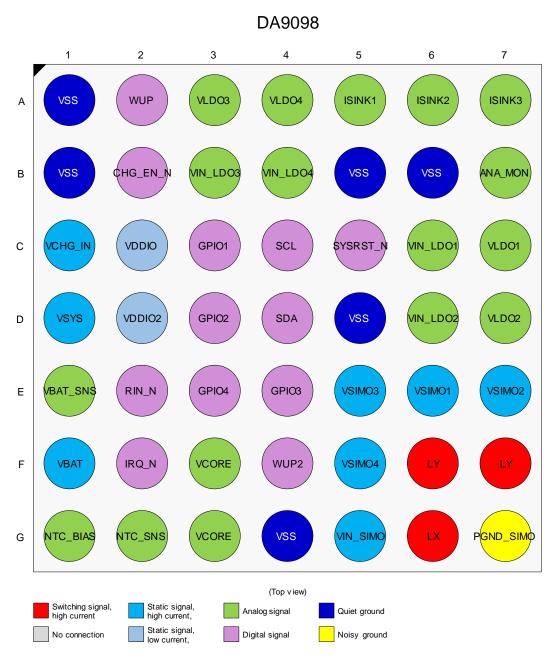

Figure 2. WLCSP pinout diagram (top view)

# 3.2 Pin Descriptions

Table 1. Pin descriptions

| Pin number | Pin name  | Type (Table 2) | Drive<br>(mA) | Description                                                                                 |

|------------|-----------|----------------|---------------|---------------------------------------------------------------------------------------------|

| C1         | VCHG_IN   | PWR            | 500           | Input power supply. In register names the VDD_PWR alias is used                             |

| D1         | VSYS      | PWR            | 2000          | Intermediate supply of power rails                                                          |

| F1         | VBAT      | PWR            | 2000          | Battery connection                                                                          |

| E1         | VBAT_SNS  | Al             | 0.1           | Sense battery voltage. To be tied with VBAT on PCB                                          |

| F3         | VCORE     | PWR            | 10            | 1.5 V Core supply                                                                           |

| G3         | VCORE     | PWR            | 10            | 1.5 V Core supply                                                                           |

| G5         | VIN_SIMO  | PWR            | 2000          | SIMO Buck input supply                                                                      |

| G6         | LX        | AIO            | 2000          | SIMO Buck switching node                                                                    |

| F7         | LY        | AIO            | 2000          | SIMO switches input node                                                                    |

| F6         | LY        | AIO            | 2000          | SIMO switches input node                                                                    |

| E6         | VSIMO1    | PWR            | 500           | SIMO1 output                                                                                |

| E7         | VSIMO2    | PWR            | 500           | SIMO2 output                                                                                |

| E5         | VSIMO3    | PWR            | 500           | SIMO3 output                                                                                |

| F5         | VSIMO4    | PWR            | 500           | SIMO4 output                                                                                |

| G7         | PGND_SIMO | GND            | 2000          | SIMO power ground                                                                           |

| C6         | VIN_LDO1  | PWR            | 250           | LDO1 supply input. Connect to VSIMO1                                                        |

| C7         | VLDO1     | PWR            | 250           | LDO1 output                                                                                 |

| D6         | VIN_LDO2  | PWR            | 250           | LDO2 supply input, Connect toVSIMO1                                                         |

| D7         | VLDO2     | PWR            | 250           | LDO2 output                                                                                 |

| B3         | VIN_LDO3  | PWR            | 250           | LDO3 supply input                                                                           |

| A3         | VLDO3     | PWR            | 250           | LDO3 output                                                                                 |

| B4         | VIN_LDO4  | PWR            | 250           | LDO4 supply input                                                                           |

| A4         | VLDO4     | PWR            | 250           | LDO4 output                                                                                 |

| C2         | VDDIO     | PWR            | 250           | IO supply                                                                                   |

| D2         | VDDIO2    | PWR            | 250           | IO supply GPIO3/GPIO4                                                                       |

| C3         | GPIO1     | DIO            | 10            | General purpose IO                                                                          |

| D3         | GPIO2     | DIO            | 10            | General purpose IO                                                                          |

| E4         | GPIO3     | DIO            | 10            | General purpose IO- VDDIO2 supplied                                                         |

| E3         | GPIO4     | DIO            | 10            | General purpose IO - VDDIO2 supplied                                                        |

| E2         | RIN_N     | DI             | 0.1           | Manual reset input and wake from SHIP mode. Internal pull-up 18.8 kΩ to max (VBAT; VCHG_IN) |

| A2         | WUP       | DI             | 10            | Dedicated pin for deep sleep mode wake-up                                                   |

| F4         | WUP2      | DI             | 10            | Additional pin for wake-up from deep sleep mode                                             |

| C5         | SYSRST_N  | DO             | 0.1           | System reset output - Host enable                                                           |

| F2         | IRQ_N     | DO             | 0.1           | Open-drain IRQ output                                                                       |

| B2         | CHG_EN_N  | DI             | 0.1           | Charge enable input. Internal pull-down 900 kΩ                                              |

| C4         | SCL       | DIO            | 10            | I <sup>2</sup> C clock input                                                                |

| D4         | SDA       | DIO            | 1             | I <sup>2</sup> C data                                                                       |

| G1         | NTC_BIAS  | AIO            | 1             | External temperature monitoring bias                                                        |

| G2         | NTC_SNS   | AIO            | 1             | External temperature monitoring sense pin                                                   |

| B7         | ANA_MON   | AO             | 1             | Various Analog signals scaled to 1.5V FS for ext. ADC measurement                           |

| A5         | ISINK1    | AO             | 250           | LED driver Output 1                                                                         |

| A6         | ISINK2    | AO             | 250           | LED driver Output 2                                                                         |

| A7         | ISINK3    | AO             | 250           | LED driver Output 3                                                                         |

| B5         | VSS       | GND            | 500           | 1                                                                                           |

## **DA9098 Datasheet**

| Pin number | Pin name | Type (Table 2) | Drive<br>(mA) | Description |

|------------|----------|----------------|---------------|-------------|

| B1         | VSS      | GND            | 500           |             |

| A1         | VSS      | GND            | 500           |             |

| B6         | VSS      | GND            | 500           |             |

| D5         | VSS      | GND            | 500           |             |

| G4         | VSS      | GND            | 500           |             |

## Table 2. Pin type definition

| Pin type | Description          | Pin type | Description         |

|----------|----------------------|----------|---------------------|

| DI       | Digital input        | Al       | Analog input        |

| DO       | Digital output       | AO       | Analog output       |

| DIO      | Digital input/output | AIO      | Analog input/output |

| PWR      | Power                | GND      | Ground              |

# 4. Specifications

Unless otherwise specified, typical characteristics (Typ) are reflecting performance under typical External Electrical Conditions at room temperature and limit characteristics (Min, Max) to correspond to performance variation across limit External Electrical Conditions for junction temperature from -40 °C to 125 °C.

# 4.1 Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

**CAUTION**: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

Table 3. Absolute maximum ratings

| Parameter           | Description                                                                                                                                                | Conditions                           | Min  | Max                    | Unit |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|------------------------|------|

| V <sub>CHG_IN</sub> | VCHG_IN                                                                                                                                                    |                                      | -0.3 | 22                     | V    |

| Vsup                | VBAT, VBAT_SNS VSYS, VDDIO, VDDIO2, VIN_LDO3, VIN_LDO4, VIN_SIMO, LX, LY, VSIMO1, VSIMO2, VSIMO3, VSIMO4, VLDO4, ISINK1, ISINK2, ISINK3, NTC_BIAS, NTC_SNS |                                      | -0.3 | 6                      | V    |

| V <sub>CORE</sub>   | VIN_LDO1, VLDO1,<br>VIN_LDO2, VLDO2, VCORE,<br>ANA_MON                                                                                                     |                                      | -0.3 | 1.8                    | V    |

| V <sub>I2C</sub>    | SDA, SCL                                                                                                                                                   |                                      | -0.3 | 6                      | V    |

| V <sub>IO</sub>     | All other pins                                                                                                                                             | Absolute voltage must not exceed 6 V | -0.3 | V <sub>SUP</sub> + 0.3 | V    |

# 4.2 Electrostatic Discharge Ratings

Table 4. Electrostatic discharge ratings

| Parameter            | Description            | Conditions                        | Rating | Unit |

|----------------------|------------------------|-----------------------------------|--------|------|

| V <sub>ESD_CDM</sub> | Maximum ESD protection | Charged device model (CDM) Note 1 | ±500   | V    |

| V <sub>ESD_HBM</sub> | Maximum ESD protection | Human body model (HBM) Note 2     |        |      |

Note 1 JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Note 2 JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 4.3 Recommended Operating Conditions

Table 5. Recommended operating conditions

| Parameter            | Description                      | Conditions     | Min | Тур  | Max | Unit |

|----------------------|----------------------------------|----------------|-----|------|-----|------|

| TA                   | Operating Ambient<br>Temperature |                | -40 |      | 85  | °C   |

| V <sub>CHG_IN</sub>  | Charger Input Supply             |                | 3.6 | 5    | 5.5 | V    |

| V <sub>BAT</sub>     | Battery voltage                  | Active battery | 2.5 | 3.6  | 4.7 | V    |

| V <sub>IN LDO</sub>  | LDO input voltage                | LDO1 and LDO2  | 0.7 | 0.95 | 1.5 | V    |

| V IN_LDO             | LDO Input voltage                | LDO3 and LDO4  | 2.5 | 3.6  | 5.5 | V    |

| V <sub>IN_SIMO</sub> | SIMO input voltage               |                | 2.5 | 3.6  | 5.5 | V    |

| V <sub>DDIO</sub>    | IO supply                        | VDDIO, VDDIO2  | 1.7 | 1.8  | 5.5 | V    |

VDDIO supplies most of the chip IOs.

VDDIO2 supplies GPIO3 and GPIO4 only.

If GPIO3 or GPIO4 are used, VDDIO2 shall be supplied by one of the DA9098 rails. Otherwise, it can be left unconnected.

One proposed configuration is LDO3 to supply VDDIO and VSYS to supply VDDIO2.

# 4.4 Recommended External Components

Component values shown in Table 6 are nominal values (before de-rating).

For capacitors, temperature profile shall be X5R type or better with a DC voltage rating of 2x the maximum applied voltage.

For inductors, the saturation current rating shall be equal or greater than the current limit value.

Table 6. Recommended external components

| Parameter           | Description                         | Nominal       | Unit |

|---------------------|-------------------------------------|---------------|------|

| Csys                | VSYS capacitance                    | 10            | μF   |

| Сват                | VBAT capacitance                    | 2.2           | μF   |

| Cvchg_in            | VCHG_IN capacitance                 | 4.7           | μF   |

| CCORE               | VCORE capacitance                   | 220           | nF   |

| L <sub>SIMO</sub>   | SIMO buck inductor                  | 0.47          | μΗ   |

| C <sub>I_SIMO</sub> | SIMO input capacitor                | not populated | μF   |

| Co_SIMO1            | SIMO1 output capacitance            | 10            | μF   |

| Co_SIMO2            | SIMO2 output capacitance            | 10            | μF   |

| Co_simo3            | SIMO3 output capacitance            | 22            | μF   |

| Co_SIMO4            | SIMO4 output capacitance            | 10            | μF   |

| C <sub>I_LDO1</sub> | LDO1 input capacitor                | not populated | μF   |

| Co_LDO1             | LDO1 output capacitor               | 2.2           | μF   |

| C <sub>I_LDO2</sub> | LDO2 input capacitor                | not populated | μF   |

| C <sub>O_LDO2</sub> | LDO2 output capacitor               | 2.2           | μF   |

| C <sub>I_LDO3</sub> | LDO3 input capacitor                | not populated | μF   |

| Co_LDO3             | LDO3 output capacitor               | 2.2           | μF   |

| C <sub>I_LDO4</sub> | LDO4 input capacitor                | not populated | μF   |

| Co_LDO4             | LDO3 output capacitor               | 2.2           | μF   |

| R <sub>NTC</sub>    | Battery thermal sensing resistance  | 10.0          | kΩ   |

| R <sub>NTC1</sub>   | External thermal sensing resistance | 14.3          | kΩ   |

| R <sub>NTC2</sub>   | Skin thermal sensing resistance     | 14.3          | kΩ   |

# 4.5 Current Consumption Characteristics

Table 7: Input currents electrical characteristics

| Parameter             | Description                                               | Conditions                                                                                                                 | Min | Тур | Max | Unit |

|-----------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Electrical perform    | nance                                                     |                                                                                                                            |     |     |     |      |

| I <sub>BAT_SHIP</sub> | Battery discharge current in SHIP mode                    | V <sub>CHG_IN</sub> = 0 V<br>SHIP mode<br>All rails off                                                                    |     | 100 |     | nA   |

| BAT_DEEP_SLEEP        | Battery discharge current in deep sleep mode              | V <sub>CHG_IN</sub> = 0 V<br>LDO3 enabled<br>SIMO, LDO1, LDO2 and<br>LDO4 disabled<br>I <sup>2</sup> C disabled            |     | 1.3 |     | μА   |

| BAT_ACT_RAILS_OFF     | Battery discharge current in active mode, power rails off | 0 °C < T <sub>J</sub> < 85 °C  V <sub>CHG_IN</sub> = 0 V  Battery active mode  All power rails off                         |     | 8   |     | μΑ   |

| IBAT_ACT              | Battery discharge current in Active battery mode          | V <sub>CHG_IN</sub> = 0 V<br>Active battery mode<br>All rails on, not loaded<br>ISINK disabled<br>I <sup>2</sup> C enabled |     | 33  |     | μΑ   |

| In_chg_ready          | Supply current for control                                | 0 °C < T <sub>J</sub> < 85 °C<br>V <sub>CHG_IN</sub> = 5 V<br>Charge ready                                                 |     |     | 1.5 | mA   |

# 4.6 SIMO Buck Regulator Characteristics

Table 8: SIMO buck electrical characteristics

| Parameter        | Description                                                    | Conditions                                                                                                                                                                                                                                                           | Min          | Тур  | Max  | Unit |

|------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|------|

| External electri | cal conditions                                                 |                                                                                                                                                                                                                                                                      |              |      |      |      |

| VIN              | SIMO Buck input voltage                                        |                                                                                                                                                                                                                                                                      | 2.5          | 3.6  | 5.5  | V    |

| Lsimo            | SIMO buck inductor                                             |                                                                                                                                                                                                                                                                      | 0.37         | 0.47 | 0.56 | μН   |

| Cout_simo1       | SIMO1 Output capacitance                                       | Effective output capacitance                                                                                                                                                                                                                                         | 4.3          |      |      | μF   |

| Cout_SIMO2       | SIMO2 Output capacitance                                       | Effective output capacitance                                                                                                                                                                                                                                         | 4.7          |      |      | μF   |

| Cout_simo3       | SIMO3 Output capacitance                                       | Effective output capacitance                                                                                                                                                                                                                                         | 5.2          |      |      | μF   |

| Cout_simo4       | SIMO4 Output capacitance                                       | Effective output capacitance                                                                                                                                                                                                                                         | 3.9          |      |      | μF   |

| Programmable     | conditions                                                     |                                                                                                                                                                                                                                                                      | <del>!</del> |      |      |      |

| Vout_rng         | Output voltage range per output rail individually programmable | Step size 12.5 mV                                                                                                                                                                                                                                                    | 0.5          |      | 1.85 | V    |

| Vout_uv_rng      | UV comparator per rail - Absolute threshold                    | Step size 100 mV                                                                                                                                                                                                                                                     | 0.4          |      | 1.8  | V    |

| IPEAK_RNG        | Peak coil current limit range                                  | 3-bits programmable range                                                                                                                                                                                                                                            | 520          |      | 1750 | mA   |

| Electrical perfo | rmance                                                         |                                                                                                                                                                                                                                                                      | <del>!</del> |      |      |      |

| louт_мах         | Maximum DC output current per rail                             |                                                                                                                                                                                                                                                                      | 100          |      |      | mA   |

| Vout_static_acc  | Output voltage static accuracy per rail                        | V <sub>IN</sub> = 3.6 V<br>I <sub>OUT</sub> = 1 mA<br>V <sub>OUT</sub> = Typ                                                                                                                                                                                         | -2           |      | 2    | %    |

| Vout_tr_line     | Output voltage transient line response                         | V <sub>IN</sub> = 3.6 V to 3.1 V in 1 μs<br>and back<br>I <sub>OUT</sub> = 100/20/100/20 mA                                                                                                                                                                          | -10          |      | 10   | mV   |

| Vout_tr_acc      | Output voltage dynamic accuracy                                | $V_{IN}$ > 3.0 V SIMO1: $V_{OUT}$ = 0.95 V, $I_{OUT}$ = 100 mA, $C_{OUT}$ = 10 μF SIMO2: $V_{OUT}$ = 0.65 V, $I_{OUT}$ = 20 mA, $I_{OUT}$ = 10 μF SIMO3: $I_{OUT}$ = 1.8 V, $I_{OUT}$ = 100 mA, $I_{OUT}$ = 22 μF SIMO4: $I_{OUT}$ = 20 mA, $I_{OUT}$ = 10 μF Note 1 | -55          |      | 55   | mV   |

| Vout_uv          | UV accuracy                                                    | Vout falling                                                                                                                                                                                                                                                         | -8           |      | 8    | %    |

| R <sub>PD</sub>  | Output discharge resistance                                    |                                                                                                                                                                                                                                                                      |              | 100  |      | Ω    |

| IQ               | Quiescent current                                              | No load - all rails enabled                                                                                                                                                                                                                                          |              | 6    |      | μΑ   |

Note 1 Capacitance nominal before derating

# 4.7 LDO Characteristics

## 4.7.1 LDO1 Characteristics

Table 9: LDO1 electrical characteristics

| Parameter                       | Description                          | Conditions                                                                                                                                                                                                | Min  | Тур   | Max | Unit |

|---------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----|------|

| External electrical             | conditions                           |                                                                                                                                                                                                           | l    |       |     | I.   |

| V <sub>IN</sub>                 | LDO input voltage                    |                                                                                                                                                                                                           | 0.55 | 0.95  | 1.5 | V    |

| Соит                            | Output capacitance                   | Effective output capacitance                                                                                                                                                                              | 0.9  |       |     | μF   |

| I <sub>OUT_MAX</sub>            | Maximum output current               |                                                                                                                                                                                                           | 100  |       |     | mA   |

| Programmable con                | ditions                              |                                                                                                                                                                                                           |      |       |     |      |

| Vouт                            | Selectable output voltage            |                                                                                                                                                                                                           | 0.5  | 0.8   | 1.2 | V    |

| Vout_LSB                        | Output voltage programming step size |                                                                                                                                                                                                           |      | 3.125 |     | mV   |

| Electrical performa             | nce                                  |                                                                                                                                                                                                           |      |       |     |      |

| Static Parameters               |                                      |                                                                                                                                                                                                           |      |       |     |      |

| Vdropout                        | Dropout voltage                      | Vout = Vout_set - 10 mV<br>lout = lout (Max)                                                                                                                                                              |      |       | 50  | mV   |

| Vout_static_tot                 | Overall output accuracy              | Part to part variation $T_A = -40 \text{ °C to } 85 \text{ °C}$ $V_{IN} = V_{OUT} + V_{DROPOUT} \text{ to } V_{IN}$ $(Max)$ $I_{OUT} = 1 \text{ mA to } 100 \text{ mA}$ $V_{OUT} = V_{OUT} \text{ (Typ)}$ | -23  |       | 23  | mV   |

| Vout_static_ld                  | Static load regulation               | I <sub>OUT</sub> = 1 mA to I <sub>OUT_MAX</sub>                                                                                                                                                           | -6   |       | 6   | mV   |

| Dynamic Paramete                | rs                                   |                                                                                                                                                                                                           |      | •     |     | •    |

| Vout_tr_line                    | Line transient response              | VIN = VOUT + VDROPOUT + 100 mV to VIN = VOUT + VDROPOUT VOUT = Min to Max IOUT = IOUT_MAX trise = tfall = 1 us                                                                                            | -5   |       | 5   | mV   |

| VOUT_TR_LD_1mA                  | Load transient response              | IOUT = 1 mA to IOUT_MAX<br>trise = trall = 1 \mus                                                                                                                                                         | -24  |       | 24  | mV   |

| ton                             | Turn-on time                         | Time to 90 % of Vout_set lout = 0 mA                                                                                                                                                                      |      |       | 1   | ms   |

| AC Parameters                   |                                      |                                                                                                                                                                                                           | l    | 4     |     | ·    |

| PSRR <sub>10Hz_10kHz_VIN</sub>  | Power supply rejection ratio         | f = 10 Hz to 10 kHz<br>I <sub>OUT</sub> = I <sub>OUT</sub> (Max)<br>V <sub>OUT</sub> = V <sub>OUT</sub> (Typ)<br>V <sub>IN</sub> = V <sub>IN</sub> (Typ)                                                  | 40   |       |     | dB   |

| PSRR <sub>10kHz_2MHz_</sub> VIN | Power supply rejection ratio         | f = 10 kHz to 2 MHz<br>Iout = Iout (Max)<br>Vout = Vout (Typ)<br>VIN = VIN (Typ)                                                                                                                          | 29   |       |     | dB   |

| Parameter                        | Description                          | Conditions                                | Min | Тур | Max | Unit |  |

|----------------------------------|--------------------------------------|-------------------------------------------|-----|-----|-----|------|--|

| Quiescent Current Specifications |                                      |                                           |     |     |     |      |  |

| IQ_ON_0mA                        | Quiescent current, no load           | I <sub>OUT</sub> = 0 mA                   |     | 6   |     | μA   |  |

| R <sub>PD</sub>                  | Output pull-down resistance when OFF | V <sub>OUT</sub> = 500 mV<br>LDO disabled |     | 61  |     | Ω    |  |

## 4.7.2 LDO3 Characteristics

Table 10: LDO3 electrical characteristics

| Parameter                  | Description                           | Conditions                                                                                                                                               | Min  | Тур  | Max  | Unit |

|----------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| External electrical        | conditions                            | -                                                                                                                                                        |      | •    | •    |      |

| VIN                        | LDO input voltage                     |                                                                                                                                                          | 2.4  | 3.6  | 5.5  | V    |

| Соит                       | Output capacitance                    | Effective output capacitance                                                                                                                             | 0.34 |      |      | μF   |

| I <sub>OUT_MAX</sub>       | Maximum output current                | V <sub>IN</sub> > V <sub>OUT</sub> + 0.2 V                                                                                                               | 20   |      |      | mA   |

| Electrical performa        | nnce                                  | •                                                                                                                                                        |      |      |      |      |

| Vout                       | Output voltage                        | $V_{IN} \ge V_{OUT} + 0.2 \text{ V}$ $I_{OUT} = 1 \text{ mA}$                                                                                            |      | 1.8  |      | V    |

| V <sub>OUT_PP</sub>        | Output voltage part-to-part variation | $V_{IN} \ge V_{OUT} + 0.2 \text{ V}$ $I_{OUT} = 1 \text{ mA}$                                                                                            | -3   |      | 3    | %    |

| Vout_uv                    | Under voltage comparator              | 20 % below typical output voltage                                                                                                                        | 1.29 | 1.44 | 1.59 | V    |

| AC Parameters              |                                       |                                                                                                                                                          |      |      |      |      |

| PSRR10Hz_10kHz_VIN         | Power supply rejection ratio          | f = 10 Hz to 10 kHz<br>I <sub>OUT</sub> = I <sub>OUT</sub> (Max)<br>V <sub>OUT</sub> = V <sub>OUT</sub> (Typ)<br>V <sub>IN</sub> = V <sub>IN</sub> (Typ) | 30   | 40   | 60   | dB   |

| En                         | Integrated output noise               | f = 10 Hz to 100 kHz<br>lout = 1 mA                                                                                                                      |      | 180  |      | μV   |

| Dynamic Paramete           | rs                                    | <u>'</u>                                                                                                                                                 | •    |      |      |      |

| tstartup                   | Startup time                          | Time to 90 % of Vout_set lout = 0 mA                                                                                                                     |      | 1.1  |      | ms   |

| Vout_tr_ld                 | Load transient response               | 0 mA to I <sub>OUT_MAX</sub> ,<br>trise = t <sub>FALL</sub> = 1 μs                                                                                       |      | 53   |      | mV   |

| Vout_tr_line               | Line transient response               | $V_{IN} = 3.8 \text{ V to } 3.2 \text{ V}$ $I_{OUT} = 1 \text{ mA}$ $t_{RISE} = t_{FALL} = 10 \mu\text{s}$                                               |      | 5.7  |      | mV   |

| Quiescent Current          | Specifications                        |                                                                                                                                                          |      |      |      |      |

| I <sub>Q_ON_NO_LD</sub>    | Quiescent current, no load            | I <sub>OUT</sub> = 0 mA<br>in normal Iq mode                                                                                                             |      | 0.77 |      | μА   |

| I <sub>Q_ON_LO_NO_LD</sub> | Quiescent current, no load            | I <sub>OUT</sub> = 0 mA<br>in low lq mode                                                                                                                |      | 0.27 |      | μА   |

| IQ_ON_1mA                  | Quiescent current, low load           | I <sub>OUT</sub> = 1 mA                                                                                                                                  | 15   | 28   | 40   | μΑ   |

| R <sub>PD</sub>            | Output pull-down resistance when OFF  | Vout = 0.5 V                                                                                                                                             |      | 120  |      | Ω    |

| Parameter         | Description                          | Conditions                                                                                                                  | Min  | Тур | Max  | Unit |  |  |

|-------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|--|--|

| Static Parameters |                                      |                                                                                                                             |      |     |      |      |  |  |

| Vout_static_tot   | Output voltage total static accuracy | Part to part variation  TA = -40 °C to 85 °C  VIN = VOUT + VDROPOUT to  VIN (Max)  IOUT = 1 mA to 100 mA  VOUT = VOUT (Typ) | 1.75 |     | 1.86 | V    |  |  |

| VOUT_STATIC_LINE  | Static line regulation               | Vout + 0.2 V < V <sub>IN</sub> < 5.5 V,<br>I <sub>OUT</sub> = 1 mA                                                          | -0.4 |     | 0.8  | %    |  |  |

| Vout_static_ld    | Static load regulation               | V <sub>IN</sub> ≥ V <sub>OUT</sub> + 0.2 V<br>0 < lout < lout_Max                                                           | -1.5 |     | 1.5  | %    |  |  |

| Vout_static_tot_% | Output voltage total static accuracy | V <sub>IN</sub> ≥ V <sub>OUT</sub> + 0.2 V,<br>0 < T <sub>J</sub> < 85 °C                                                   | -2.7 |     | 3.1  | %    |  |  |

| VDROPOUT          | Dropout voltage                      | Vout = Vout_set - 10 mV<br>lout = lout (Max)                                                                                |      |     | 200  | mV   |  |  |

## 4.7.3 LDO4 Characteristics

Table 11: LDO4 electrical characteristics

| Parameter                      | Description                                | Conditions                                                                                                                                                      | Min  | Тур | Max | Unit |  |  |

|--------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|--|--|

| External electrical conditions |                                            |                                                                                                                                                                 |      |     |     |      |  |  |

| V <sub>IN</sub>                | LDO input voltage                          |                                                                                                                                                                 | 2.5  | 3.6 | 5.5 | V    |  |  |

| C <sub>OUT</sub>               | Output capacitance                         | Effective output capacitance                                                                                                                                    | 0.39 |     |     | μF   |  |  |

| Iout_max                       | Maximum output current                     |                                                                                                                                                                 | 100  |     |     | mA   |  |  |

| Programmable                   | conditions                                 |                                                                                                                                                                 |      |     |     |      |  |  |

| Vouт                           | Selectable output voltage                  | Step size 5 mV                                                                                                                                                  | 1.2  | 3.3 | 3.3 | V    |  |  |

| Electrical perfo               | rmance                                     |                                                                                                                                                                 |      |     | '   |      |  |  |

| Static Paramete                | ers                                        |                                                                                                                                                                 |      |     |     |      |  |  |

| Vout_static_tot                | Overall static output accuracy             | Vout = 3.3 V Part to part + temperature + static line regulation                                                                                                | -3   |     | 2.5 | %    |  |  |

| V <sub>OUT_TEMP</sub>          | Temperature dependence of V <sub>OUT</sub> | Iout = 1mA<br>Vout = Vout (Typ)                                                                                                                                 | -1   |     | 1   | %    |  |  |

| V <sub>DROPOUT</sub>           | Dropout voltage                            | Vout = Vout_set - 10 mV<br>lout = lout (Max)                                                                                                                    |      |     | 200 | mV   |  |  |

| Dynamic Param                  | neters                                     |                                                                                                                                                                 |      |     |     |      |  |  |

| tstartup                       | Startup time                               | Time to 90 % of VouT_SET lout = 0 mA                                                                                                                            |      |     | 1   | ms   |  |  |

| Vout_tr_line                   | Line transient response                    | $V_{IN} = V_{OUT} + V_{DROPOUT} + 100$ mV to $V_{IN} = V_{OUT} + V_{DROPOUT}$ $V_{OUT} = Min to Max$ $I_{OUT} = I_{OUT\_MAX}$ $t_{RISE} = t_{FALL} = 1 \ \mu s$ | -20  |     | 20  | mV   |  |  |

## **DA9098 Datasheet**

| Parameter       | Description                        | Conditions                                        | Min | Тур | Max | Unit |  |  |

|-----------------|------------------------------------|---------------------------------------------------|-----|-----|-----|------|--|--|

| Vout_tr_ld      | Load transient response            | lout = 1 mA to lout_max<br>trise = tfall = 1 \mus | -50 |     | 50  | mV   |  |  |

| Quiescent Cur   | Quiescent Current Specifications   |                                                   |     |     |     |      |  |  |

| IQ_ON_0mA       | Quiescent current, no load         | Iout = 0 mA                                       |     | 4   |     | μA   |  |  |

| R <sub>PD</sub> | Output pull-down resistance in OFF | V <sub>OUT</sub> = 0.5 V<br>LDO disabled          |     | 80  |     | Ω    |  |  |

# 4.8 ISINK - LED Driver Characteristics

**Table 12: ISINK electrical characteristics**

| Parameter               | Description                                             | Conditions                                                                        | Min   | Тур | Max  | Unit |  |  |

|-------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------|-------|-----|------|------|--|--|

| Programmable conditions |                                                         |                                                                                   |       |     |      |      |  |  |

| Іоит                    | Programmable output current range per sink              |                                                                                   | 0.05  |     | 12.8 | mA   |  |  |

| f <sub>PWM</sub>        | PWM frequency                                           |                                                                                   | 0.001 |     | 1    | kHz  |  |  |

| Electrical pe           | Electrical performance                                  |                                                                                   |       |     |      |      |  |  |

| I <sub>OUT_ACC</sub>    | Absolute output current accuracy                        | T <sub>A</sub> = 25 °C<br>V <sub>SINK</sub> = 0.2 V<br>I <sub>SINK</sub> = 3.3 mA | -2    |     | 2    | %    |  |  |

| Vouт                    | Absolute operating voltage of the sink                  |                                                                                   | 0     |     | 5.5  | V    |  |  |

| VDROPOUT                | Dropout voltage above which sink operates in regulation |                                                                                   | 0.2   |     |      | V    |  |  |

| IQ                      | Quiescent current per active current sink               |                                                                                   |       | 5   | 15   | μΑ   |  |  |

# 4.9 Power Path Management Electrical Characteristics

Table 13: Power-path management electrical characteristics

| Parameter                   | Description                    | Conditions                                                                                | Min | Тур | Max | Unit |  |  |  |

|-----------------------------|--------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|

| Programmable conditions     |                                |                                                                                           |     |     |     |      |  |  |  |

| Vsys_rng                    | VSYS output voltage            | Programmable in 100 mV steps                                                              | 3.2 |     | 4.8 | V    |  |  |  |

| Vchg_dpm_rng                | DPM voltage threshold          | Programmable in 100 mV steps                                                              | 4.2 |     | 4.9 | V    |  |  |  |

| Ivchg_in_lim_rng            | Input current limit            | Programmable in 25 mA steps                                                               | 0   |     | 600 | mA   |  |  |  |

| Electrical perfor           | mance                          |                                                                                           |     |     |     |      |  |  |  |

| VCHG_IN_DPM_ACC             | DPM voltage threshold accuracy |                                                                                           | -3  |     | 3   | %    |  |  |  |

| Ron                         | On resistance VCHG_IN to VSYS  | SYS LDO in pass-through mode,  I <sub>CHG_IN</sub> = 150 mA,  V <sub>CHG_IN</sub> = 3.6 V |     | 280 |     | mΩ   |  |  |  |

| Vsys_acc                    | VSYS static accuracy           | V <sub>SYS</sub> = 4.5 V<br>I <sub>CHG_IN</sub> = 0 to 500 mA                             | -4  |     | 4   | %    |  |  |  |

| I <sub>CHG_IN_LIM_ACC</sub> | Input current limit accuracy   | I <sub>CHG_IN_LIM</sub> = 500 mA                                                          |     | 500 | 550 | mA   |  |  |  |

# 4.10 Battery Charger Electrical Characteristics

Table 14: Battery charger electrical characteristics

| Parameter                 | Description                                       | Conditions                                                                                                                                                                            | Min   | Тур               | Max  | Unit |

|---------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------|------|------|

| Programmable cond         | itions                                            |                                                                                                                                                                                       | · ·   | ·                 |      |      |

| IBAT_DCHG_RNG             | Discharge current limit setting range             | Programmable                                                                                                                                                                          | 0.15  |                   | 2    | А    |

| VBAT_CHG                  | Charge voltage range                              | Operating in voltage regulation, programmable in 10 mV steps                                                                                                                          | 3.6   |                   | 4.65 | V    |

| I <sub>CHG</sub>          | Fast charge current range                         |                                                                                                                                                                                       | 2.5   |                   | 500  | mA   |

| I <sub>TER_5%</sub>       | Termination charge current 5 % of ICHG            |                                                                                                                                                                                       | 0.125 |                   | 25   | mA   |

| ITER_10%                  | Termination charge current 10 % of ICHG           |                                                                                                                                                                                       | 0.25  |                   | 50   | mA   |

| I <sub>TER_20%</sub>      | Termination charge current 20 % of ICHG           |                                                                                                                                                                                       | 0.5   |                   | 100  | mA   |

| ITER_35%                  | Termination charge current 35 % of ICHG           |                                                                                                                                                                                       | 0.875 |                   | 175  | mA   |

| I <sub>PRE_CHG_RNG</sub>  | Pre-charge current range                          | Note 1                                                                                                                                                                                | 0.5   |                   | 64   | mA   |

| Vrchg                     | Recharge threshold voltage range                  | V <sub>BAT</sub> below V <sub>BAT_CHG</sub> - 2<br>programmable thresholds                                                                                                            | 140   |                   | 300  | mV   |

| Vvsys_dppm_thr            | VSYS DPPM voltage threshold                       | Vsys falling, relative to Vbat<br>Programmable in 50 mV<br>steps                                                                                                                      | 100   |                   | 250  | mV   |

| VPRE_TO_FAST_CHG_THR      | Pre charge to fast charge threshold voltage range | V <sub>BAT</sub> rising<br>Programmable in 100 mV<br>steps                                                                                                                            | 2.7   |                   | 3.4  | V    |

| Electrical performan      | ce                                                |                                                                                                                                                                                       | Į.    | l                 | ļ    |      |

| Ron_chg_int               | Battery charger MOSFET on-<br>resistance          | $\begin{aligned} &\text{Measured from V}_{\text{BAT}} \text{ to V}_{\text{SYS}} \\ &\text{V}_{\text{BAT}} = 4.35 \text{ V}, \\ &\text{I}_{\text{BAT}} = 100 \text{ mA} \end{aligned}$ |       |                   | 175  | mΩ   |

| V <sub>VBAT_</sub> SM_THR | Threshold to enter the battery supplement mode    | Vvbat > Vvbat_uvlo                                                                                                                                                                    |       | VSYS<br><<br>VBAT |      | V    |

| V <sub>BAT_CHG_ACC</sub>  | Charge voltage accuracy                           | 0 °C < T <sub>J</sub> < 85 °C                                                                                                                                                         | -0.5  |                   | 0.5  | %    |

| ICHG_ACC                  | Fast charge current accuracy                      | I <sub>CHG</sub> > 5 mA<br>T <sub>A</sub> = 25 °C                                                                                                                                     | -5    |                   | 5    | %    |

| IPRE_CHG_ACC              | Pre-charge current accuracy                       | V <sub>BAT</sub> > 2 V                                                                                                                                                                | -10   |                   | 10   | %    |

| Iter_acc                  | Termination charge current accuracy               | I <sub>TER</sub> = 10 mA<br>T <sub>A</sub> = 25 °C                                                                                                                                    | -10   |                   | 10   | %    |

Note 1 See CHG\_IPRECHG\_CFG in register map

# 4.11 Battery Temperature Sensor Characteristics

Table 15: Battery temperature sensor characteristics

| Parameter              | Description                | Conditions                               | Min  | Тур  | Max  | Unit |  |  |

|------------------------|----------------------------|------------------------------------------|------|------|------|------|--|--|

| Electrical performance |                            |                                          |      |      |      |      |  |  |

| Vтемр_нот              | Hot temperature threshold  | % of V <sub>SYS</sub> ,NTC_SNS falling   | 14.5 | 15   | 15.2 | %    |  |  |

| VTEMP_WARM             | Warm threshold             | % of V <sub>SYS</sub> ,NTC_SNS falling   | 20.1 | 20.5 | 20.8 | %    |  |  |

| V <sub>TEMP_COOL</sub> | Cool threshold             | % of V <sub>SYS</sub> ,NTC_SNS rising    | 34.4 | 35   | 35.4 | %    |  |  |

| VTEMP_COLD             | Cold temperature threshold | % of V <sub>SYS</sub> , NTC_SNS rising   | 39.3 | 39.8 | 40.2 | %    |  |  |

| Voff_temp_sns          | NTC_SNS disable threshold  | % of V <sub>SYS</sub> for rising NTC_SNS | 55   |      | 60   | %    |  |  |

| ttemp_sns_deglitch     | NTC_SNS deglitch time      | NTS_SNS at any threshold                 |      | 10   |      | ms   |  |  |

## 4.12 Protection Electrical Characteristics

**Table 16: Protection electrical characteristics**

| Parameter                  | Description                                                    | Conditions                                                    | Min | Тур | Max  | Unit |

|----------------------------|----------------------------------------------------------------|---------------------------------------------------------------|-----|-----|------|------|

| Programmable of            | conditions                                                     |                                                               |     |     |      |      |

| Twarn_rng                  | Warning temperature                                            | T <sub>J,</sub><br>Programmable in 10 °C steps                | 70  |     | 100  | °C   |

| Electrical perfor          | mance                                                          |                                                               |     | •   | •    |      |