## **HA456**

120MHz, Low Power, 8x8 Video Crosspoint Switch

FN4153 Rev 7.00 September 26, 2008

The HA456 is the first 8x8 video crosspoint switch suitable for high performance video systems. Its high level of integration significantly reduces component count, board space, and cost. The crosspoint switch contains a digitally controlled matrix of 64 fully buffered switches that connect 8 video input signals to any, or all, matrix outputs. Each matrix output connects to an internal, high-speed (200V/ $\mu$ s), unity gain buffer capable of driving 400 $\Omega$  and 5pF to ±2V.

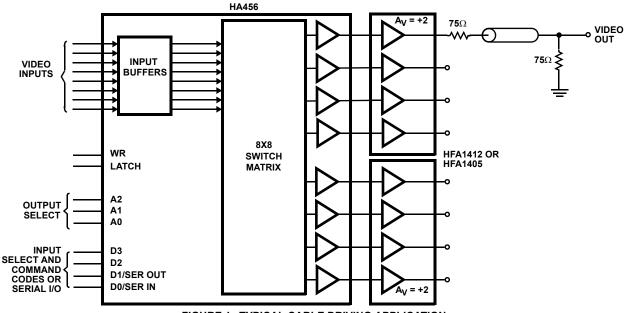

For applications requiring gain or increased drive capability, the HA456 outputs can be connected directly to two HFA1412 quad, gain of two video buffers, which are capable of driving  $75\Omega$  loads.

This crosspoint's true high impedance three-state output capability, makes it feasible to parallel multiple HA456s and form larger switch matrices.

## Ordering Information

| PART<br>NUMBER     | PART<br>MARKING | TEMP.<br>RANGE<br>(°C) | PACKAGE                 | PKG.<br>DWG.# |

|--------------------|-----------------|------------------------|-------------------------|---------------|

| HA456CM            | HA456CM         | 0 to +70               | 44 Ld PLCC              | N44.65        |

| HA456CMZ<br>(Note) | HA456CMZ        | 0 to +70               | 44 Ld PLCC<br>(Pb-free) | N44.65        |

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Features

- Fully Buffered Inputs and Outputs (A<sub>V</sub> = +1)

- · Routes Any Input Channel to Any Output Channel

- · Switches Standard and High Resolution Video Signals

- · Serial or Parallel Digital Interface

- · Expandable for Larger Switch Matrices

| • | Wide Bandwidth              | 20MHz    |

|---|-----------------------------|----------|

| • | High Slew Rate              | 200V/µs  |

| • | Differential Gain and Phase | %, 0.05° |

|   | Low Crosstalk at 10MHz      | -55dB    |

· Pb-Free Available (RoHS Compliant)

## **Applications**

- · Professional Video Switching and Routing

- · Security and Video Editing Systems

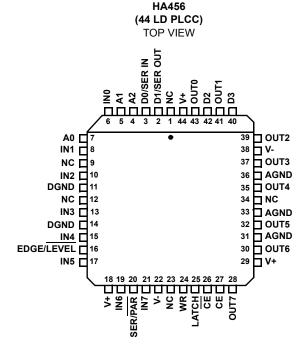

### **Pinout**

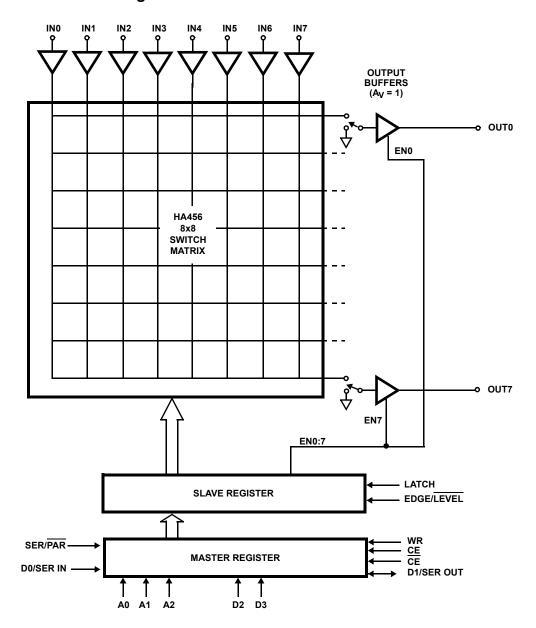

# HA456 Functional Block Diagram

# Pin Descriptions

| NAME       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC         | No connect. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D1/SER OUT | Parallel Data Bit input D1 for Parallel Programming Mode. Serial Data Output (MSB of shift register) for cascading multiple HA456s in serial programming mode. Simply connect Serial Data Out of one HA456 to Serial Data In of another HA456 to daisy chain multiple devices.                                                                                                                                                                                                                                                                                                            |

| D0/SER IN  | Parallel Data Bit Input D0 for Parallel Programming Mode. Serial Data Input (input to shift register) for serial programming mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A2, A1, A0 | Output Channel Address Bits. These inputs select the output being programmed in parallel programming mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IN0-IN7    | Analog Video Input Lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DGND       | Digital Ground. Connect both DGND pins to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

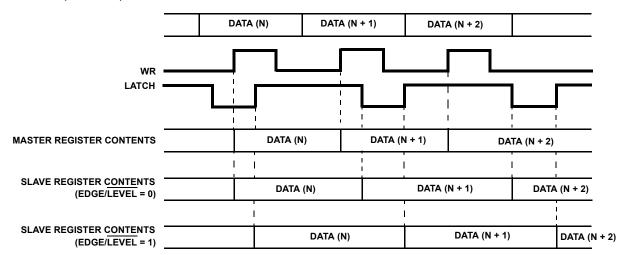

| EDGE/LEVEL | A user strapped input that defines whether synchronous channel switching is edge or level controlled. With this pin is strapped high, the slave register loads from the master register (thus changing the switch matrix state) on the rising edge of the LATCH signal. If it is strapped low (level mode), the slave register is transparent while LATCH is low, passing data directly from the master register to the switch state decoders. Strapping EDGE/LEVEL and LATCH low causes the channel switch to execute on the WR rising edge (not recommended for serial mode operation). |

| V+         | Positive Supply Voltage. Connect all V+ pins together and decouple each pin to AGND (see Figure 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SER/PAR    | A user strapped input that defines whether the serial (SER/PAR = 1) or parallel (SER/PAR = 0) digital programming interface is being utilized.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V-         | Negative Supply Voltage. Connect both V- pins together and decouple each pin to AGND (see Figure 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| WR         | WRITE Input. In serial mode, data shifts into the shift register (Master Register) LSB from SER IN on the WR rising edge. In parallel mode, the Master Register loads with D3:0 (if D3:0 = 0000 through 1000), or the appropriate action is taken (if D3:0 = 1011 through 1111), on the WR rising edge (see Table 1).                                                                                                                                                                                                                                                                     |

| LATCH      | Synchronous Channel Switch Control Input. If EDGE/LEVEL = 1, data is loaded from the Master Register to the Slave Register on the rising edge of LATCH. If EDGE/LEVEL = 0, data is loaded from the Master to the Slave Register while LATCH = 0. In parallel mode, commands 1011 through 1110 execute asynchronously, on the WR rising edge, regardless of the state of LATCH or EDGE/LEVEL. Parallel mode command 1111 executes a software "Latch" (see Table 1).                                                                                                                        |

| CE         | $\overline{\text{Chip Enable}}$ . When $\overline{\text{CE}} = 0$ and $\overline{\text{CE}} = 1$ , the WR line is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CE         | Chip Enable. When $\overline{CE} = 0$ and $CE = 1$ , the WR line is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OUT7-OUT0  | Analog Video Outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AGND       | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D3         | Parallel Data Bit Input D3 when SER/PAR = 0. D3 is unused with serial programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D2         | Parallel Data Bit Input D2 when SER/PAR = 0. D2 is unused with serial programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## **Absolute Maximum Ratings**

| Supply Voltage (V+ to V-)                              |

|--------------------------------------------------------|

| Positive Supply Voltage (V+) Referred to AGND 6V       |

| Negative Supply Voltage (V-) Referred to AGND6V        |

| DGND Voltage AGND ±1V                                  |

| Analog Input Voltage                                   |

| Digital Input Voltage (V+ + 0.3V) to (DGND - 0.3V)     |

| ESD Rating                                             |

| Human Body Model (Per MIL-STD-883 Method 3015.7) 1.5kV |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)             | θ <sub>JA</sub> (°C/W) |

|--------------------------------------------------|------------------------|

| PLCC Package                                     | 47                     |

| Maximum Junction Temperature                     |                        |

| Maximum Storage Temperature Range65              | °C to +150°C           |

| Pb-free reflow profile                           | ee link below          |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                        |

### **Operating Conditions**

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTE:

1. θ<sub>JA</sub> is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

**Electrical Specifications**  $V_{SUPPLY} = \pm 5V$ , AGND = DGND = 0V,  $R_L = 400\Omega$  (Note 2), Unless Otherwise Specified.

| PARAMETER                                                                       | TEST CONDITIONS                                              | TEST<br>LEVEL<br>(Note 3) | TEMP<br>(°C) | MIN<br>(Note 7) | TYP   | MAX<br>(Note 7) | UNITS             |

|---------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------|--------------|-----------------|-------|-----------------|-------------------|

| Voltage Gain                                                                    | V <sub>IN</sub> = -1.5V to +1.5V, Worst Case                 | Α                         | 25           | 0.990           | 0.996 | 1.00            | V/V               |

|                                                                                 | Switch Configuration                                         | Α                         | Full         | 0.988           | 0.995 | 1.00            |                   |

| Channel-to-Channel Gain Mismatch                                                |                                                              | Α                         | 25           | -               | 0.001 | 0.004           | V/V               |

|                                                                                 |                                                              | Α                         | Full         | -               | 0.001 | 0.005           |                   |

| Supply Current                                                                  | All Outputs Enabled, R <sub>L</sub> = Open,                  | Α                         | 25           | -               | 68    | 80              | mA                |

|                                                                                 | V <sub>IN</sub> = 0V,<br>Total for All V+ (3) or V- (2) Pins | Α                         | Full         | -               | 71    | 83              |                   |

| Disabled Supply Current                                                         | All Outputs Disabled, R <sub>L</sub> = Open,                 | Α                         | 25           | -               | 47    | 65              | mA                |

|                                                                                 | Total for All V+ (3) or V- (2) Pins                          | Α                         | Full         | -               | 47    | 67              |                   |

| Input Voltage Range                                                             |                                                              | Α                         | Full         | ±2              | ±2.5  | -               | ٧                 |

| Analog Input Current                                                            | V <sub>IN</sub> = 0V                                         | Α                         | Full         | -               | 1.6   | 12              | μA                |

| Input Noise ( $R_S = 75\Omega$ )                                                | DC to 40MHz                                                  | В                         | 25           | -               | 0.15  | -               | mV <sub>RMS</sub> |

|                                                                                 | ≥10kHz                                                       | В                         | 25           | -               | 22    | -               | nV/√Hz            |

| Analog Input Resistance                                                         | DC                                                           | С                         | 25           | -               | 4     | -               | ΜΩ                |

| Analog Input Capacitance (Input Connected to One Output or All Outputs, Note 6) |                                                              | В                         | 25           | -               | 3.2   | -               | pF                |

| Output Offset Voltage                                                           | V <sub>IN</sub> = 0V, Worst Case Switch                      | Α                         | 25           | -18             | -6.5  | 5               | mV                |

|                                                                                 | Configuration                                                | Α                         | Full         | -20             | -7.5  | 6               |                   |

| Channel-to-Channel Offset Voltage                                               |                                                              | Α                         | 25           | -               | 2     | 11              | mV                |

| Mismatch                                                                        |                                                              | Α                         | Full         | -               | 4     | 13              |                   |

| Offset Voltage Drift                                                            |                                                              | В                         | Full         | -               | 20    | -               | μV/°C             |

| Output Voltage Swing                                                            | V <sub>IN</sub> = ±2.5V                                      | Α                         | 25           | ±2.2            | ±2.48 | -               | V                 |

|                                                                                 |                                                              | Α                         | Full         | ±2.1            | ±2.47 | -               | V                 |

| Output Resistance                                                               | Enabled, DC                                                  | В                         | 25           | -               | 0.25  | -               | Ω                 |

| Output Leakage Current                                                          | All Outputs Disabled,                                        | Α                         | 25           | -               | 0.2   | 5               | μA                |

| (Including D1/SER OUT)                                                          | V <sub>OUT</sub> = 2.5V                                      | Α                         | Full         | -               | 1     | 10              | μA                |

| Output Resistance                                                               | Output Disabled                                              | Α                         | 25           | 0.6             | 15    | -               | ΜΩ                |

## **Electrical Specifications** $V_{SUPPLY} = \pm 5V$ , AGND = DGND = 0V, $R_L = 400\Omega$ (Note 2), Unless Otherwise Specified. (Continued)

| PARAMETER                                                | TEST CONDITIONS                                    | TEST<br>LEVEL<br>(Note 3) | TEMP<br>(°C) | MIN<br>(Note 7) | TYP  | MAX<br>(Note 7) | UNITS |

|----------------------------------------------------------|----------------------------------------------------|---------------------------|--------------|-----------------|------|-----------------|-------|

| Output Capacitance<br>(Output Disabled)                  |                                                    | В                         | 25           | -               | 3.5  | -               | pF    |

| Power Supply Rejection Ratio                             | DC, $V_S = \pm 4.5V$ to $\pm 5.5V$ , $V_{IN} = 0V$ | Α                         | Full         | 45              | 53   | -               | dB    |

| Digital Input Current (Note 5)                           | V <sub>IN</sub> = 0V or 5V                         | Α                         | Full         | -               | 1    | 1               | μA    |

| Digital Input Low Voltage                                |                                                    | Α                         | Full         | -               | -    | 0.8             | V     |

| Digital Input High Voltage                               |                                                    | Α                         | 25           | 2.0             | -    | -               | V     |

|                                                          |                                                    | Α                         | Full         | 2.2             | -    | -               | V     |

| SER OUT Logic Low Voltage                                | Serial Mode, I <sub>OL</sub> = 1.6mA               | Α                         | Full         | -               | -    | 0.4             | V     |

| SER OUT Logic High Voltage                               | Serial Mode, I <sub>OH</sub> = -0.4mA              | Α                         | Full         | 3.0             | -    | -               | V     |

| AC CHARACTERISTICS (Note 4)                              |                                                    | Į.                        |              | I               |      |                 |       |

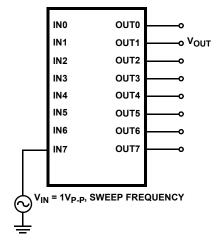

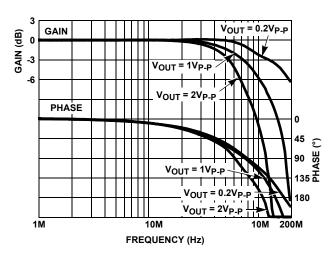

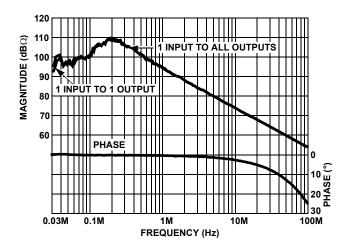

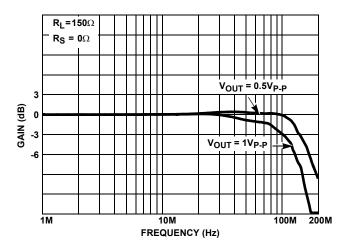

| -3dB Bandwidth (Note 6)                                  | $C_L = 5pF, V_{IN} = 200mV_{P-P}$                  | В                         | 25           | -               | 120  | -               | MHz   |

|                                                          | $C_L = 5pF, V_{IN} = 1V_{P-P}$                     | В                         | 25           | -               | 70   | -               | MHz   |

|                                                          | $C_L = 5pF, V_{IN} = 2V_{P-P}$                     | В                         | 25           | -               | 50   | -               | MHz   |

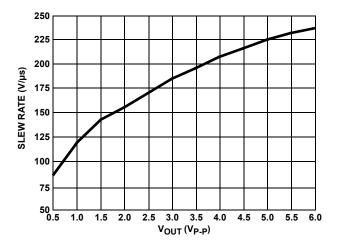

| Slew Rate (Note 6)                                       | $V_{OUT} = 4V_{P-P}$                               | В                         | 25           | -               | 200  | -               | V/µs  |

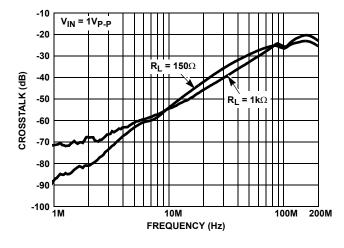

| All Hostile Crosstalk (Note 6)                           | 10MHz, $V_{IN} = 1V_{P-P}$ , $R_L = 1k\Omega$      | В                         | 25           | -               | -55  | -               | dB    |

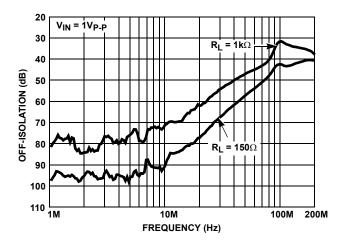

| All Hostile Off-Isolation (Note 6)                       | 10MHz, V <sub>IN</sub> = 1V <sub>P-P</sub>         | В                         | 25           | -               | 70   | -               | dB    |

| Differential Phase                                       | NTSC or PAL, $R_L = 1k\Omega$                      | В                         | 25           | -               | 0.05 | -               | ۰     |

|                                                          | NTSC or PAL, $R_L \ge 10k\Omega$                   | В                         | 25           | -               | 0.05 | -               | ۰     |

| Differential Gain                                        | NTSC or PAL, $R_L = 1k\Omega$                      | В                         | 25           | -               | 0.05 | -               | %     |

|                                                          | NTSC or PAL, $R_L \ge 10 k\Omega$                  | В                         | 25           | -               | 0.02 | -               | %     |

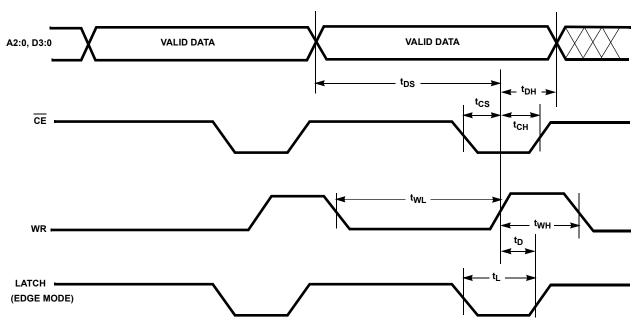

| TIMING CHARACTERISTICS (See Figure 3 for                 | More Information)                                  |                           |              |                 |      |                 |       |

| Write Pulse Width High (t <sub>WH</sub> )                |                                                    | А                         | Full         | 20              | -    | -               | ns    |

| Write Pulse Width Low (t <sub>WL</sub> )                 |                                                    | Α                         | Full         | 20              | -    | -               | ns    |

| Chip-Enable Setup Time to Write (t <sub>CS</sub> )       |                                                    | Α                         | Full         | 5               | -    | -               | ns    |

| Chip-Enable Hold Time From Write (t <sub>CH</sub> )      |                                                    | Α                         | Full         | 5               | -    | -               | ns    |

| Data and Address Setup Time to Write (t <sub>DS</sub> )  | Parallel Mode                                      | Α                         | Full         | 20              | -    | -               | ns    |

|                                                          | Serial Mode                                        | Α                         | Full         | 20              | -    | -               | ns    |

| Data and Address Hold Time from Write (t <sub>DH</sub> ) |                                                    | Α                         | Full         | 25              | -    | -               | ns    |

| Latch Pulse Width (t <sub>L</sub> )                      |                                                    | Α                         | Full         | 40              | -    | -               | ns    |

| Latch Delay From Write (t <sub>D</sub> )                 |                                                    | Α                         | Full         | 40              | -    | -               | ns    |

| LATCH Edge to Output Disabled (t <sub>OFF</sub> )        | Serial Mode                                        | В                         | Full         | -               | 30   | -               | ns    |

| LATCH Edge to Output Enabled (t <sub>ON</sub> )          | Serial Mode                                        | В                         | Full         | -               | 185  | -               | ns    |

| Output Break-Before-Make Delay (ton - toff)              | Serial Mode                                        | В                         | Full         | -               | 155  | -               | ns    |

#### NOTES:

- 2. For the lowest crosstalk, and the best composite video performance, use  $R_L \geq 1 k \Omega$

- 3. Test Level: A. Production Tested; B. Typical or Established Limit Based on Characterization; C. Design Typical for Information Only.

- 4. See AC Test Circuits (Figure 6 through Figure 9).

- 5. Excludes D1/SER OUT which is a bidirectional terminal and thus falls under the higher Output Leakage limit.

- 6. See "Typical Performance Curves" beginning on page 11 for more information.

- 7. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

## Application Information

#### **HA456 Architecture**

The HA456 video crosspoint switch consists of 64 switches in an 8x8 grid (see Figure 1). Each input is fully buffered and presents a constant input capacitance whether the input connects to one output or all 8 outputs. This yields consistent input termination impedances regardless of the switch configuration. The 8 matrix outputs are followed by 8 unity gain, wideband, tristatable buffers optimized for driving  $400\Omega$  and 5pF loads. The output disable function is useful for multiplexing two or more HA456s to create a larger input matrix (e.g., two multiplexed HA456s yield a 16x8 crosspoint).

The HA456 outputs can be disabled individually or collectively under software control. When disabled, an output enters a high-impedance state. In multichip parallel applications, the disable function prevents inactive outputs from loading lines driven by other devices. Disabling an unused output also reduces power consumption.

The HA456 outputs connect easily to two HFA1412 quad, gain-of-two buffers when  $75\Omega$  loads must be driven.

#### Power-On RESET

The HA456 has an internal power-on reset (POR) circuit that disables all outputs at power-up, and presets the switch matrix so that all outputs connect to INO. In parallel mode, the desired switch state may be programmed before the outputs are enabled. In serial mode, all outputs are connected to GND each time they are enabled, so switch state programming must occur after the output is enabled.

## Digital Interface

The desired switch state can be loaded using a 7-bit parallel interface mode or 32-bit serial interface mode (see Tables 1 through 3). All actions associated with the WR line occur on its rising edge. The same is true for the LATCH line if

EDGE/LEVEL = 1. Otherwise, the Slave Register updates asynchronously (while LATCH=0, if EDGE/LEVEL = 0). WR is logically AND'ed with CE and CE to allow active high or active low chip enable.

#### 7-Bit Parallel Mode

In the parallel programming mode (SER/PAR = 0), the 7 control bits (A2:0 and D3:0) typically specify an output channel (A2:0) and the corresponding action to be taken (D3:0). Command codes are available to enable or disable all outputs, or individual outputs, as shown in Table 1. Each output has 4-bit Master and Slave Registers associated with it that hold the output's currently selected input address (defined by D3:0). The input address (if applicable) is loaded into the Master Register on the rising edge of WR. If the HA456 is in level mode, and if LATCH = 0 (asynchronous switching), then the input address flows through the transparent Slave Register and the output immediately switches to the new input. For synchronous switching on the rising edge of LATCH, strap the HA456 for edge mode, program all the desired switch connections, and then drive an inverted pulse on the LATCH input. Note: Operations defined by commands 1011 - 1111 occur asynchronously on the WR rising edge, without regard for the state of LATCH or EDGE/LEVEL.

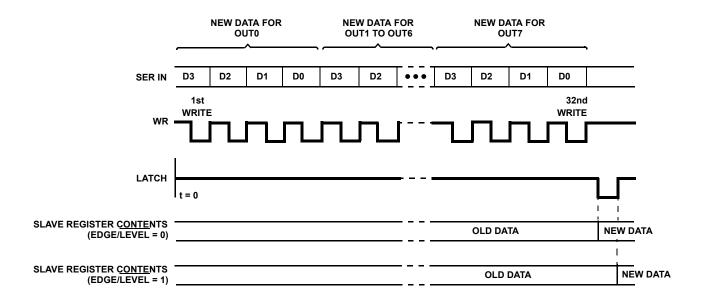

#### 32-Bit Serial Mode

In the serial programming mode, all master registers are loaded with data, making it unnecessary to specify an output address (A2:0). The input data format is D3-D0, starting with OUT0 and ending with OUT7 for 32 total bits (i.e., first bit shifted in is D3 for OUT0, and 32nd bit shifted in is D0 for OUT7). Only codes 0000 through 1010 are valid serial mode commands. Code 1010 disables an individual output, while code 1001 enables it. After data is shifted into the 32-bit Master Register, it transfers to the Slave Register on the rising edge of the LATCH line (Edge mode), or when LATCH = 0 (Level mode, see Figure 5).

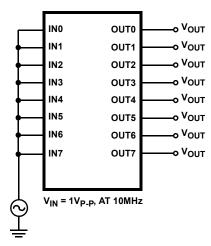

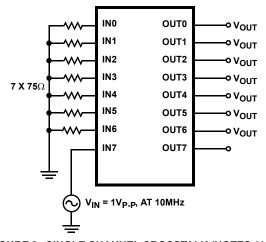

FIGURE 1. TYPICAL CABLE DRIVING APPLICATION

#### TABLE 1. PARALLEL INTERFACE COMMANDS

| A2:0                                               | D3:0         | ACTION                                                                                                                                                                                                                   |

|----------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Selects                                            | 0000 to 0111 | Connect the input defined by D3:0 to the output selected by A2:0. Doesn't enable a disabled output.                                                                                                                      |

| Output<br>Being                                    | 1000         | Connect the output selected by A2:0 to GND. Doesn't enable a disabled output.                                                                                                                                            |

| Programmed                                         | 1011         | Asynchronously disable the single output selected by A2:0, and leave the Master Register unchanged.                                                                                                                      |

|                                                    | 1100         | Asynchronously enable the single output selected by A2:0, and leave the Master Register unchanged.                                                                                                                       |

| Address                                            | 1101         | Asynchronously disable all outputs, and leave the Master Register unchanged.                                                                                                                                             |

| Inputs are<br>Irrelevant for<br>These<br>Functions | 1110         | Asynchronously enable all outputs, and leave the Master Register unchanged.                                                                                                                                              |

|                                                    | 1111         | Send a Software "Latch" pulse to the Slave Register to load it from the Master Register, iff, the LATCH input = 1. If the LATCH input = 0, then this command is a NOP. The Master Register is unchanged by this command. |

|                                                    | 1001 or 1010 | Do not use these codes in the parallel programming mode. These codes are for serial programming only.                                                                                                                    |

#### **TABLE 2. SERIAL INTERFACE COMMANDS**

| D3:0         | ACTION                                                                                                                                                                                                   |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000 to 0111 | Connect the output to the input channel defined by D3:0. Doesn't enable a disabled output.                                                                                                               |

| 1000         | Connect the output to GND. Doesn't enable a disabled output.                                                                                                                                             |

| 1001         | Enable the output and connect it to GND. The default power-up state is all outputs disabled, so use this code to enable outputs after power is applied, but before programming the switch configuration. |

| 1010         | Disable the output. The output is no longer associated with any input channel; the desired input must be redefined after re enabling the output.                                                         |

| 1011 to 1111 | Do not use these codes in the serial programming mode.                                                                                                                                                   |

#### TABLE 3. DEFINITION OF DATA AND ADDRESS BIT FUNCTIONS

| SER/PAR | D3 | D2                     | D1                     | D0                     | A2:0              | COMMENT                                               |

|---------|----|------------------------|------------------------|------------------------|-------------------|-------------------------------------------------------|

| Н       | X  | Х                      | Serial Data<br>Output  | Serial Data Input      | Х                 | 32-Bit Serial Mode                                    |

| L       | Н  | Parallel Data<br>Input | Parallel Data<br>Input | Parallel Data<br>Input | Output<br>Address | Parallel Mode; D2:0 define the command to be executed |

| L       | L  | Parallel Data<br>Input | Parallel Data<br>Input | Parallel Data<br>Input | Output<br>Address | Parallel Mode; D2:0 define the Input<br>Channel       |

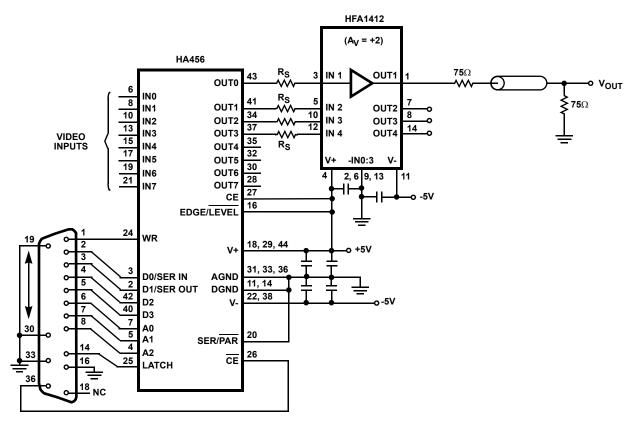

Figure 2 shows a typical application of the HA456 with HFA1412 quad, gain-of-two buffers at the outputs to drive  $75\Omega$  loads. This application shows the HA456 digital-switch control interface set up in the 7-bit parallel mode. The HA456 uses 7 data lines and 3 control lines (WR,  $\overline{\text{CE}}$  and LATCH).

The input/output information is presented to the chip at A2:0 and D3:0 by a parallel printer port. The data is stored in the Master Registers on the rising edge of WR. When the LATCH line goes high, the switch configuration loads into the Slave Registers, and all 8 outputs reconfigure at the same time. Each 7-bit word updates only one output at a time.

If several outputs are to be updated, the data is individually loaded into the Master Registers. Then, a single LATCH pulse can reconfigure all channels simultaneously.

An IBM compatible PC loads the programming data into the HA456 via its parallel port (LPT1) using a simple BASIC program.

NOTE: All decoupling capacitors  $0.1\mu F$  Ceramic (1 per supply pin). For lowest crosstalk, connect unused pins to GND use  $R_S$  to tune the overall output response.

FIGURE 2. TYPICAL HIGH PERFORMANCE, PARALLEL MODE APPLICATION CIRCUIT (SEE FIGURE 18)

## Waveforms

FIGURE 3. DIGITAL TIMING REQUIREMENTS

# Waveforms (Continued)

FIGURE 4. PARALLEL PROGRAMMING MODE OPERATION (SER/PAR = 0)

FIGURE 5. SERIAL PROGRAMMING MODE OPERATION (SER/PAR = 1)

#### AC Test Circuits

FIGURE 6. -3dB BANDWIDTH (NOTES 8 thru 11)

FIGURE 7. ALL HOSTILE OFF-ISOLATION (NOTES 11 thru 13)

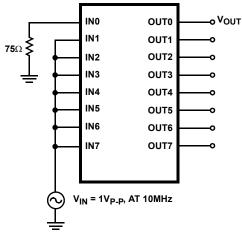

FIGURE 8. SINGLE CHANNEL CROSSTALK (NOTES 11, 14 thru 17)

FIGURE 9. ALL HOSTILE CROSSTALK (NOTES 11, 16, 18 thru 20)

#### NOTES:

- 8. Program the desired input to output combination (e.g., IN7 to OUT1).

- 9. Enable the selected output(s).

- 10. Drive the selected input with  $V_{IN}$ , and measure the -3dB frequency at the selected output ( $V_{OUT}$ ).

- 11. Load all outputs with the desired  $R_L$ .

- 12. Disable all outputs.

- 13. Drive all inputs with  $V_{IN}$  and measure  $V_{OUT}$  at any output; isolation (in dB) = -20log<sub>10</sub> ( $V_{OUT}/V_{IN}$ ).

- 14. Drive  $V_{\mbox{\scriptsize IN}}$  on one input which connects to one output (e.g., IN7 to OUT7).

- 15. Terminate all other inputs to GND.

- 16. Enable all outputs.

- 17. Measure  $V_{OUT}$  at any undriven output; crosstalk (in dB) =  $20log_{10}$  ( $V_{OUT}/V_{IN}$ ).

- 18. Terminate one input to GND, and connect that input to a single output (e.g., IN0 to OUT0).

- 19. Drive the other seven inputs with V<sub>IN</sub>, and connect these active inputs to the remaining seven outputs.

- 20. Measure  $V_{OUT}$  at the quiescent output; crosstalk (in dB) =  $20log_{10}$  ( $V_{OUT}/V_{IN}$ ).

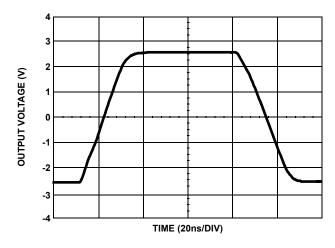

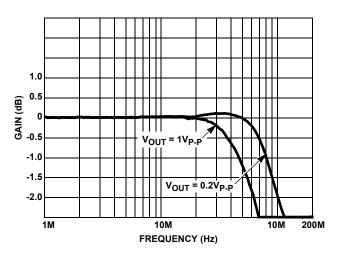

# **Typical Performance Curves** $V_{SUPPLY} = \pm 5V$ , $T_A = +25^{\circ}C$ , $R_L = 400\Omega$ , Unless Otherwise Specified.

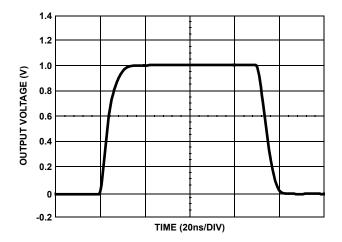

FIGURE 10. SMALL SIGNAL PULSE RESPONSE

FIGURE 11. LARGE SIGNAL PULSE RESPONSE

FIGURE 12. FREQUENCY RESPONSE

FIGURE 13. GAIN FLATNESS

FIGURE 14. ALL HOSTILE CROSSTALK

FIGURE 15. ALL HOSTILE OFF-ISOLATION

# Typical Performance Curves V<sub>SUPPLY</sub> = ±5V, T<sub>A</sub> = +25°C, R<sub>L</sub> = 400Ω, Unless Otherwise Specified. (Continued)

FIGURE 16. SLEW RATE vs  $V_{\mbox{OUT}}$

FIGURE 17. INPUT IMPEDANCE vs FREQUENCY

FIGURE 18. FREQUENCY RESPONSE OF HA456-HFA1412 COMBINATION (PER FIGURE 2)

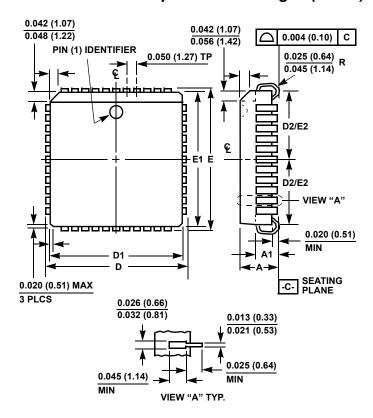

## Plastic Leaded Chip Carrier Packages (PLCC)

N44.65 (JEDEC MS-018AC ISSUE A)

44 LEAD PLASTIC LEADED CHIP CARRIER PACKAGE

|        | INCHES |       | MILLIN |         |      |

|--------|--------|-------|--------|---------|------|

| SYMBOL | MIN    | MAX   | MIN    | MIN MAX |      |

| Α      | 0.165  | 0.180 | 4.20   | 4.57    | -    |

| A1     | 0.090  | 0.120 | 2.29   | 3.04    | -    |

| D      | 0.685  | 0.695 | 17.40  | 17.65   | -    |

| D1     | 0.650  | 0.656 | 16.51  | 16.66   | 3    |

| D2     | 0.291  | 0.319 | 7.40   | 8.10    | 4, 5 |

| Е      | 0.685  | 0.695 | 17.40  | 17.65   | -    |

| E1     | 0.650  | 0.656 | 16.51  | 16.66   | 3    |

| E2     | 0.291  | 0.319 | 7.40   | 8.10    | 4, 5 |

| N      | 4      | 4     | 4      | 6       |      |

Rev. 2 11/97

#### NOTES:

- Controlling dimension: INCH. Converted millimeter dimensions are not necessarily exact.

- 2. Dimensions and tolerancing per ANSI Y14.5M-1982.

- Dimensions D1 and E1 do not include mold protrusions. Allowable mold protrusion is 0.010 inch (0.25mm) per side. Dimensions D1 and E1 include mold mismatch and are measured at the extreme material condition at the body parting line.

- 4. To be measured at seating plane -C- contact point.

- 5. Centerline to be determined where center leads exit plastic body.

- 6. "N" is the number of terminal positions.

© Copyright Intersil Americas LLC 2003-2008. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>