## Features

- Operates from a 2.7V to 5.25V supply

- Five programmable, current-mode, step-down converters

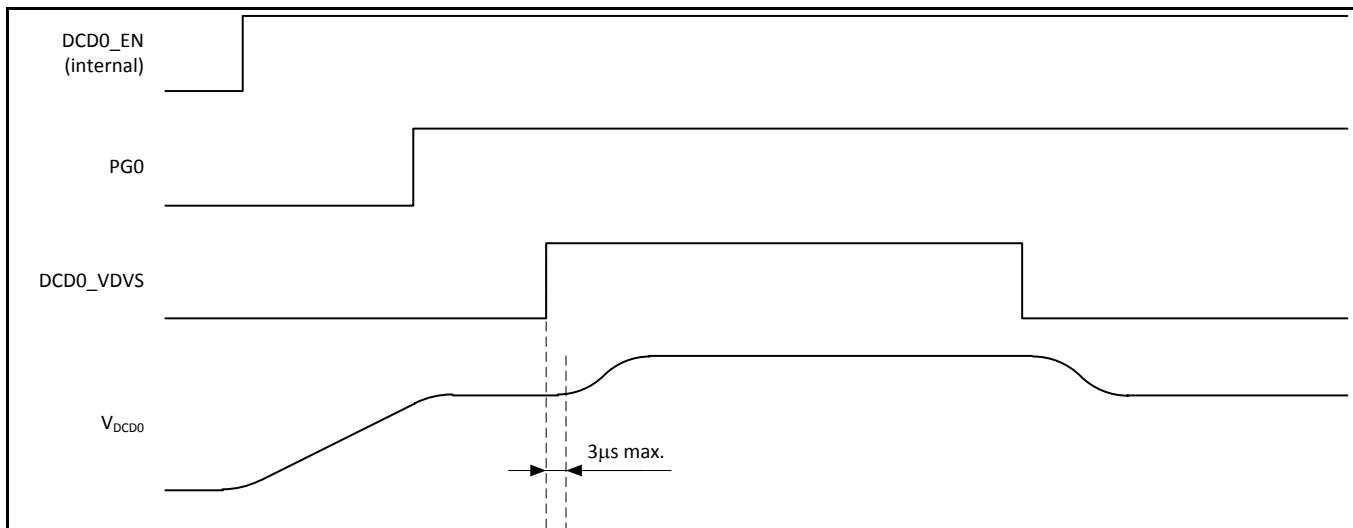

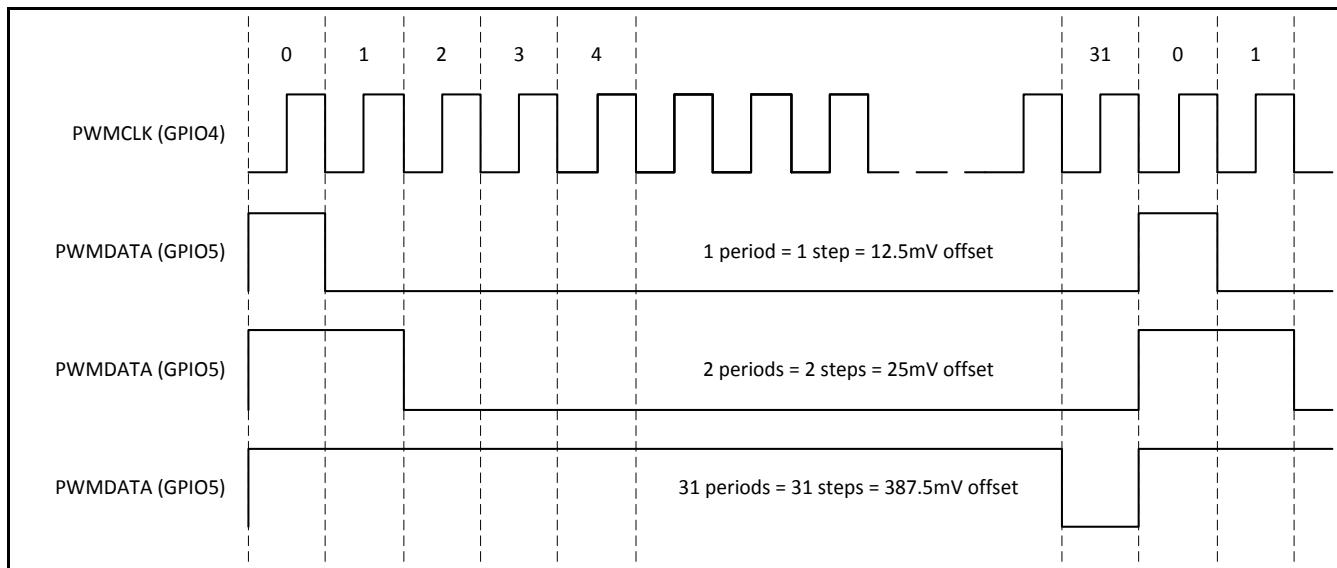

- Dynamic voltage scaling (12.5mV steps)

- Automatic PWM/PFM transition at light load

- 0.75V to 3.3V software programmable output voltage range

- Two converters with 1.5A output current

- One converter with 5A output current

- One 10A or two 5A output current converters

- Remote voltage sensing

- Support for external power modules to increase DCD1 rail output current up to 20A

- 11 programmable general purpose LDOs

- Eight 200mA, and three 160mA capable LDOs

- DCD0 or DCD1 Tracking LDO

- 1.0V to 5.25V input voltage range

- 0.75V to 3.3V software programmable output voltage range

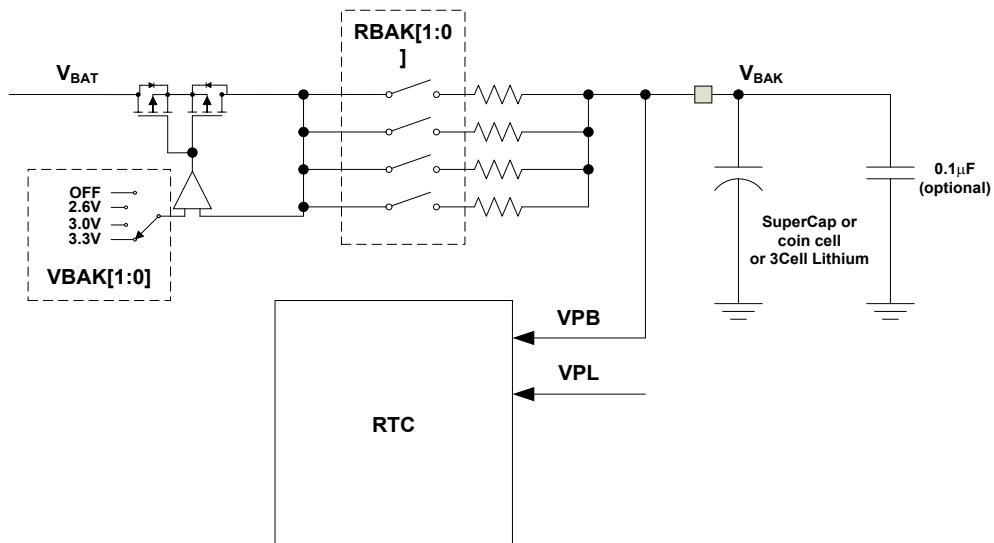

- Always-on LDO for RTC with coin cell/SuperCap charging capability

- Low power RTC module

- Counts seconds, minutes, hours, day, date, month and year

- 10-bit ADC

- Host interface and system management

- Interrupt controller with mask-able interrupts,

- Reset function

- Power good monitoring

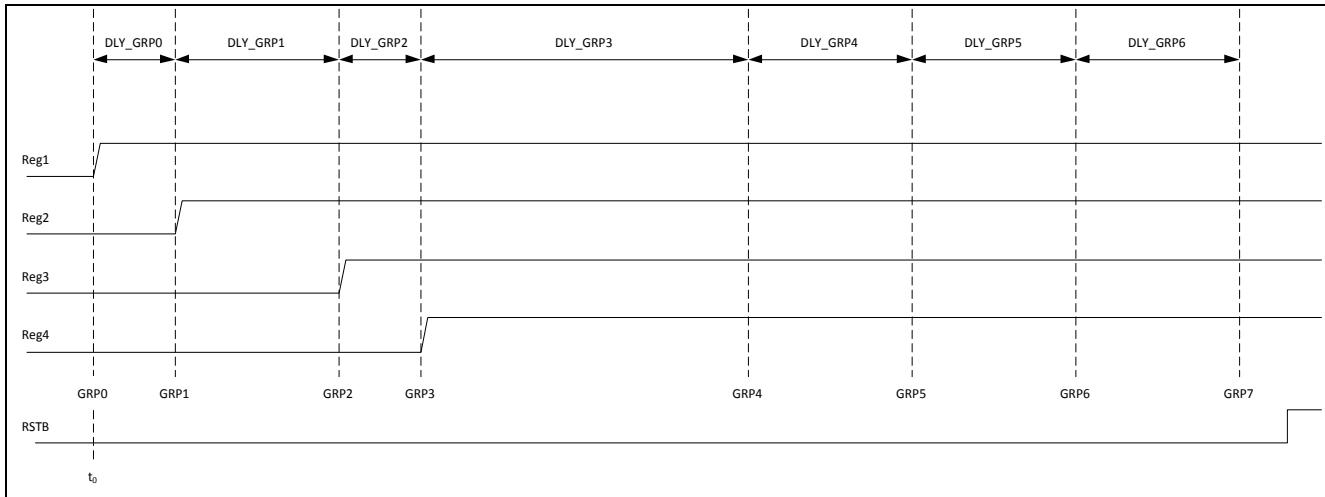

- Programmable sequencing of output rails

- High speed I<sup>2</sup>C interface, 3.4Mbit/s

- Eight programmable GPIOs

- 84-lead 7mm x 7mm x 0.8mm dual-row QFN package

## Applications

- Tablet PCs

- ClamShell

- SoC power management

## Description

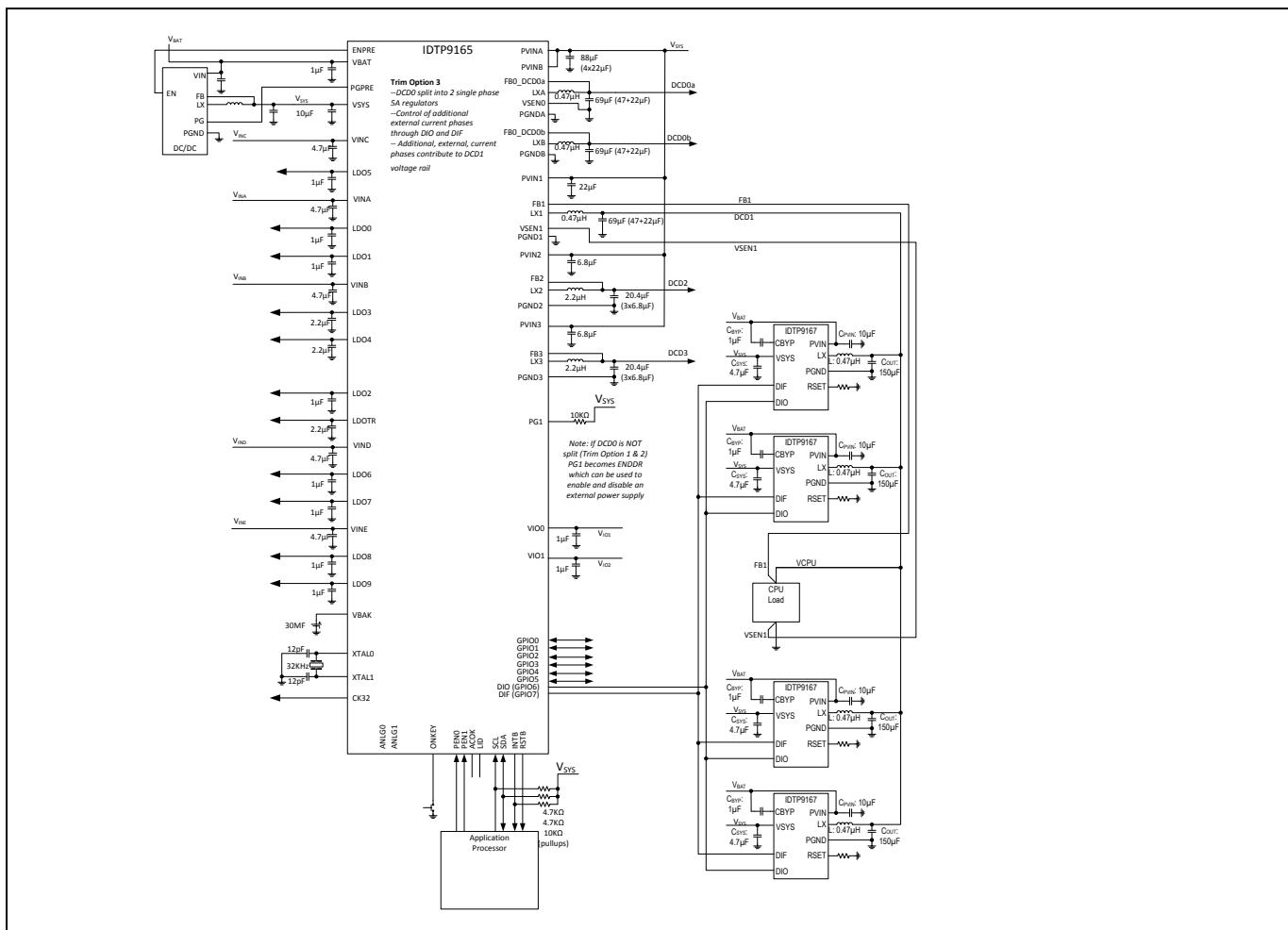

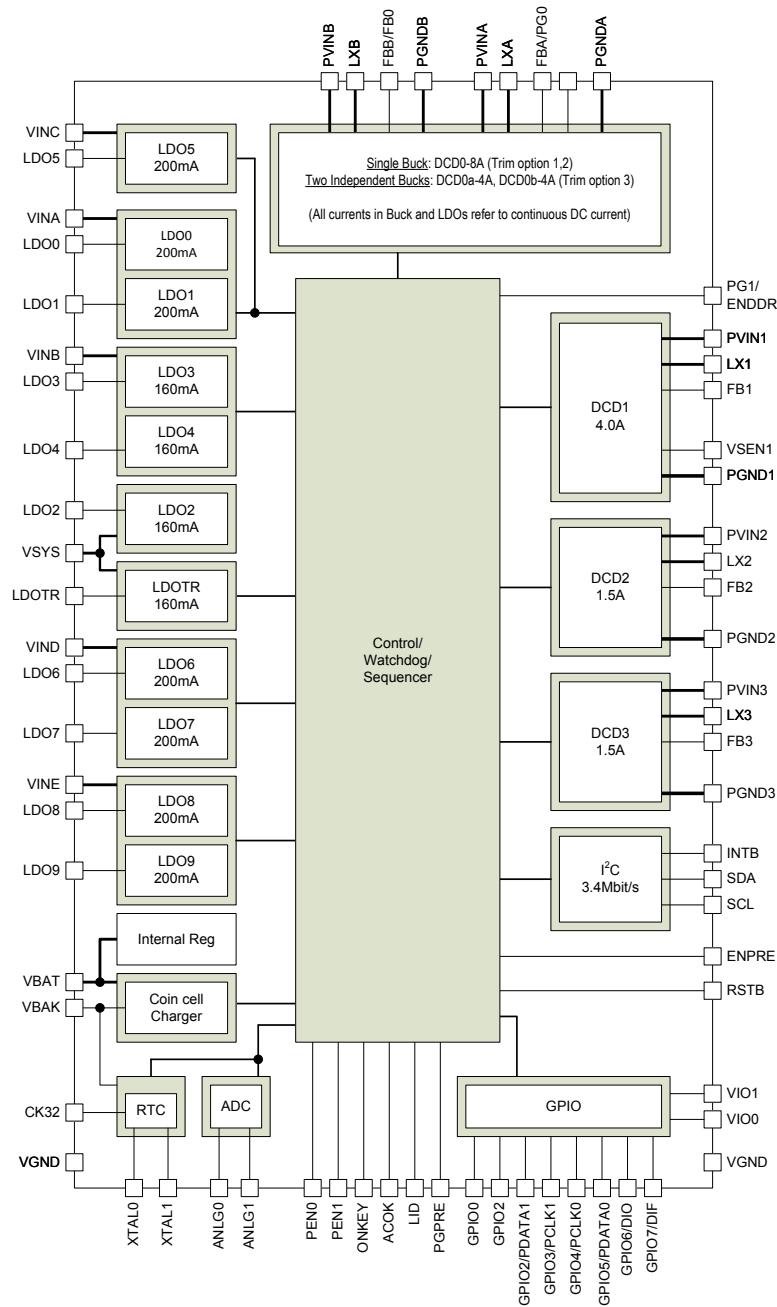

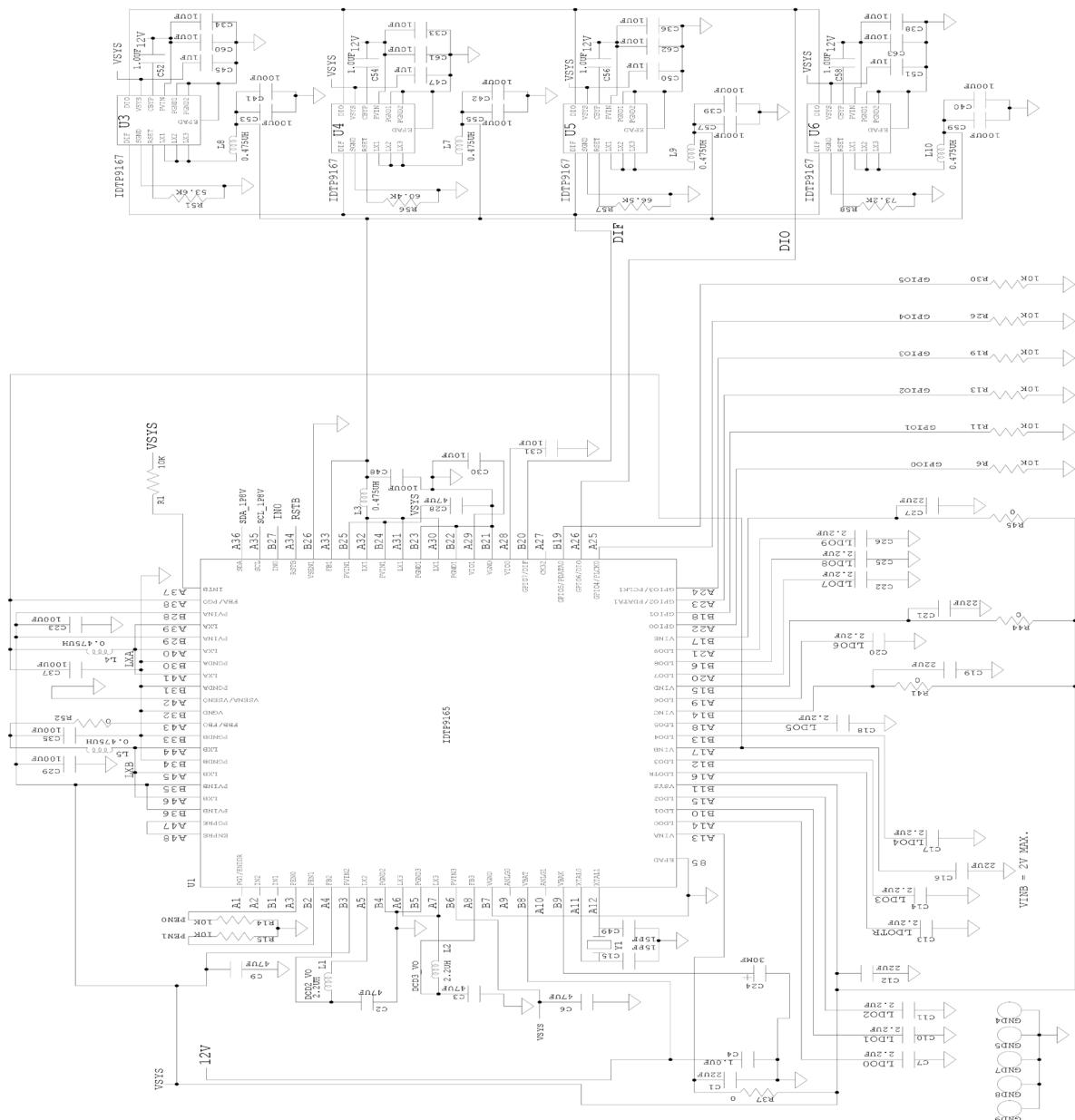

IDTP9165 is a programmable, multiple channel power management IC (PMIC). It includes 5 integrated, synchronous, step-down DC/DC regulators (DCD0a, DCD0b, DCD1 through DCD3), 11 LDOs (LDO0 through LDO9, and LDOTR), a Real Time Clock (RTC), a 10-bit ADC, eight GPIOs (GPIO0 through GPIO7), and a high speed I<sup>2</sup>C interface (I<sup>2</sup>C bus address: 0x4F). The product is ideal for Tablet PCs and other multi rail applications and is specifically designed to support the power management requirements of quad-core processor platforms.

The PMIC DC/DC regulators can support the output current requirements for the CPU (DCD0) and SOC (DCD1) of the application processor with up to 10A and 5A, respectively. The output voltages are programmable from 0.7V to 1.5V.

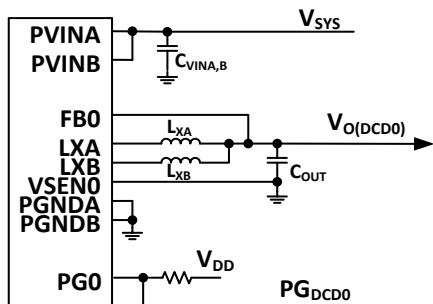

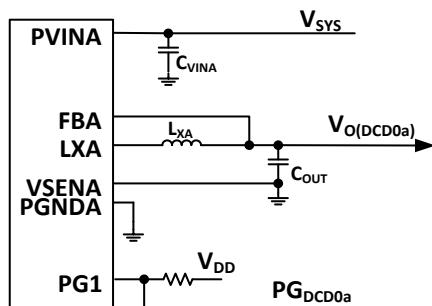

DCD0 can be configured as a dual-phase, step-down regulator or as two single-phase regulators (DCD0a and DCD0b). Both DCD0 and DCD1 offer remote sensing of the rail voltage and dynamic voltage scaling (DVS) in 12.5mV steps. The DVS set output voltage slew rate is software adjustable. Furthermore, DCD1 supports the addition of external power modules (IDTP9167) to increase the output current to over 20A.

There are two step-down regulators (DCD2, DCD3) with output currents of up to 1.5A. Those regulators are output voltage software adjustable in 12.5mV steps. All step down switching regulators are current-mode controlled with a switching frequency of 2.1MHz.

Also integrated in the IDTP9165 are 11 software programmable LDOs with a wide output voltage range and with output currents capabilities up to 280mA. All LDOs are low noise, high PSRR, and low dropout regulators.

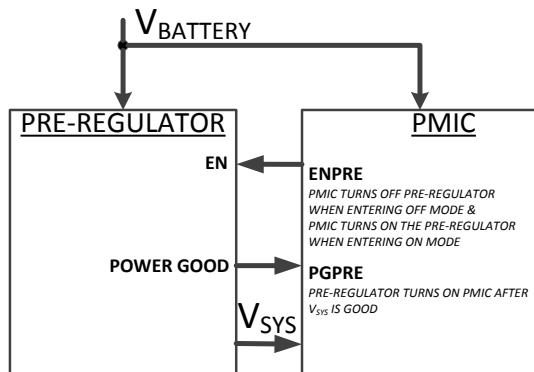

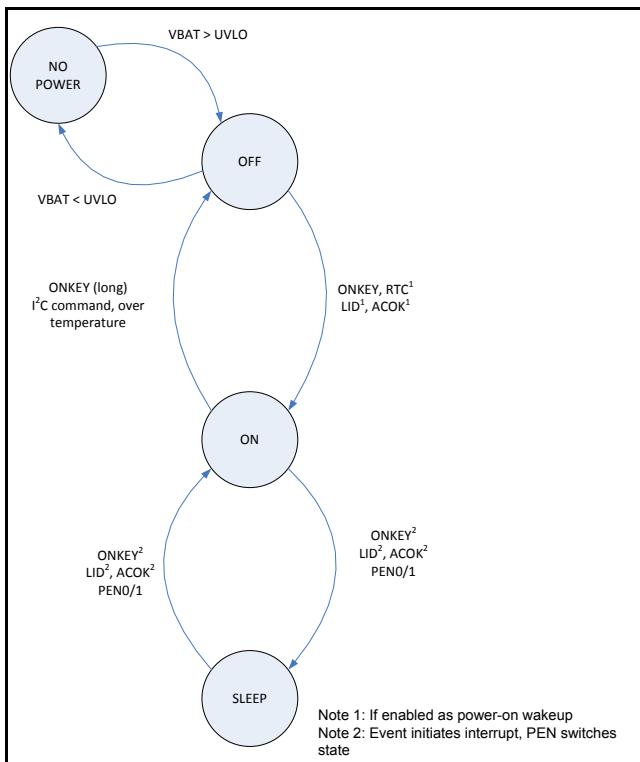

The output voltages of all regulators as well as device sequencing can be software programmable by writing to volatile registers through the I<sup>2</sup>C interface (Default address: 0x4F) or permanently programmed by OTP (One Time Programmable fuse cells). The PMIC operates from a single 2.7V to 5.25V supply. Additionally, the device has an internal high voltage regulator to supply the ONKEY button and RTC circuitry. This feature allows the complete shutdown of the pre-regulator in a dual-cell or triple-cell battery system, thus increasing the battery life of the tablet. IDTP9165 also provides a dedicated pin to sequence the DDR memory power supply.

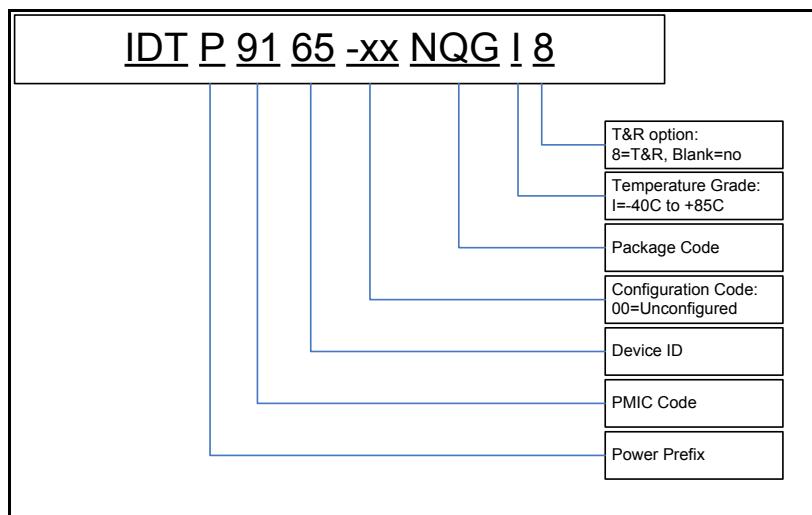

The package for the IDTP9165 is a 7mm x 7mm, 84 lead, dual row QFN package. Operation through the commercial temperature range -40°C to +85°C is guaranteed.

## ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings (AMR) are stress ratings only. Stresses greater than those listed below (Tables 1 and 2) may cause permanent damage to the device. Operation of the IDTP9165 at AMR is not implied. Exposure to AMR may affect long-term reliability.

Table 1 – Absolute Maximum Ratings.

| PINS                                                                                    | MAXIMUM RATING     | UNIT |

|-----------------------------------------------------------------------------------------|--------------------|------|

| VSEN0 to VGND, VSEN1 to VGND<br>VINB to VGND<br>XTAL0 to VGND, XTAL1 to VGND            | -0.3 to 2.2        | V    |

| VBAT to VGND                                                                            | -0.3 to 20         | V    |

| LDO0 to VGND, LDO1 to VGND                                                              | -0.3 to VINA + 0.3 | V    |

| LDO0 to VGND, LDOTR to VGND                                                             | -0.3 to VSYS + 0.3 | V    |

| LDO3 to VGND, LDO4 to VGND                                                              | -0.3 to VINB + 0.3 | V    |

| LDO5 to VGND                                                                            | -0.3 to VINC + 0.3 | V    |

| LDO6 to VGND, LDO7 to VGND                                                              | -0.3 to VIND + 0.3 | V    |

| LDO8 to VGND, LDO9 to VGND                                                              | -0.3 to VINE + 0.3 | V    |

| GPIO0 through GPIO7 to VGND                                                             | -0.3 to VSYS + 0.3 | V    |

| PGNDA to VGND, PGNDB to VGND, PGND1 to VGND<br>PGND2 to VGND, PGND3 to VGND, EP to VGND | -0.3 to 0.3        | V    |

| All Other Pins to VGND                                                                  | -0.3V to 6.0       | V    |

Table 2- Package Thermal Information

| SYMBOL        | DESCRIPTION                                              | MAXIMUM RATING | UNIT |

|---------------|----------------------------------------------------------|----------------|------|

| $\theta_{JA}$ | Thermal Resistance Junction to Ambient (NQG84 – QFN)     | 30.6           | °C/W |

| $\theta_{JC}$ | Thermal Resistance Junction to Case (NQG84 – QFN)        | 21.9           | °C/W |

| $\theta_{JB}$ | Thermal Characterization Junction to Board (NQG84 – QFN) | 1.2            | °C/W |

| $T_J$         | Junction Temperature                                     | -40 to +125    | °C   |

| $T_A$         | Ambient Operating Temperature                            | -40 to +85     | °C   |

| $T_{STG}$     | Storage Temperature                                      | -55 to +150    | °C   |

| $T_{LEAD}$    | Lead Temperature (soldering, 10s)                        | +300           | °C   |

Note: The maximum power dissipation is  $P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$  where  $T_{J(MAX)}$  is 125°C. Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the device will enter thermal shutdown. This thermal rating was calculated on a JEDEC 4 layer board (4.5" x 4.0"), using a 0.169" x 0.169" ePad soldered down, with 16 PCB Thermal vias, arranged in a 4x4 symmetrical array. Actual thermal resistance is affected by PCB size, solder joint quality, layer count, copper thickness, air flow, altitude, and other unlisted variables.

Table 3 – ESD Information

| TEST MODEL                | PINS                      | MAXIMUM RATING | UNIT |

|---------------------------|---------------------------|----------------|------|

| (HBM) Human Body Model    | All (except PVIN2, PVIN3) | $\pm 2000$     | V    |

|                           | PVIN2, PVIN3              | $\pm 1000$     |      |

| (CDM) Charge Device Model | All                       | $\pm 500$      |      |

# ELECTRICAL CHARACTERISTICS

$V_{INA}, V_{INC}, V_{IND}, V_{INE} = 5V$ ,  $T_J = -40$  to  $+125^\circ C$ , unless otherwise noted. Typical values are at  $25^\circ C$ , unless otherwise noted.

Table 4. General Electrical Characteristics

| SYMBOL          | DESCRIPTION                                                                                                          | CONDITIONS                                                  | MIN  | TYP       | MAX  | UNIT       |

|-----------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|-----------|------|------------|

| $V_{BAT}$       | Input voltage operating range<br><i>Note: Default option is C=1. Contact IDT marketing for other device options.</i> | Single-cell option (C=1)                                    | 2.7  |           | 6    | V          |

|                 |                                                                                                                      | Two-cell option (C=2)                                       | 2.7  |           | 12   |            |

|                 |                                                                                                                      | Three-cell option (C=3)                                     | 2.7  |           | 18   |            |

|                 | UVLO threshold, VBAT rising                                                                                          | Register UVLO [2:0] = 000 (default)                         |      | (2.8 x C) |      |            |

|                 |                                                                                                                      | Register UVLO [2:0] = 001                                   |      | (2.9 x C) |      |            |

|                 |                                                                                                                      | Register UVLO [2:0] = 010                                   |      | (3.0 x C) |      |            |

|                 |                                                                                                                      | Register UVLO [2:0] = 011                                   |      | (3.1 x C) |      |            |

|                 |                                                                                                                      | Register UVLO [2:0] = 100                                   |      | (3.2 x C) |      |            |

|                 |                                                                                                                      | Register UVLO [2:0] = 101                                   |      | (3.3 x C) |      |            |

|                 |                                                                                                                      | Register UVLO [2:0] = 110                                   |      | (3.4 x C) |      |            |

|                 |                                                                                                                      | Register UVLO [2:0] = 111                                   |      | (3.5 x C) |      |            |

|                 | UVLO Hysteresis, VBAT falling                                                                                        |                                                             |      | -10       |      | %          |

|                 | Additional hysteresis (added to 10% UVLO hysteresis)                                                                 | Register UVLOHYS [1:0] = 00                                 |      | 0         |      | mV         |

|                 |                                                                                                                      | Register UVLOHYS [1:0] = 01                                 |      | (100 x C) |      |            |

|                 |                                                                                                                      | Register UVLOHYS [1:0] = 10                                 |      | (200 x C) |      |            |

|                 |                                                                                                                      | Register UVLOHYS [1:0] = 11                                 |      | (300 x C) |      |            |

| $I_{Q(VBAT)}$   | VBAT quiescent current                                                                                               | Device in OFF state, RTC running, backup charger turned-on. |      | 10        |      | $\mu A$    |

| $V_{SYS}$       | Input voltage operating range                                                                                        |                                                             | 2.7  |           | 5.25 | V          |

| $I_{Q(VSYS)}$   | VSYS quiescent current                                                                                               | Device in OFF state                                         |      | 1         |      | $\mu A$    |

|                 |                                                                                                                      | Device in ON state, ADC disabled                            |      | 125       |      | $\mu A$    |

|                 |                                                                                                                      | Device in ON state, ADC enabled                             |      | 190       |      | $\mu A$    |

| $V_{IL(PGPRE)}$ | Low level input voltage                                                                                              |                                                             |      |           | 0.65 | V          |

| $V_{IH(PGPRE)}$ | High level input voltage                                                                                             |                                                             | 1.35 |           |      | V          |

| $V_{BAK}$       | UVLO threshold, VBAK rising                                                                                          | For RTC to start working                                    | 1.2  |           | 1.6  | V          |

| $T_{SDN}$       | Thermal shutdown                                                                                                     | Temperature increasing (Guaranteed by design)               | 125  | 132       |      | $^\circ C$ |

| $t_{SDNfilt}$   | Thermal shutdown filter time                                                                                         |                                                             |      | 3         |      | ms         |

## ELECTRICAL CHARACTERISTICS – DCD0,1,2,3 REGULATORS

Table 5. DCD0, (Dual Phase, 10A, DVS capable, Trim Options 1 &amp; 2) Electrical Characteristics

$C_{O(DCD0)} = 47\mu F \times 4$ ,  $L = 0.47\mu H$ ,  $V_{O(DCD0)} = 1.000V$ ,  $V_{PVIN0} = V_{PVINA} = V_{PVINB} = 5V$ ,  $T_A = 25^\circ C$

| SYMBOL            | PARAMETER                                                            | CONDITIONS                                                  | MIN  | TYP               | MAX  | UNIT  |

|-------------------|----------------------------------------------------------------------|-------------------------------------------------------------|------|-------------------|------|-------|

| $V_{PVIN0}$       | Input voltage range                                                  |                                                             | 2.7  |                   | 5.25 | V     |

| $V_{O(DCD0)}$     | Output voltage range                                                 |                                                             | 0.76 |                   | 1.55 | V     |

|                   | Regulation voltage accuracy                                          |                                                             | -2   |                   | +2   | %     |

|                   | Line Regulation                                                      | $V_{PVIN0} = 3V$ to $5V$                                    |      | 0.03              |      | %/V   |

|                   | Load Regulation                                                      | $I_{OUT} = 0.5A$ to $6A$ , PWM mode<br>(see PWM definition) |      | 0.3               |      | mV/A  |

|                   | Voltage resolution                                                   |                                                             |      | 12.5              |      | mV    |

|                   | Offset voltage in PFM mode<br>$V_{O(PFM)} = V_{O(PWM)} + V_{offset}$ | PFM mode<br>(see PFM definition)                            |      | 15                |      | mV    |

| $I_{SHDN(DCD0)}$  | Shutdown current                                                     |                                                             |      | 1                 |      | µA    |

| $SR_{(DCD0)}$     | Slew rate during DVS                                                 | Register DCD0_SR [1:0]                                      | 00   | 12.5 <sup>1</sup> |      | mV/µs |

|                   |                                                                      |                                                             | 01   | 25.0 <sup>1</sup> |      | mV/µs |

|                   |                                                                      |                                                             | 10   | 37.5 <sup>1</sup> |      | mV/µs |

|                   |                                                                      |                                                             | 11   | 50.0 <sup>1</sup> |      | mV/µs |

| $I_{Q(DCD0)}$     | Quiescent Current<br>(see PWM definition)<br>(see PFM definition)    | No load, Forced PWM mode                                    |      | 30                |      | mA    |

|                   |                                                                      | No load, Forced PFM mode                                    |      | 120               |      | µA    |

| $I_{OP(DCD0)}$    | Continuous operating DC current                                      | $T_J < 115^\circ C$                                         |      |                   | 8    | A     |

| $I_{PULSE(DCD0)}$ | Pulsed Load Current                                                  | $t_{LOAD} < 1ms$                                            |      | $10^2$            |      | A     |

| $R_{(on)}$        | High side switch                                                     | Per phase                                                   |      | 60                | 80   | mΩ    |

|                   | Low side switch                                                      | Per phase                                                   |      | 35                | 60   | mΩ    |

| $R_{DIS(DCD0)}$   | Output discharge resistance                                          |                                                             |      | 570               | 650  | Ω     |

| $f_{SW(DCD0)}$    | Switching frequency                                                  | Forced PWM mode                                             |      | 2                 |      | MHz   |

| $T_{ssr(DCD0)}$   | Soft-start ramp rate                                                 |                                                             |      | 5                 |      | mV/µs |

| $\Delta V_{SEN0}$ | VSEN0 pin diff. voltage range                                        |                                                             |      | 250               |      | mV    |

| $Z_{VSEN0}$       | VSEN0 pin input impedance                                            |                                                             |      | 1                 |      | MΩ    |

| $I_{FB0}$         | FB0 input bias current                                               |                                                             |      | 2                 |      | µA    |

| $V_{PGD(DCD0)}$   | Power good voltage rising threshold                                  | Output voltage increasing to programmed output voltage      | -10  | -8                | -6   | %     |

**Table 6. DCD0a (Single Phase, 5A, DVS capable, Trim Option 3) Electrical Characteristics** $C_{O(DCD0)} = 47\mu F \times 2, L = 0.47\mu H, V_{O(DCD0A)} = 1.000V, V_{PVINO} = V_{PVINA} = V_{PVINB} = 5V, T_A = 25^\circ C$

| SYMBOL             | PARAMETER                                                            | CONDITIONS                          | MIN  | TYP               | MAX  | UNIT       |

|--------------------|----------------------------------------------------------------------|-------------------------------------|------|-------------------|------|------------|

| $V_{PVINA}$        | Input voltage range                                                  |                                     | 2.7  |                   | 5.25 | V          |

| $V_{O(DCD0a)}$     | Output voltage range                                                 |                                     | 0.76 |                   | 1.55 | V          |

|                    | Regulation voltage accuracy                                          |                                     | -2   |                   | +2   | %          |

|                    | Line Regulation                                                      | $V_{PVINO} = 3V$ to $5V$            |      | 0.03              |      | %/V        |

|                    | Load Regulation                                                      | $I_{OUT} = 0.5A$ to $6A$ , PWM mode |      | 0.3               |      | mV/A       |

|                    | Voltage resolution                                                   |                                     |      | 12.5              |      | mV         |

|                    | Offset voltage in PFM mode<br>$V_{O(PFM)} = V_{O(PWM)} + V_{offset}$ | PFM mode                            |      | 15                |      | mV         |

| $I_{SHDN(DCD0a)}$  | Shutdown current                                                     |                                     |      | 1                 |      | $\mu A$    |

| $SR_{(DCD0)}$      | Slew rate during DVS                                                 | Register DCD0_SR [1:0]              | 00   | 12.5 <sup>1</sup> |      | $mV/\mu s$ |

|                    |                                                                      |                                     | 01   | 25.0 <sup>1</sup> |      | $mV/\mu s$ |

|                    |                                                                      |                                     | 10   | 37.5 <sup>1</sup> |      | $mV/\mu s$ |

|                    |                                                                      |                                     | 11   | 50.0 <sup>1</sup> |      | $mV/\mu s$ |

| $I_{Q(DCD0a)}$     | Quiescent Current                                                    | No load, Forced PWM mode            |      | 15                |      | mA         |

|                    |                                                                      | PFM mode                            |      | 80                |      | $\mu A$    |

| $I_{OP(DCD0a)}$    | Continuous operating DC current                                      | $T_J < 115^\circ C$                 |      |                   | 4    | A          |

| $I_{PULSE(DCD0a)}$ | Pulsed Load Current                                                  | $t_{Load} < 1ms$                    |      | 5 <sup>3</sup>    |      | A          |

| $R_{(on)}$         | High side switch                                                     |                                     |      | 60                | 80   | $m\Omega$  |

|                    | Low side switch                                                      |                                     |      | 35                | 60   | $m\Omega$  |

| $R_{DIS(DCD0a)}$   | Output discharge resistance                                          |                                     |      | 570               | 650  | $\Omega$   |

| $f_{SW(DCD0a)}$    | Switching frequency                                                  | PWM mode                            |      | 2                 |      | MHz        |

| $T_{ssr(DCD0a)}$   | Soft-start ramp rate                                                 |                                     |      | 5 <sup>3</sup>    |      | $mV/\mu s$ |

| $\Delta V_{SENA}$  | VSENA pin diff. voltage range                                        |                                     |      | 250               |      | mV         |

| $Z_{VSENA}$        | VSENA pin input impedance                                            |                                     |      | 1                 |      | $M\Omega$  |

| $I_{FBA}$          | FBA input bias current                                               |                                     |      | 1                 | 1.8  | $\mu A$    |

## Advanced Datasheet

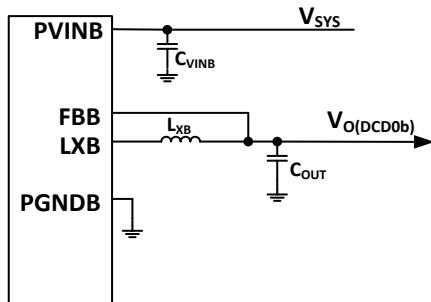

**Table 7. DCD0b (Single Phase, 5A, NOT DVS capable, Trim Option 3) Electrical Characteristics** $C_{O(DCD0b)} = 47\mu\text{F} \times 2$ ,  $L = 0.47\mu\text{H}$ ,  $V_{O(DCD0b)} = 1.000\text{V}$ ,  $V_{PVIN0} = V_{PVINA} = V_{PVINB} = 5\text{V}$ ,  $T_A = 25^\circ\text{C}$

| SYMBOL             | PARAMETER                                                            | CONDITIONS                                        | MIN  | TYP            | MAX  | UNIT                    |

|--------------------|----------------------------------------------------------------------|---------------------------------------------------|------|----------------|------|-------------------------|

| $V_{PVIN0}$        | Input voltage range                                                  |                                                   | 2.7  |                | 5.25 | V                       |

| $V_{O(DCD0b)}$     | Output voltage range                                                 |                                                   | 0.76 |                | 1.55 | V                       |

|                    | Regulation voltage accuracy                                          |                                                   | -2   |                | +2   | %                       |

|                    | Line Regulation                                                      | $V_{PVIN0} = 3\text{V}$ to $5\text{V}$            |      | 0.03           |      | %/V                     |

|                    | Load Regulation                                                      | $I_{OUT} = 0.5\text{A}$ to $6\text{A}$ , PWM mode |      | 0.3            |      | mV/A                    |

|                    | Voltage resolution                                                   |                                                   |      | 12.5           |      | mV                      |

|                    | Offset voltage in PFM mode<br>$V_{O(PFM)} = V_{O(PWM)} + V_{offset}$ | PFM mode                                          |      | 15             |      | mV                      |

| $I_{SHDN(DCD0b)}$  | Shutdown current                                                     |                                                   |      | 1              |      | $\mu\text{A}$           |

| $I_{Q(DCD0a)}$     | Quiescent Current                                                    | No load, Forced PWM mode                          |      | 15             |      | mA                      |

|                    |                                                                      | No load, Forced PFM mode                          |      | 80             |      | $\mu\text{A}$           |

| $I_{OP(DCD0a)}$    | Continuous operating DC current                                      | $T_J < 115^\circ\text{C}$                         |      |                | 4    | A                       |

| $I_{PULSE(DCD0a)}$ | Pulsed Load Current                                                  | $t_{Load} < 1\text{ms}$                           |      | 5 <sup>3</sup> |      | A                       |

| $R_{(on)}$         | High side switch                                                     |                                                   |      | 60             | 80   | $\text{m}\Omega$        |

|                    | Low side switch                                                      |                                                   |      | 35             | 60   | $\text{m}\Omega$        |

| $R_{DIS(DCD0a)}$   | Output discharge resistance                                          |                                                   |      | 570            | 650  | $\Omega$                |

| $f_{SW(DCD0a)}$    | Switching frequency                                                  | PWM mode                                          |      | 2              |      | MHz                     |

| $T_{ssr(DCD0a)}$   | Soft-start ramp rate                                                 |                                                   |      | 5              |      | $\text{mV}/\mu\text{s}$ |

| $I_{FB}$           | FBA input bias current                                               |                                                   |      | 1              | 1.8  | $\mu\text{A}$           |

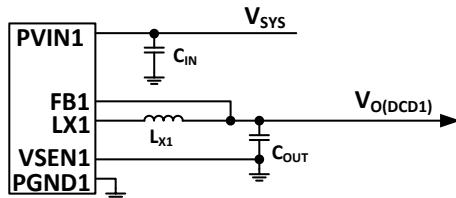

**Table 8. DCD1 (Single-Phase Step-Down Regulator) Electrical Characteristics** $C_{O(DCD1)} = 47\mu F$ ,  $L = 1\mu H$ ,  $V_{O(DCD1)} = 1.000V$ ,  $V_{PVIN1} = 5V$ ,  $T_A = 25^\circ C$

| SYMBOL            | PARAMETER                                                            | CONDITIONS                          | MIN  | TYP               | MAX  | UNIT       |

|-------------------|----------------------------------------------------------------------|-------------------------------------|------|-------------------|------|------------|

| $V_{IN(DCD1)}$    | Input voltage range                                                  |                                     | 2.7  |                   | 5.25 | V          |

| $V_{O(DCD1)}$     | Output voltage range                                                 | LDOTR tracking disabled             | 0.76 |                   | 1.55 | V          |

|                   |                                                                      | LDOTR tracking enabled              | 0.6  |                   | 1.5  | V          |

|                   | Regulation voltage accuracy                                          |                                     | -2   |                   | +2   | %          |

|                   | Line Regulation                                                      | $V_{PVIN1} = 3V$ to $5V$            |      | 0.03              |      | %/V        |

|                   | Load Regulation                                                      | $I_{OUT} = 0.5A$ to $3A$ , PWM mode |      | 0.3               |      | mV/A       |

|                   | Voltage resolution                                                   |                                     |      | 12.5              |      | mV         |

|                   | Offset voltage in PFM mode<br>$V_{O(PFM)} = V_{O(PWM)} + V_{offset}$ | PFM mode                            |      | 15                |      | mV         |

| $I_{SHDN(DCD1)}$  | Shutdown current                                                     |                                     |      | 1                 |      | $\mu A$    |

| $SR_{(DCD1)}$     | Slew rate during DVS                                                 | Register DCD0_SR [1:0]              | 00   | 12.5 <sup>1</sup> |      | $mV/\mu s$ |

|                   |                                                                      |                                     | 01   | 25.0 <sup>1</sup> |      | $mV/\mu s$ |

|                   |                                                                      |                                     | 10   | 37.5 <sup>1</sup> |      | $mV/\mu s$ |

|                   |                                                                      |                                     | 11   | 50.0 <sup>1</sup> |      | $mV/\mu s$ |

| $I_{Q(DCD1)}$     | Quiescent Current                                                    | No load, Forced PWM mode            |      | 15                |      | mA         |

|                   |                                                                      | No load, Forced PFM mode            |      | 80                |      | $\mu A$    |

| $I_{OP(DCD1)}$    | Continuous operating DC current                                      | $T_J < 115^\circ C$                 |      |                   | 4    | A          |

| $I_{PULSE(DCD1)}$ | Pulsed Load Current                                                  | $t_{Load} < 1ms$                    |      | 5.0 <sup>3</sup>  |      | A          |

| $R_{(on)}$        | High side switch                                                     |                                     |      | 60                | 80   | $m\Omega$  |

|                   | Low side switch                                                      |                                     |      | 35                | 60   | $m\Omega$  |

| $R_{DIS(DCD1)}$   | Output discharge resistance                                          |                                     |      | 570               | 650  | $\Omega$   |

| $f_{SW(DCD1)}$    | Switching frequency                                                  | PWM mode                            |      | 2                 |      | MHz        |

| $T_{ssr(DCD1)}$   | Soft-start ramp rate                                                 |                                     |      | 5                 |      | $mV/\mu s$ |

| $\Delta V_{SEN1}$ | VSEN1 diff. voltage range                                            |                                     |      | 250               |      | mV         |

| $Z_{VSEN1}$       | VSEN1 input impedance                                                |                                     |      | 1                 |      | $M\Omega$  |

| $I_{FB1}$         | FB1 input bias current                                               |                                     |      | 1                 | 1.8  | $\mu A$    |

## Advanced Datasheet

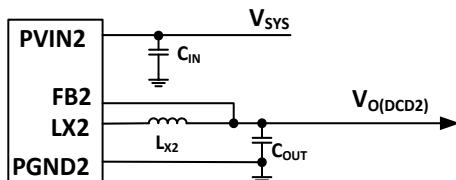

**Table 9. DCD2 (Single-Phase Step-Down Regulator) Electrical Characteristics** $C_{O(DCD2)} = 22\mu F$ ,  $L = 2.2\mu H$ ,  $V_{O(DCD2)} = 1.8V$ ,  $V_{PVIN2} = 5V$ ,  $T_A = 25^\circ C$

| SYMBOL            | PARAMETER                                                            | CONDITIONS                            | MIN  | TYP  | MAX  | UNIT       |

|-------------------|----------------------------------------------------------------------|---------------------------------------|------|------|------|------------|

| $V_{PVIN2}$       | Input voltage range                                                  |                                       | 2.7  |      | 5.25 | V          |

| $V_{O(DCD2)}$     | Output voltage range                                                 |                                       | 0.76 |      | 3.3  | V          |

|                   | Regulation voltage accuracy                                          | $DCD2\_RNG[1:0] = 01$                 | -2   |      | +2   | %          |

|                   | Line Regulation                                                      | $V_{PVIN2} = 3V$ to $5V$              |      | 0.03 |      | %/V        |

|                   | Load Regulation                                                      | $I_{OUT} = 0.2A$ to $1.5A$ , PWM mode |      | 0.3  |      | mV/A       |

|                   | Offset voltage in PFM mode<br>$V_{O(PFM)} = V_{O(PWM)} + V_{offset}$ | PFM mode                              |      | 15   |      | mV         |

| $I_{SHDN(DCD2)}$  | Shutdown current                                                     |                                       |      | 1    |      | $\mu A$    |

| $I_{Q(DCD2)}$     | Quiescent Current                                                    | No load, PFM mode                     |      | 60   |      | $\mu A$    |

| $I_{OP(DCD2)}$    | Continuous operating DC current                                      | $T_J < 115^\circ C$                   |      |      | 1.5  | A          |

| $I_{PULSE(DCD2)}$ | Pulsed Load Current                                                  | $t_{Load} < 1ms$                      |      | 2    |      | A          |

| $R_{(on)}$        | High side switch                                                     |                                       |      | 125  | 160  | $m\Omega$  |

|                   | Low side switch                                                      |                                       |      | 75   | 100  | $m\Omega$  |

| $R_{DIS(DCD2)}$   | Output discharge resistance                                          |                                       |      | 1000 | 1300 | $\Omega$   |

| $f_{SW(DCD2)}$    | Switching frequency                                                  | PWM mode                              |      | 2    |      | MHz        |

| $T_{ssr(DCD2)}$   | Soft-start ramp rate                                                 |                                       |      | 5    |      | $mV/\mu s$ |

| $I_{FB2}$         | FB2 input bias current                                               | $V_{O(DCD2)} > 2.6625V$               |      | 3    | 4    | $\mu A$    |

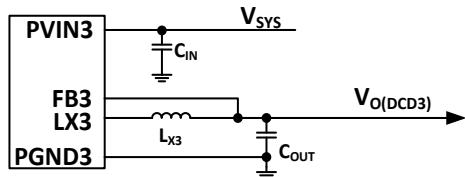

**Table 10. DCD3 (Single-Phase Step-Down Regulator) Electrical Characteristics** $C_{O(DCD3)} = 22\mu F$ ,  $L = 2.2\mu H$ ,  $V_{O(DCD3)} = 1.35V$ ,  $V_{VIN3} = 5V$ ,  $T_A = 25^\circ C$

| SYMBOL            | PARAMETER                                                            | CONDITIONS                            | MIN  | TYP  | MAX  | UNIT       |

|-------------------|----------------------------------------------------------------------|---------------------------------------|------|------|------|------------|

| $V_{VIN3}$        | Input voltage range                                                  |                                       | 2.7  |      | 5.25 | V          |

| $V_{O(DCD3)}$     | Output voltage range                                                 |                                       | 0.76 |      | 3.3  | V          |

|                   | Regulation voltage accuracy                                          |                                       | -2   |      | +2   | %          |

|                   | Line Regulation                                                      | $V_{VIN3} = 3V$ to $5V$               |      | 0.03 |      | %/V        |

|                   | Load Regulation                                                      | $I_{OUT} = 0.2A$ to $1.5A$ , PWM mode |      | 0.3  |      | mV/A       |

|                   | Offset voltage in PFM mode<br>$V_{O(PFM)} = V_{O(PWM)} + V_{offset}$ | PFM mode                              |      | 15   |      | mV         |

| $I_{SHDN(DCD3)}$  | Shutdown current                                                     |                                       |      | 1    |      | $\mu A$    |

| $I_Q(DCD3)$       | Quiescent Current                                                    | No load, Forced PFM mode              |      | 60   |      | $\mu A$    |

| $I_{OP(DCD3)}$    | Continuous operating DC current                                      | $T_J < 115^\circ C$                   |      |      | 1.5  | A          |

| $I_{PULSE(DCD3)}$ | Pulsed Load Current                                                  | $t_{Load} < 1ms$                      |      | 2    |      | A          |

| $R_{(on)}$        | High side switch                                                     |                                       |      | 125  | 160  | $m\Omega$  |

|                   | Low side switch                                                      |                                       |      | 75   | 100  | $m\Omega$  |

| $R_{DIS(DCD3)}$   | Output discharge resistance                                          |                                       |      | 1000 | 1300 | $\Omega$   |

| $f_{SW(DCD3)}$    | Switching frequency                                                  | Forced PWM mode                       |      | 2    |      | MHz        |

| $T_{ssr(DCD3)}$   | Soft-start ramp rate                                                 |                                       |      | 5    |      | $mV/\mu s$ |

| $I_{FB3}$         | FB3 input bias current                                               | $V_{O(DCD3)} > 2.6625V$               |      | 3    | 4    | $\mu A$    |

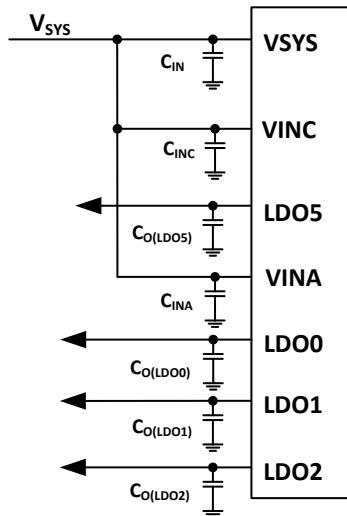

## ELECTRICAL CHARACTERISTICS -LDO Regulators

Table 11. LDO0, 1, 2, 5 Electrical Characteristics

$C_0 = 1\mu F$ ,  $V_{IN} > V_0 + 0.3V$ ,  $T_A = 25^\circ C$

| SYMBOL     | PARAMETER                   | CONDITIONS                                                                  | MIN  | TYP   | MAX  | UNIT          |

|------------|-----------------------------|-----------------------------------------------------------------------------|------|-------|------|---------------|

| $V_{IN}$   | Input voltage range         |                                                                             | 2.40 |       | 5.25 | V             |

| $V_0$      | Output voltage range        |                                                                             | 1.00 |       | 3.35 | V             |

| $I_{SHDN}$ | Shutdown current            |                                                                             |      | 0.1   |      | $\mu A$       |

| $I_Q$      | Quiescent current           | No Load                                                                     |      | 18    |      | $\mu A$       |

|            | Regulation voltage accuracy |                                                                             | -2   |       | +2   | %             |

|            | Line regulation             |                                                                             |      | 30    | 160  | ppm/V         |

|            | Load regulation             | LDO1, 5                                                                     |      | 2     | 4    | $\mu V/mA$    |

|            |                             | LDO0, 2                                                                     |      | 5     | 30   |               |

| $I_o$      | Output current              |                                                                             |      |       | 200  | mA            |

| $I_{LIM}$  | Internal current limit      |                                                                             | 260  |       |      | mA            |

| $V_{drop}$ | Dropout voltage             | $I_o = 200mA$ , $V_{IN} > 2.8V$                                             |      |       | 300  | mV            |

| $R_{DIS}$  | Output discharge resistance |                                                                             |      | 10    |      | $k\Omega$     |

| PSRR       | Ripple rejection ratio      | 1V input to output,<br>$I_o = 40mA$                                         |      |       |      | dB            |

|            |                             | < 200Hz                                                                     |      | > 120 |      |               |

|            |                             | 1kHz                                                                        |      | 120   |      |               |

|            |                             | 10kHz                                                                       |      | 90    |      |               |

|            |                             | 100kHz                                                                      |      | 53    |      |               |

|            | Output noise voltage        | $V_0 = 1.2V$ , $V_{IN} > 2.8V$<br>$I_o = 100\mu A$ ,<br>BW = 10Hz to 100kHz |      | 52    |      | $\mu V_{RMS}$ |

| $T_{ss}$   | Start-up time               |                                                                             |      |       | 120  | $\mu s$       |

| $T_{ssr}$  | LDO soft-start ramp rate    |                                                                             |      | 35    |      | $mV/\mu s$    |

| $C_0$      | External output capacitor   | De-rated value                                                              | 0.7  |       | 1.2  | $\mu F$       |

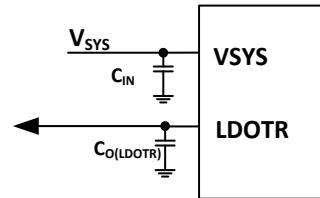

**Table 12. LDOTR (Tracking LDO) Electrical Characteristics** $C_0 = 2.2\mu F$ ,  $V_{IN} > V_O + 0.3V$ ,  $T_A = 25^\circ C$

| SYMBOL     | PARAMETER                   | CONDITIONS                                                                                         | MIN | TYP   | MAX  | UNIT          |

|------------|-----------------------------|----------------------------------------------------------------------------------------------------|-----|-------|------|---------------|

| $V_{IN}$   | Input voltage range         |                                                                                                    | 2.4 |       | 5.25 | V             |

| $V_O$      | Output voltage range        |                                                                                                    | 0.6 |       | 1.5  | V             |

| $I_{SHDN}$ | Shutdown current            |                                                                                                    |     | 0.1   |      | $\mu A$       |

| $I_Q$      | Quiescent current           | No Load                                                                                            |     | 23    |      | $\mu A$       |

|            | Regulation voltage accuracy |                                                                                                    | -2  |       | +2   | %             |

|            | Line regulation             |                                                                                                    |     | 15    | 90   | ppm/V         |

|            | Load regulation             |                                                                                                    |     | 2     | 4    | $\mu V/mA$    |

| $I_O$      | Output current              |                                                                                                    |     |       | 160  | mA            |

| $I_{LIM}$  | Internal current limit      |                                                                                                    | 280 |       |      | mA            |

| $R_{DIS}$  | Output discharge resistance |                                                                                                    |     | 10    |      | $k\Omega$     |

| PSRR       | Ripple rejection ratio      | 1V input to output,<br>$I_O = 40mA$                                                                |     |       |      | dB            |

|            |                             | < 200Hz                                                                                            |     | > 120 |      |               |

|            |                             | 1kHz                                                                                               |     | 120   |      |               |

|            |                             | 10kHz                                                                                              |     | 90    |      |               |

|            |                             | 100kHz                                                                                             |     | 53    |      |               |

|            | Output noise voltage        | $V_O = 0.90V$ , $V_{IN} > 2.8V$<br>$I_O = 100\mu A$ ,<br>BW = 10Hz to 100kHz,<br>Tracking disabled |     | 32    |      | $\mu V_{RMS}$ |

| $T_{ss}$   | Start-up time               | (GBD)                                                                                              |     |       | 120  | $\mu s$       |

| $T_{ssr}$  | LDO soft-start ramp rate    |                                                                                                    |     | 35    |      | $mV/\mu s$    |

| $C_O$      | External output capacitor   | De-rated value                                                                                     | 1.6 |       | 2.5  | $\mu F$       |

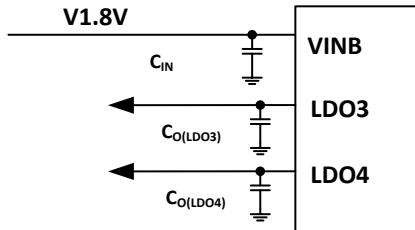

## Advanced Datasheet

Table 13– LDO3, 4 Electrical Characteristics

$C_O = 2.2\mu F$ ,  $V_{IN} > V_O + 0.3V$ ,  $T_A = 25^\circ C$

| SYMBOL     | PARAMETER                   | CONDITIONS                                                                  | MIN   | TYP   | MAX   | UNIT          |

|------------|-----------------------------|-----------------------------------------------------------------------------|-------|-------|-------|---------------|

| $V_{IN}$   | Input voltage range         |                                                                             | 1.0   |       | 2.0   | V             |

| $V_O$      | Output voltage range        |                                                                             | 1.000 |       | 1.475 | V             |

| $I_{SHDN}$ | Shutdown current            |                                                                             |       | 0.5   |       | $\mu A$       |

| $I_Q$      | Quiescent current           | No Load                                                                     |       | 19    |       | $\mu A$       |

|            | Regulation voltage accuracy |                                                                             | -2    |       | +2    | %             |

|            | Line regulation             |                                                                             |       | 1     | 300   | ppm/V         |

|            | Load regulation             |                                                                             |       | 6     | 20    | $\mu V/mA$    |

| $I_O$      | Output current              |                                                                             |       |       | 160   | mA            |

| $I_{LIM}$  | Internal current limit      |                                                                             | 200   |       |       | mA            |

| $V_{drop}$ | Dropout voltage             | $I_O = 160mA$ , $V_{IN} > 1.2V$                                             |       |       | 120   | mV            |

| $R_{DIS}$  | Output discharge resistance |                                                                             |       | 10    |       | $k\Omega$     |

| PSRR       | Ripple rejection ratio      | 1V input to output,<br>$I_O = 30mA$                                         |       |       |       | dB            |

|            |                             | < 200Hz                                                                     |       | > 120 |       |               |

|            |                             | 1kHz                                                                        |       | 120   |       |               |

|            |                             | 10kHz                                                                       |       | 95    |       |               |

|            |                             | 100kHz                                                                      |       | 57    |       |               |

|            | Output noise voltage        | $V_O = 1.0V$ , $V_{IN} = 1.8V$<br>$I_O = 100\mu A$ ,<br>BW = 10Hz to 100kHz |       | 28    |       | $\mu V_{RMS}$ |

| $T_{ss}$   | Start-up time               | (GBD)                                                                       |       |       | 120   | $\mu s$       |

| $T_{ssr}$  | LDO soft-start ramp rate    |                                                                             |       | 30    |       | $mV/\mu s$    |

| $C_O$      | External output capacitor   | De-rated value                                                              | 1.6   |       | 2.5   | $\mu F$       |

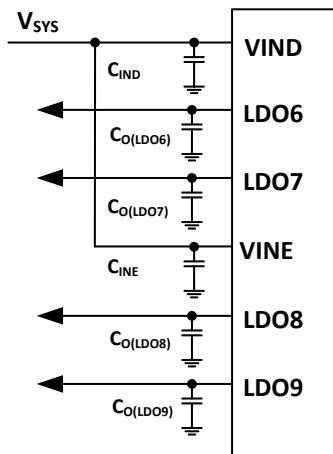

**Table 14– LDO6, 7, 8, 9 Electrical Characteristics** $C_0 = 1\mu\text{F}$ ,  $V_{IN} > V_0 + 0.3\text{V}$ ,  $T_A = 25^\circ\text{C}$

| SYMBOL     | PARAMETER                   | CONDITIONS                                                                                      | MIN  | TYP   | MAX  | UNIT                       |

|------------|-----------------------------|-------------------------------------------------------------------------------------------------|------|-------|------|----------------------------|

| $V_{IN}$   | Input voltage range         |                                                                                                 | 1.7  |       | 5.25 | V                          |

| $V_0$      | Output voltage range        |                                                                                                 | 1.00 |       | 3.35 | V                          |

| $I_{SHDN}$ | Shutdown current            |                                                                                                 |      | 0.1   |      | $\mu\text{A}$              |

| $I_Q$      | Quiescent current           | No Load                                                                                         |      | 19    |      | $\mu\text{A}$              |

|            | Regulation voltage accuracy |                                                                                                 | -2   |       | +2   | %                          |

|            | Line regulation             |                                                                                                 |      | 50    | 100  | $\text{ppm/V}$             |

|            | Load regulation             | LDO7, 9                                                                                         |      | 1     | 3    | $\mu\text{V/mA}$           |

|            |                             | LDO6, 8                                                                                         |      | 1     | 50   |                            |

| $I_o$      | Output current              |                                                                                                 |      |       | 200  | mA                         |

| $I_{LIM}$  | Internal current limit      |                                                                                                 | 260  |       |      | mA                         |

| $V_{drop}$ | Dropout voltage             | $I_o = 200\text{mA}$ , $V_{IN} > 1.8\text{V}$                                                   |      |       | 440  | mV                         |

| $R_{DIS}$  | Output discharge resistance |                                                                                                 |      | 10    |      | $\text{k}\Omega$           |

| PSRR       | Ripple rejection ratio      | 1V input to output,<br>$I_o = 40\text{mA}$                                                      |      |       |      | dB                         |

|            |                             | < 200Hz                                                                                         |      | > 120 |      |                            |

|            |                             | 1kHz                                                                                            |      | 120   |      |                            |

|            |                             | 10kHz                                                                                           |      | 90    |      |                            |

|            |                             | 100kHz                                                                                          |      | 53    |      |                            |

|            | Output noise voltage        | $V_0 = 1.2\text{V}$ , $V_{IN} > 2.8\text{V}$<br>$I_o = 100\mu\text{A}$ ,<br>BW = 10Hz to 100kHz |      | 34    |      | $\mu\text{V}_{\text{RMS}}$ |

| $T_{ss}$   | Start-up time               | (GBD)                                                                                           |      |       | 120  | $\mu\text{s}$              |

| $T_{ssr}$  | LDO soft-start ramp rate    |                                                                                                 |      | 35    |      | $\text{mV}/\mu\text{s}$    |

| $C_0$      | External output capacitor   | De-rated value                                                                                  | 0.7  |       | 1.2  | $\mu\text{F}$              |

## ELECTRICAL CHARACTERISTICS - Charger

Table 15– Charger Module Electrical Characteristics

$T_A = 25^\circ\text{C}$

| SYMBOL         | PARAMETER                   | CONDITIONS     |    | MIN  | TYP      | MAX  | UNIT          |

|----------------|-----------------------------|----------------|----|------|----------|------|---------------|

| $V_{O(BAK)}$   | Output voltage setting      | VBAK_VCHG[1:0] | 00 |      | Disabled |      | V             |

|                |                             |                | 01 |      | 2.6      |      |               |

|                |                             |                | 10 |      | 3.0      |      |               |

|                |                             |                | 11 |      | 3.3      |      |               |

|                | Regulation voltage accuracy |                |    | -1.5 |          | +1.5 | %             |

| $I_{O(BAK)}$   | Maximum Output current      | CC mode        |    | 0.7  | 1.2      | 1.9  | A             |

| $I_{LIM(BAK)}$ | Internal series resistance  | VBAK_RCHG[1:0] | 00 |      | 250      |      | $\Omega$      |

|                |                             |                | 01 |      | 1K       |      |               |

|                |                             |                | 10 |      | 2K       |      |               |

|                |                             |                | 11 |      | 4K       |      |               |

| $C_{O(BAK)}$   | External output capacitor   | Optional       |    |      | 1.0      |      | $\mu\text{F}$ |

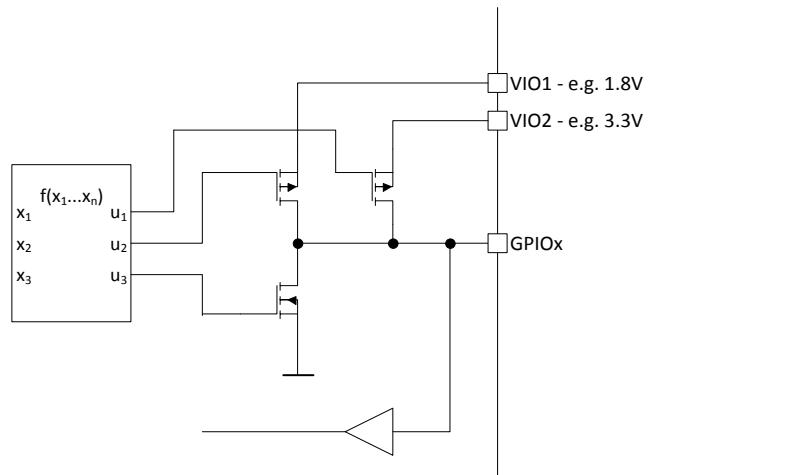

## ELECTRICAL CHARACTERISTICS - GPIO

Table 16– GPIO Interface Electrical Characteristics

| SYMBOL         | PARAMETER                 | CONDITIONS                             | MIN          | TYP | MAX  | UNIT          |

|----------------|---------------------------|----------------------------------------|--------------|-----|------|---------------|

| $V_{OL(GPIO)}$ | Low level output voltage  | $I_{OL(GPIO)} = 12\text{mA}$ , OD mode |              |     | 0.4  | V             |

|                |                           | $I_{OL(GPIO)} = 4\text{mA}$ , PP mode  |              |     | 0.4  | V             |

| $V_{OH(GPIO)}$ | High level output voltage | $I_{OH(GPIO)} = -4\text{mA}$           | VIO-<br>0.4V |     |      | V             |

| $V_{IL(GPIO)}$ | Low level input voltage   |                                        |              |     | 0.6  | V             |

| $V_{IH(GPIO)}$ | High level input voltage  |                                        | 1.5          |     |      | V             |

| $I_{LK(GPIO)}$ | Input leakage current     |                                        |              |     | 1    | $\mu\text{A}$ |

| $I_{SK(GPIO)}$ | Sink current              | GPIO in input mode                     |              | 1   |      | $\mu\text{A}$ |

| $V_{IO1}$      | VIO1 supply input range   |                                        | 1.5          |     | VSYS | V             |

| $V_{IO2}$      | VIO2 supply input range   |                                        | 1.5          |     | VSYS | V             |

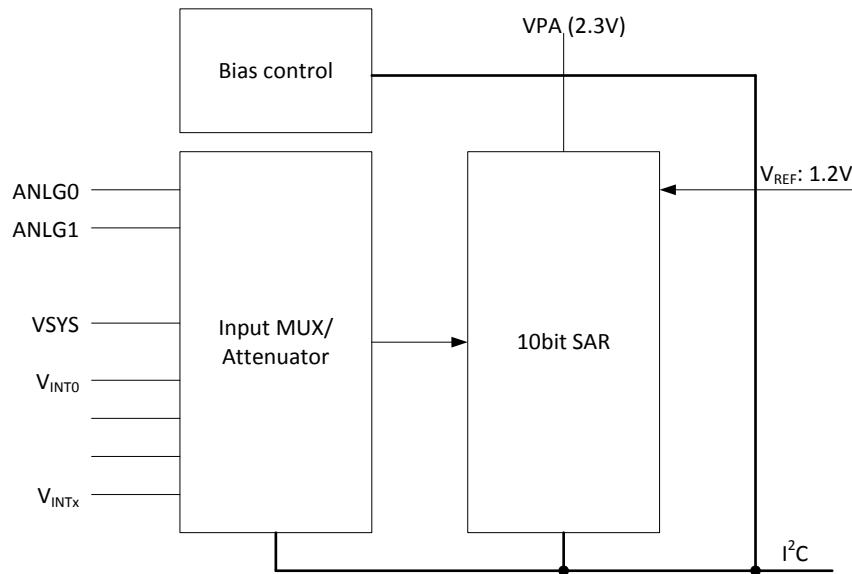

## ELECTRICAL CHARACTERISTICS - ADC

Table 17– ADC Electrical Characteristics

| SYMBOL          | PARAMETER                  | CONDITIONS                | MIN | TYP  | MAX | UNIT      |

|-----------------|----------------------------|---------------------------|-----|------|-----|-----------|

| $V_{REF}$       | ADC reference voltage      | Internally provided       |     | 1.2  |     | V         |

| $I_{DD(ADC)}$   | Supply Current             | Full scale current        |     | 60   |     | $\mu$ A   |

| RES             | ADC resolution             | External pins ANLGx       |     | 10   |     | Bits      |

| INL             | Integral Non Linearity     | External pins ANLGx (GBD) | -2  |      | +2  | LSB       |

| DNL             | Differential Non Linearity | External pins ANLGx (GBD) | -1  |      | +1  | LSB       |

| Gain            | Gain Error                 | External pins ANLGx (GBD) | -2  |      | +2  | LSB       |

| $F_s$           | Conversion rate            |                           |     | 50   |     | kS/s      |

| $V_{MEAS(ADC)}$ | ADC input voltage          | External pins ANLGx (GBD) | 0   |      | 1.2 | V         |

|                 |                            | VSYS (GBD)                | 0   |      | 5.6 | V         |

|                 |                            | VBAT (GBD)                | 0   |      | 4.4 | V         |

| SF              | Voltage scale factor       | External pins ANLGx       |     | 1.0  |     | V/V       |

|                 |                            | VSYS                      |     | 3/14 |     | V/V       |

|                 |                            | VBAT                      |     | 3/11 |     | V/V       |

| $R_{IN(ANLGx)}$ | ANLGx input resistance     |                           |     | 10   |     | $M\Omega$ |

## ELECTRICAL CHARACTERISTICS – RTC

Table 18– RTC Electrical Characteristics

| SYMBOL                    | PARAMETER                                     | CONDITIONS                             | MIN      | TYP    | MAX    | UNIT             |

|---------------------------|-----------------------------------------------|----------------------------------------|----------|--------|--------|------------------|

| $T_A = 25^\circ\text{C}$  |                                               |                                        |          |        |        |                  |

| $V_{IN(RTC)}$             | RTC supply voltage                            |                                        | 1.6      |        | VBAK   | V                |

| $I_{DD(RTC)}$             | RTC supply current                            |                                        |          | 4      | 5      | $\mu\text{A}$    |

| UVLO                      |                                               | Voltage rising                         | 2.0      |        | 2.4    | V                |

|                           |                                               | Voltage falling                        | 1.2      |        | 1.6    | V                |

| <b>Crystal oscillator</b> |                                               |                                        |          |        |        |                  |

| $f_0$                     | Crystal frequency                             |                                        |          | 32.768 |        | kHz              |

| ESR                       | Crystal series resistor                       |                                        | 5        |        | 70     | $\text{k}\Omega$ |

| $C_{PIN}$                 | Effective total capacitance per pin to ground |                                        |          | 7.2    |        | pF               |

| $t_{start(OSC)}$          | Oscillator startup time                       |                                        |          |        | 400    | ms               |

| <b>CK32 output</b>        |                                               |                                        |          |        |        |                  |

| $V_{CK32}$                | CK32 output voltage                           |                                        |          |        | VIO0/1 | V                |

| $V_{OL(CK32)}$            | Low level output voltage                      | $I_{OL(CK32)} = 12\text{mA}$ , OD mode |          |        | 0.4    | V                |

|                           |                                               | $I_{OL(CK32)} = 4\text{mA}$ , PP mode  |          |        | 0.4    | V                |

| $V_{OH(CK32)}$            | High level output voltage                     | $I_{OH(CK32)} = -4\text{mA}$           | VIO-0.4V |        |        | V                |

| $t_r/t_f$                 | CK32 rise and fall time                       | $CL_{CK32} = 35\text{pF}$              |          |        | tbd    | ns               |

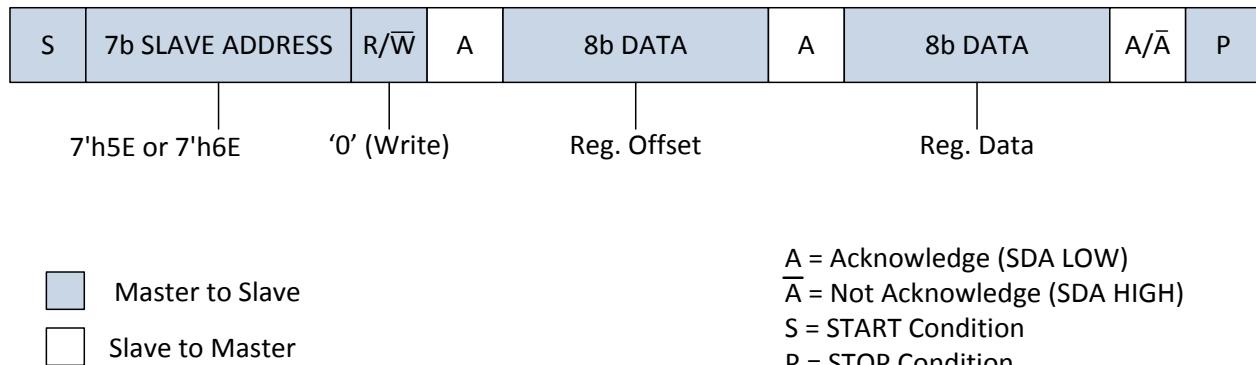

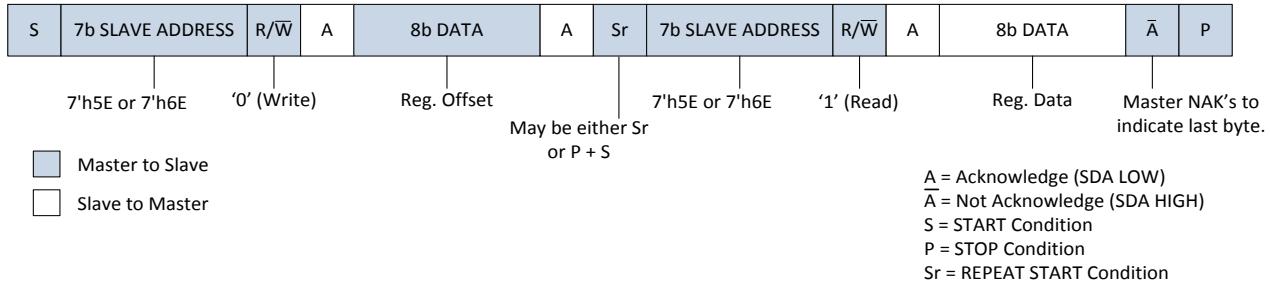

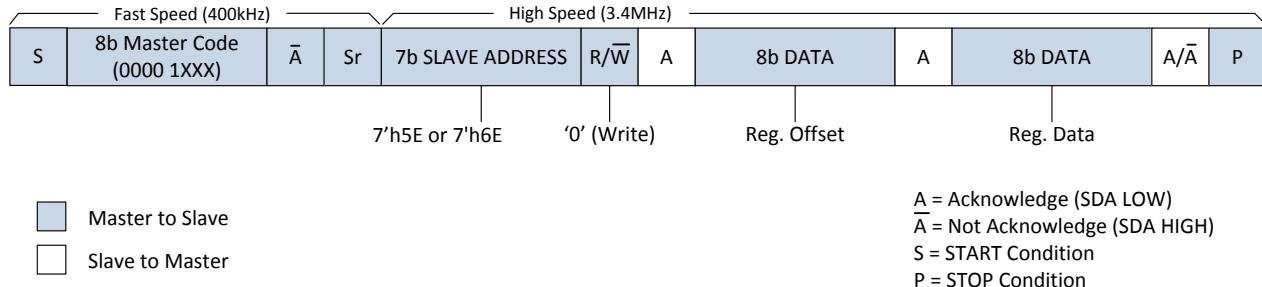

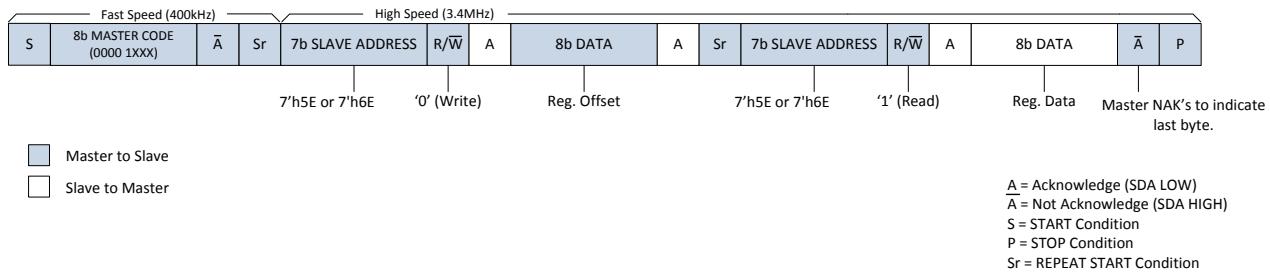

## ELECTRICAL CHARACTERISTICS - I<sup>2</sup>C Interface

Table 19– I<sup>2</sup>C Electrical CharacteristicsUnless otherwise specified, typical values at  $T_A = 25^\circ\text{C}$ ,  $V_{DD} = V_{IO1}$ ,  $T_A = 40^\circ\text{C}$  to  $+85^\circ\text{C}$ .

| SYMBOL    | PARAMETER                                                                     | CONDITIONS                                            | MIN         | TYP | MAX          | UNIT |

|-----------|-------------------------------------------------------------------------------|-------------------------------------------------------|-------------|-----|--------------|------|

| $V_{IL}$  | Low level input voltage                                                       | $I_{OL(GPIO)} = 3\text{mA}$                           | -0.5        |     | $0.3V_{DD}$  | V    |

| $V_{IH}$  | High level input voltage                                                      |                                                       | $0.7V_{DD}$ |     | $V_{DD}+0.5$ | V    |

| $V_{HYS}$ | Input hysteresis                                                              |                                                       | $0.1V_{DD}$ |     |              | V    |

| $V_{OL}$  | Low-level output voltage                                                      | $V_{DD} > 2\text{V}$ , 3mA sink current, (open-drain) | 0           |     | 0.4          | V    |

|           |                                                                               | $V_{DD} < 2\text{V}$ , 3mA sink current, (open-drain) | 0           |     | $0.2V_{DD}$  | V    |

| $t_{FDA}$ | Fall time of SDAH signal                                                      | Capacitive load from 10pF to 100pF                    | 10          |     | 80           | ns   |

|           |                                                                               | Capacitive load of 400pF                              | 20          |     | 160          | ns   |

| $t_{SP}$  | Pulse width of spikes that must be suppressed by the pulse width input filter | SDAH and SDAL                                         | 0           |     | 10           | ns   |

| $I_I$     | Input current each I/O pin                                                    |                                                       |             |     | 10           | mA   |

| $C_I$     | Capacitance for each I/O pin                                                  |                                                       |             |     | 10           | pF   |

## I<sup>2</sup>C – Interface Timing

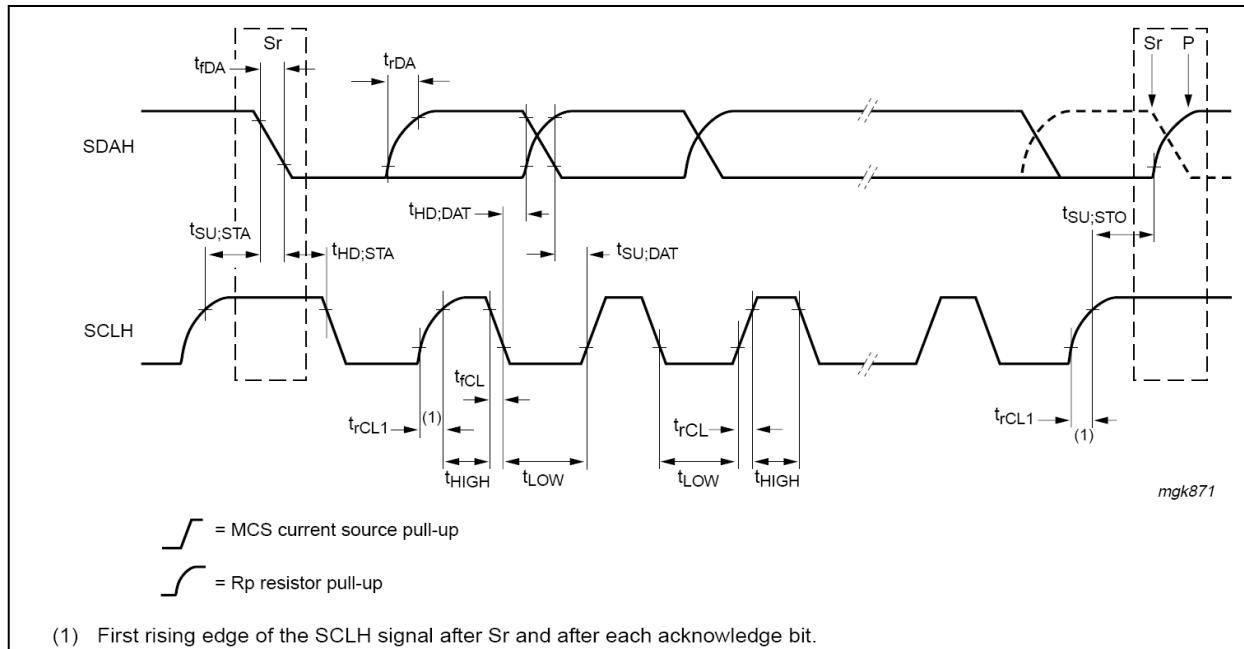

Figure 1. I<sup>2</sup>C Interface Timing

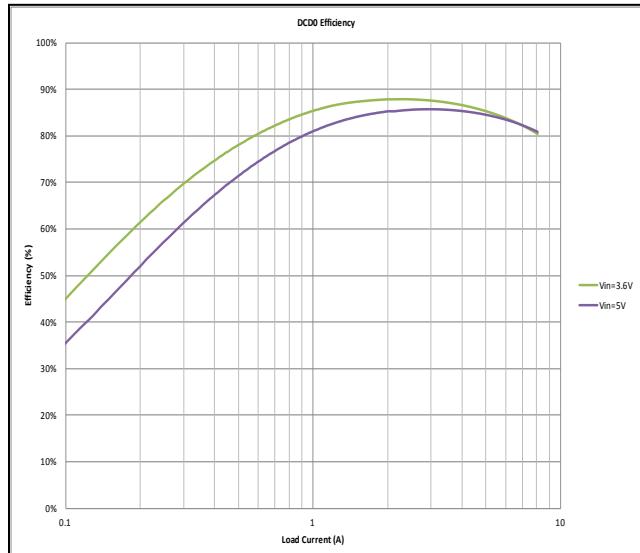

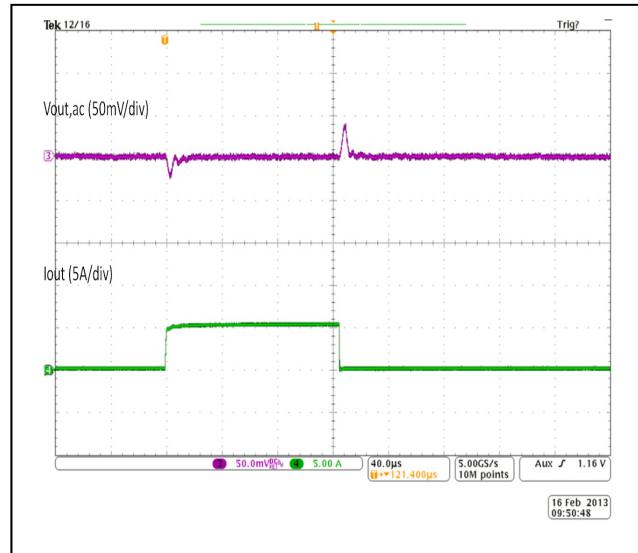

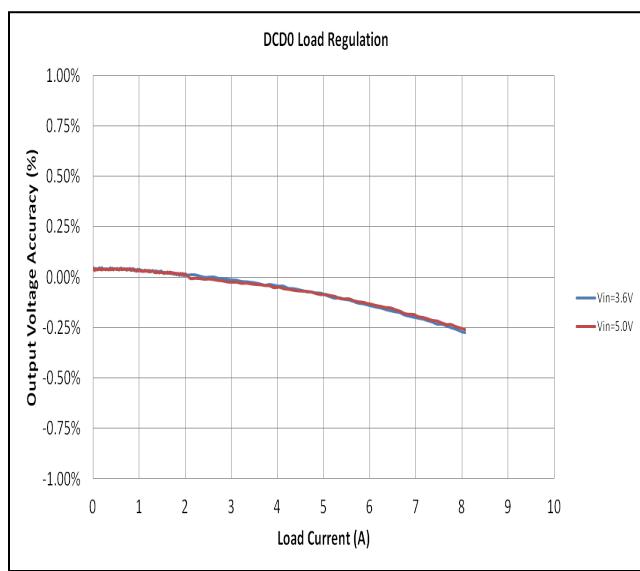

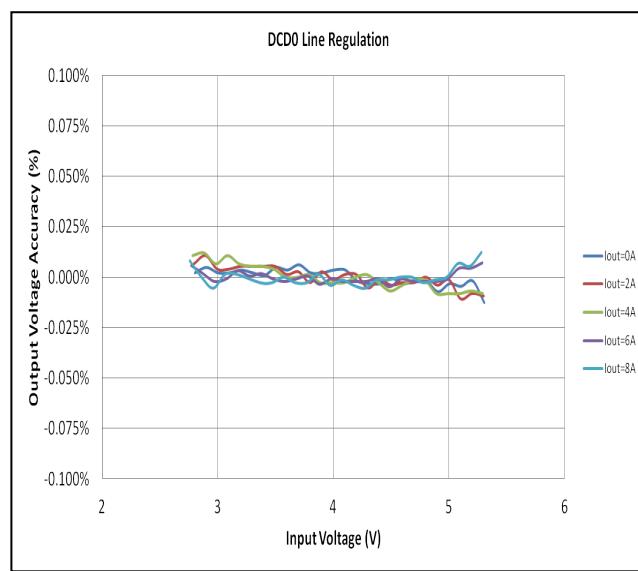

## TYPICAL PERFORMANCE CHARACTERISTICS – DCD0

$C_{O(DCD0)} = 150\mu F$ ,  $L = 0.47\mu H$ ,  $V_{O(DCD0)} = 1.000V$ ,  $V_{PVIN0} = V_{PVINA} = V_{PVINB} = 5V$ ,  $T_A = 25^\circ C$

Figure 2. Efficiency

Figure 3. Transient Response (100mA-6A)

Figure 4. Load Regulation

Figure 5. Line Regulation

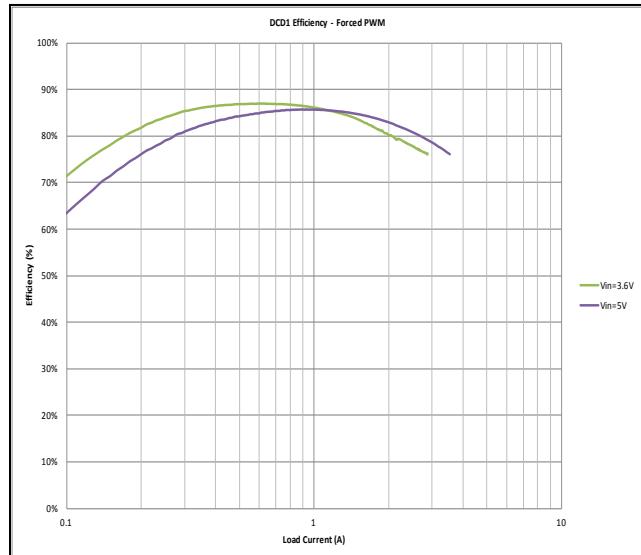

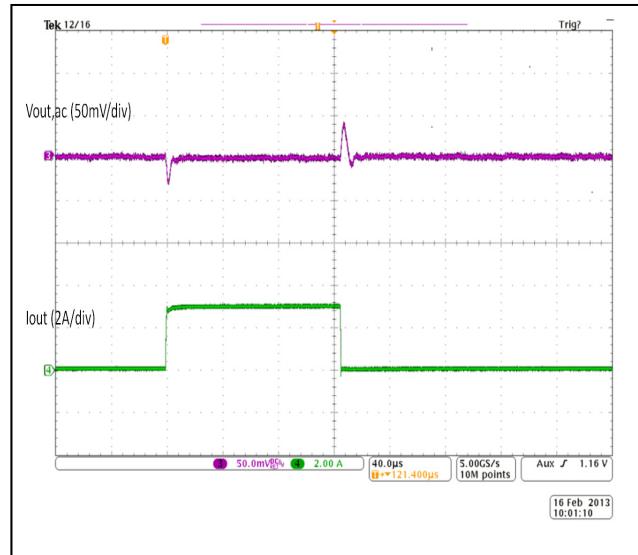

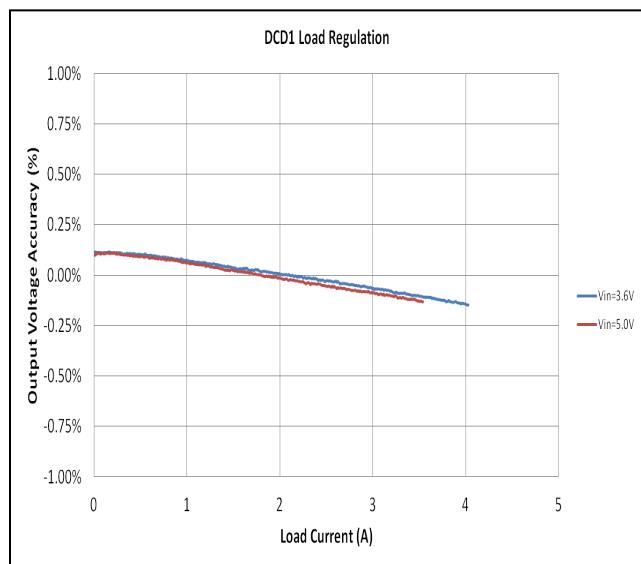

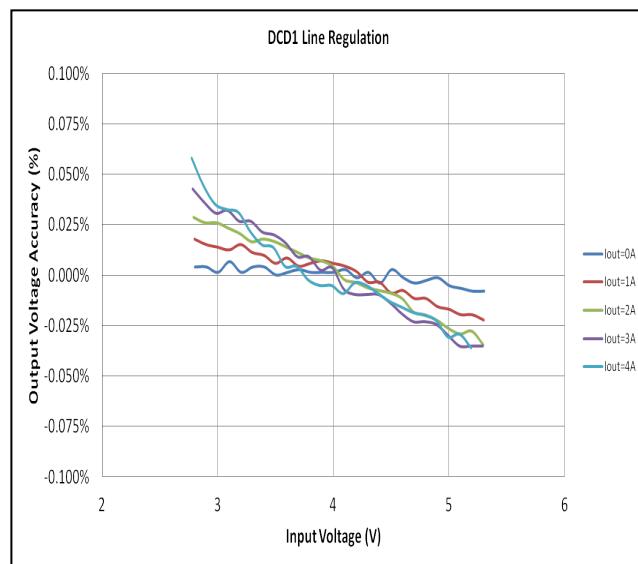

# TYPICAL PERFORMANCE CHARACTERISTICS – DCD1

$C_{O(DCD1)} = 68\mu F$ ,  $L = 1\mu H$ ,  $V_{O(DCD1)} = 1.000V$ ,  $V_{PVIN1} = 5V$ ,  $T_A = 25^\circ C$

Figure 6. Efficiency

Figure 7. Transient Response (100mA – 3A)

Figure 8. Load Regulation

Figure 9. Line Regulation

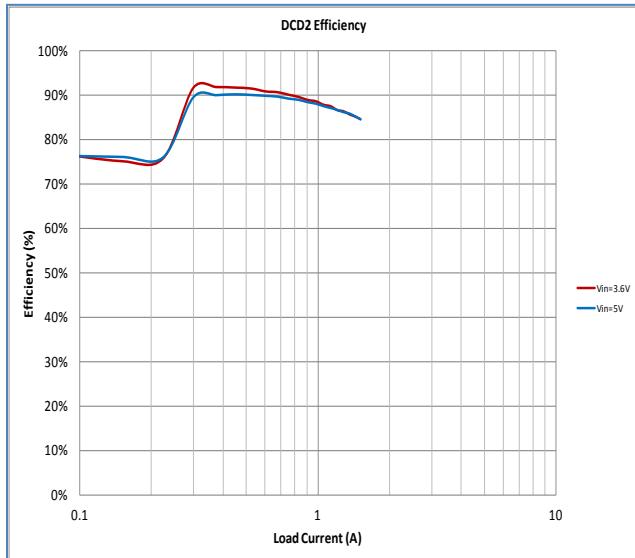

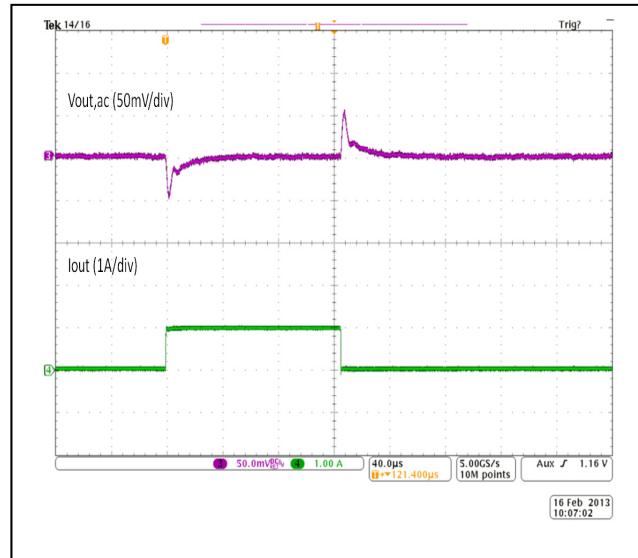

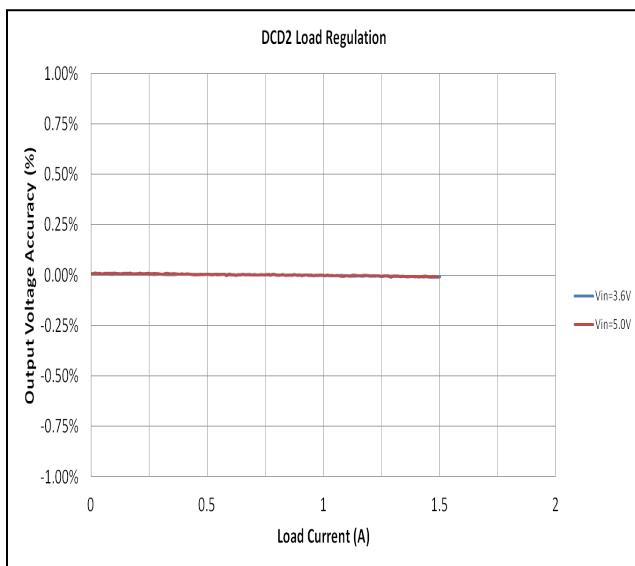

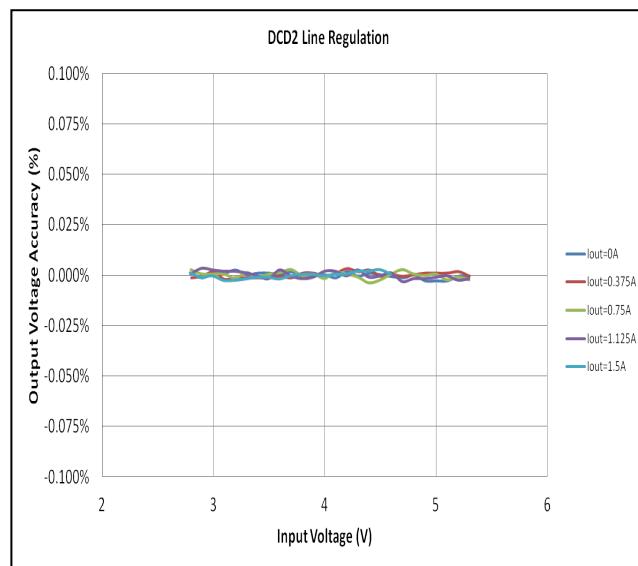

## TYPICAL PERFORMANCE CHARACTERISTICS – DCD2

$C_{O(DCD2)} = 22\mu F$ ,  $L = 2.2\mu H$ ,  $V_{O(DCD2)} = 1.8V$ ,  $V_{PVIN2} = 5V$ ,  $T_A = 25^\circ C$

Figure 10. Efficiency

Figure 11. Transient Response (100mA – 1A)

Figure 12. Load Regulation

Figure 13. Line Regulation

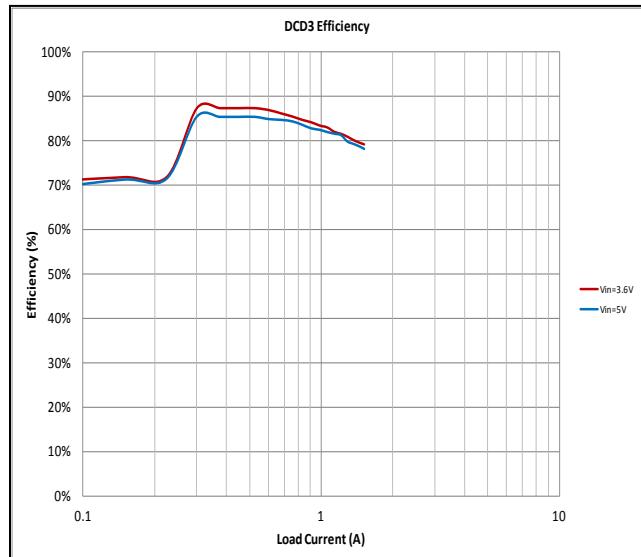

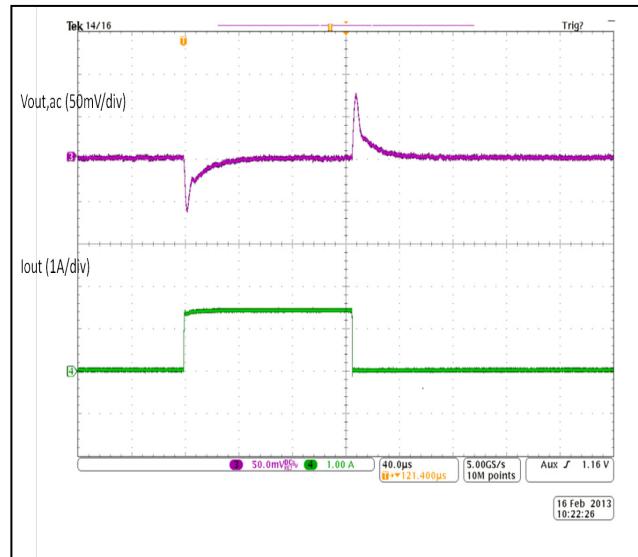

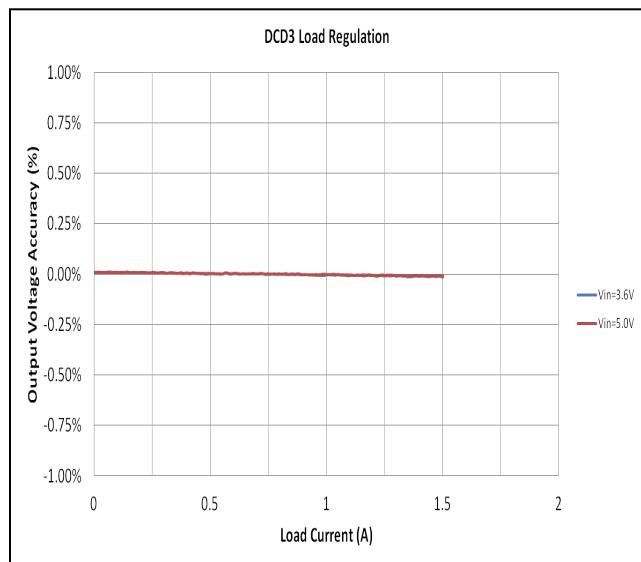

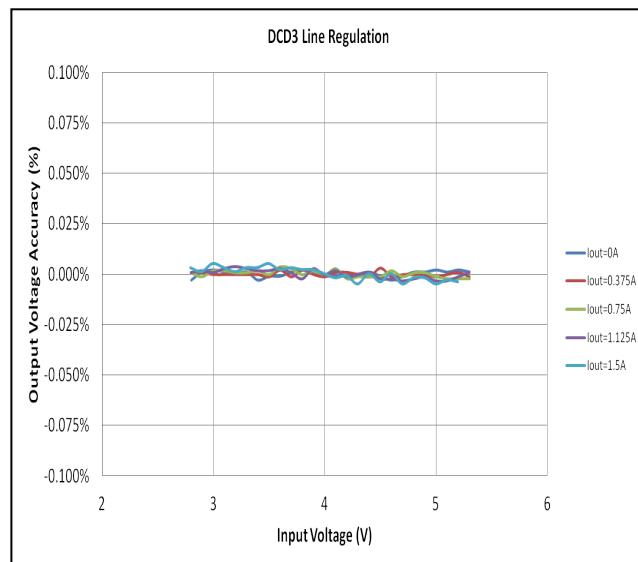

# TYPICAL PERFORMANCE CHARACTERISTICS – DCD3

$C_O(DCD3) = 22\mu F$ ,  $L = 2.2\mu H$ ,  $V_O(DCD3) = 1.35V$ ,  $V_{VIN3} = 5V$ ,  $T_A = 25^\circ C$

Figure 14. Efficiency

Figure 15. Transient Response (100mA – 1.5A)

Figure 16. Load Regulation

Figure 17. Line Regulation

# OVERVIEW OF POWER SUPPLIES

Table 20– Power Supply, Inductance, and Output Capacitance Summary

| NAME               | I <sub>OUT</sub> [A]<br>Cont/Pulse | OUTPUT                                    | V <sub>O(MIN)</sub><br>[V] | V <sub>O(MAX)</sub><br>[V] | V <sub>STEPS</sub><br>[mV] | PFM | DVS | C/L            |

|--------------------|------------------------------------|-------------------------------------------|----------------------------|----------------------------|----------------------------|-----|-----|----------------|

| DCD0 <sup>4</sup>  | 8.0/10.0                           | Programmable                              | 0.76                       | 1.55                       | 12.5                       | no  | yes | 150µF/2x0.47µH |

| DCD0a <sup>5</sup> | 4.0/5.0                            | Programmable                              | 0.76                       | 1.55                       | 12.5                       | no  | yes | 68µF/0.47µH    |

| DCD0b <sup>5</sup> |                                    |                                           |                            |                            |                            | yes | no  | 68µF/0.47µH    |

| DCD1               | 4.0/5.0                            | Programmable                              | 0.76                       | 1.55                       | 12.5                       | yes | yes | 68µF/0.47µH    |

| DCD2               | 1.5/2.1                            | Programmable                              | 0.76                       | 3.3                        | 12.5                       | yes | no  | 22µF/2.2µH     |

| DCD3               | 1.5/2.1                            | Programmable                              | 0.76                       | 3.3                        | 12.5                       | yes | no  | 22µF/2.2µH     |

| LDOTR              | 0.16/0.28                          | Programmable/<br>Tracking<br>DCD0 or DCD1 | 0.6                        | 1.5                        | 12.5                       | -   | yes | 2.2µF          |

| LDO0               | 0.2/0.26                           | Programmable                              | 1.0                        | 3.35                       | 50                         | -   | -   | 1µF            |

| LDO1               | 0.2/0.26                           | Programmable                              | 1.0                        | 3.35                       | 50                         | -   | -   | 1µF            |

| LDO2               | 0.2/0.26                           | Programmable                              | 1.0                        | 3.35                       | 50                         | -   | -   | 1µF            |

| LDO3               | 0.16/0.2                           | Programmable                              | 1.0                        | 1.475                      | 25                         | -   | -   | 2.2µF          |

| LDO4               | 0.16/0.2                           | Programmable                              | 1.0                        | 1.475                      | 25                         | -   | -   | 2.2µF          |

| LDO5               | 0.2/0.26                           | Programmable                              | 1.0                        | 3.35                       | 50                         | -   | -   | 1µF            |

| LDO6               | 0.2/0.26                           | Programmable                              | 1.0                        | 3.35                       | 50                         | -   | -   | 1µF            |

| LDO7               | 0.2/0.26                           | Programmable                              | 1.0                        | 3.35                       | 50                         | -   | -   | 1µF            |

| LDO8               | 0.2/0.26                           | Programmable                              | 1.0                        | 3.35                       | 50                         | -   | -   | 1µF            |

| LDO9               | 0.2/0.26                           | Programmable                              | 1.0                        | 3.35                       | 50                         | -   | -   | 1µF            |

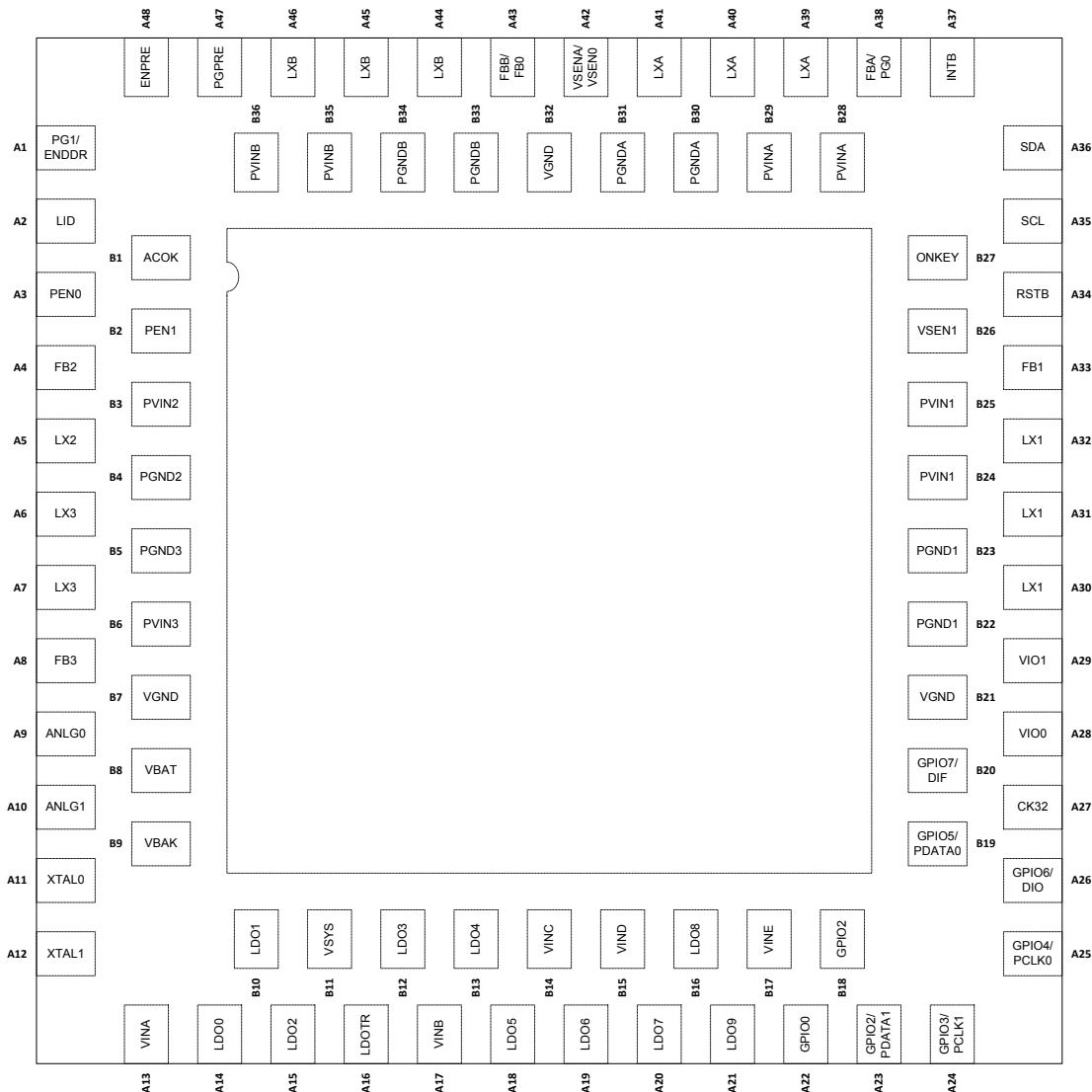

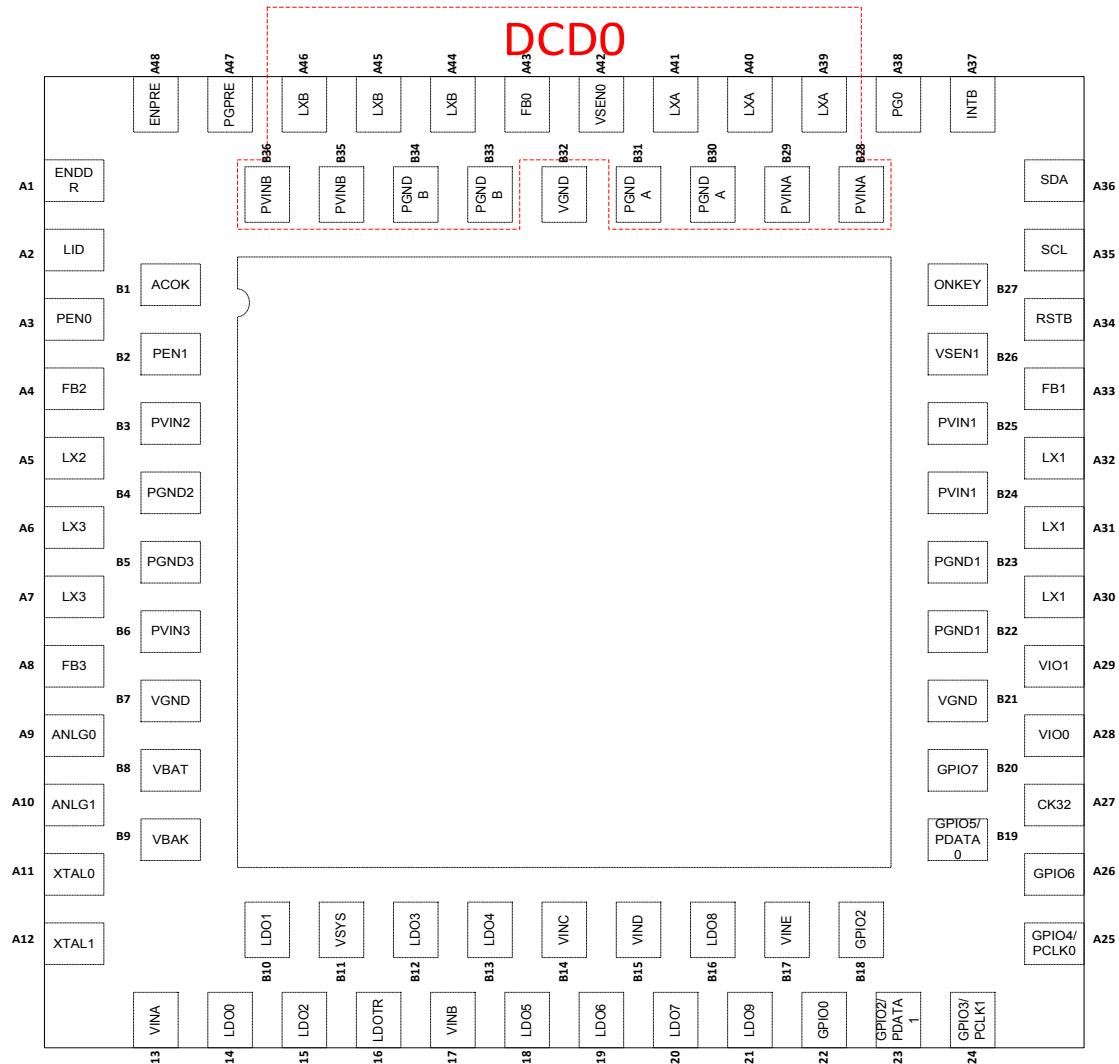

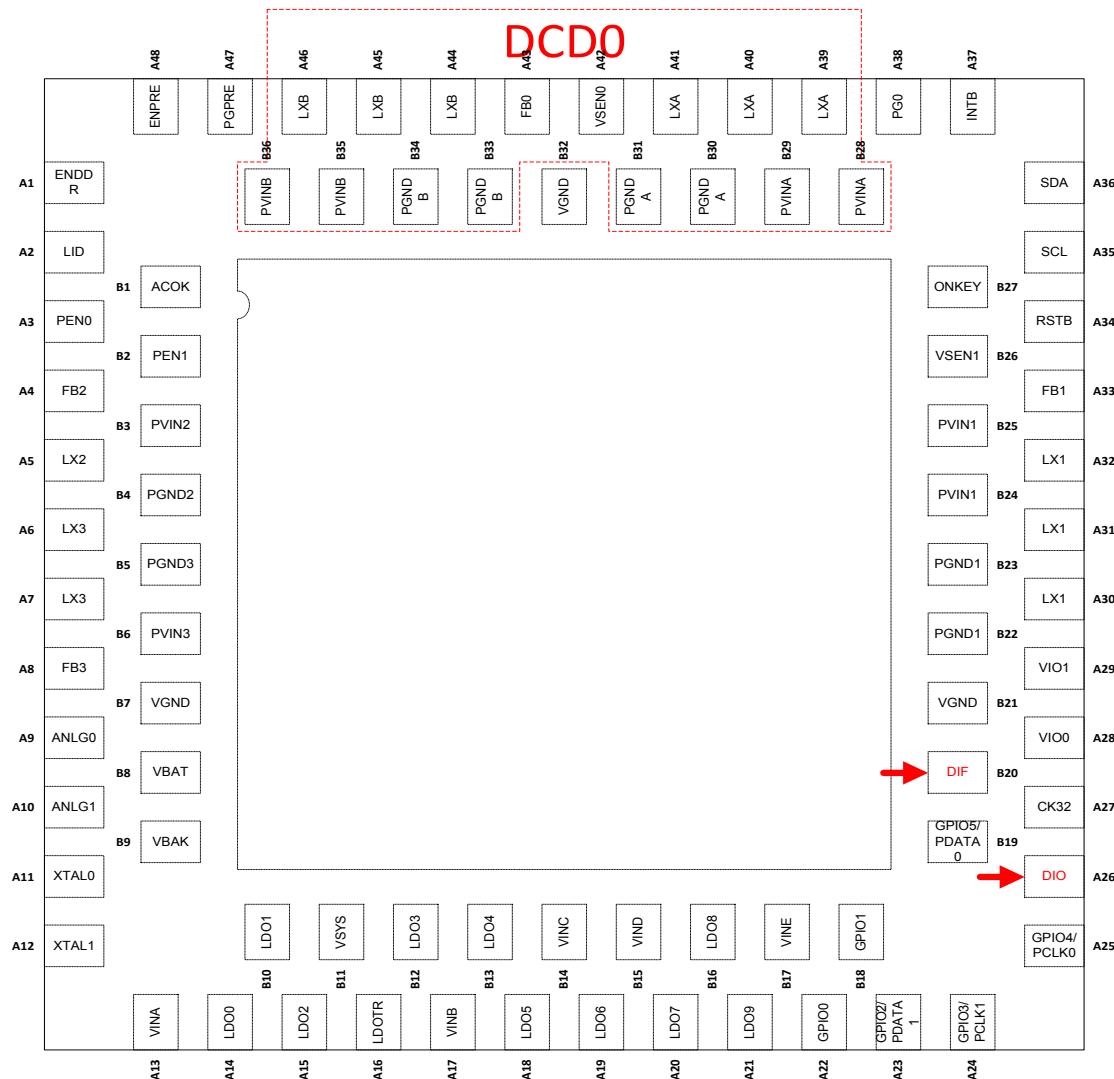

## PIN CONFIGURATION AND DESCRIPTION

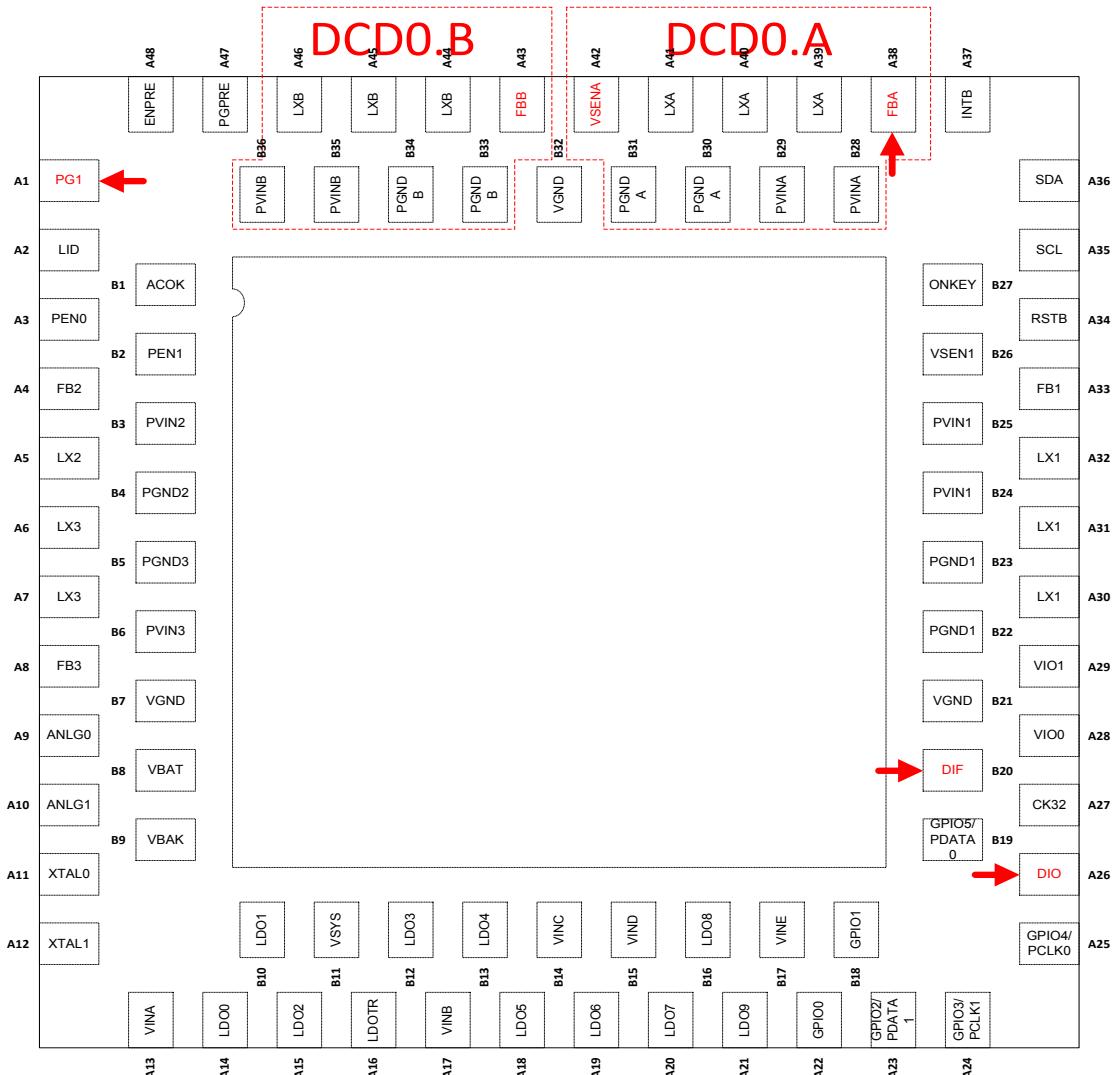

**Trim option 1:** DCD0 is a 10A Buck with DVS capability. There is no ability to control external power ICs.

**Trim option 2:** The same as option 1 with the exception that GPIO6 becomes DIO and GPIO7 becomes DIF. These are the data (DIO) and clock (DIF) serial communication lines which enable IDTP9165 to control external IDTP9167 type power ICs.

**Trim option 3:** The same as option 2 except that DCD0 is split into two 5A Bucks – DCD0a and DCD0b. Only DCD0a is capable of DVS control (as well as the usual I<sup>2</sup>C interface). DCD0b is controlled only through the I<sup>2</sup>C interface.

Figure 18 – IDTP9165 Pinout (all possible pin functions shown)

Figure 19 – IDTP9165 Pinout, Trim Option 1 (top view)

Figure 20 – IDTP9165 Pinout, Trim Option 2 (top view)

**Figure 21 – IDTP9165 Pinout, Trim Option 3 (top view)**

# DETAILED PIN CONFIGURATION

Table 21 – NQG84 Pin Functions by Pin Number

| NUMBER | LABEL        | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|--------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | ENDDR/ PG1   | DO   | Enable pin to external power supply/Power Good Pin when DCD0 is split into DCD0a,DCD0b. (The original power good pin – PG0 - becomes DCD0a feedback)                                                                                                                                                                                                                                                                     |

| A2     | LID          | DI   | Open/closed LID indication                                                                                                                                                                                                                                                                                                                                                                                               |

| A3     | PEN0         | DI   | Power Enable control input 0                                                                                                                                                                                                                                                                                                                                                                                             |

| A4     | FB2          | A    | DCD2 regulator feedback connection                                                                                                                                                                                                                                                                                                                                                                                       |

| A5     | LX2          | A    | Inductor connection to the DCD2 converter                                                                                                                                                                                                                                                                                                                                                                                |